Energy-efficient pipeline circuit templates for high performance asynchronous circuits

An asynchronous circuit and asynchronous processing technology, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve the problems of unstable equipment and difficult for synchronous designers to overcome.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

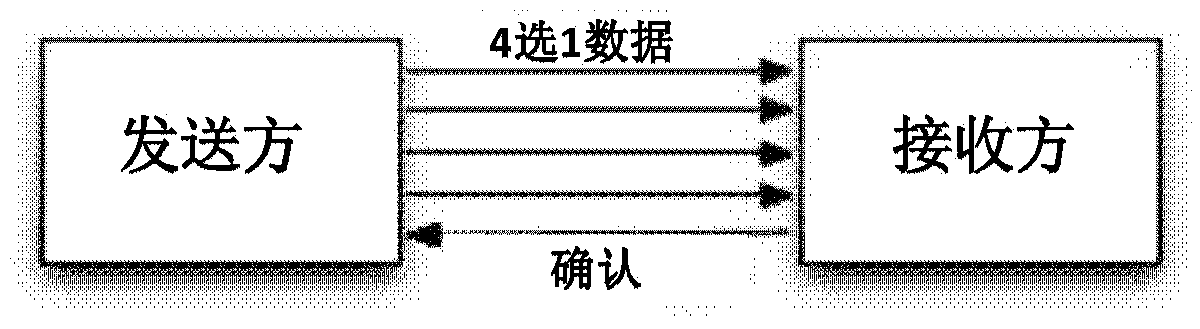

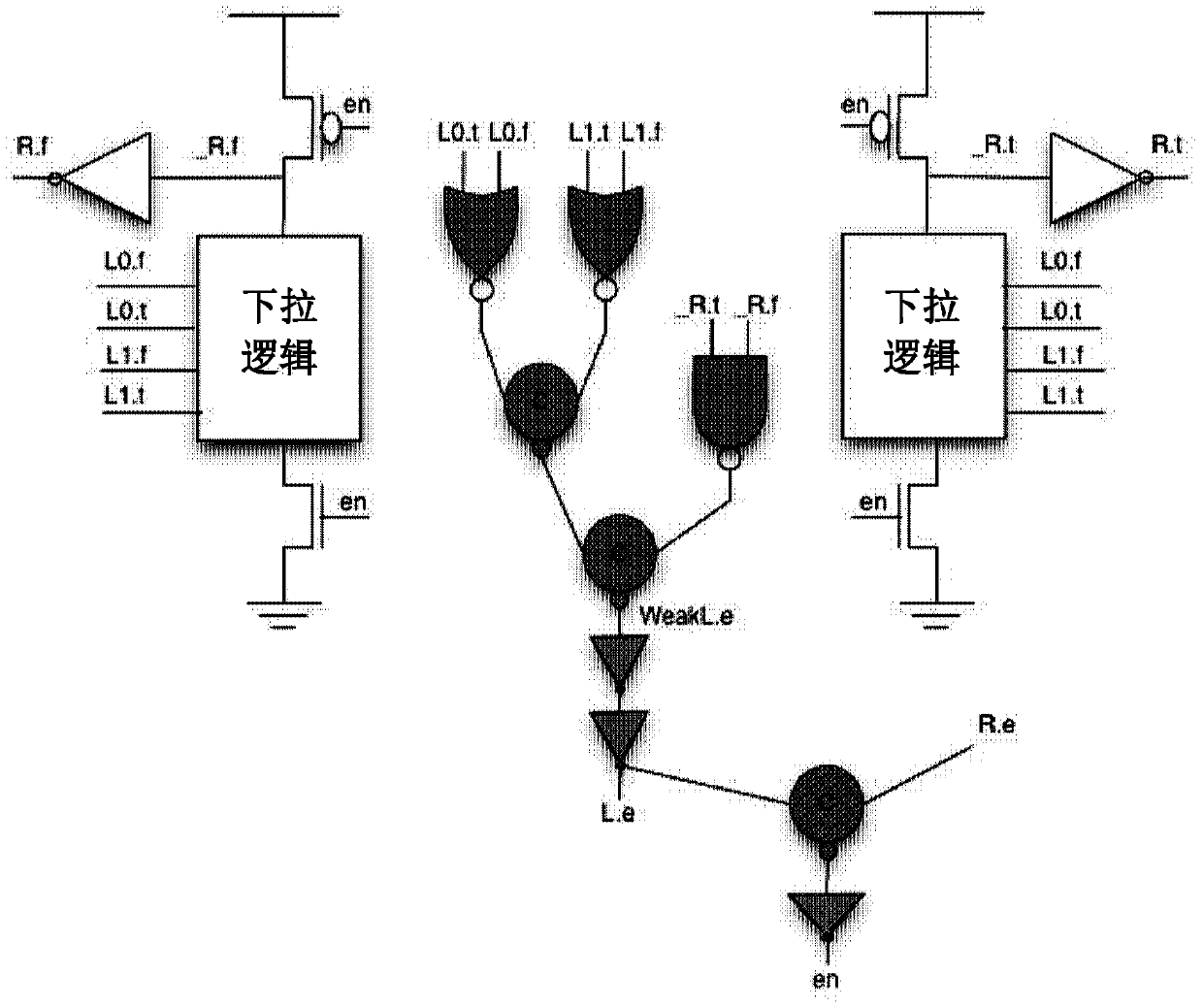

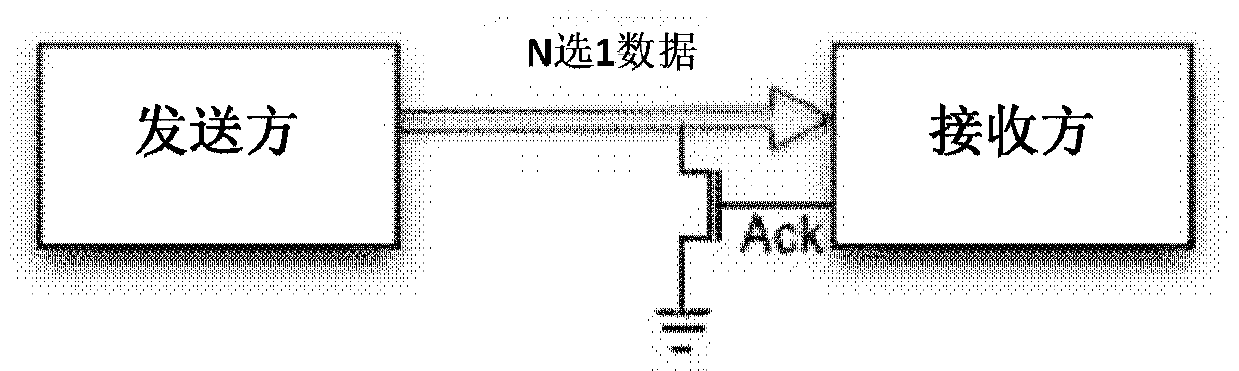

[0037]Asynchronous quasi-delay-insensitive (QDI) circuits with robustness to process variations, no global clock dependencies, and inherently perfect clock gating represent a viable design alternative for future chip designs. QDI circuits have been used in a variety of high-performance, power-efficient asynchronous designs [Sheikh and Manohar 2010] [D. Fang and Manohar 2005], including fully realized and fabricated asynchronous microprocessors [Martin et al. 1997]. QDI circuits lose some energy efficiency gains when implementing handshaking between different parallel pipeline processes. In order to ensure the QDI behavior for each handshake, each upstream and downstream transition within the pipeline is checked, which results in a lot of handshaking circuitry and energy overhead. Each stage of the high-throughput QDI pipeline consists of only a small amount of logic. The large number of pipeline stages required for high throughput makes the handshaking overhead a large part o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More