Patents

Literature

46 results about "Domino circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

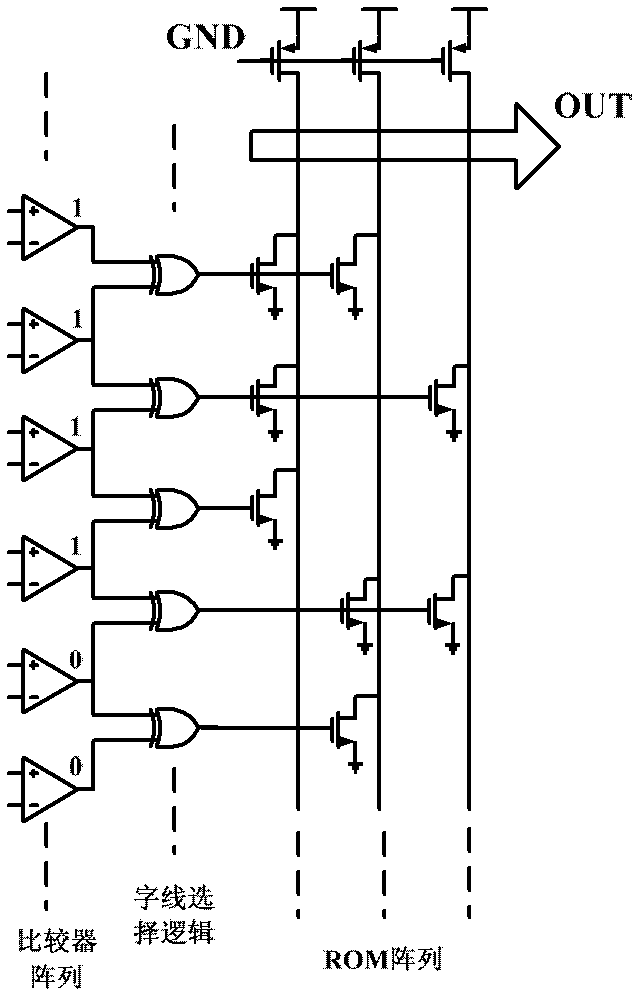

Tamper-resistant memory integrated circuit and encryption circuit using same

InactiveUS20130129083A1Improve reliabilityEliminate needRandom number generatorsDigital storageBit lineComputer architecture

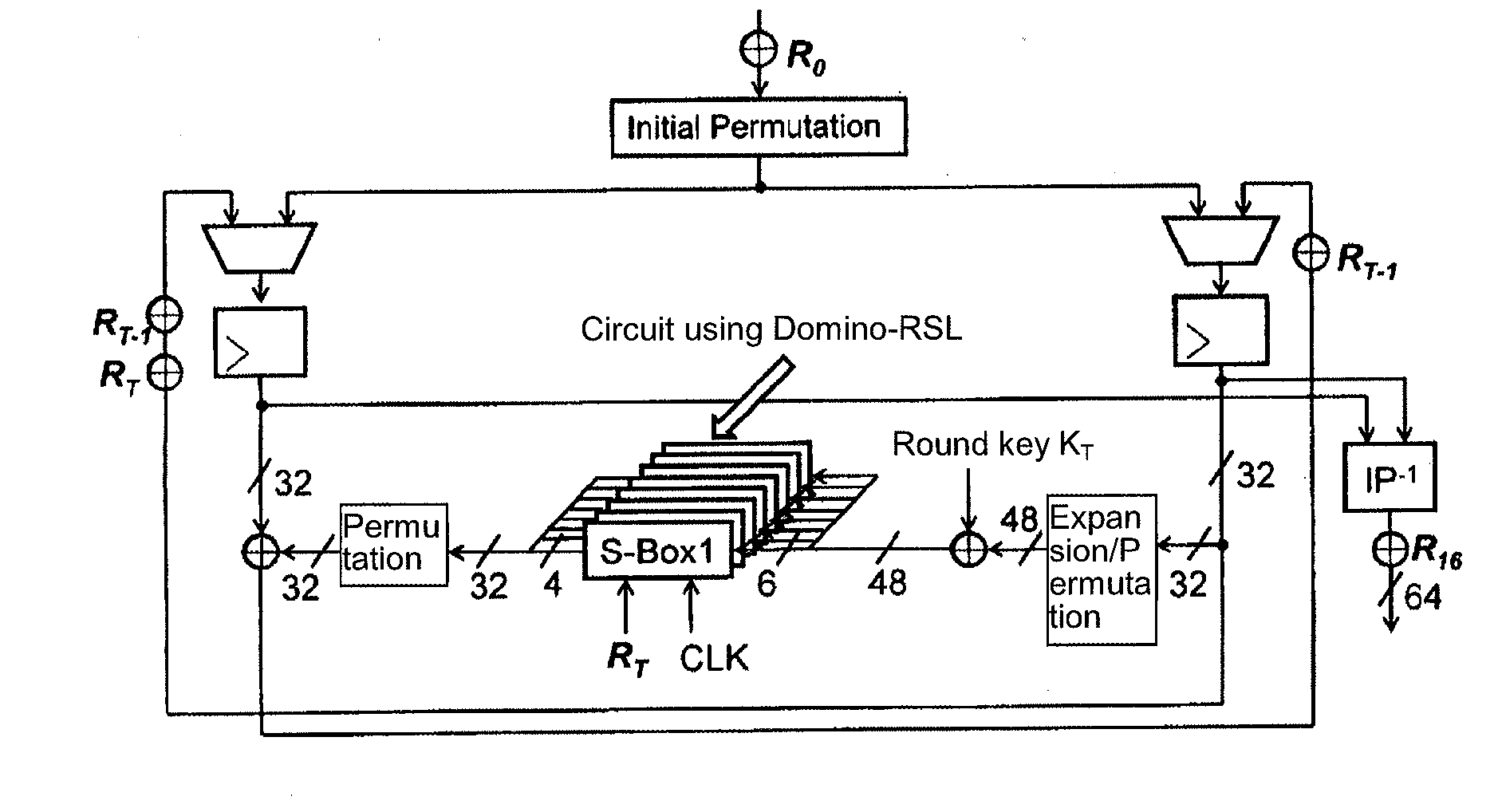

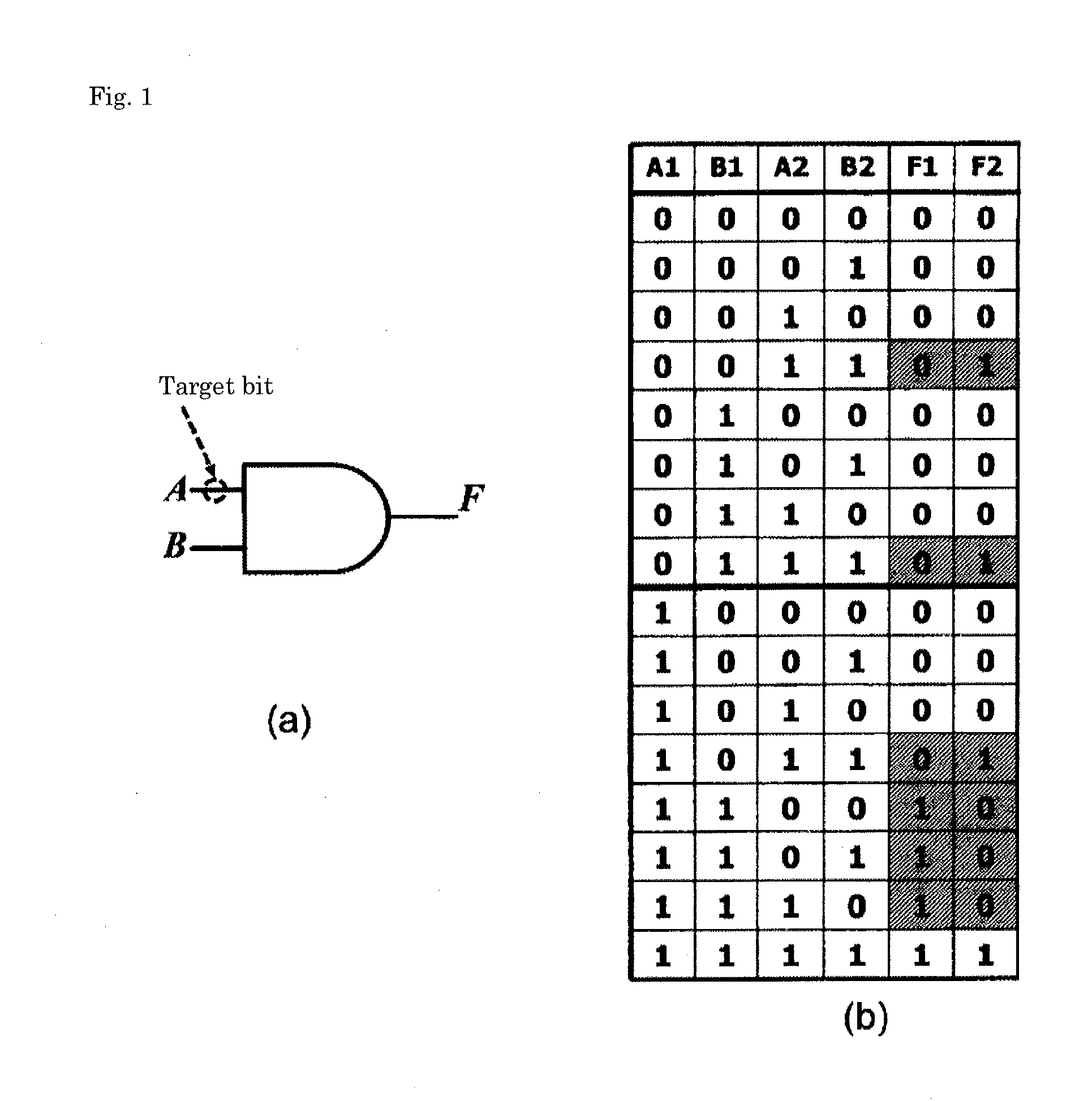

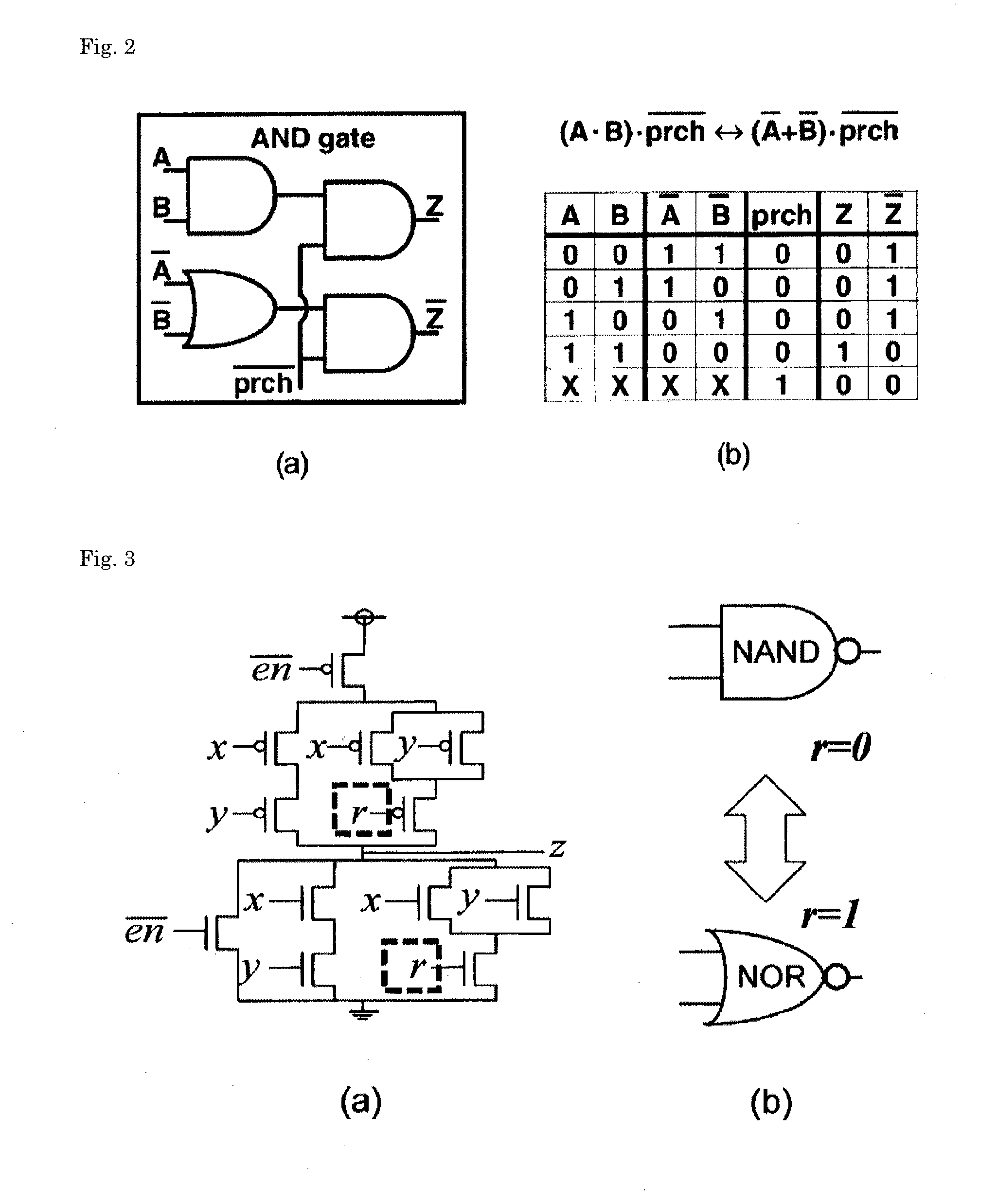

The present invention provides an integrated memory circuit applicable to an S-box of a cryptographic circuit, the integrated memory circuit having a row decoder, a column decoder, and a sense amplifier composed of a domino-RSL circuit, wherein data reading and data writing from / to memory cells of a memory cell array are performed via two complementary bit lines, and the transition probability of a signal line is equalized by input of random-number data supplied from a random-number generating circuit using an arbiter circuit.

Owner:THE RITSUMEIKAN TRUST

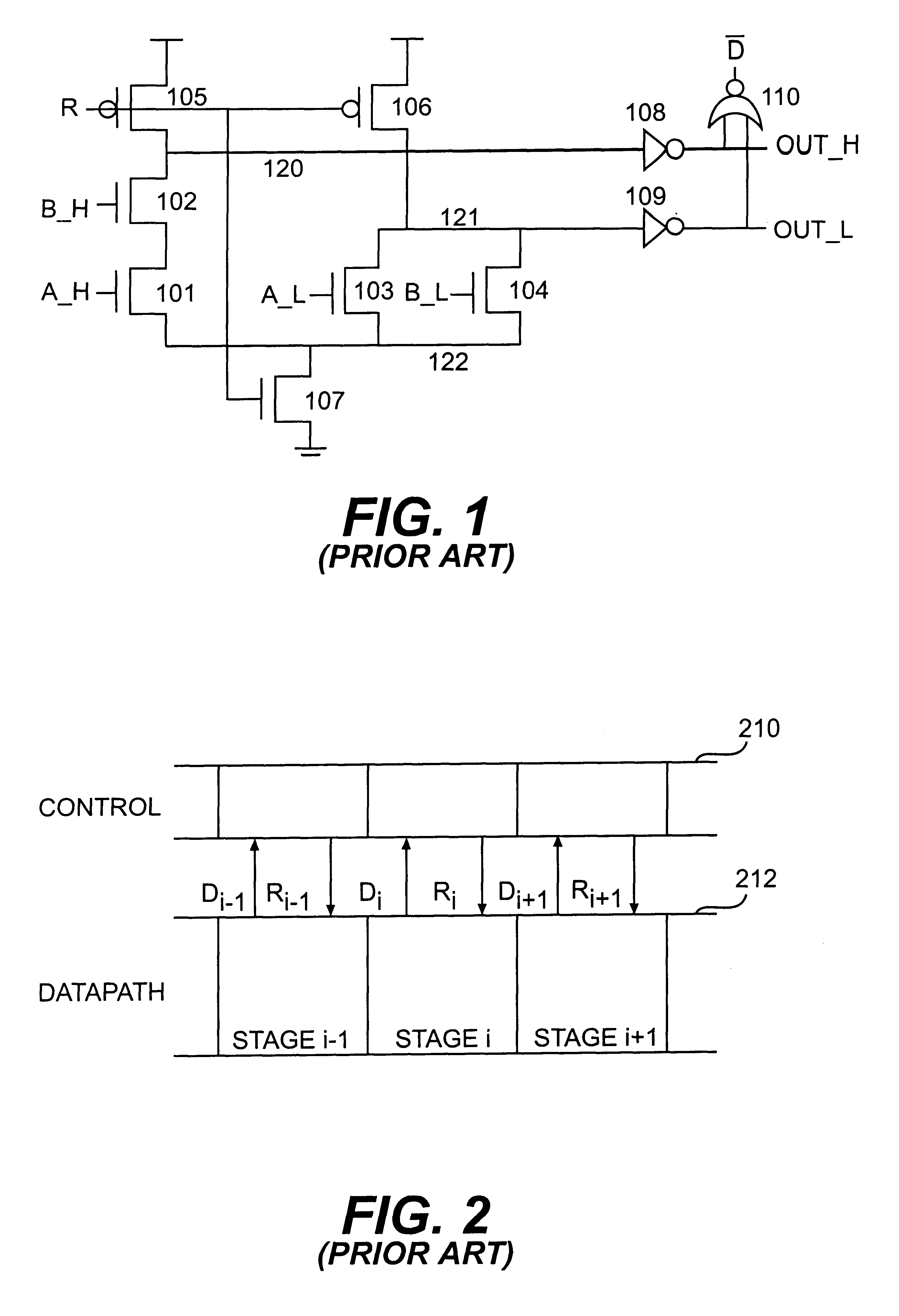

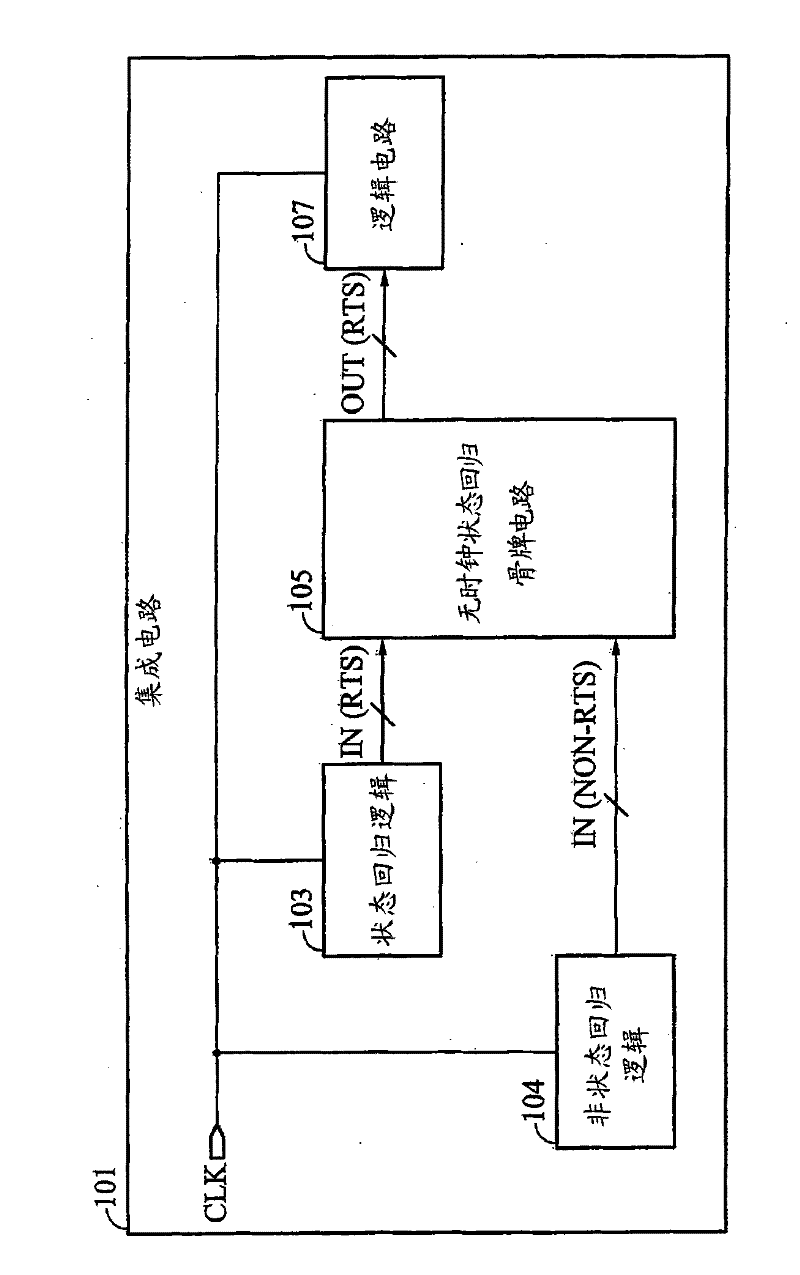

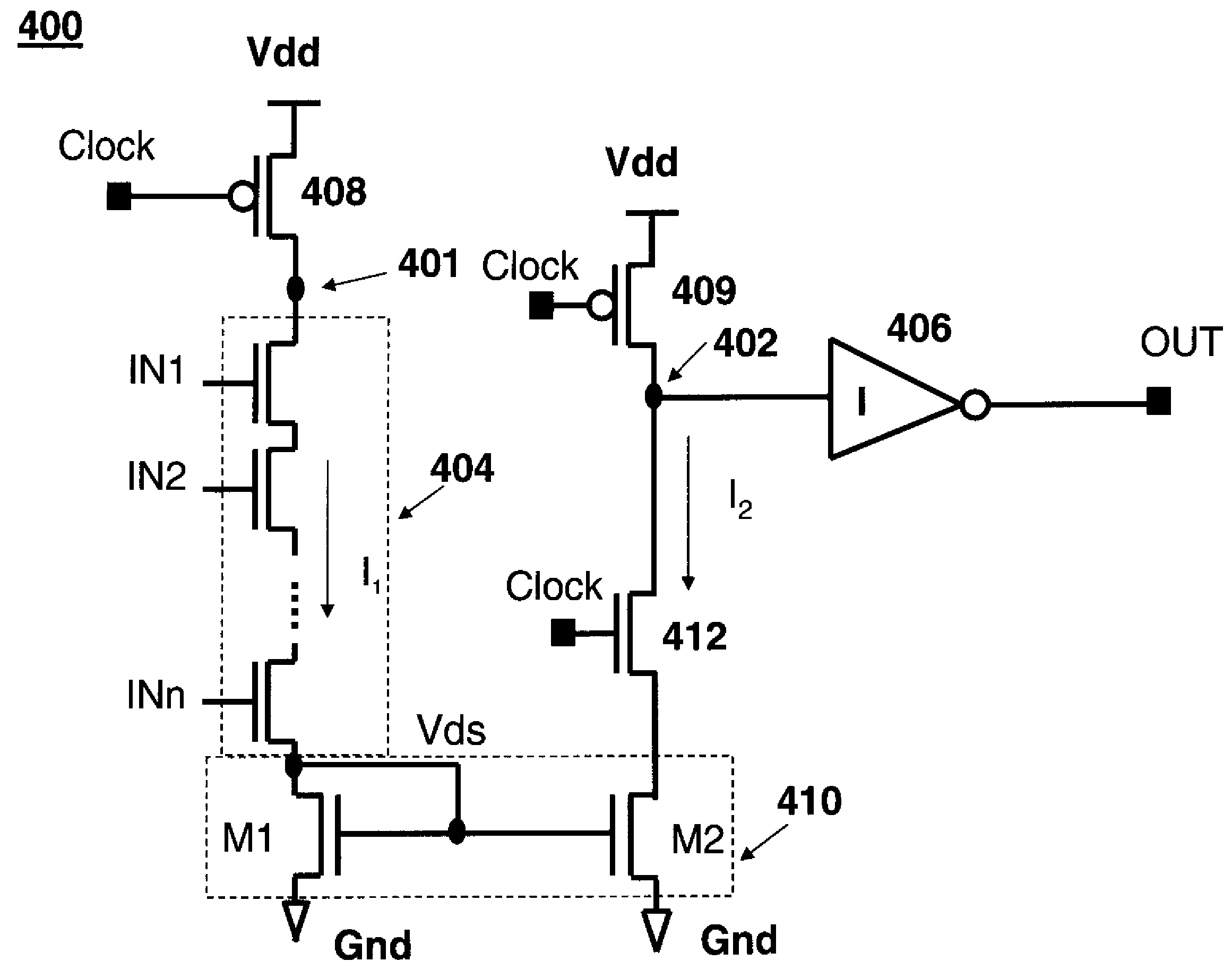

Multistage dynamic domino circuit with internally generated delay reset clock

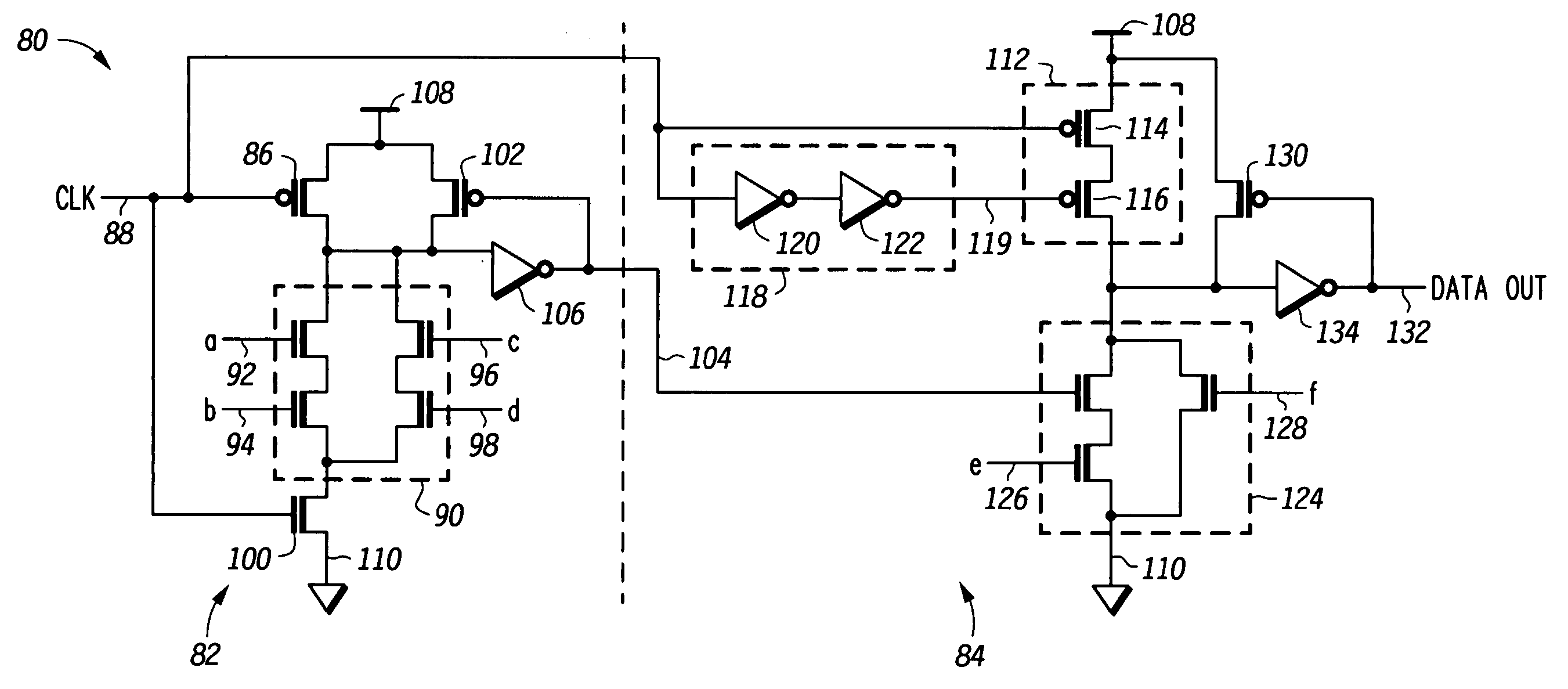

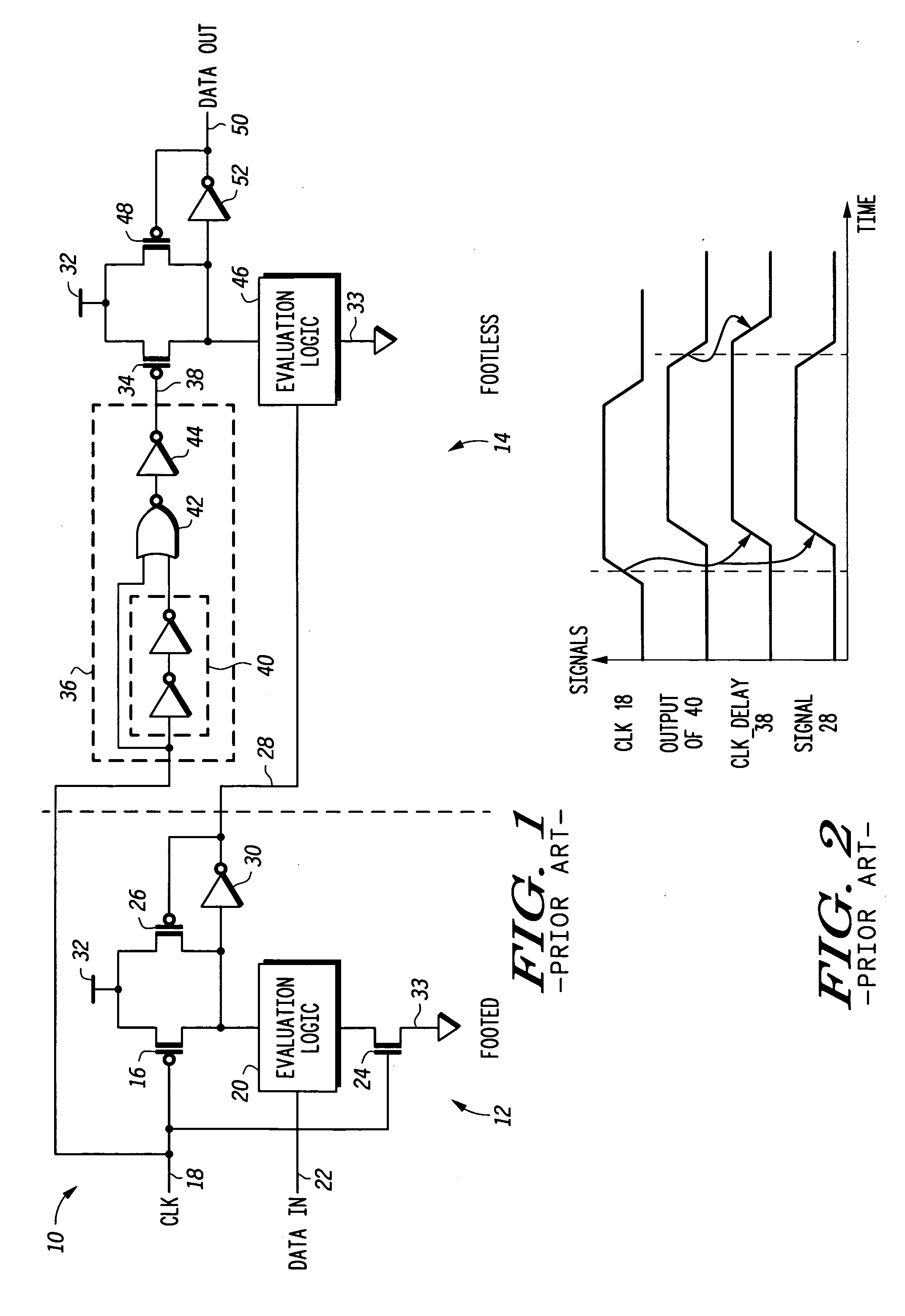

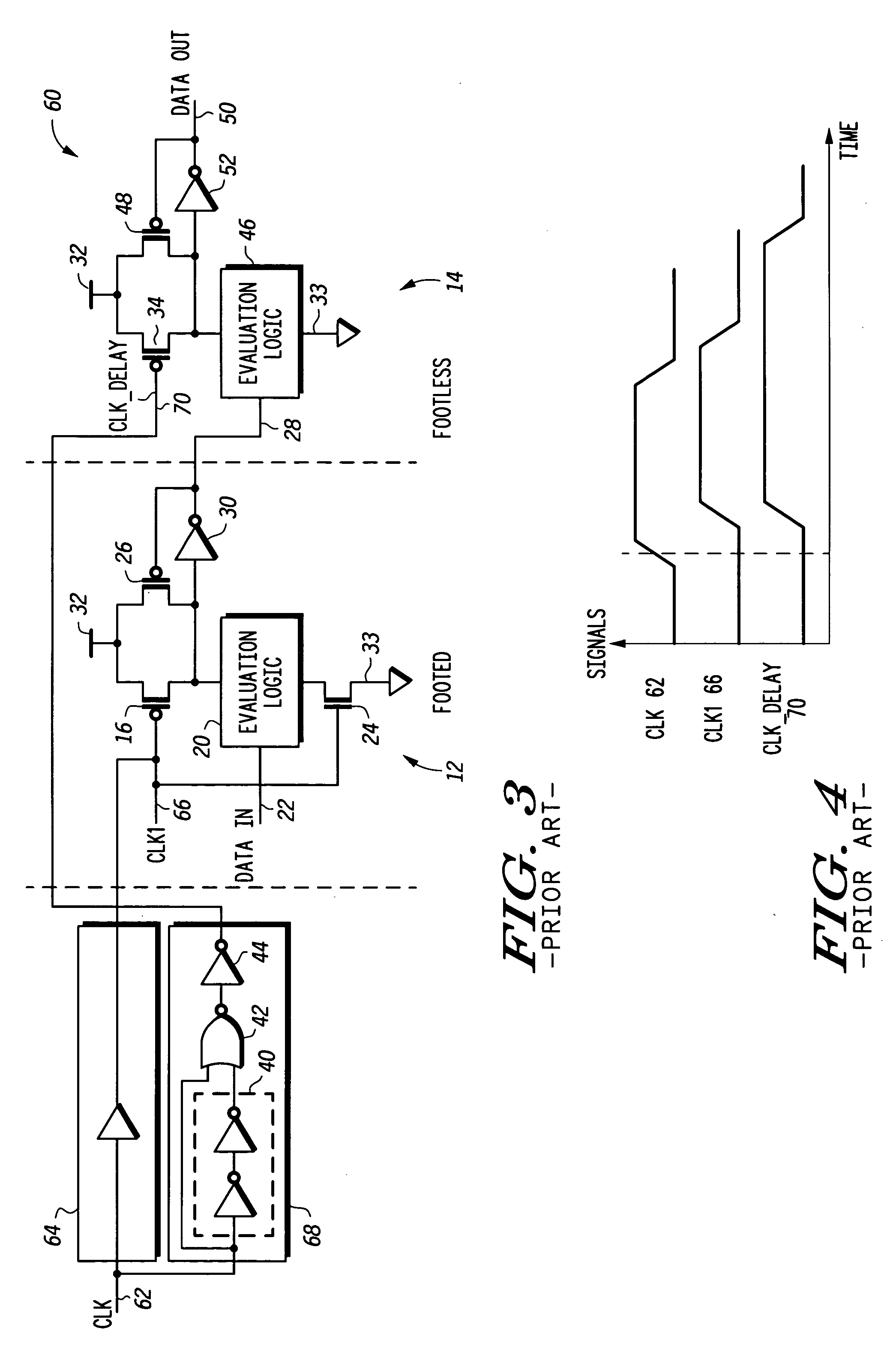

A multistage dynamic domino circuit includes a footed dynamic domino stage, a footless dynamic domino stage, and a internal delay circuit. The footed dynamic domino stage includes a first precharge circuit, evaluation logic, and a data output coupled to the evaluation logic. The footless dynamic domino stage includes evaluation logic including a data input coupled to the data output of the footed dynamic domino stage and a second precharge circuit. The second precharge circuit includes a first precharge device including a first current terminal and a control terminal coupled to a clock line. The second precharge circuit further includes a second precharge device including a first current terminal coupled to the first current terminal of first precharge device and a control terminal. The delay circuit includes an input coupled to the clock line and an output coupled to the control terminal of the second precharge device to provide a delayed version of a clock signal provided at the input of the delay circuit.

Owner:FREESCALE SEMICON INC

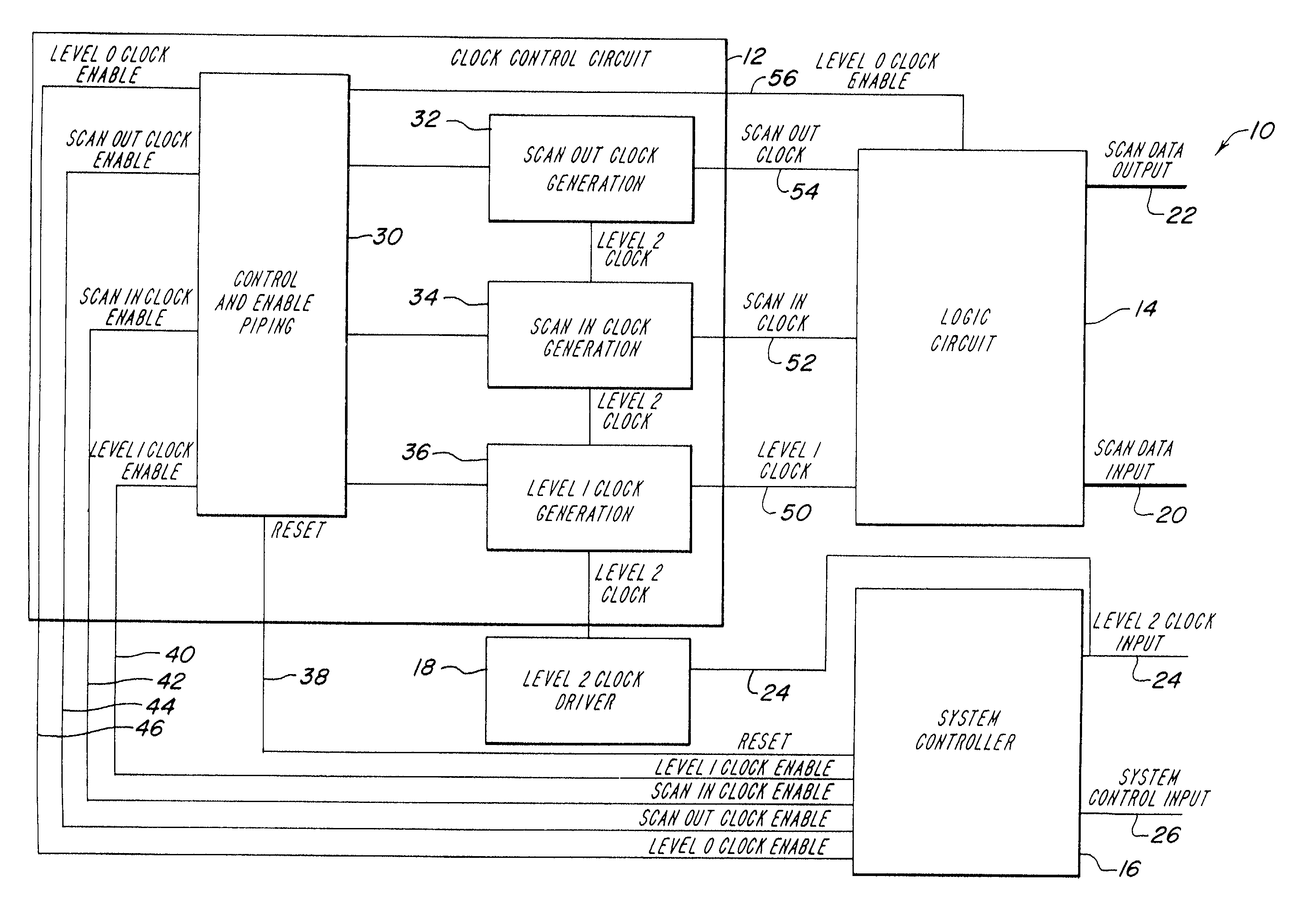

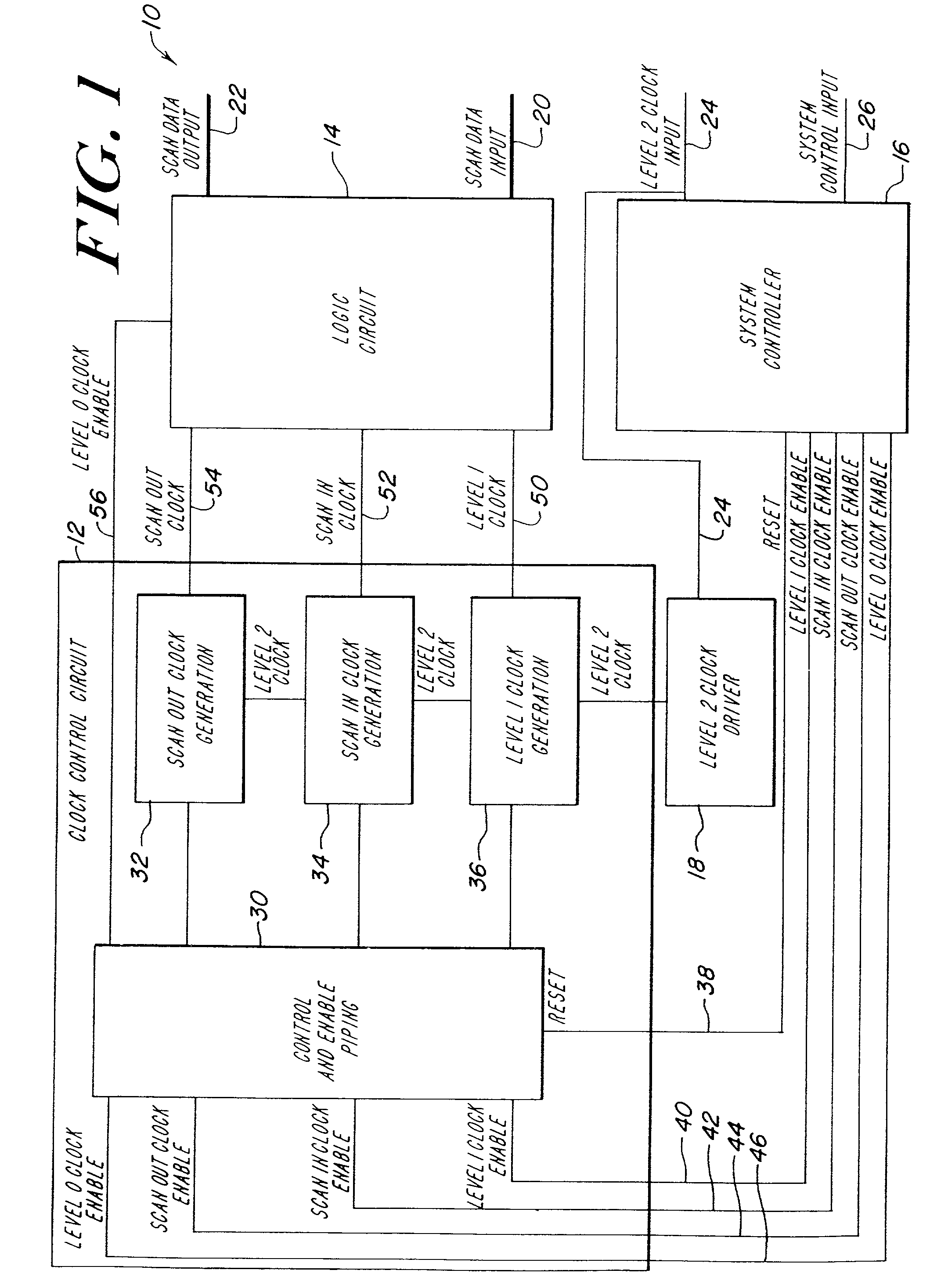

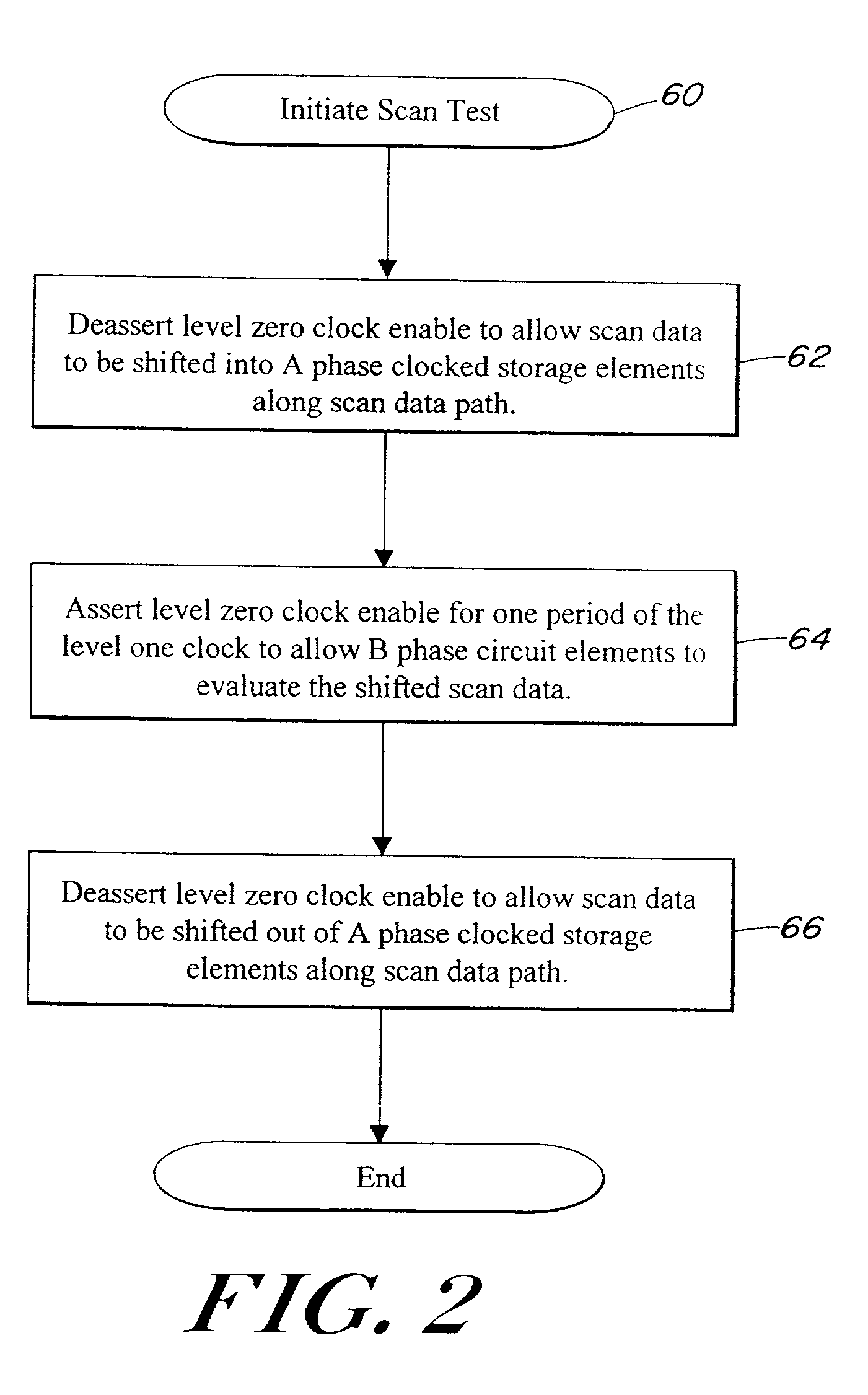

Method for scan testing and clocking dynamic domino circuits in VLSI systems using level sensitive latches and edge triggered flip flops

InactiveUS7000164B2Impacting speedImpacting efficiencyElectronic circuit testingGenerating/distributing signalsMultiplexerVlsi systems

A system and method is provided for scan control and observation of a logical circuit that does not halt the operation of the system clock. Thus, all dynamic circuits within the system continue to evaluate and precharge normally. Moreover, the traditional method of placing a multiplexer before the data input of a clocked storage element to perform scan control and observation is no longer required. Consequently, the system and method provide a more efficient manner in which to perform scan control and observation of a logical circuit.

Owner:ORACLE INT CORP

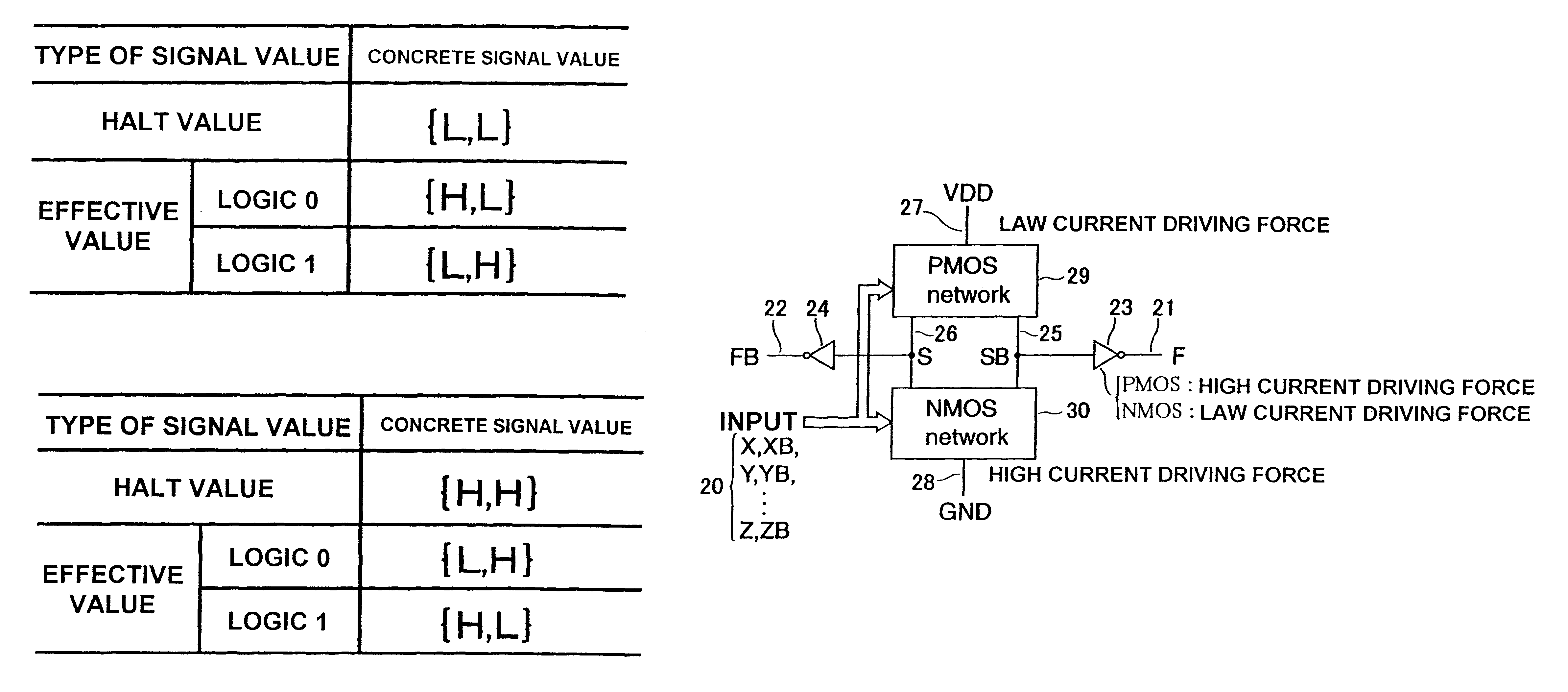

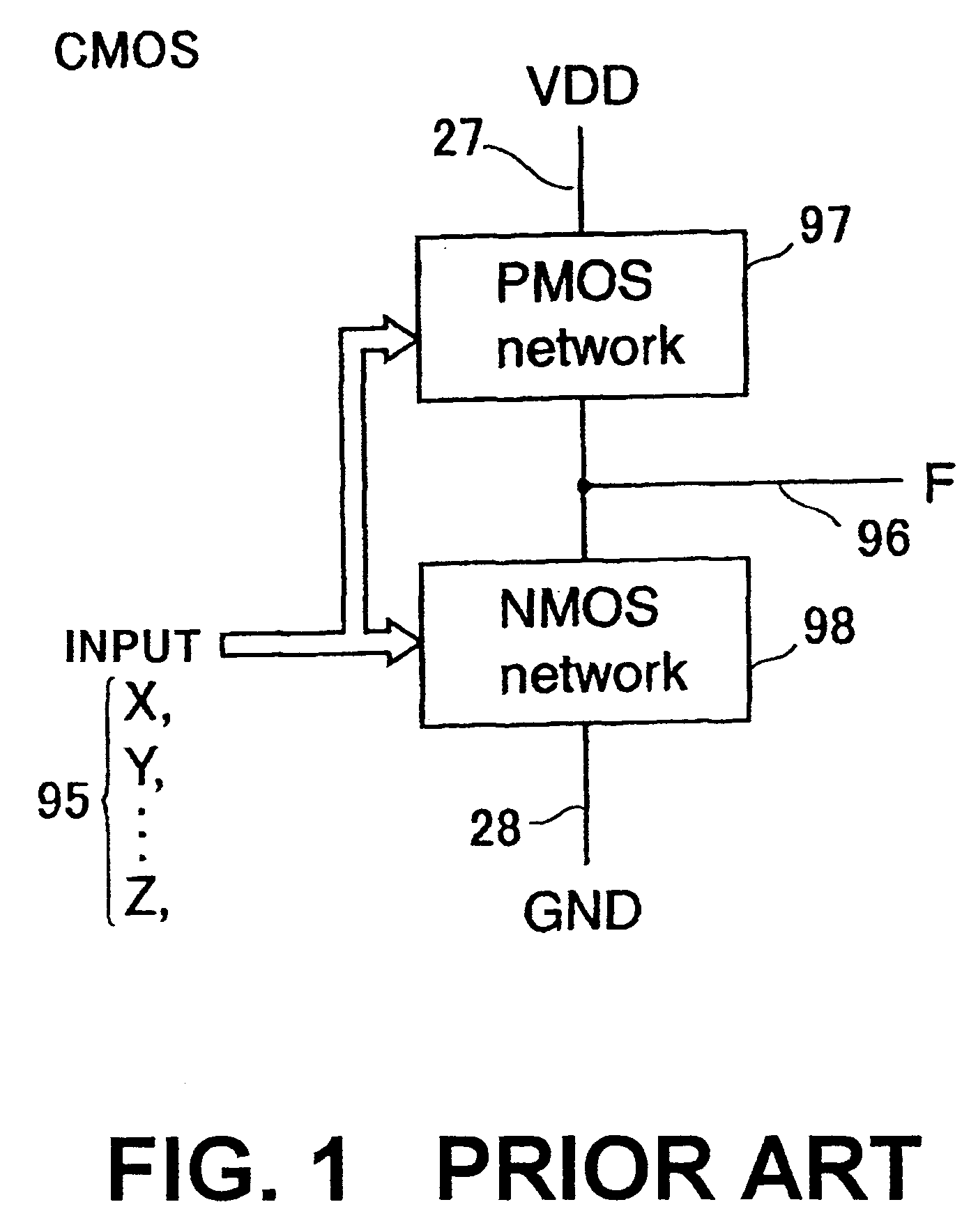

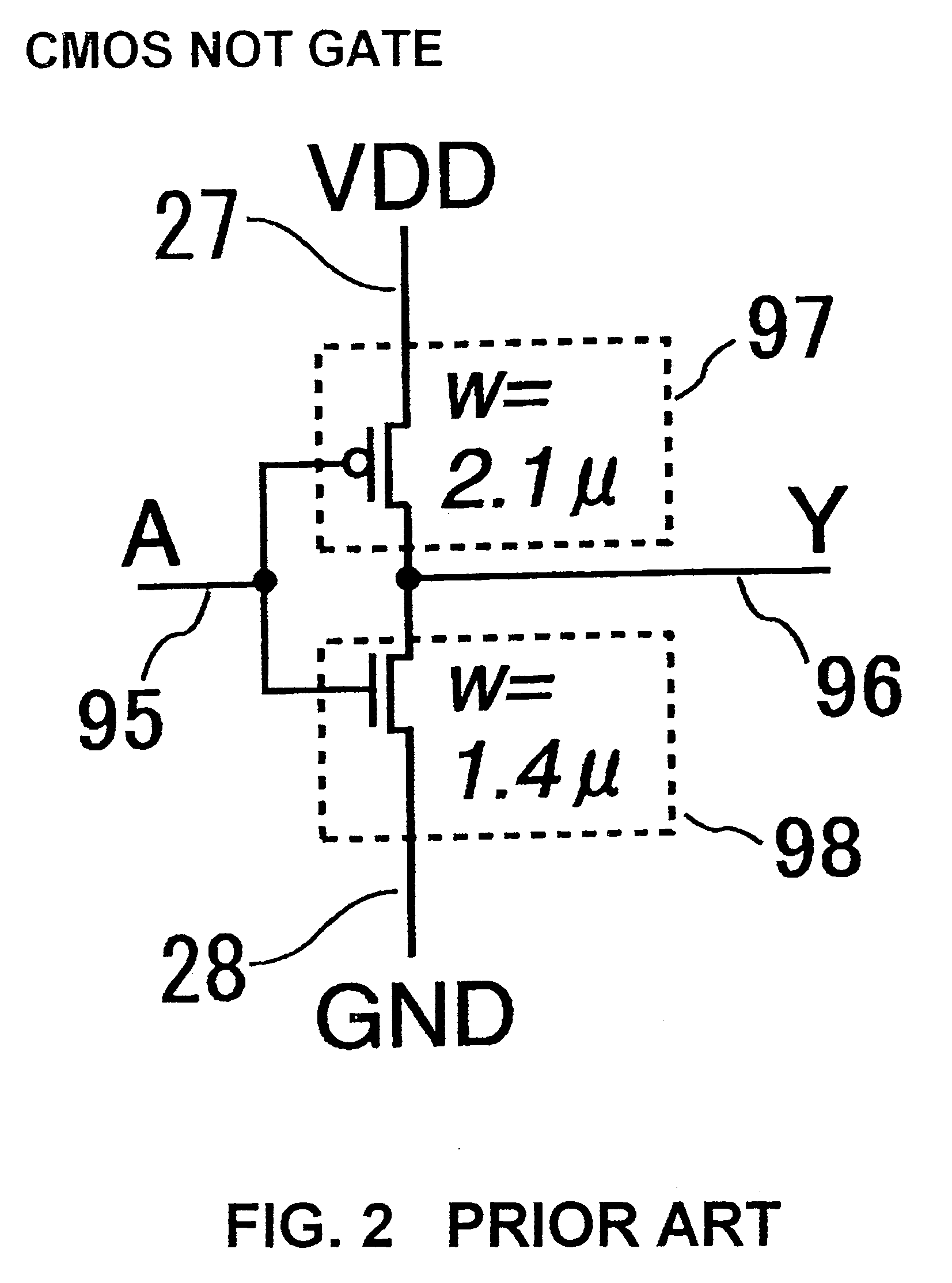

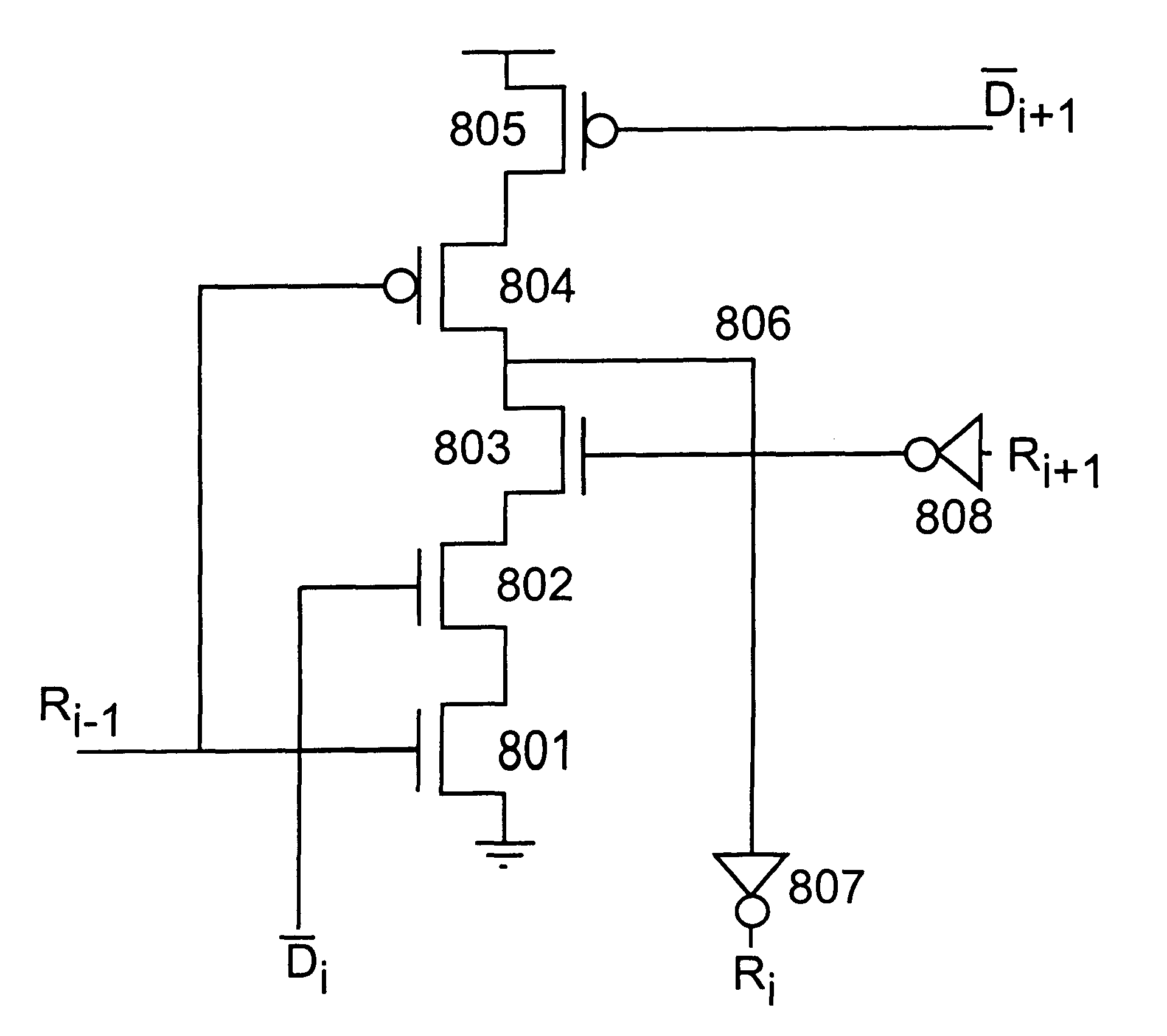

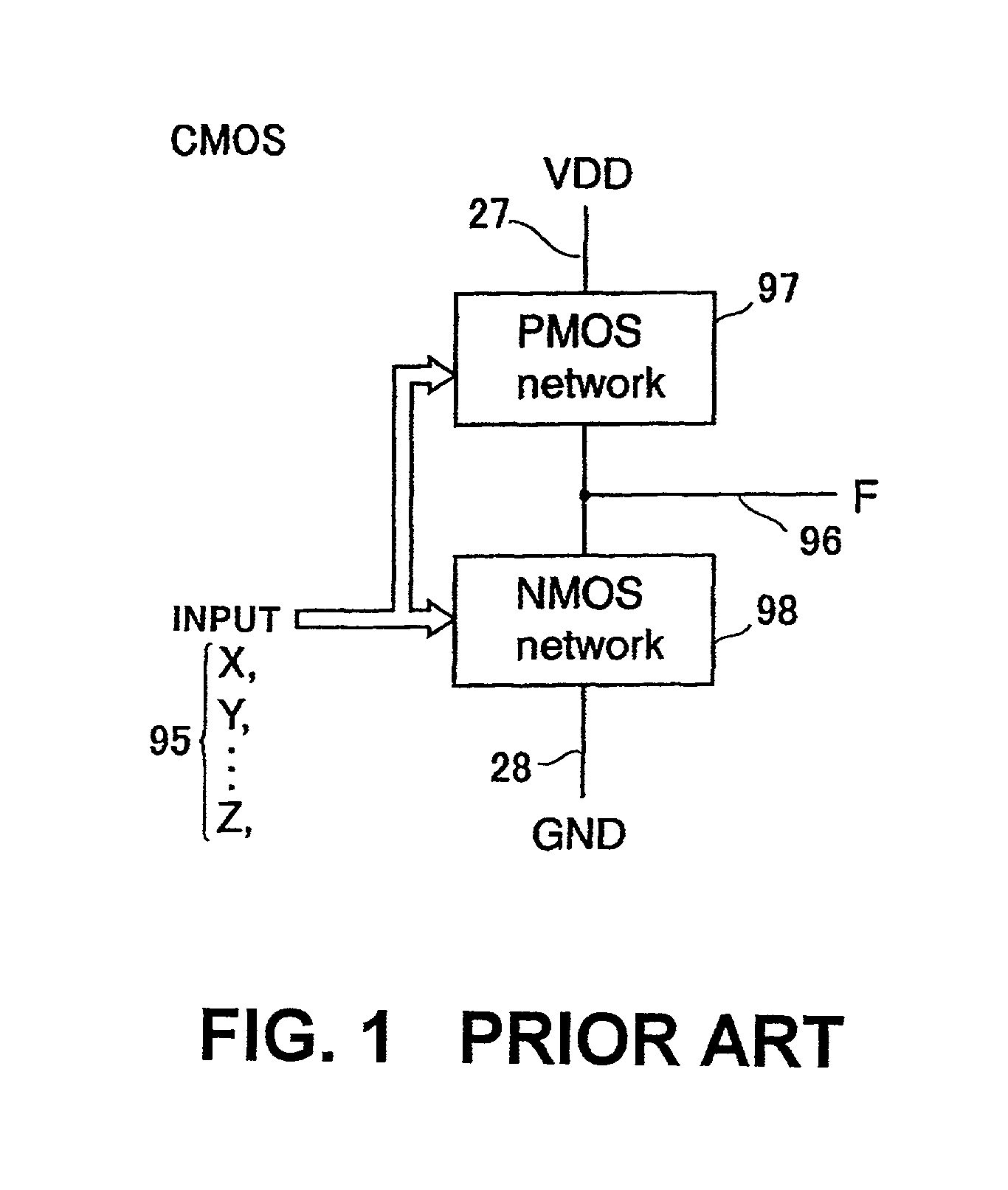

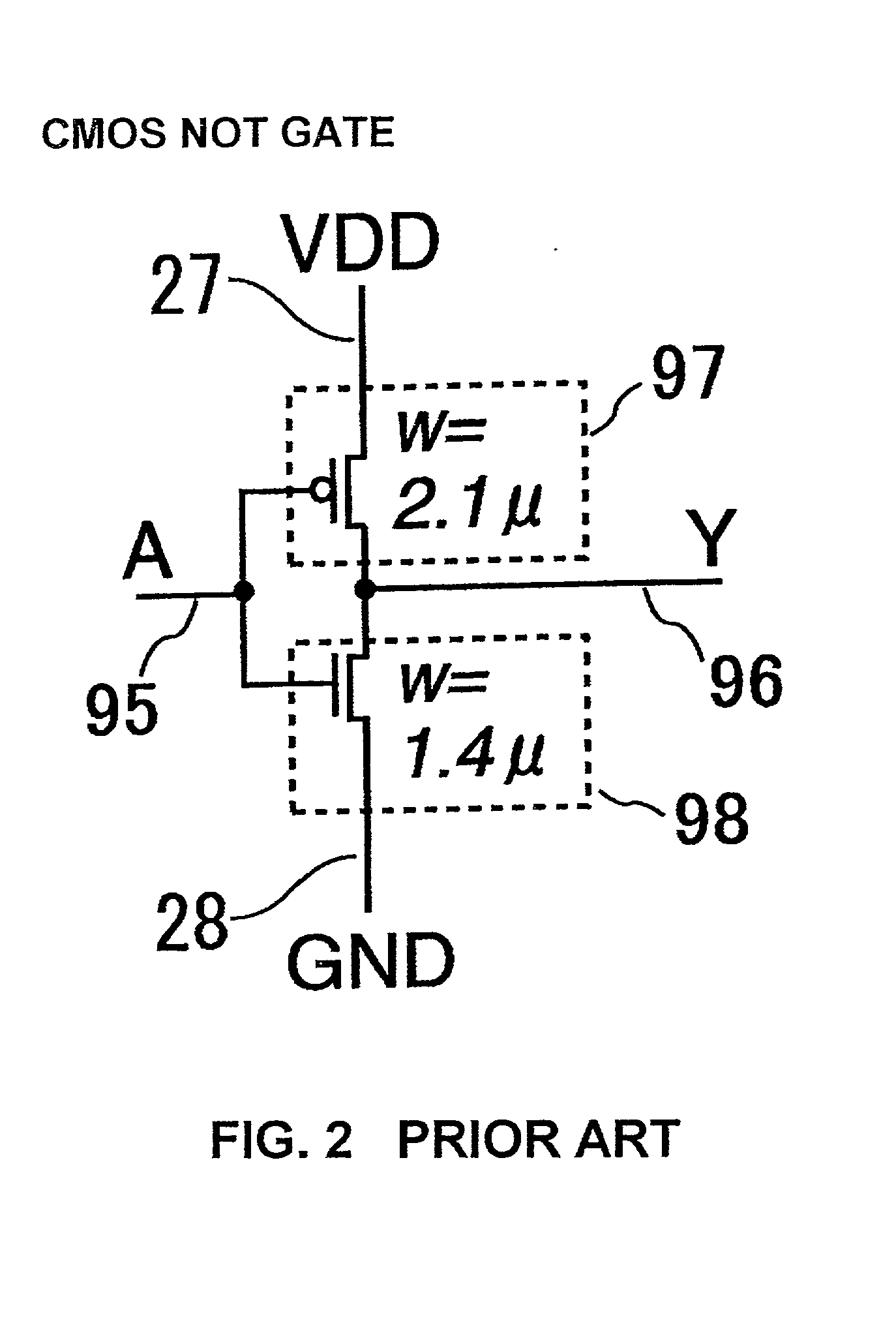

Logical circuit

InactiveUS6509761B2Logic circuits characterised by logic functionComputation using non-contact making devicesDelayed timeValid Value

Very high speed operation and reduction of power consumption are realized simultaneously in a two-wire type logical circuit having a halt value and an effective value as signal values. Signal rise transition delay time and signal fall transition delay time are purposely designed asymmetrically and an effective value propagation delay is shortened, thereby accelerating an operating speed of the logical circuit. By eliminating a clock signal from a DOMINO circuit, power consumption is reduced. An architecture for concealing a halt value propagation delay is employed.

Owner:A I L

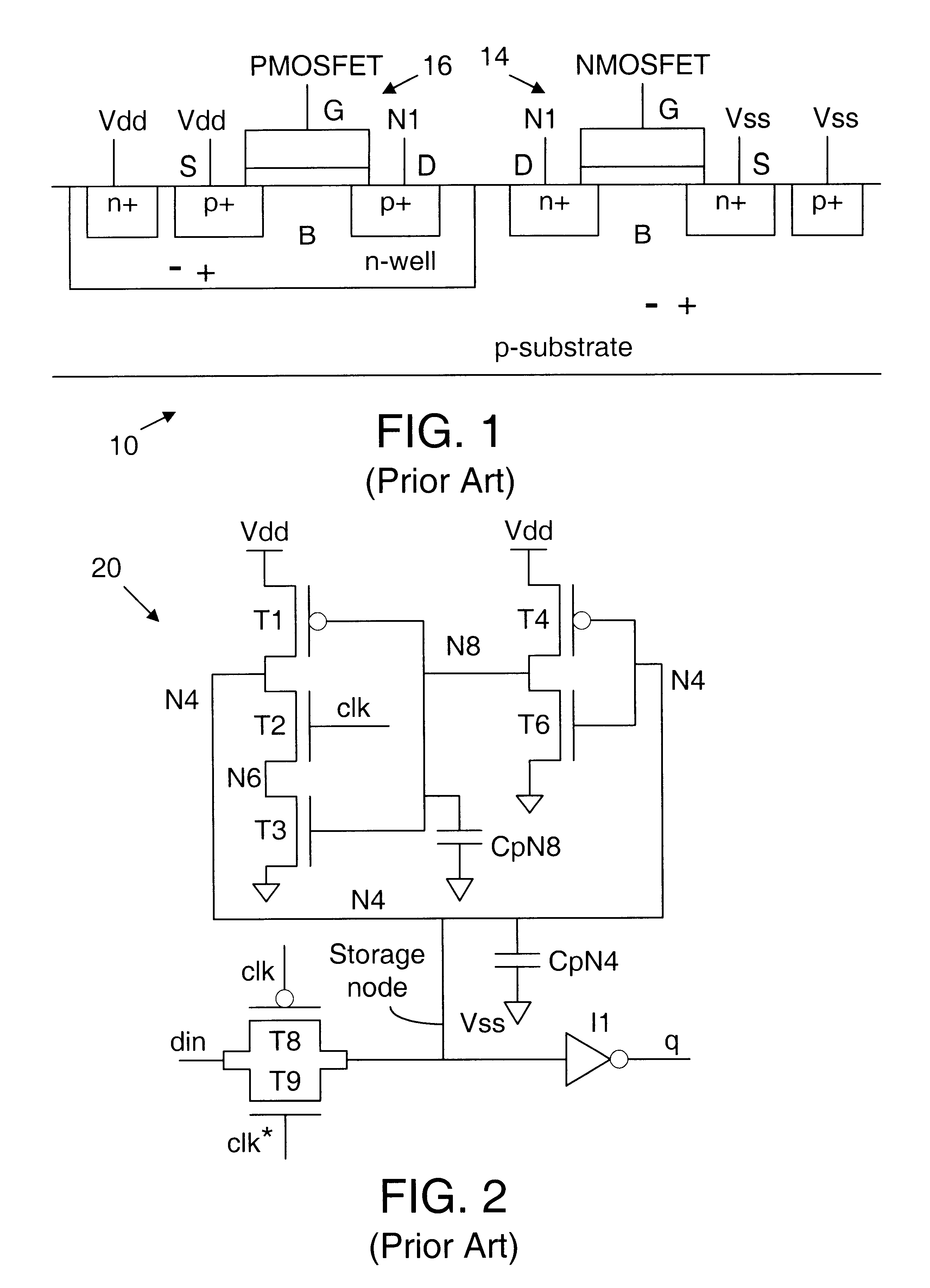

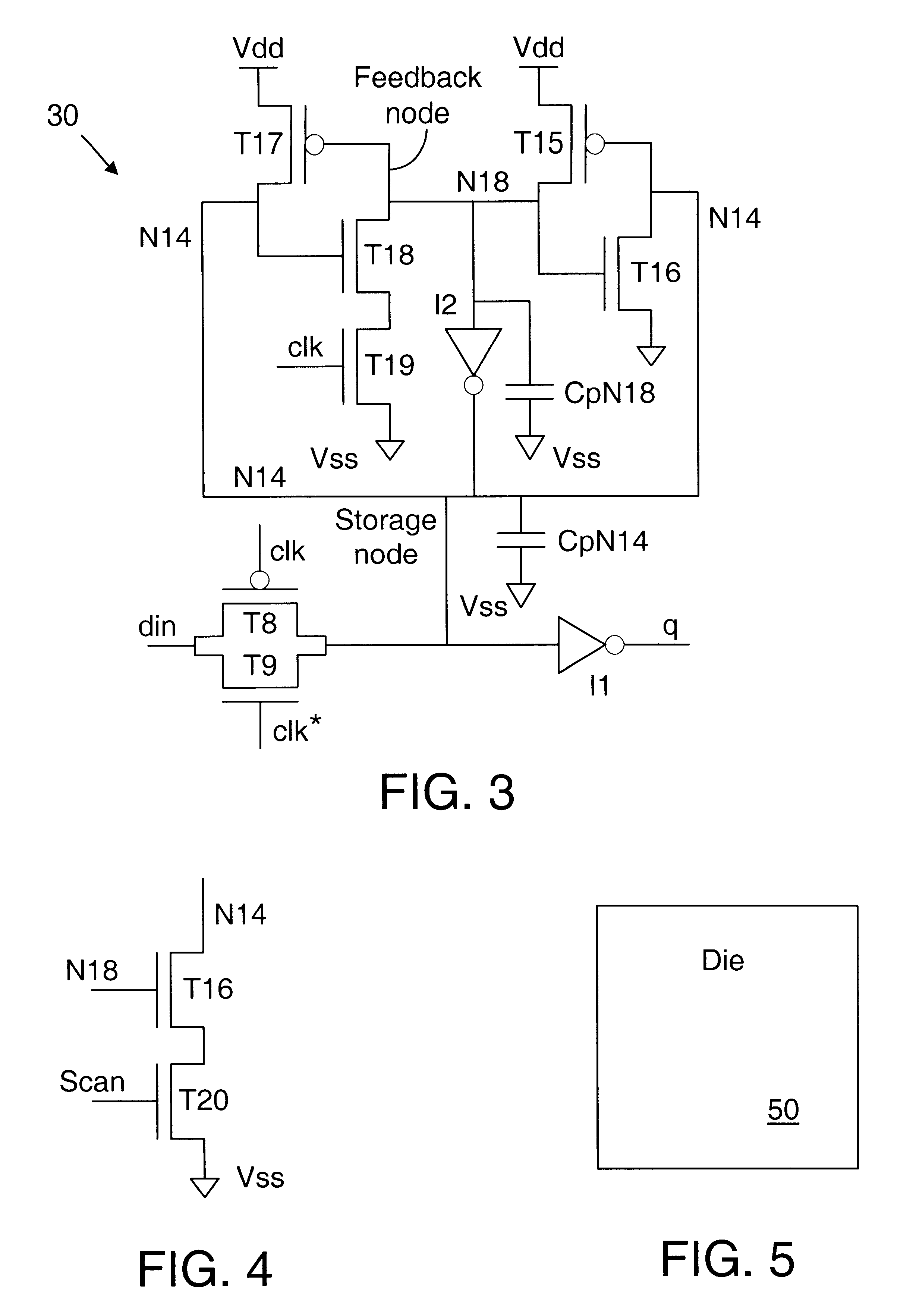

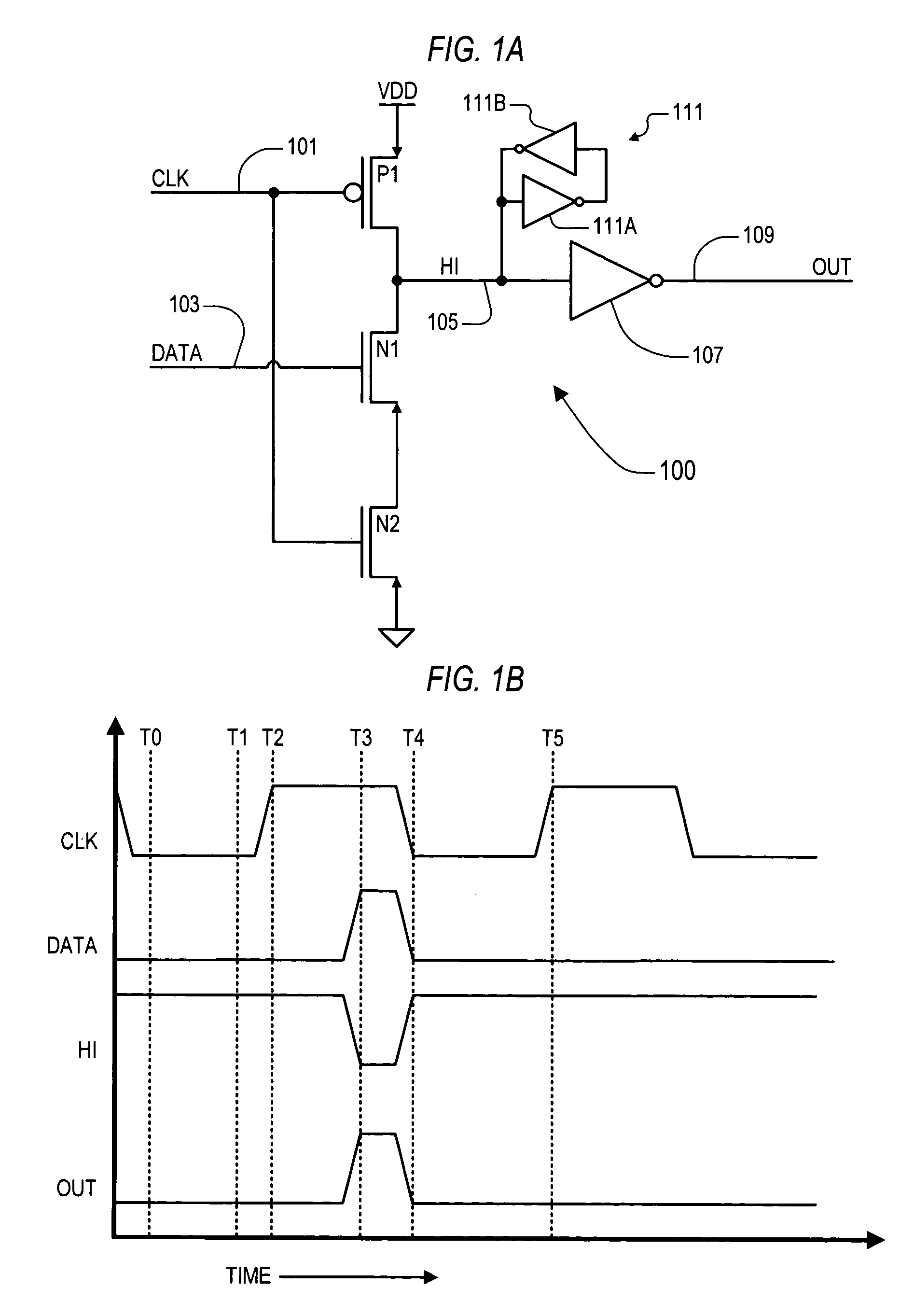

Soft error resistant circuits

InactiveUS6366132B1Reliability increasing modificationsLogic circuits characterised by logic functionReverse connectionComputer science

In some embodiments, the invention includes a soft error resistant latch circuit. The latch circuit includes a storage node, a feedback node, and an inverter between the storage node and the feedback node. The latch circuit also includes split connection storage node drivers and split connection feedback node drivers each connected to the storage node and the feedback node. In some embodiments, the invention includes a soft error resistant domino circuit a domino node, a keeper node, and a soft error resistant keeper. The soft error resistant keeper includes (a) a FET having a gate connected to the keeper node; (b) a FET having a gate connected to the domino node; and (c) an inverter between the domino and keeper nodes. In some embodiments, the invention includes a soft error resistant domino circuit having a domino node, a keeper node, and an inverter between the domino and keeper nodes. The circuit also includes reverse connection keeper drivers connected between the domino node and the keeper node.

Owner:INTEL CORP

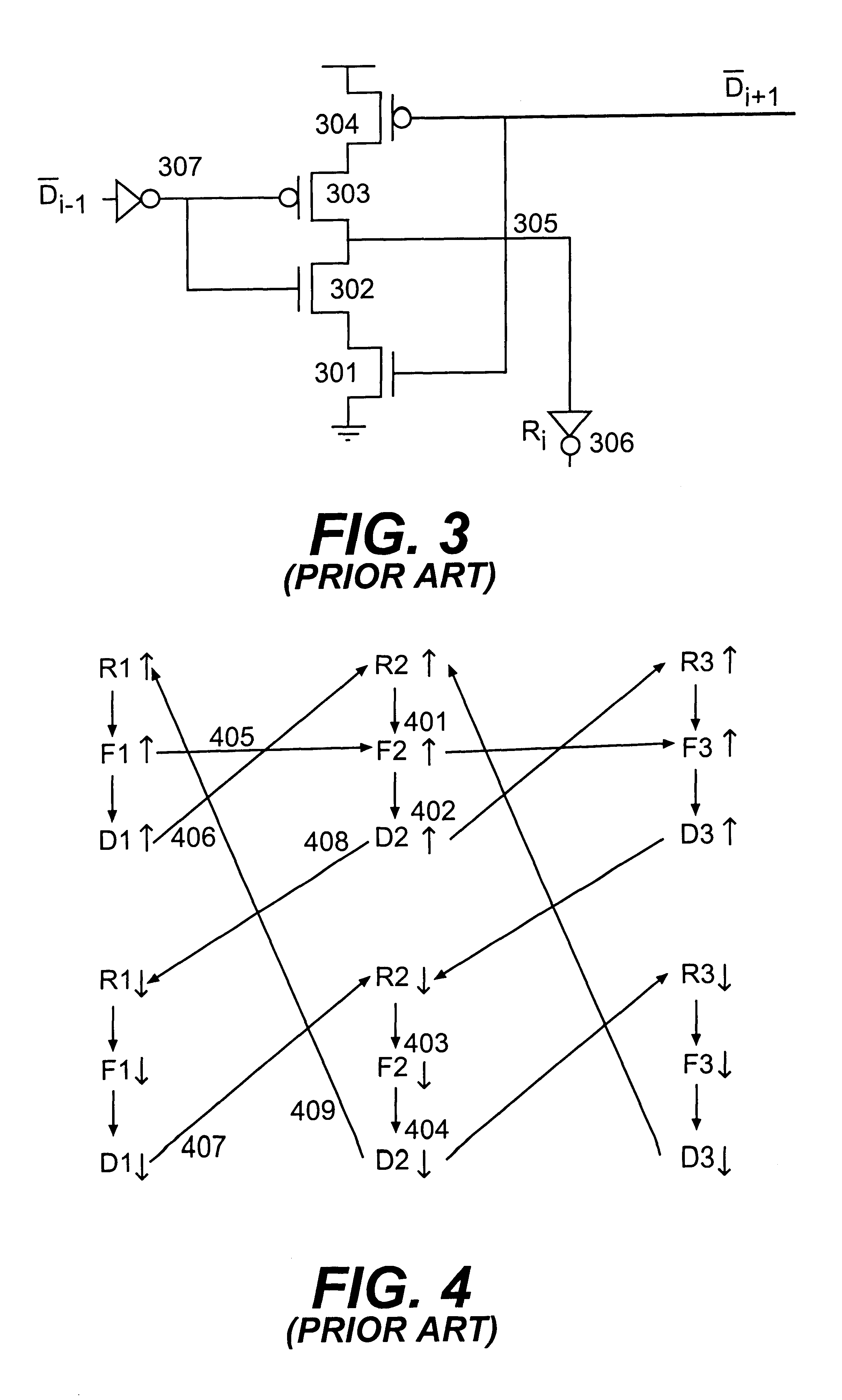

Apparatus and methods for high throughput self-timed domino circuits

InactiveUS6169422B1Faster cycle timeLimit cycle timeLogic circuits characterised by logic functionShort cycleDomino circuit

Asynchronous circuitry provides a domino circuit having short cycle times and zero overhead latency. The control circuit of a datapath circuit may utilize a completion signal from the datapath circuit to develop a request signal to the datapath circuit. The request signal may also be based on a request signal from a previous stage. Using the completion signal of a stage to develop the request signal for the same stage allows the circuitry to reduce the impact of constraints that are required for the asynchronous circuitry to operate. Similarly, using the request signal from a previous stage of the asynchronous circuitry to develop the request signal for a present stage also allows the circuitry to reduce the impact of constraints required to implement the asynchronous circuitry. These techniques allow the achievement of fast cycle times while maintaining zero overhead.

Owner:ORACLE INT CORP

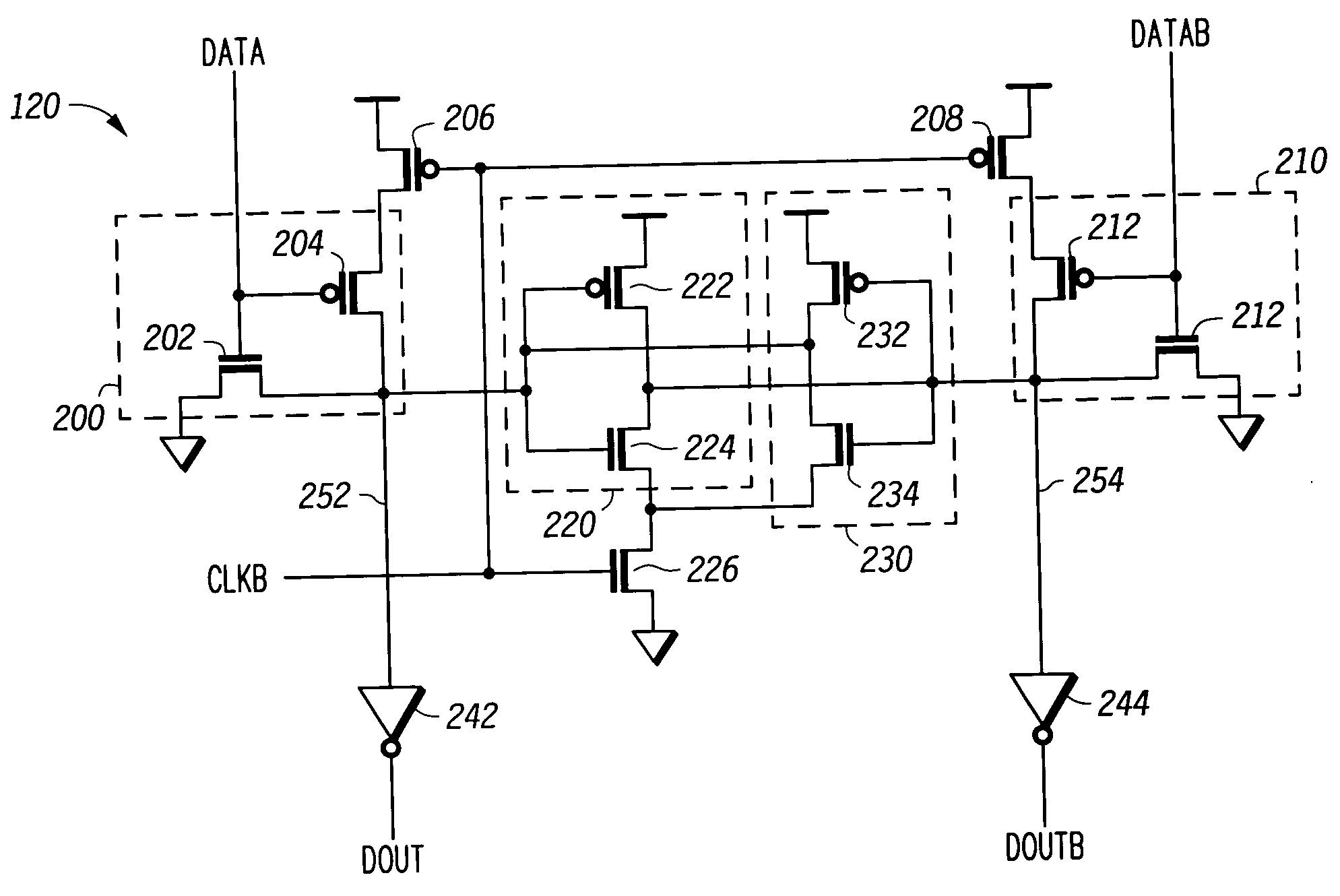

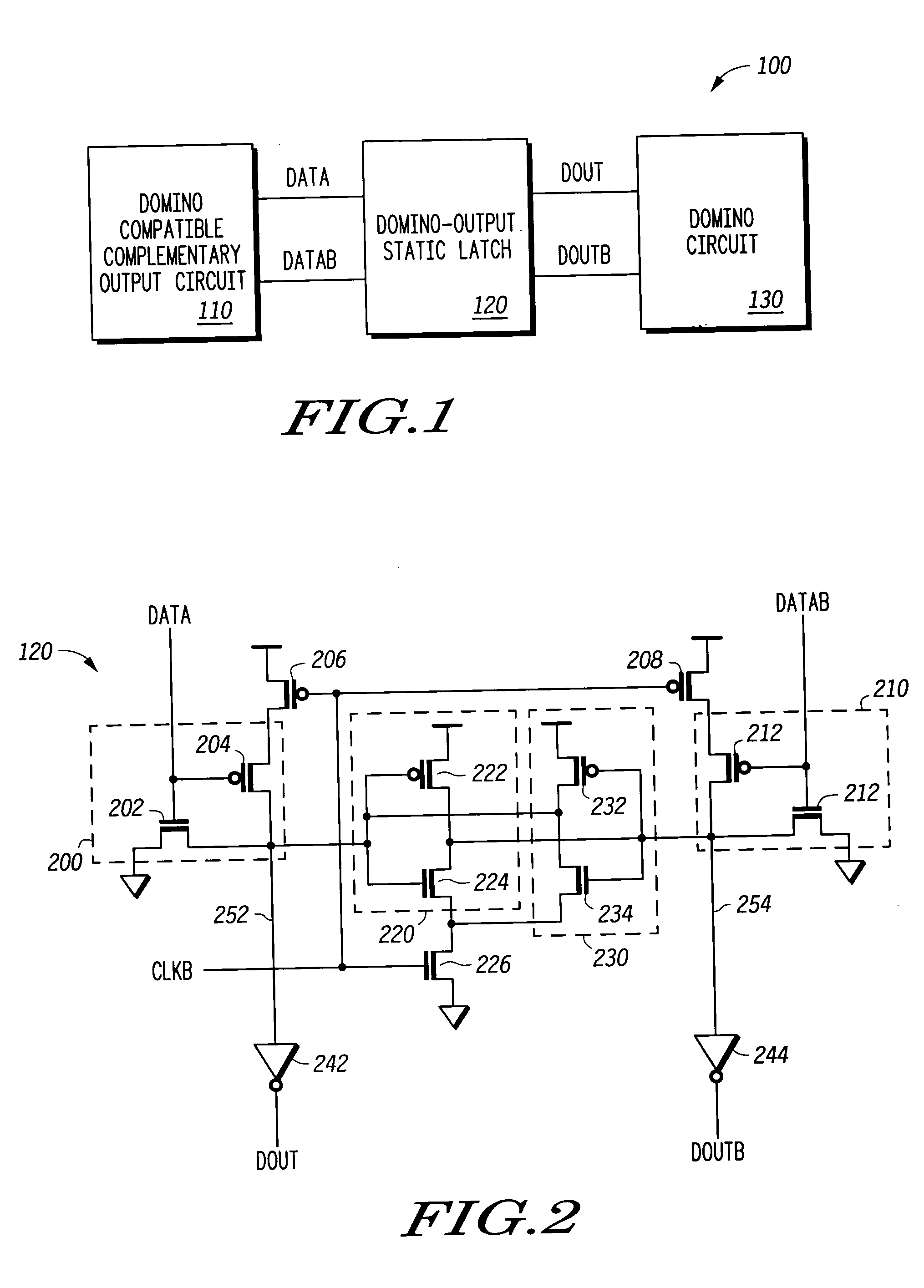

Domino circuitry compatible static latch

A circuit provides latched data in a domino circuit environment. The circuit receives a pair of input signals that are either in complementary logic states, which is data, or in the same logic state, which is the reset condition. The circuit responds to the complementary logic states by providing intermediate signals and output signals in corresponding complementary logic states. The intermediate logic states are latched by cross-coupled clocked inverters prior to the pair of signals switching from data to reset. The intermediate signals are thus latched in the complementary logic states that correspond to data even after the pair of input signals have returned to reset. The output signals are also thus provided in complementary logic states that correspond to data prior to the input signals being reset.

Owner:FREESCALE SEMICON INC

Logical circuit

InactiveUS20020101262A1Logic circuits characterised by logic functionComputation using non-contact making devicesHemt circuitsComputer science

Very high speed operation and reduction of power consumption are realized simultaneously in a two-wire type logical circuit having a halt value and an effective value as signal values. Signal rise transition delay time and signal fall transition delay time are purposely designed asymmetrically and an effective value propagation delay is shortened, thereby accelerating an operating speed of the logical circuit. By eliminating a clock signal from a DOMINO circuit, power consumption is reduced. An architecture for concealing a halt value propagation delay is employed.

Owner:A I L

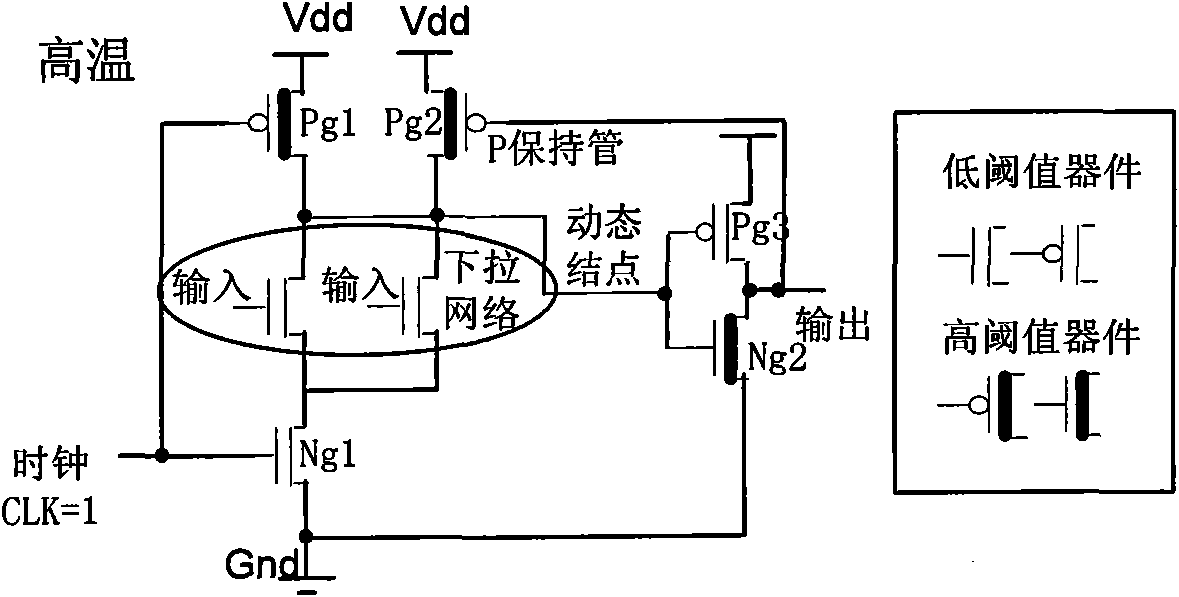

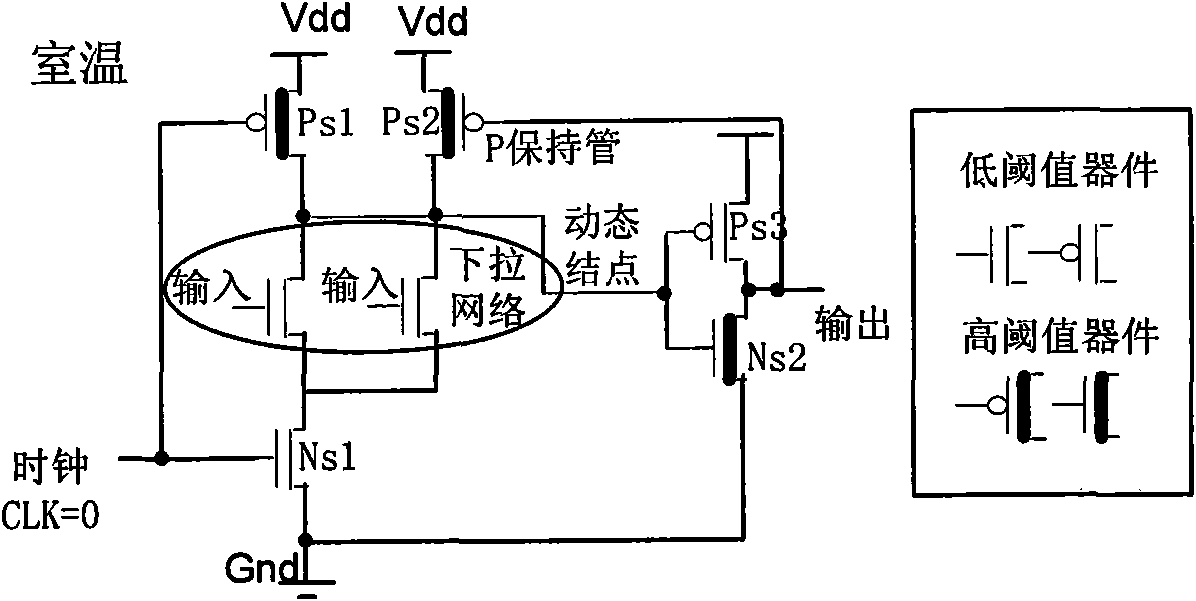

Dual-threshold domino circuit with optimal gate control vector used in low-power consumption VLSI (very large scale integration)

The invention relates to a dual-threshold domino circuit with an optimal gate control vector used in low-power consumption VLSI (very large scale integration), i.e., when the dual-threshold domino circuit is in a dormant state, leakage power consumption of the domino circuit is reduced by utilizing the optimal gate control vector. In the invention, after the dual-threshold domino circuit just enters the dormant state from an operating state, a chip is kept at unchanged high temperature owing to short time, and at the moment, the leakage power consumption can be effectively reduced by utilizing the gate control vector with a high-level input signal and a high-level clock signal; and after the dual-threshold domino circuit is changed into the dormant state from the operating state for a period of time, the temperature of the chip is reduced to room temperature, and at the moment, the leakage power consumption can be more effectively reduced by utilizing the gate control vector with a low-level input signal and a low-level clock signal.

Owner:BEIJING UNIV OF TECH

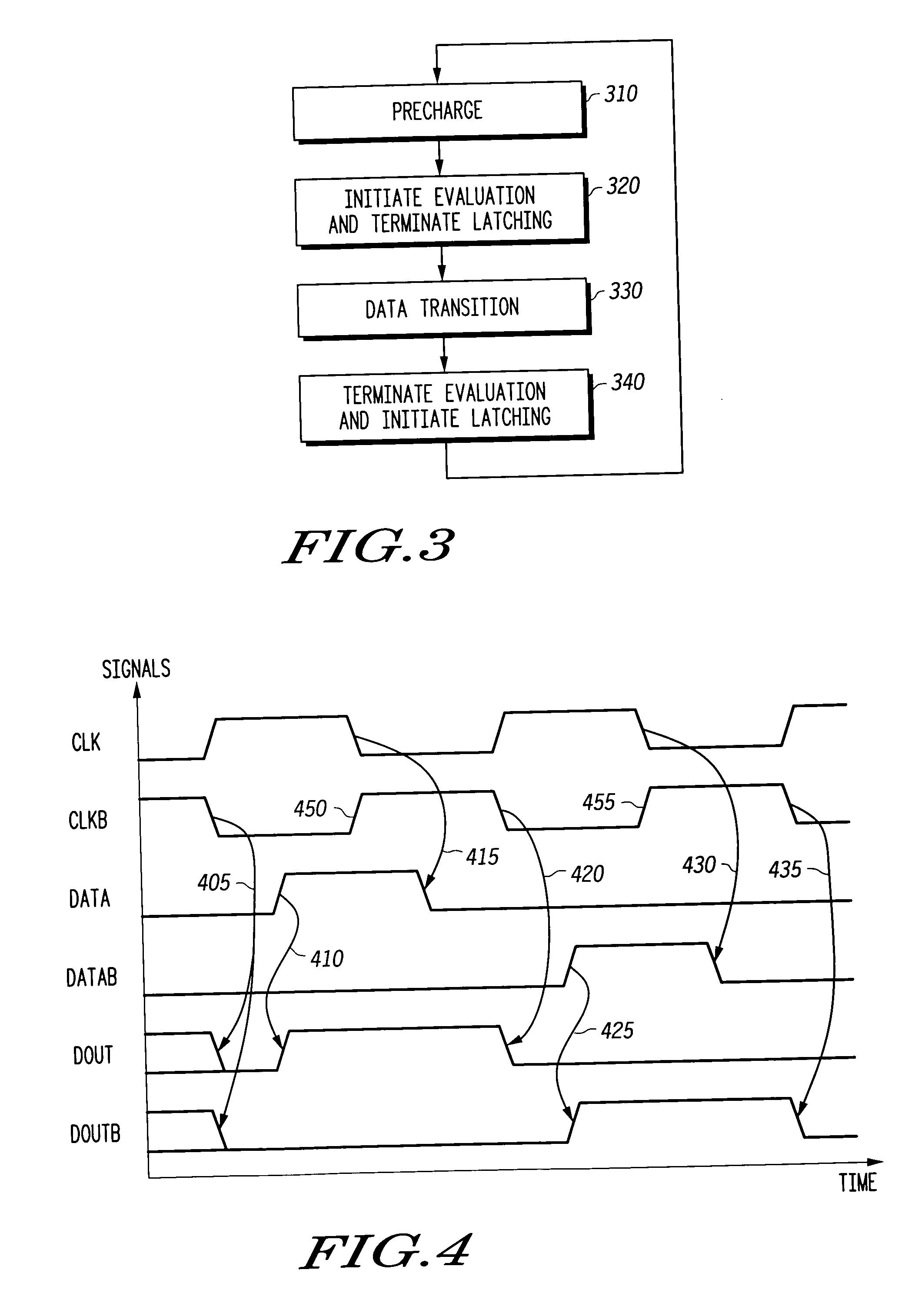

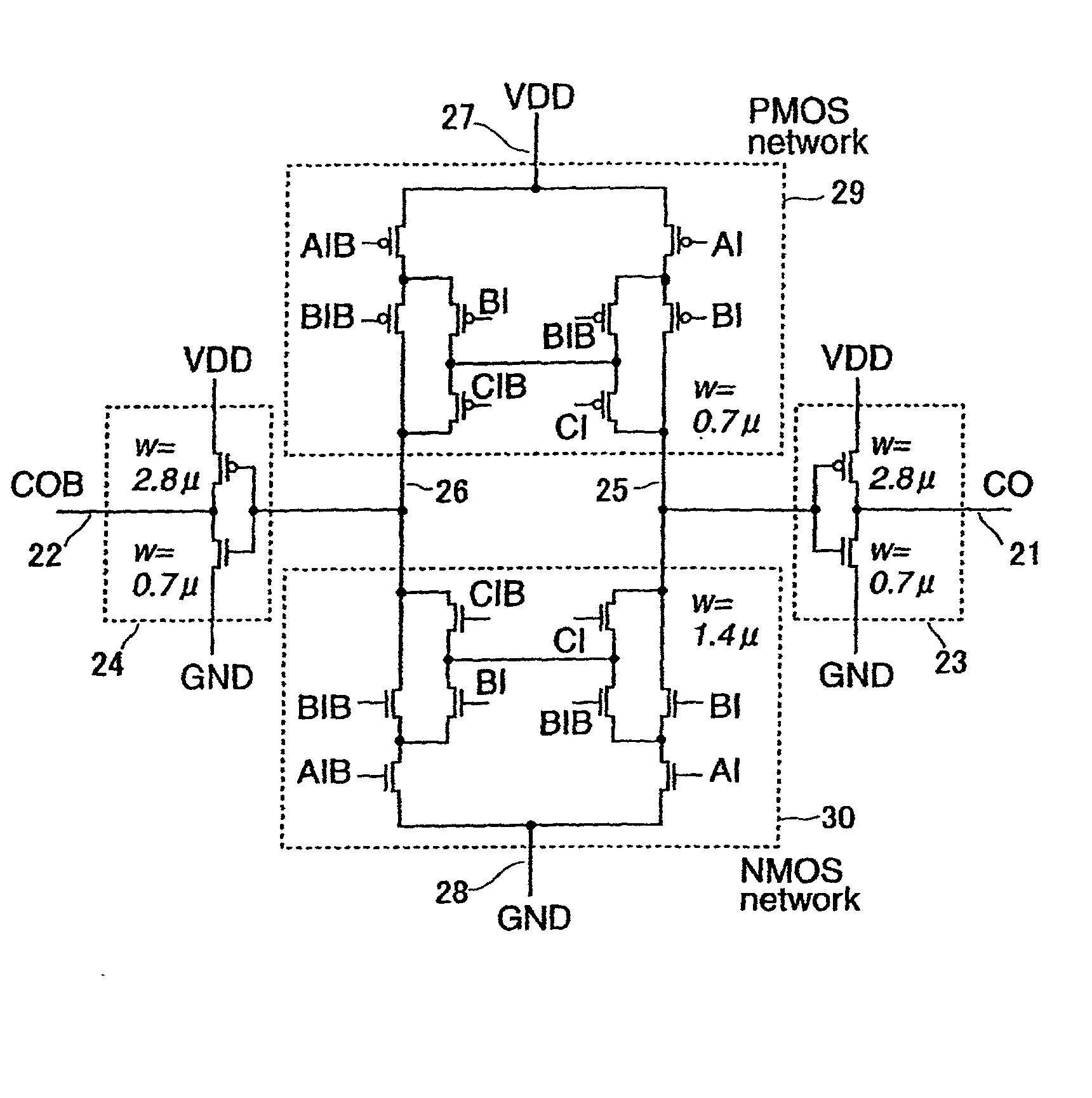

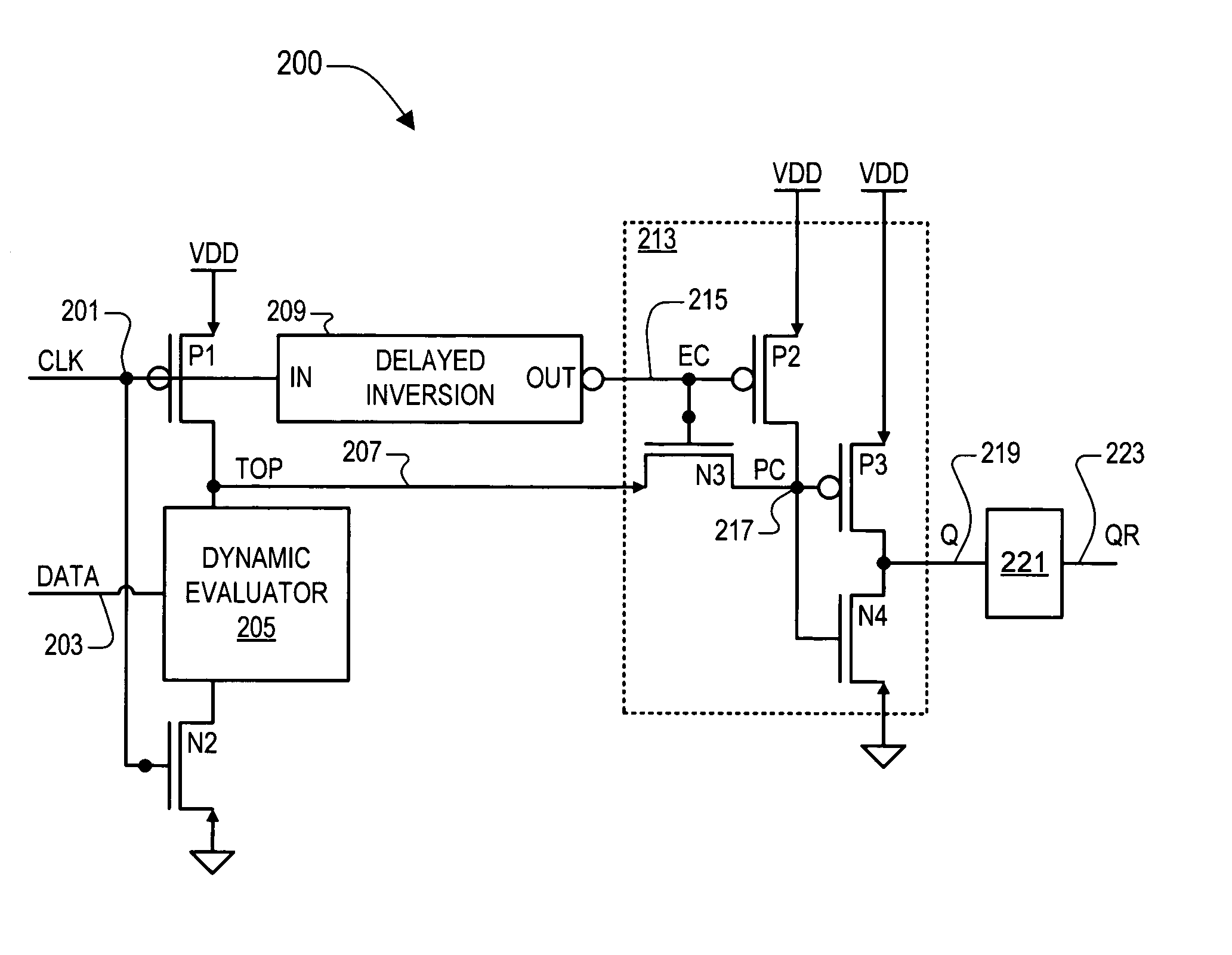

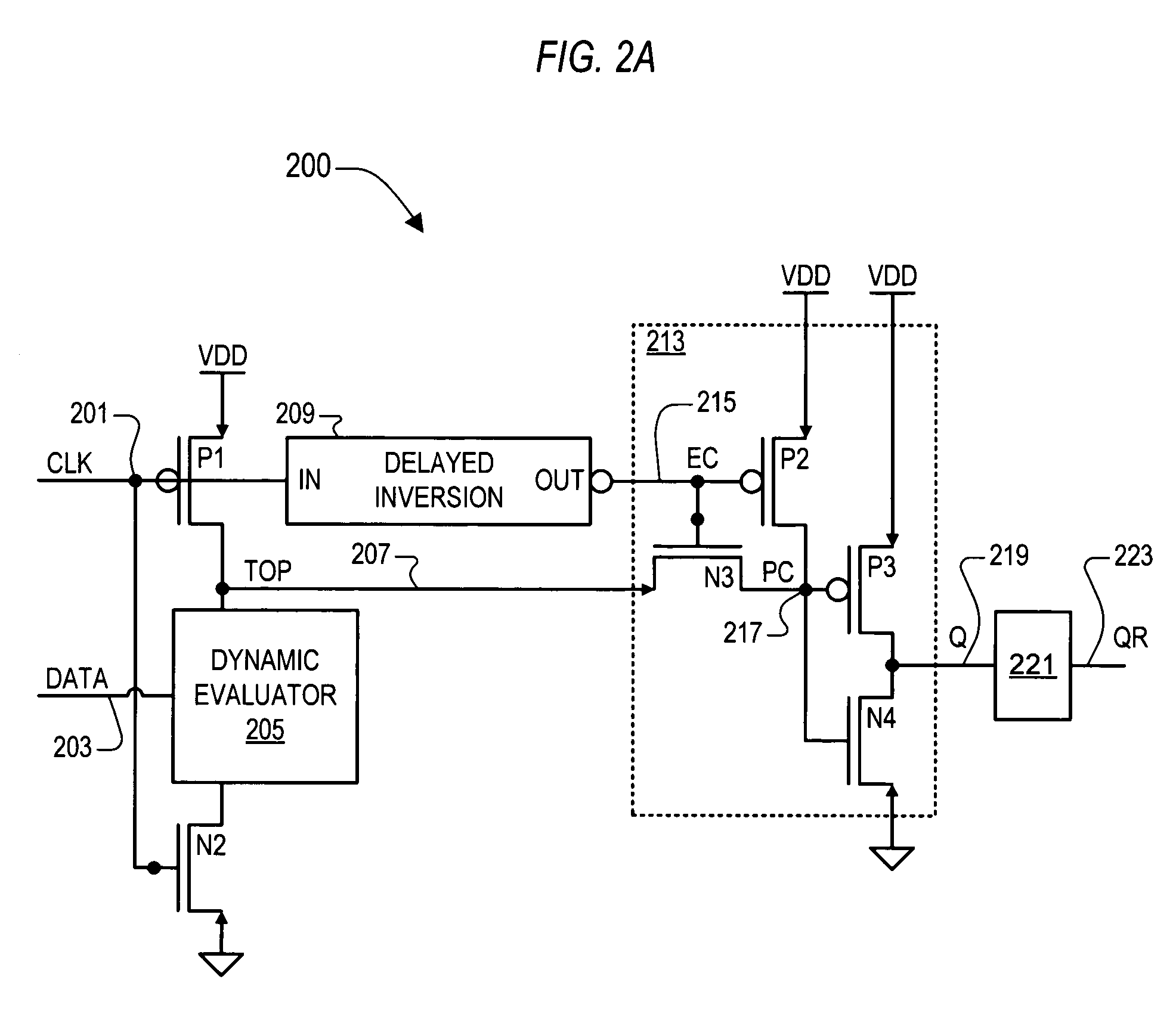

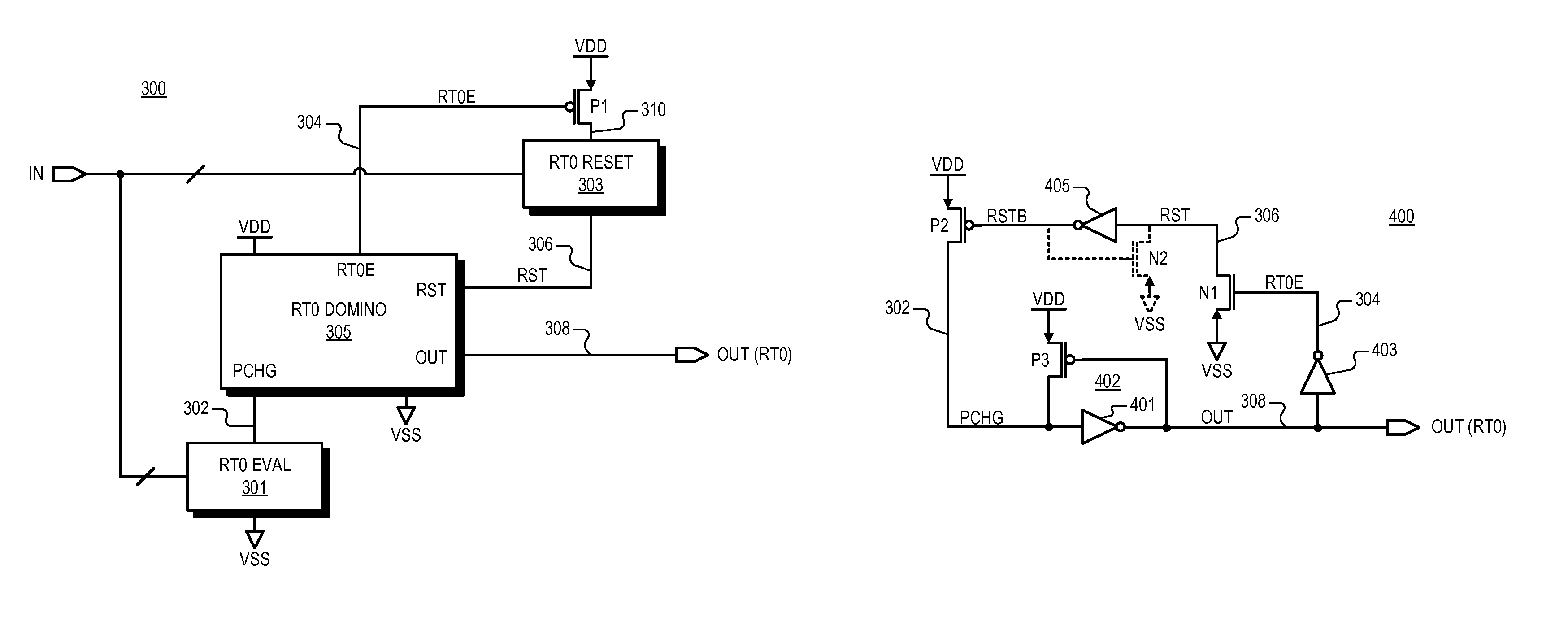

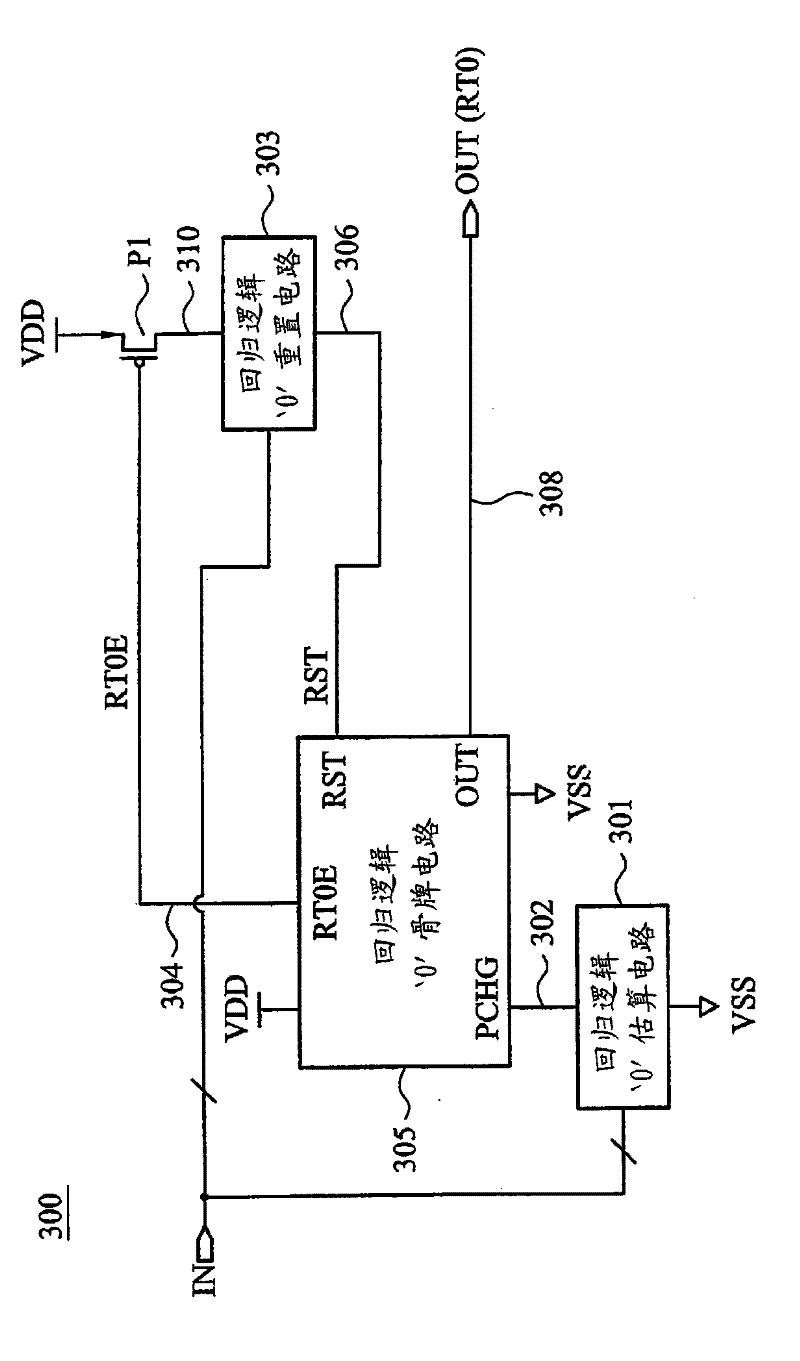

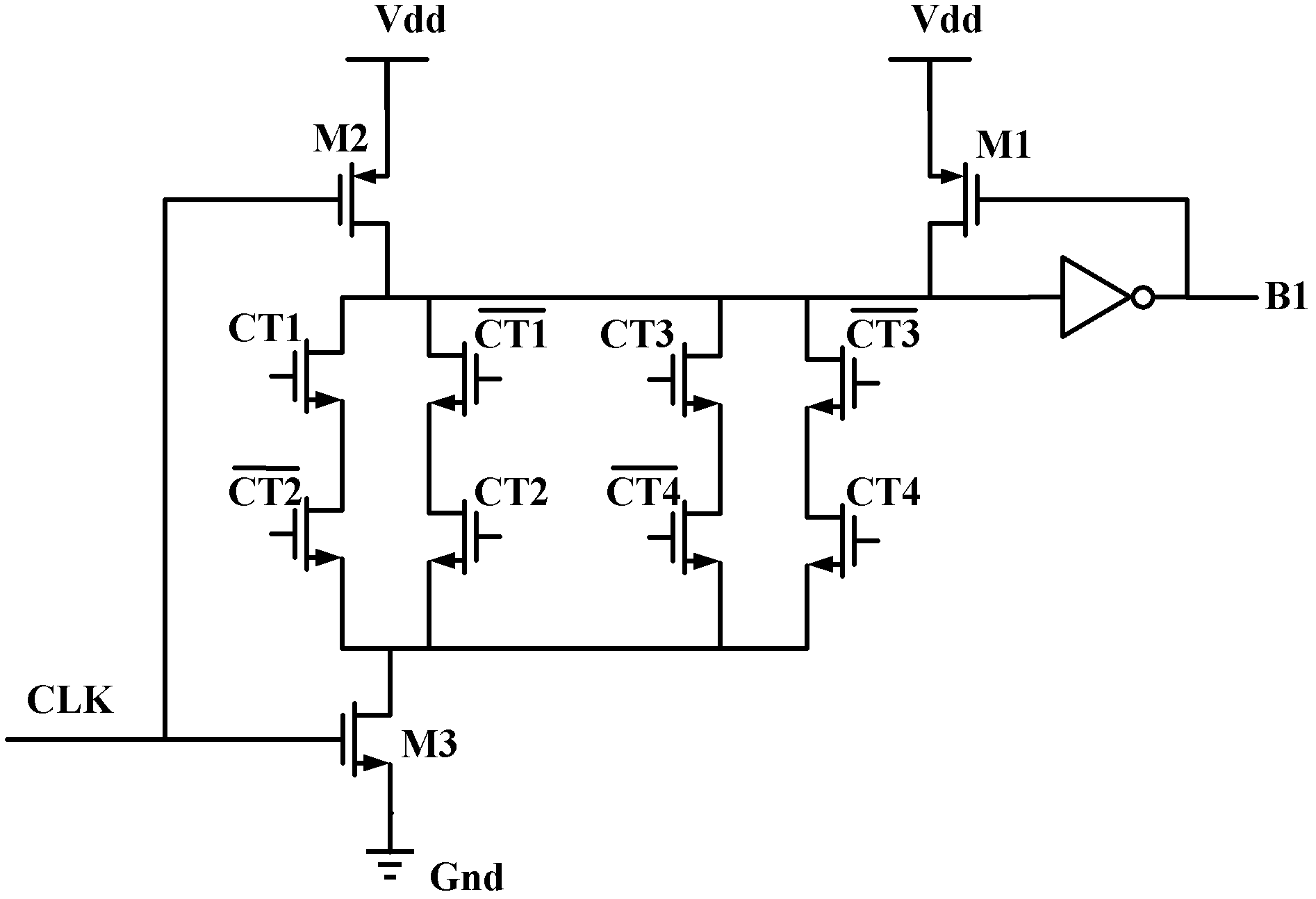

Dynamic logic return-to-zero latching mechanism

ActiveUS7173456B2General purpose stored program computerElectric pulse generatorReturn-to-zeroData signal

A dynamic logic return-to-zero (RTZ) latching mechanism including a complementary pair of evaluation devices responsive to a clock signal, a dynamic evaluator, delayed inversion logic, and latching logic. The dynamic evaluator is coupled between the complementary pair of evaluation devices at a pre-charged node and evaluates a logic function based on at least one input data signal. The latching logic asserts the logic state of an output node based on the state of the pre-charged node during an evaluation period between an operative edge of the clock signal and the next edge of an evaluation complete signal, which is a delayed and inverted version of the clock signal. The output node is returned to zero between evaluation periods. A footless latching domino circuit may be added to convert the RTZ output to a registered output signal.

Owner:IP FIRST

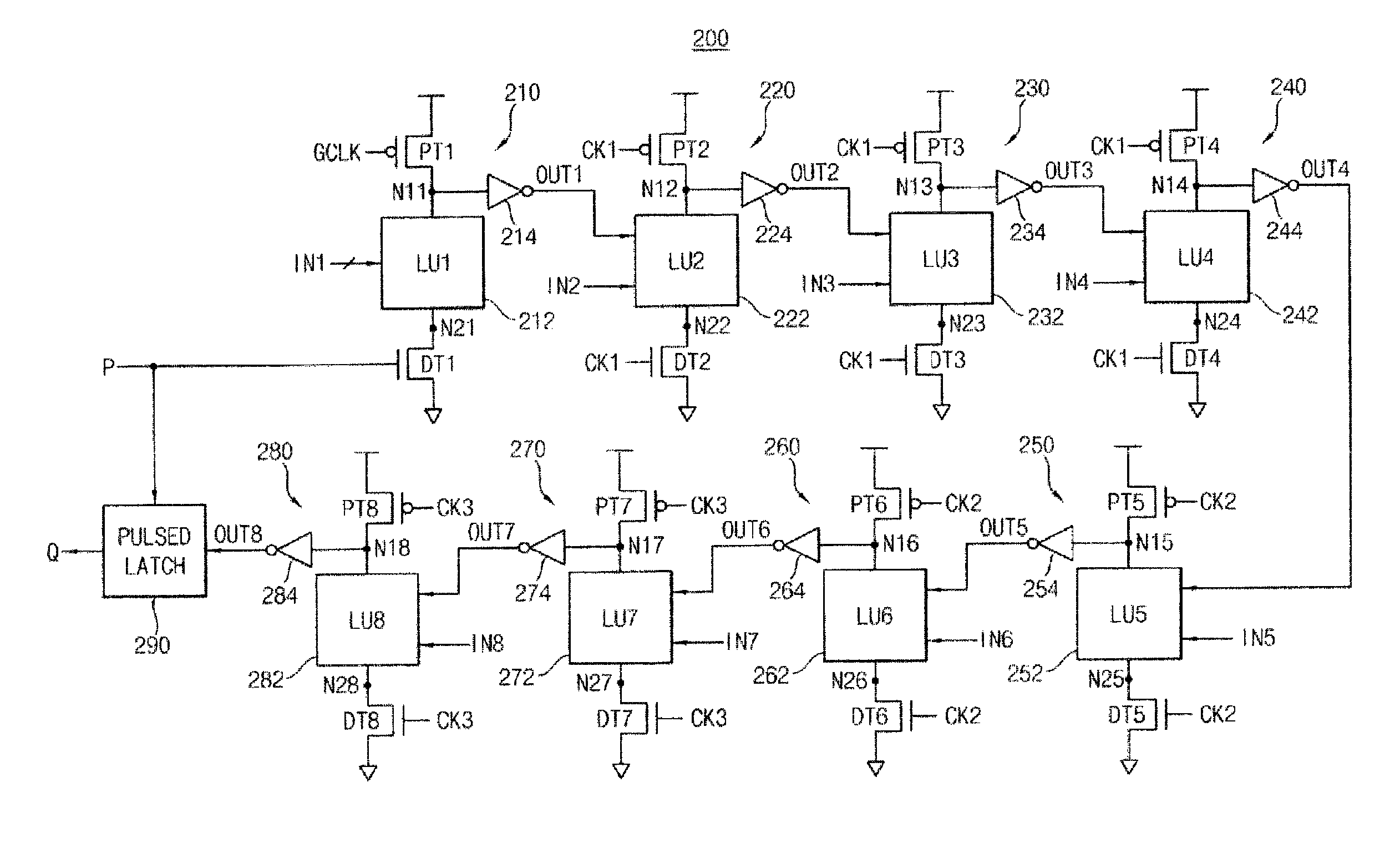

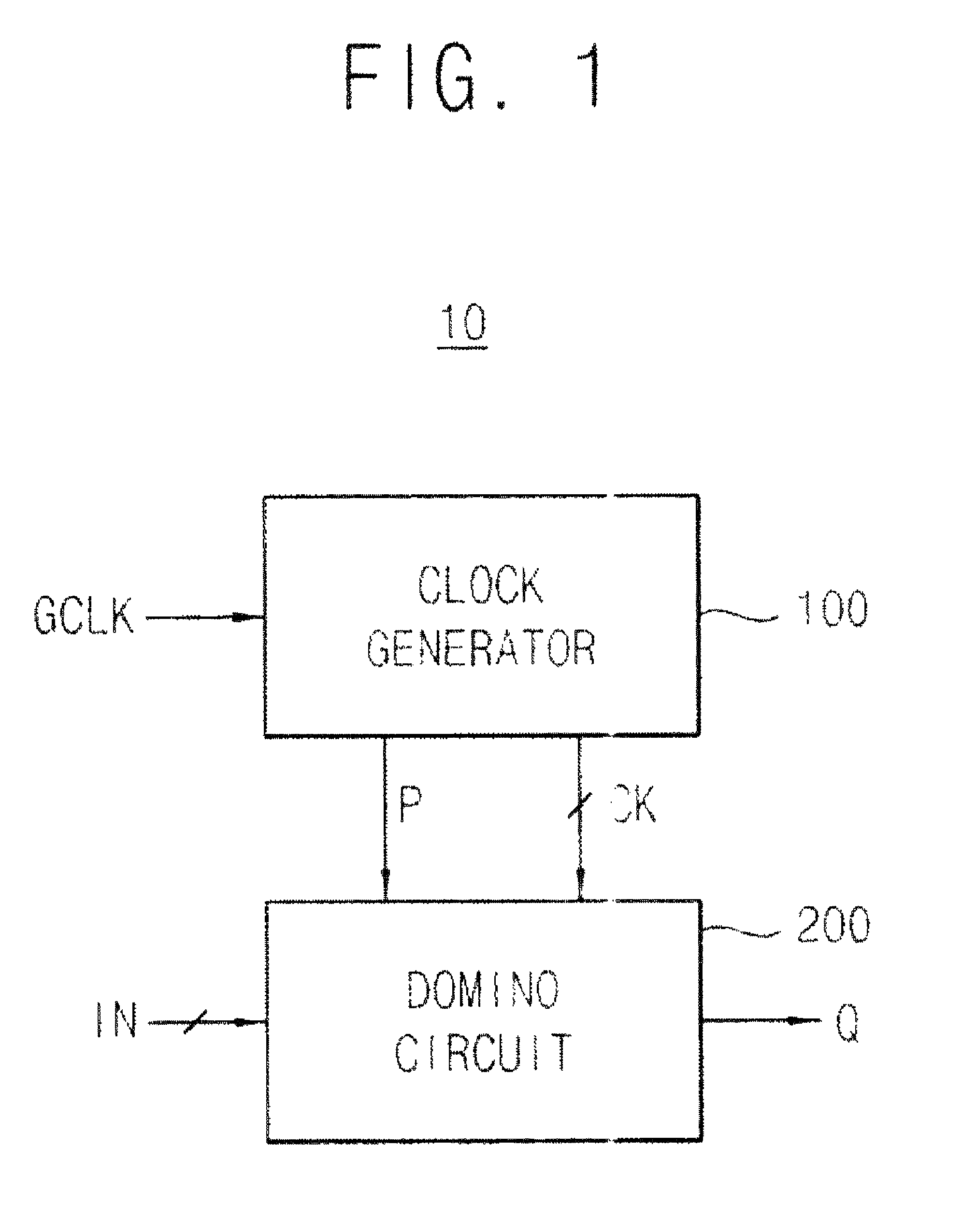

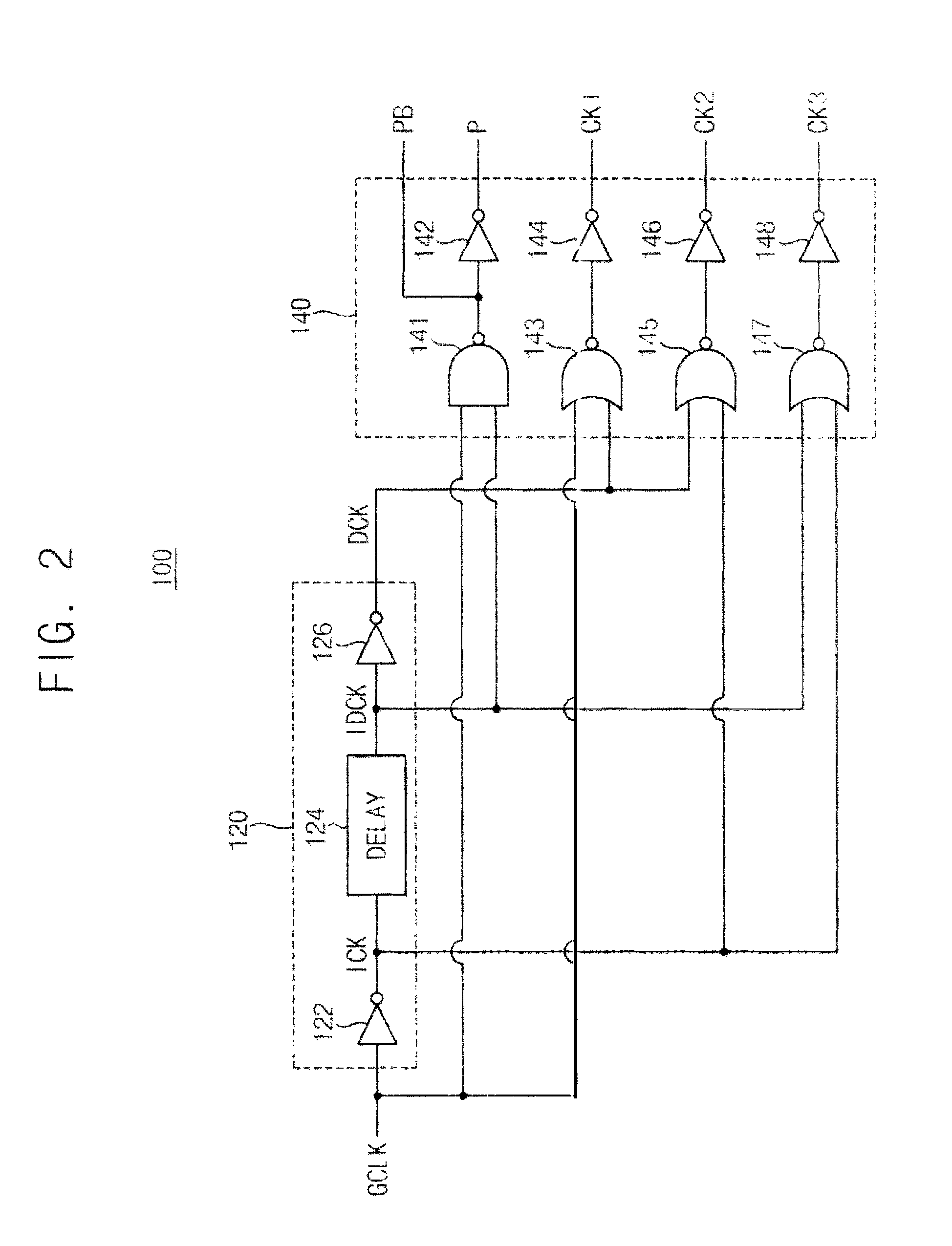

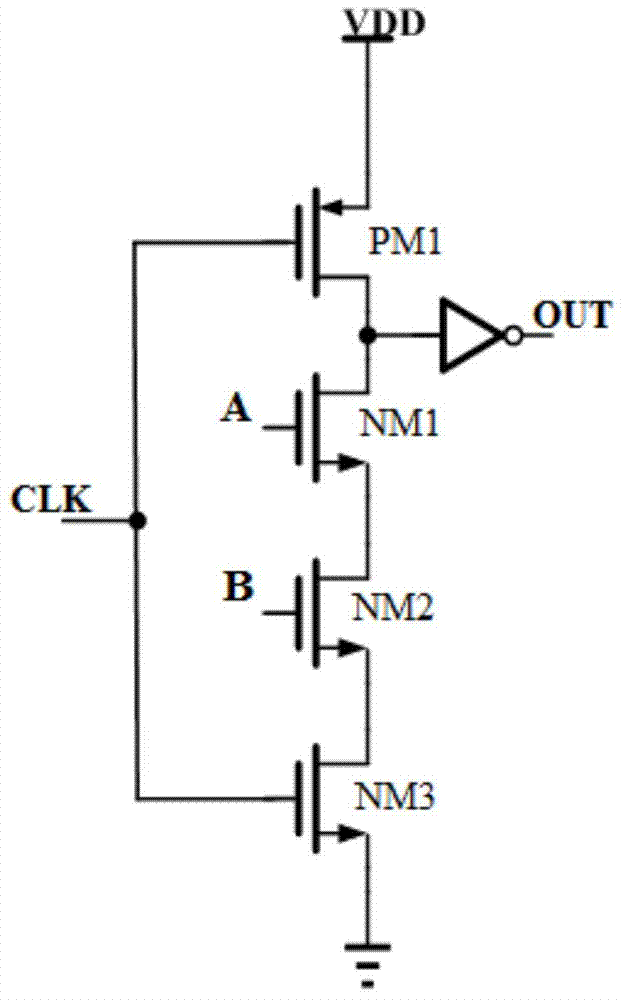

Dynamic domino circuit and integrated circuit including the same

InactiveUS7932750B2Improve reliabilityIncrease speedLogic circuits characterised by logic functionLogic circuits using elementary logic circuit componentsEngineeringClock generator

A dynamic domino circuit includes a clock generator and a domino circuit. The clock generator generates a pulse signal and a plurality of internal clock signals based on a global clock signal. Phases of the plurality of internal clock signals are sequentially delayed. The domino circuit sequentially performs a plurality of logic operations based on a plurality of input signals, the pulse signal and the plurality of internal clock signals and generates an output signal in synchronization with the pulse signal. The dynamic domino circuit may provide an effective interface with static logics.

Owner:SAMSUNG ELECTRONICS CO LTD

Low-power-consumption domino three-value character arithmetic circuit

InactiveCN102624378AReduce power consumptionReduce areaLogic circuitsInformation densitySignaling nodes

The invention discloses a low-power-consumption domino three-value character arithmetic circuit, which comprises a first character arithmetic circuit unit, a second character arithmetic circuit unit and a third character arithmetic circuit unit. The first character arithmetic circuit unit, the second character arithmetic circuit unit and the third character arithmetic circuit unit all achieve functions through a heat insulation circuit, a three-value character arithmetic circuit and a domino circuit. The low-power-consumption domino three-value character arithmetic circuit has the advantages of integrating the heat insulation circuit and the domino circuit into the three-value character arithmetic circuit, converting energy of circuits according to a sequence of a power supply-a signal node-a power supply through the heat insulation circuit, being capable of effectively reducing power consumption of the circuits, enabling the power consumption of the circuits to be low, enabling the circuits to have smaller area by combining the domino circuit with a multi-value circuit, further improving information density of the circuits, reducing the quantity of chip pins and connecting wires, and enabling the circuits to have simple structures.

Owner:HANGZHOU MAEN TECH

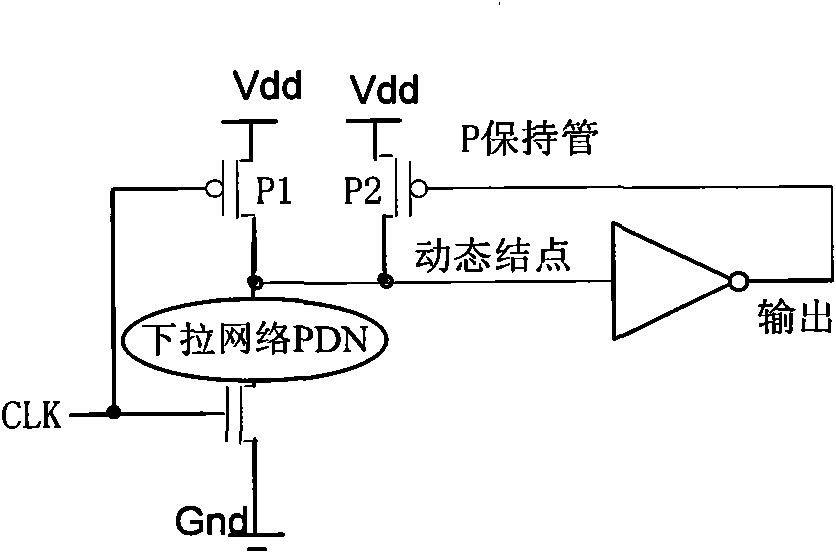

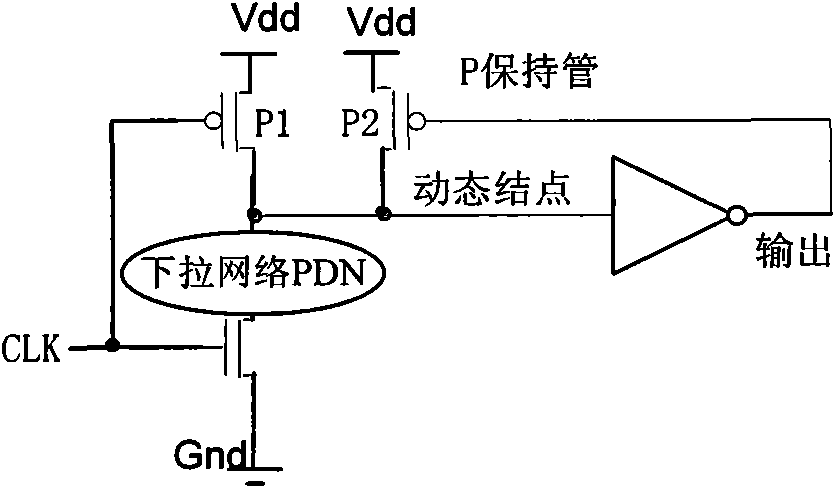

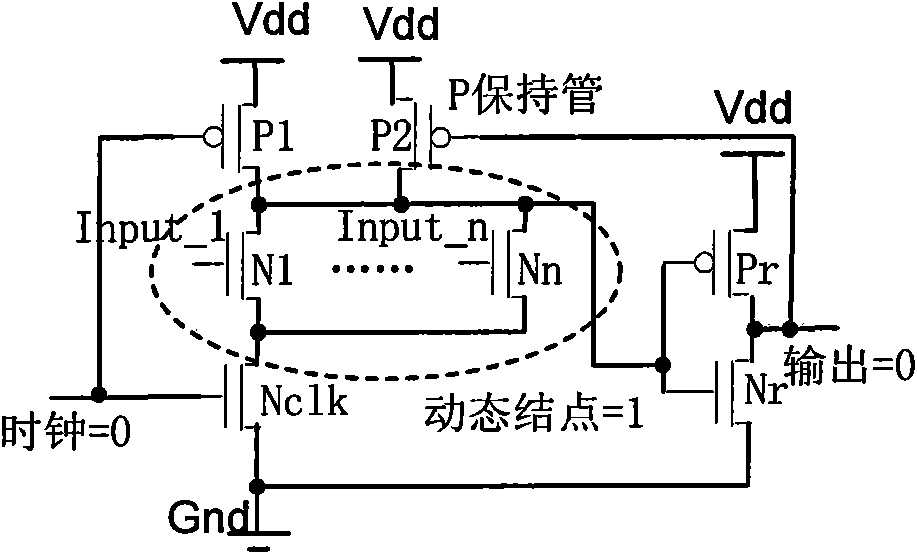

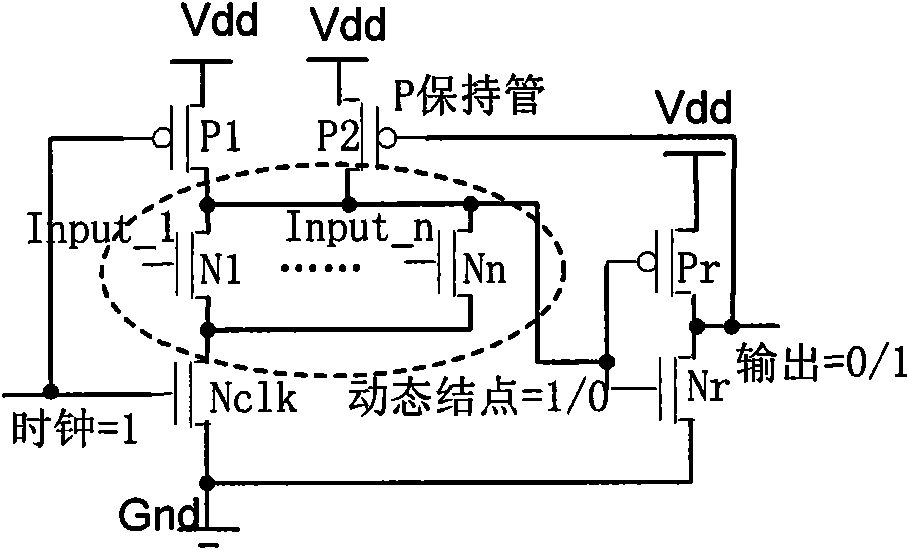

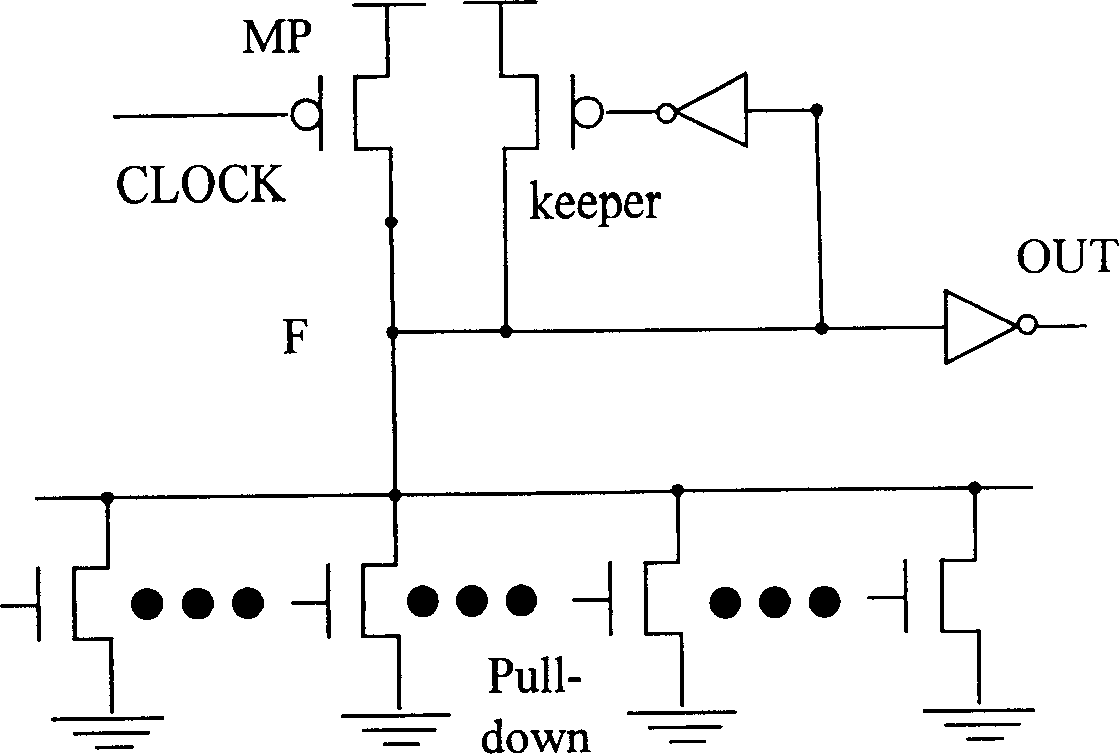

Optimal maintaining pipe domino circuit used for high-performance VLSI (Very Large Scale Integrated Circuit)

InactiveCN102035530AImprove noise immunityIncrease power consumptionLogic circuitsVery large scale integrated circuitsCircuit delay

The invention relates to an optimal maintaining pipe domino circuit used for a high-performance VLSI (Very Large Scale Integrated Circuit), i.e. in the domino circuit, the balance of a plurality of important parameters of dynamic power consumption, leakage current, noise margin, circuit delay, process fluctuation resisting coefficients and the like is realized by applying an optimal maintaining pipe technology through regulating the substrate voltage and the power supply voltage of the maintaining pipe, therefore, the domino circuit reaches optimal comprehensive property, wherein the power supply voltage and the substrate voltage of the maintaining pipe are respectively VddL and Vb, the power supply voltages and the substrate voltages of left PMOS (P-channel Metal Oxide Semiconductor) pipes except the maintaining pipe are Vdd, the substrate voltages of all NOMS (N-channel Metal Oxide Semiconductor) pipes in the circuit are ground voltages Gnd, and the relation of the voltages is: Gnd<Vb<VddL<Vdd.

Owner:BEIJING UNIV OF TECH

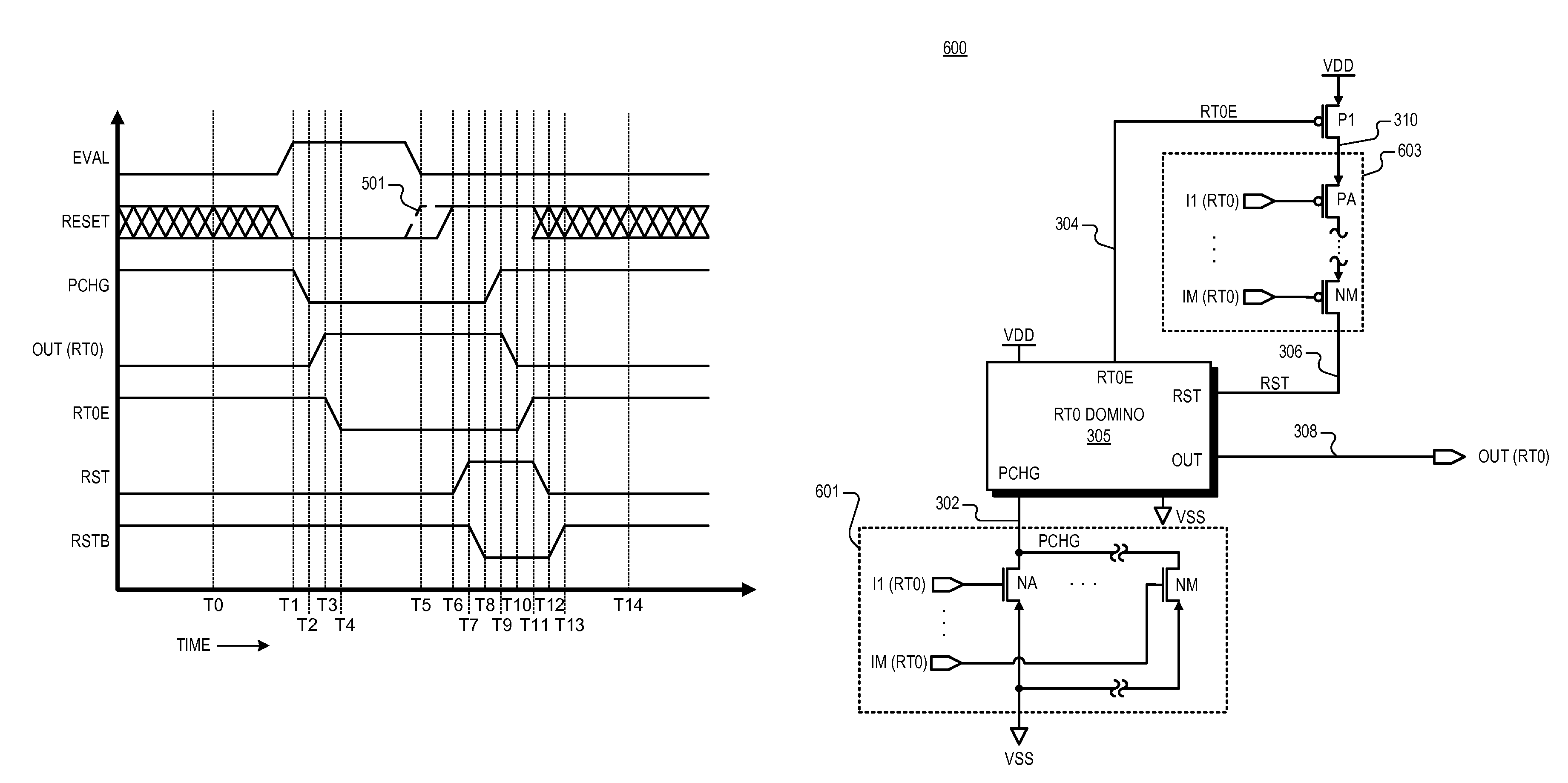

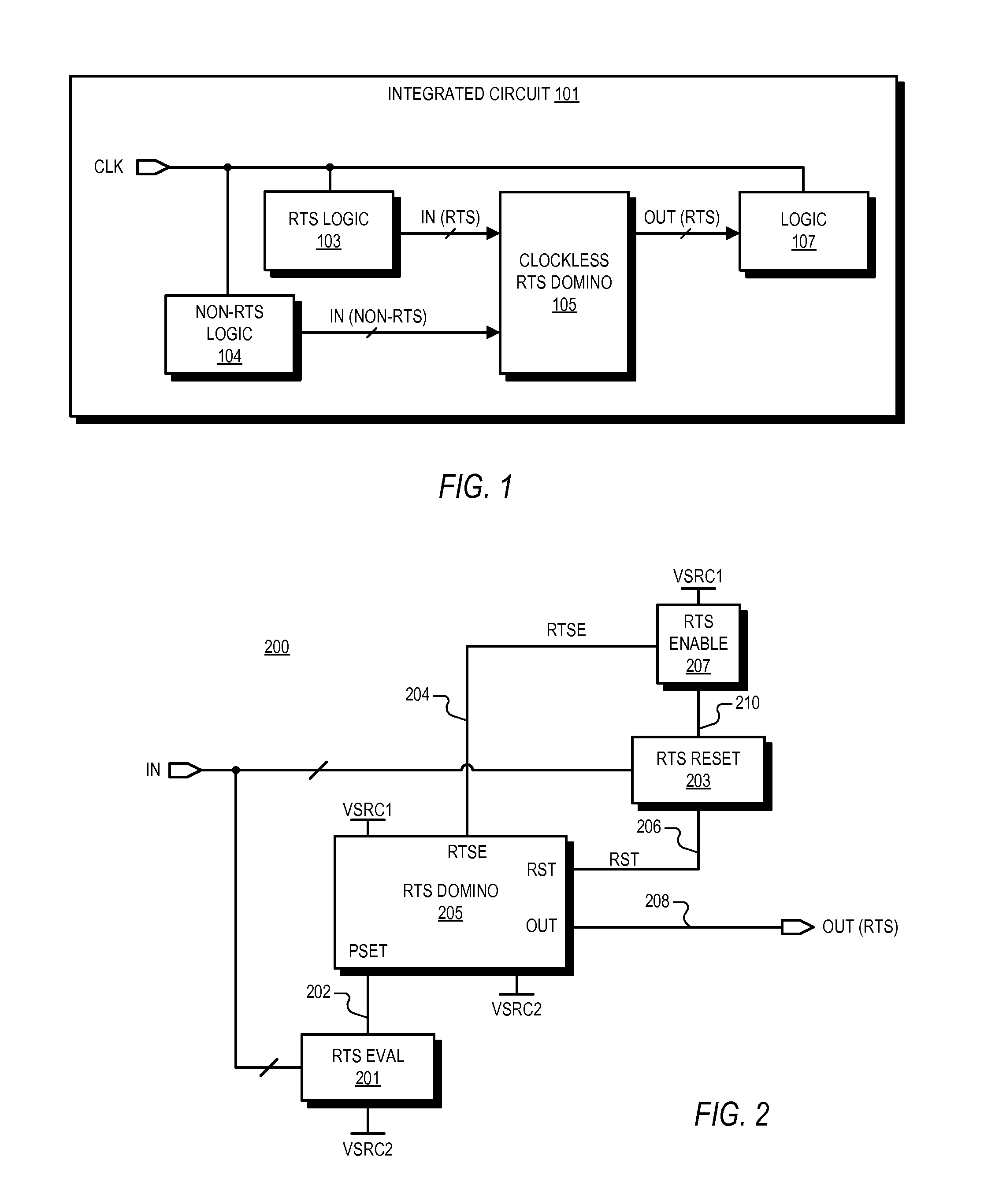

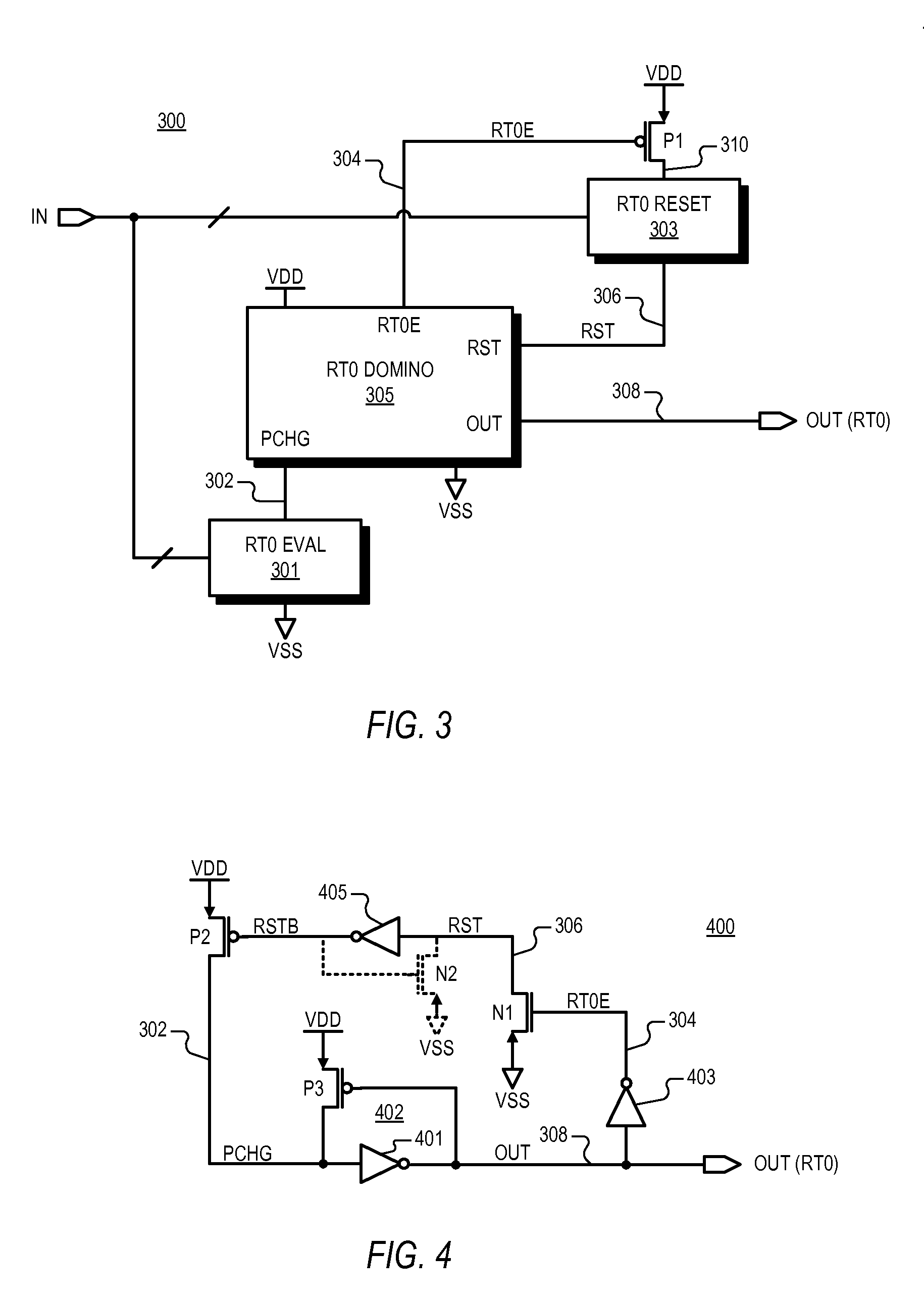

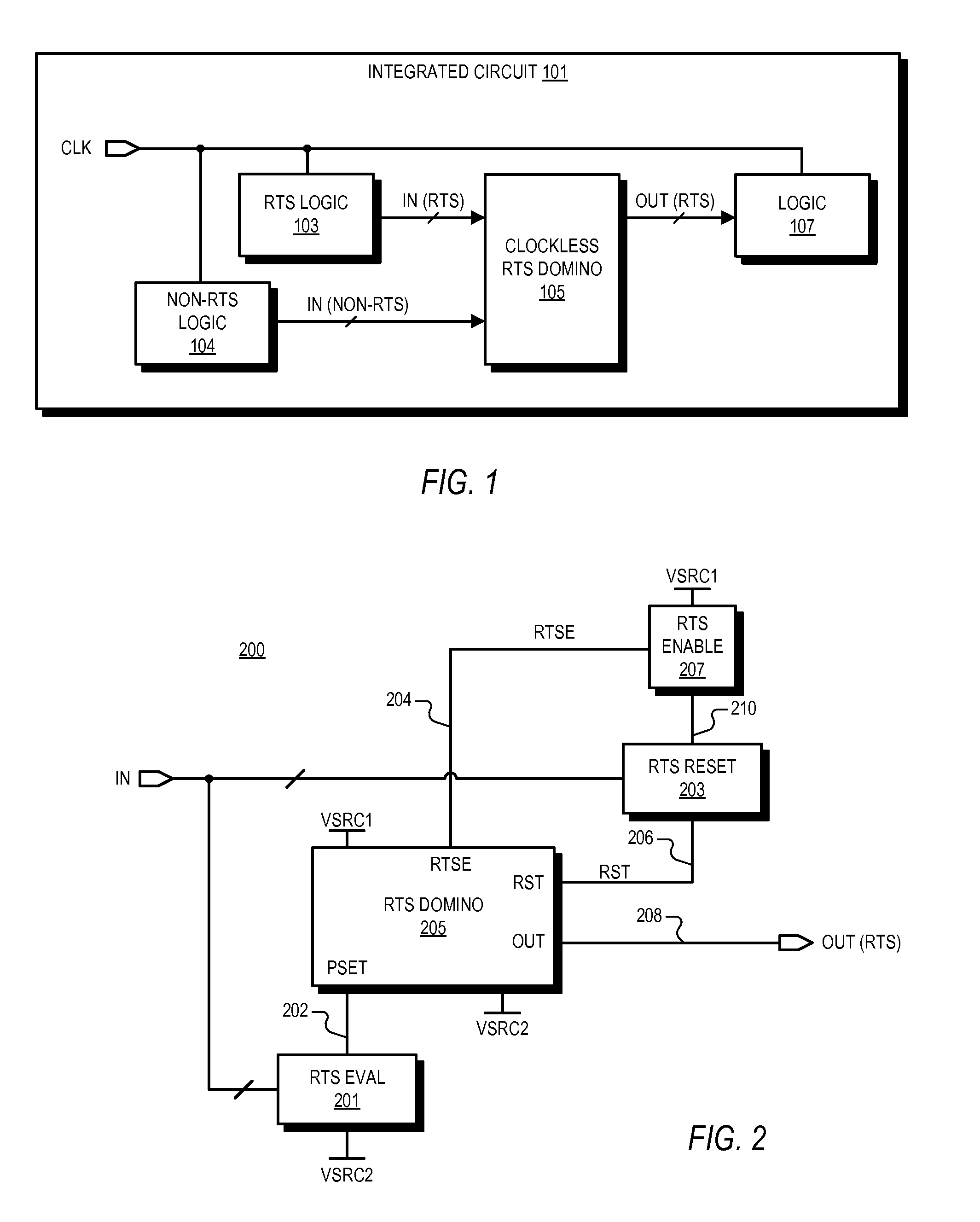

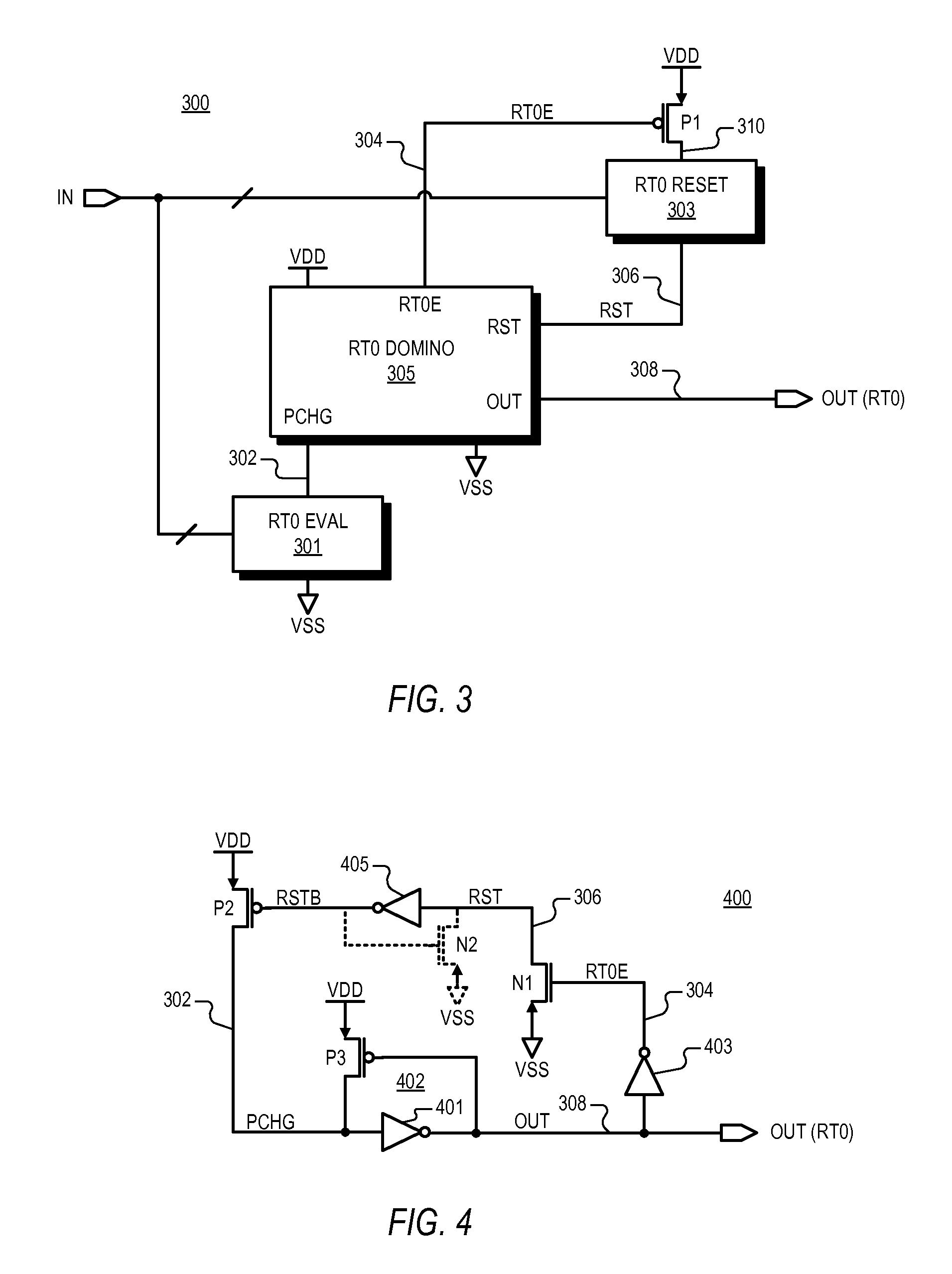

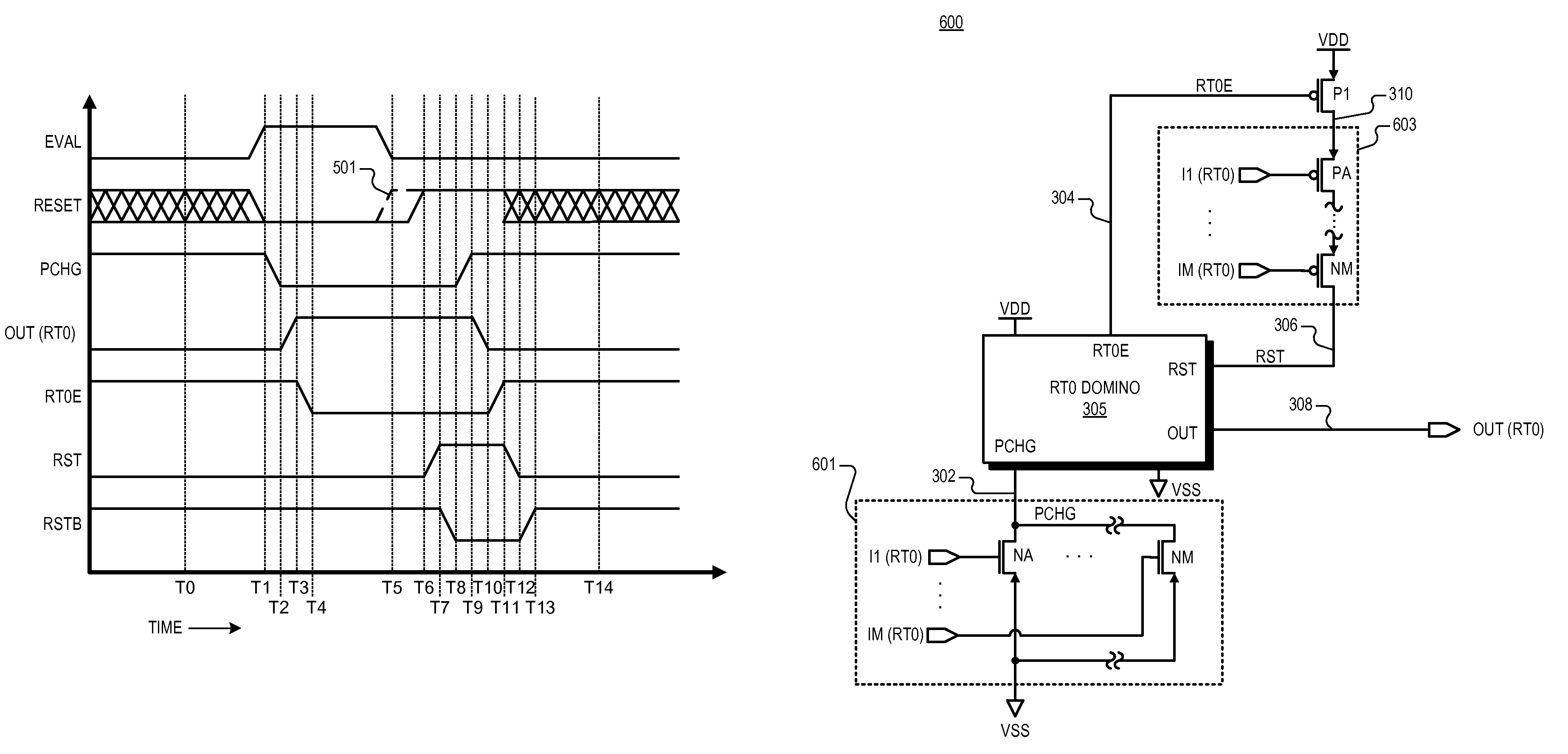

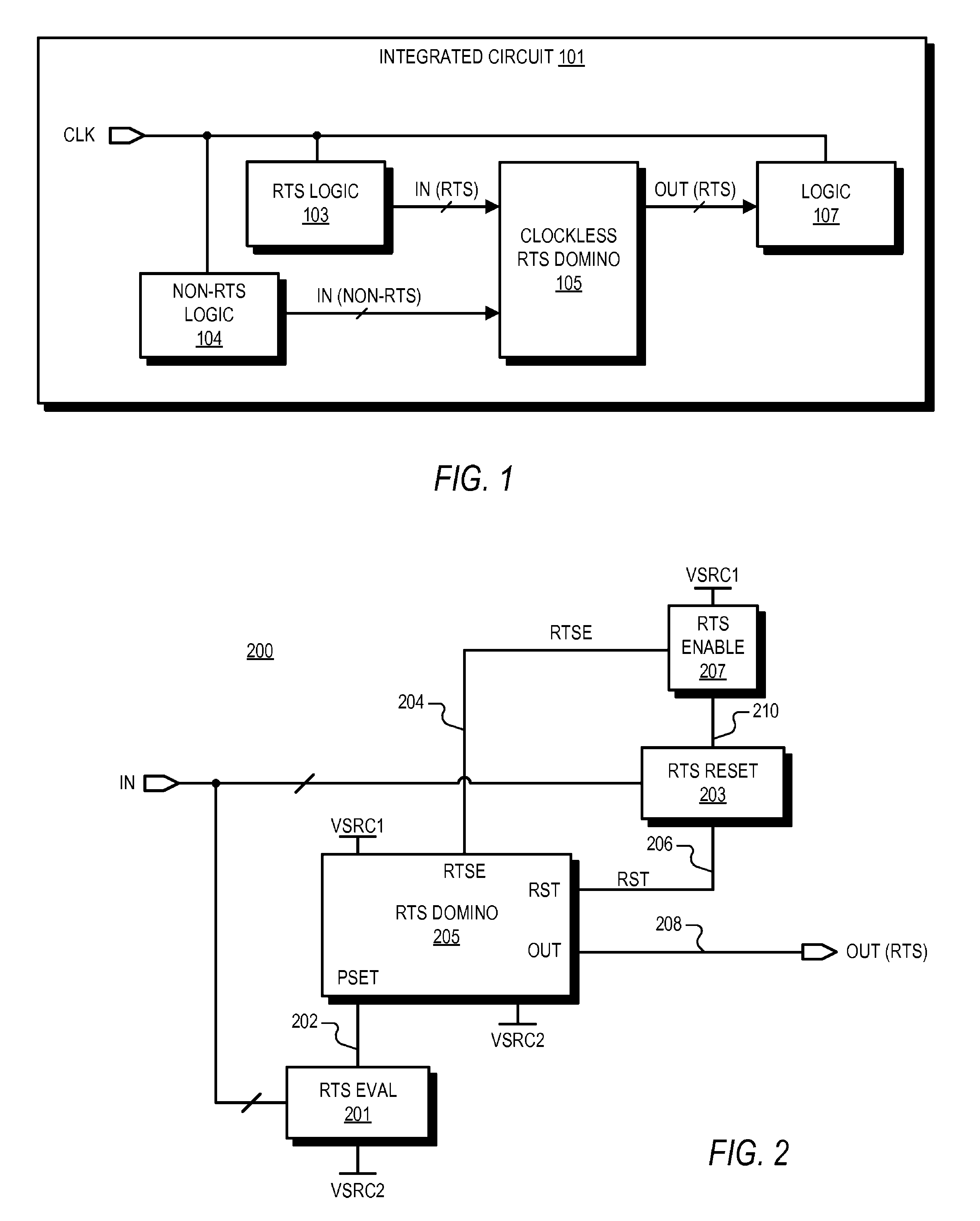

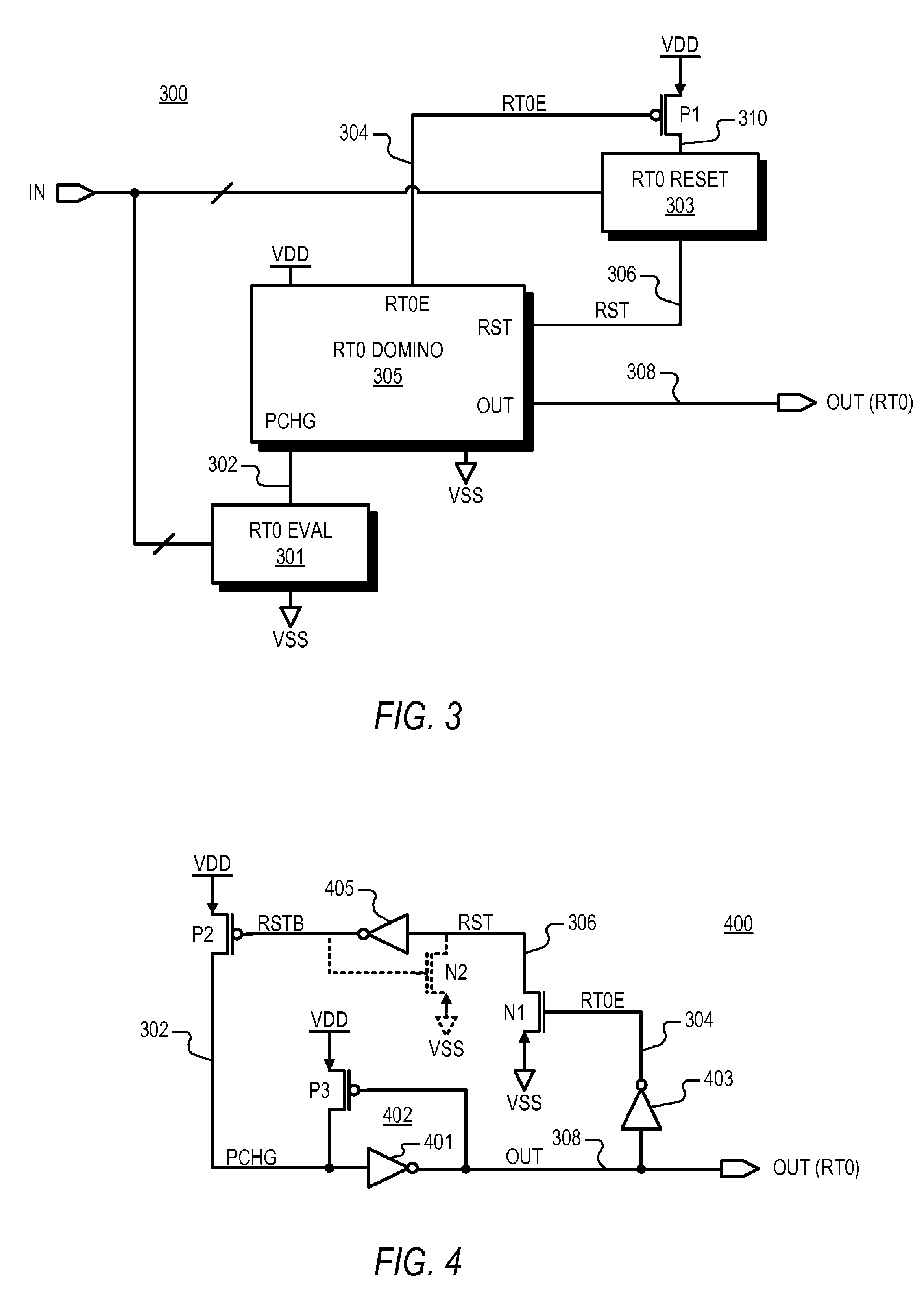

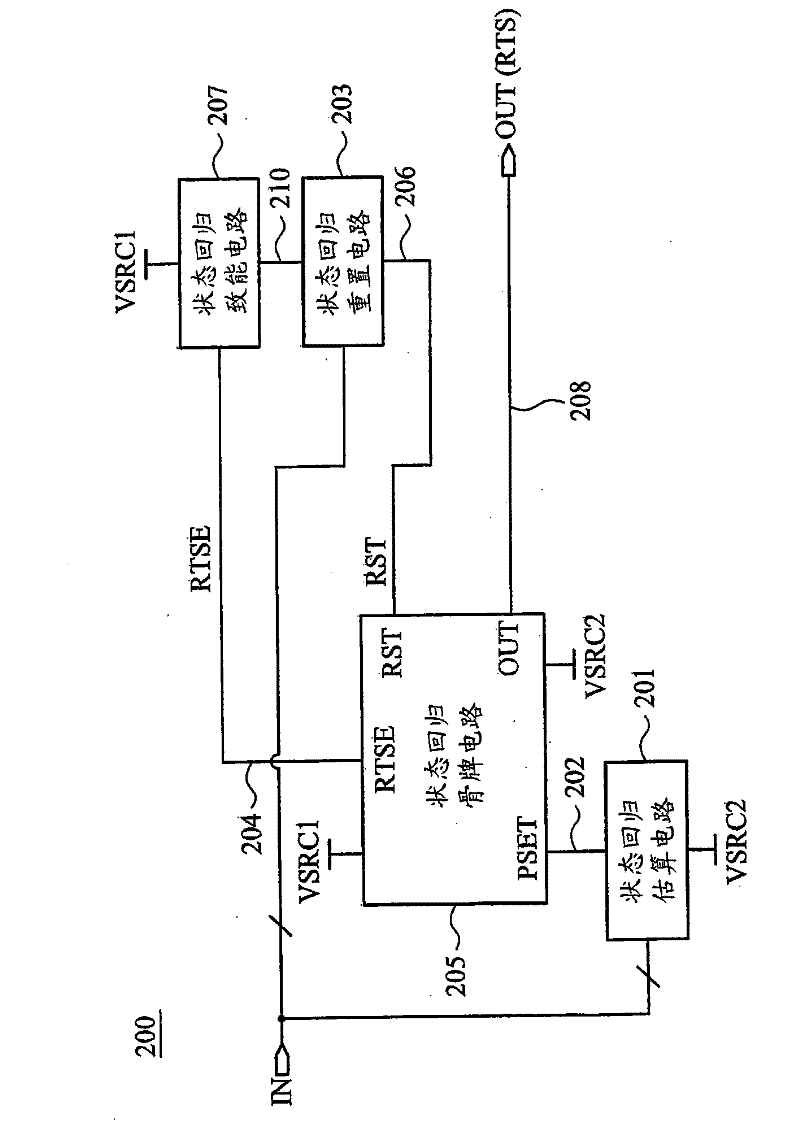

Clockless return to state domino logic gate

A clockless return to state domino logic gate is disclosed responsive to multiple return to state input nodes. A domino circuit has a preset state in which it presets a preset node to a second state. The domino circuit switches to a latch state and switches an output node when the preset node is pulled to a first state. The domino circuit resets back to the preset state and switches the output node back to its default state when a reset node is pulled to the second state. An evaluation circuit pulls the preset node to the second state when the input nodes are in an evaluation state. An enable circuit enables a reset condition when the domino circuit is in its latch state. A reset circuit pulls the reset node to the first state after an evaluation event when the input nodes are no longer in the evaluation state.

Owner:VIA TECH INC

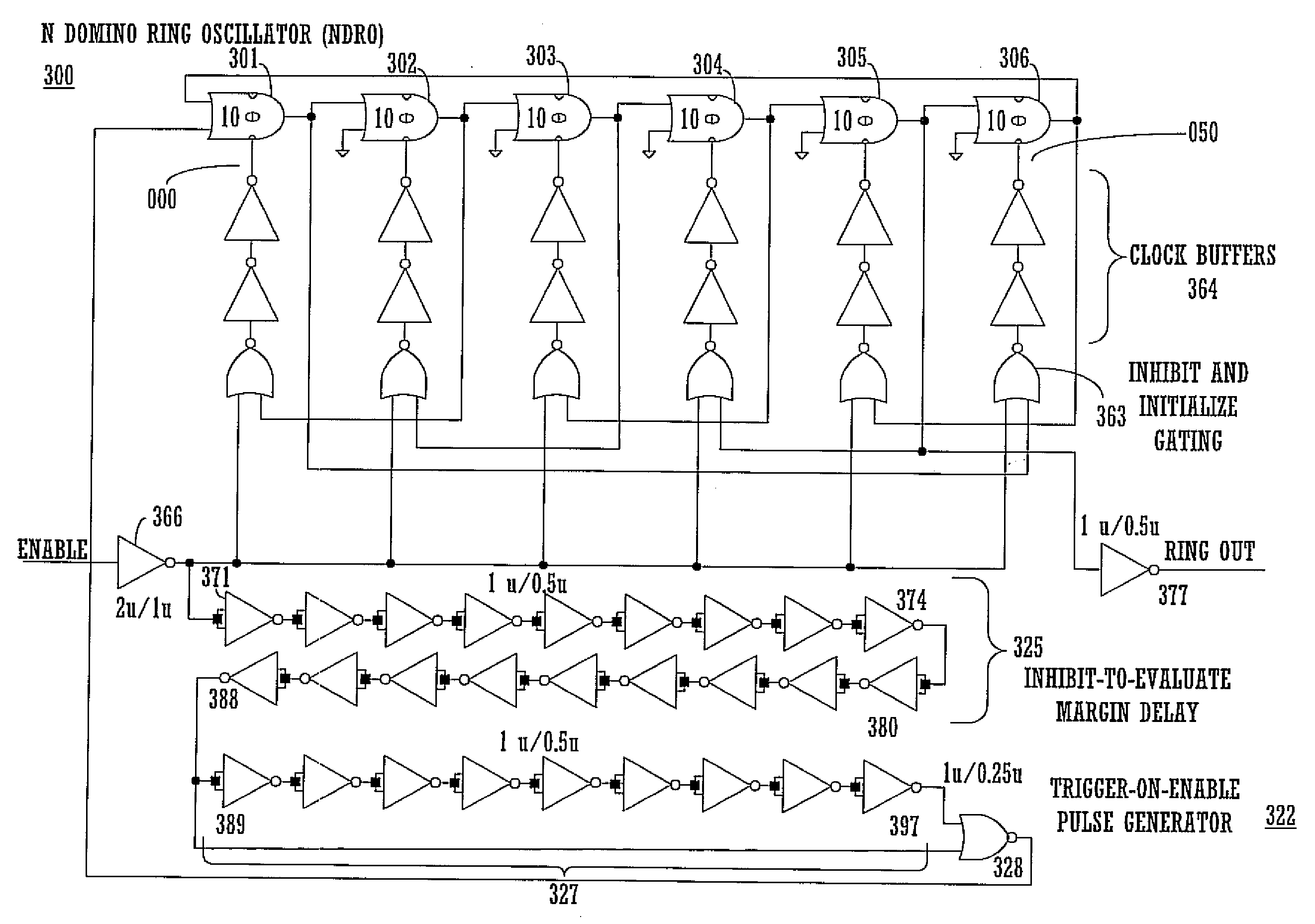

Dynamic ring oscillators

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

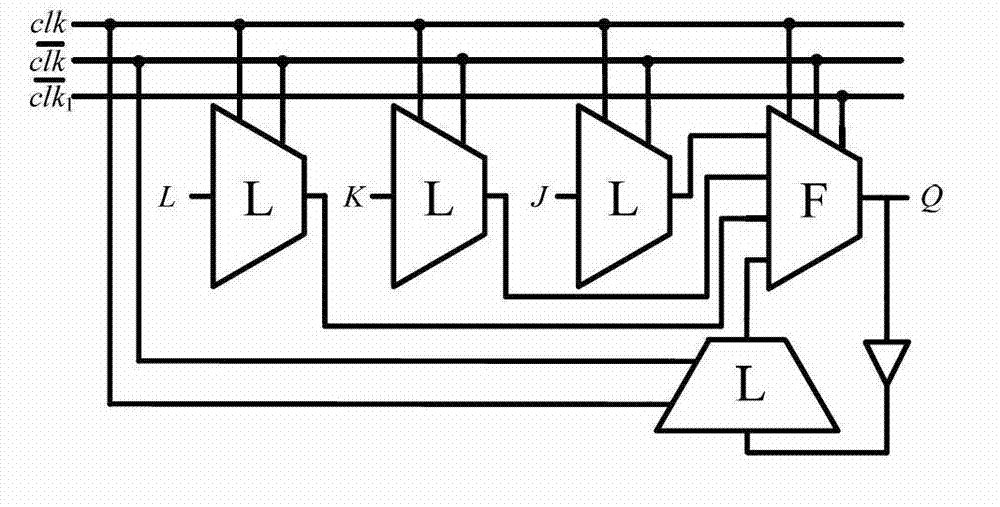

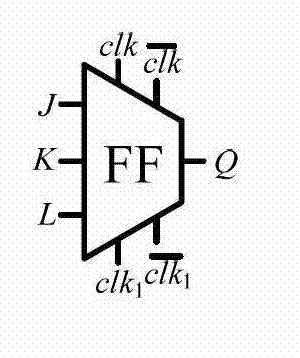

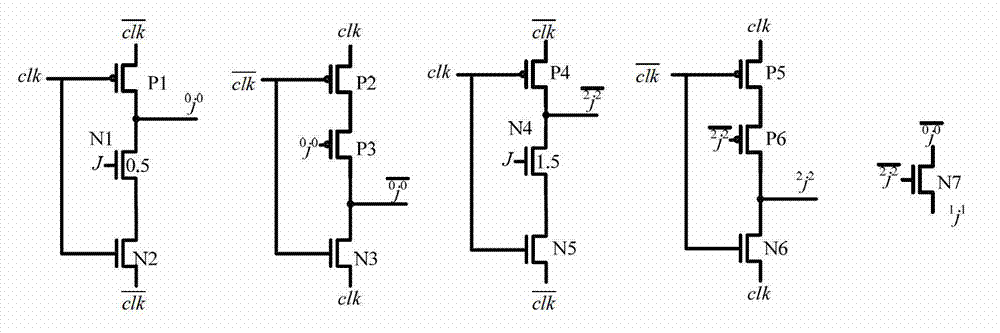

Three-valued thermal-insulation domino direct circulation valve and reverse circulation valve

ActiveCN102857215AHighly integratedHigh densityLogic circuits characterised by logic functionElectric pulse generatorThermal insulationInformation density

The invention discloses a three-valued thermal-insulation domino direct circulation valve and a three-valued thermal-insulation domino reverse circulation valve which respectively comprise a three-valued low-power dissipation domino JKL trigger, wherein each three-valued low-power dissipation domino JKL trigger consists of a first three-valued thermal-insulation domino text calculation circuit, a second three-valued thermal-insulation domino text calculation circuit, a third three-valued thermal-insulation domino text calculation circuit, a fourth three-valued thermal-insulation domino text calculation circuit and a basic three-valued JKL trigger circuit; thermal-insulation logic, multi-valued logic and multi-domino circuits are combined together through the first to fourth three-valued thermal-insulation domino text calculation circuits, thus realizing a three-valued low-power dissipation domino JKL trigger; and the three-valued thermal-insulation domino direct circulation valve and the three-valued thermal-insulation domino reverse circulation valve have the advantages of being high in circuit integration and information density and low in power dissipation on the basis of the three-valued low-power dissipation domino JKL trigger.

Owner:NINGBO UNIV

Clockless return to state domino logic gate

A clockless return to state domino logic gate including a domino circuit and an input circuit. The domino circuit asserts s preset node and an enable node to a first logic state and asserts an output node and a reset node to a second logic state in a preset state, and switches to a latch state when the preset node is pulled to the second state. In the latch state, the domino circuit pulls the output node to the first logic state and pulls the enable node to the second logic state. The domino circuit resets back to the preset state when the first reset node is pulled to the first logic state. The input circuit controls the domino circuit based on collective state of input signals, and is configured to perform a selected logic function using at least one return to state signal without use of a clock signal.

Owner:VIA TECH INC

Ultra-low power consumption three-valued counting unit and multi-bit counter based on Domino circuit

ActiveCN103095288ALogical function is correctReduce power consumptionCounting chain pulse countersLevel structureSwitching signal

The invention discloses an ultra-low power consumption three-valued counting unit and a multi-bit counter based on a Domino circuit. The three-valued counter is designed with a switch-signal theory as guidance and combining the heat insulation logic, the multi-value logic and a Domino circuit. A three-valued positive cycle gate circuit switch-level structure with an Enable Pin is deduced first, a three-valued heat insulation Domino text arithmetic circuit and a heat insulation Domino bumper are combined to obtain a three-valued counting unit (namely, a single-bit three-valued counter). Then, a three-valued counter Enable signal generating circuit structural formula is deduced, and the three-valued counting unit and the three-valued counter Enable signal generating circuit are in cascade connection to obtain the three-valued multi-bit counter. According to Spice software simulation, the ultra-low power consumption three-valued four-bit counter based on the Domino circuit has the advantages of being correct in logic function and capable of saving power consumption by approximately 63% compared with a traditional three-valued four-bit Domino counter.

Owner:HANGZHOU HANGUANG ILLUMINATION

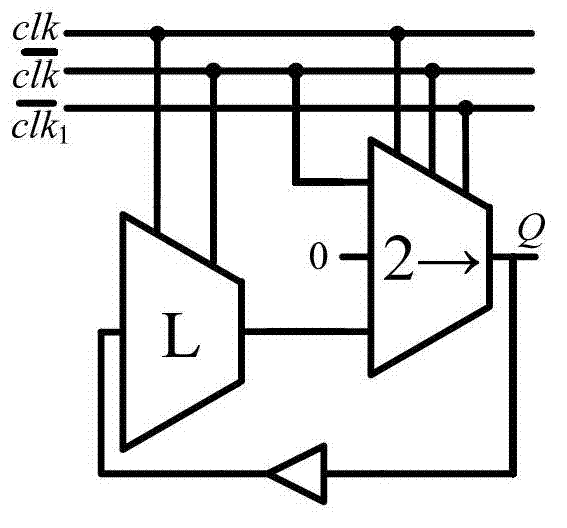

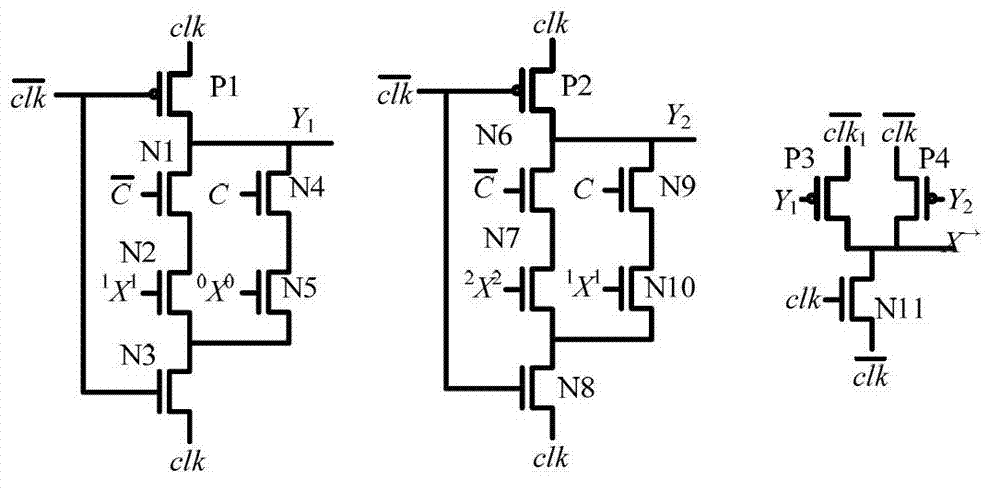

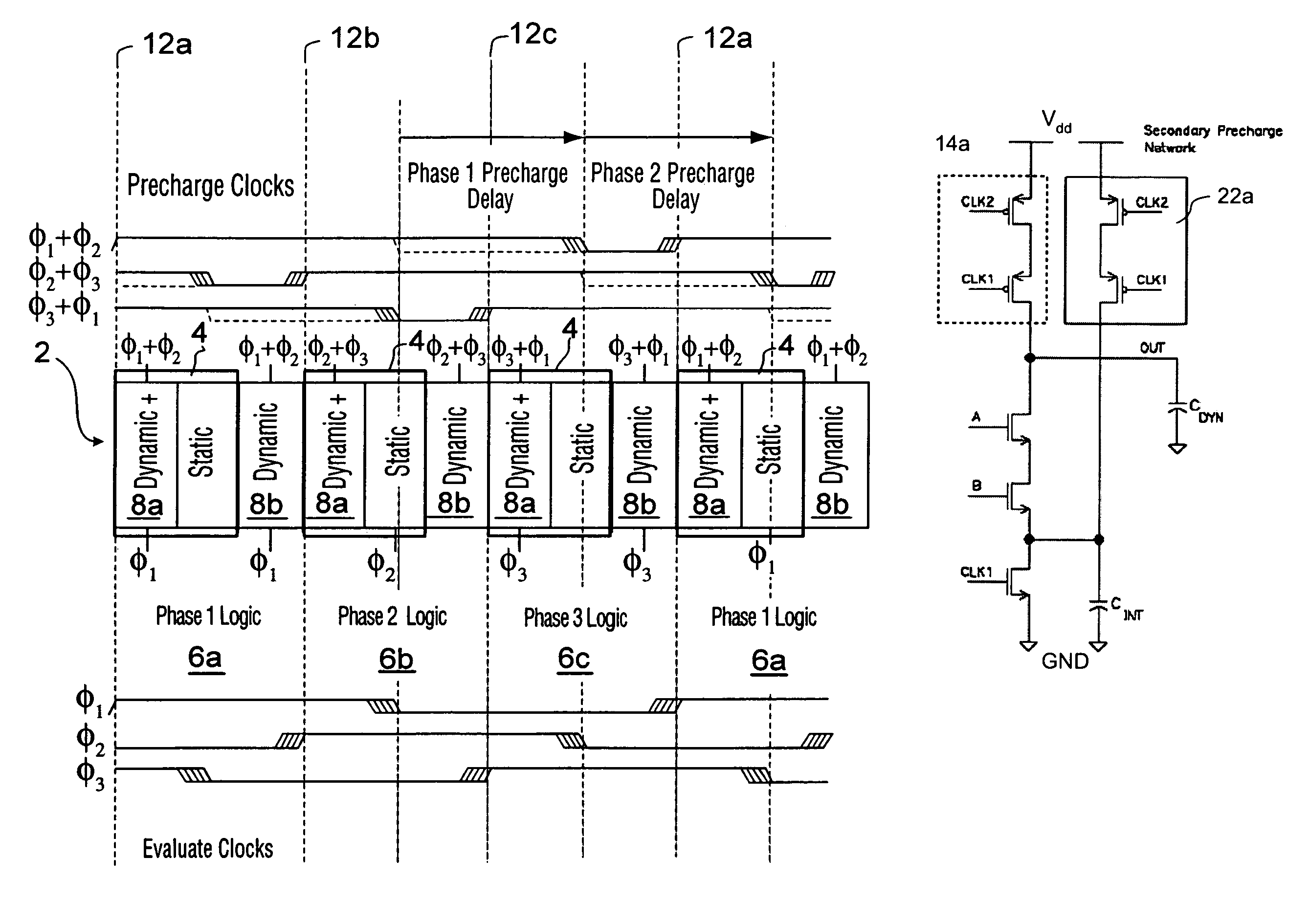

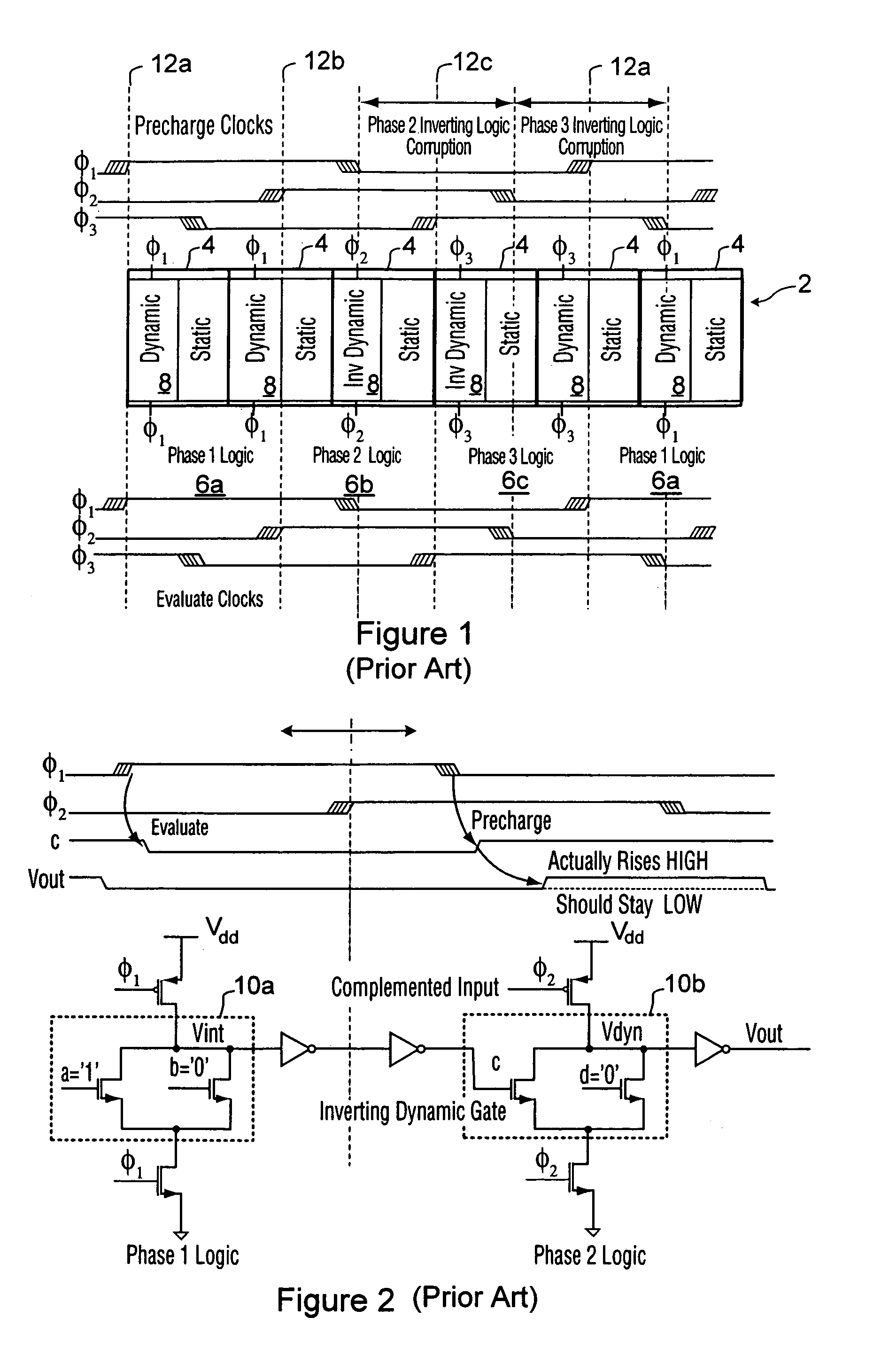

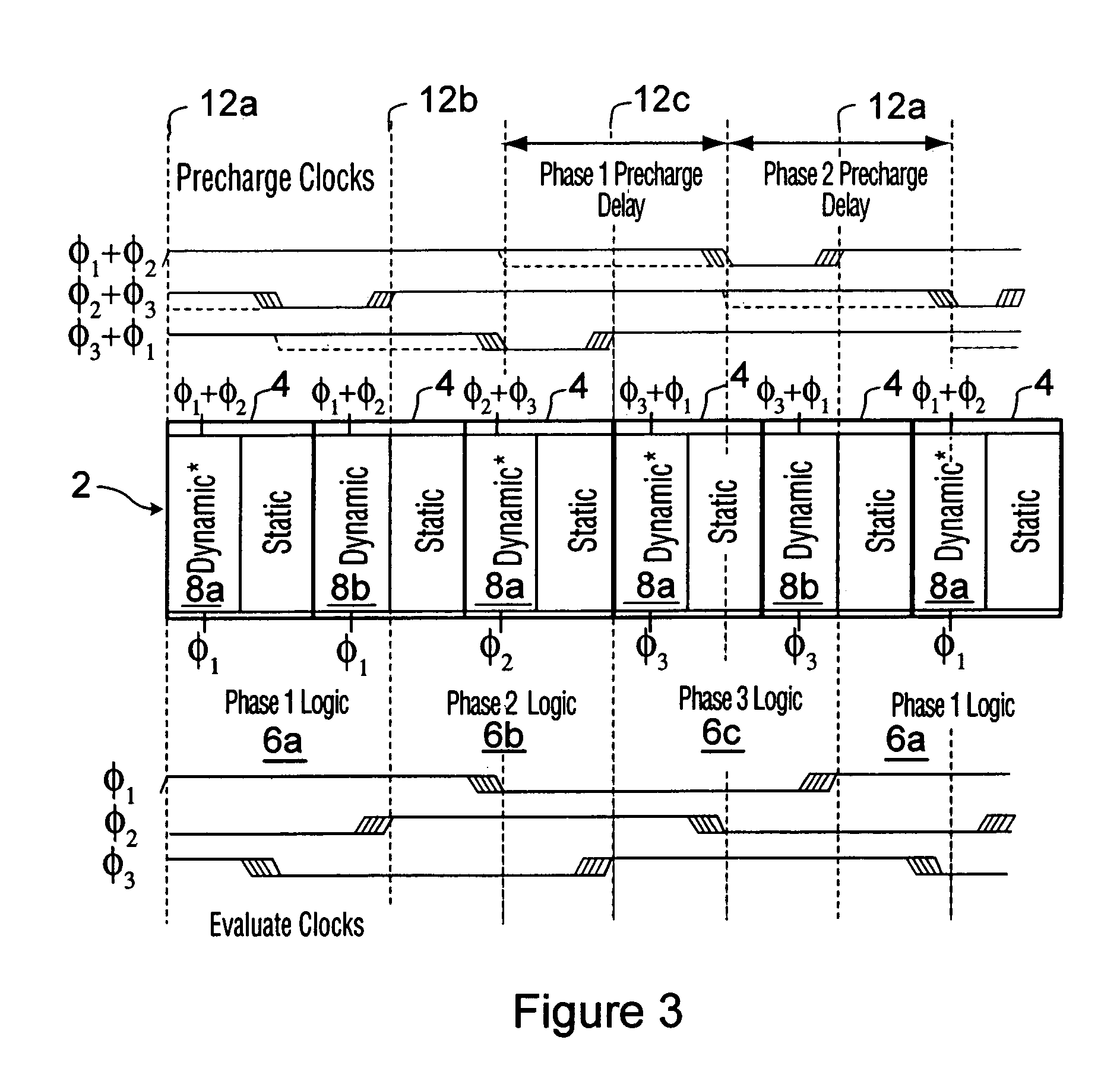

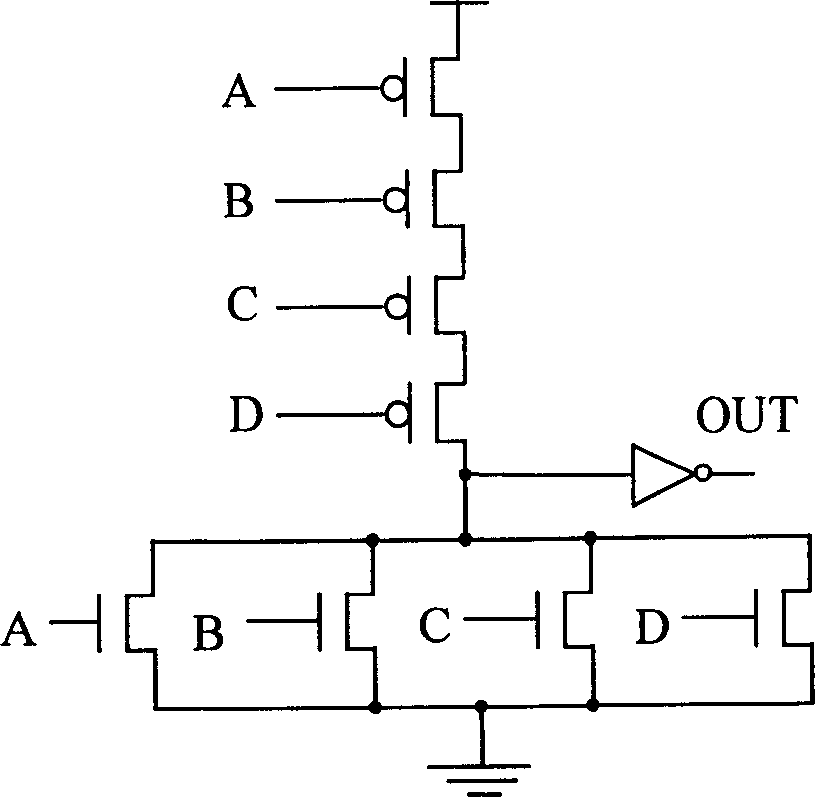

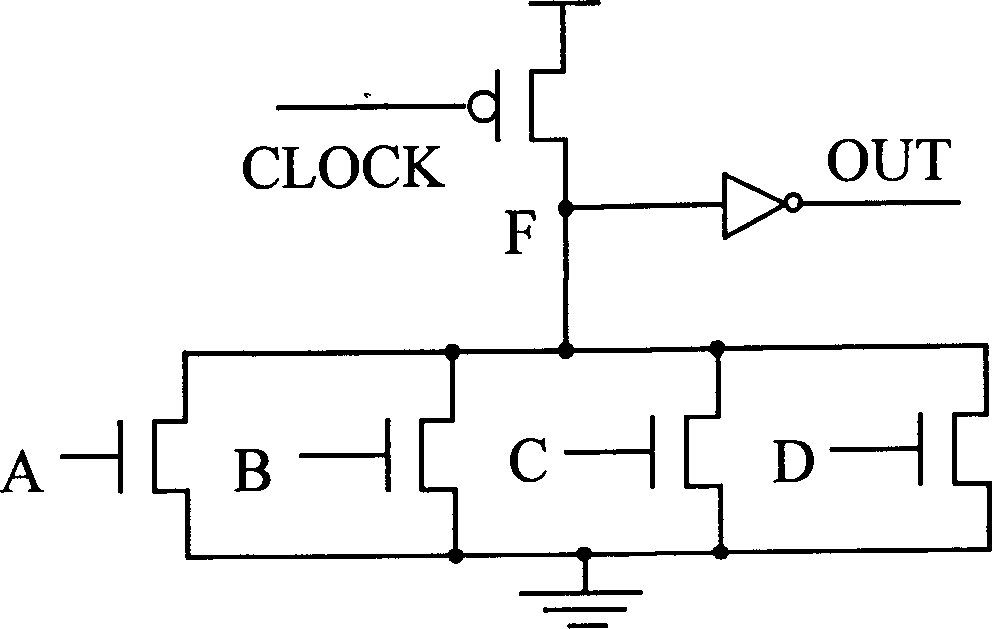

Clock logic domino circuits for high-speed and energy efficient microprocessor pipelines

ActiveUS7123056B2Reduce power consumptionGuaranteed high speed operationLogic circuitsNon-monotonic logicDomino logic

A systematic method for single-rail domino logic circuits is provided, in which inverting and non-monotonic logic functions can be integrated into a pipelined system with almost zero overhead. This logic family, called Clock Logic (CL)-domino is functionally complete while tolerating skew and minimizing the number of clock phases that must be distributed. Simulation results for a CL-domino ALU at 1-GHz under high skew (1-FO4) conditions, shows a power reduction of 41% over the same ALU implemented in dual-rail skew-tolerant domino logic. This power reduction incurs no performance penalty over dual-rail techniques, although in some cases additional design effort is required.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Novel anti-noise high-speed domino circuit

InactiveCN1808904AHigh speedReduce parasitic capacitanceLogic circuitsElectric currentVery high frequency

This invention belongs to large scale digital integration circuit technique field and relates to one new anti-noise domino digital logic circuit, which Uses one thin impulse generator effective control dynamic points to make the output dynamic point keep original level in the noise situation to realize strong anti-noise property and Adopts pull network parallel structure to eliminate current compactor to work under high frequency.

Owner:FUDAN UNIV

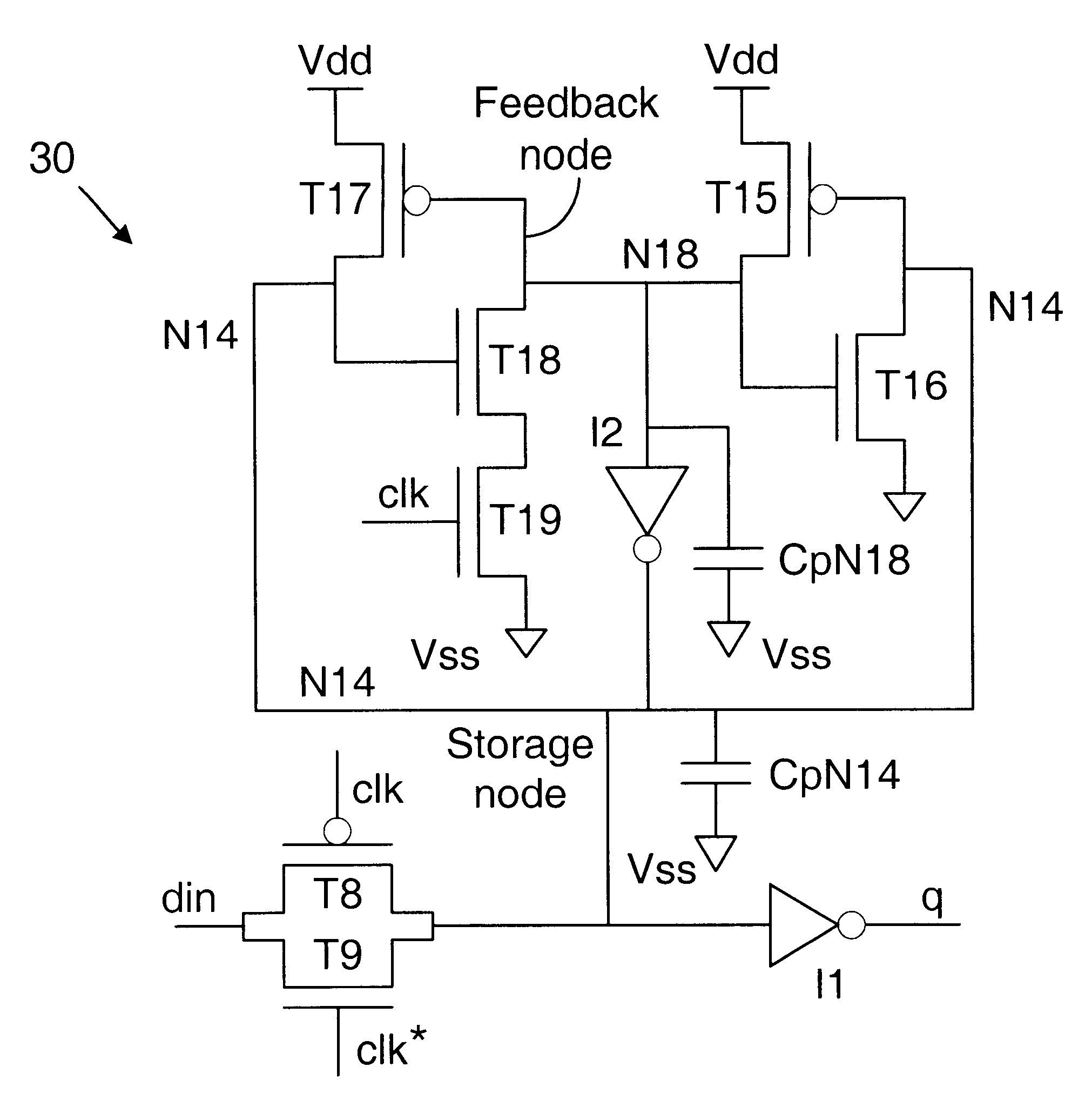

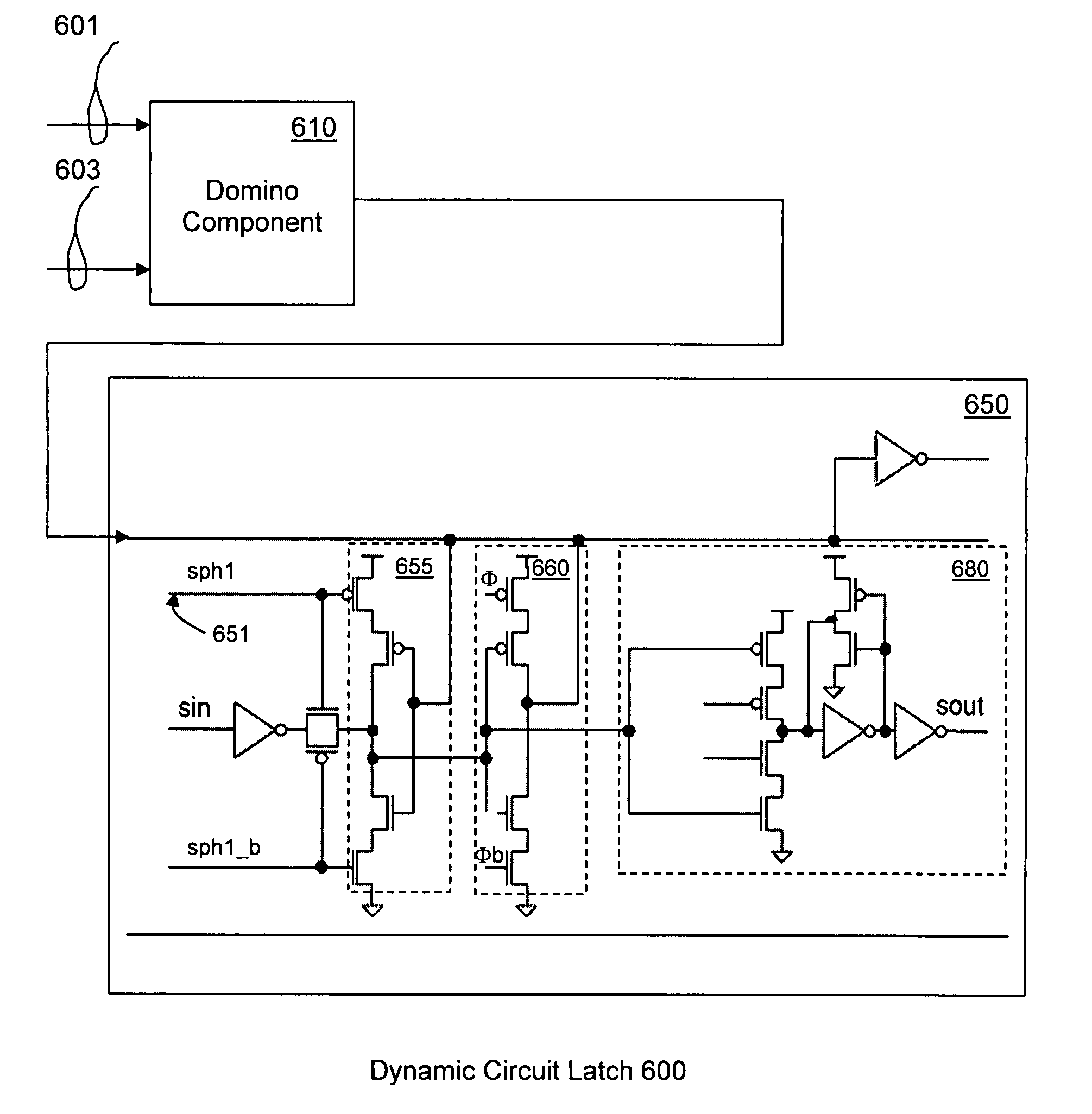

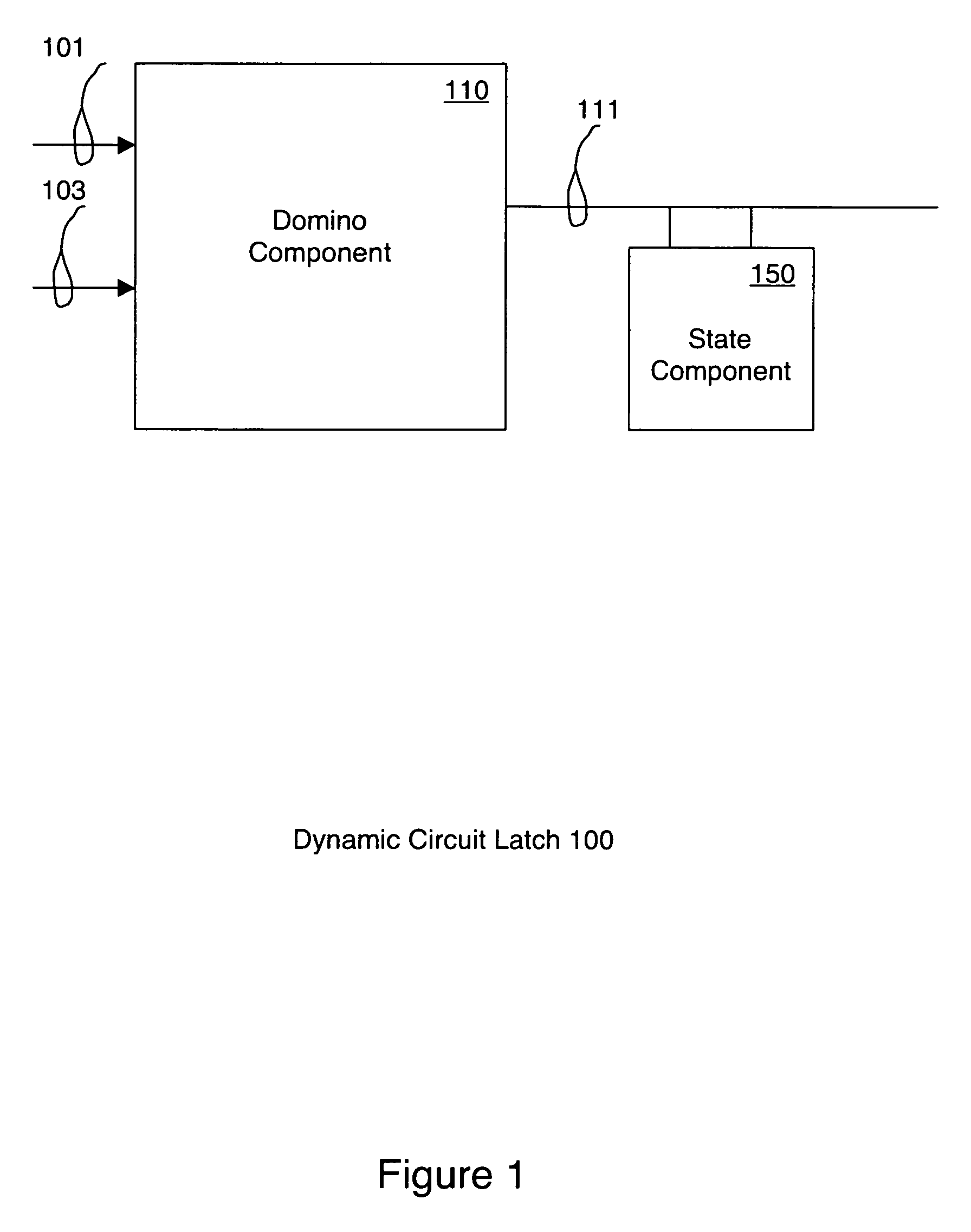

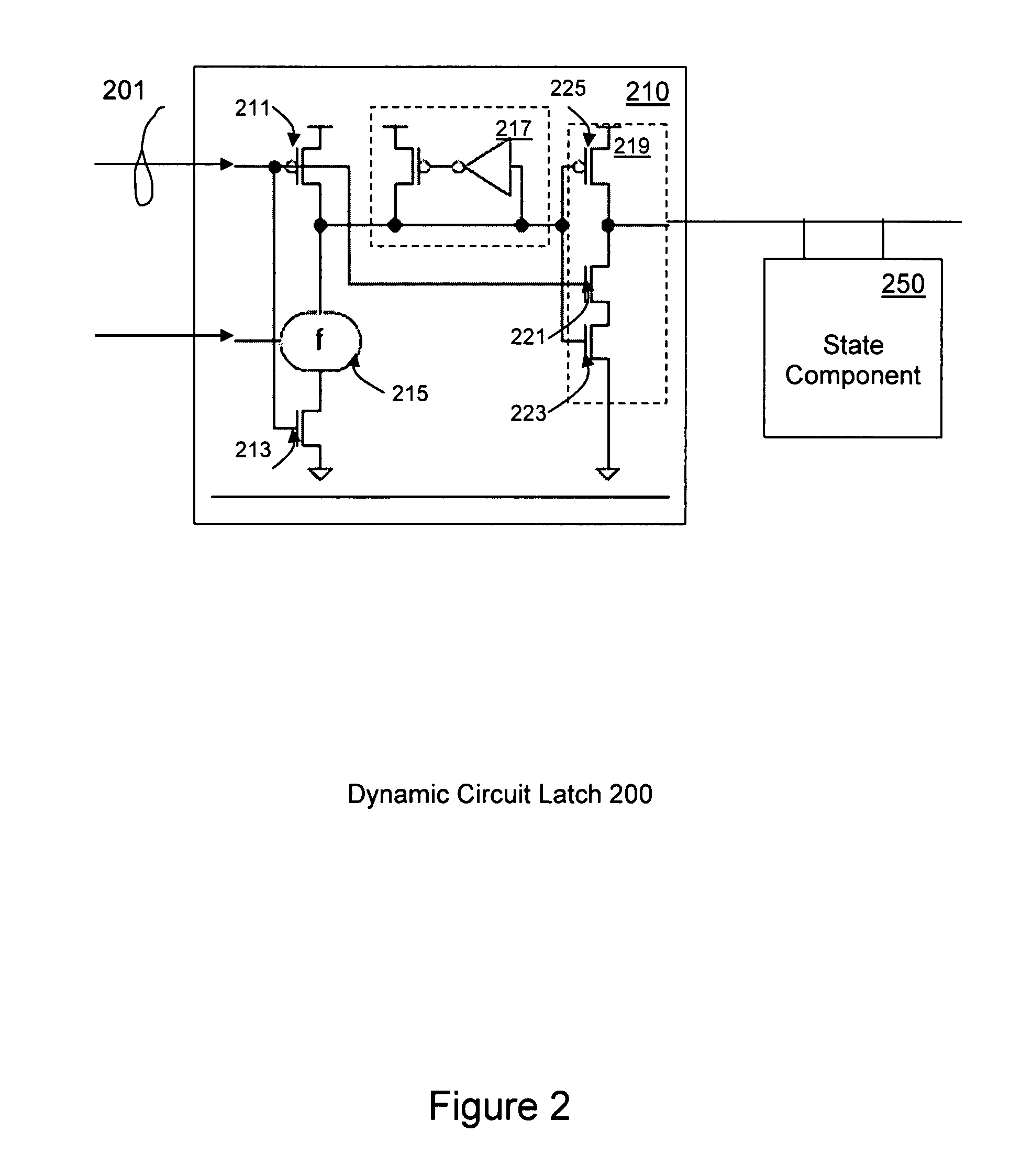

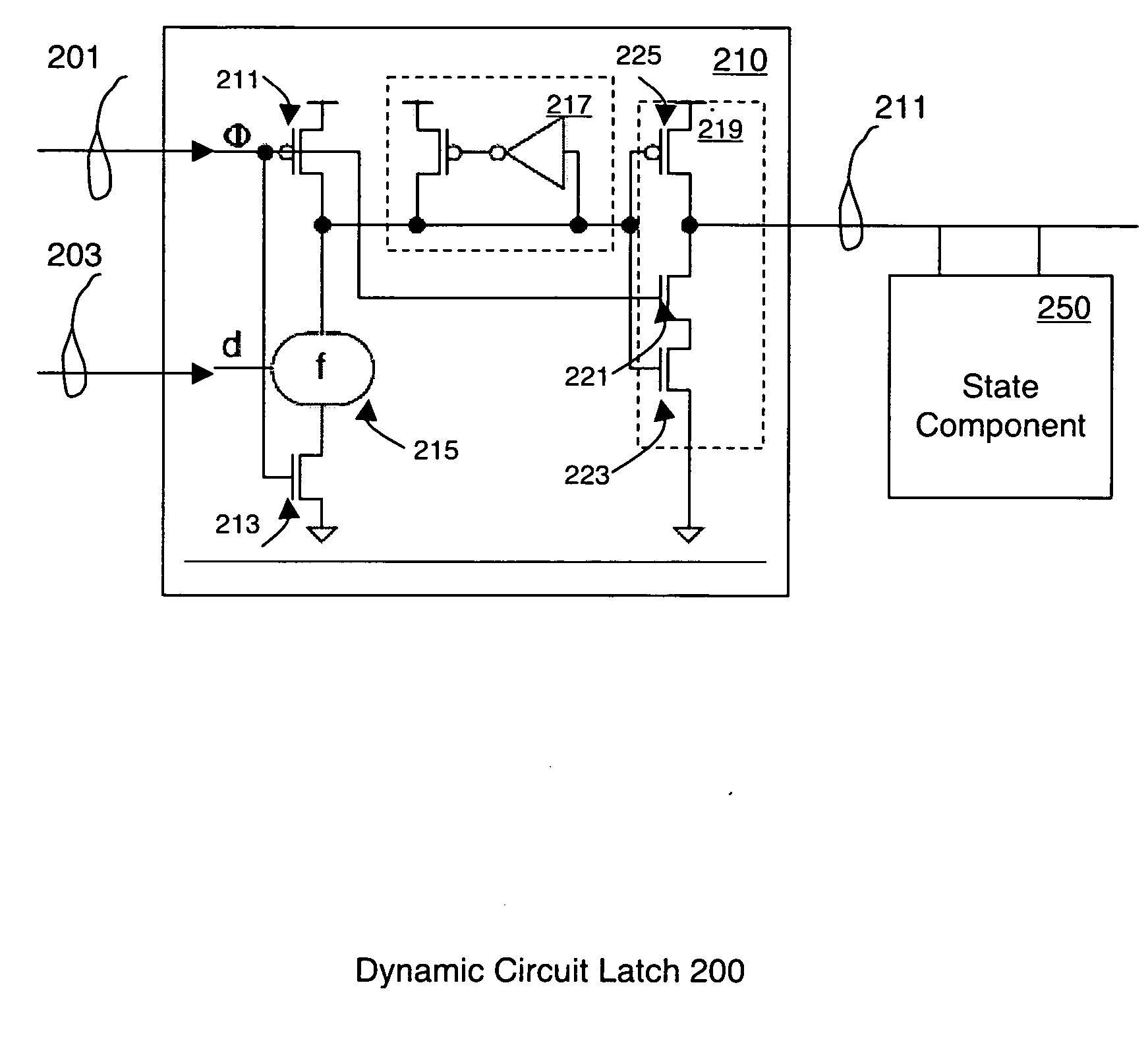

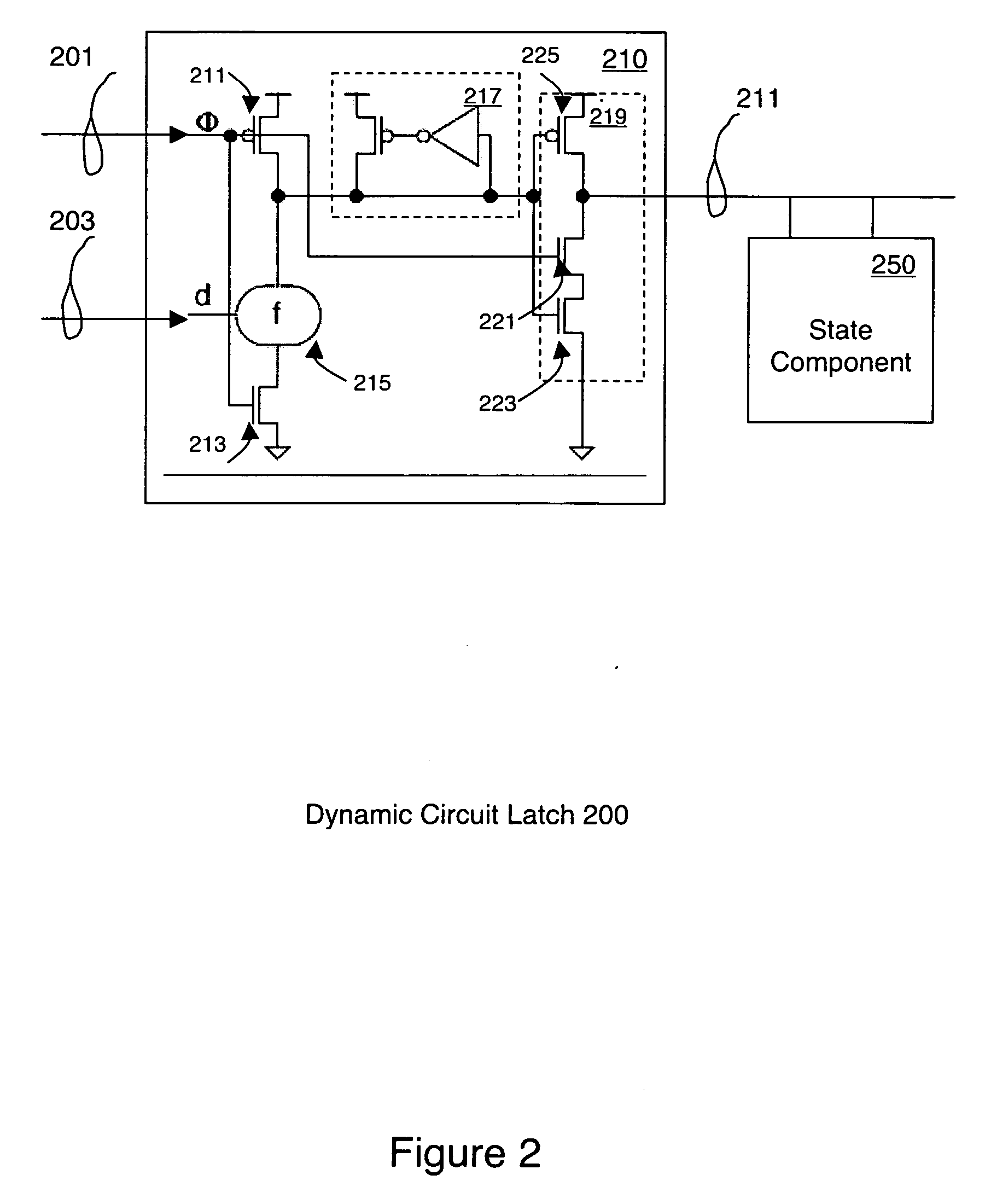

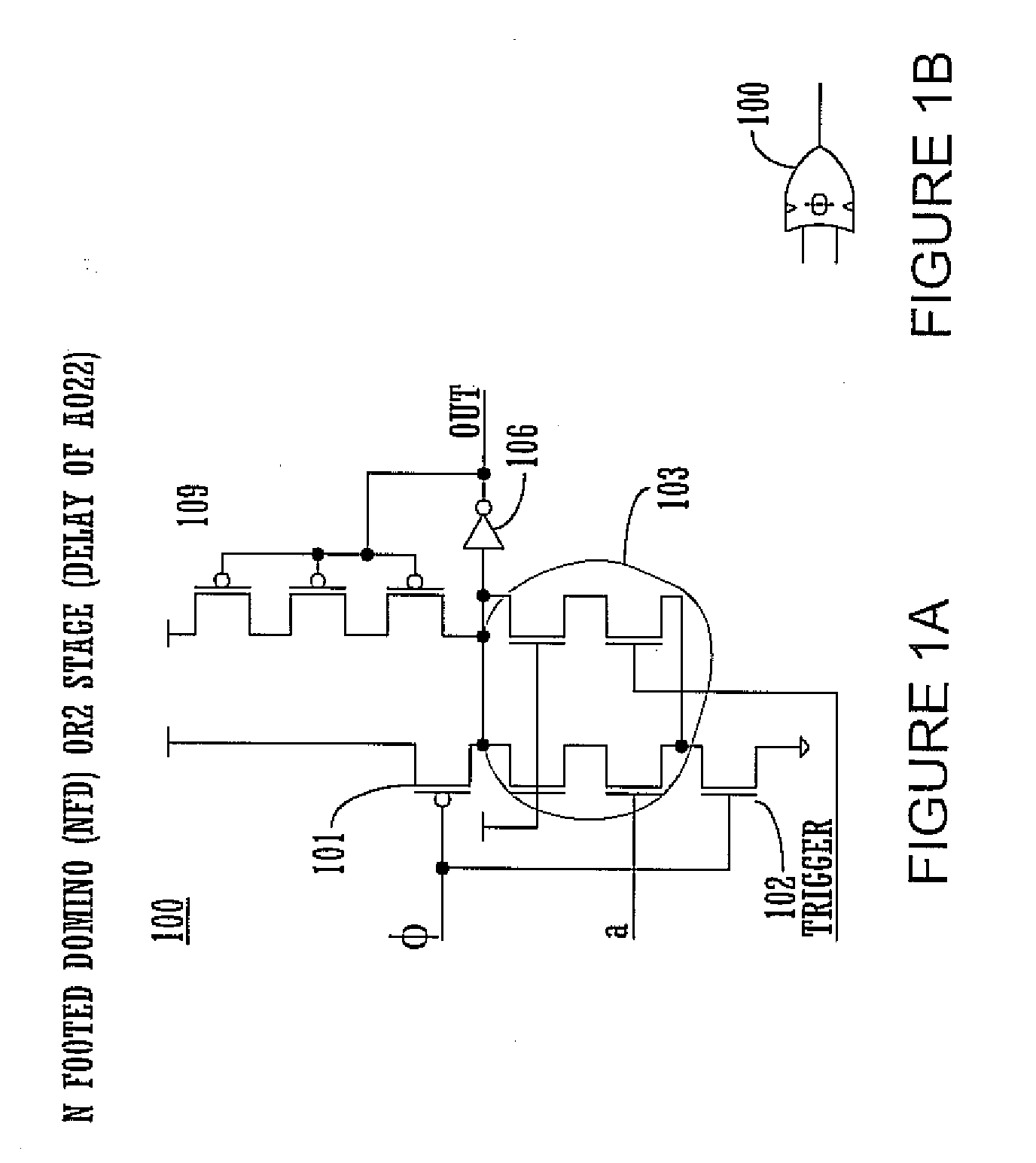

Scannable dynamic circuit latch

ActiveUS7663408B2Logic circuits characterised by logic functionLogic circuits using elementary logic circuit componentsElectrical and Electronics engineeringDynamic circuit

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Scannable dynamic circuit latch

ActiveUS20070008012A1Logic circuits characterised by logic functionLogic circuits using elementary logic circuit componentsEngineeringElectrical and Electronics engineering

A dynamic circuit latch, having the functionality of a domino circuit and a transparent latch, without the delay associated with the inclusion of a separate series latch element. Embodiments include a fast scannable footed Domino dyanmic latch. Also described is a fast scannable delay reset Domino dynamic latch. A fast scannable compound Domino dynamic latch is also described.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Clockless return to state domino logic gate

A clockless return to state domino logic gate is disclosed responsive to multiple input nodes including at least one return to state node. A domino circuit presets a preset node to a second state. The domino circuit switches to a latch state and switches an output node when the preset node is pulled to a first state, and resets back to the preset state and switches the output node back to its default state when a reset node is pulled to the second state. An evaluation circuit pulls the preset node to the second state when the input nodes are in an evaluation state. An enable circuit enables a reset condition when the domino circuit is in its latch state. A reset circuit pulls the reset node to the first state after an evaluation event when the input nodes are no longer in the evaluation state.

Owner:VIA TECH INC

Non-clock-state regression domino logic gate and related integrated circuit and estimation method

ActiveCN102355254AIncrease contentLogic circuits using elementary logic circuit componentsDomino logicEstimation methods

The invention relates to a non-clock-state regression domino logic gate and a related integrated circuit and an estimation method. The non-clock-state regression domino logic gate responds to a plurality of input nodes comprising at least one state regression node, and a preset node is prearranged to a first state by a domino circuit. When the preset node is pulled to a second state, the domino circuit switches to a locking state and switches the state of an output node; and when a reset node is pulled to the first state, the domino circuit resets to the preset state and switches the output node to a preset value. When the above input node is in an estimation state, an estimation circuit pulls the preset node to a second state, and when the domino circuit is in a locking state, an enable circuit enables a reset condition. After an estimation event, if the rest condition is satisfied and the input node is not in an estimation state, a reset circuit pulls the rest node to a first state.

Owner:VIA TECH INC

Domino Circuit with Master and Slave (DUAL) Pull Down Paths

A domino circuit and method include a master evaluation node to which a master discharge path with a wide input AND gate is coupled and a virtual evaluation node to which an output stage and slave discharge path are coupled. A current mirror interconnects the master discharge path and the slave discharge path. The devices in the current mirror are sized so that current flowing in the master discharge path is amplified into the slave transmission path.

Owner:IBM CORP

Input-driven domino circuit design

InactiveCN103701451AReduce dynamic power consumptionReduce openingLogic circuitsEngineeringCircuit performance

The invention relates to input-driven domino circuit design. A domino circuit is structurally optimized, transistors of a clock are removed, and a clock signal is replaced by combined input data, so that dynamic power consumption can be reduced, the number of transistors of the circuit is decreased, the working time is shortened, the circuit performance is improved, and the layout area of the circuit is reduced. According to the input-driven domino circuit design, the problem of high power consumption caused by the clock is effectively solved, and the clock signal is removed from the circuit and is replaced by the combined input data, so that the turn-on and turn-off frequency of the transistors can be greatly reduced, the dynamic power consumption of the circuit is effectively reduced, and the layout area of a chip is reduced.

Owner:BEIJING UNIV OF TECH

Three-value low power consumption domino JKL trigger

InactiveCN102790602AHighly integratedHigh densityElectric pulse generatorInformation densityEngineering

The invention discloses a three-value low power consumption domino JKL trigger. The three-value low power consumption domino JKL trigger consists of a first three-value heat-insulating domino character operational circuit, a second three-value heat-insulating domino character operational circuit, a third three-value heat-insulating domino character operational circuit, a fourth three-value heat-insulating domino character operational circuit and a three-value JKL trigger basic circuit, wherein a heat-insulating logic, a multi-value logic and a domino circuit are combined together by the first three-value heat-insulating domino character operational circuit, the second three-value heat-insulating domino character operational circuit, the third three-value heat-insulating domino character operational circuit and the fourth three-value heat-insulating domino character operational circuit. The three-value low power consumption domino JKL trigger has the advantages that the circuit integration level and information density of the JKL trigger are improved; and compared with a conventional three-value domino JKL trigger, the three-value low power consumption domino JKL trigger disclosed by the invention has the characteristic that energy consumption is saved by 69 percent.

Owner:HANGZHOU MAEN TECH

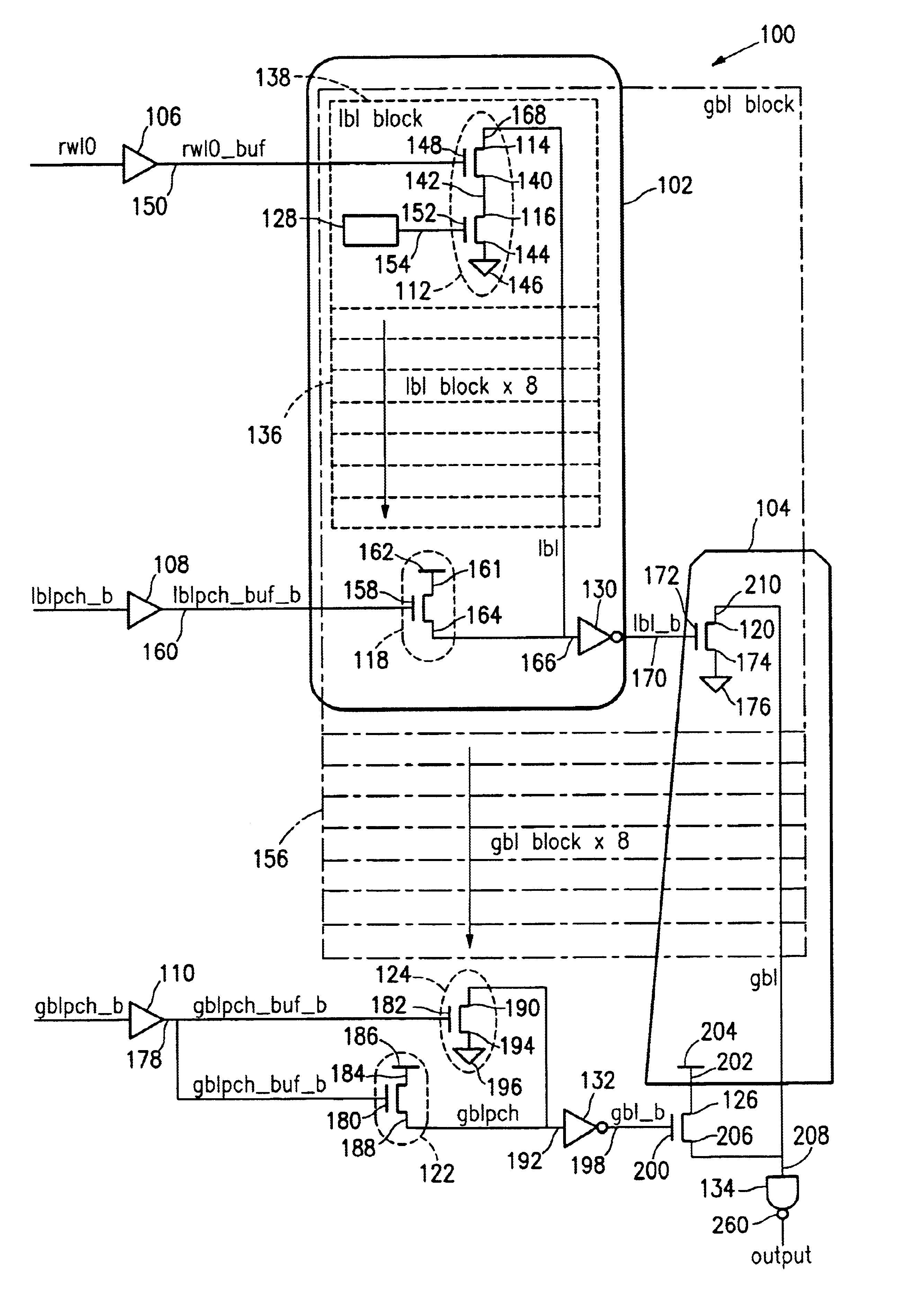

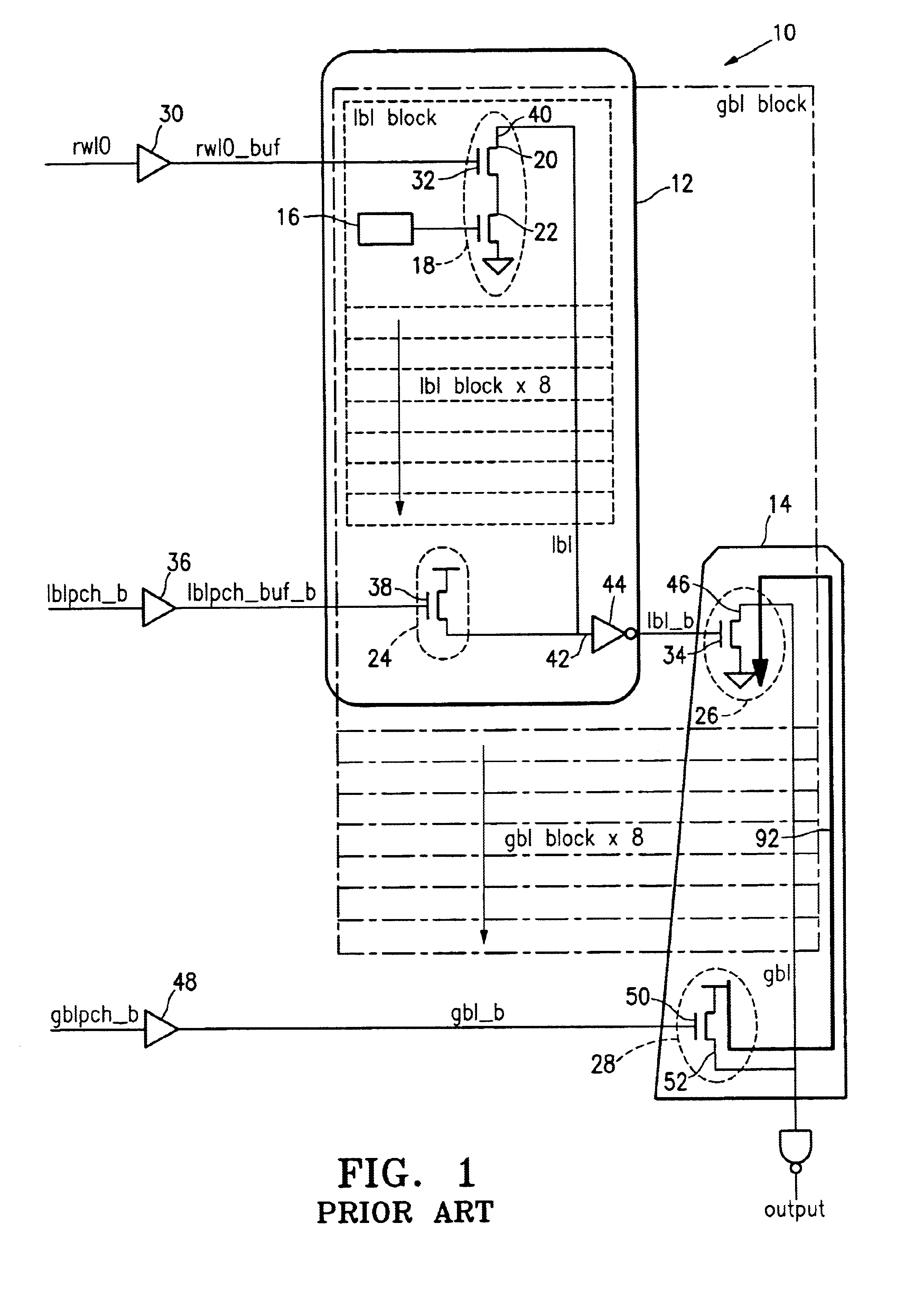

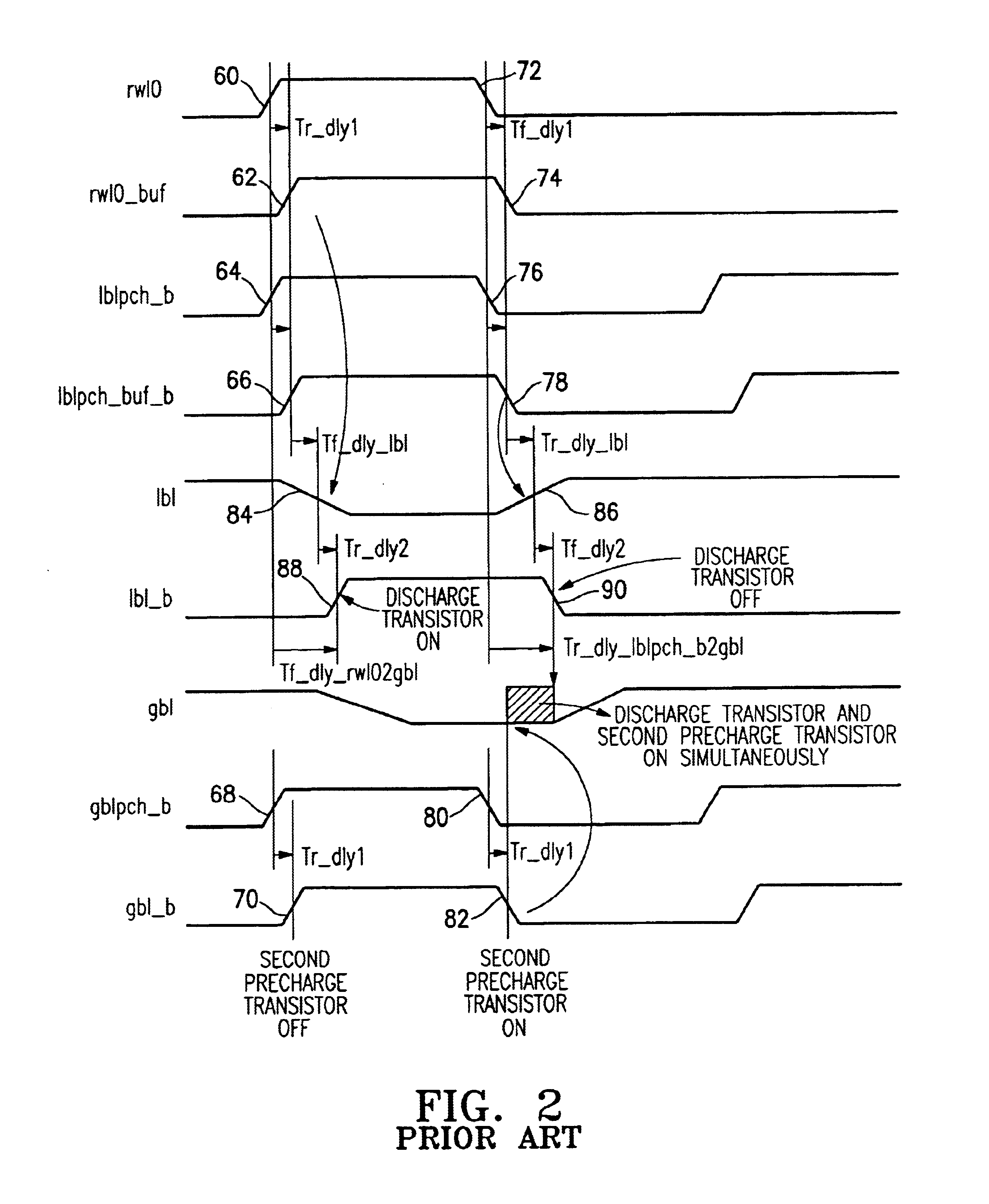

Apparatus and method for precharging and discharging a domino circuit

A domino circuit configuration includes a precharge transistor coupled to a discharge transistor, wherein the precharge transistor and the discharge transistor are not on simultaneously.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS +1

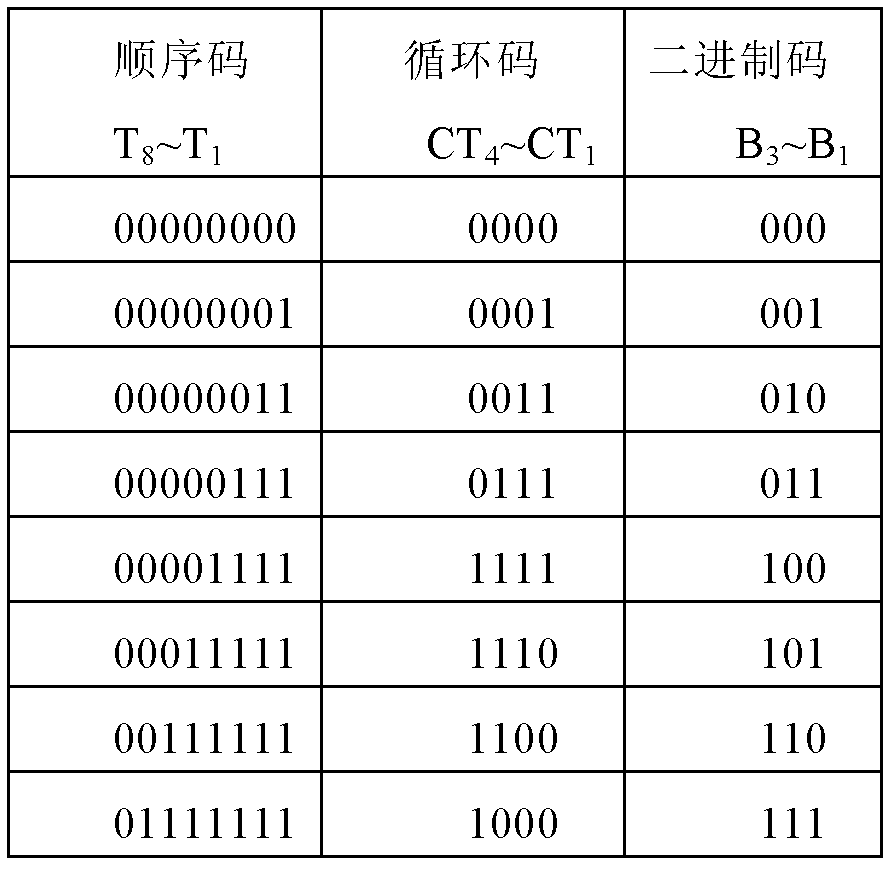

High-speed low-power-consumption cyclic code encoder

InactiveCN102868407AReduced output load capacitanceHigh speedAnalogue/digital conversionElectric signal transmission systemsCapacitanceExclusive or

The invention discloses a high-speed low-power-consumption cyclic code encoder which comprises a preprocessing module and an or module, wherein the preprocessing module is used for realizing a plurality of exclusive or logics by the aid of a plurality of domino circuits, the domino circuits receive a clock signal and are provided with a plurality of output ends, and the or module is used for realizing or logics and comprises a plurality of MOS (metal oxide semiconductor) transistors in parallel connection, and grid electrodes of the MOS transistors are connected to the output ends of the domino circuits. By the aid of the cascade domino circuits, output load capacitance can be decreased, so that speed is increased, and power consumption is reduced.

Owner:AEROSPACE INFORMATION

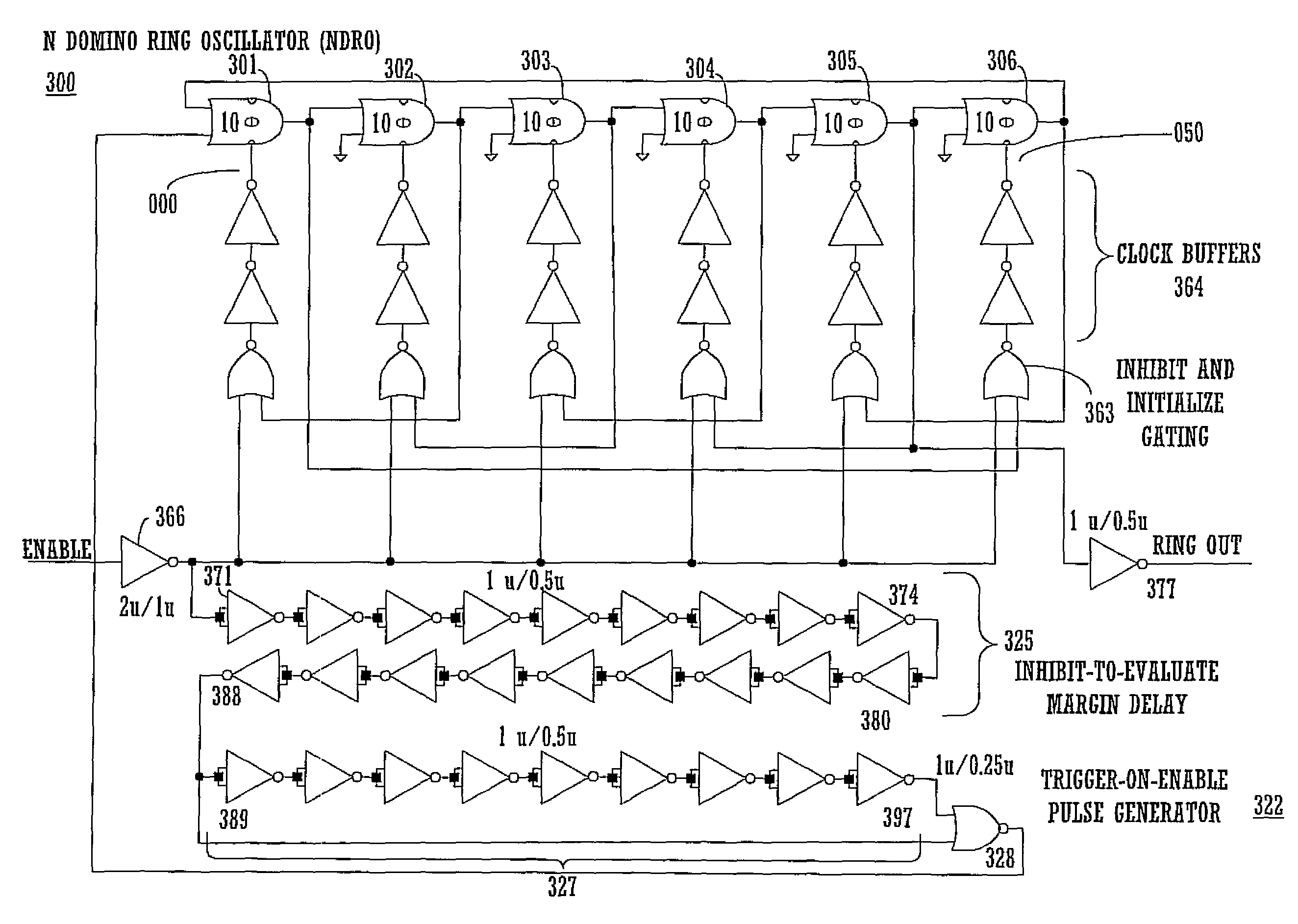

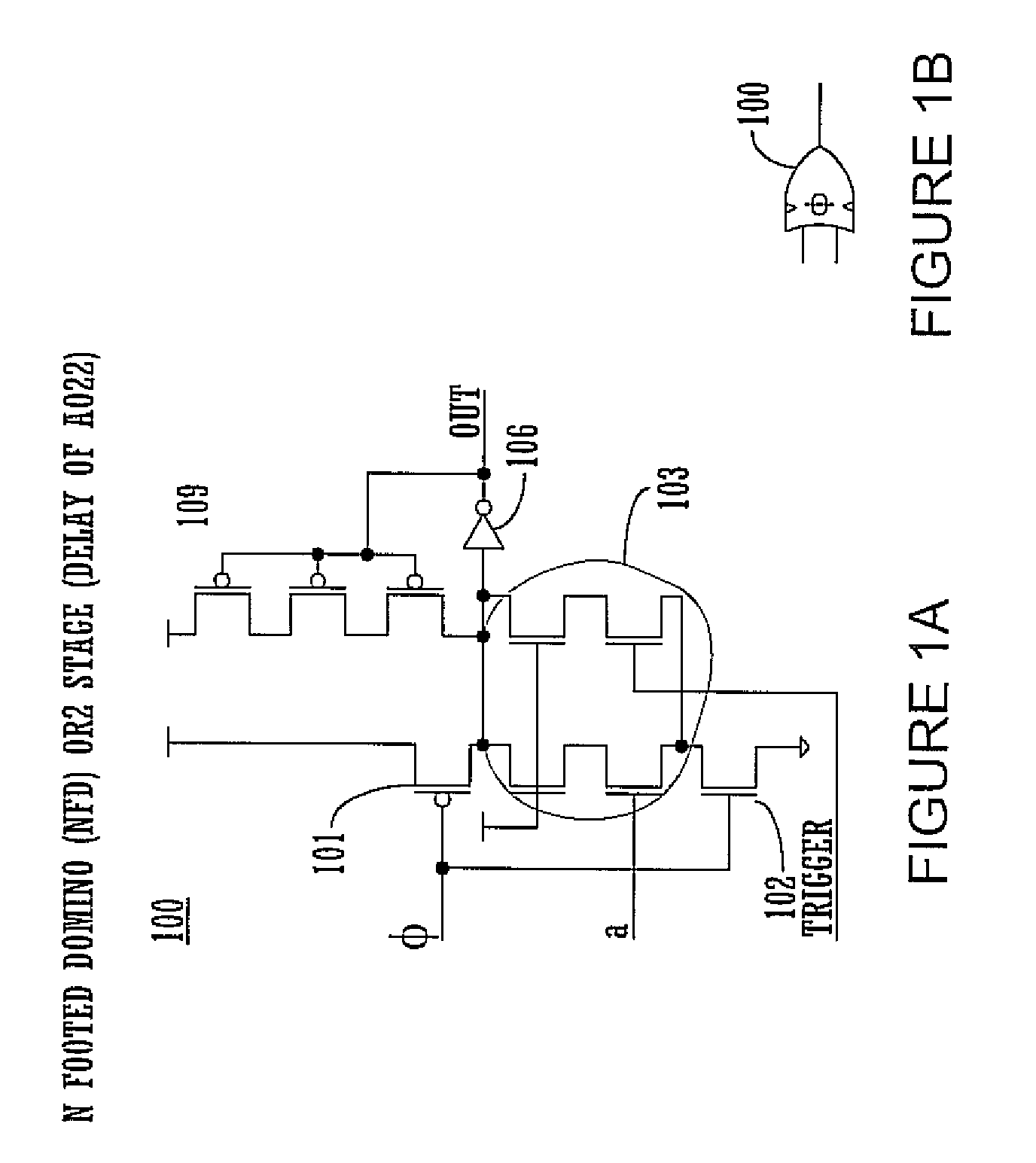

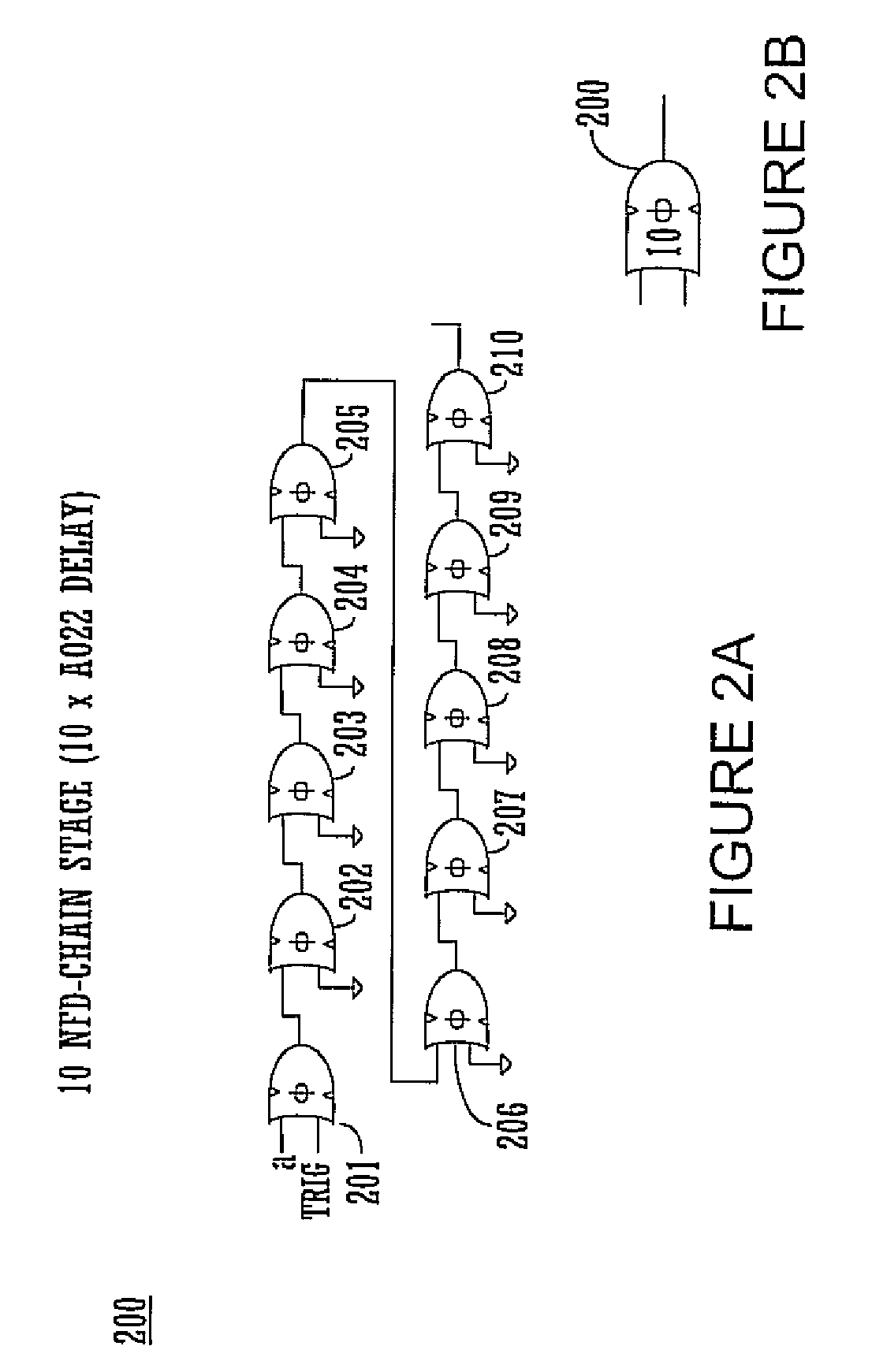

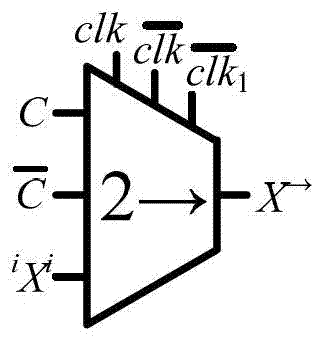

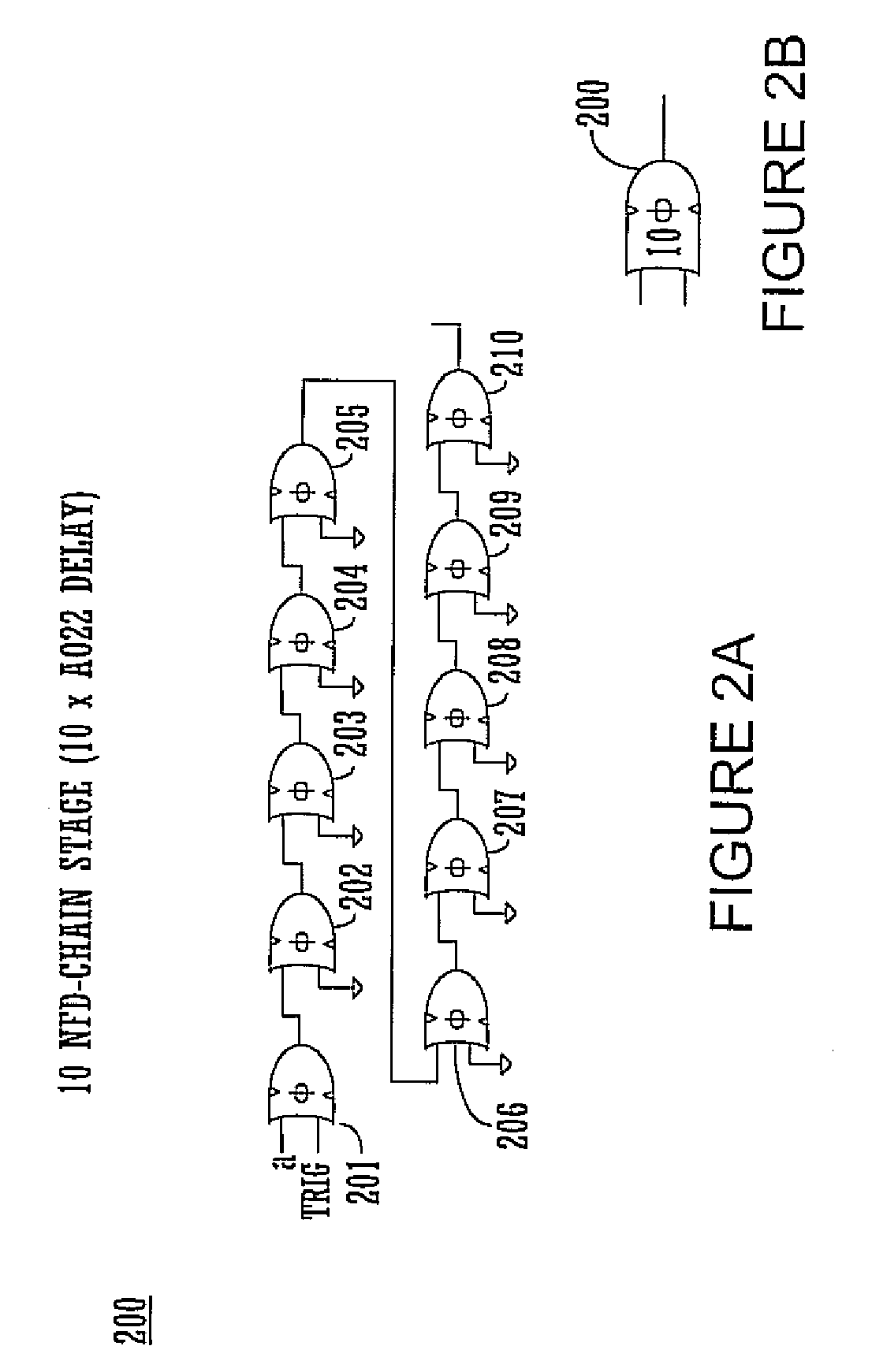

Dynamic Ring Oscillators

ActiveUS20080303600A1Easy to observeEasily measured electrical characteristicPulse generation by logic circuitsFrequency analysisRing circuitSoftware engineering

A dynamic oscillating ring circuit is described, which has multiple non-inverting domino circuits, each having a signal input, a trigger input, inputs for charge state clock and clocked cutoff and an output inverter. A number of the domino circuits are coupled in series, the output of one feeding the input of the next, to form a chain, which form stages of the ring. A number of the stages are coupled in series, the output of one feeding the input of the next, to form the ring. The first domino circuit of said chain receives a logic signal input and a single trigger input for the chain. Within the ring, the output of each stage feeds the input signal to the next stage and is fed back to clock an earlier stage to allow the ring to oscillate.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC