Dual-threshold domino circuit with optimal gate control vector used in low-power consumption VLSI (very large scale integration)

A domino, dual-threshold technology, applied in logic circuits, electrical components, pulse technology, etc., to achieve the effect of reducing leakage power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0021] This embodiment applies the optimal gating vector to a double-threshold domino OR gate.

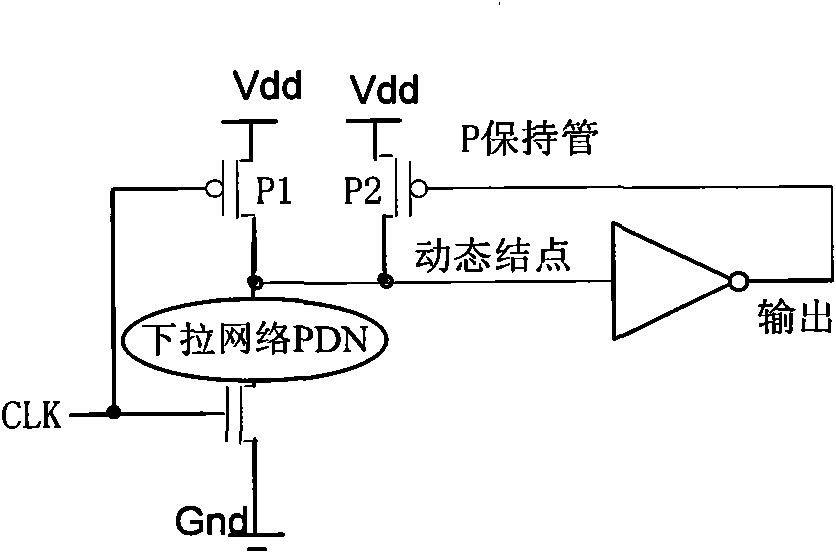

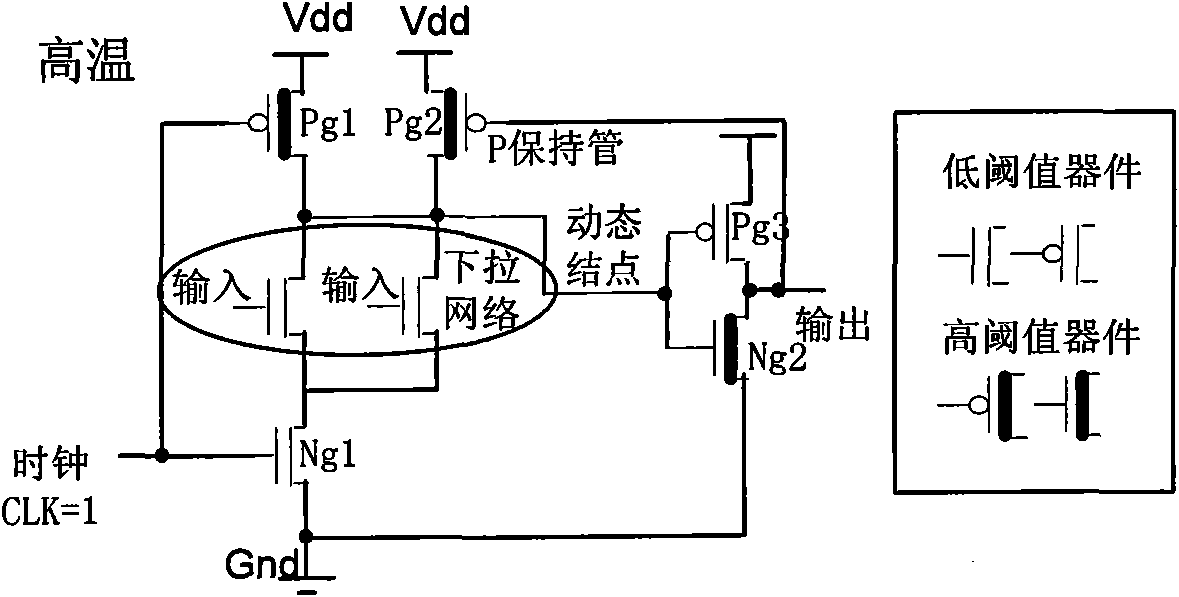

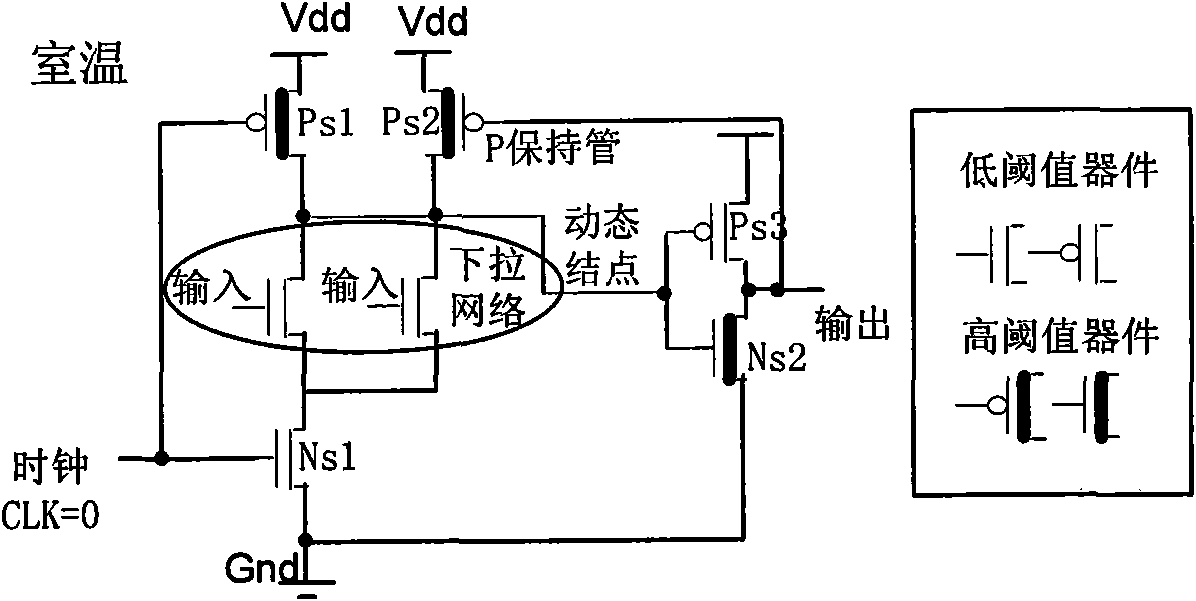

[0022] Such as figure 2 and 3 Shown is the optimal gating vector for a dual-threshold domino OR gate, which consists of several parts:

[0023] Such as figure 2 As shown, at high temperature, including input signal terminal, output signal terminal, clock signal terminal, pre-charge tube Pg1, holding tube Pg2, clock tube Ng1, Pg3 and Ng2 in the output static inverter, and pull-down network (PDN) in NMOS transistors, wherein the NMOS transistors in the pre-charging transistor, the holding transistor and the static inverter are high-threshold transistors, and the rest of the transistors are low-threshold transistors. In sleep mode, the input is high level 1, and the clock signal is high level 1.

[0024] Such as image 3 As shown, at room temperature, i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More