Non-clock-state regression domino logic gate and related integrated circuit and estimation method

A state regression and clockless technology, applied in the field of logic circuits, can solve the problem of slow operation of semiconductor logic gates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

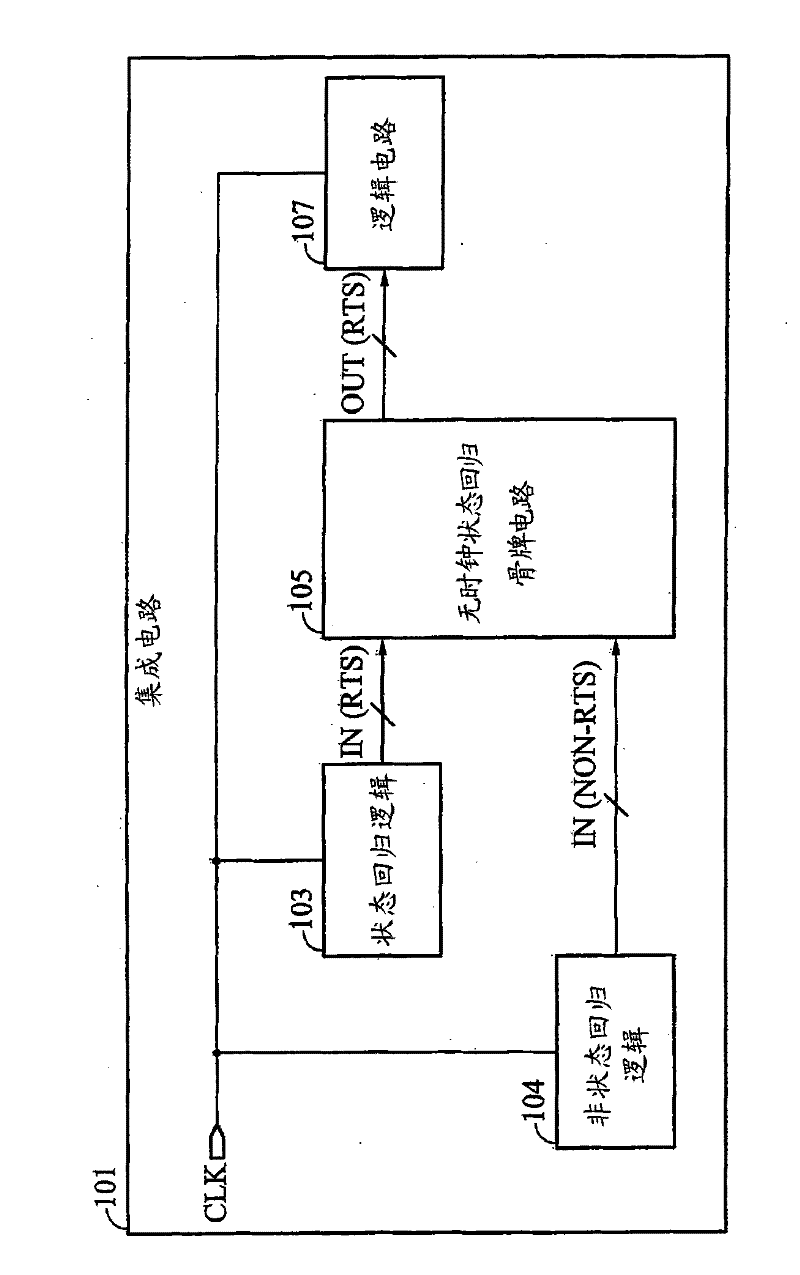

[0111] The following description will help those skilled in the art to make and apply the invention disclosed in this specification to specific applications and conditions. Those skilled in the art may develop various modifications according to the embodiments disclosed below, and the techniques disclosed in the specification may also be implemented in other embodiments. Therefore, the scope of the present invention is not intended to be limited to the specific embodiments shown or described below, but should in fact be interpreted with the broadest scope of the techniques and features disclosed. The inventors have discovered the industry's need for high-speed, efficient logic operations that do not rely on clock signals. Therefore, the inventor has developed a state regression domino logic gate without a clock signal, which is provided below Figure 1 to Figure 17 discuss.

[0112] figure 1 As a simplified block diagram, a chip (or an integrated circuit, IC) 101 is illustr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More