Novel anti-noise high-speed domino circuit

A domino and anti-noise technology, applied in logic circuits, electrical components, pulse technology, etc., can solve problems affecting speed and anti-noise ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

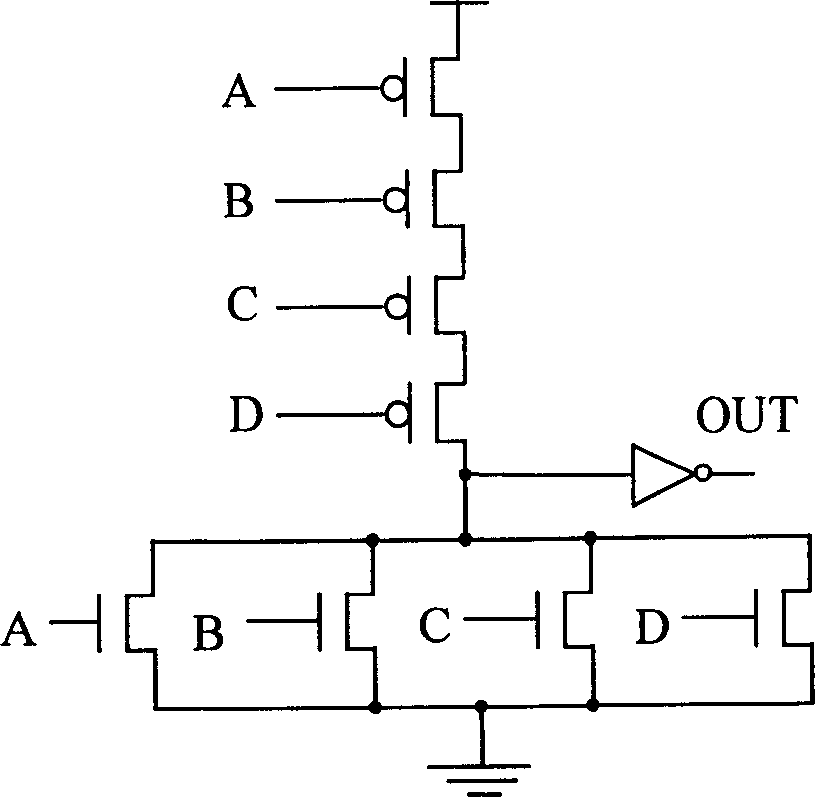

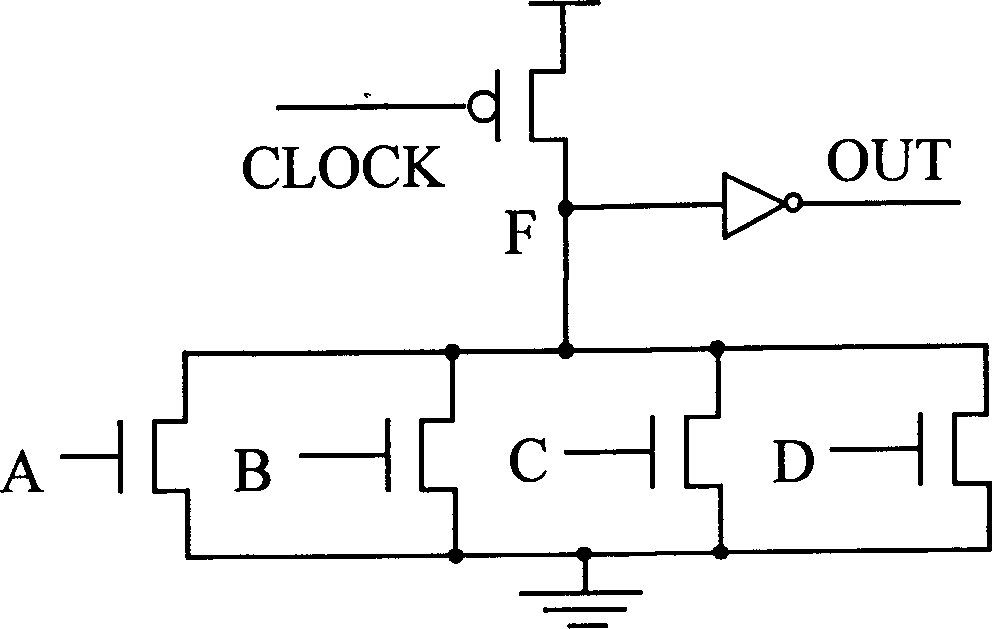

[0022] Figure 1 to Figure 4 This has been briefly explained in the background information.

[0023] Figure 5 It is a general block diagram of the structure proposed according to the working principle, which has been described in detail in the content of the invention above.

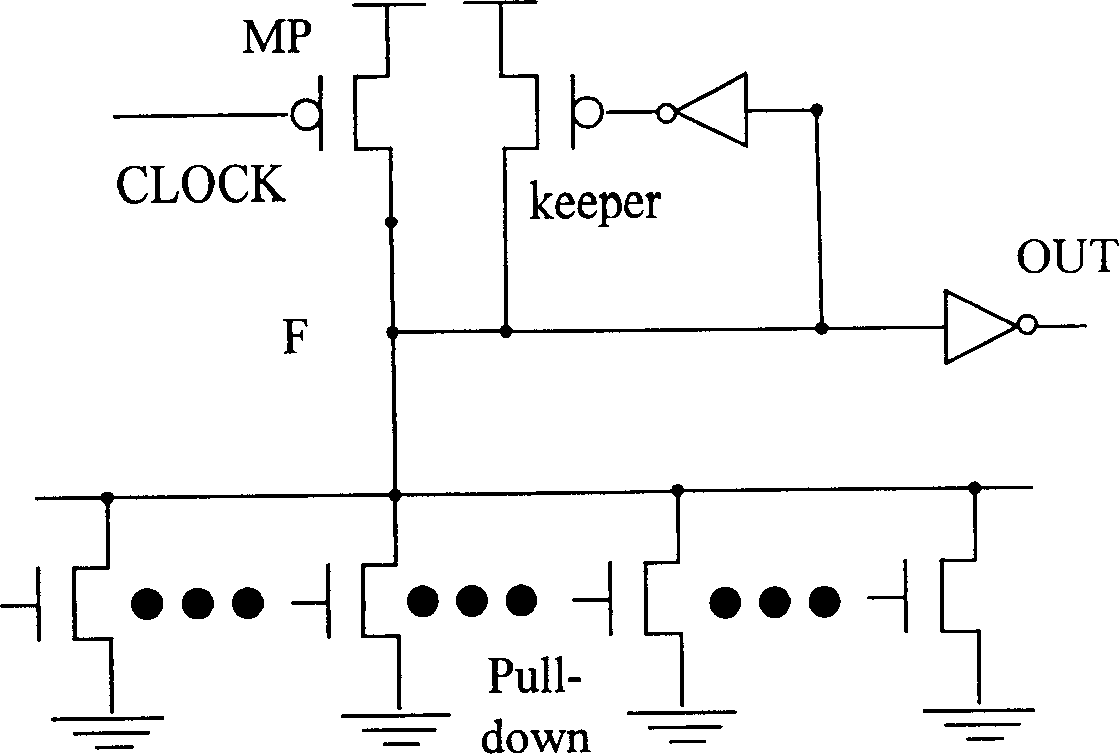

[0024] Image 6 yes Figure 5One of the special cases is a specific circuit structure diagram realized by the structure of a single pull-down network (the pull-down network has only one branch). Wherein G is an external dynamic point, F is an output dynamic point, that is, an internal dynamic point; the narrow pulse generator mainly includes PMOS transistors 1 and 2, NMOS transistor 3 and a delay network 11; and 10 is a pull-down network. Their connection relationship is: the clock is transmitted to the gates of NMOS transistor 3 and PMOS transistor 1 through the delay of delay network 11; PMOS transistors 1 and 2 are connected in series; the drain of PMOS transistor 2 and the drain of NMOS transist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More