Firmware ISP writer and writing method for SPI bus interface

A technology of SPI bus and programming method, which is applied to instruments, electrical digital data processing, program control devices, etc., can solve problems such as low product efficiency, and achieve the effects of improved work efficiency, simple structure, and safety assurance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and through specific implementation methods.

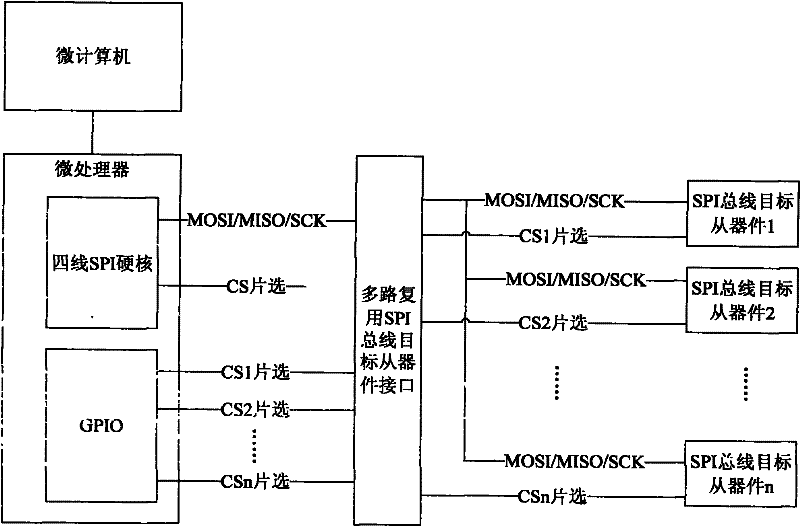

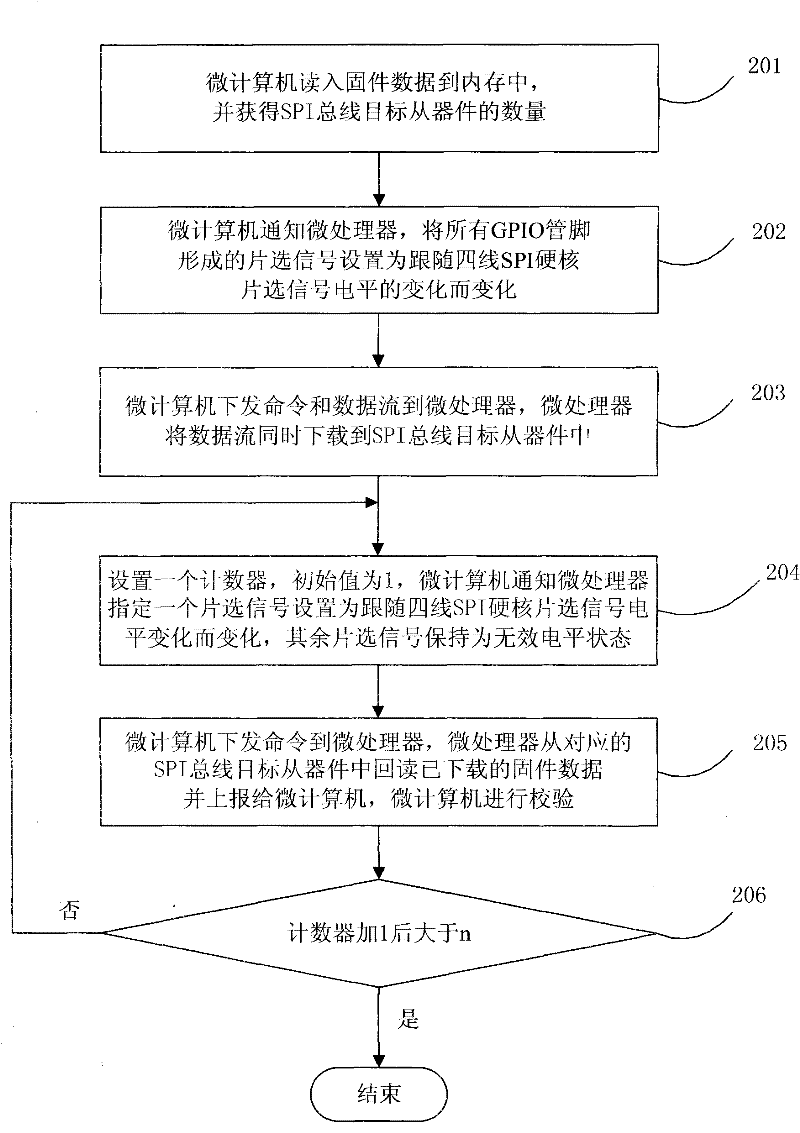

[0027] The main idea of the technical solution of the present invention is based on a rule about FLASH or EEPROM memory chips supporting the multiplexing SPI bus interface of the in-system programming (ISP) function, because four signals (MOSI, MISO, SCK, CS) is unidirectional transmission, so the four-wire SPI bus signal pins (MOSI, MISO, SCK, CS) of a single microprocessor can be fanned out to multiple memory chips on the panel-board in parallel. Four-wire SPI bus signal (MOSI, MISO, SCK, CS), when the microprocessor initiates a firmware download operation for a single chip, the firmware of these multiple chips connected in parallel is actually downloaded, which is simultaneous download. The SPI bus target slave device that it can support, that is, the maximum number of memory chips, is determin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More