Patents

Literature

68 results about "Synchronous serial communication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

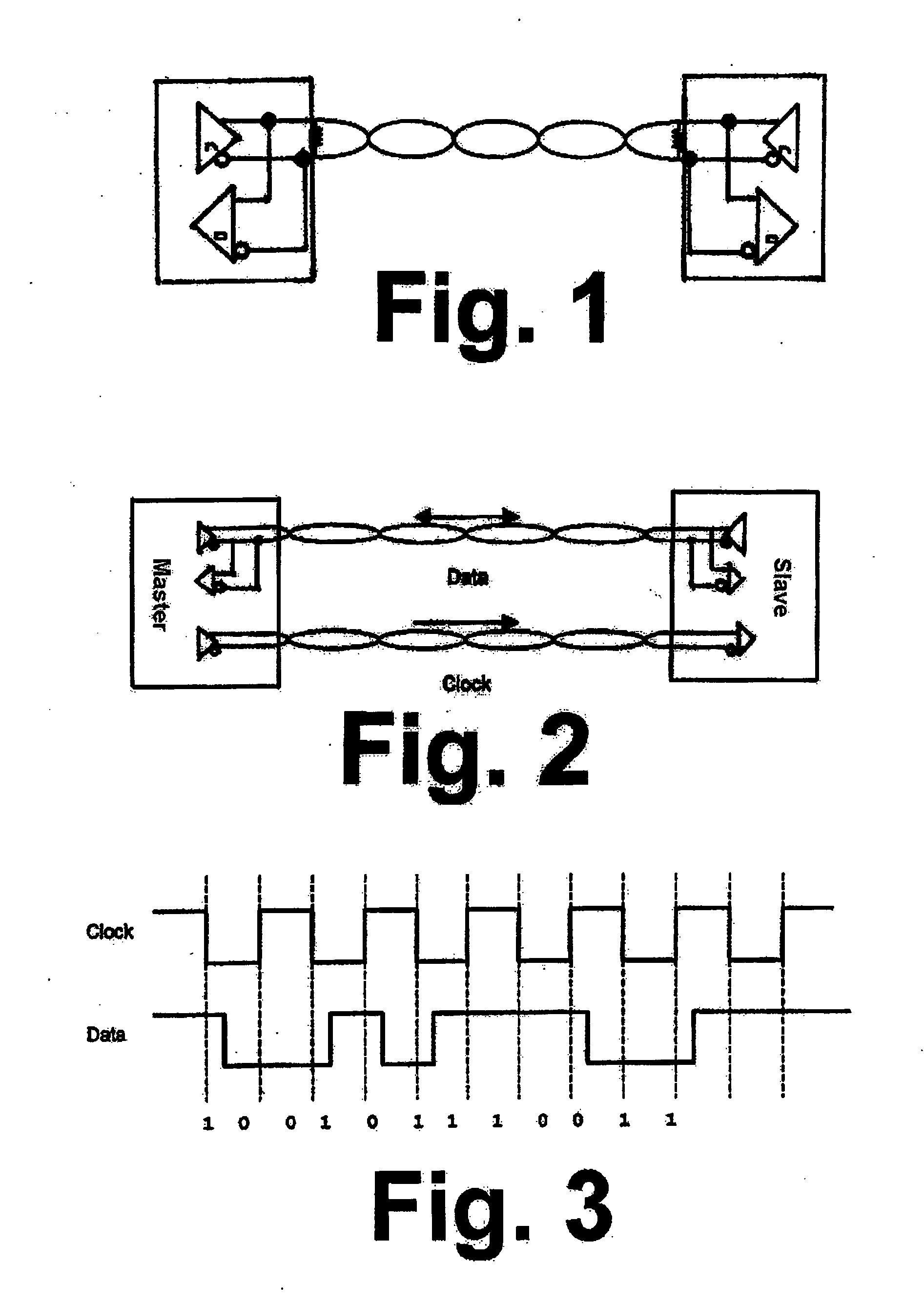

Synchronous serial communication describes a serial communication protocol in which "data is sent in a continuous stream at constant rate." Synchronous communication requires that the clocks in the transmitting and receiving devices are synchronized – running at the same rate – so the receiver can sample the signal at the same time intervals used by the transmitter. No start or stop bits are required. For this reason "synchronous communication permits more information to be passed over a circuit per unit time" than asynchronous serial communication. Over time the transmitting and receiving clocks will tend to drift apart, requiring resynchronization.

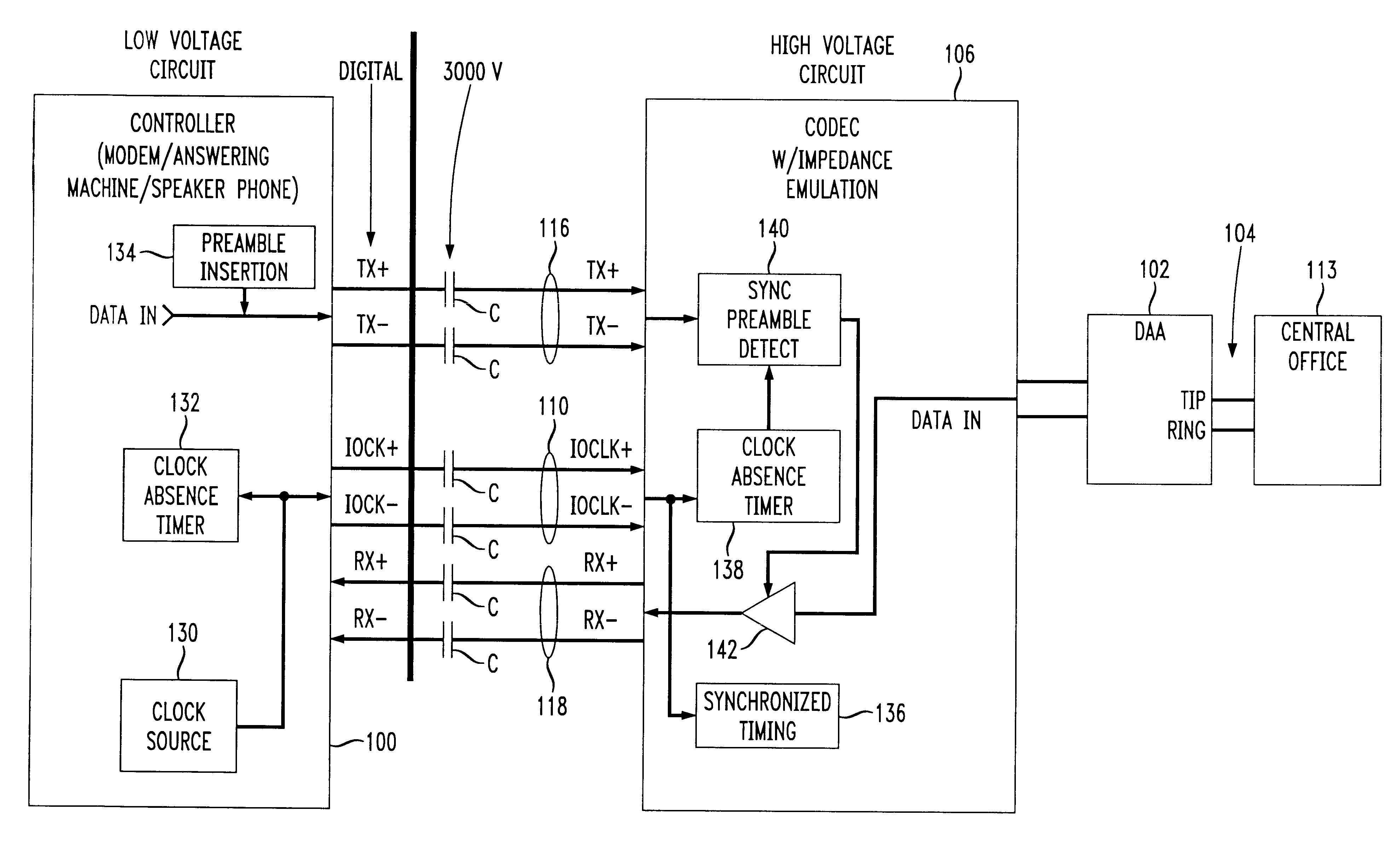

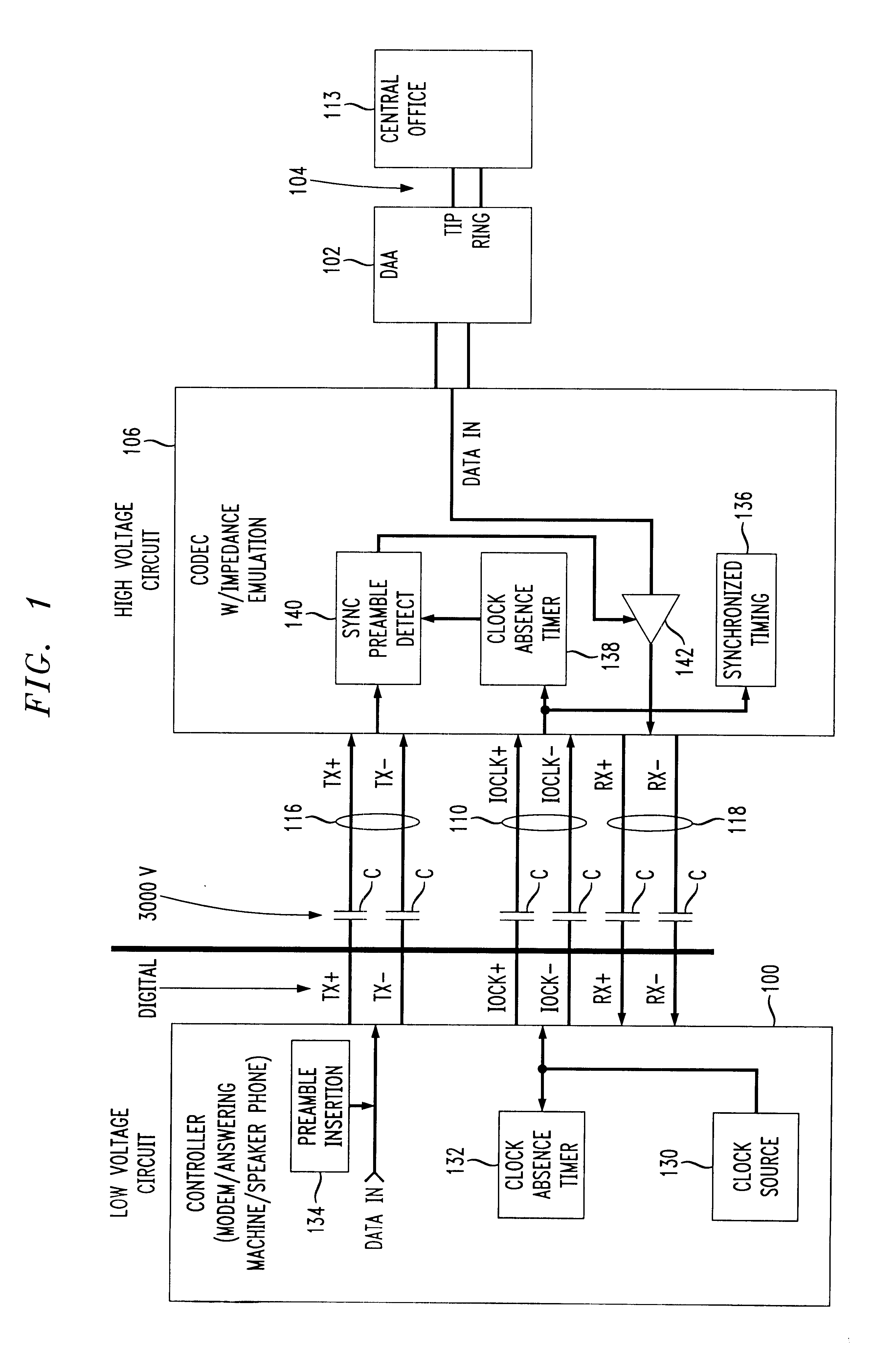

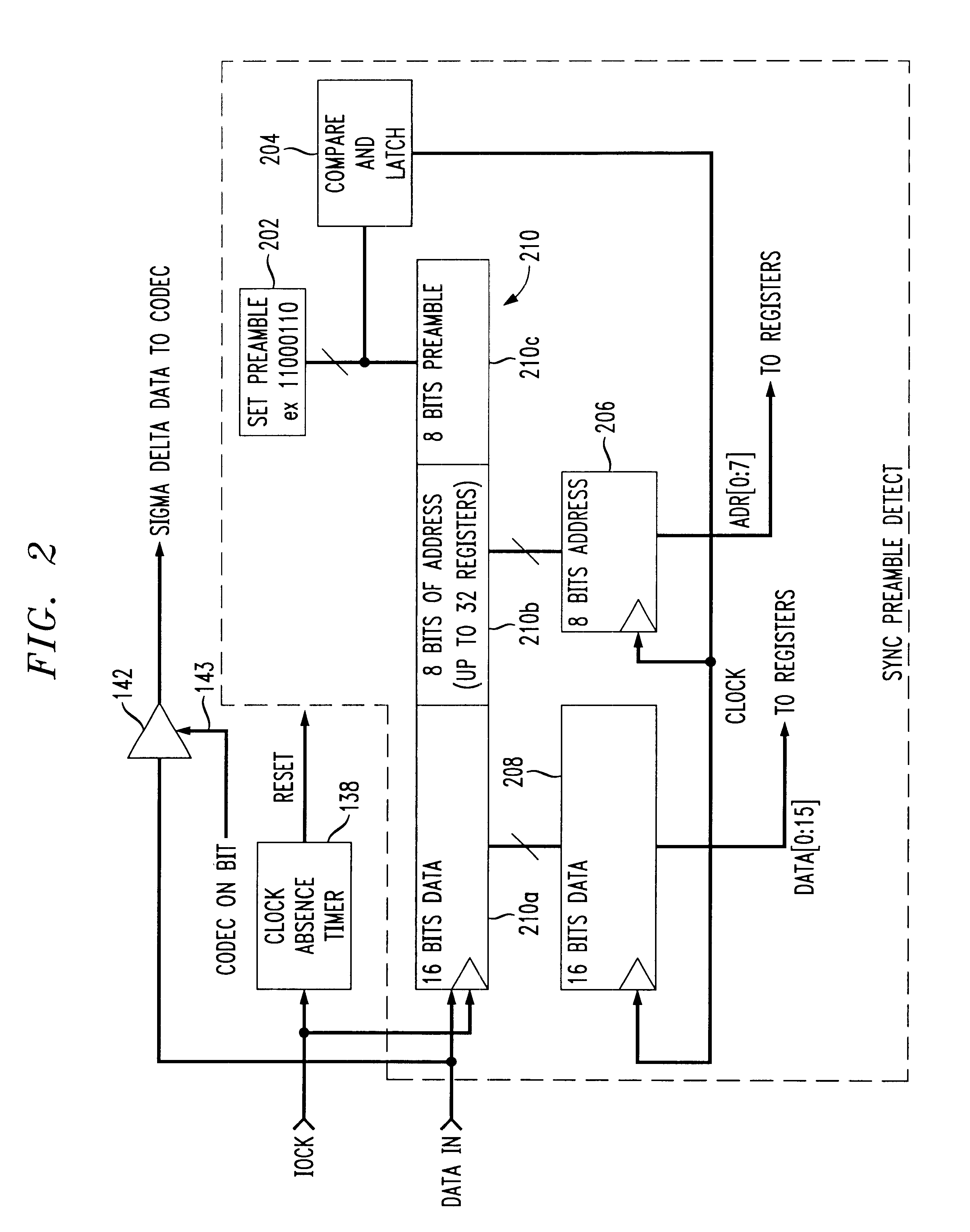

Synchronizing data transfer protocol across high voltage interface

InactiveUS6404780B1Time-division multiplexSynchronisation signal speed/phase controlTransmission protocolData stream

The present invention provides a synchronizing data protocol comprising one or more serial input-output (SIO) control word(s) and data passed across a high voltage interface, to allow the elimination of a frame synchronization signal (and corresponding AC coupling capacitors). The present invention has particular applicability to, e.g., time division multiplexed (TDM) data, serial data communication devices, or synchronous serial communication interfaces in general, and to the communication between a controller and a codec in an audio codec device in accordance with the AC '97 Specification, i.e., the AC Link. The synchronizing data protocol is implemented over a transmit data signal line to provide occasional synchronization (i.e., not frame-by-frame synchronization) between the two communicating devices. The master device includes a preamble insertion module to insert a predetermined preamble code word into the transmitted data stream. An interrupt is sent to the slave device by withholding the data clock signal for a predetermined amount of time. Upon receipt of the interrupt, the slave device monitors the data stream for the presence of the preamble code word. Upon detection of the preamble code word, data transmitted by the codec is again enabled.

Owner:LUCENT TECH INC

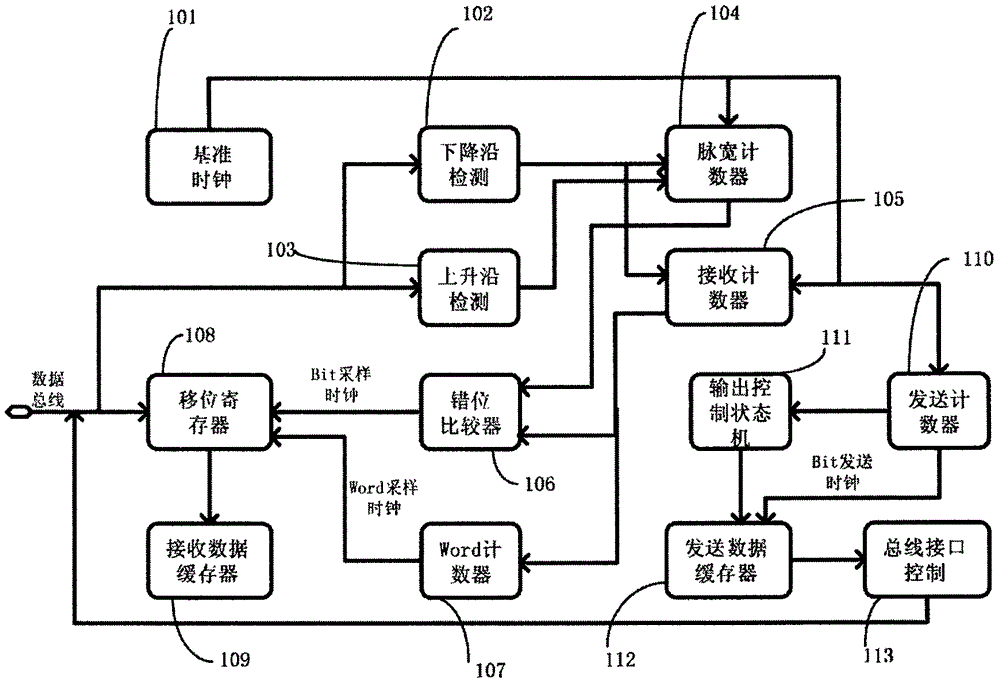

Single-bus asynchronous serial port communication system and communication method thereof

ActiveCN106528478AReduce complexityAccurate automatic detectionElectric digital data processingCommunication interfaceAsynchronous serial communication

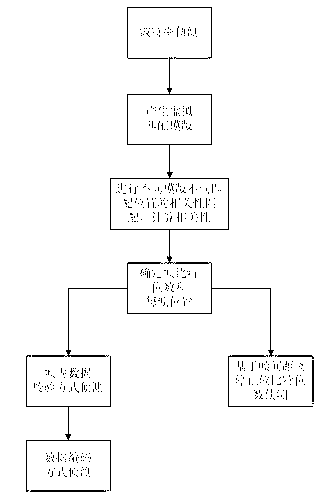

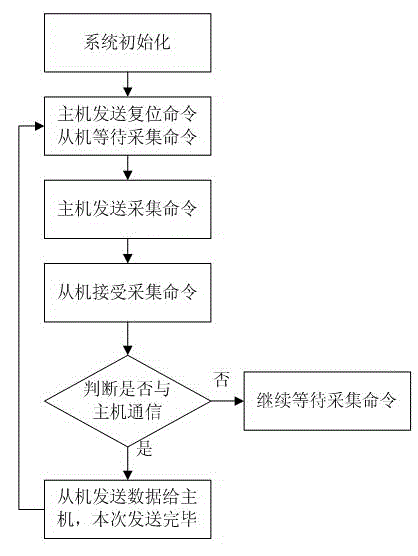

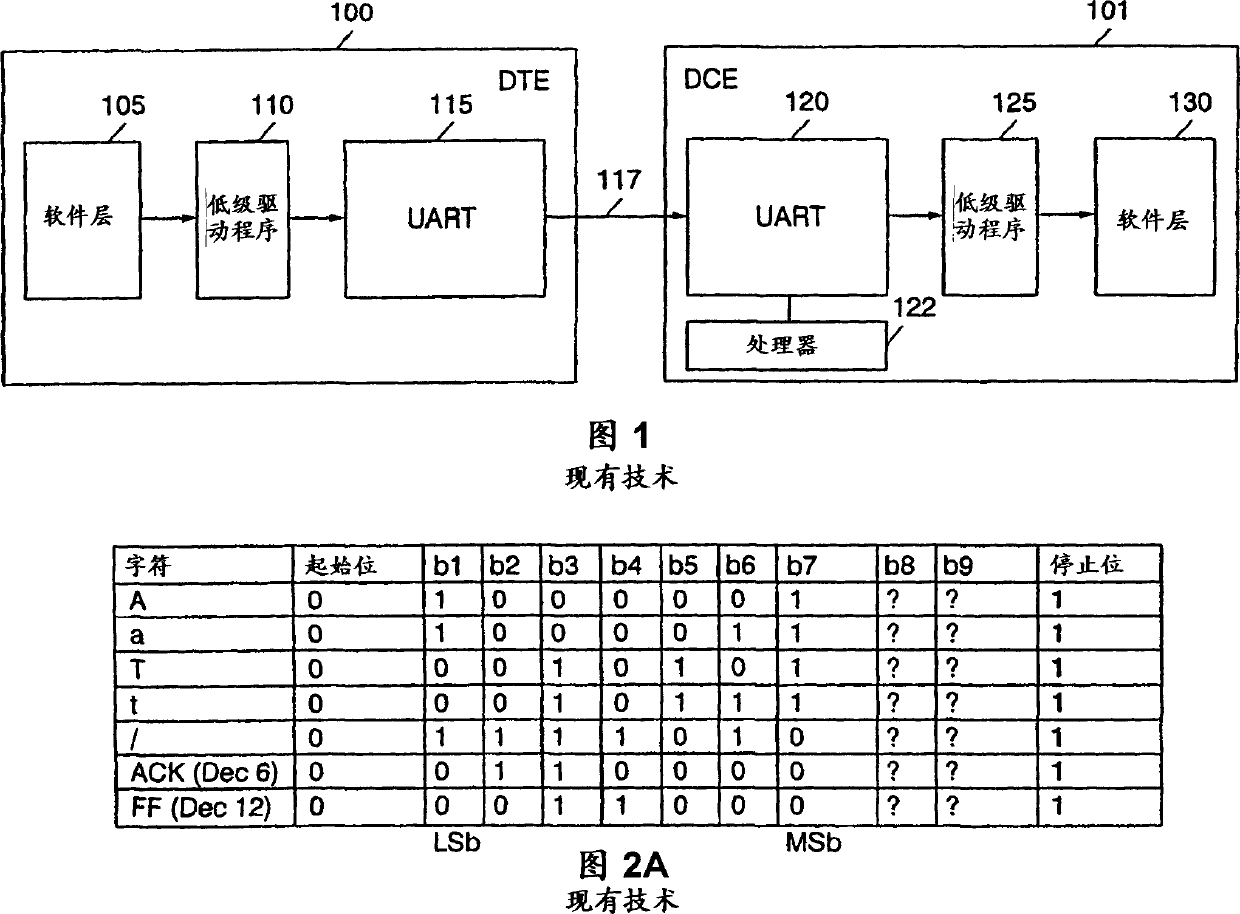

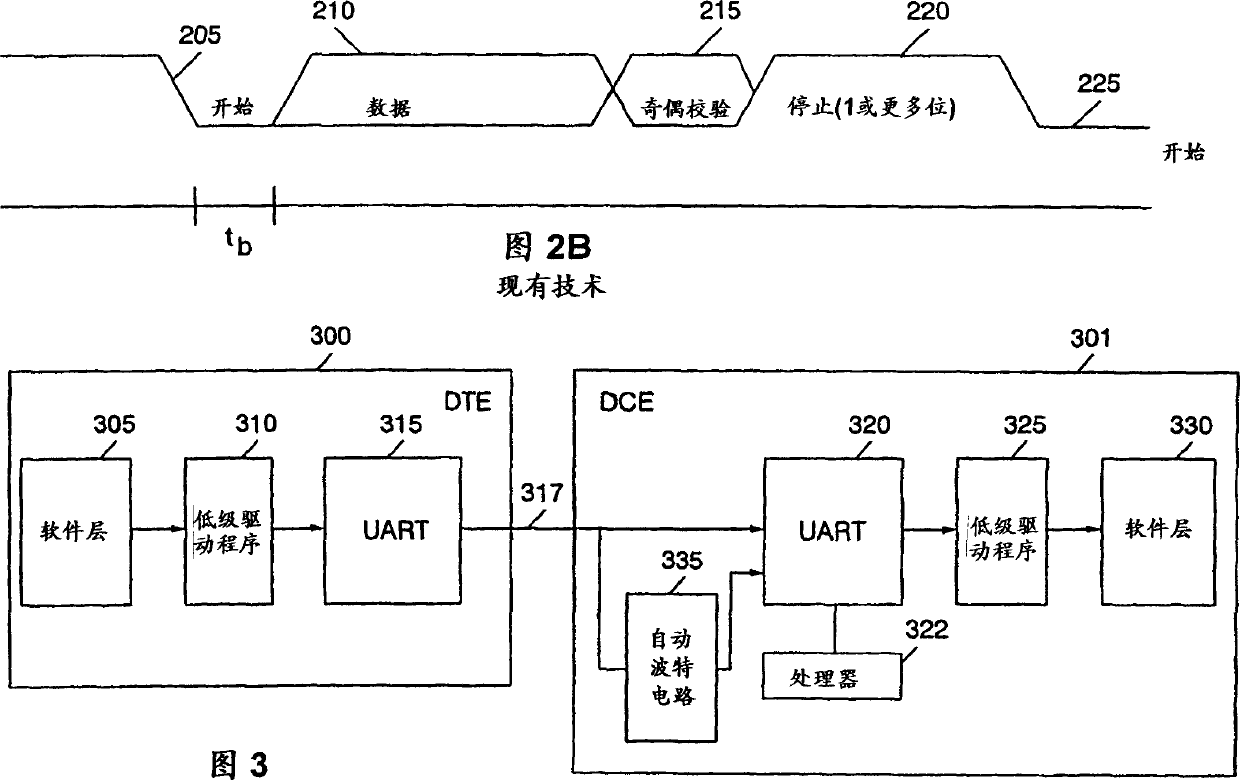

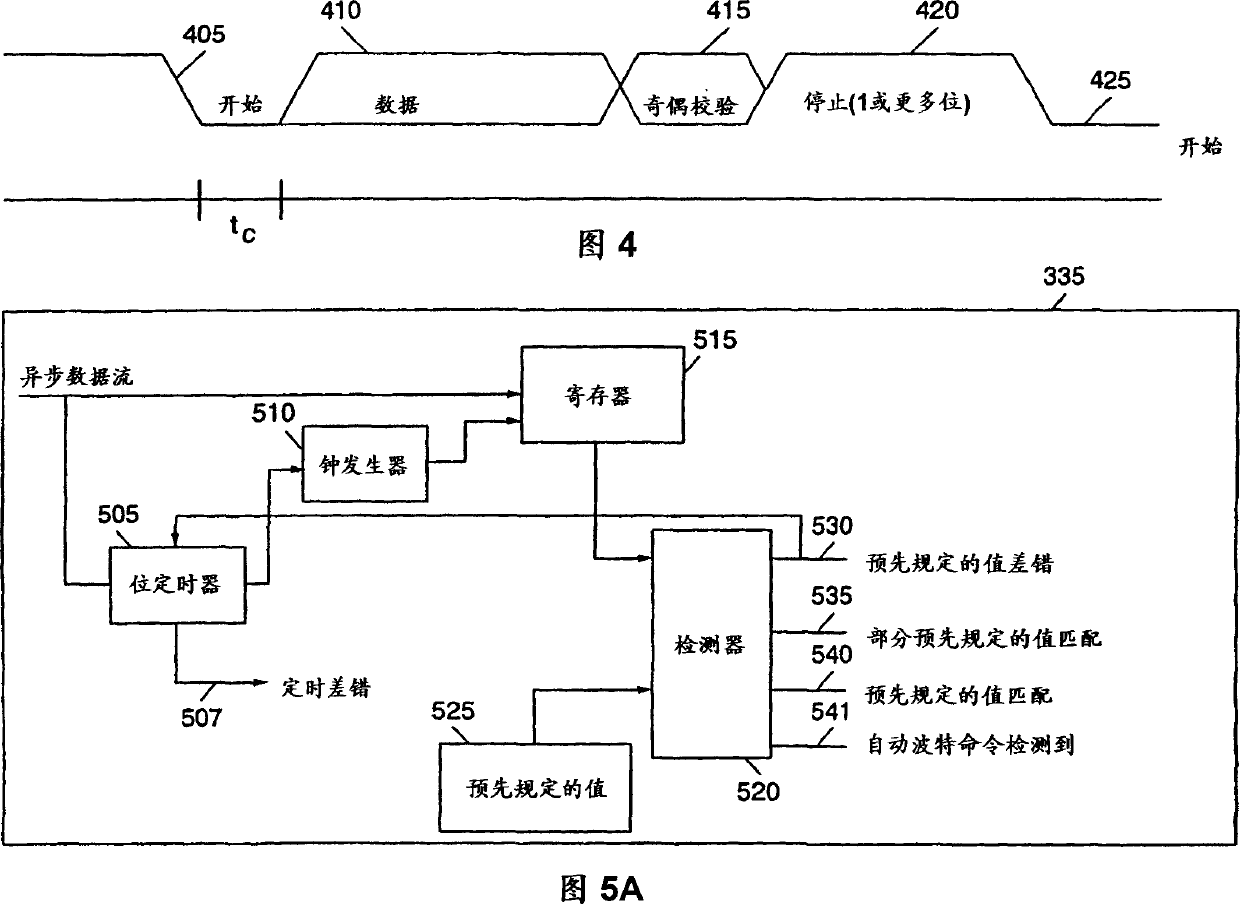

The invention discloses a single-bus asynchronous serial port communication system and a communication method thereof. The single-bus asynchronous serial port communication system comprises master equipment and slave equipment, wherein the master equipment is connected with the slave equipment through a data bus; and a serial port communication interface circuit is arranged in the slave equipment, and the slave equipment realizes Baud rate detection and adjustment of the master equipment, receives a control command and data of the master equipment and returns corresponding response data. The single-bus asynchronous serial port communication system transmits data through a single bus, and automatic Baud rate detection is realized by adopting a bit width counting and comparing technology; namely, the slave equipment can transmit data to the master equipment only via one data bus, so that the complexity of a communication interface is greatly reduced; by the adoption of the special bit width counting and comparing technology, the communication Baud rate can be automatically detected quickly and accurately through the automatic Baud rate detection; and the number of adopted integrated circuit transistors is small, and the chip cost is reduced.

Owner:北京中科银河芯科技有限公司

Method for automatically detecting asynchronous serial port communication protocol on basis of level sampling

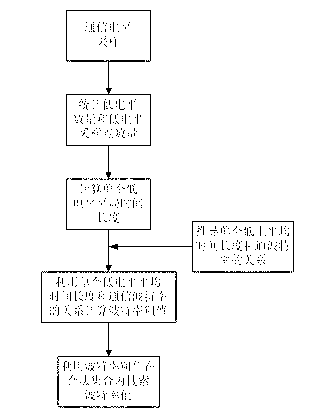

The invention belongs to the technical field of digital communication, and particularly relates to a method for automatically detecting asynchronous serial port communication protocol on the basis of level sampling. The method includes firstly sampling level signals of asynchronous serial port communication, and detecting asynchronous serial port communication Baud rate according to the relation of the asynchronous serial port communication Baud rate and average time span of a single low level of the sampled signals; secondly, determining data frame bit digits and data frame positions of target signals which are the detected level signals by Baud rate by means of stop bit correlation matching algorithm; thirdly, analyzing in-frame data and inter-frame bit distance to determine data bit digits, checking manners and stop bit digits of the target signals; and finally determining a data coding manner of the target signals by Bayes policy method on the basis of the minimum error rate. The method can be applicable to communication protocol detection of communication and data transmission equipment utilizing the asynchronous serial port communication protocol.

Owner:NAVAL UNIV OF ENG PLA

One-master multi-slave high-speed synchronous serial communication data transmission method

InactiveCN104954096AMeet the requirements of high-speed data transmissionSimple structureForward error control useDecoding methodsData transmission

Provided is a one-master multi-slave high-speed synchronous serial communication data transmission method, which is suitable for the field of master-slave multi-channel high-speed transmission. Data to be transmitted and a communication clock are modulated to one signal line in a coding manner and the data are transmitted by the one-master multi-slave mode, thereby simplifying the system communication structure, reducing the number of communication lines and the communication cost and increasing the transmission speed. In addition, an excellent serial synchronous clock is obtained by the decoding method, thereby reducing the bit error rate of transmission.

Owner:HENAN UNIV OF SCI & TECH

Data rate calibration for asynchronous serial communications

InactiveUS6944248B2Reduce cost and complexityEliminate needData rate detection arrangementsTransmission monitoringLeading edgeAsynchronous serial communication

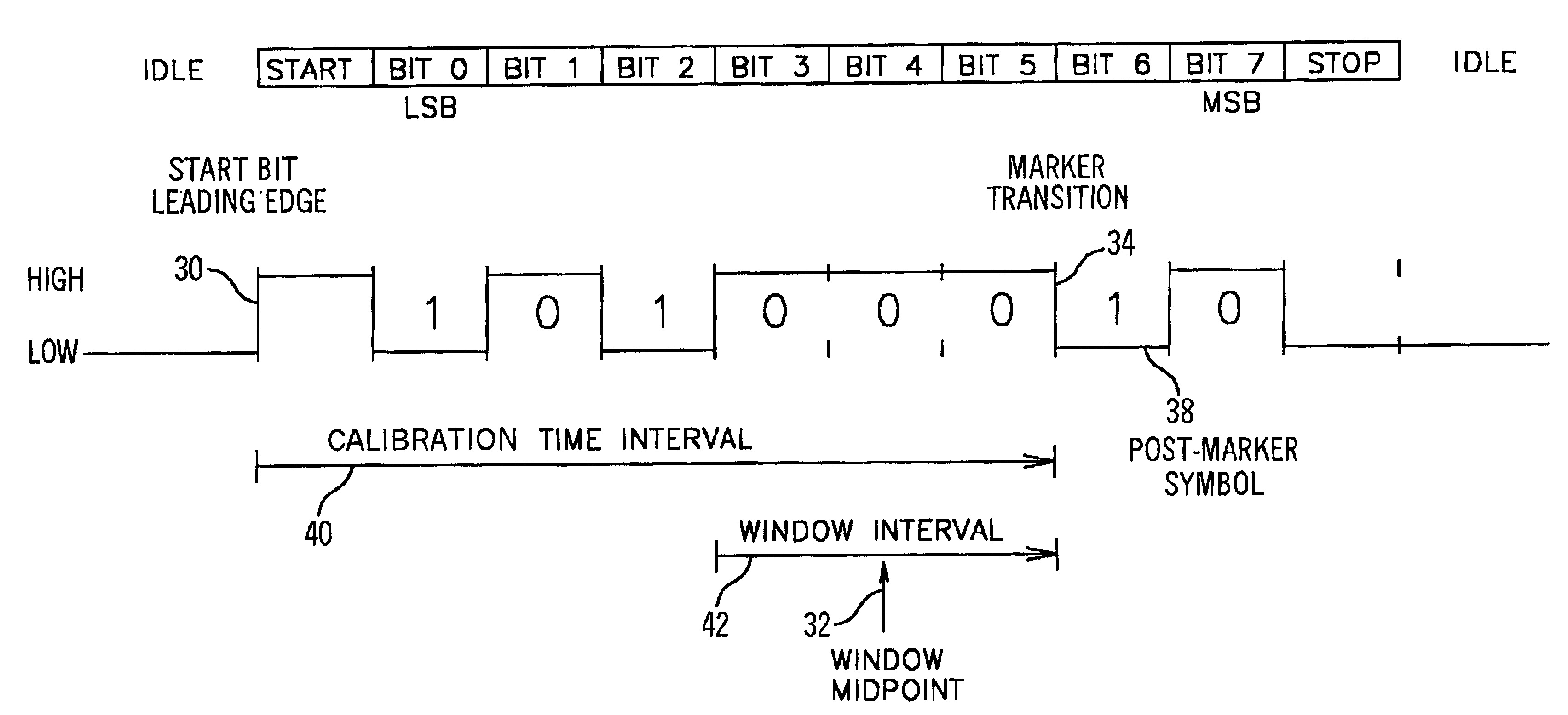

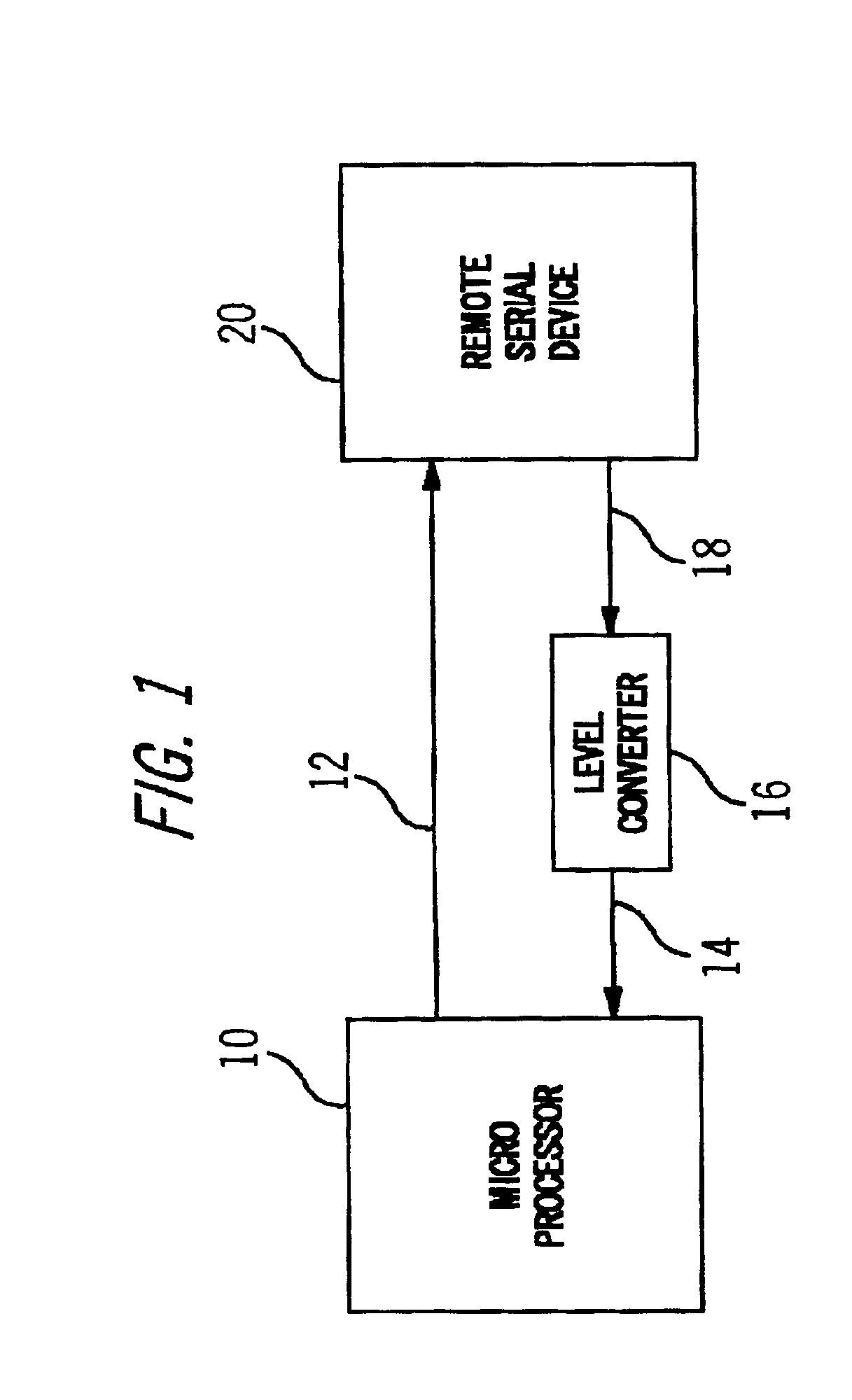

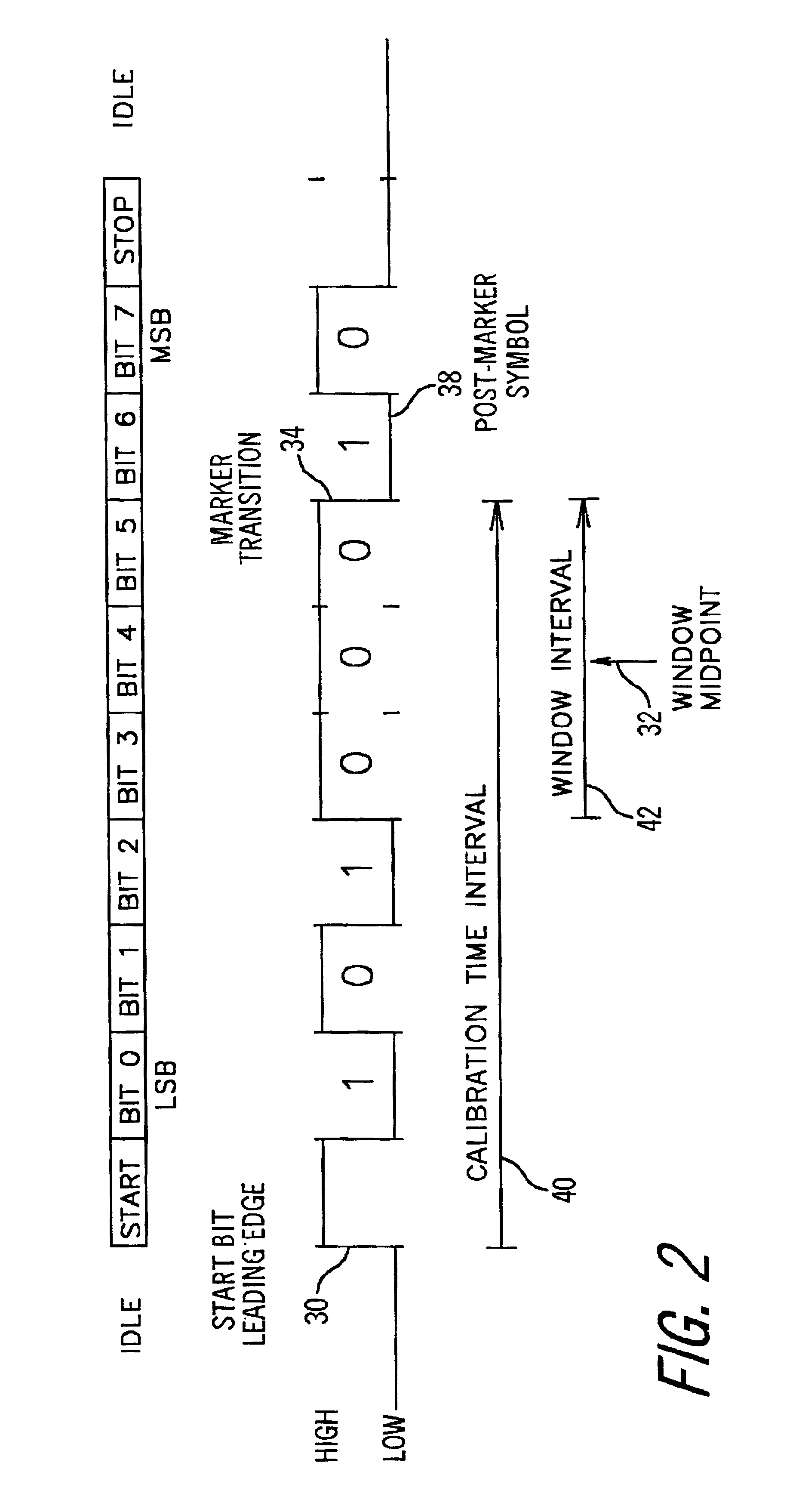

A method and apparatus for determining the appropriate timing interval for each bit or data symbol in serial data communications. A sending device transmits a predetermined bit sequence, such as a binary pattern corresponding to one byte, either on its own initiative or in response to an action of a receiving device. A microprocessor in the receiving device measures a calibration time interval between the leading edge of a start bit and a subsequent marker transition, either between subsequent data bits or between the final data bit and the stop bit. This measured interval may be mathematically converted to units useful to calibrate a function or device that conducts input / output operations. Optionally, the process may be repeated periodically to compensate for clock rate drift. This invention may be used for autobaud data rate detection, or matching the actual data rate of a remote serial device, and permits accurate communications without precision timing references.

Owner:BLUEBROOK ASSOCS

Automatic speed detection for asynchronous serial communications

InactiveCN1293852AReduce waiting timeImprove processing efficiencyData rate detection arrangementsElectric digital data processingAsynchronous serial communicationData stream

The speed of asynchronous serial communications is detected by determining a duration of a data bit within an asynchronous data stream. The duration of the data bit is used to generate a clock frequency. The clock frequency is used to clock data from the asynchronous data stream into a register. The clocked data is processed according to an error indication.

Owner:TELEFON AB LM ERICSSON (PUBL)

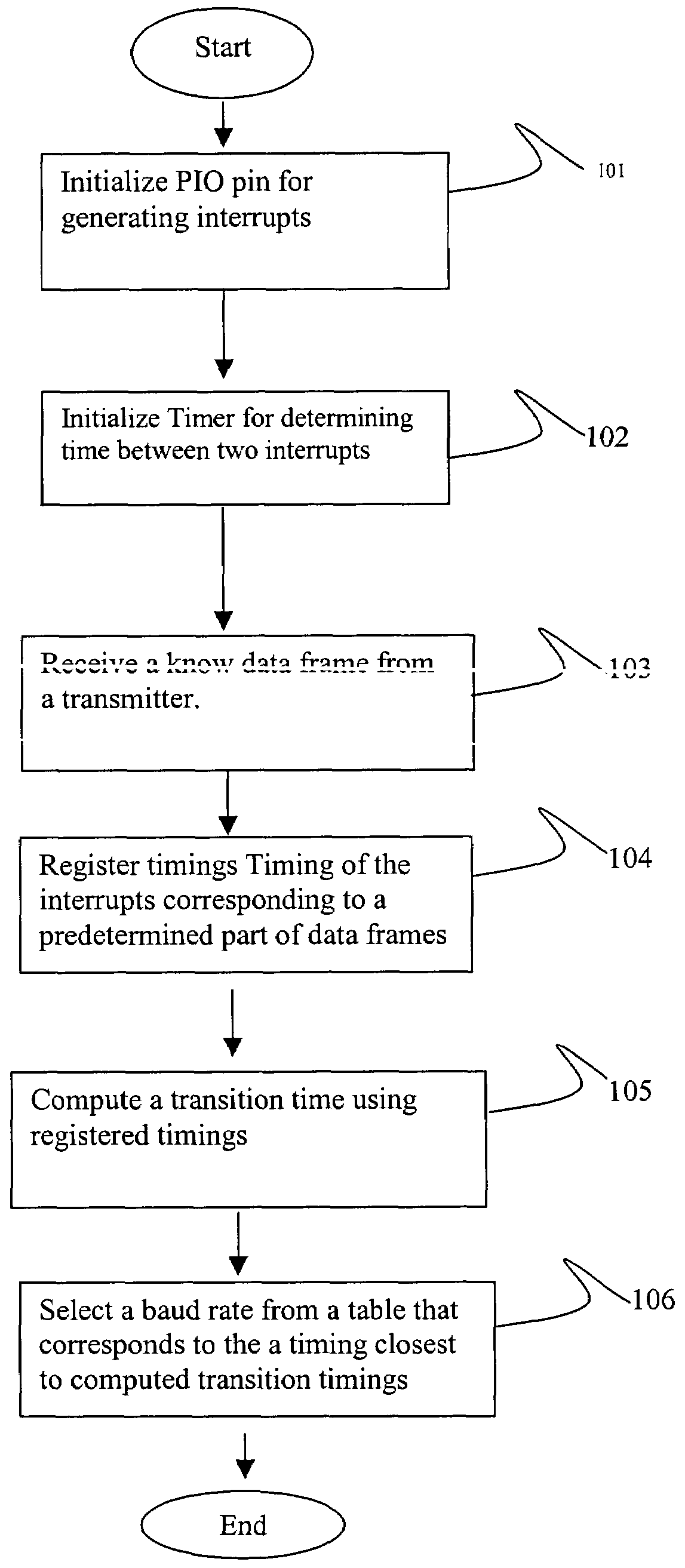

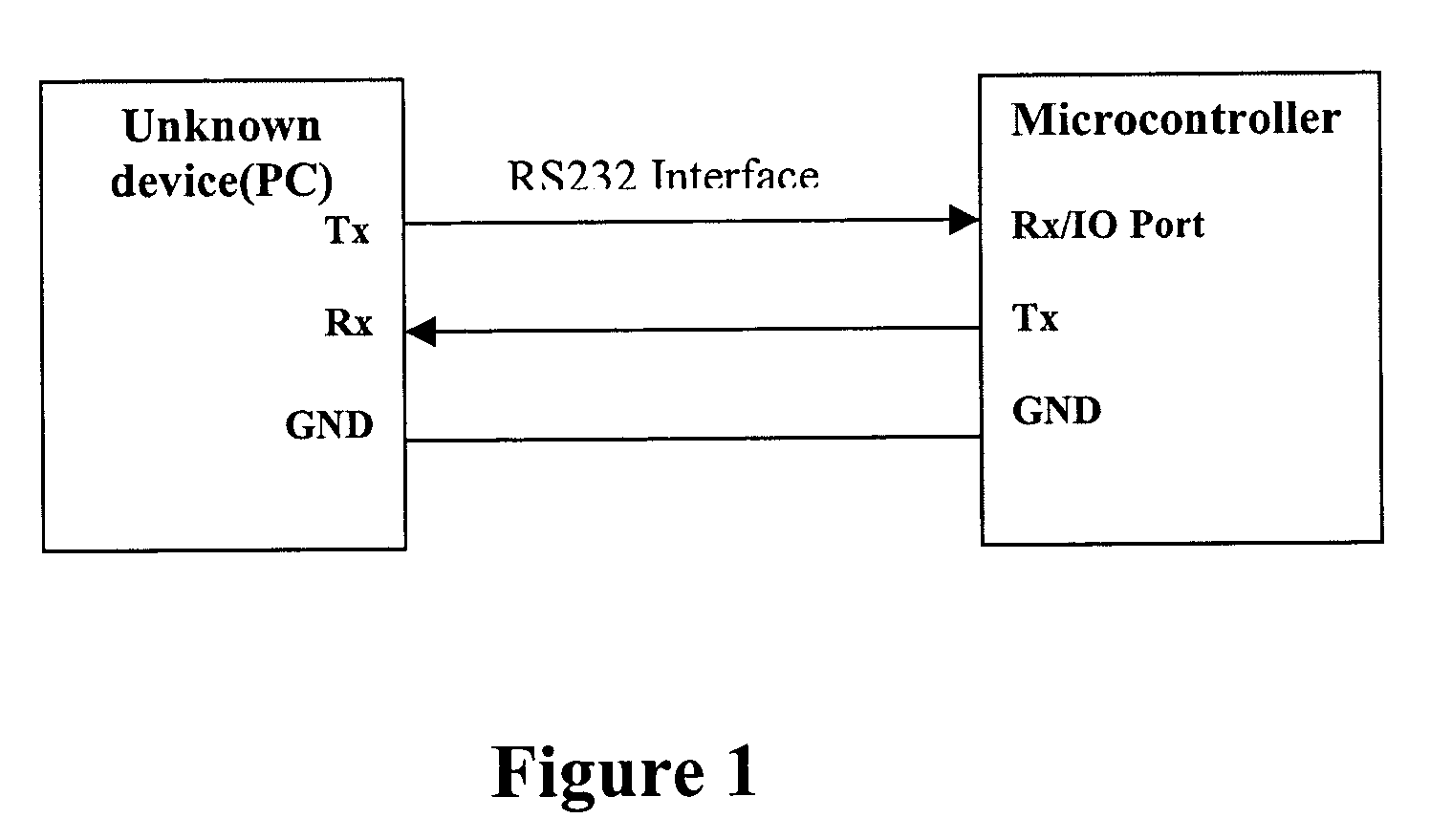

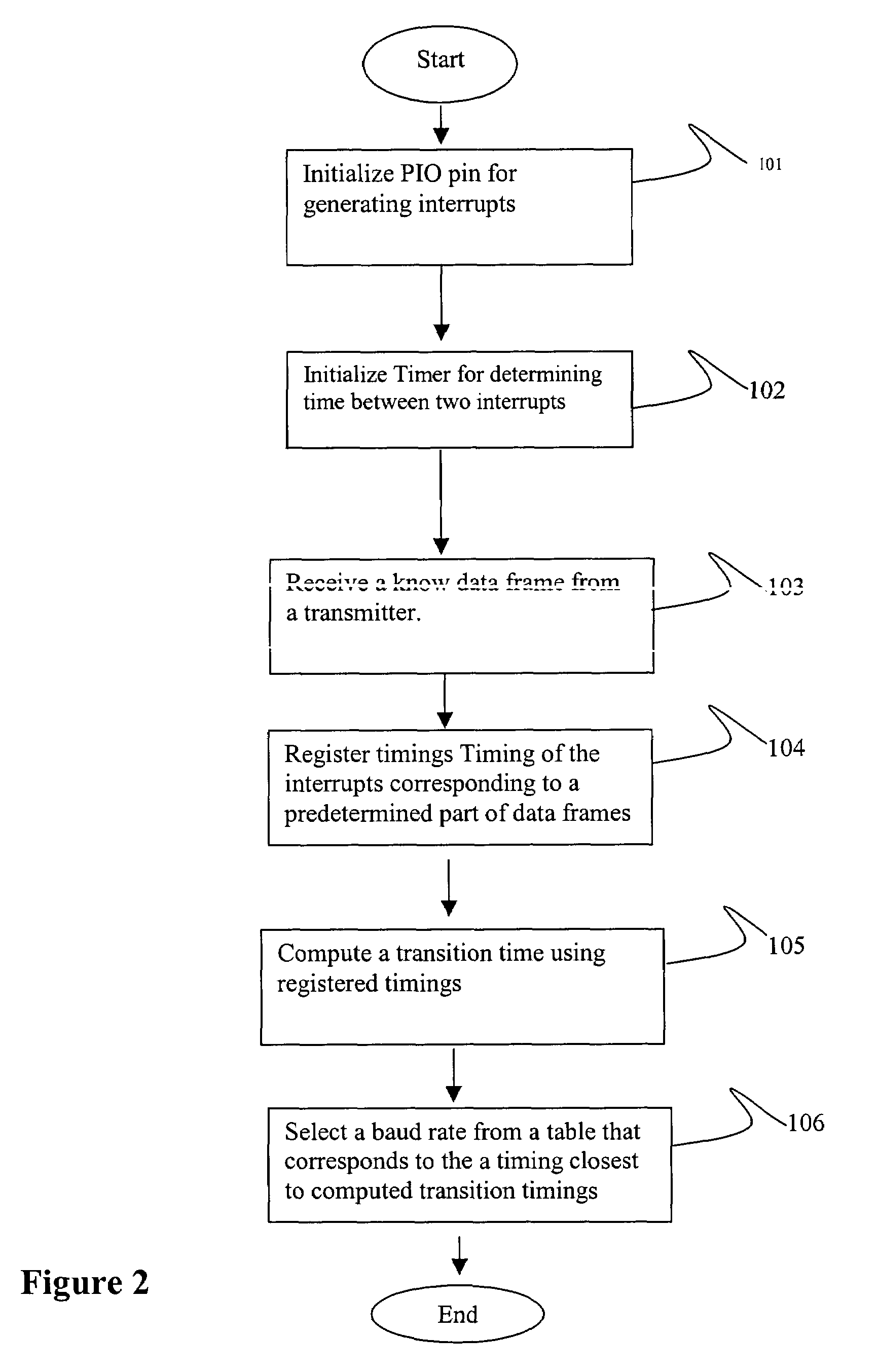

System and method for auto baud rate detection in asynchronous serial communication

ActiveUS7333536B2Accurately determinedImprove accuracyData rate detection arrangementsTransmission monitoringMicrocontrollerAsynchronous serial communication

A microcontroller with embedded software for automatically detecting a baud rate of an asynchronous serial bit stream during an initial set up phase of a microcontroller. The microcontroller is configured to receive a data set from a transmitter and includes a transition detector for identifying bit transitions in the data set. The microcontroller includes a timer triggered by the transition detector that is measures the time interval between two predefined bit transitions, a storage element for registering the measured time interval, and a look up table that provides defines baud rates relative to various time intervals that can be accessed to determine a nearest baud rate value corresponding to the registered time interval.

Owner:STMICROELECTRONICS PVT LTD

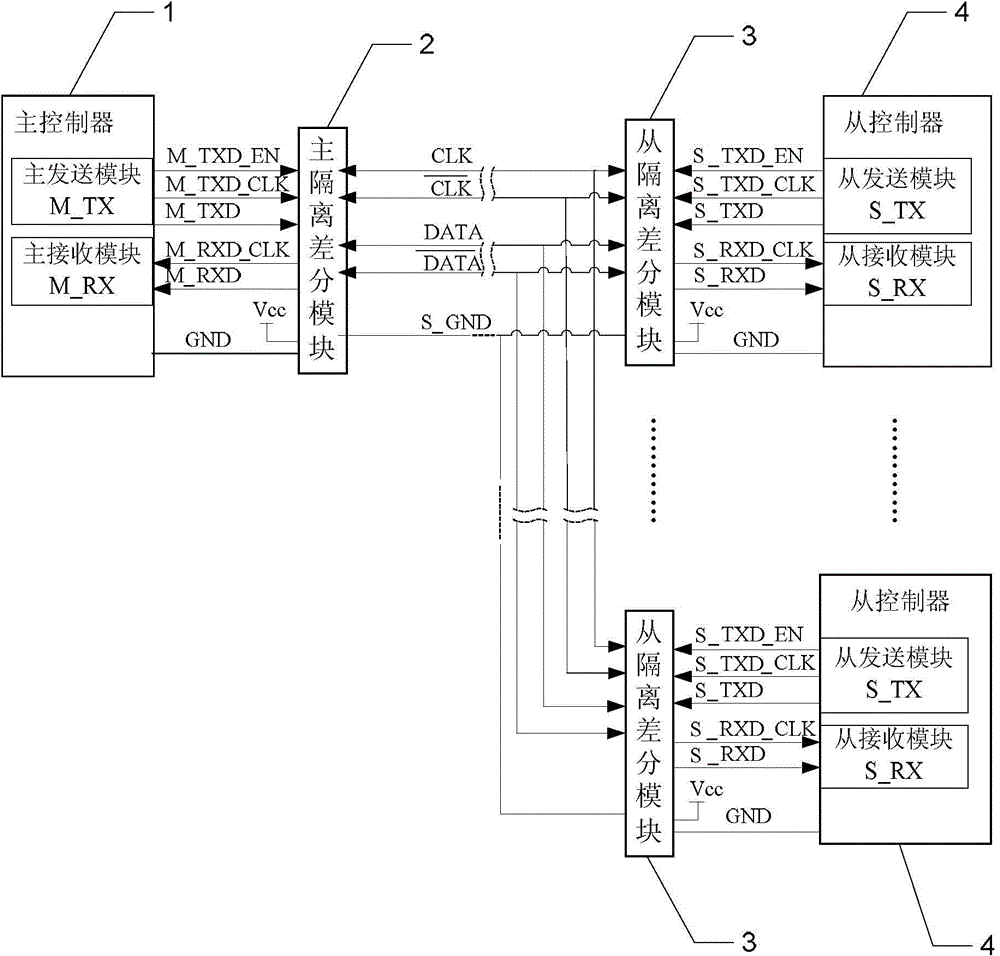

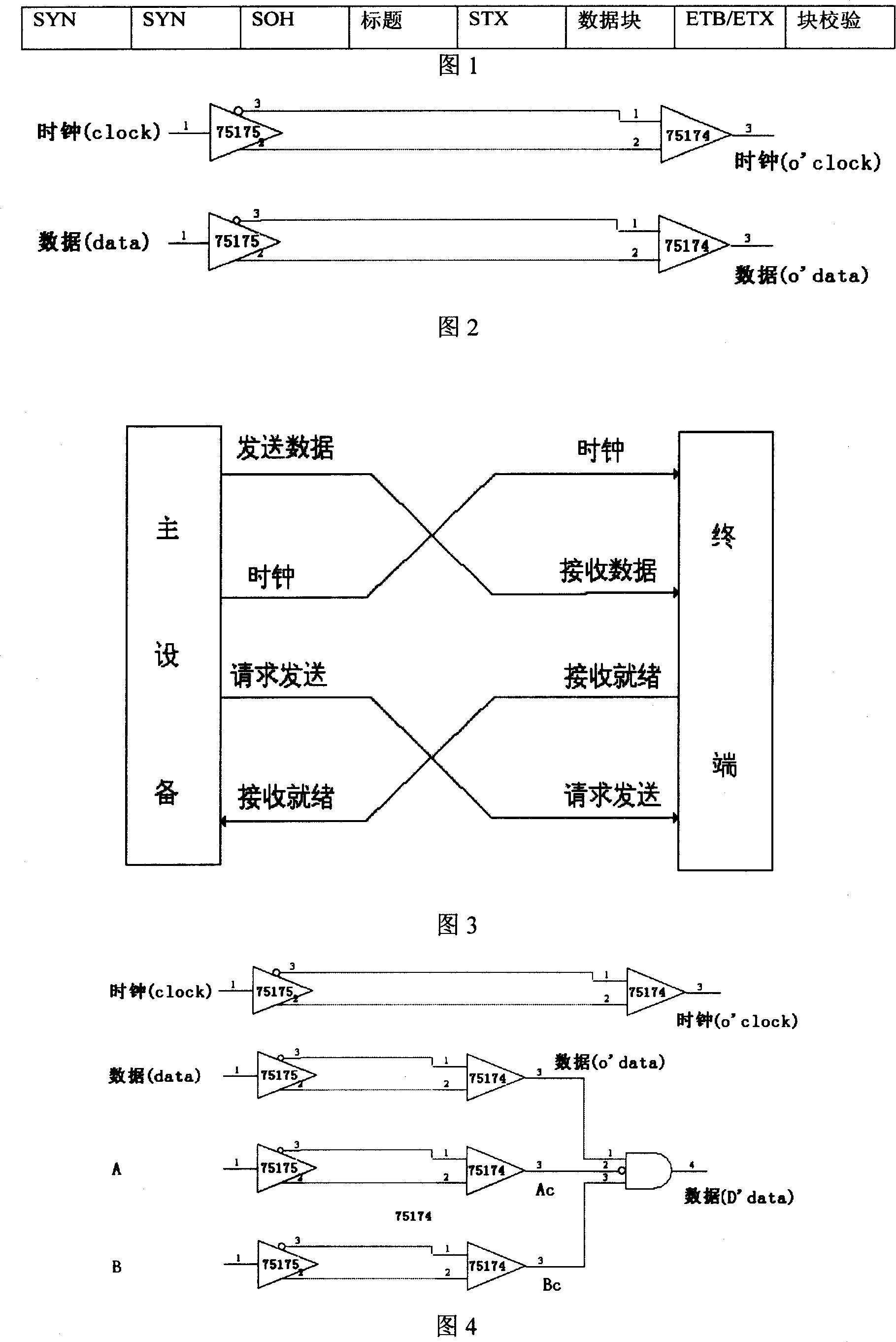

Master-slave synchronous serial communication bus based on differential signal and realization method of master-slave synchronous serial communication bus

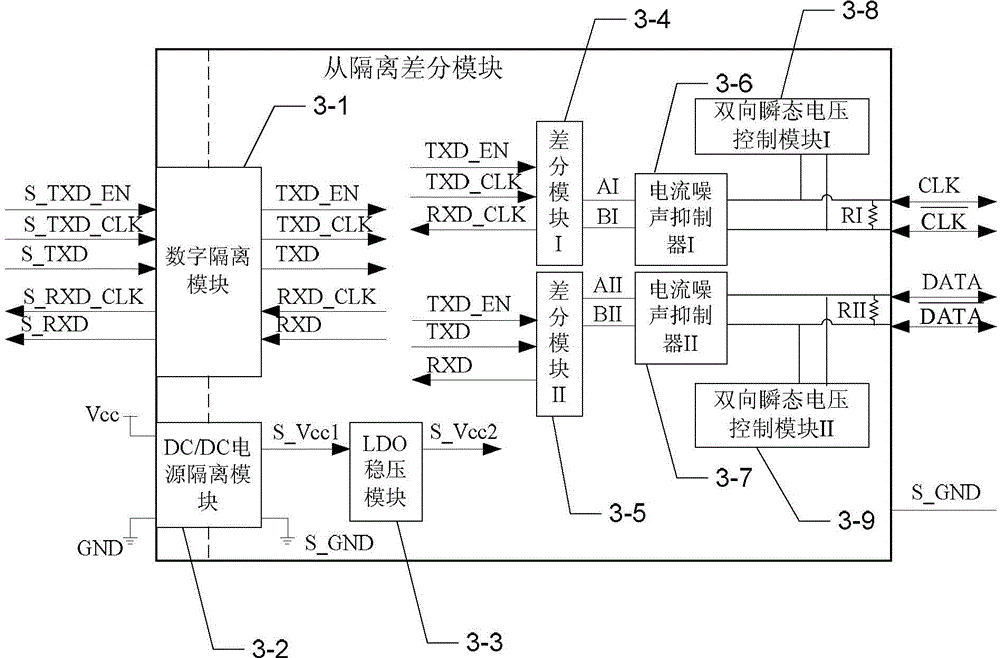

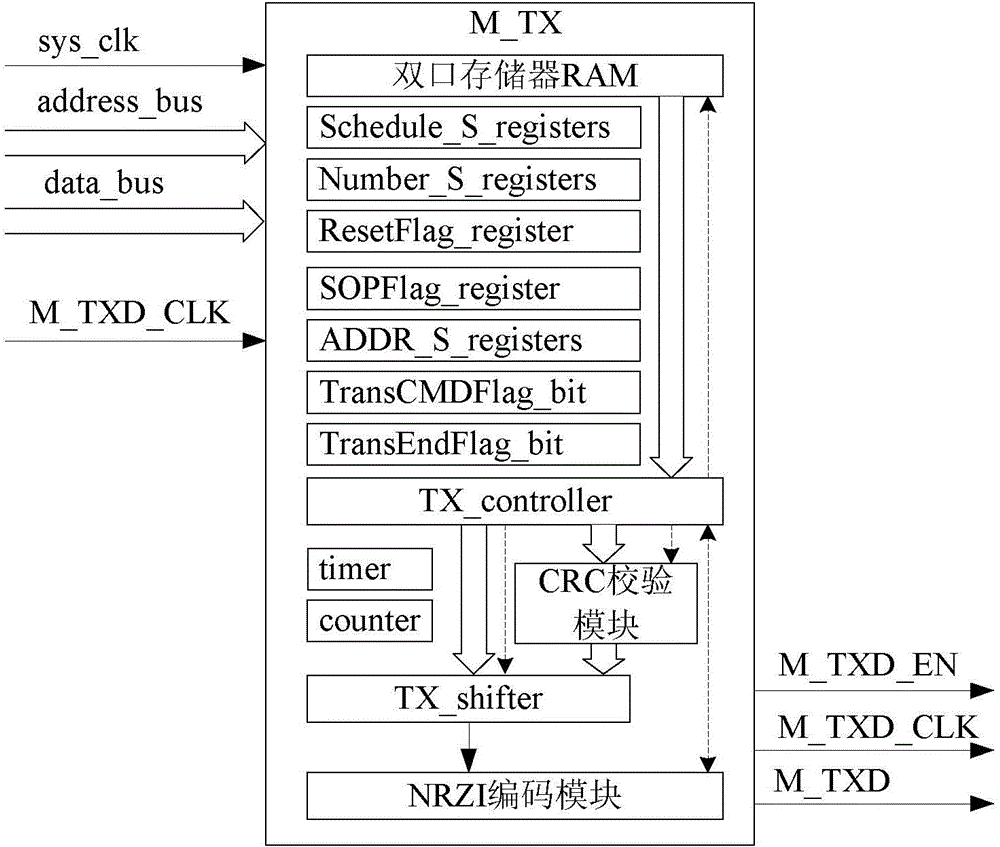

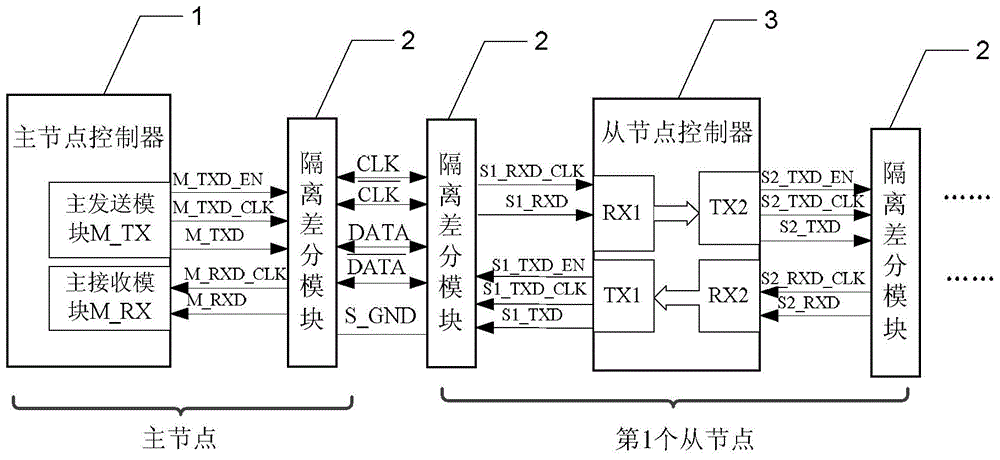

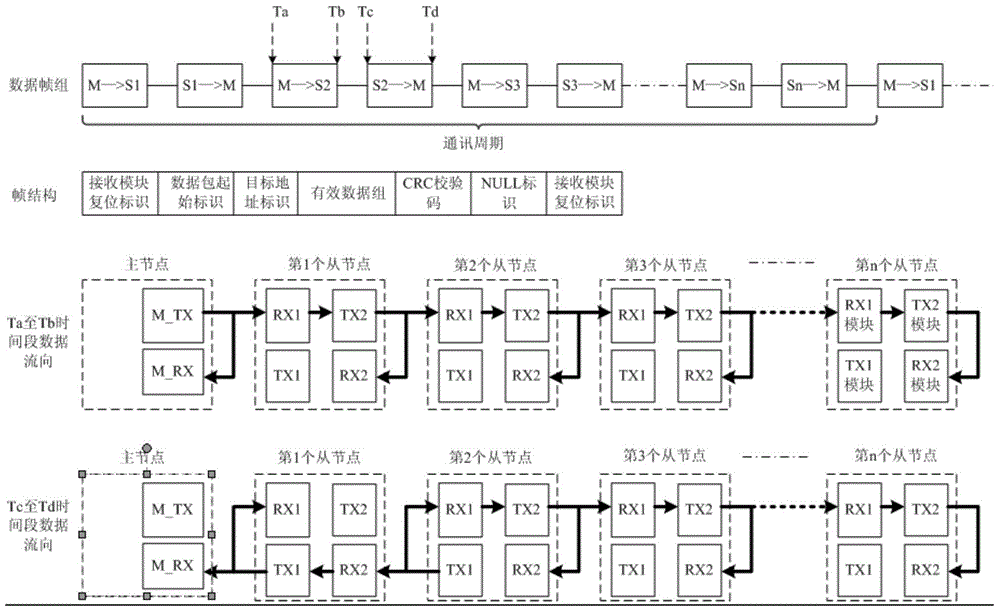

ActiveCN104484306AEliminate latency effectsGuaranteed timing relationshipElectric digital data processingVoltage regulator moduleDifferential signaling

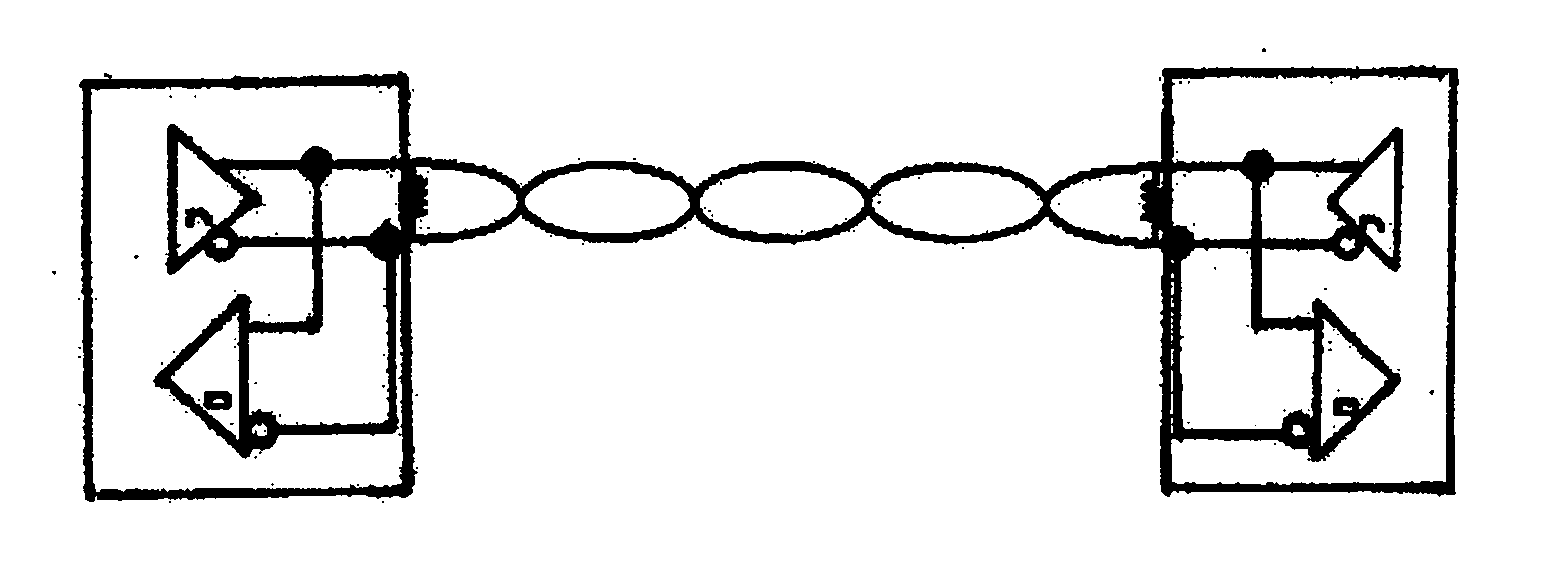

The invention provides a master-slave synchronous serial communication bus based on a differential signal and a realization method of the master-slave synchronous serial communication bus, relates to a master-slave synchronous serial communication bus, and aims at solving the problems that the existing master-slave synchronous serial communication is low in transmission speed, the real-time transmission of massive data cannot be guaranteed, and only the single byte check can be realized through code error detection. A master-slave synchronous serial communication bus based on the differential signal comprises a master controller, a master isolation difference module, n slave isolation difference modules and n slave controllers; the master controller comprises a master transmitting module and a master receiving module; each of the slave controllers comprises a slave transmitting module and a slave receiving module; the slave isolation difference modules are same in structure; each of the slave isolation difference modules comprises a digital isolation module, a DC / DC (Direct Current / Direct Current) power isolation module, an LDO (Low Dropout Regulator) voltage regulator module, two difference modules, two current noise suppressors, two two-way transient voltage control modules and two impedance matching resistors. The master-slave synchronous serial communication bus and the realization method of the master-slave synchronous serial communication bus are mainly used for master-slave synchronous serial communication.

Owner:HARBIN INST OF TECH

Master-slave synchronous serial communication bus based on node cascading and implementation method thereof

ActiveCN104461985AImprove communication distanceImprove anti-interference abilityElectric digital data processingSynchronous serial communicationEmbedded system

Owner:HARBIN INST OF TECH

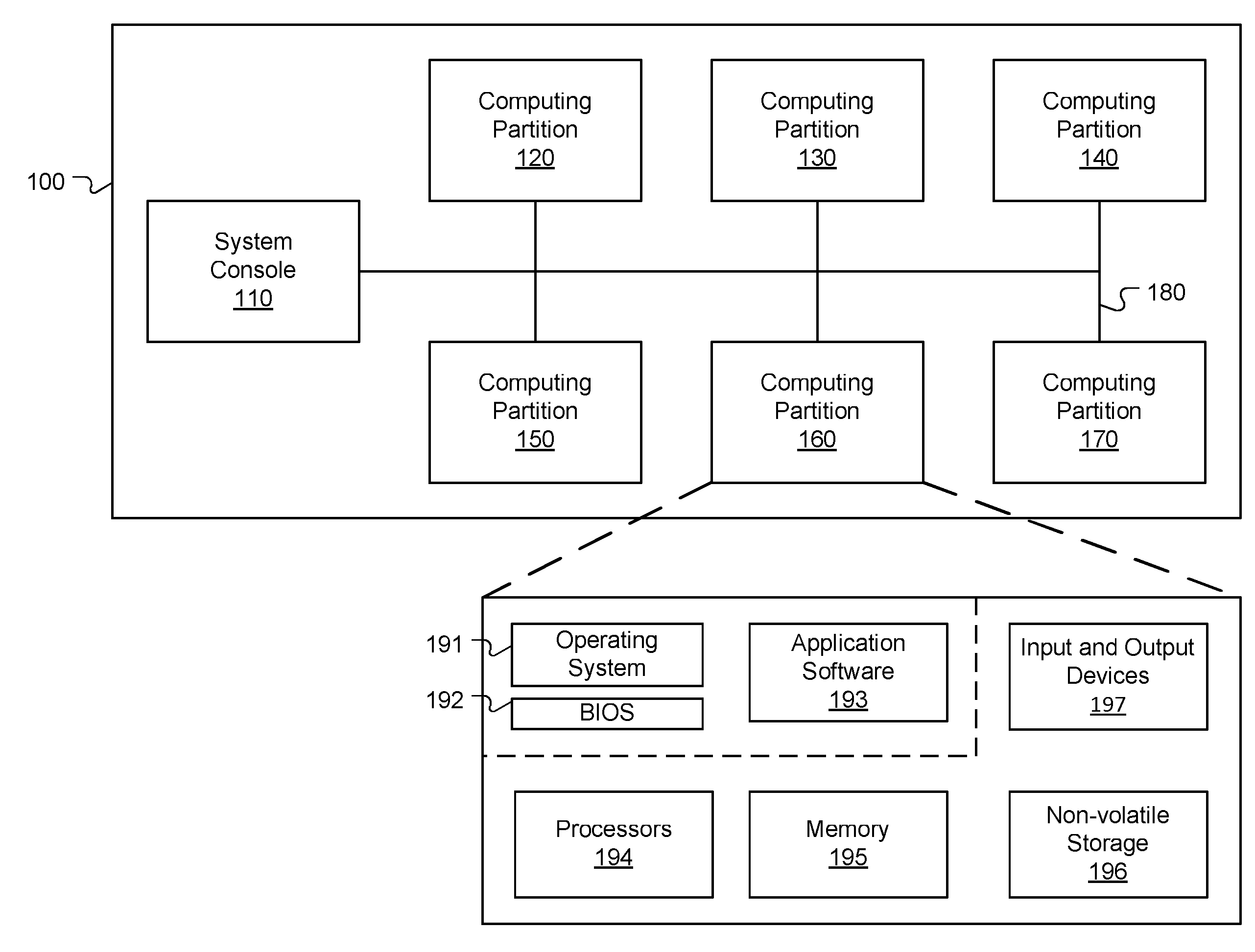

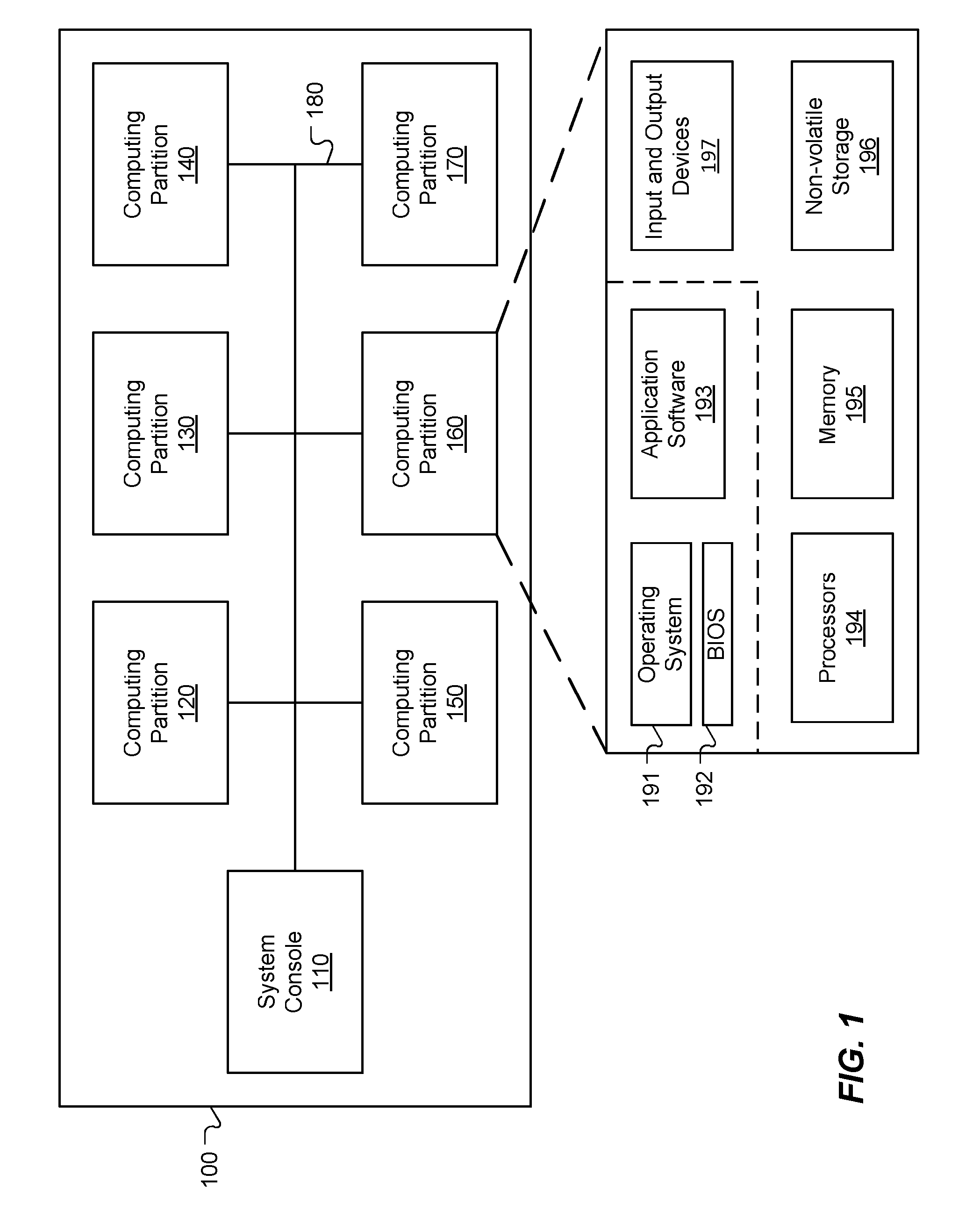

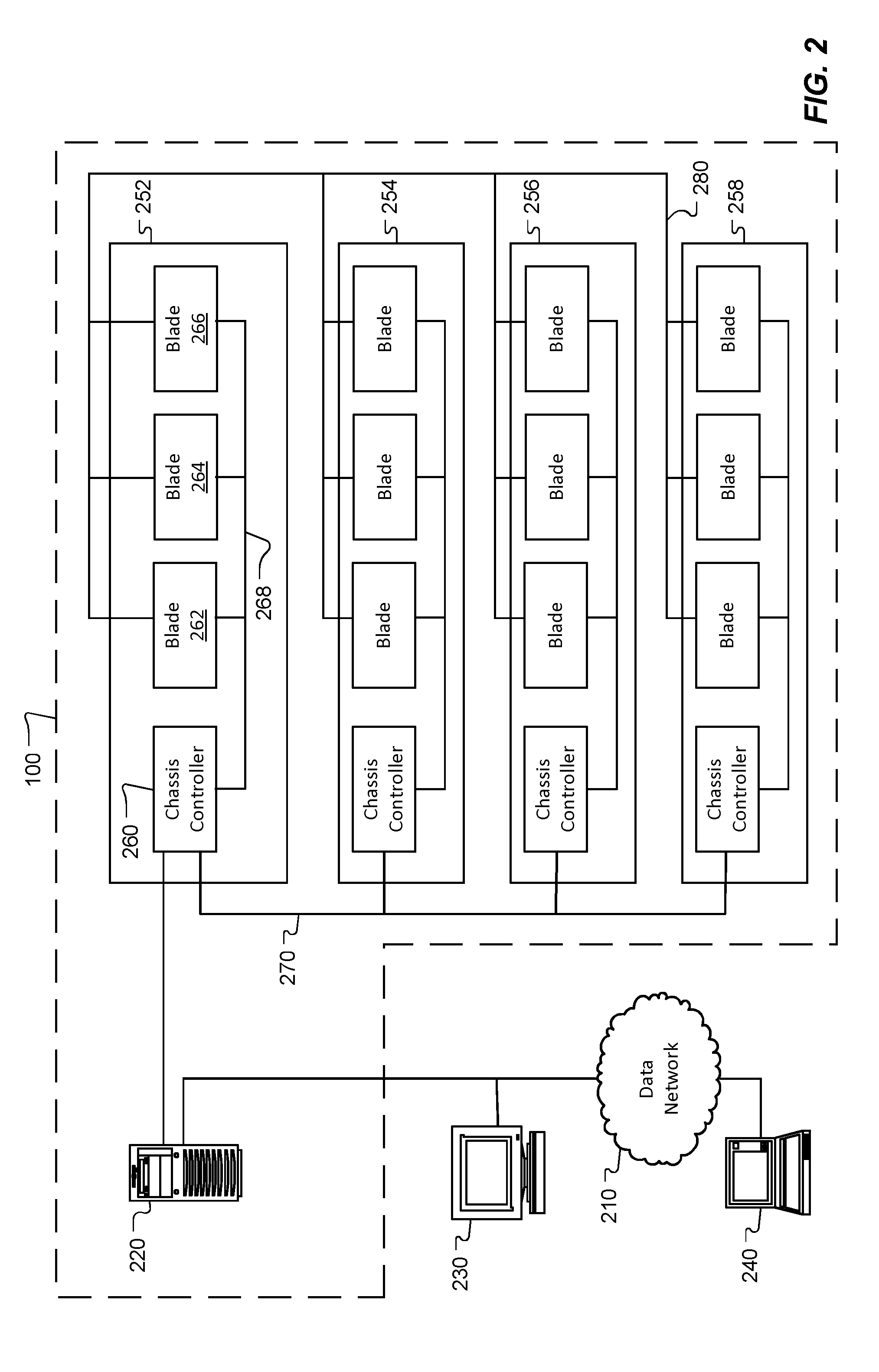

Global Synchronous Clock

ActiveUS20140281656A1Time-division multiplexGenerating/distributing signalsCommunications systemComputer science

Processor clock signals are generated for each processor in a HPC system, such that all the processor clock signals are of the same frequency. Furthermore, as part of a startup (boot) procedure, a process sets all time stamp counters (TSCs) of the processors, such they indicate identical times. Each blade of the HPC system recovers a recovered clock signal from a synchronous communication network, to which the blade is coupled. The blade generates a processor clock from the recovered clock signal and provides the processor clock to processor(s) on the blade. Each chassis is coupled to a second, system-wide, synchronous communication network, and each chassis synchronizes its chassis synchronous communication network with the system-wide synchronous communication system. Thus, all the processor clock signals are generated with the same frequency.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

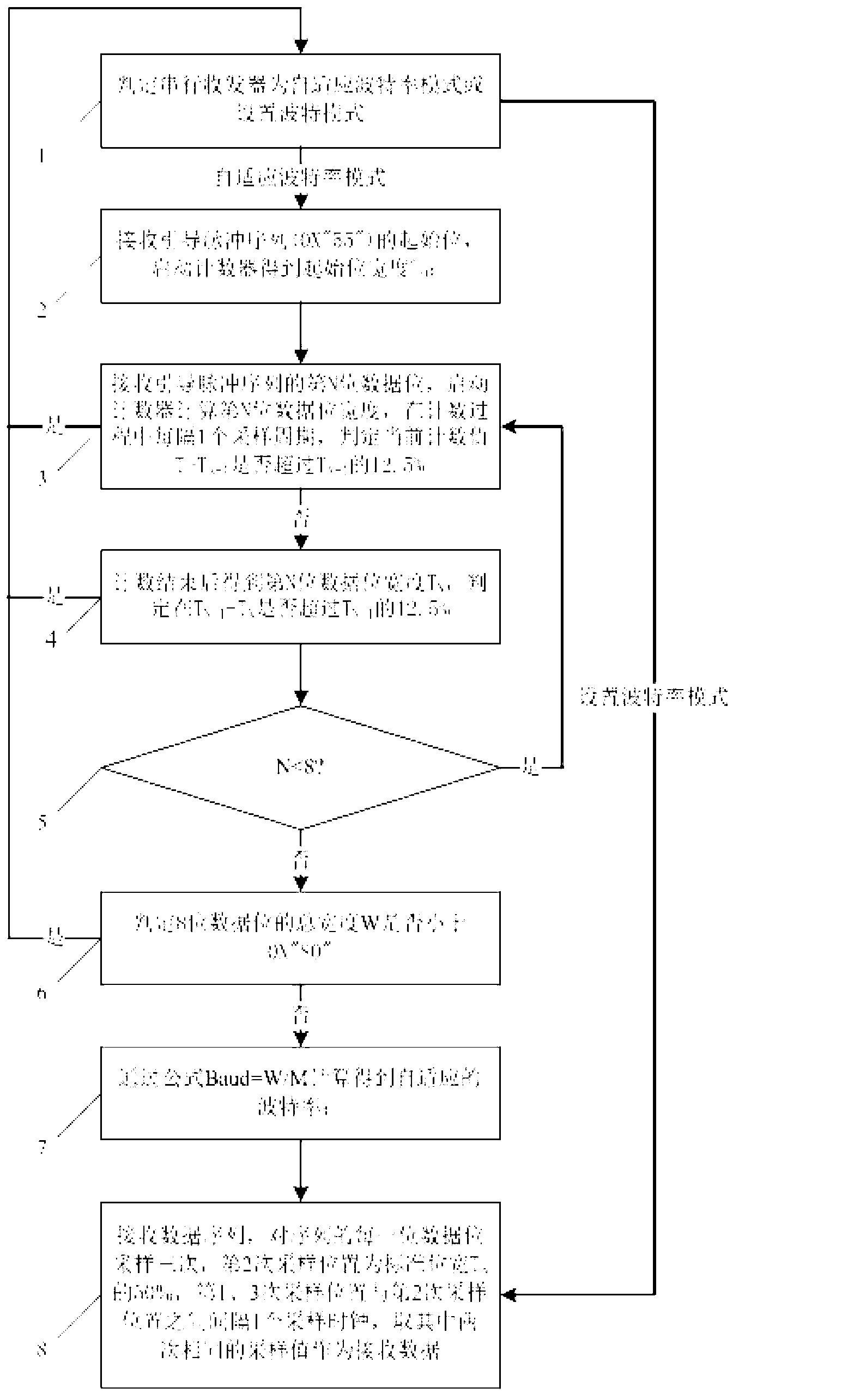

Method for realizing universal serial transceiver

ActiveCN102938744AImprove anti-interference abilityImprove reliabilityBaseband system detailsCommunication interfaceAsynchronous serial communication

The invention provides a method for realizing a universal serial transceiver. The baud rate of a sending end can be determined by receiving a pilot pulse sequence; the total width of the data bit of the pilot pulse sequence must be more than 16*M, the width difference of two adjacent bits (Nth bit and (Nth-1) bit, 1<=N<=M) of the pilot pulse sequence can not be more than x% (x value can be allocated) of the width of the (Nth-1) bit, if more than x%, the pilot pulse sequence needs to be received again for automatic matching connection; and the error of the accumulative bit width of a received data sequence can not be more than y% (y can be allocated) of a standard bit width. The method provided by the invention can not only enhance the anti-interference capacity of serial communications, but also have universality. In combined with a certain communication protocol controller, the universal serial transceiver can form a corresponding serial communication interface, such as a debugging interface and an asynchronous serial communication interface, achieves the effects of flexibility and high reliability and has wide application prospect.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

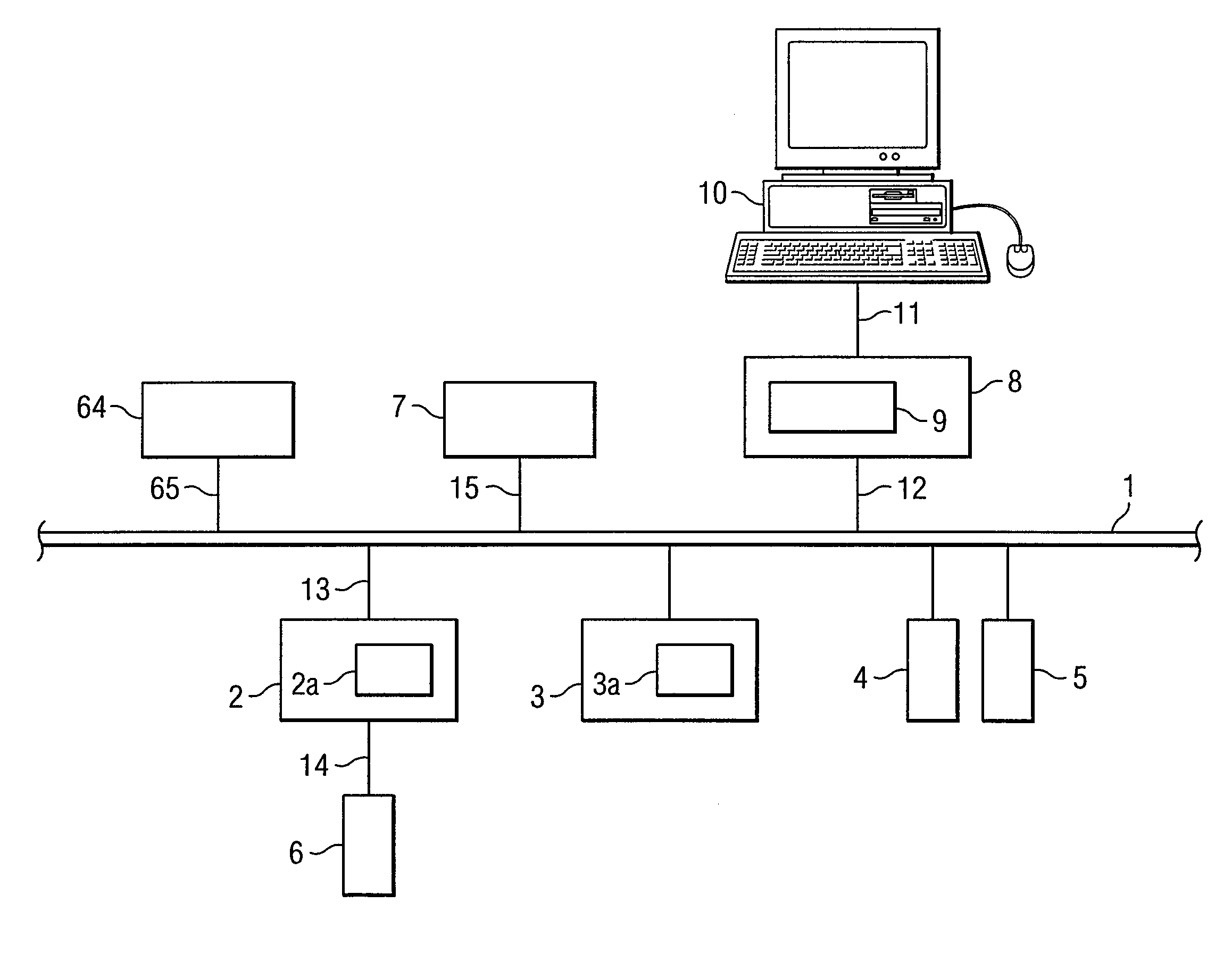

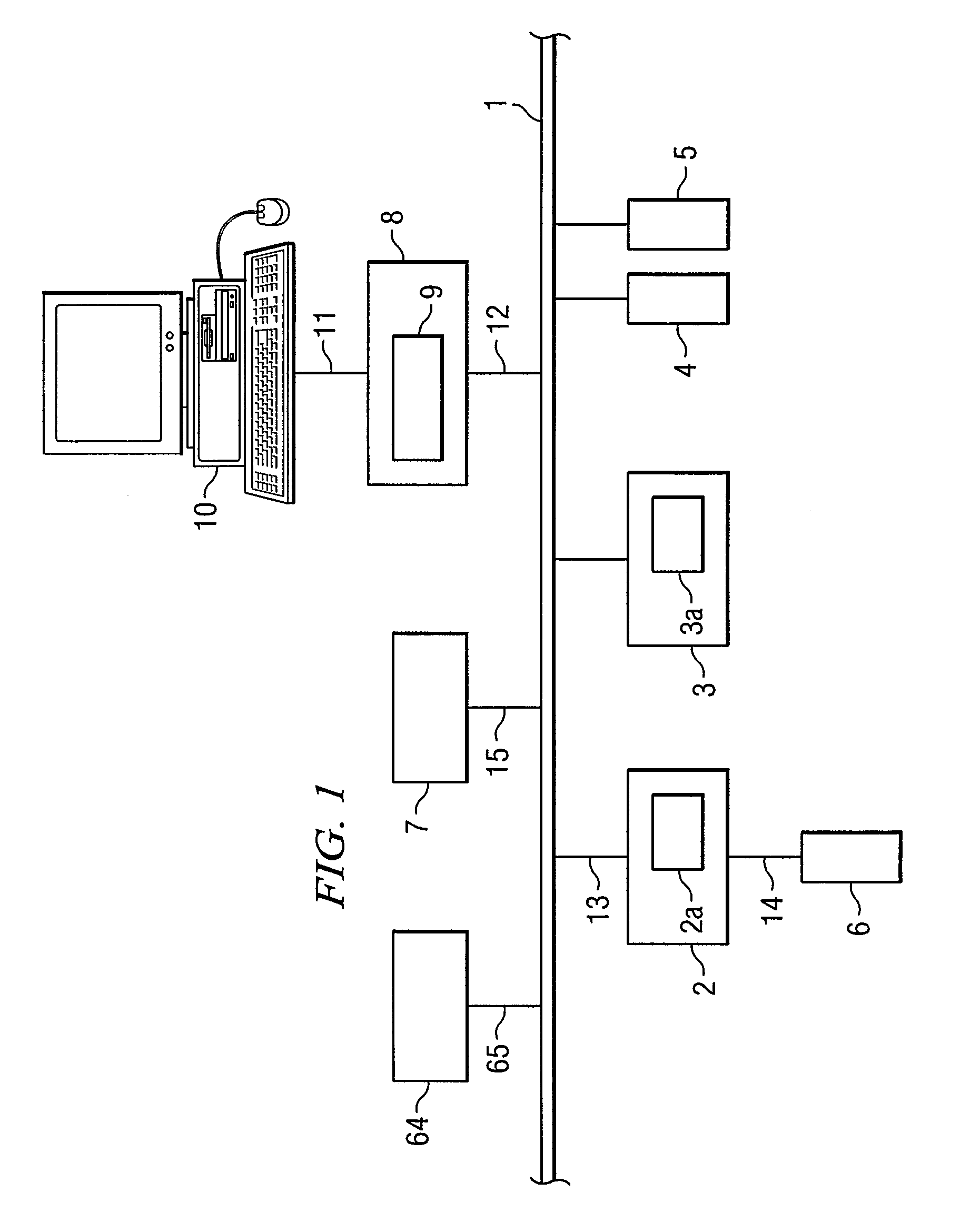

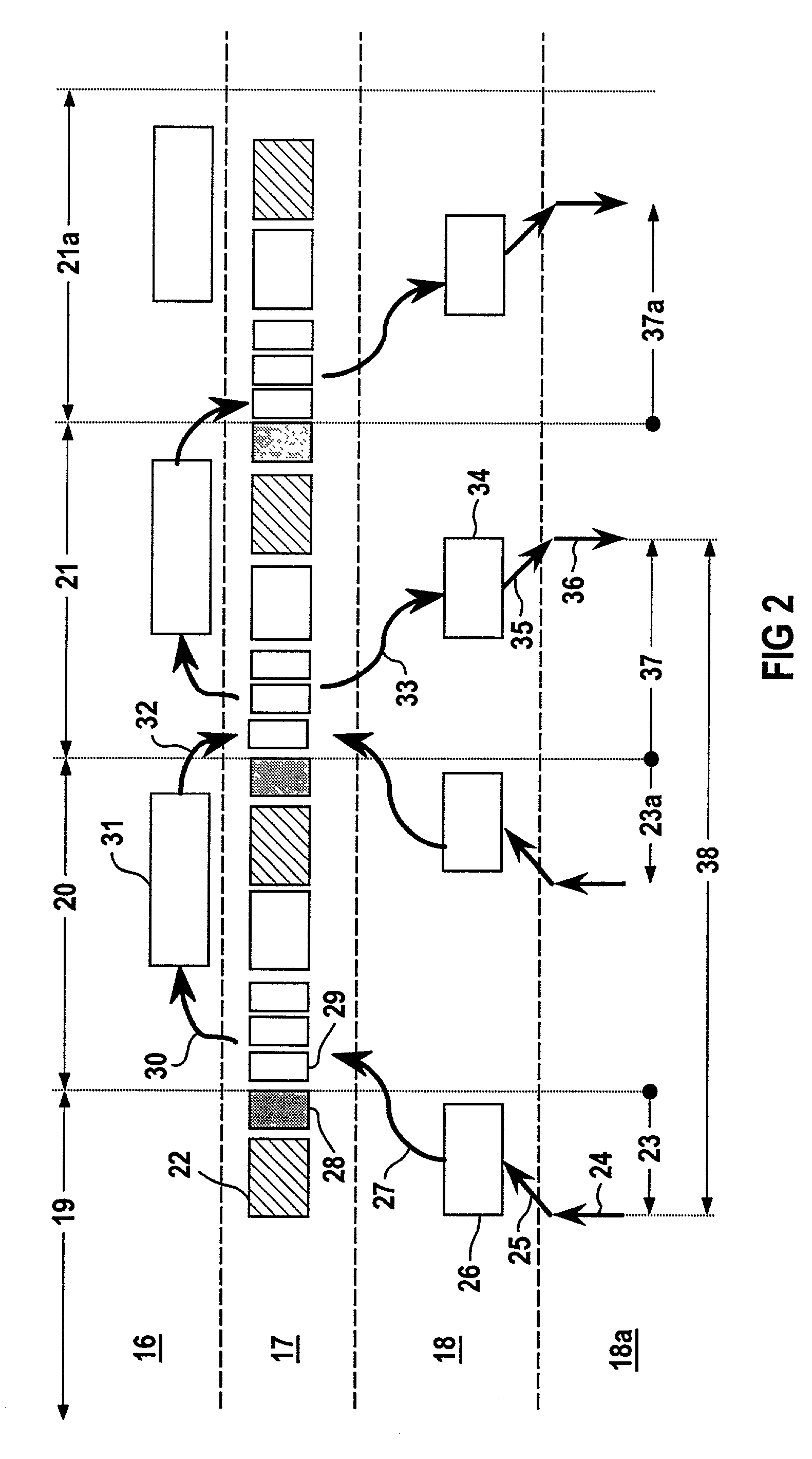

Synchronous clocked communication system with decentralized input/output modules and method for linking decentralized input/output modules into such a system

ActiveUS7280565B2Maximum accuracyMinimum possible timeProgramme controlComputer controlCommunications systemGranularity

The invention relates to a synchronous clocked communication system, for example a distributed automation system, the stations of which can be arbitrary automation components and which are coupled to one another via a data network. Using the disclosed method for integrating decentralized input / output modules, these decentralized input / output modules can be linked into the synchronous clocked communication system in such a manner that they can use their characteristics unrestrictedly. Thus, in particular, the detection of input signals and the output of output signals is possible in a deterministic and synchronous manner in the decentralized input / output modules. In addition, the disclosed method enables input signals to be detected with an accuracy of less than the length of one communication cycle of the communication system and to support the switching of output signals in smaller time granularities than the length of one communication cycle which, in particular, finds use, e.g. for switching cams.

Owner:SIEMENS AG

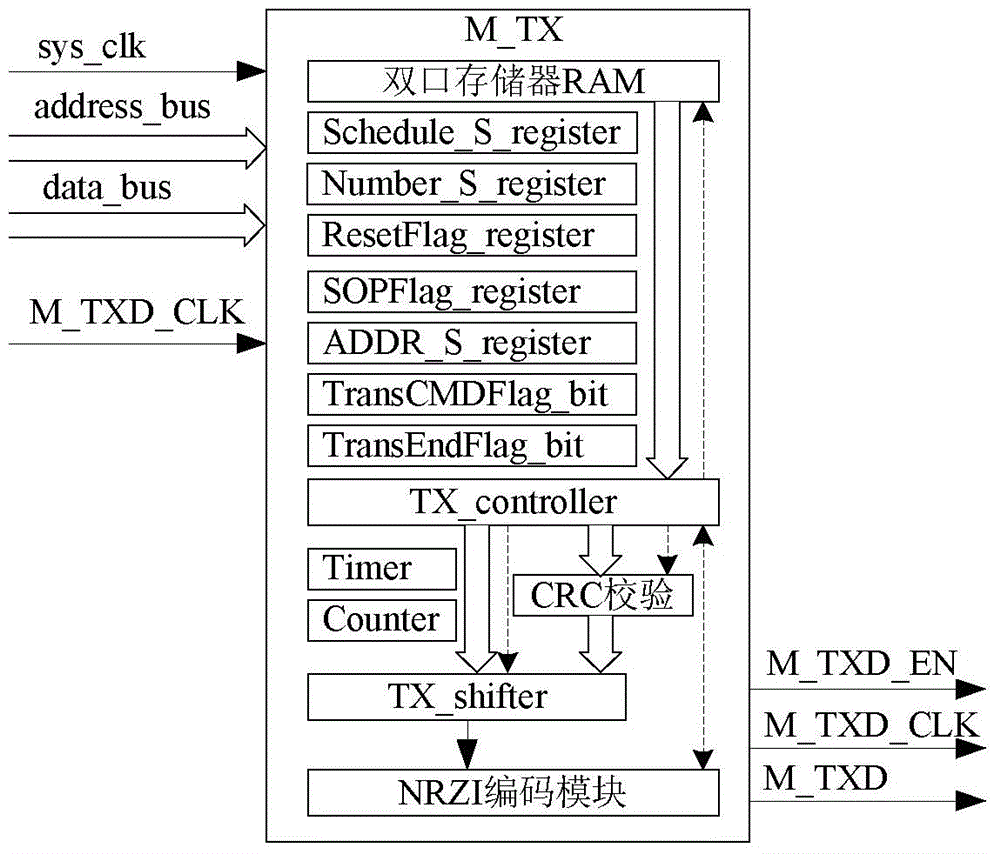

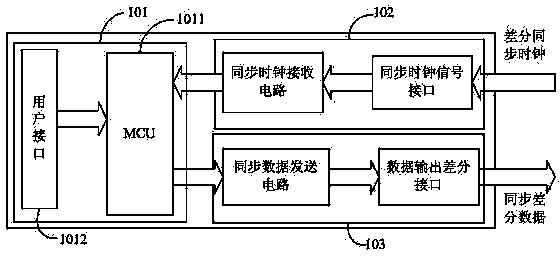

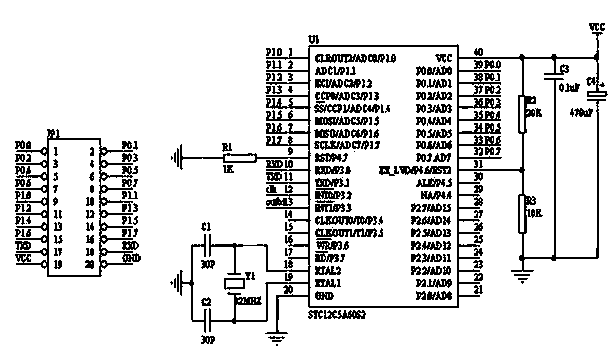

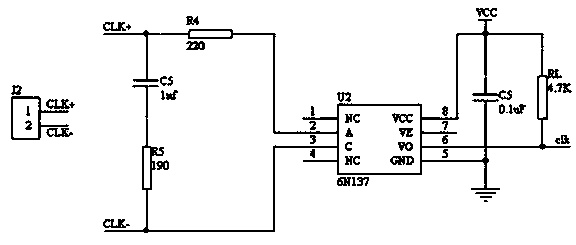

Synchronous serial communication interface device

InactiveCN103454951AIncrease transfer rateLow costProgramme controlComputer controlControl cellData transmission

A synchronous serial communication interface device comprises three parts, namely a master control unit, a synchronous clock receiving unit and a synchronous data output unit. According to a synchronous clock signal, received asynchronous serial data or parallel data are converted into synchronous serial differential data which are output; the synchronous clock receiving unit is used for converting a received synchronous clock differential signal into a single-ended signal and transmitting the single-ended signal to the master control unit; the synchronous data output unit is used for differencing of synchronous data output by the master control unit so as to improve the anti-interference performance in the data transmission process. The synchronous serial communication interface device has quite strong practicability; by means of being connected with the synchronous serial communication interface device, external devices which are subjected to asynchronous serial output or parallel output can achieve the synchronous serial communication function, and therefore the application range of the synchronous serial communication interface device is expanded to a large extent.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

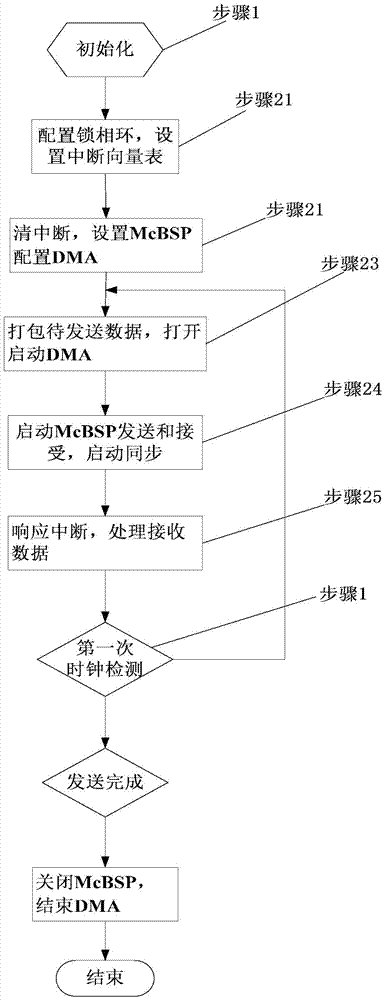

Full-duplex asynchronous serial communication method

InactiveCN103577378AImprove work efficiencyReduce Clock SkewDigital computer detailsConcurrent instruction executionAsynchronous serial communicationData stream

The invention relates to the field of communication, in particular to a full-duplex asynchronous serial communication method. The method comprises the following steps of the step 1, carrying out pre-communication on two microprocessors to carry out first clock detection, the step 2, initializing the two microprocessor in serial communication, storing data sent and received by the two microprocessors into a data storer and finishing the data transmission between the sent and received data and a transmitting register DXR of an McBSP and data transmission between the sent and received data and a receiving register DDR through a DMA channel, the step 3, sending data and packing characters to be sent into data formats received by serial communication when the data are sent, and the step 4, receiving the data and sampling and correcting the received data flow to carry out second clock detection. On the premise without increasing hardware cost, the full-duplex asynchronous serial communication method improves the work efficiency of a CPU, reduces clock skew between signals and enables serial communication to be more stable, efficient, low in cost and simple and easy to achieve.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

Asynchronous serial communication method and system

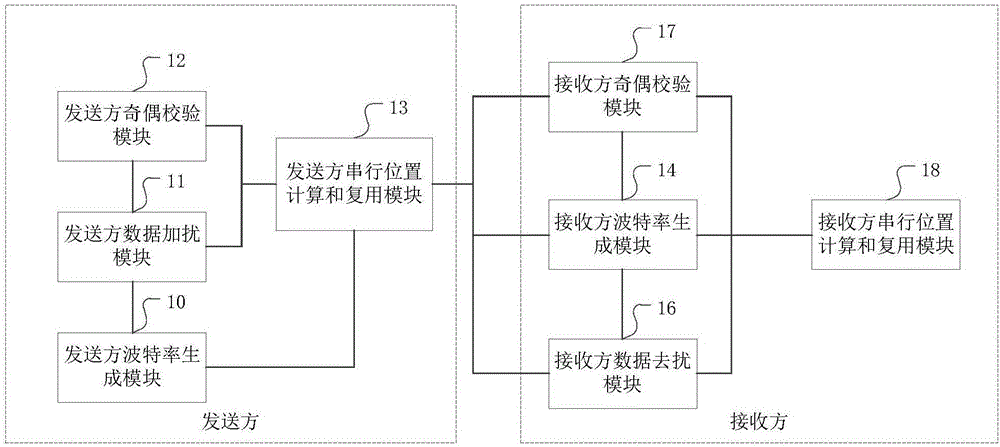

ActiveCN106301685AEnsure safetyReduce chances of eavesdroppingElectric digital data processingTransmission format adaptationComplete dataAsynchronous serial communication

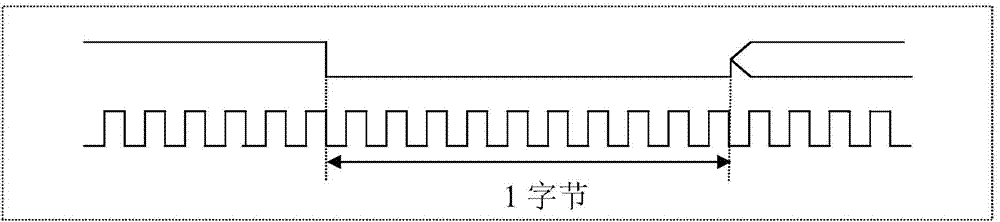

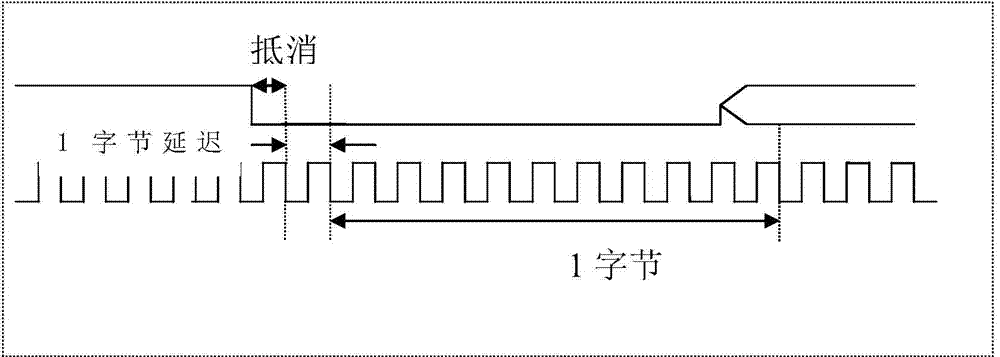

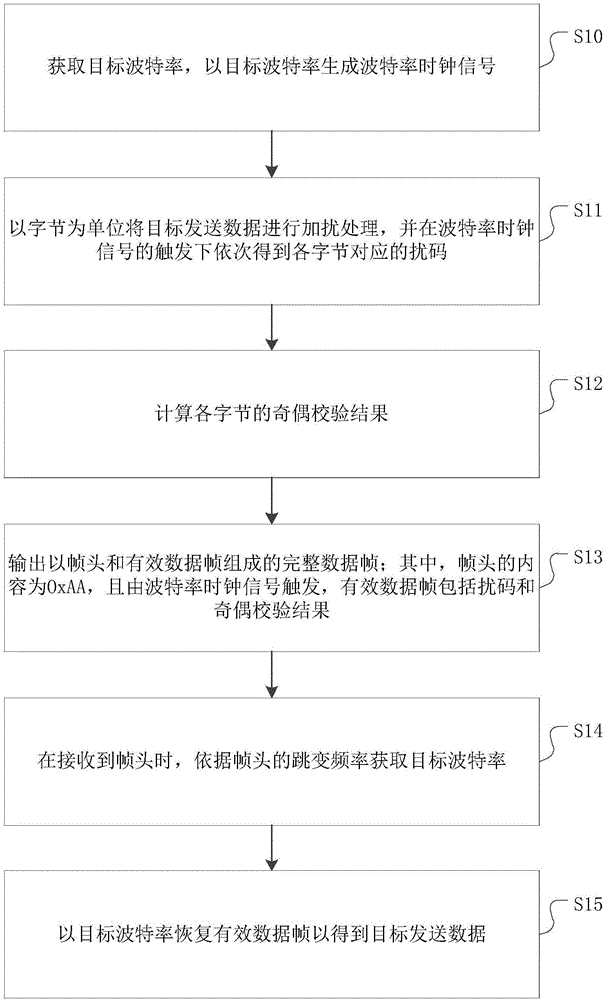

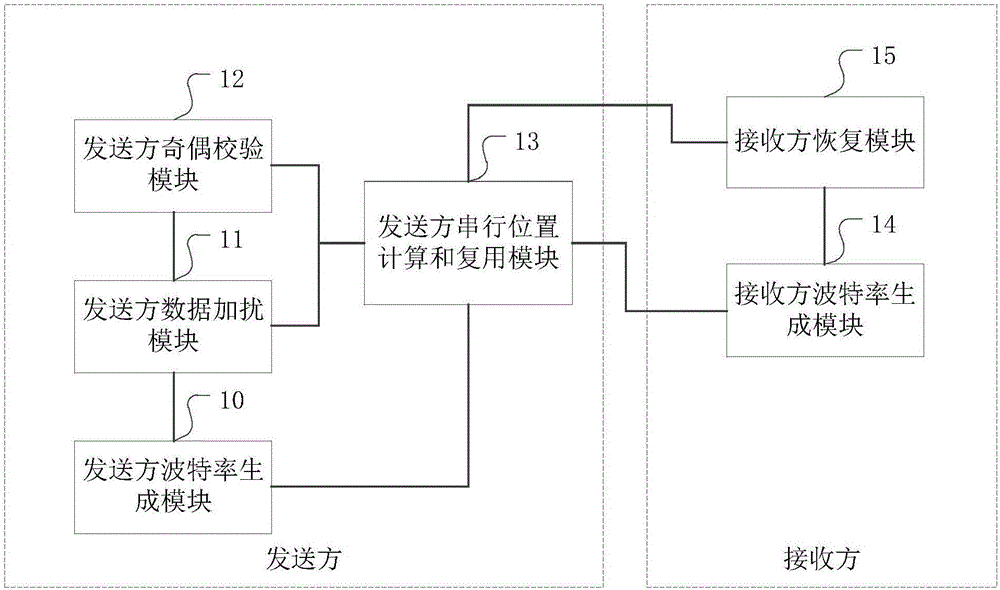

The invention discloses an asynchronous serial communication method. The asynchronous serial communication method comprises the following steps: obtaining a target baud rate, and generating a baud rate clock signal according to the target baud rate; performing scrambling processing on target sending data in bytes, and successively obtaining a scrambling code corresponding to each byte at the trigger of the baud rate clock signal; calculating the odd-even check result of each byte; outputting a completed data frame consisting of a frame header and valid data frames; obtaining the target baud rate according to the jump frequency of the frame header while the frame header is received; and recovering the valid data frames according to the target baud rate. The frame header is added at the front of the valid data frames, and the frame header is triggered by the baud rate clock signal, therefore, while a receiver receives the frame header, the baud rate used by a sender is obtained through the bit jump information of the frame header. Furthermore, the security of communication is further ensured by means of the scrambling processing. The probability that communication contents are eavesdropped is reduced by means of the asynchronous serial communication method. The invention also discloses an asynchronous serial communication system, and the effect is realized as mentioned above.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

Method for synchronous awakening communication of active RFID (Radio Frequency Identification Devices) system

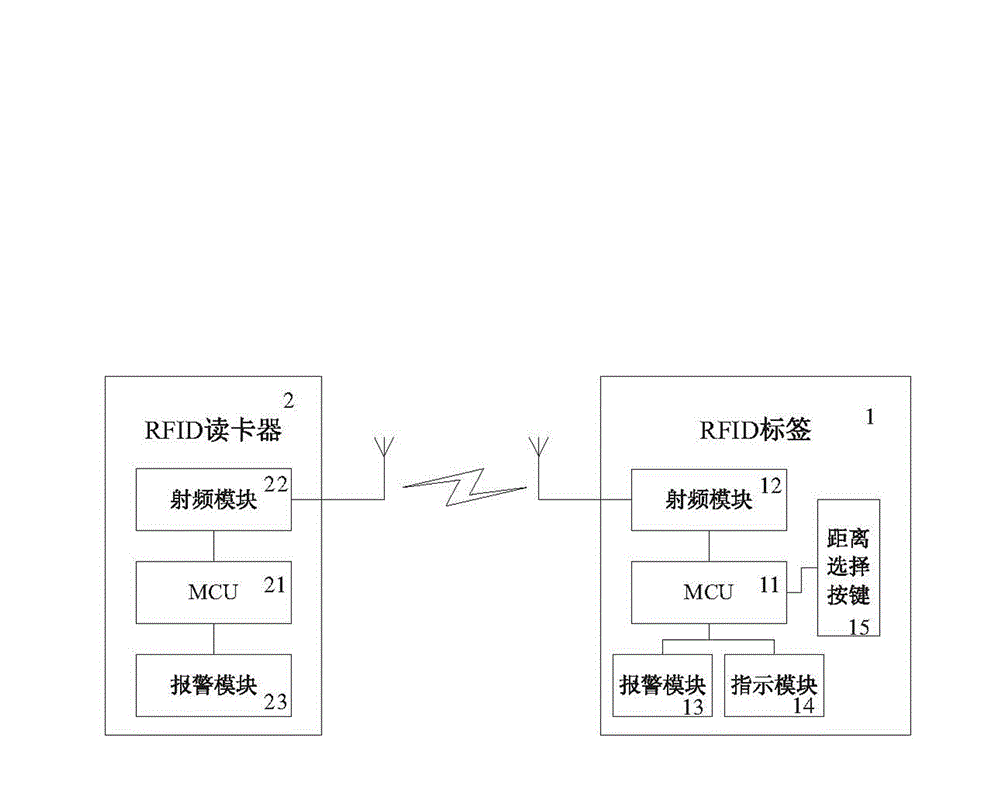

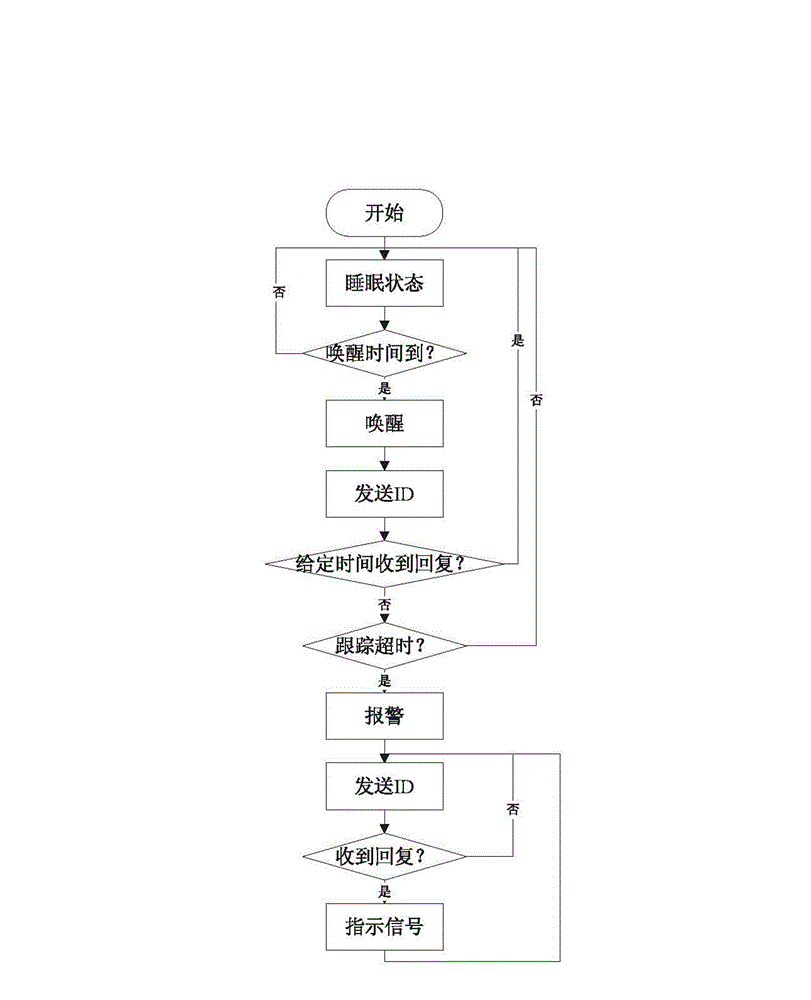

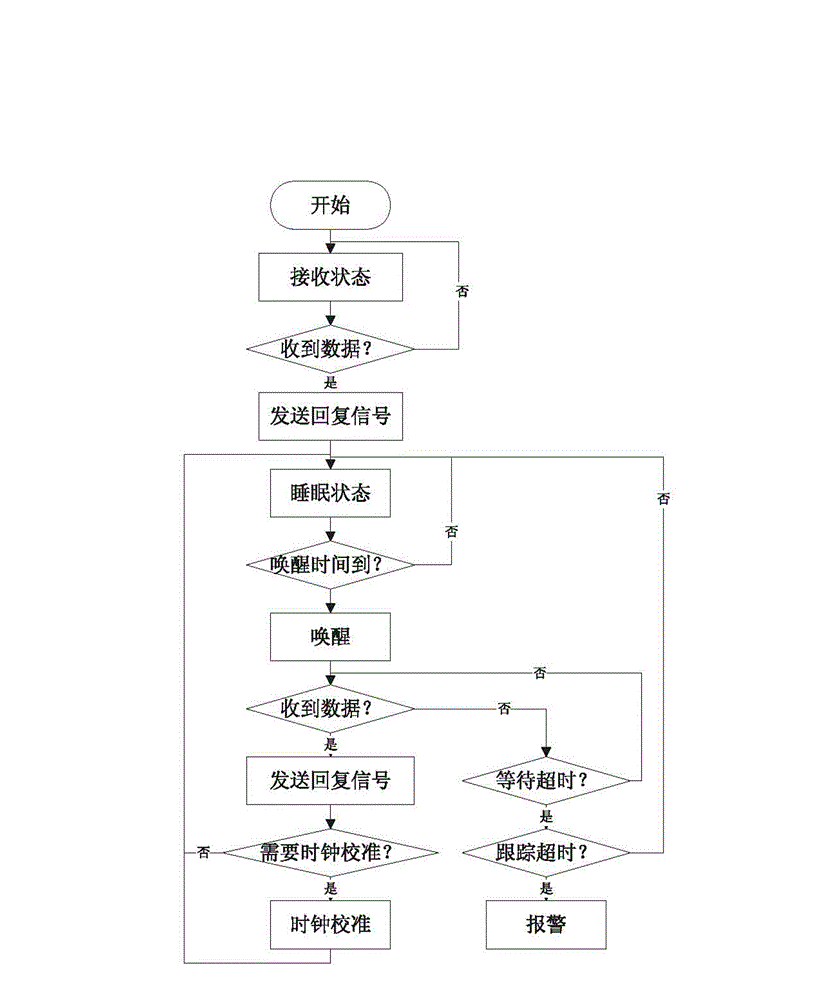

InactiveCN102799839AReduce power consumptionSynchronous CalibrationCo-operative working arrangementsSensing record carriersElectricityElectronic tagging

The invention provides a method for synchronous awakening communication of an active RFID (Radio Frequency Identification Devices) system. After a system is electrified, an active RFID card reader works at a receiving state and an active RFID electronic tag sends information to the card reader; and after the card reader receives the information, a replaying signal is sent to the electronic tag and two parties take the moment as a time initial point to enter synchronization. A timed synchronous awakening method, a synchronous calibration process and a synchronous frequency hopping process are added into a synchronous awakening process. The RFID electronic tag and the RFID card reader are successfully communicated for the first time to obtain a time synchronous signal and subsequent communication is awakened according to set time so as to realize that the RFID electronic tag and the RFID card reader are synchronously awakened and the power consumption is lower; furthermore, a clock signal is used as one part of communication and clocks of the two parties are used for realizing synchronous calibration; and the method utilizes a synchronous frequency hopping mechanism to avoid fixed interference.

Owner:阿艾夫技术有限公司

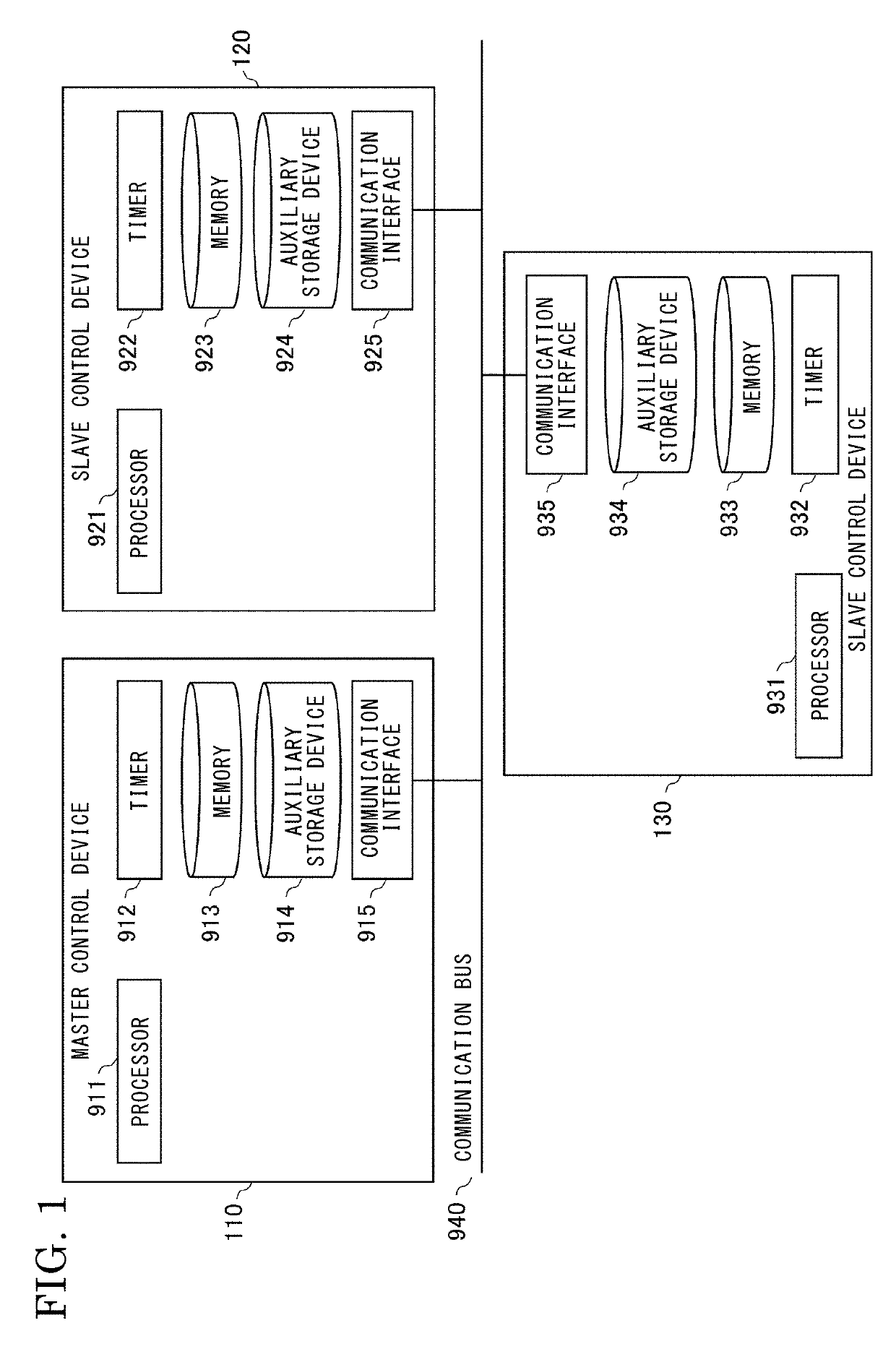

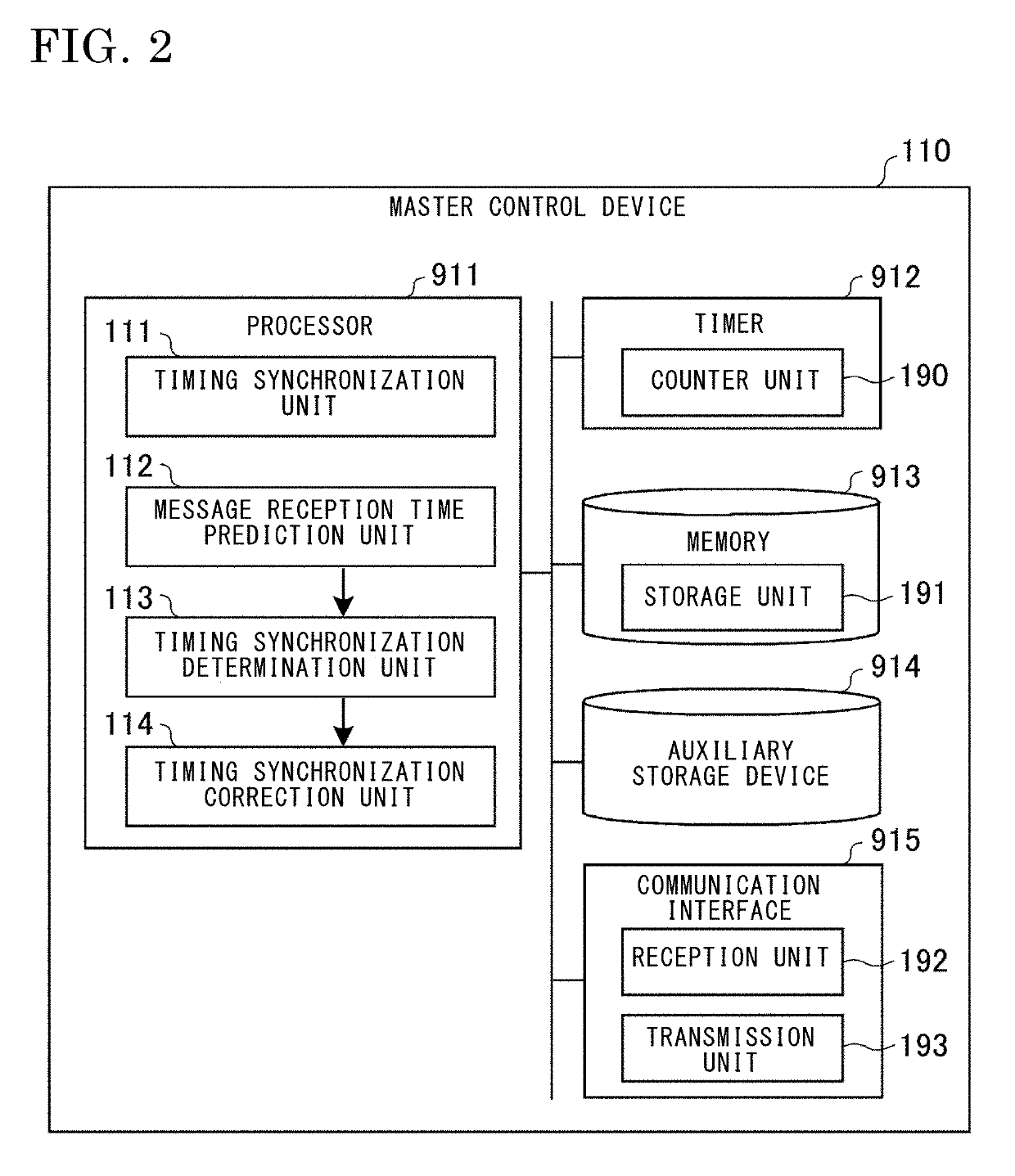

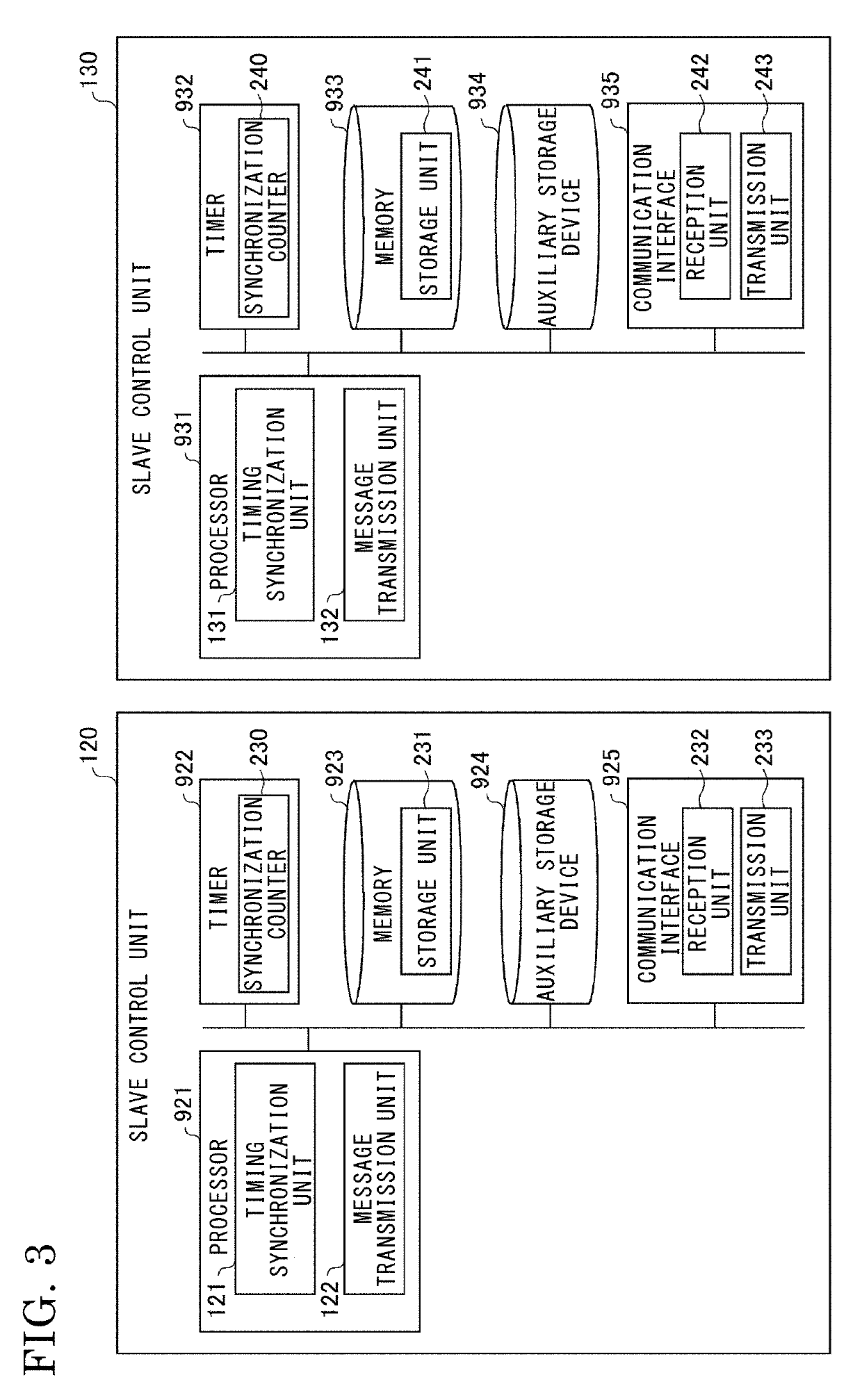

Master control device and synchronous communication system using same

ActiveUS20190222407A1Accurate timingSynchronisation error detectionTime-division multiplexCommunications systemSynchronous serial communication

Owner:MITSUBISHI ELECTRIC CORP

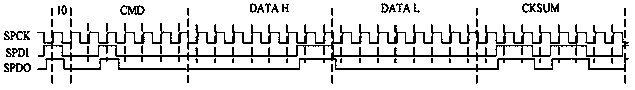

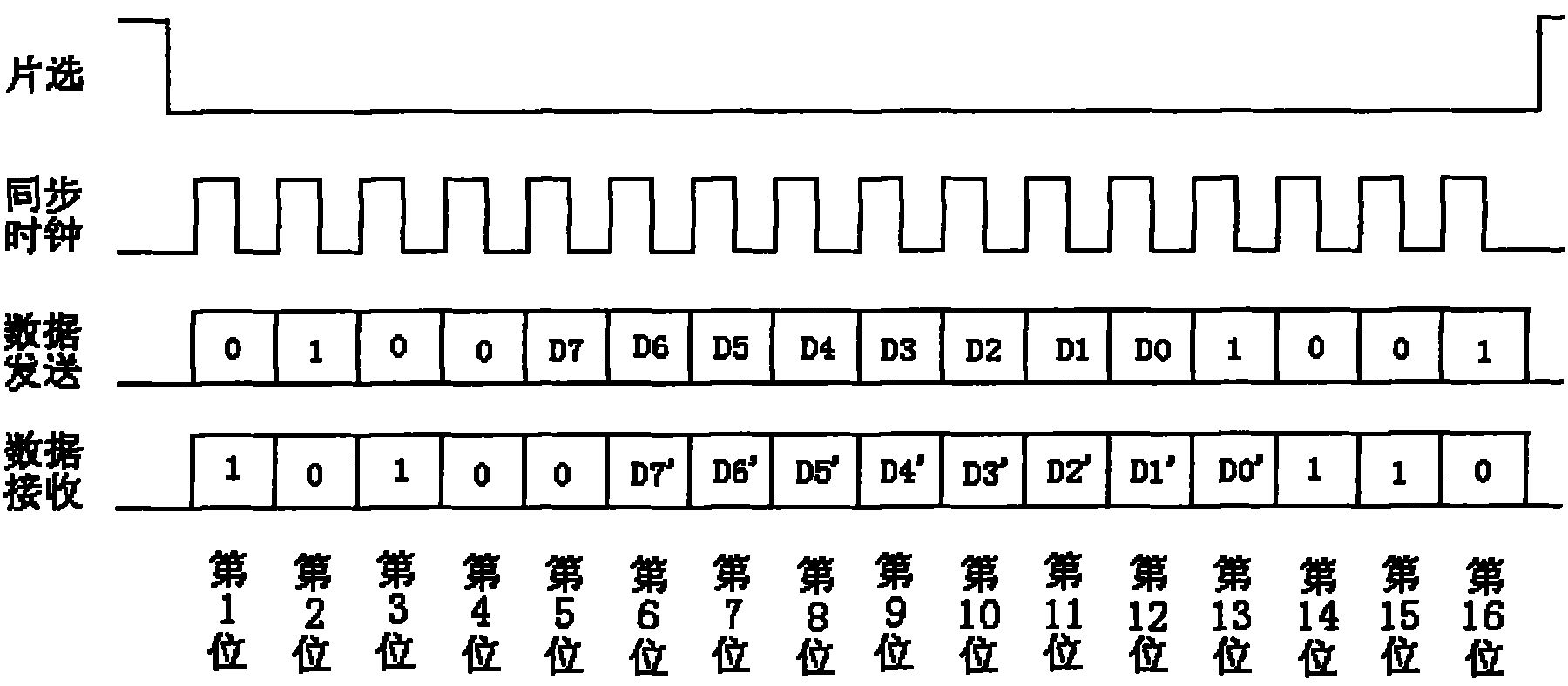

Synchronous serial communication interface and communication method thereof

ActiveCN103427945AResolve interferenceSolve the problem of mutation and errorError preventionComputer hardwareAsynchronous serial communication

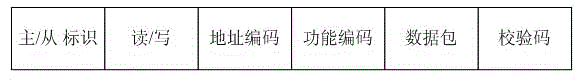

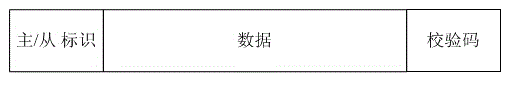

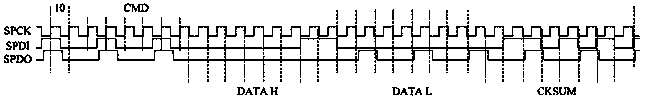

The invention discloses a communication method of a synchronous serial communication interface. According to the communication method of the synchronous serial communication interface, data frames are adopted to perform communication, wherein each data frame includes a start bit, a command area, data areas and a checksum, wherein the command area is used for determining the effect of a current data frame, the data areas is data which are transmitted according to commands in the current data frame, and the checksum is check values for checking the start bit, the command area and the data in the data areas of the data frame; after the communication of each data frame terminates, both sides of communication clearly know whether faults occur in communication; and at the same time, read-write operation marks can be obtained through command field decoding. Read-write operation can be obtained through multi-bit decoding, such that the probability of misoperation caused by interferences can be reduced. Read-write mark bits and data fields in an existing communication method of a synchronous serial communication interface are vulnerable to electromagnetic interference, as a result, mutations will occur on the read-write mark bits and the data fields, and errors will be produced, while with the communication method of the invention adopted, the problem can be solved.

Owner:HANGZHOU VANGO TECH

Highly configurable radar module link

InactiveUS20050068987A1Error prevention/detection by using return channelSynchronisation information channelsRadarData signal

A communications apparatus having a bidirectional, fair multiple-access, synchronous serial communications protocol operational with a single clock and a single data signal, which single clock is adapted to provide a uni-directional clock signal to synchronize a remote end of the apparatus with the single clock.

Owner:GAS RES INST

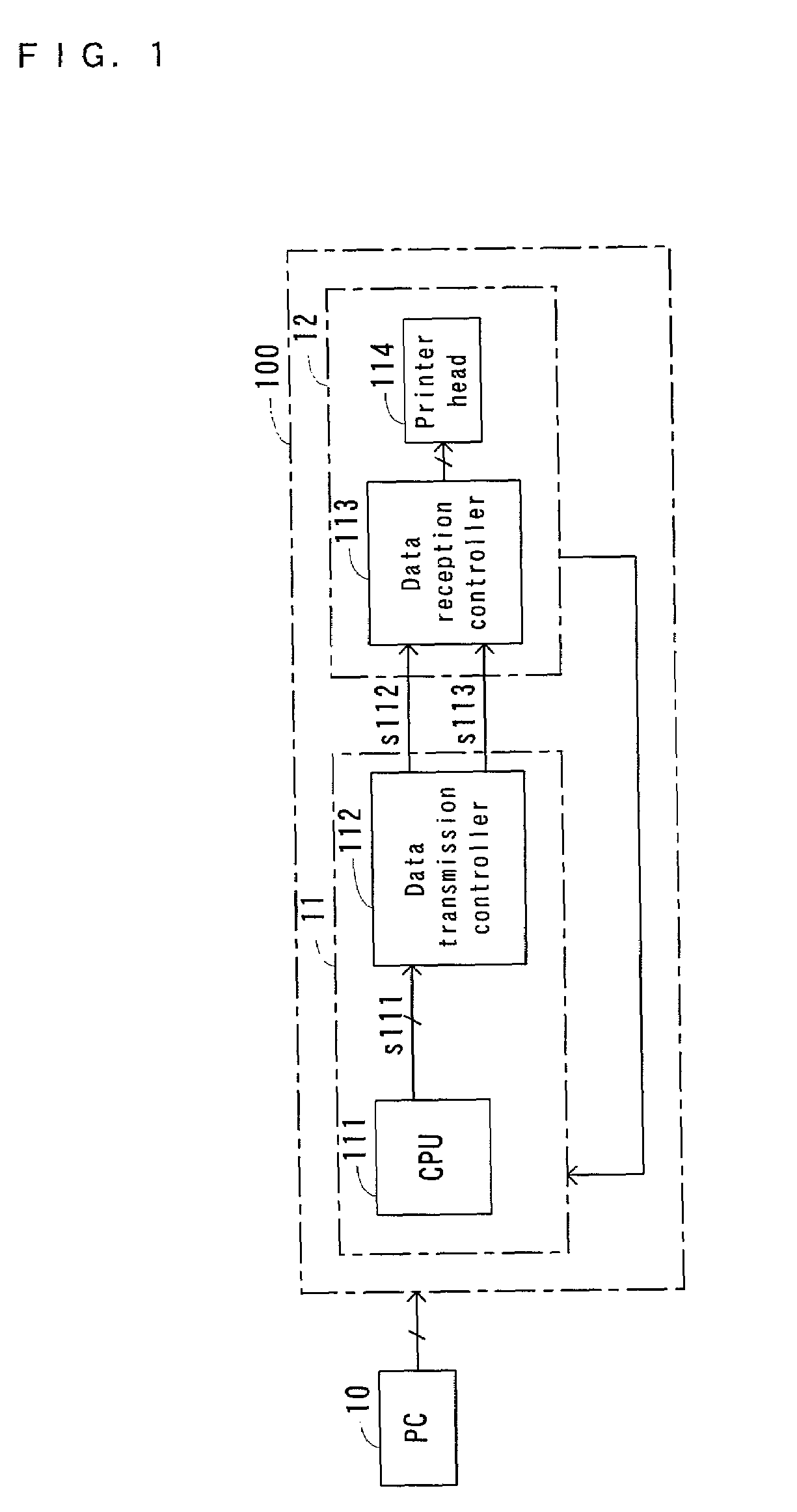

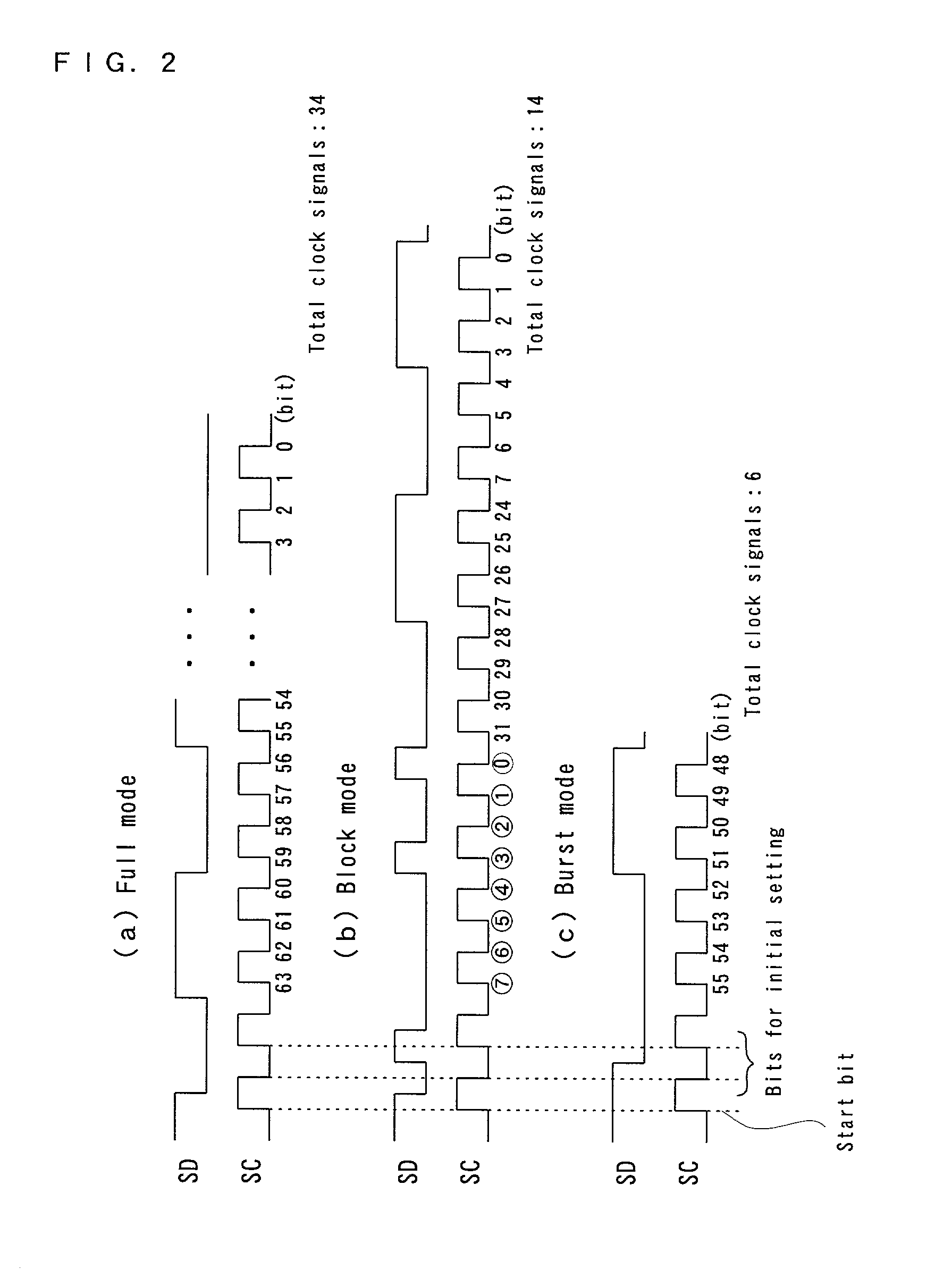

Method of synchronous serial communication and system for synchronous serial communication

InactiveUS7184501B1Electric signal transmission systemsError preventionAsynchronous serial communicationData transmission

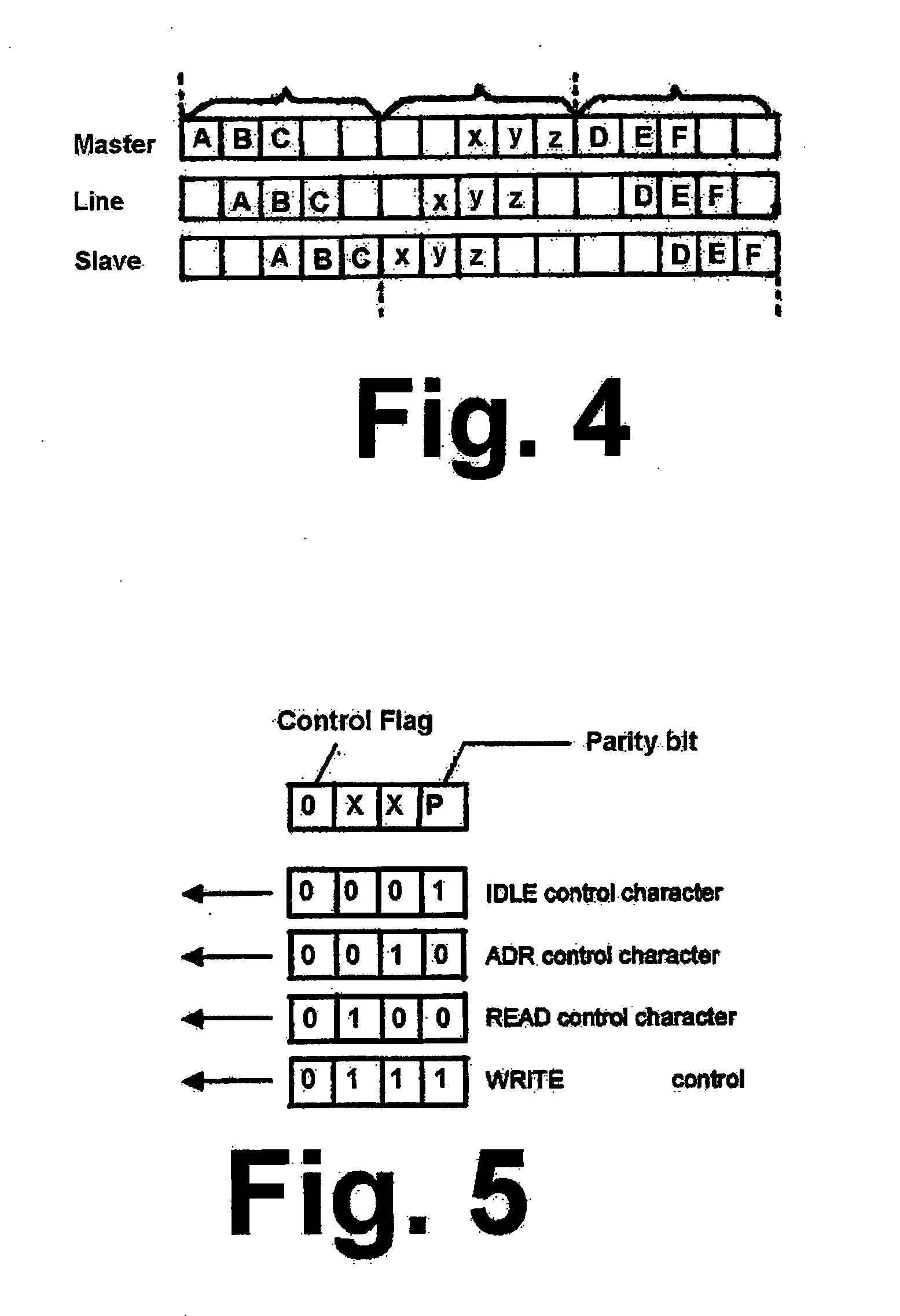

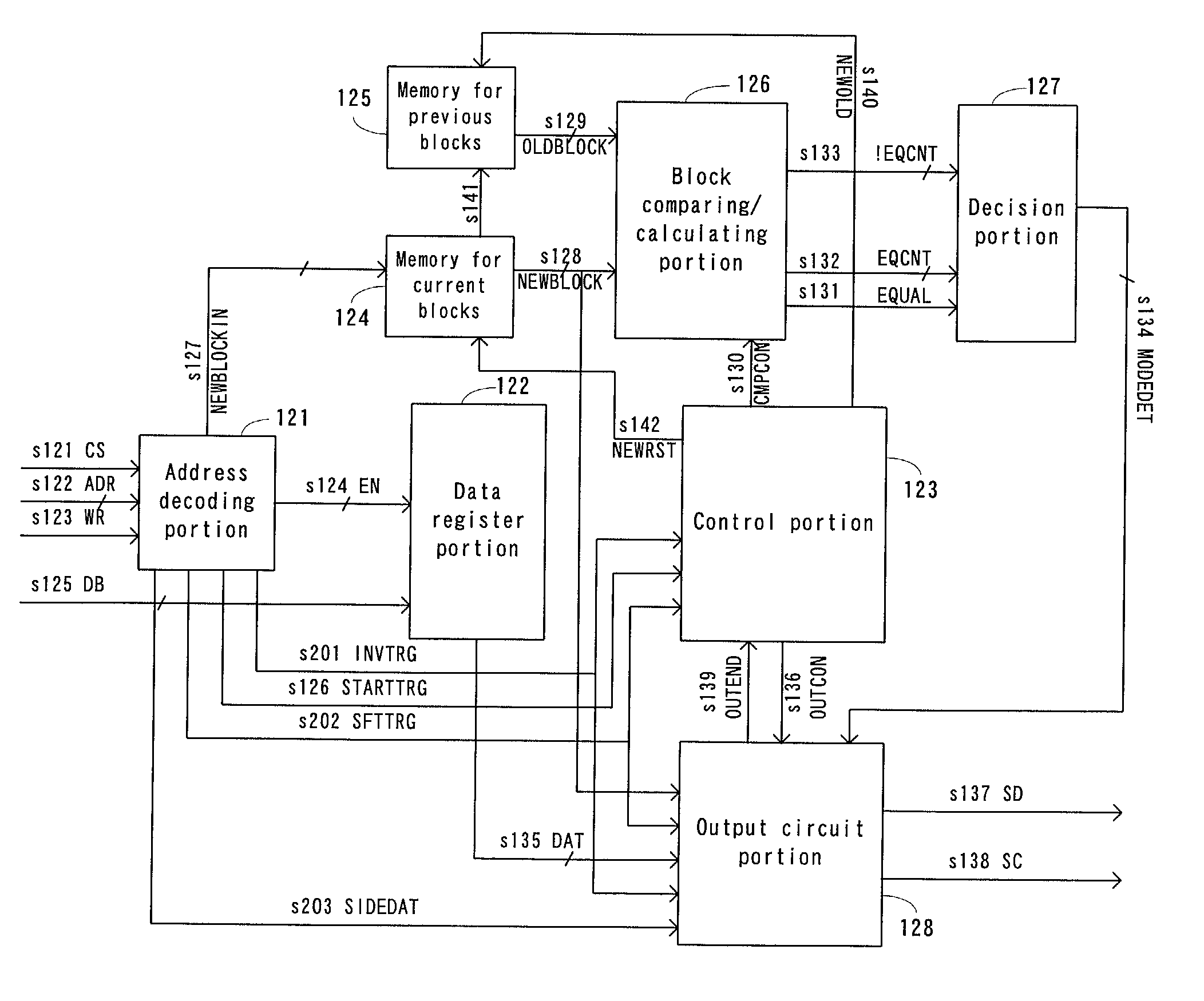

A method and system for serial communication capable of increasing the speed of the transmission of serial data are provided. A block mode is employed if transmission of serial data having a specific length is required, and under which data to be transmitted are divided into plural blocks, and firstly transmitted is block information that notifies which blocks out of the entire blocks will be transmitted, and then transmitted are the data included in the blocks notified by the block information. The burst mode is a mode under which the block information which is currently transmitted is compared with the block information which was previously transmitted, and, if the two are the same, transmission of the data is introduced, while the block information being omitted. The system attached mode information notifying the mode through which data will be transmitted, to the data to be transmitted.

Owner:COPYER

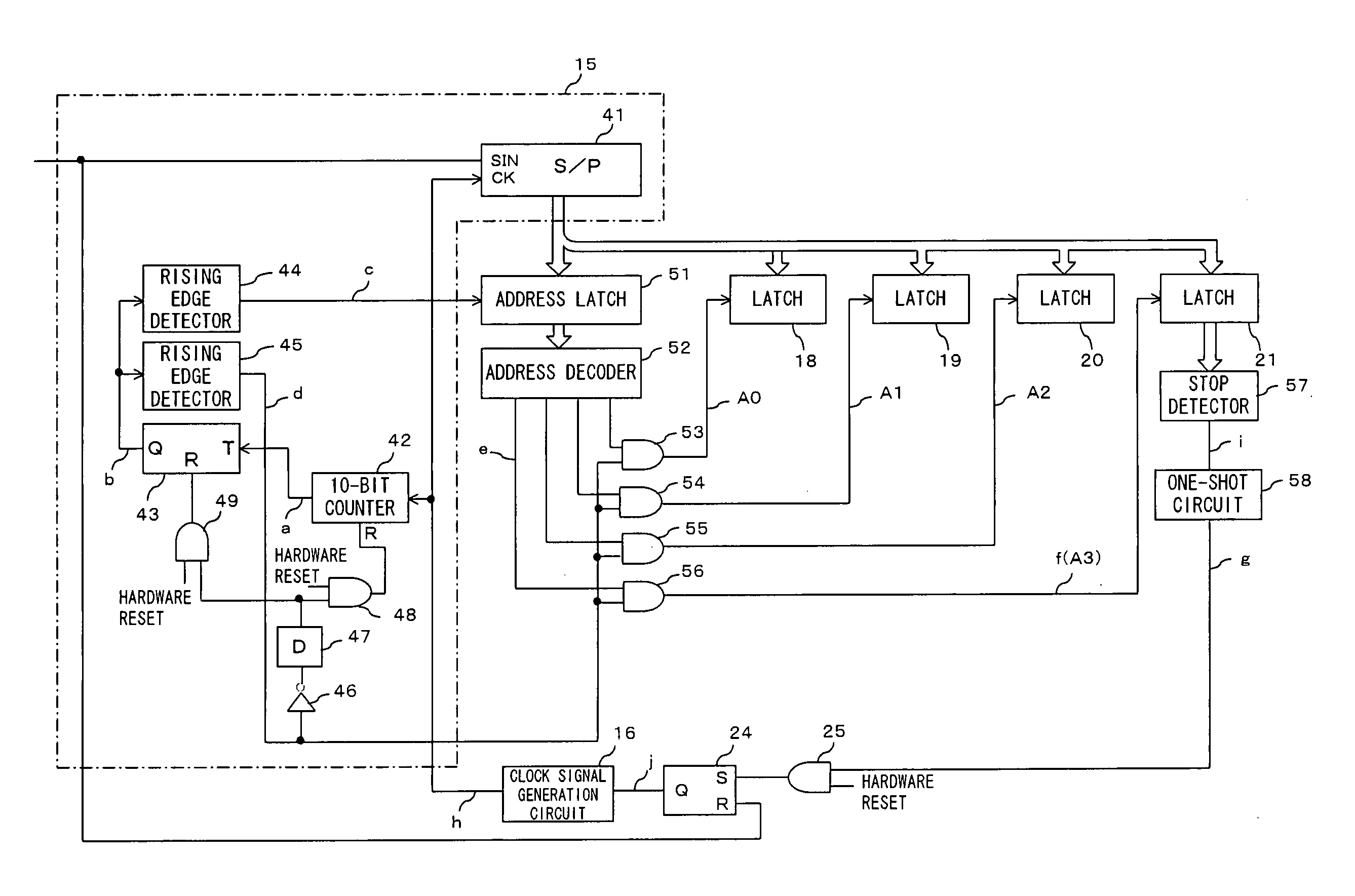

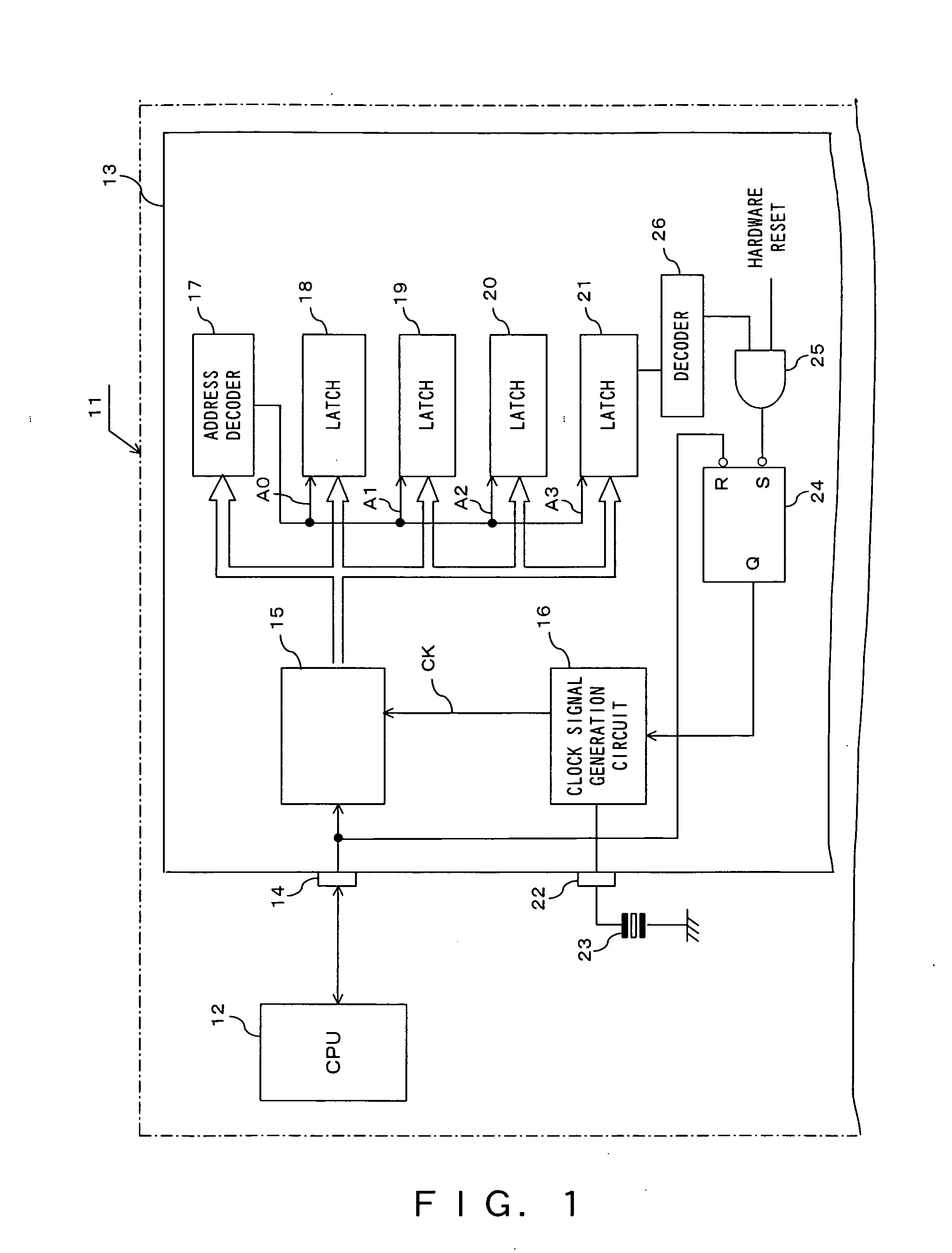

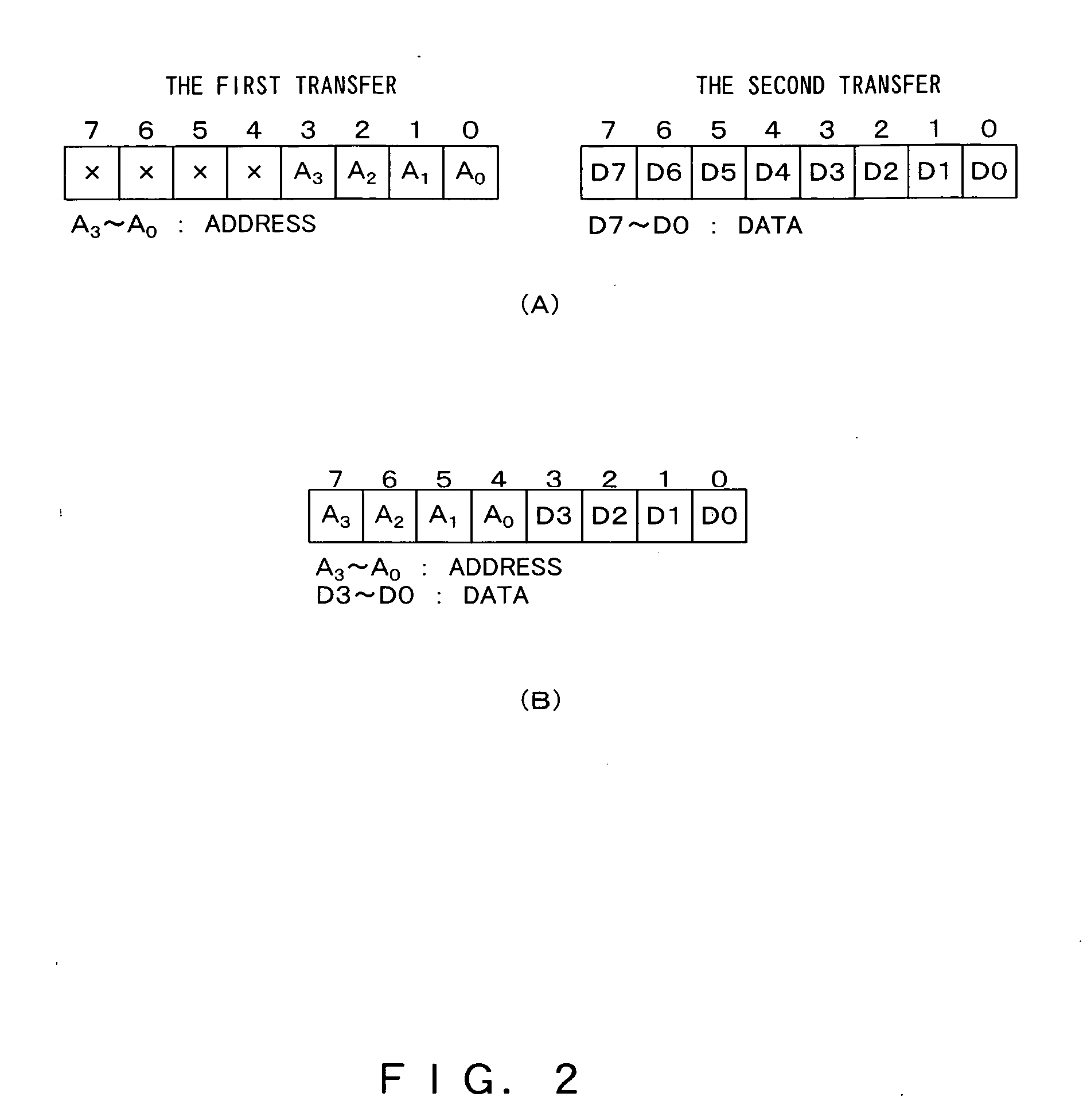

Start-stop synchronization serial communication circuit and semiconductor integrated circuit having start-stop synchronization serial communication circuit

InactiveUS20060146970A1Reduce power consumptionStop operationPower supply for data processingSynchronisation signal speed/phase controlStart stopComputer science

When detecting a start bit, a start bit detection circuit 15a outputs a signal for starting the oscillating operation of a clock signal generation circuit 16. When latching an end code for indicating the end of serial communication, a latch circuit 21 outputs the end code to a decoder 26. The decoder 26 decodes the end code and outputs a signal for stopping the oscillating operation of the clock signal generation circuit 16. Thus, the power consumption of the clock signal generation circuit 16 can be reduced.

Owner:TOYOTA KK +1

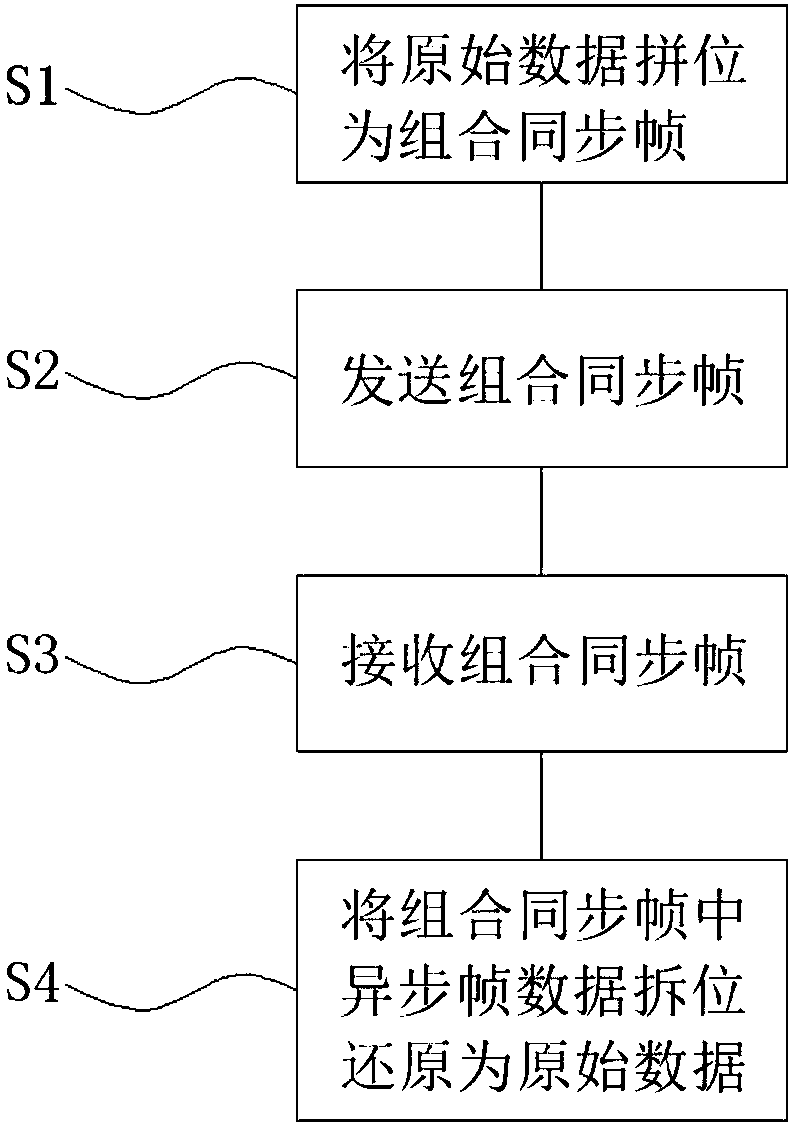

Data transmission protocol method

ActiveCN108512785AImprove transmission efficiencyData switching networksTransmission format adaptationAsynchronous serial communicationOriginal data

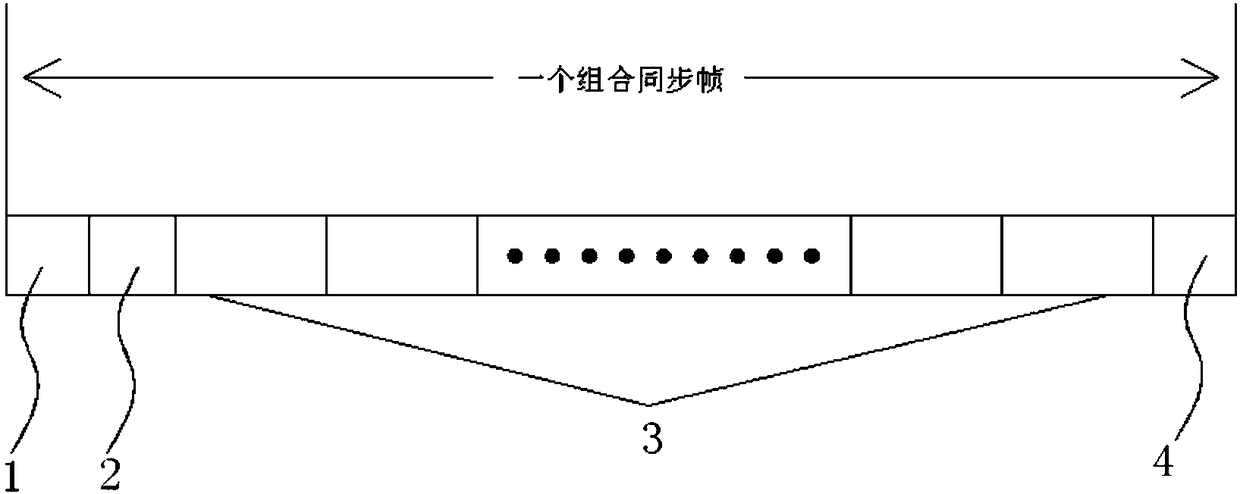

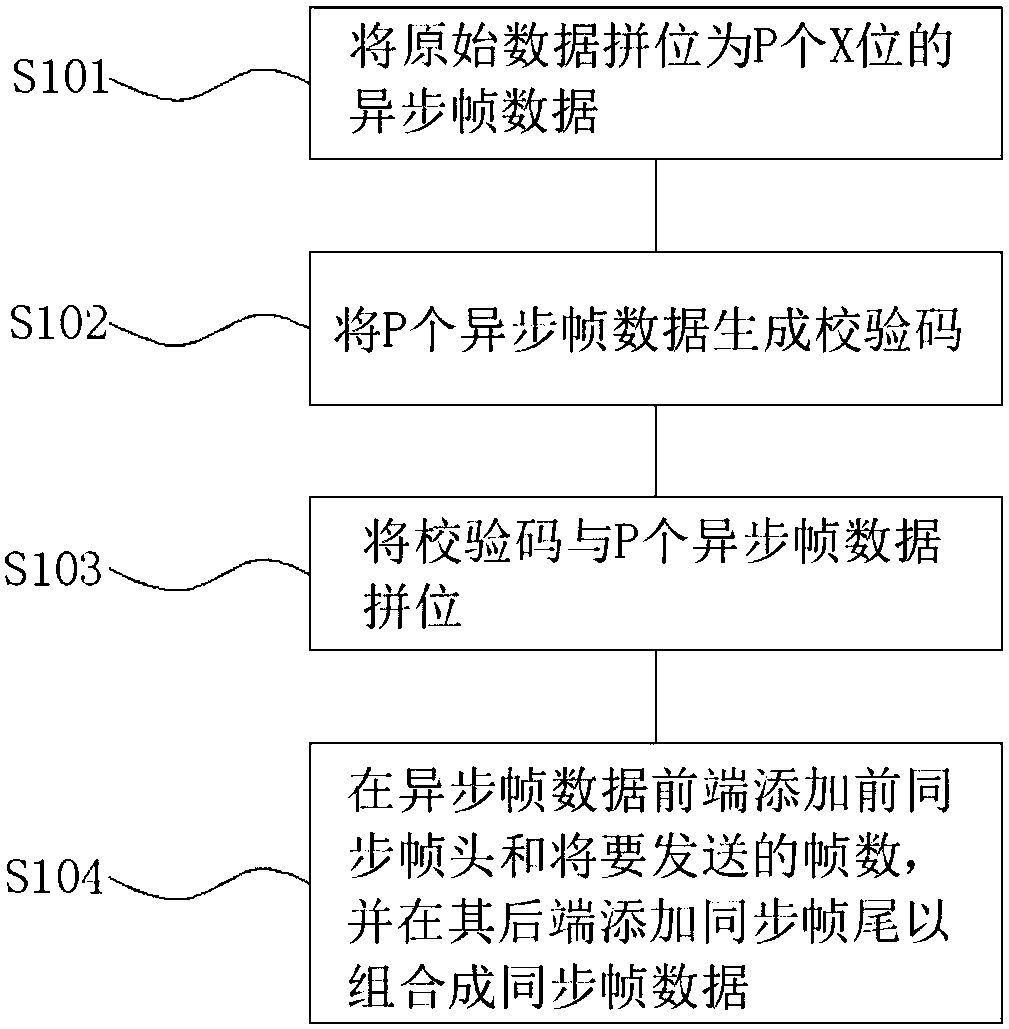

The invention discloses a data transmission protocol method. The data transmission protocol method is used for data transmission between a client and a host computer, and comprises: a step S1 of performing bit merging for original data to obtain a combined synchronous frame, wherein the size of the original data is M bytes, each byte has N bits, and the synchronous frame successively comprises a synchronous frame head, the frame number of asynchronous frames, data bits of the plurality of asynchronous frames and a synchronous frame end from beginning to end; a step S2 of transmitting the combined synchronous frame; a step S3 of receiving the combined synchronous frame; and a step S4 of performing bit decomposition for the asynchronous frame data in the combined synchronous frame to recoverthe original data. Through adoption of the data transmission protocol method of the invention, defects that synchronous serial communication is high in efficiency but short in communication distanceand asynchronous serial communication is long in transmission distance but low in efficiency can be avoided, different asynchronous frame bits are selected, a bit stream can be obtained through automatic merging when data is transmitted, and data bytes can be obtained through automatic decomposition when the data is received; therefore, transmission efficiency is improved in the case of ensuring reliable long-distance transmission.

Owner:南京优米亚信息科技有限公司

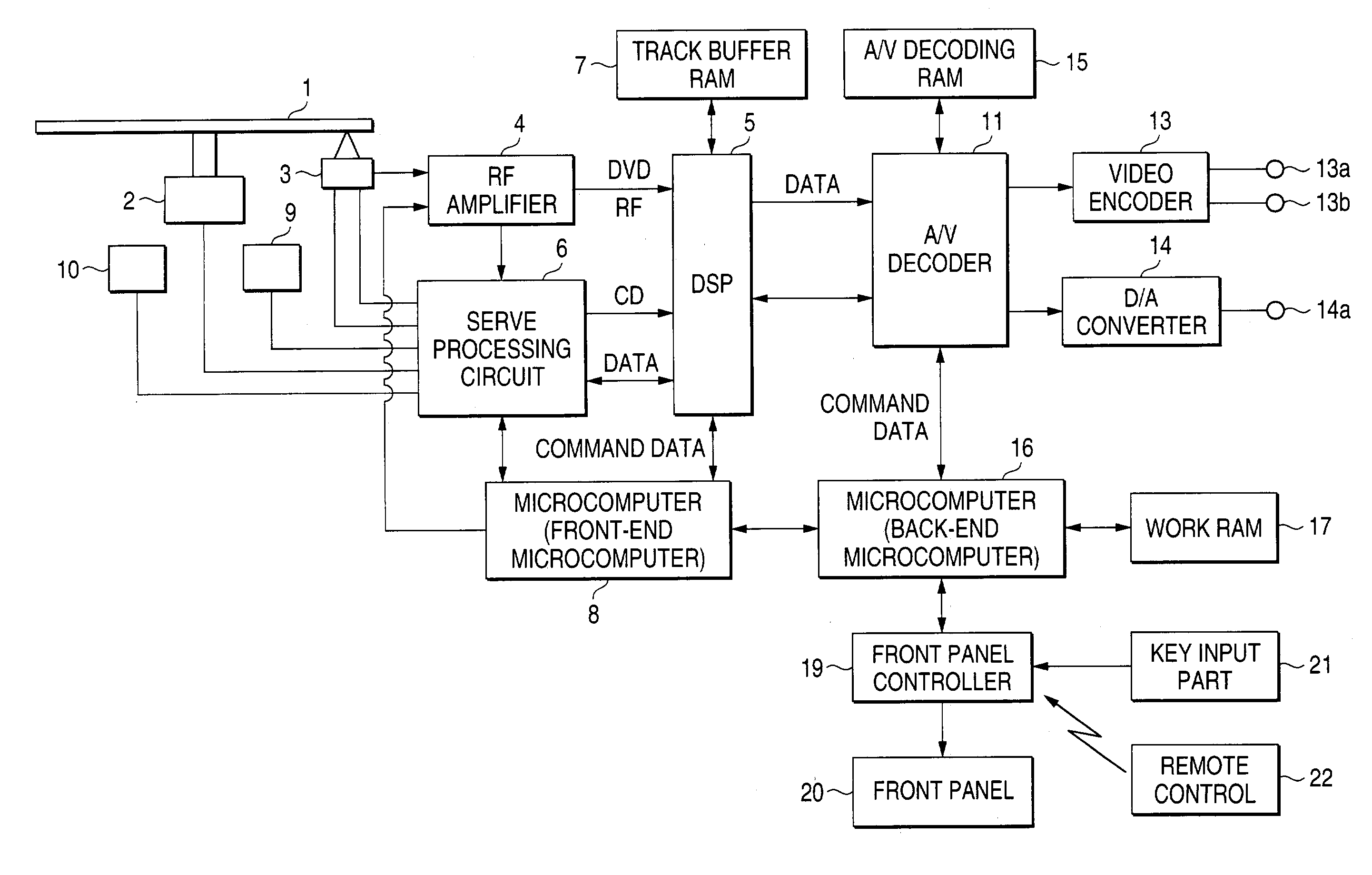

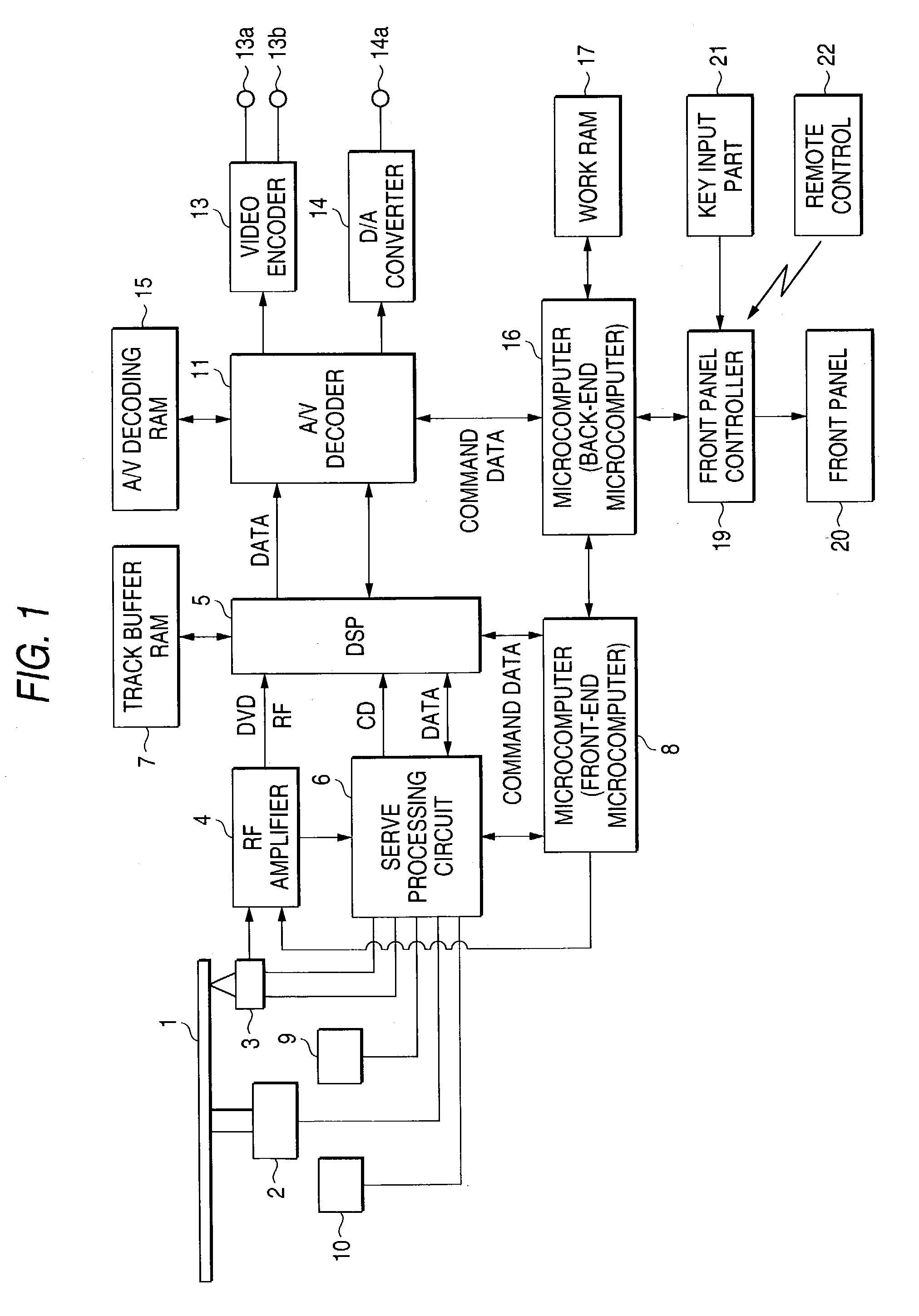

Disk reproducing apparatus

InactiveUS7257742B2Reduce generationMore surelyError prevention/detection by using return channelInput/output to record carriersMicrocomputerByte

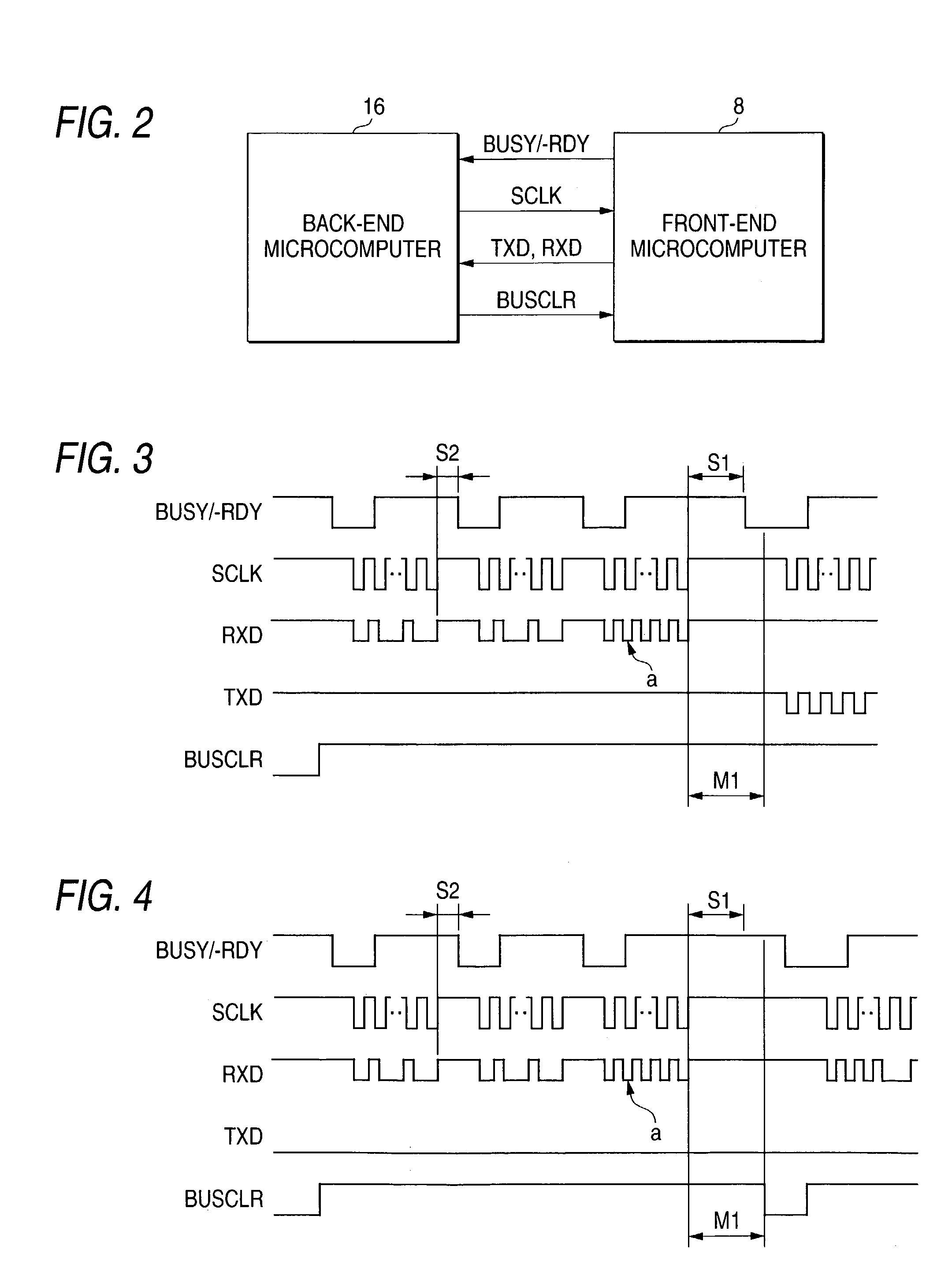

With regard to two-way clock synchronous serial communication conducted between a back-end microcomputer 16 and a front-end microcomputer 8, data is sent from the front-end microcomputer 8 to the back-end microcomputer 16 in a form of responding to data sent from the back-end microcomputer 16 between the back-end microcomputer 16 and the front-end microcomputer 8 and from the sending side, sending target data formed by adding a byte for error detection to a byte which is the original sending target is sent and in the receiving side, when a byte corresponding to the byte for error detection is received, error detection of received data is performed using said byte and when an error is detected in the received data, by providing notification to the effect that a communication error occurrs from the receiving side to the sending side.

Owner:FUNAI ELECTRIC CO LTD

Speed and mileage measuring instrument based on single-chip microcomputer

InactiveCN104006824ALow priceReduce development costsLinear/angular speed measurementNavigation instrumentsMicrocomputerMicrocontroller

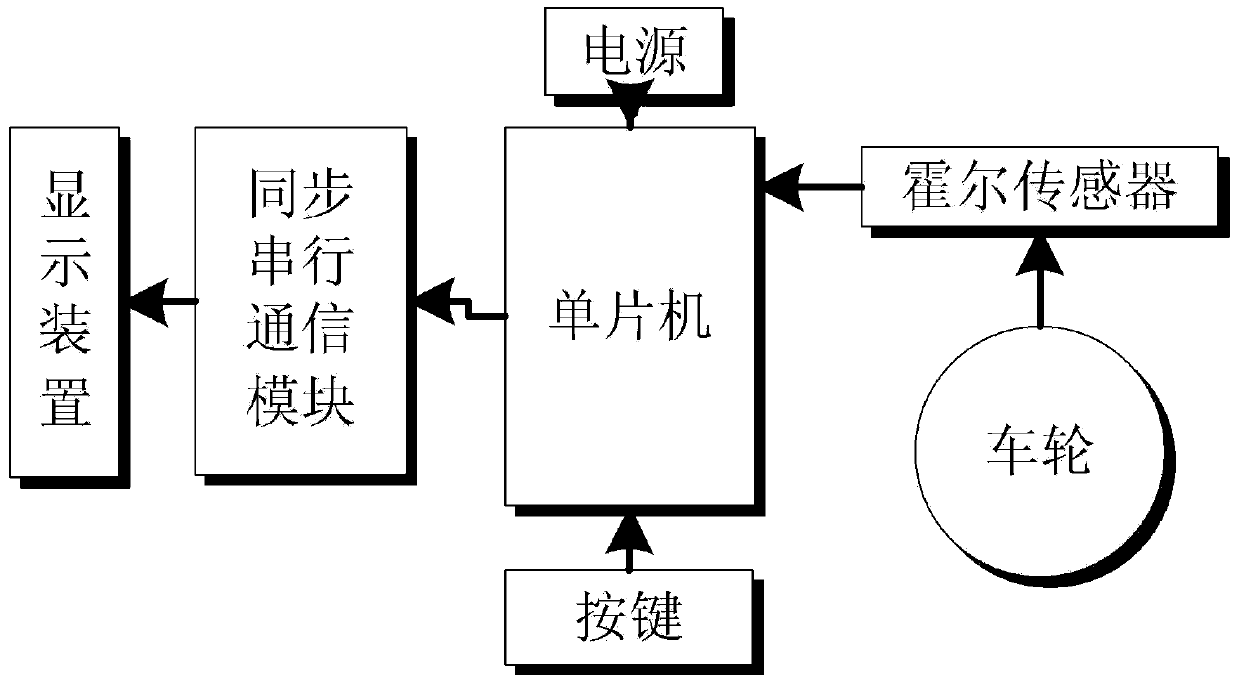

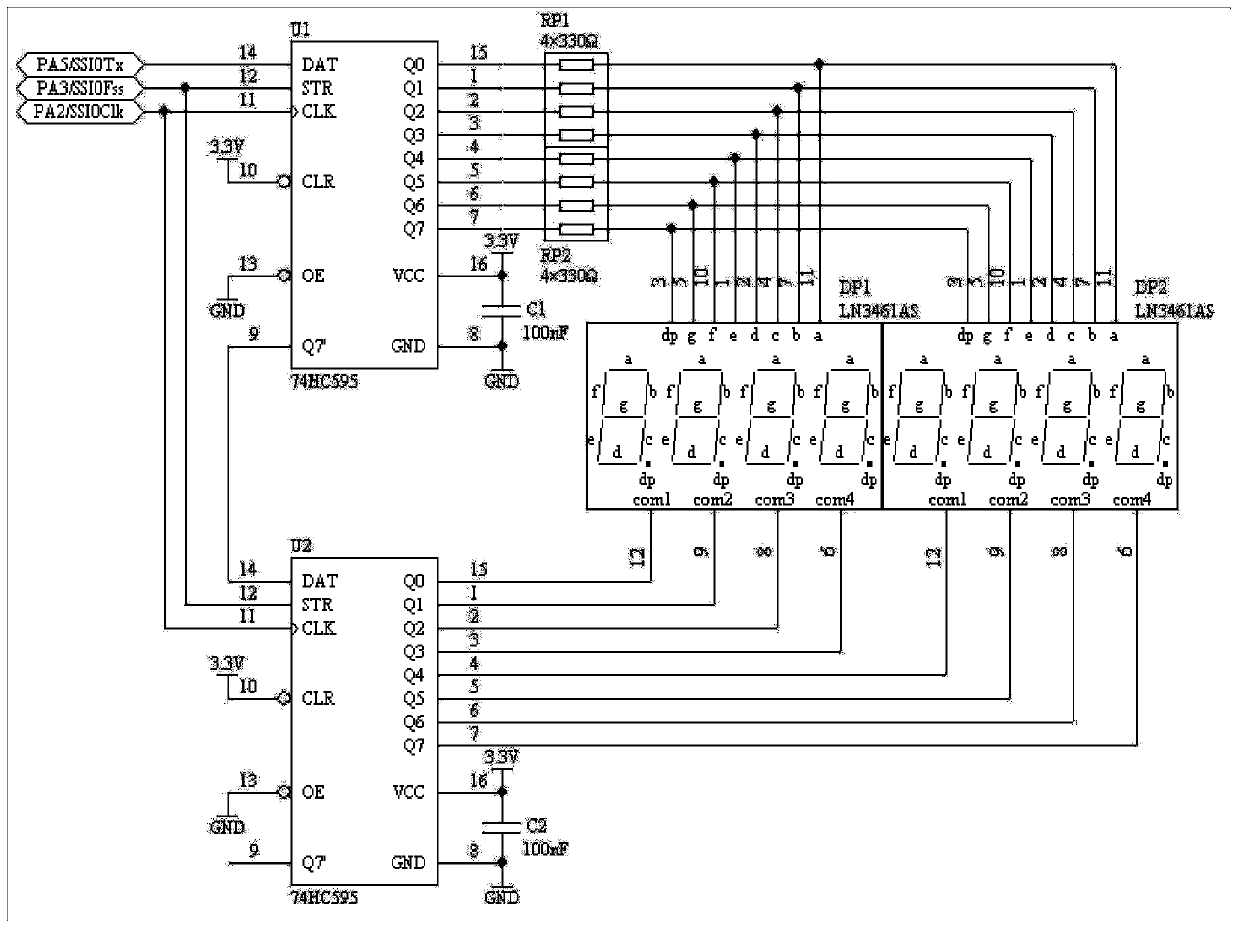

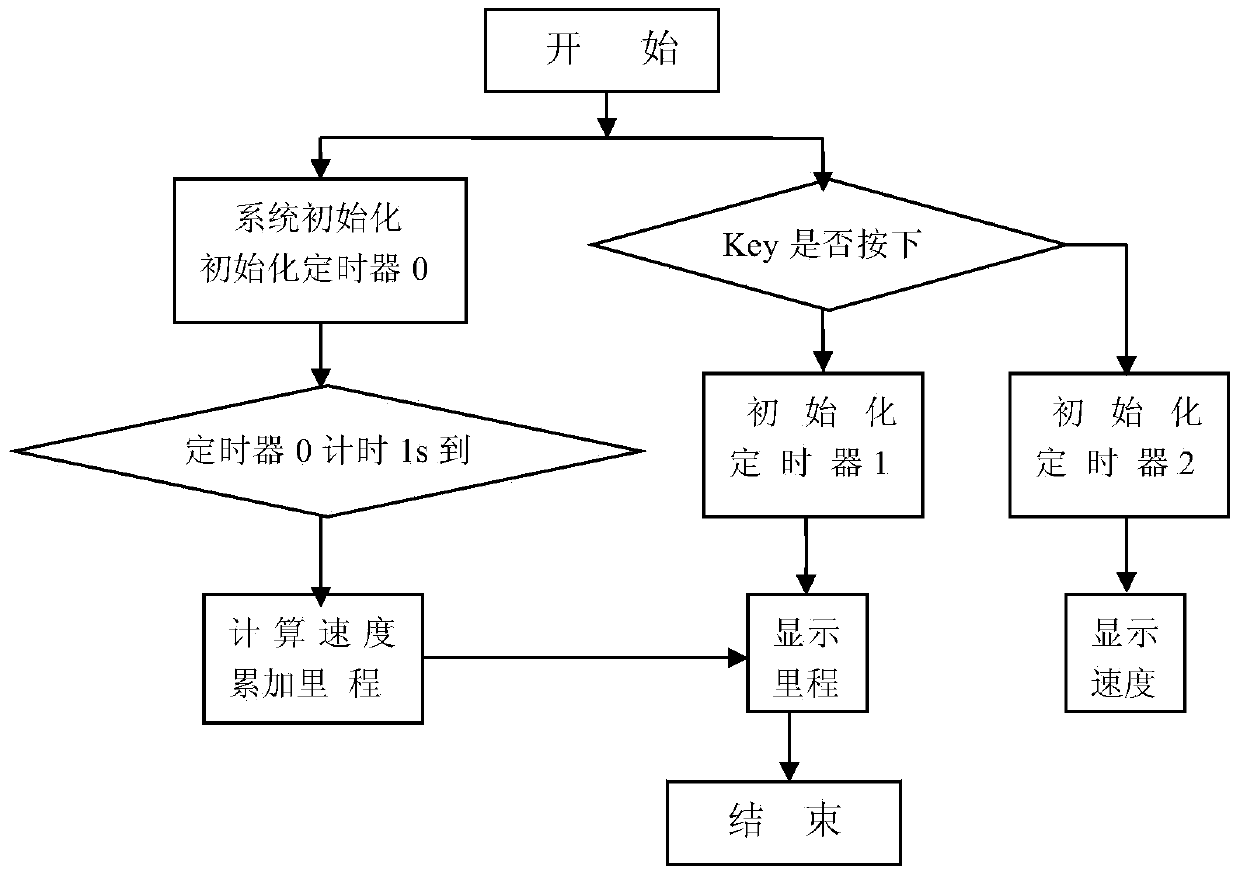

The invention discloses a speed and mileage measuring instrument based on a single-chip microcomputer. The speed and mileage measuring instrument comprises the single-chip microcomputer, a power source, a button, a synchronous serial communication module, a display device and a Hall sensor, the single-chip microcomputer is respectively connected with the power source, the button, the synchronous serial communication module and the Hall sensor, the display device is in communication connection with the single-chip microcomputer through the synchronous serial communication module, and the Hall sensor is arranged on a corresponding frame on a wheel and is used for detecting the number of revolutions of the wheel. The speed and mileage measuring instrument has the advantages of being cheap in adopted material, low development cost, capable of independently forming a system, capable of being directly integrated on a bicycle, an electric bicycle and other vehicles to be used, simple in circuit, and easy to use and popularize within a large range.

Owner:苏州笔画网络技术有限公司

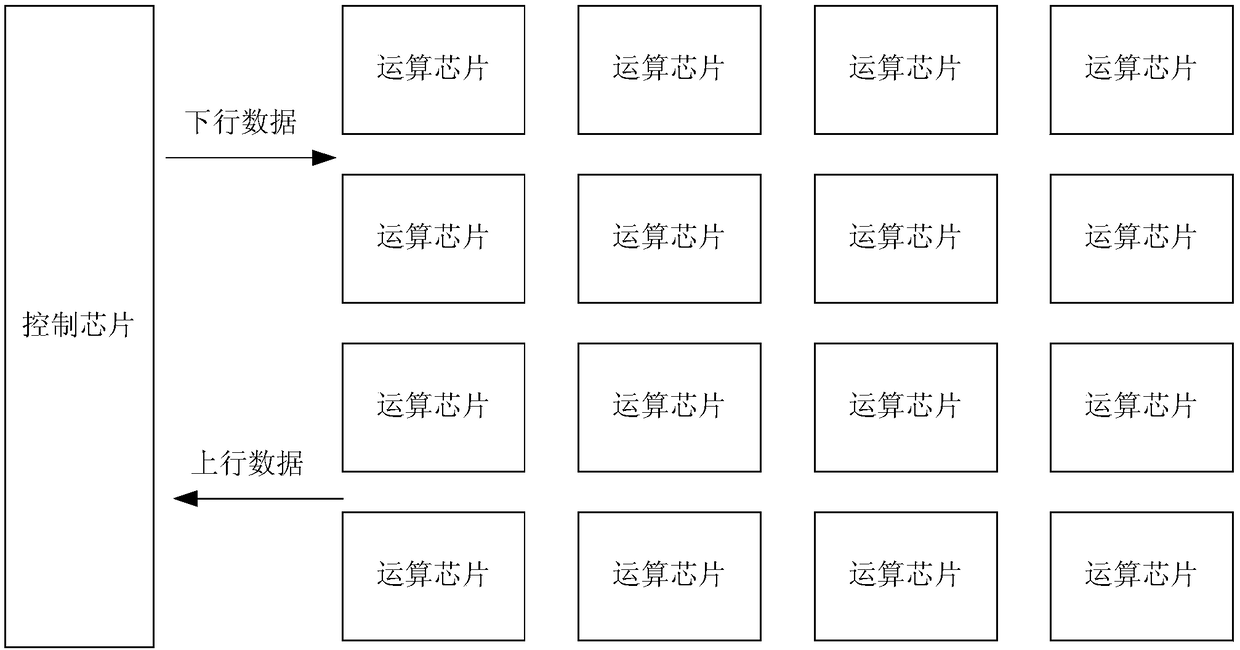

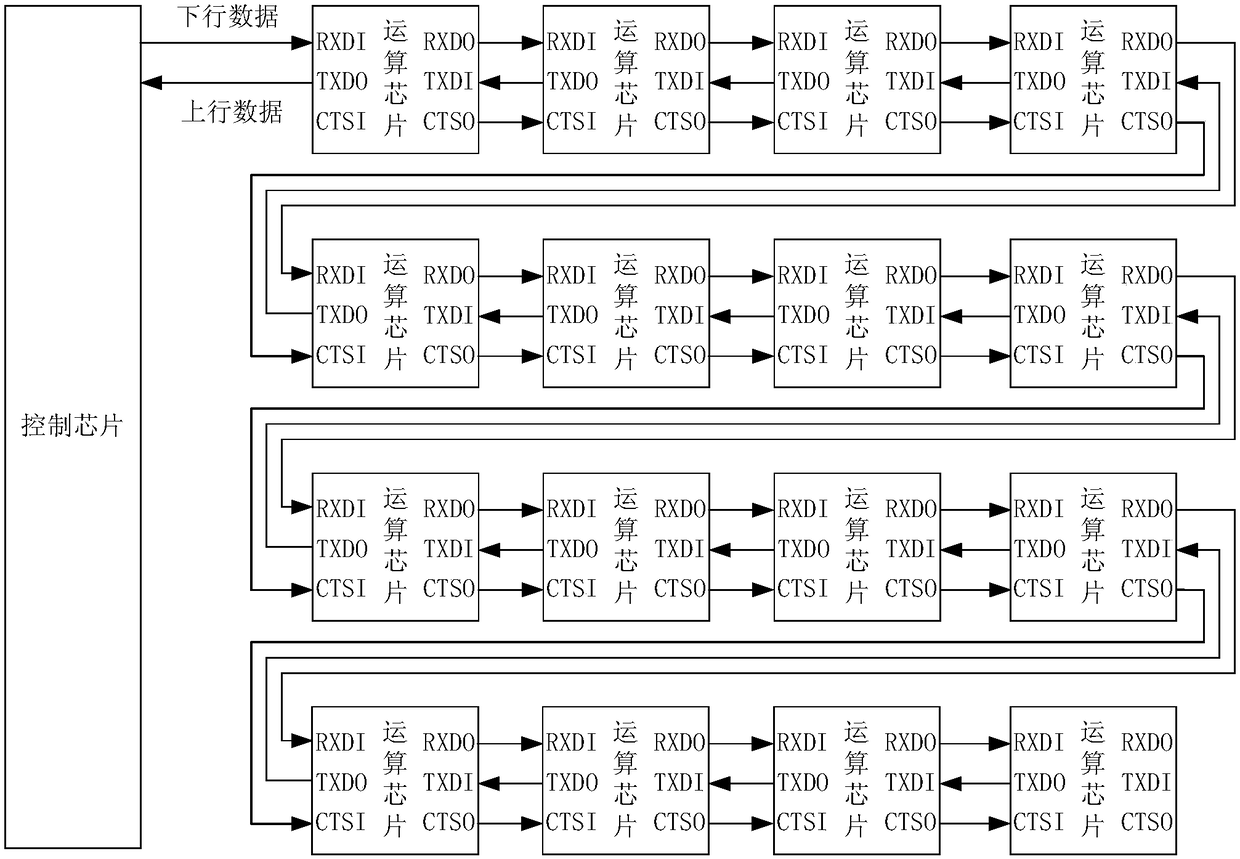

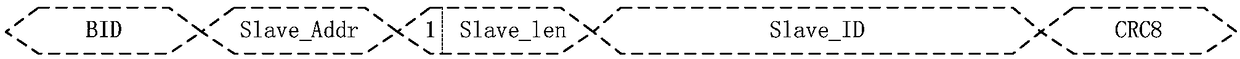

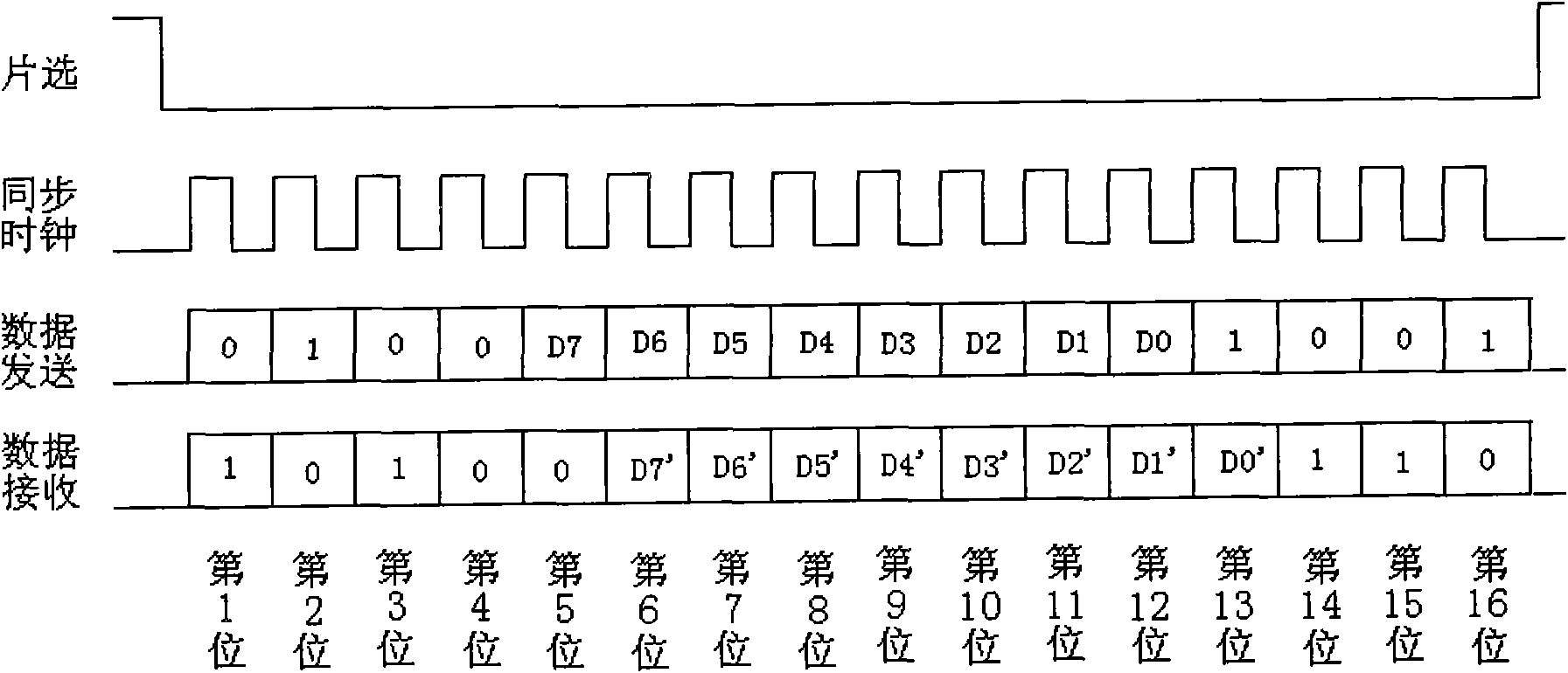

Multi-chip serial communication system

ActiveCN108255756AReduce the difficulty of structural designEliminate mutual interferenceForward error control useElectric digital data processingCommunications systemStaging operation

The invention discloses a multi-chip serial communication system. The multi-chip serial communication system is a multistage operation chip serial communication structure formed through connecting downlink data reception ends, downlink data transmission ends, uplink data reception ends, uplink data transmission ends, flow control reception ends and flow control transmission ends of a plurality ofoperation chips; and a control chip is connected with the 0-stage operation chip to form a serial communication system structure. Transmission of uplink data of the operation chips is coordinated through flow control signals of the flow control reception ends and the flow control transmission ends by utilizing designed downlink and uplink communication protocols. The system provided by the invention is low in line structure design difficulty, so that the production cost is lower; by means of uplink and downlink serial communication protocols, mutual interference between the uplink and downlinkcommunication data of each operation chip is eliminated, so that each operation chip and correctly receive and transmit the data; and meanwhile, two manners of broadcast and unicast are supported, sothat both efficiency and flexibility are considered.

Owner:SHENZHEN MICROBT ELECTRONICS TECH CO LTD

Method for detecting reliability of data communication of synchronous serial communication

InactiveCN102118214ADiscard in timeHigh practical valueError preventionData switching networksAsynchronous serial communicationSynchronous serial communication

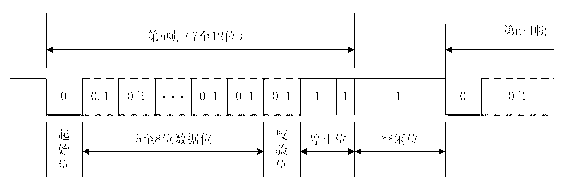

The invention provides a method for detecting reliability of data communication of synchronous serial communication, relates to the technical field of communication detection, and is used for solving the technical problem of the reliability of the data communication of synchronous serial communication. A data frame format used in the method comprises a two-bit header, a two-bit address choice, an eight-bit communication data, a one-bit feature bit, a two-bit flag bit and a one-bit mark bit. The method comprises the following steps: 1) sending the front 13 bits by a data communication initiator according to the format, monitoring a feedback data of a receiving terminal at real time, and comparing; 2) if the result is correct, sending '00'on the two-bit flag bit, and if not, sending '11'; and 3) if a receiver has any fault bit in detection process, abandoning the data and requiring for resending through the last one-bit mark bit, and if any bit is correct, transferring the last one-bit mark bit '0'and receiving the next frame data. The method provided by the invention has the advantages that the operation is simple, the comparison is reliable and the treatment is timely.

Owner:上海申瑞电力科技股份有限公司

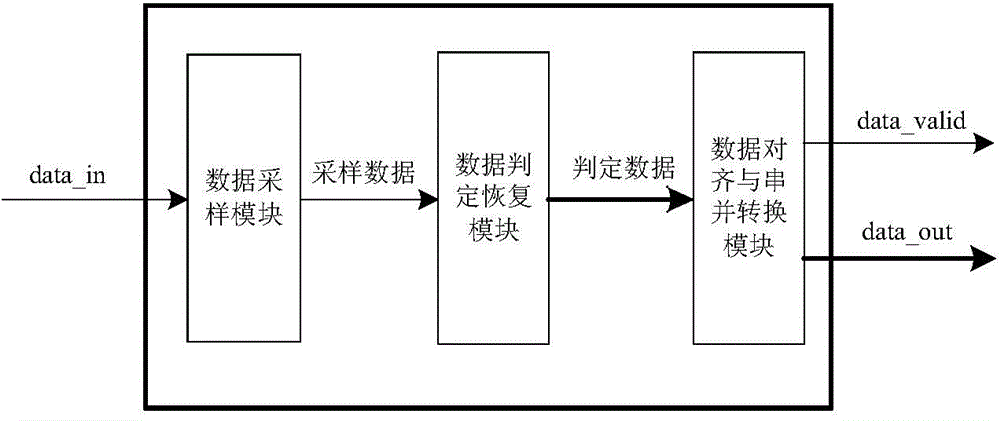

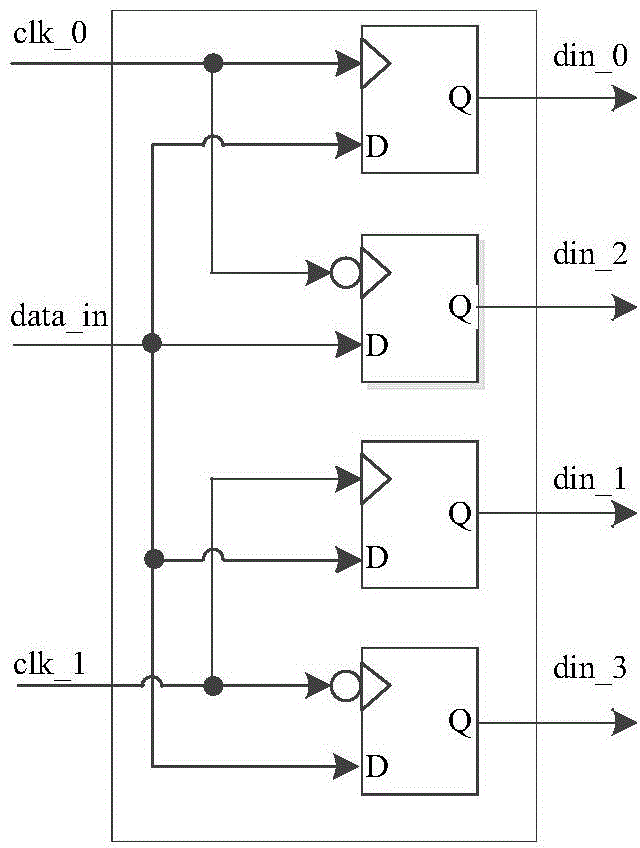

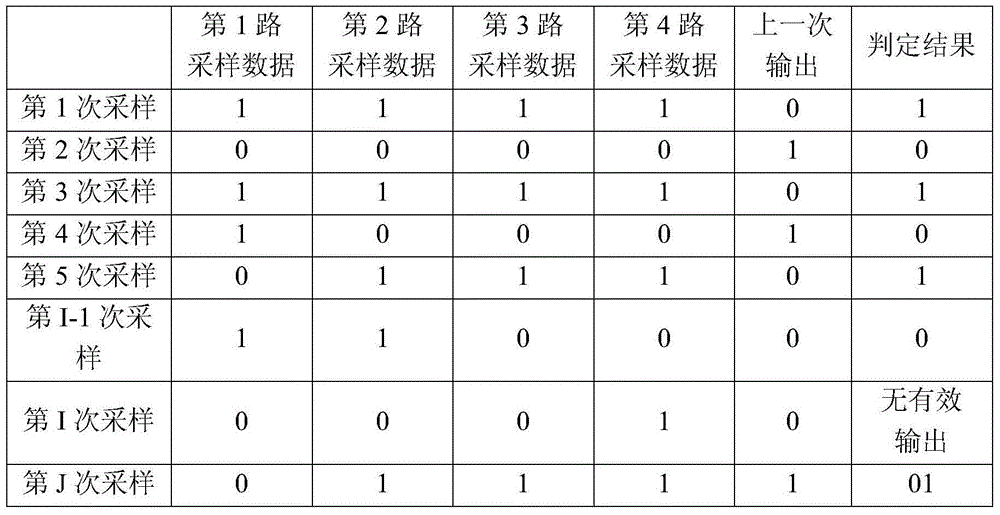

High-speed asynchronous serial communication method

InactiveCN105468561AGuaranteed correctnessEasy to implementElectric digital data processingSerial transferAsynchronous serial communication

The invention discloses a high-speed asynchronous serial communication method. The method comprises the following processing steps of: inputting a high-speed serial signal, performing over-sampling on the input serial signal, sending the sampled data to a data determination recovery module, detecting whether data redundancy or missing exists in the currently input sampled data through the data determination recovery module according to a phase relationship between former output data and clocks, performing operation of redundant data removal, missed data recovery or normal data determination, updating a phase relationship between current output data and clocks, inputting the determined valid data to a data alignment and series-parallel conversion operation module for performing the data frame format alignment operation according to a data communication protocol, and outputting the valid data. Circuit modules related to the method comprise a data sampling module, the data determination recovery module and the data alignment and series parallel conversion operation module. The method belongs to the field of communication; and through adoption of the method, the data sampling error rate caused by clock or signal jittering in a high-speed serial transmission communication system is reduced, the implementation method is simple and the system is reliable.

Owner:山东维航电子科技有限公司

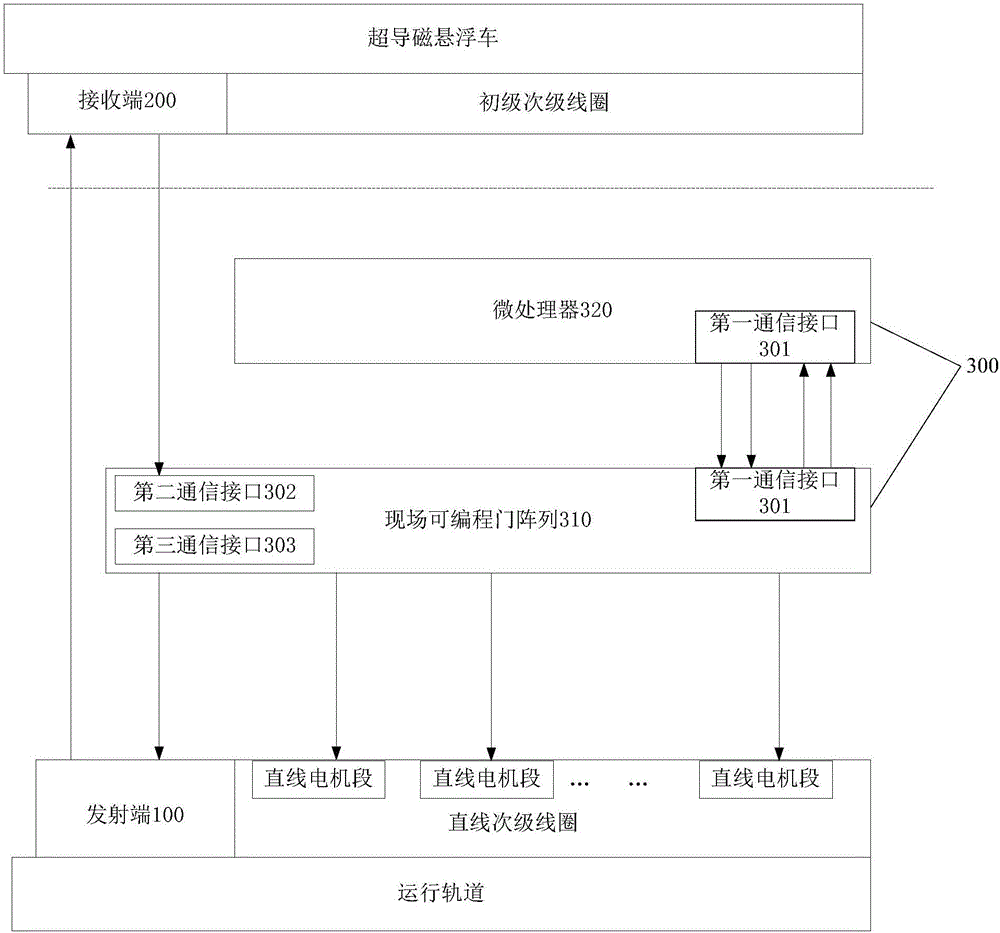

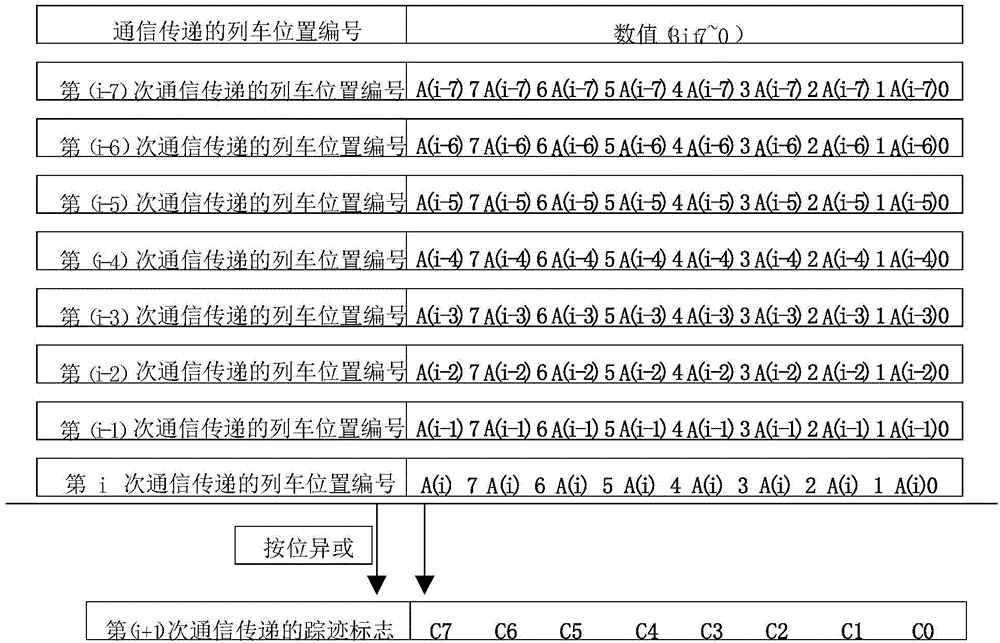

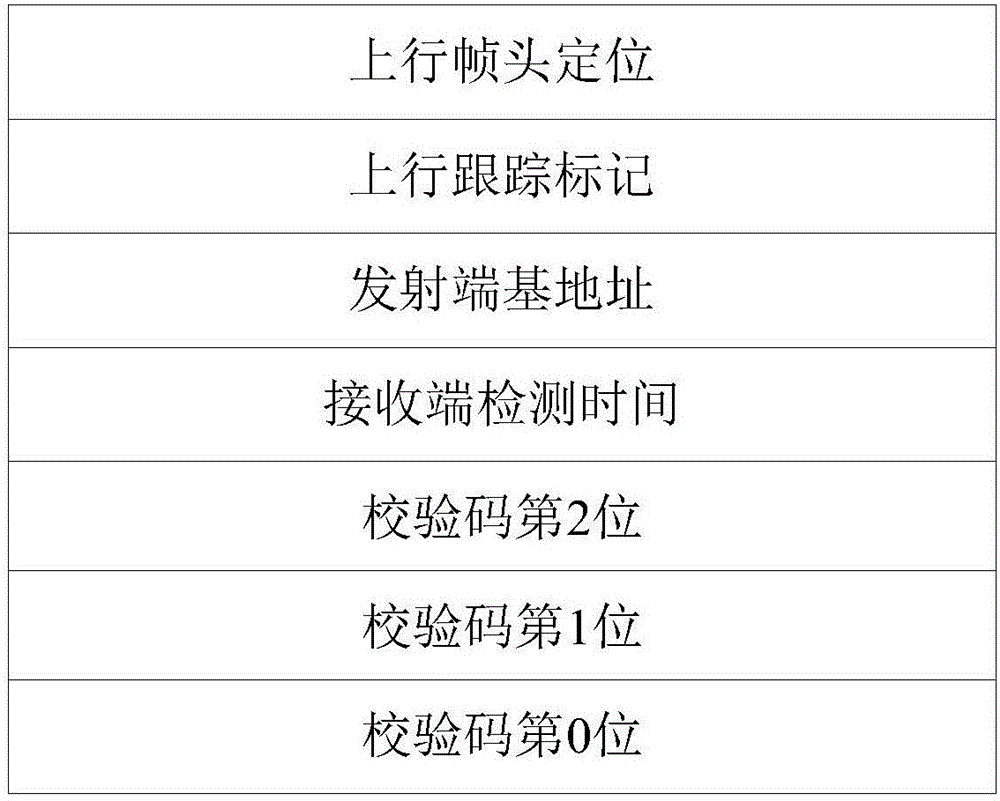

Controller and superconducting maglev vehicle control system provided with same

InactiveCN106740254AFast communication speedGuaranteed uptimeElectric vehicle charging technologyElectric propulsionElectricityControl system

The embodiment of the invention discloses a controller and a superconducting maglev vehicle control system provided with the same. The controller is applied to the superconducting maglev vehicle control system and comprises a transmitting terminal and a receiving terminal. The transmitting terminal is installed on the side of straight line primary coils on a superconducting maglev vehicle operation track and is used for transmitting detection signals. The receiving terminal is installed on the side of linear motor secondary coils on a superconducting maglev vehicle and is used for receiving the detection signals and converting the detection signals into electrical signals. The controller comprises a field programmable gate array and a microprocessor and is used for controlling the operation state of the superconducting maglev vehicle according to the electrical signals so that real-time communicate between the field programmable gate array and the microprocessor can be conducted, the communication speed between the field programmable gate array and the microprocessor is increased, accordingly the processing speed of the controller is increased, and operation security of the superconducting maglev vehicle at high speed is guaranteed.

Owner:SOUTHWEST JIAOTONG UNIV

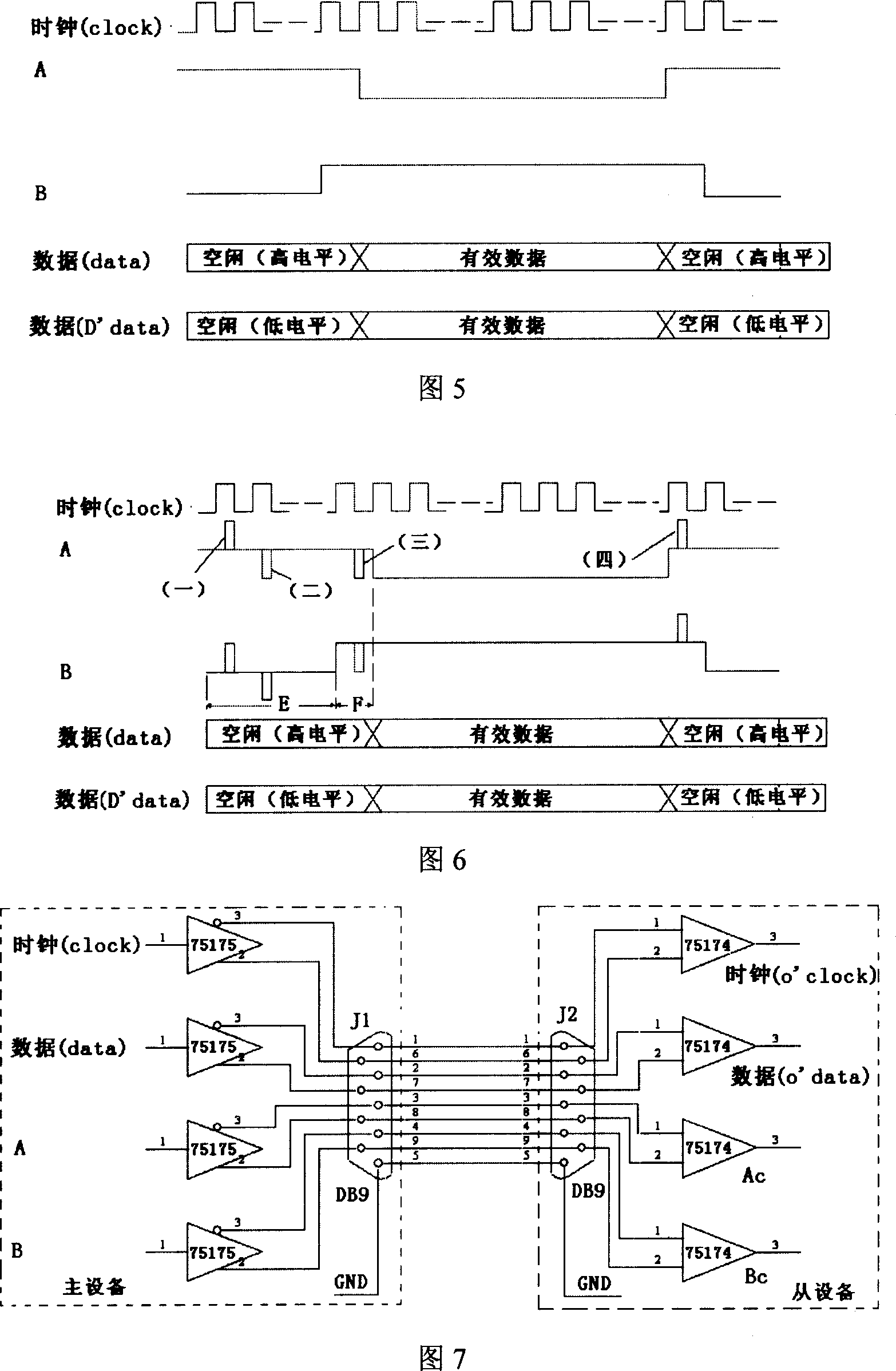

RS485 character-oriented anti-interference device against idle synchronous serial communication bus

ActiveCN1964245AImprove reliabilityImprove efficiencyError preventionInterference resistanceAsynchronous serial communication

The RS485 orientated-character anti-interference device for free synchronous serial communication bus employs a primary device to send data, a secondary device to receive data, the RS485 standard interface as physical interface, and the synchronous serial communication protocol. This invention adds two path control signal and takes simple logic combination to inhibit error synchronizing and receiving, and thereby improves communication efficiency and anti-interference capacity.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

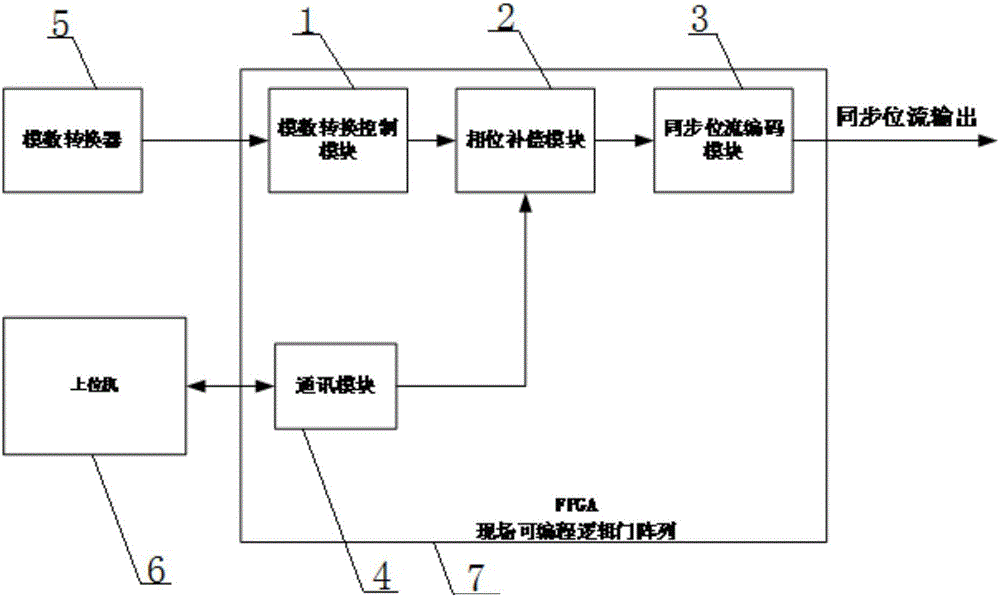

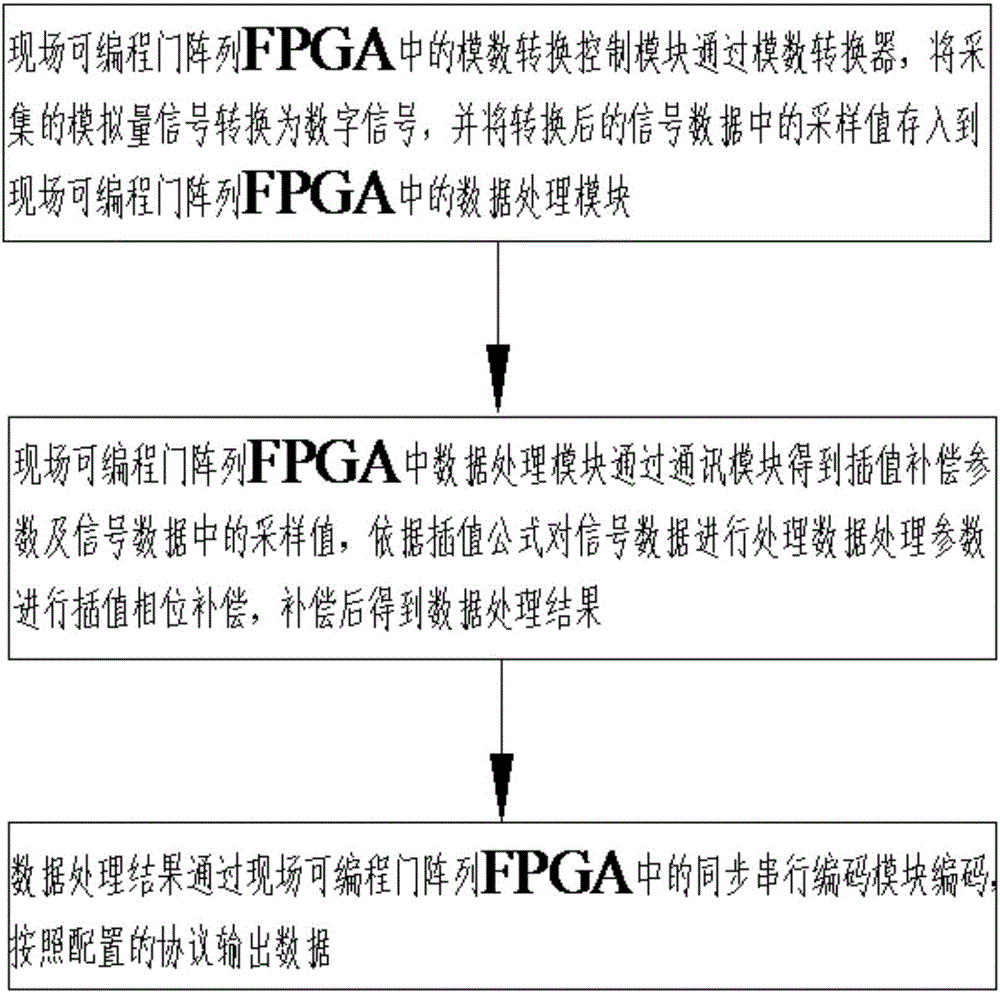

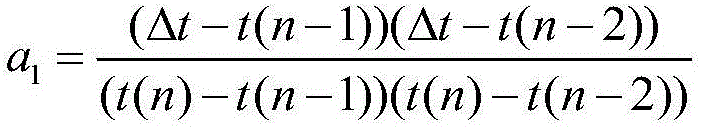

Data processing method of electronic transformer under synchronous serial coding

ActiveCN106353550ARelieve stressImprove the phase deviation of different channelsVoltage/current isolationTransformerAnalog-to-digital converter

The invention discloses a data processing method of electronic transformer under synchronous serial coding, the field programmable gate array comprises an analog-digital conversion control module under successive connection, a data processing module, a synchronous serial coding module and a communication module, the method comprises the following steps: the analog-digital conversion control module converts the collected analog quantity signal into the digital signal via the analog-digital converter, and stores the sampling value in the converted signal data to the data processing module; the host computer generates the interpolation compensation parameter based on the data processing parameter; the communication module receives the interpolation compensation parameter generated by the host computer; processing the signal data according to the interpolation formula, and getting the data processing result; outputting the data processing result through the synchronous serial coding, the coding protocol can be configured. The data processing method of electronic transformer under synchronous serial coding achieves accuracy of different channel data with phase coincidence, and reduces the back-end data processing pressure.

Owner:BEIJING SIFANG JIBAO AUTOMATION +2