FPGA program multi-image loading method based on ARM

A multi-mirror and program technology, applied in the direction of program loading/starting, program control devices, etc., can solve the problem of slow switching speed, achieve the effect of fast switching speed and improve product production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

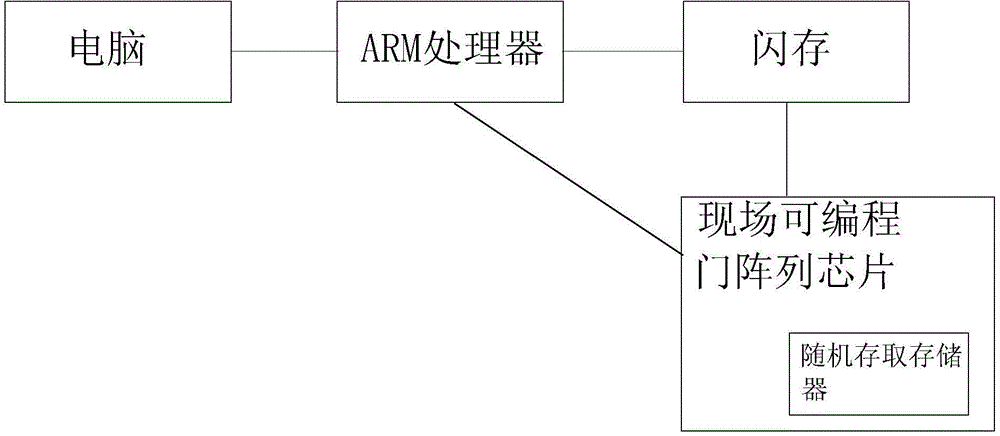

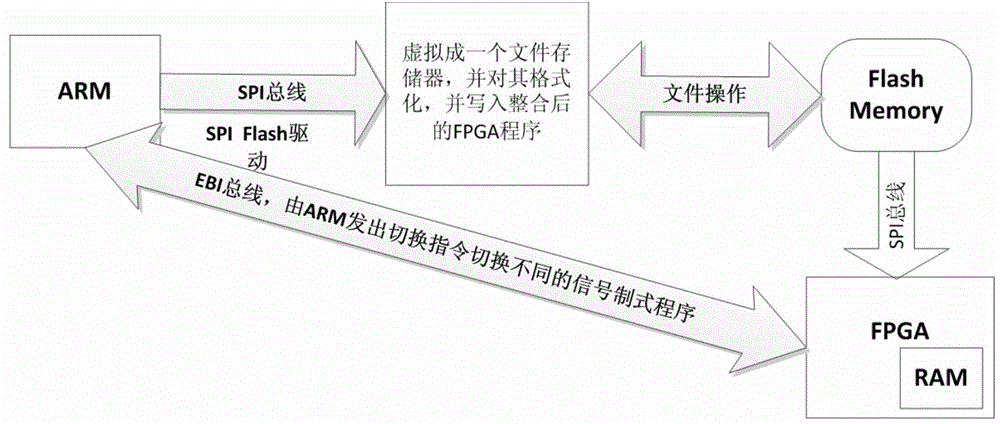

[0019] The hardware environment of the FPGA program multi-image loading method based on ARM of the present invention, such as figure 1 Described it comprises: computer, ARM processor, flash memory, field programmable gate array chip and the random access memory of field programmable gate array chip, described computer is connected ARM processor, and ARM processor passes serial peripheral interface bus To connect the flash memory, the ARM processor is also connected to the field programmable gate array chip through the external bus interface, and the flash memory is connected to the field programmable gate array chip through the serial peripheral interface bus.

[0020] FPGA program multi-image loading method based on ARM of the present invention, it comprises the steps:

[0021] Step 1: Pack the FPGA files of different signal formats through th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More