Single-chip microcomputer

a single-chip microcomputer and chip technology, applied in the field of single-chip microcomputers, to achieve the effect of multiple functions and high performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

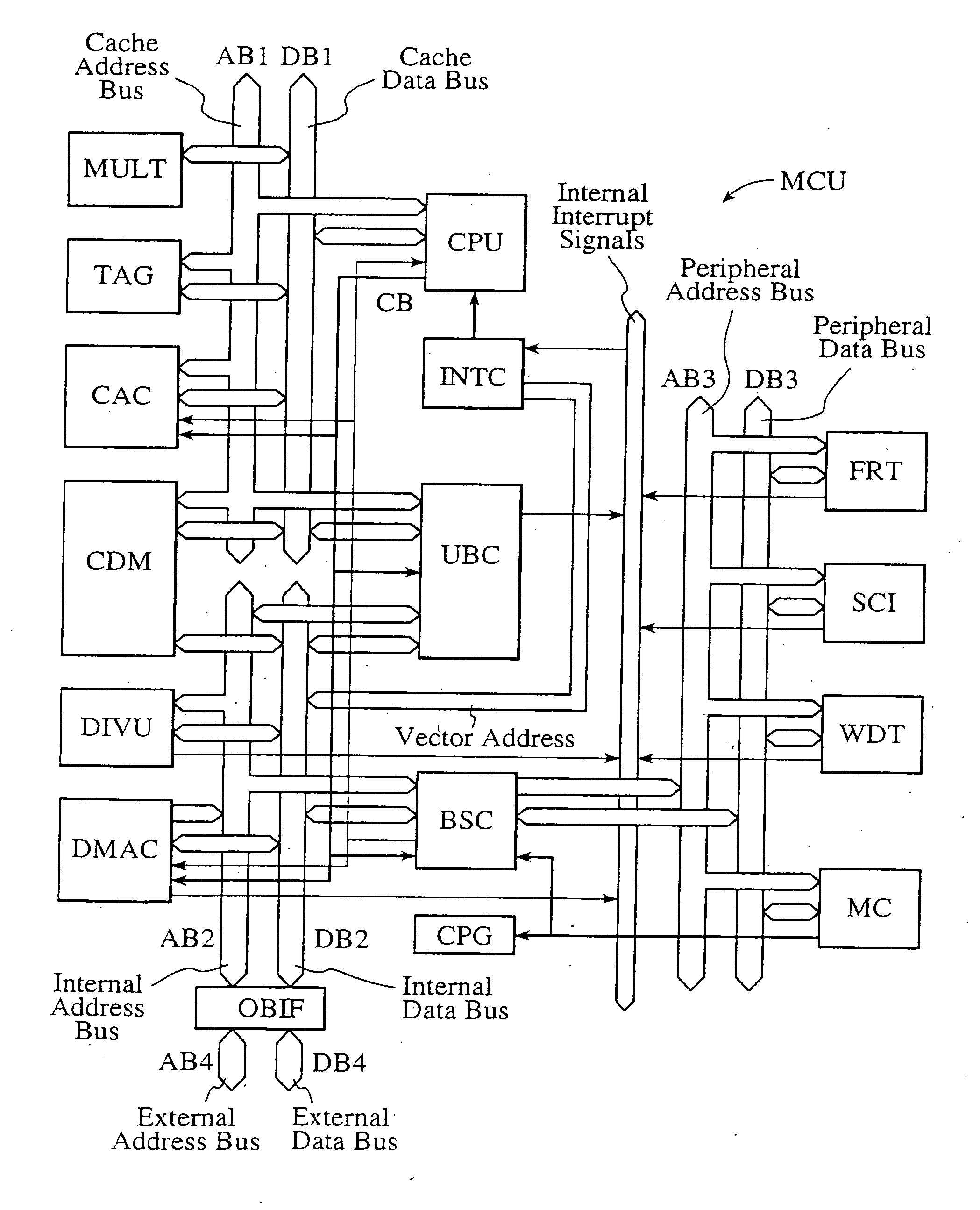

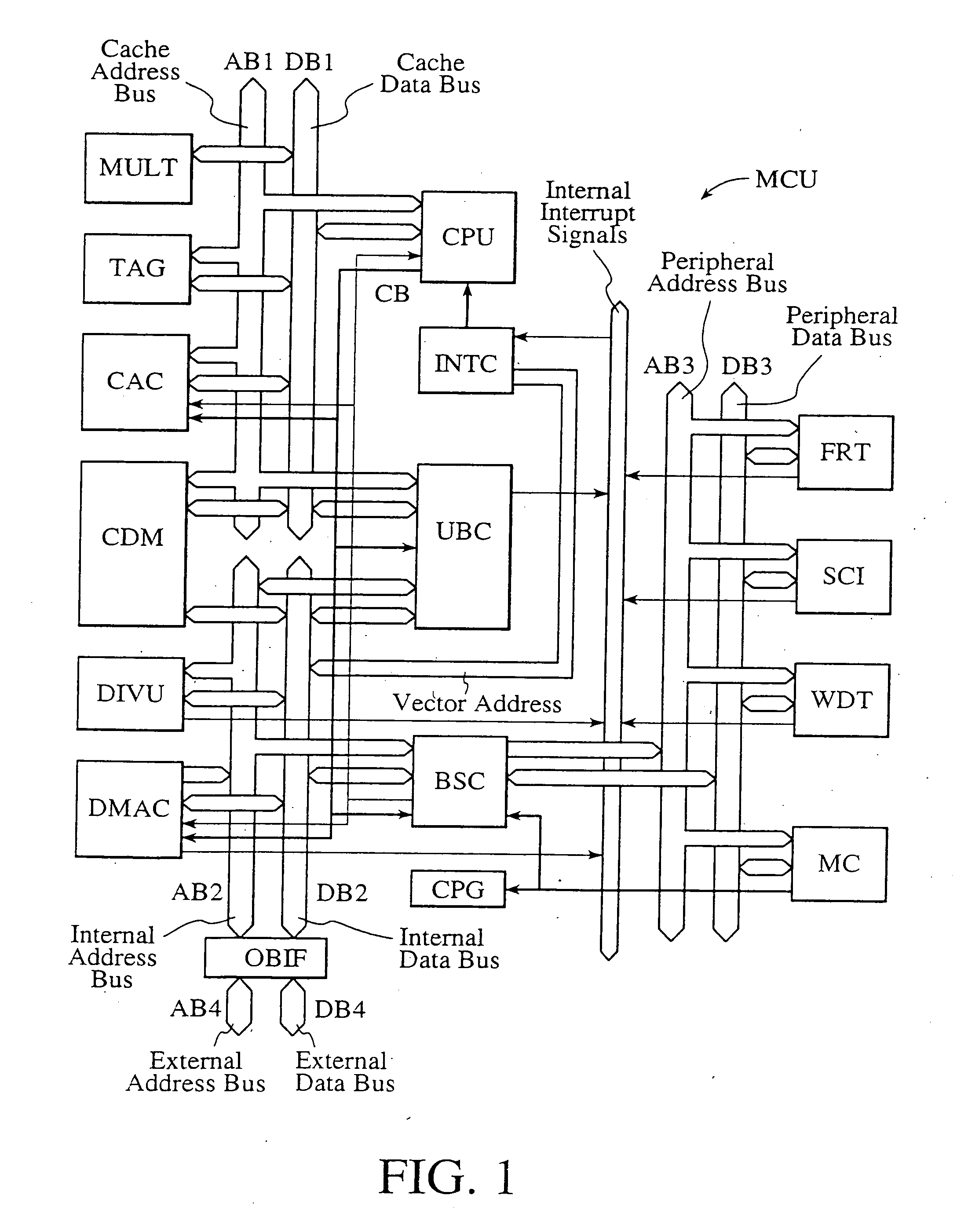

[0086]FIG. 1 is a block diagram showing one embodiment of a single-chip microcomputer or microprocessor MCU according to the present invention. The individual circuit blocks of FIG. 1 are formed over a single substrate of single-crystalline silicon by the well-known CMOS (i.e., Complementary MOS) semiconductor integrated circuit manufacturing technology.

[0087]The single-chip microcomputer MCU in this embodiment is so directed toward the new generation, although not especially limitative thereto, as to realize high-performance arithmetic operations thereby to integrate the peripheral devices necessary for the system construction by a RISC (i.e., Reduced Instruction Set Computer) type central processing unit CPU and to realize a low power dissipation indispensable for applications to portable devices.

[0088]The central processing unit CPU has a set of the RISC type instructions and can improve the instruction executing speed drastically because a fundamental instruction is subjected to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More