Error correction method for dynamic refreshing of ROM (read only memory) mapping zone in FRGA (field programmable gate array)

An error correction method and dynamic technology, applied in the direction of responding to the generation of errors, redundant codes for error detection, etc., can solve problems such as limited applications, large resource usage, etc., and achieve the effects of easy analysis, simple structure, and reduced usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

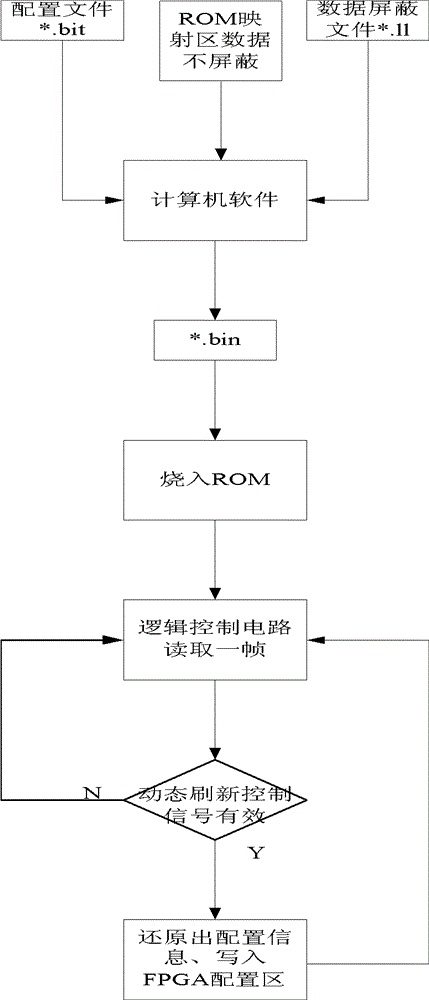

[0040] The present invention divides the data in Xilinx FPGA configuration file into two kinds:

[0041] 1) Shield data. Shielded data is data that is not allowed to be repeatedly written into the configuration area when the internal logic of the FPGA is running, that is, data that is prohibited from being dynamically refreshed. It corresponds to Xilinx FPGA configuration instructions or RAM resources of the Xilinx FPGA internal hardware structure. When the FPGA is working, the internal logic will operate these RAM resources, and writing to these RAM resources during dynamic refresh will change the operating state of the internal logic.

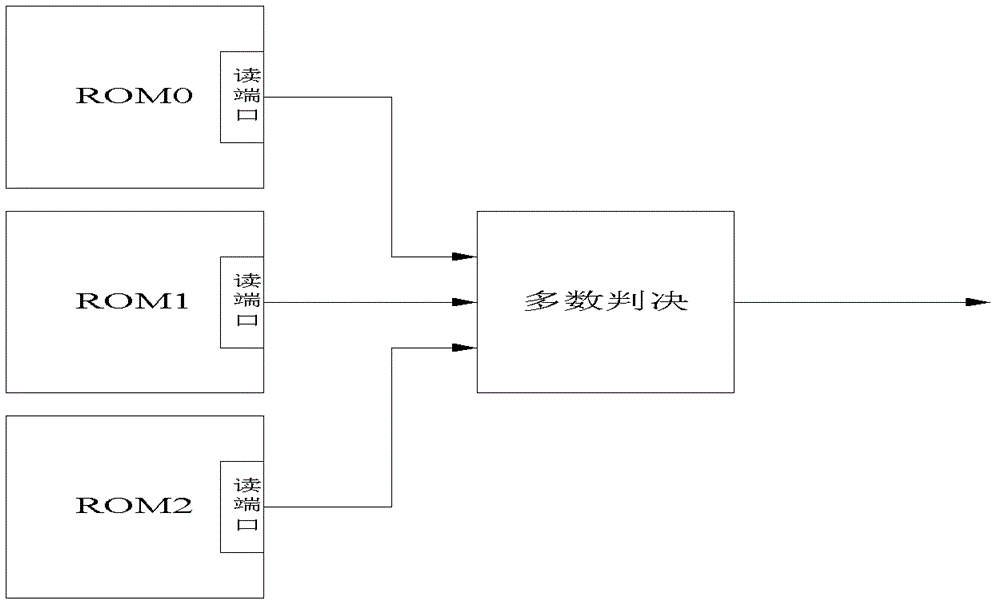

[0042] Through analysis, it is found that for the ROM mapping area instantiated from RAM, although it is essentially a RAM resource, the ROM mapping area is used to store fixed data, and these data can and should be dynamically refreshed to ensure that the data in the ROM mapping area The correctness, and refreshing the ROM mapping area will...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More