Efficient method and computer program for modeling and improving static memory performance across process variations and environmental conditions

a static memory and environmental condition technology, applied in probabilistic cad, digital storage, instruments, etc., can solve the problems of critical limitations, predicted to become even more critical limitations, and increasingly subject to variability, so as to increase the yield of devices, reduce processing power requirements, and increase analysis speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

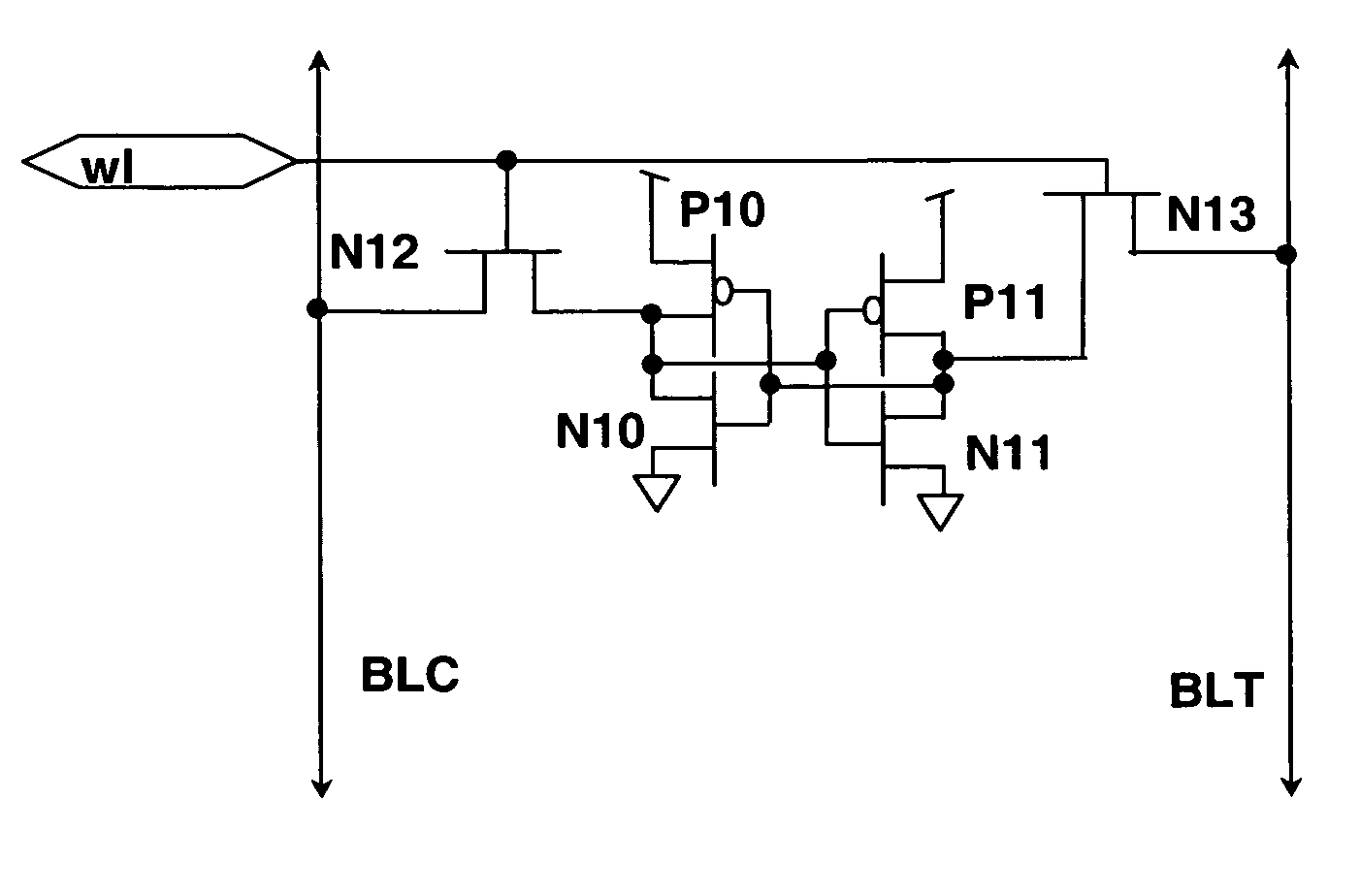

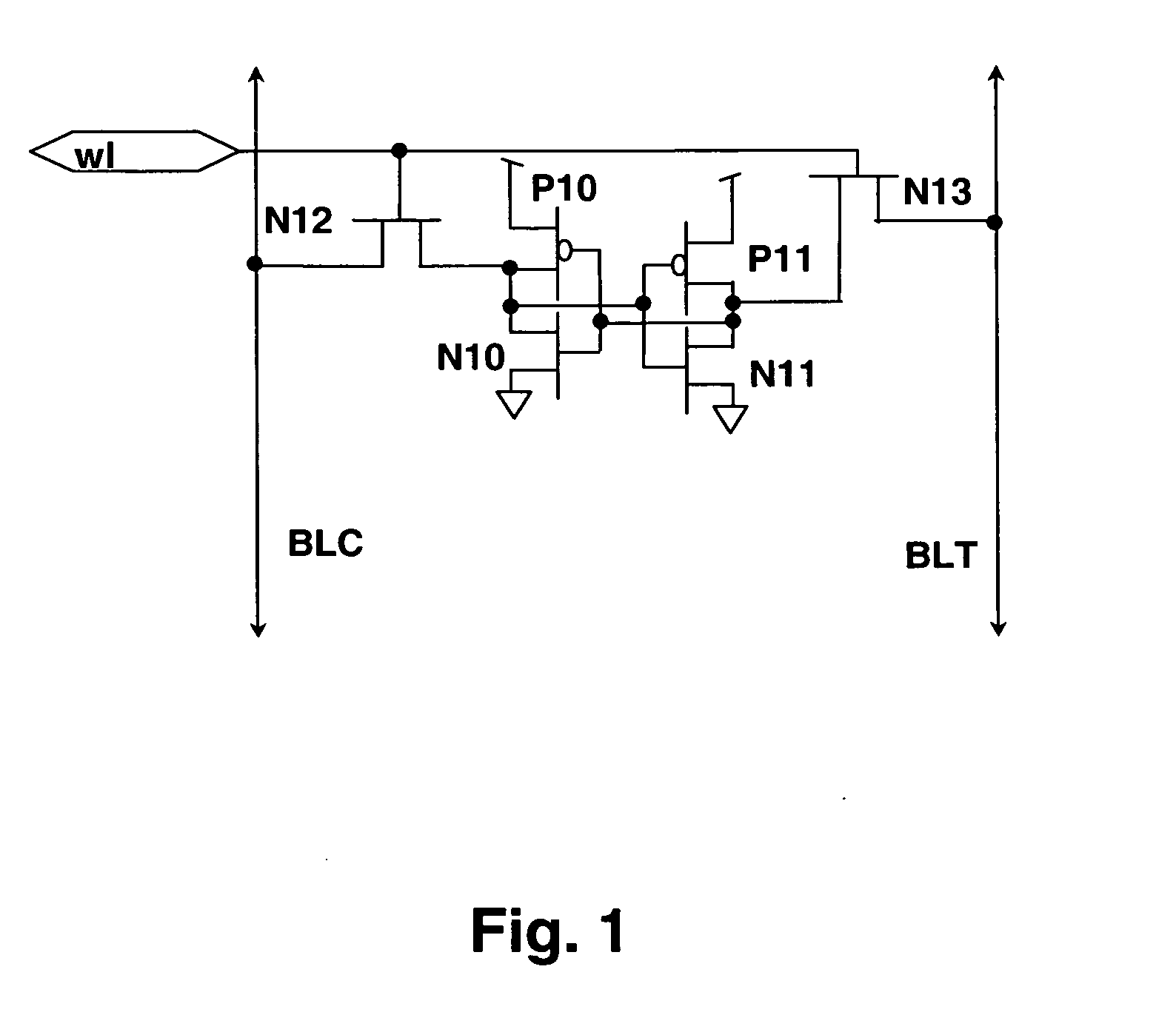

[0023] With reference now to the figures, and in particular with reference to FIG. 1, a memory cell that can be modeled by a method in accordance with an embodiment of the invention is shown. Transistors P10, N10, P11 and N11 form a cross-coupled static latch that provides the storage of a value in the cell. Transistors N12 and N13 provide for access to the value in response to a wordline select signal WL. Bitlines BLT (true bitline) and BLC (complement bitline) couple all cells in a column, so that when a row is selected by signal WL, only one row cell from each column is exposed to the memory logic. For a write operation, bitlines BLC and BLT are charged to voltages corresponding to the desired state of the memory cell and WL is activated (pulsed), setting the state of the latch formed by transistors P10, N10, P11 and N11. For a read operation, the bitlines BLC and BLT are previously charged to opposite state predetermined voltages (generally Vdd and ground), and to commence the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More