Skew detection and skew elimination regulation circuit for on-chip clock system of VLSI (very large scale integrated circuit)

A technology for adjusting circuits and clock systems, applied in pulse shaping, pulse description, etc., can solve the problems of incompatibility with digital integrated circuit design process, low flexibility, complex circuits, etc., and achieve easy programming, good flexibility, logic simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

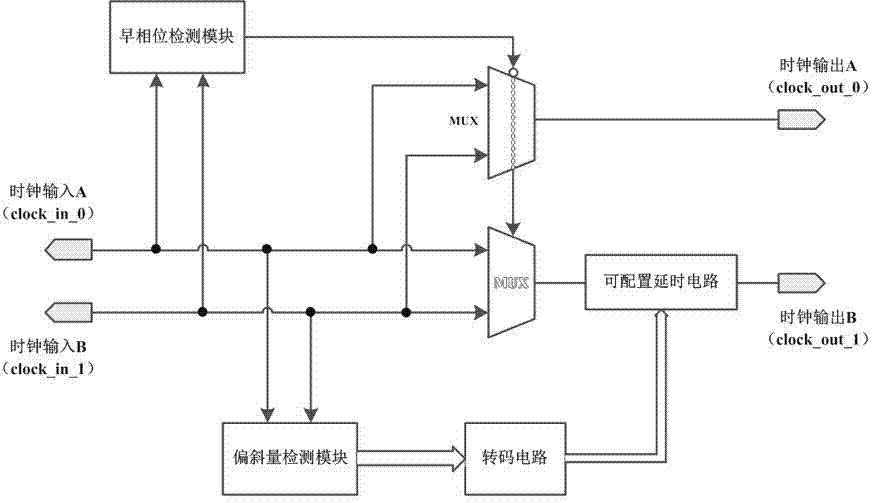

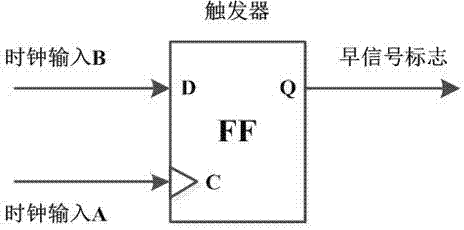

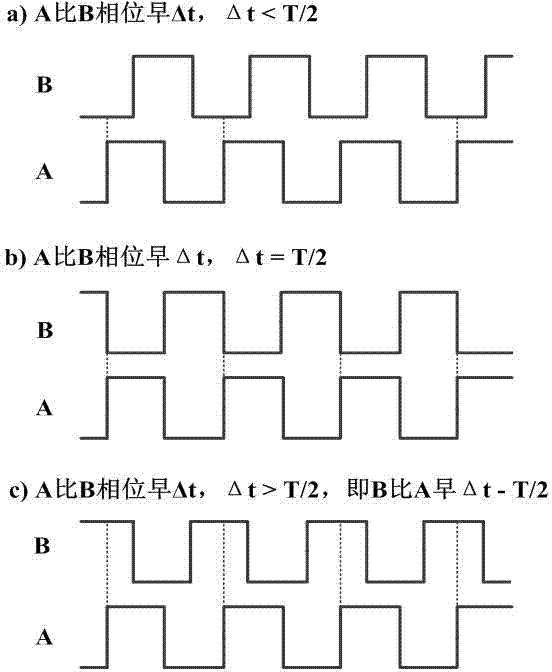

[0023] When there are two clock inputs, such as clock input A and clock input B, the early phase detection module is used to detect the sequence of the two clock phases. It is actually a flip-flop, and the clock B signal is triggered by the rising edge of clock input A. to sample the output from image 3 As shown in the figure, it can be seen that the flip-flop output '1' indicates that clock B is earlier than clock A, and the output '0' indicates that clock A is earlier than clock B, and the output signal is sent to two alternative MUXs. Among them, MUX_0 is used to select a clock with a later phase, and MUX_1 is used to select a clock with an earlier phase.

[0024] The two input clocks are sent to the offset detection module while being sent to the early phase detection module. The two clocks A and B are first generated by a NOT gate and an AND gate. Signal, which is a pulse sequence whose width is equal to the skew of clock A and clock B, and detecting the pulse width is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More