Spread spectrum clock generating circuit with power-saving control

A technology for generating circuits and spreading spectrum, applied in the direction of delay line pulse generation, electrical components, pulse processing, etc., can solve the problems of not too high input clock signal frequency, high circuit cost, high circuit complexity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

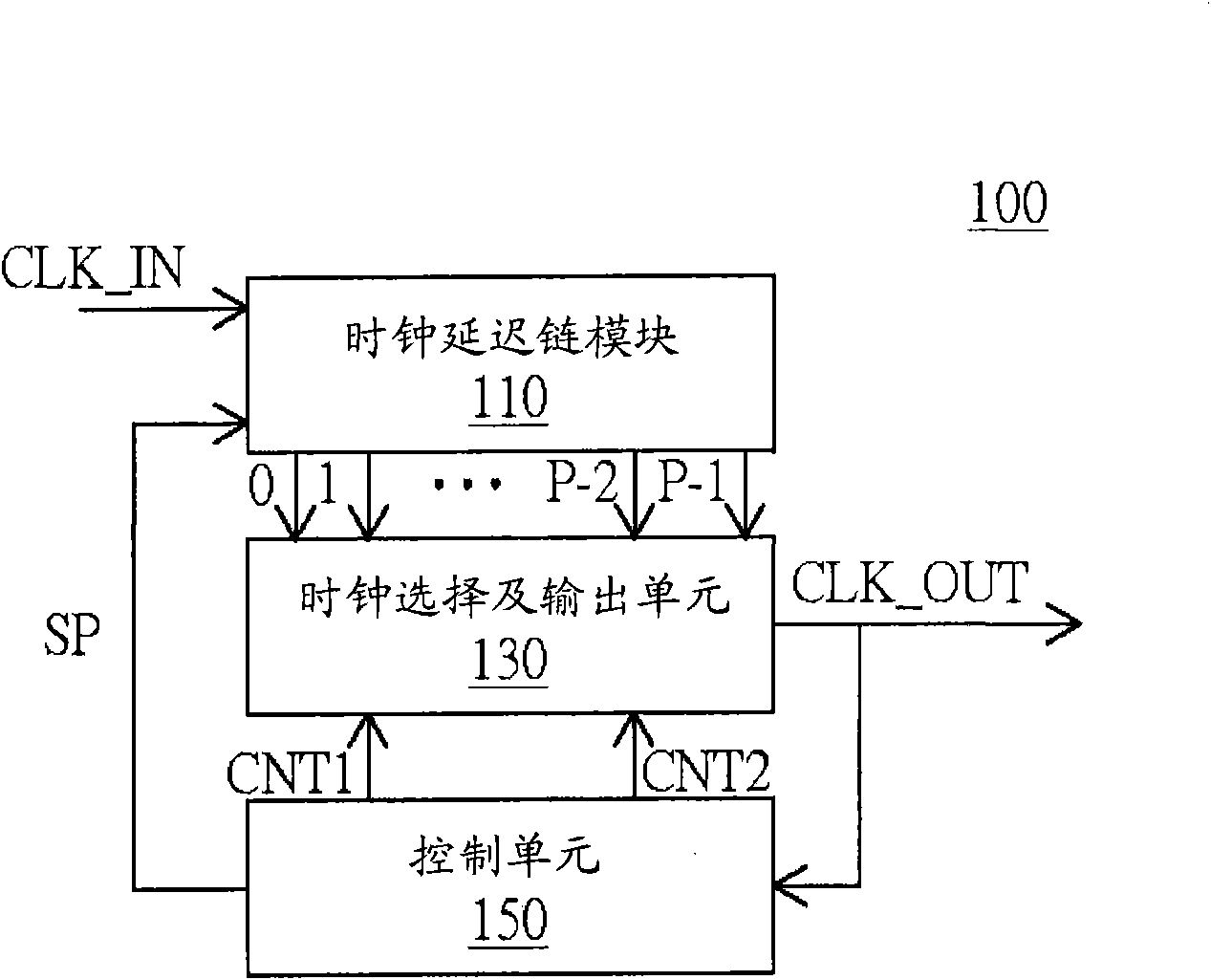

[0042] Please refer to figure 1 Shown is a block diagram of a clock signal spread spectrum generating circuit according to the first embodiment of the present invention. Such as figure 1 As shown, the clock spread frequency generating circuit 100 is used for spreading the input clock signal CLK_IN into the output clock signal CLK_OUT. The clock signal spread spectrum generation circuit 100 includes: a clock delay chain module 110 , a clock selection and output unit 130 and a control unit 150 .

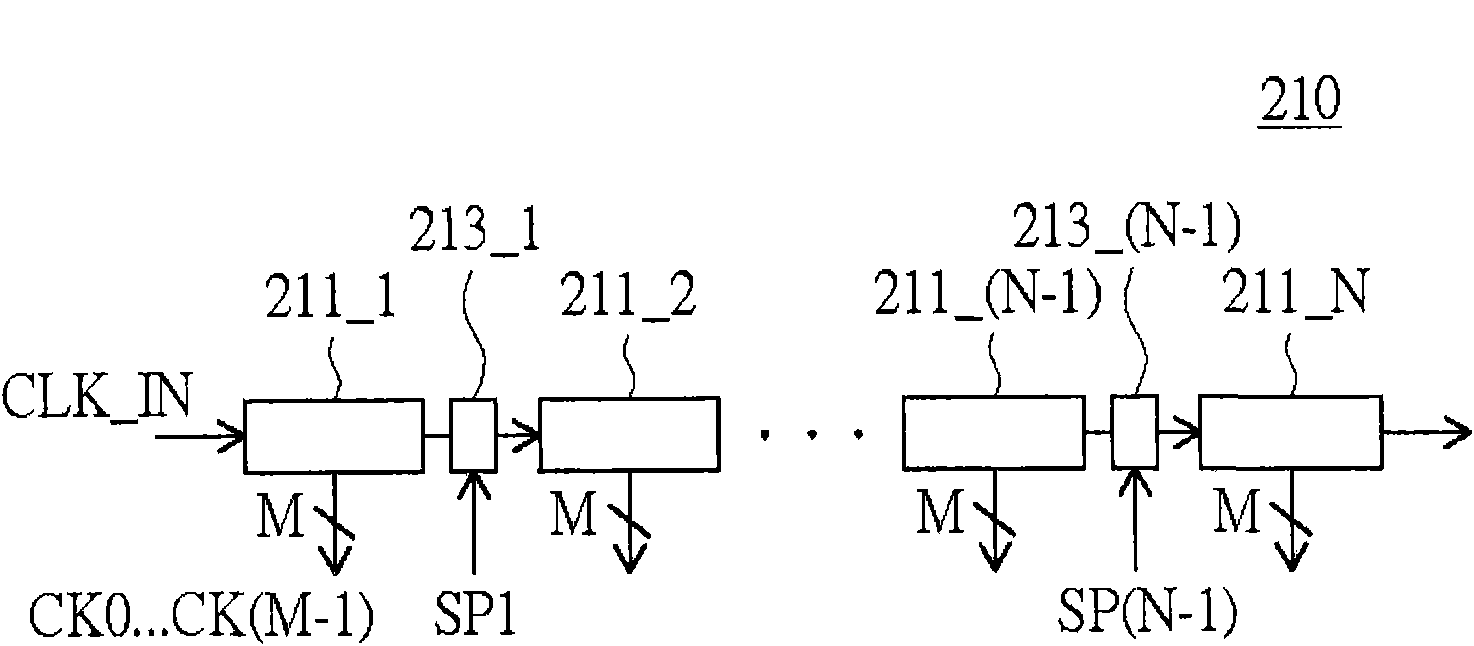

[0043] The clock delay chain module 110 is used for delaying the input clock signal CLK_IN to generate a delayed clock signal group including a plurality of delayed clock signals CK0 to CK(P−1), wherein P is a positive integer. The clock delay chain module 110 includes a plurality of clock delay chains (delay chain), for example figure 2 The clock delay chain module 210 shown includes: clock delay chains 211_1 to 211_N. Each clock delay chain includes a plurality of delay units (d...

no. 2 example

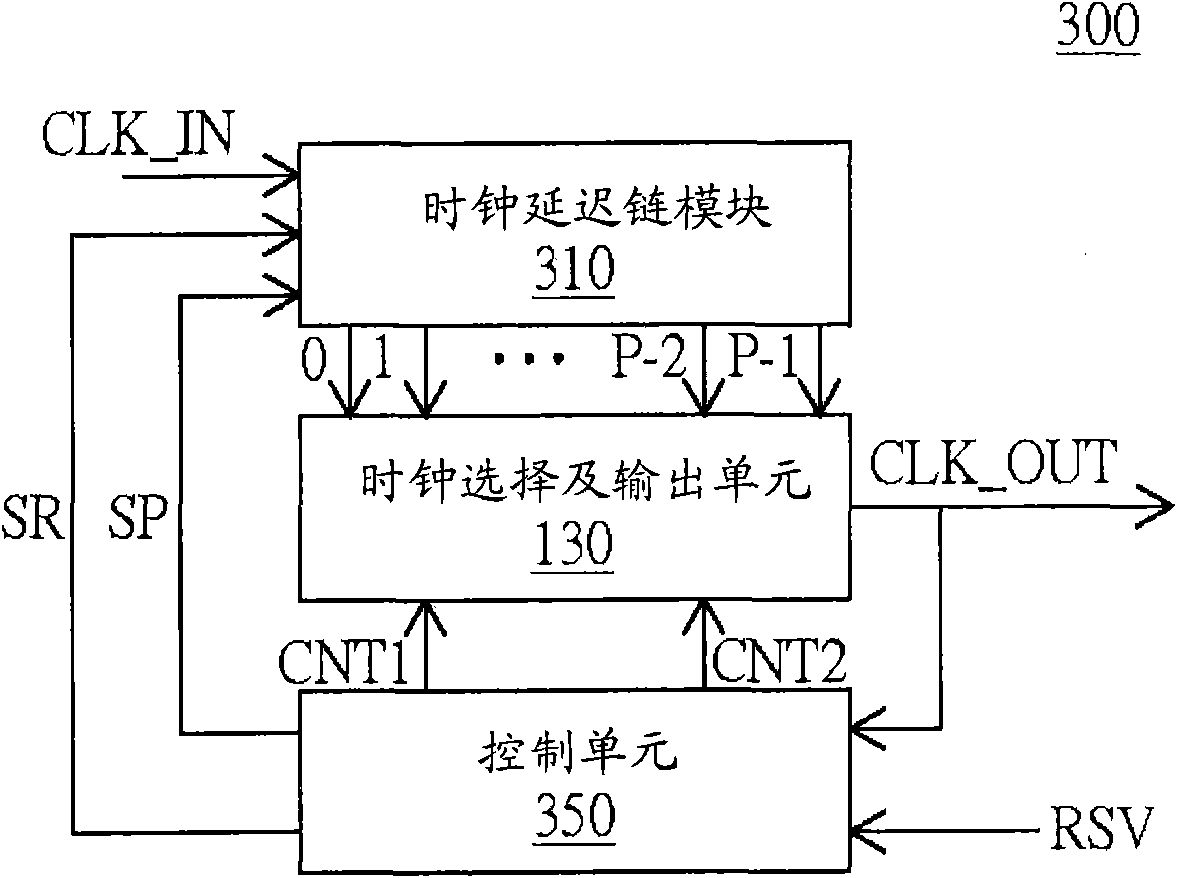

[0052] Please refer to image 3 The present invention further proposes a second embodiment of the clock signal spread spectrum generating circuit, which differs from the clock signal spread spectrum generating circuit 100 of the above-mentioned first embodiment in that the former also has a structure and an operation mode that can change the spread spectrum ratio. The following is image 3 In the description, the signals generated by the clock delay chain module 310 and the control unit 350 of the clock signal spread spectrum generation circuit 300 are described.

[0053] Such as Figure 4A Shown is an embodiment of the clock delay chain module 310 of the clock signal spread spectrum generating circuit 300 of the second embodiment. exist Figure 4A The clock delay chain module 410A in the figure 2 The difference of the middle clock delay chain module 210 is: the former also includes at least one selection unit 414 across non-adjacent clock delay chains, and at least two c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More