Clock generator circuit and related method for generating output clock signal

A clock generation circuit and clock signal technology, applied in the direction of generating/distributing signals, delay line pulse generation, single pulse train generator, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

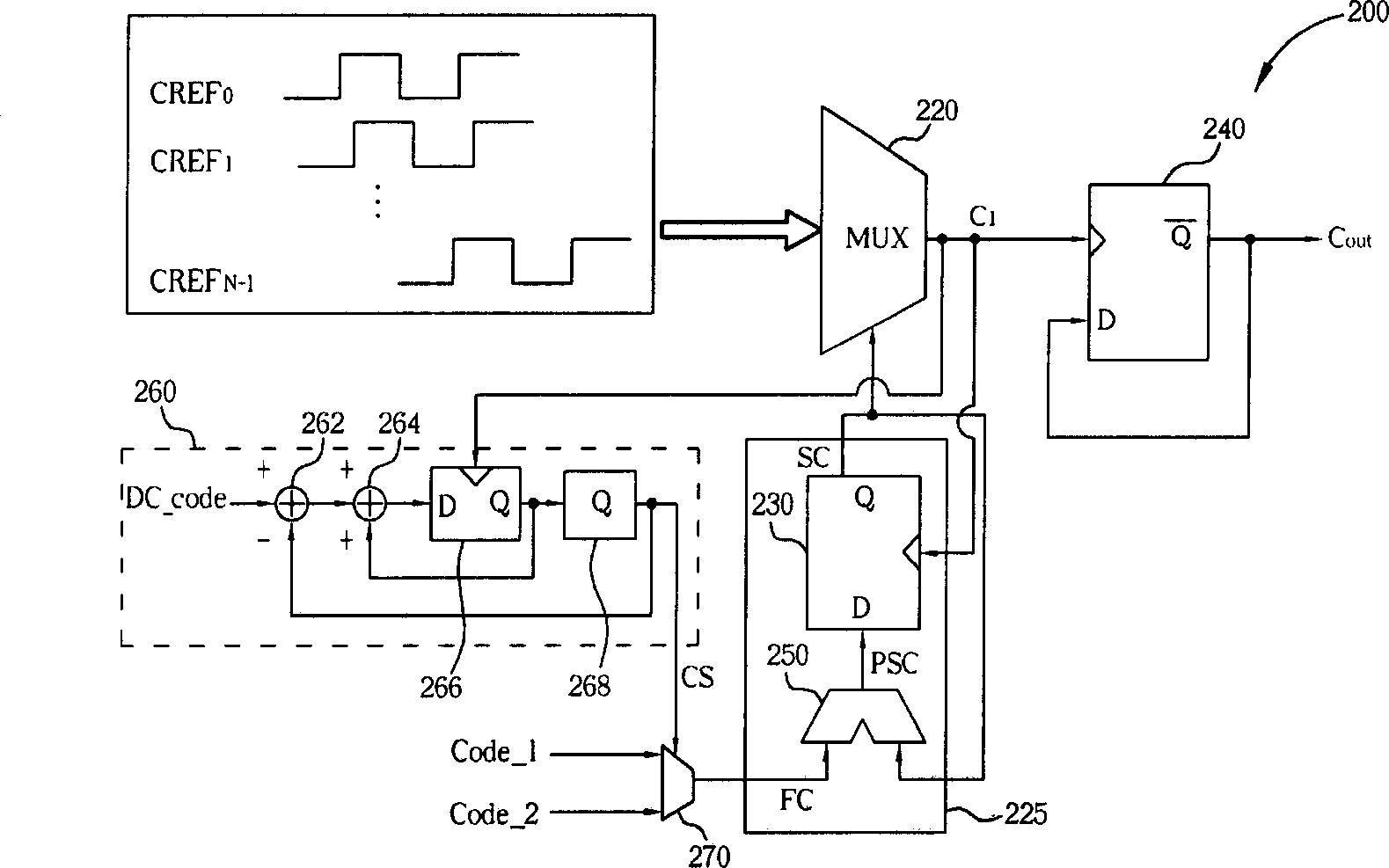

[0019] see figure 2 It is a schematic diagram of an embodiment of the clock generation circuit of the present invention. A clock generating circuit 200 shown in FIG. 2 includes a first multiplexer (multiplexer) 220, an accumulator 225, a toggle circuit (toggle circuit) 240, and a random frequency code generator. The random frequency code generator includes a random signal generator 260 and a second multiplexer 270 . The accumulator 225 includes a register 230 and an adder 250 . In this embodiment, the register 230 is implemented by a first D-flipflop (D-flipflop) 230 , and the trigger circuit 240 is implemented by a second D-flipflop 240 . The signals input to the multiplexer 220 include N reference clock signals in total. N reference clock signals have the same period T REF , the same frequency f REF , but with different phases, where every two adjacent reference clock signals (such as CREF 0 with CREF 1 ) between the phase difference is equal to T REF / N. In other ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More