Data-latching circuit adopting phase selector

A technology of phase selector and data latch, applied in multiple input and output pulse circuits, delay line pulse generation, etc., can solve the problems of sampling error, lock circuit 100 data error, and failure to guarantee correctness, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

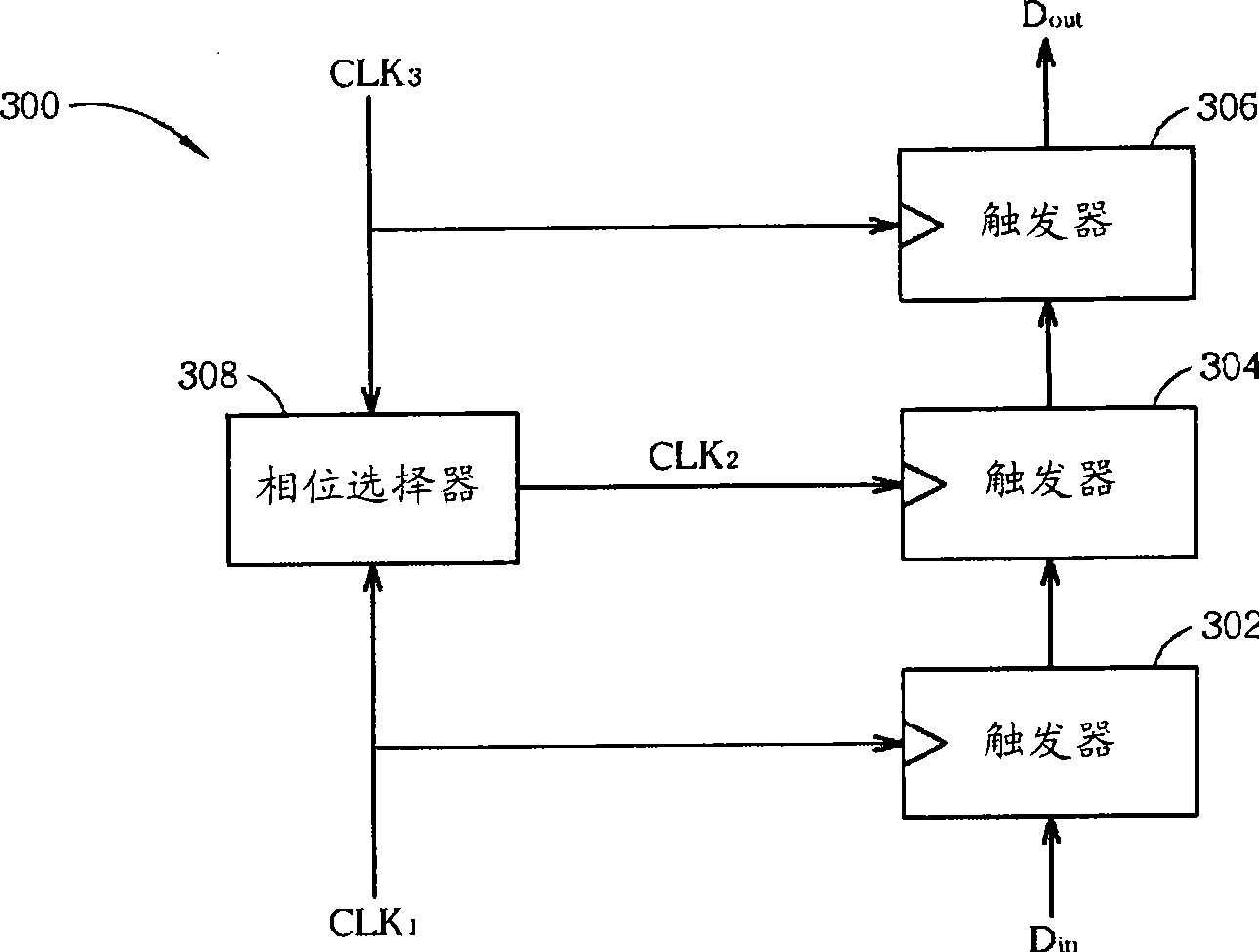

[0017] see image 3 , image 3 It is a schematic diagram of an embodiment of the data latch circuit 300 of the present invention. In this embodiment, the data latch circuit 300 includes three series-connected flip-flops (such as D-type flip-flops) 302, 304, 306 and a phase selector 308, wherein the input data D in The flip-flop 302 is clocked by a first CLK 1 to trigger, and the flip-flop 306 that finally generates output data is controlled by another third clock CLK 3 to trigger. For the flip-flop 304 in the middle, it is driven by a second clock CLK 2 triggered, and the second clock CLK 2 is determined by the phase selector 308 according to the first clock CLK 1 with the third clock CLK 3 The phase relationship between them is generated. In this embodiment, the phase selector 308 is based on the first clock CLK 1 with the third clock CLK 3 phase relationship between to selectively use the third clock CLK 3 or third clock CLK 3 The inverted signal is used as the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More