Zero clearing method and system for superconducting circuit

A clearing and superconducting technology, applied in electrical components, generating electric pulses, single output arrangement, etc., can solve the problems of no pipeline mechanism, incompatibility, low performance, etc., and achieve the effect of ensuring the clearing effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

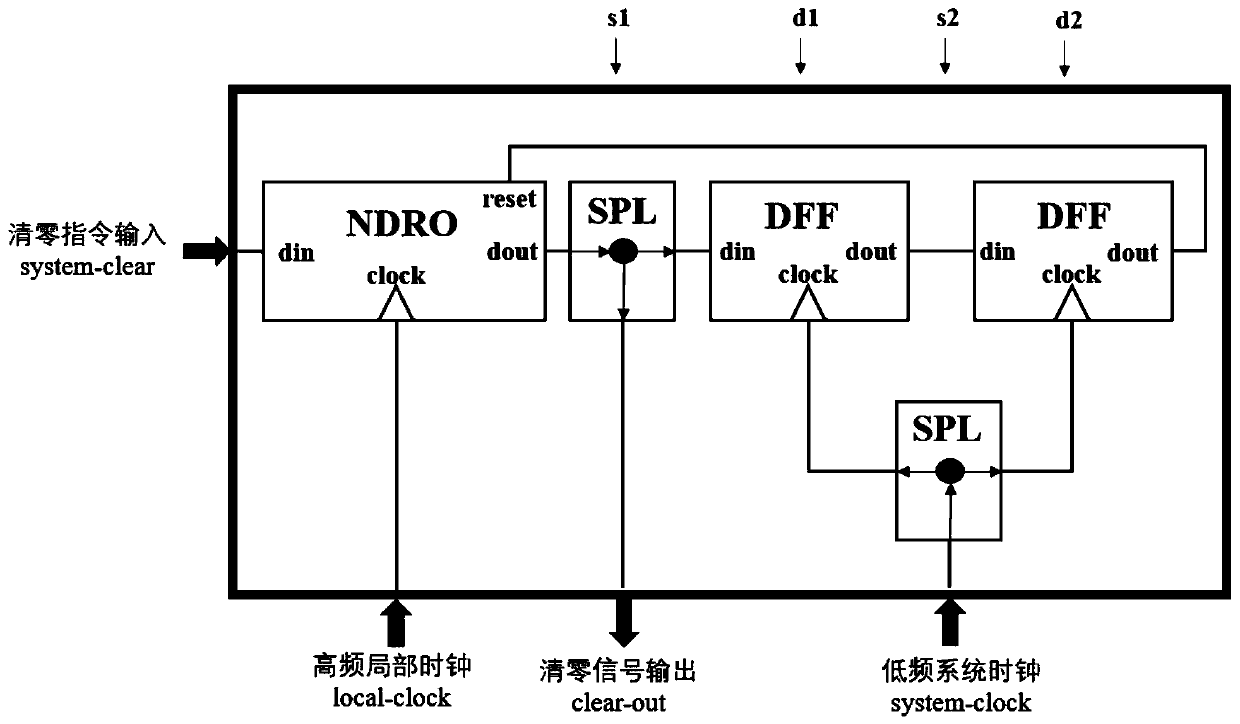

[0026] In the process of designing a pipeline-based superconducting processor, the inventor needs to provide a clearing signal that meets the timing requirements for the superconducting circuit register. There is no specific and practical clearing signal generating device in the prior art. Therefore, the present invention is used in superconducting circuit design. After obtaining a clearing command signal, it provides a specific clearing signal generating device and method for superconducting registers that meet the actual working sequence requirements of superconducting circuits.

[0027] The present invention includes following key points:

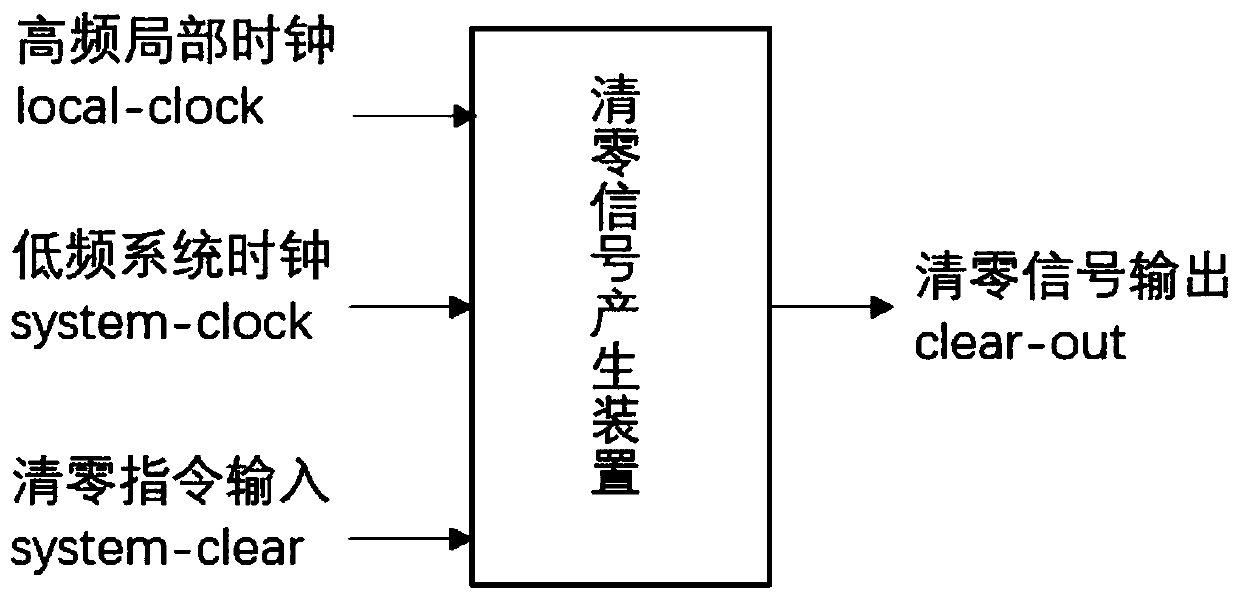

[0028] Key point 1, the clearing signal generating device includes a clearing command signal input port, a high-frequency local clock input port, a low-frequency system clock input port, and a clearing signal output port;

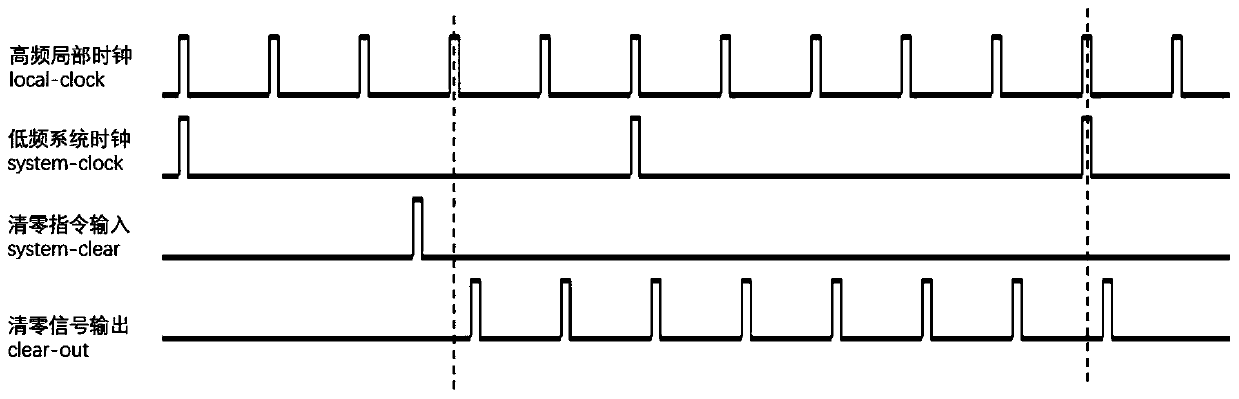

[0029] Key point 2, after receiving a clearing instruction signal, the clearing signal generating device starts to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More