Patents

Literature

688 results about "Rapid access" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

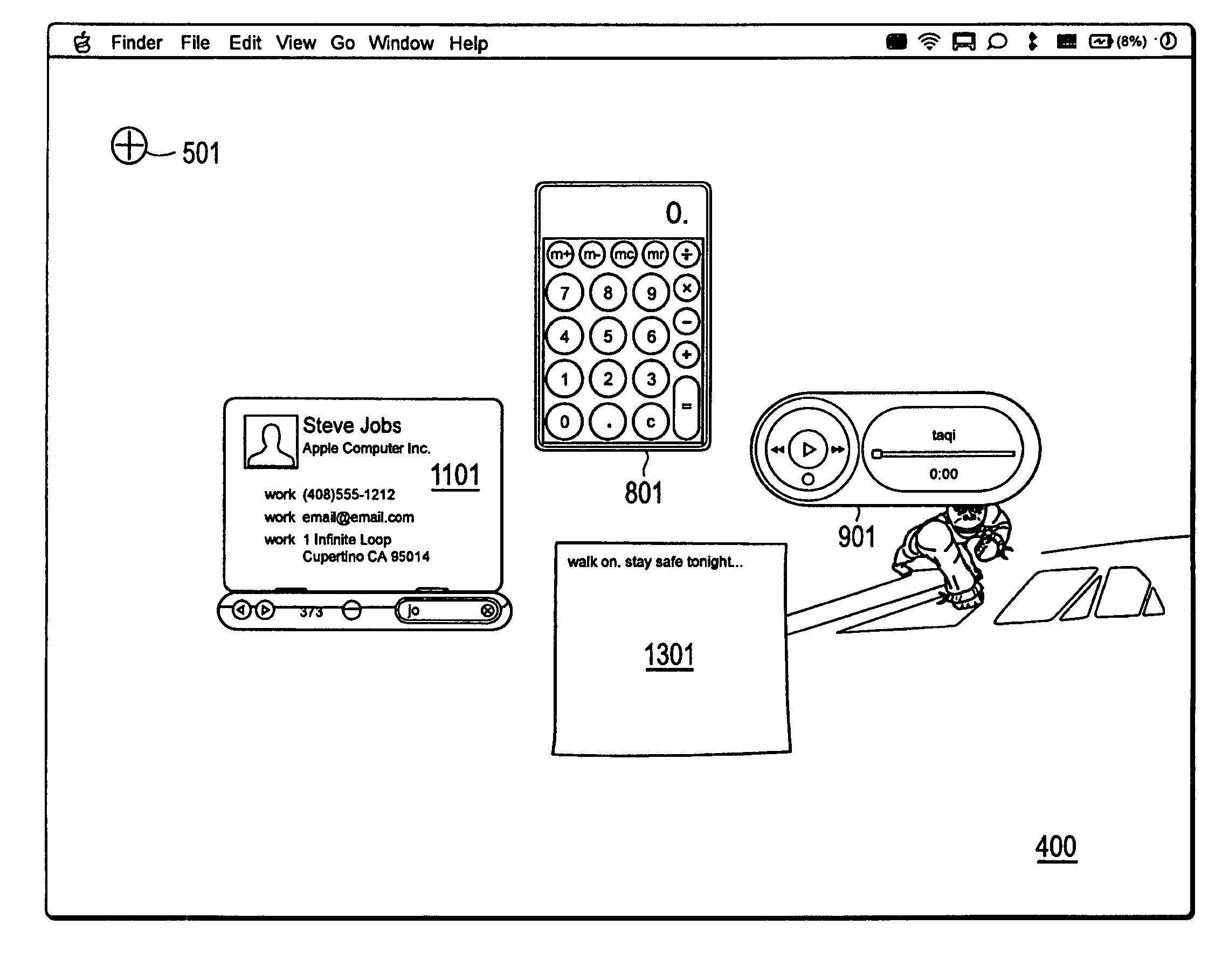

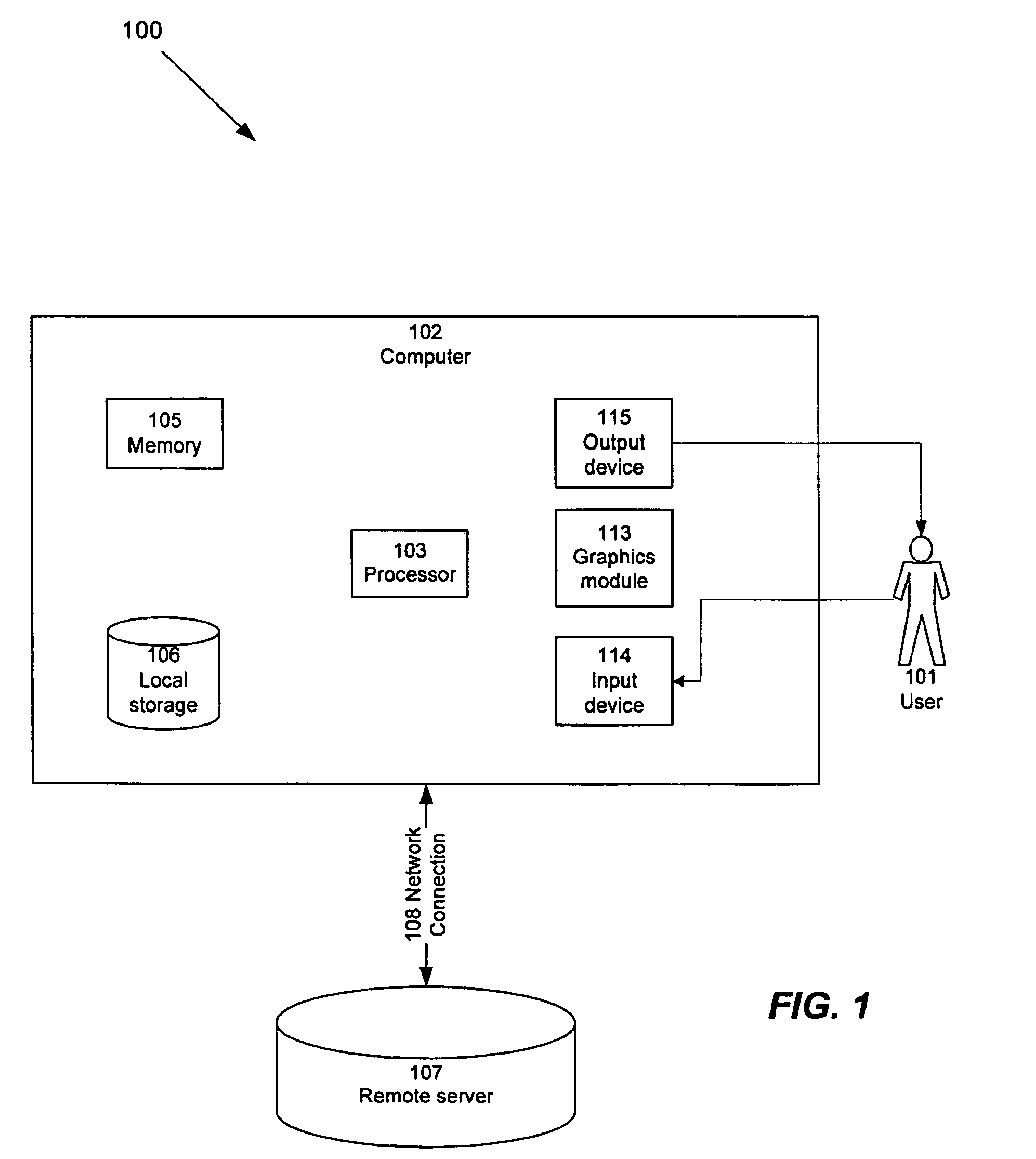

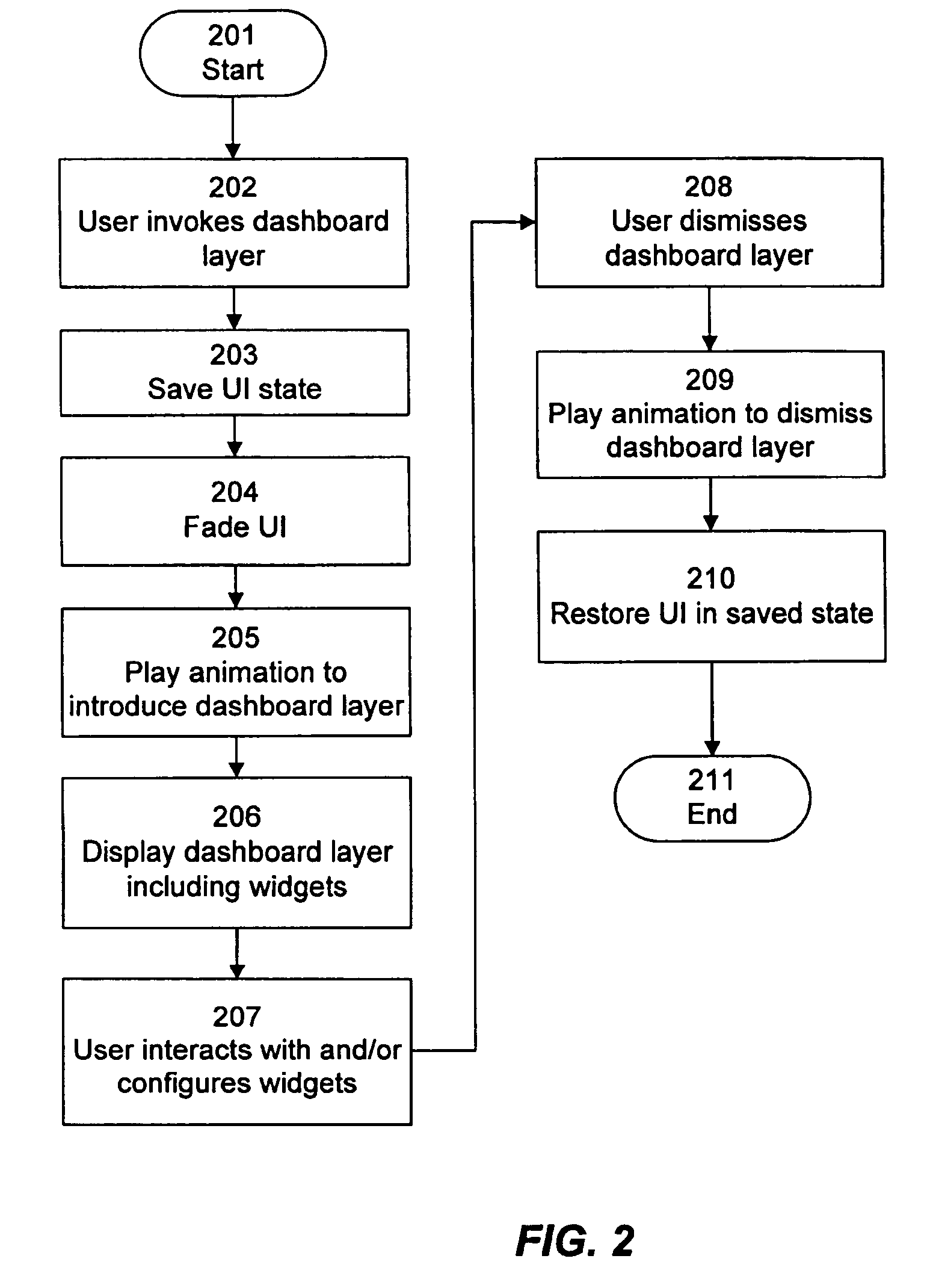

Unified interest layer for user interface

ActiveUS20060015818A1Assisting understandingExecution for user interfacesInput/output processes for data processingDashboardOperational system

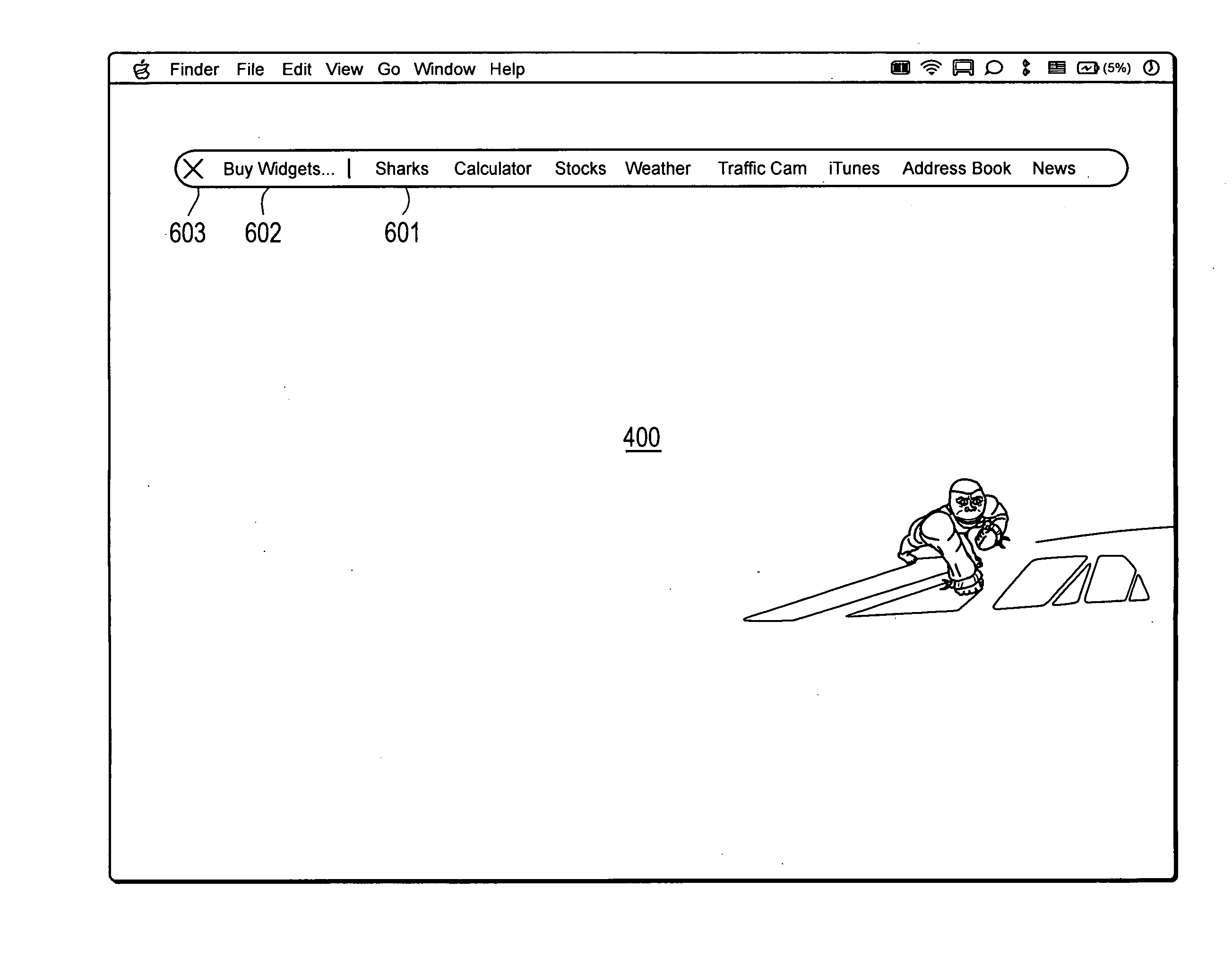

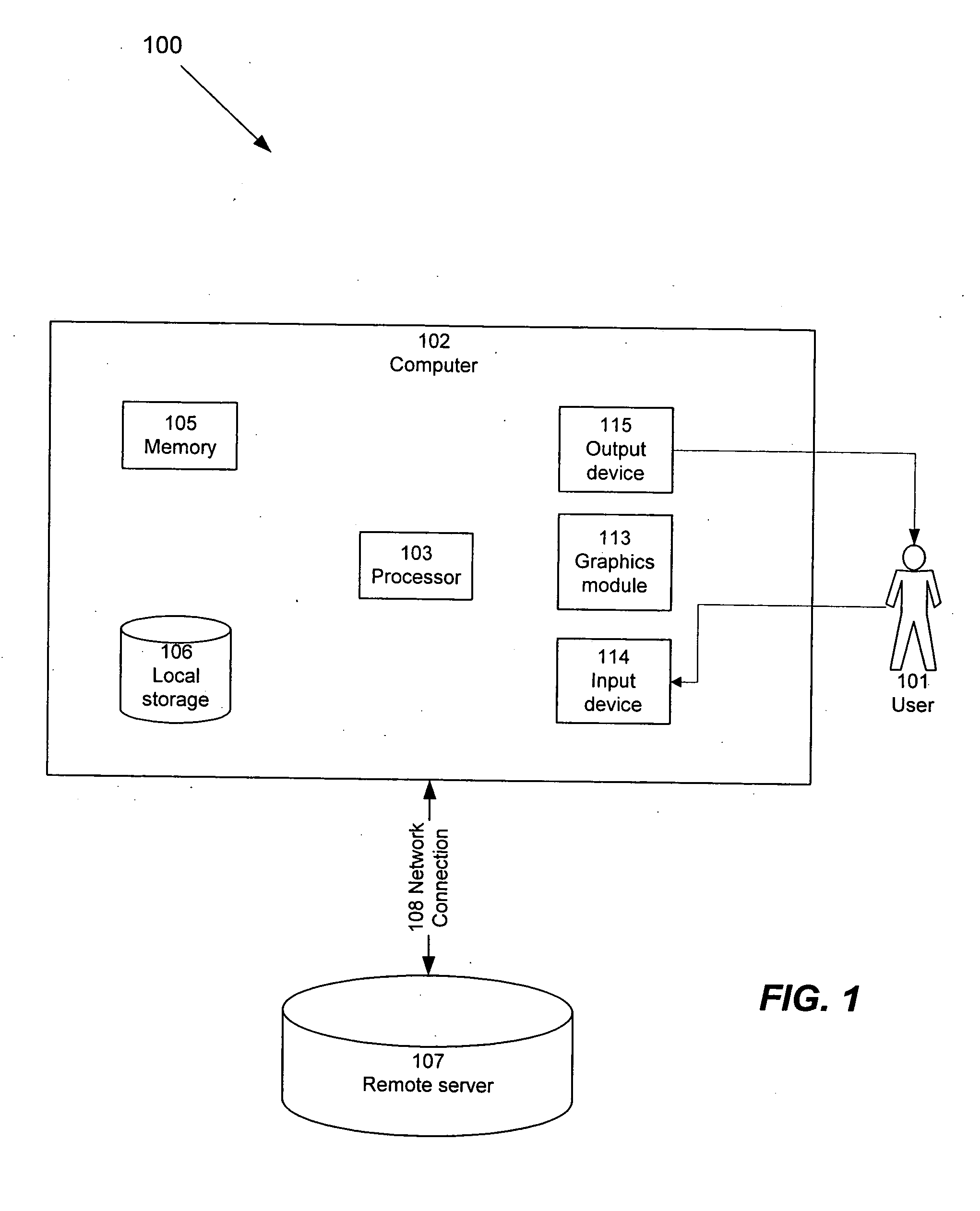

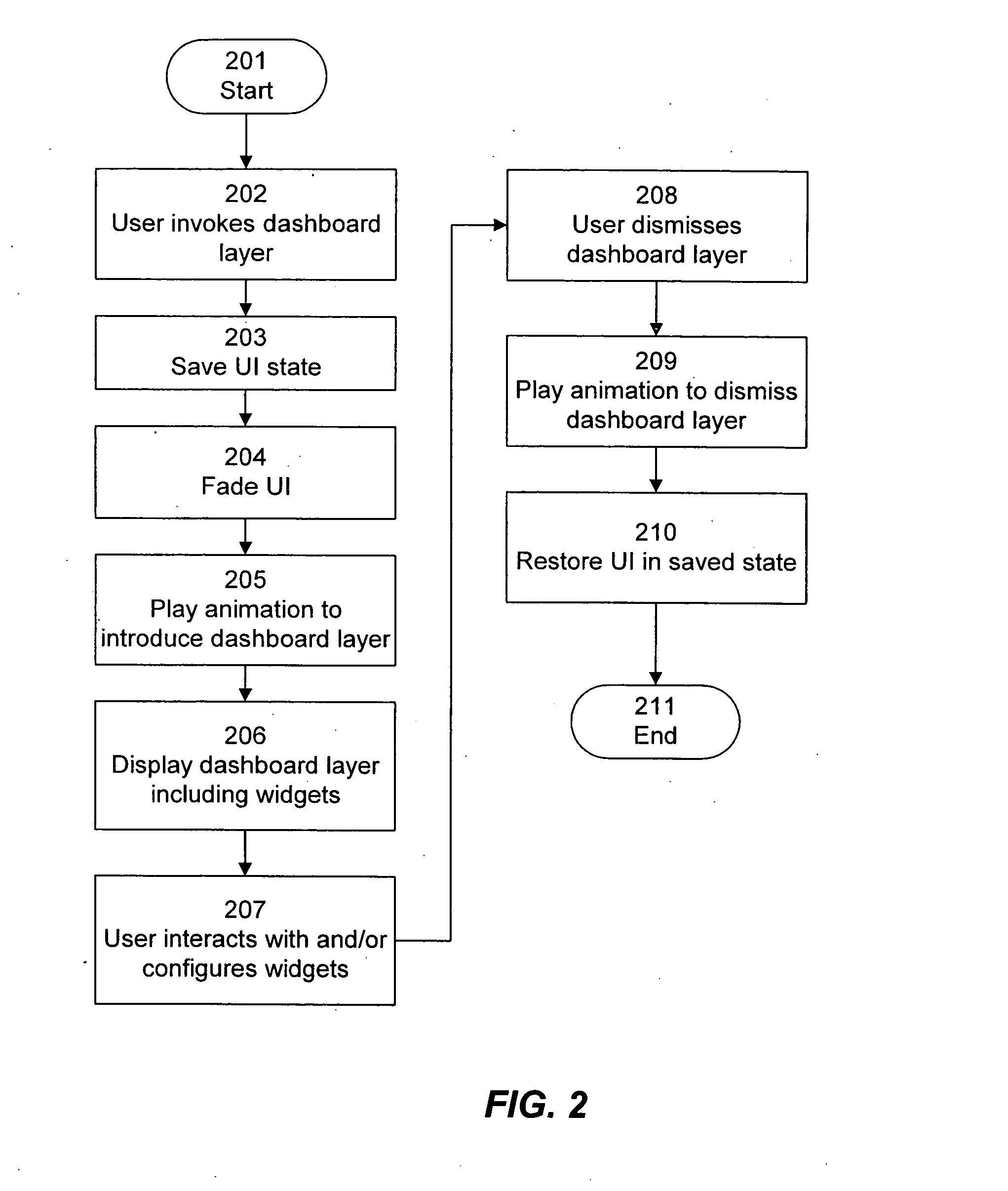

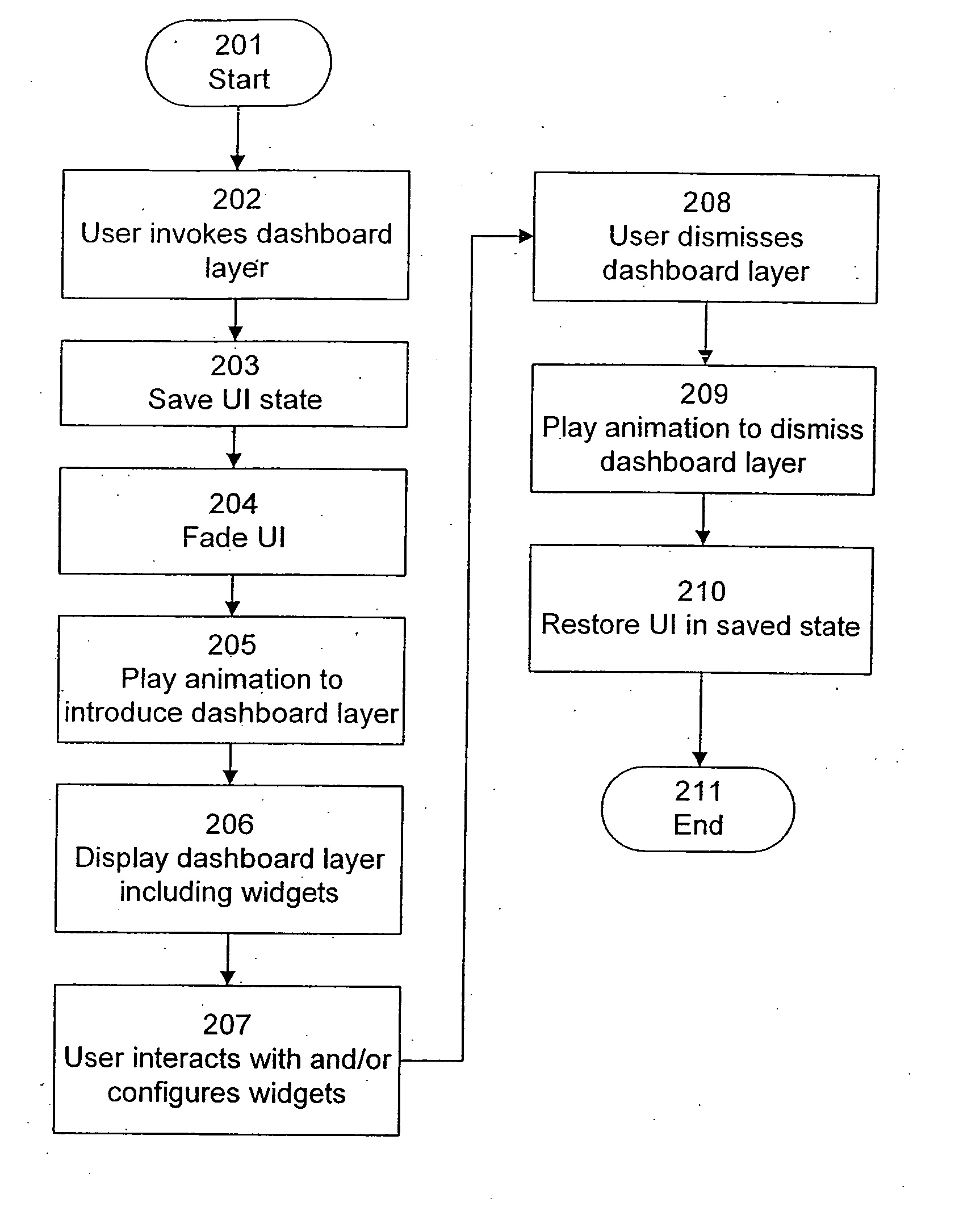

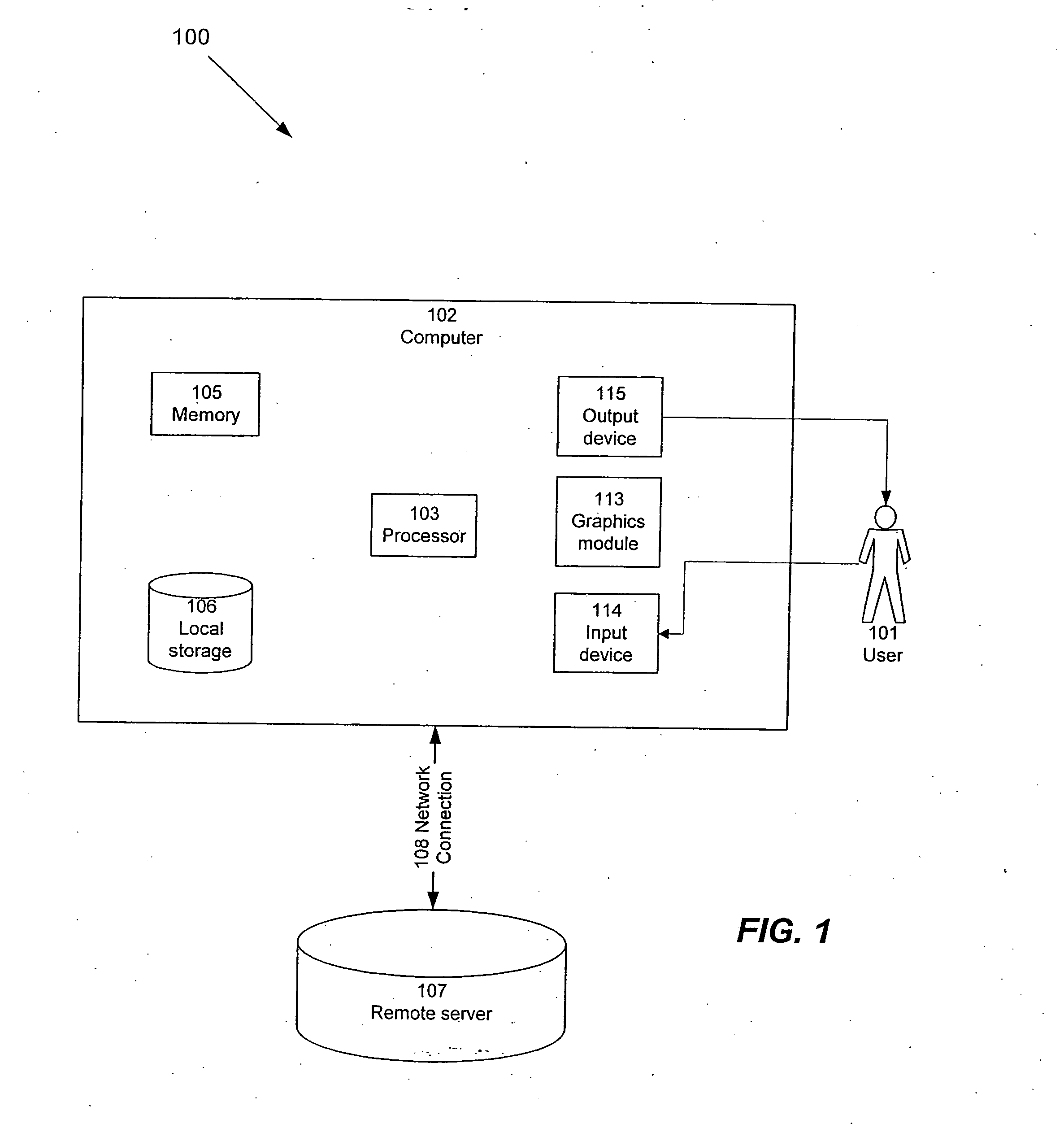

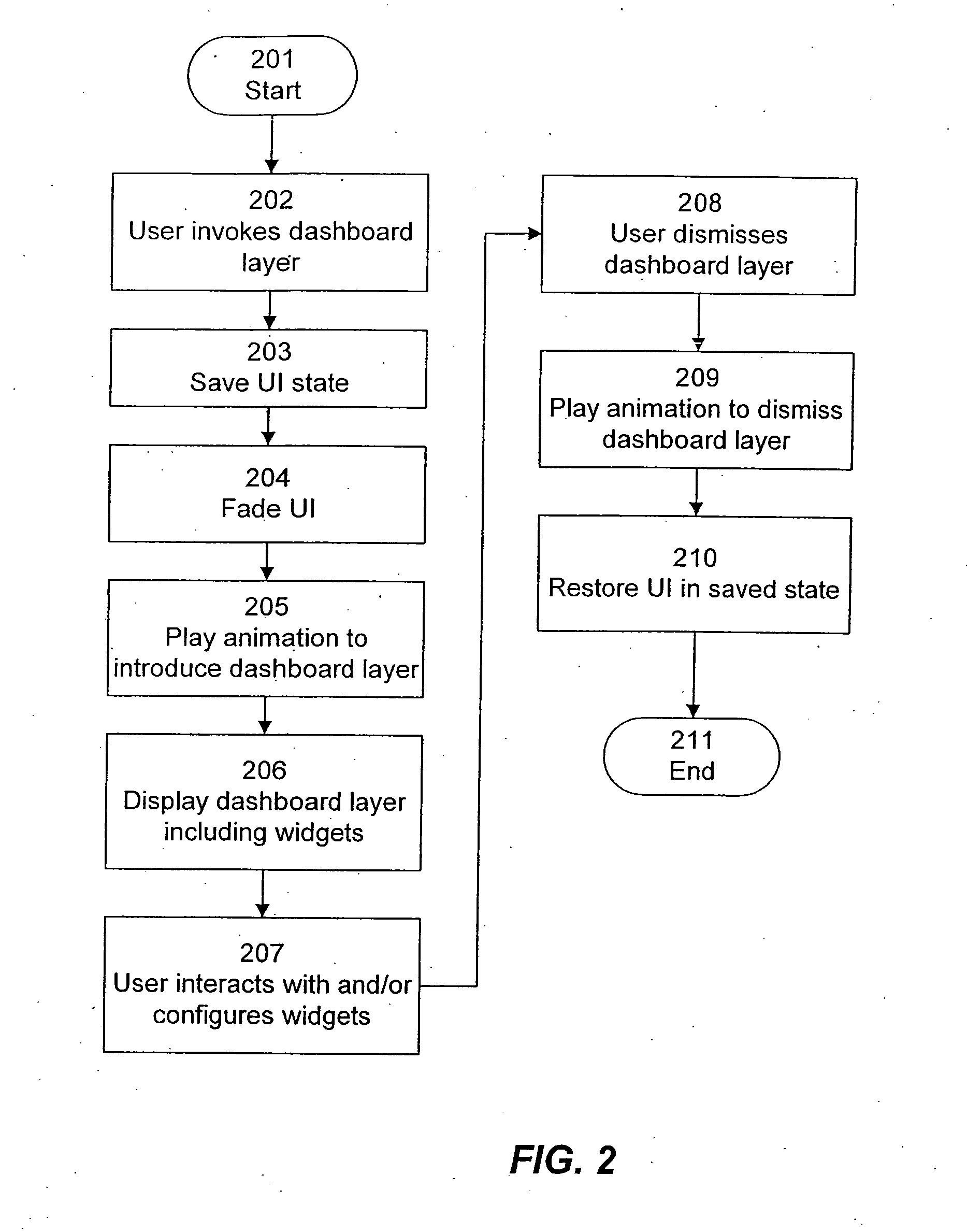

A user-activatable dashboard (also referred to as a unified interest layer) contains any number of user interface elements, referred to herein as “widgets,” for quick access by a user. In response to a command from a user, the dashboard is invoked and the widgets are shown on the screen. The user can activate the dashboard at any time, causing the dashboard to temporarily replace the existing user interface display on the user's screen. Once the dashboard has been activated, the user can interact with any or all of the widgets, and can configure the dashboard by adding, deleting, moving, or configuring individual widgets as desired. When the user wishes to return to the normal user interface he or she was working with, the user issues a command causing the dashboard to be dismissed. Once the dashboard has been dismissed, the previous user interface state is restored, allowing the user to resume normal interactions with the operating system.

Owner:APPLE INC

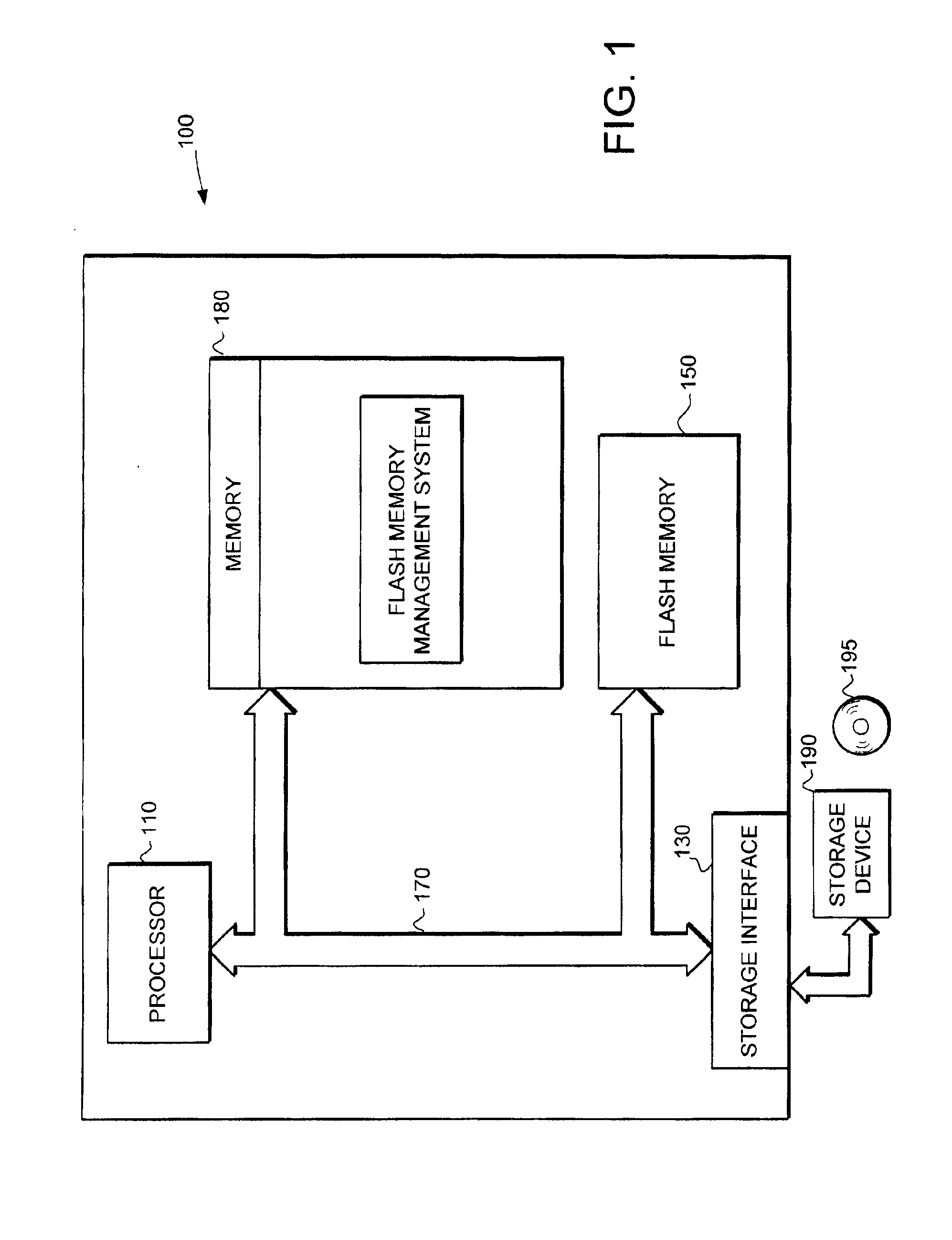

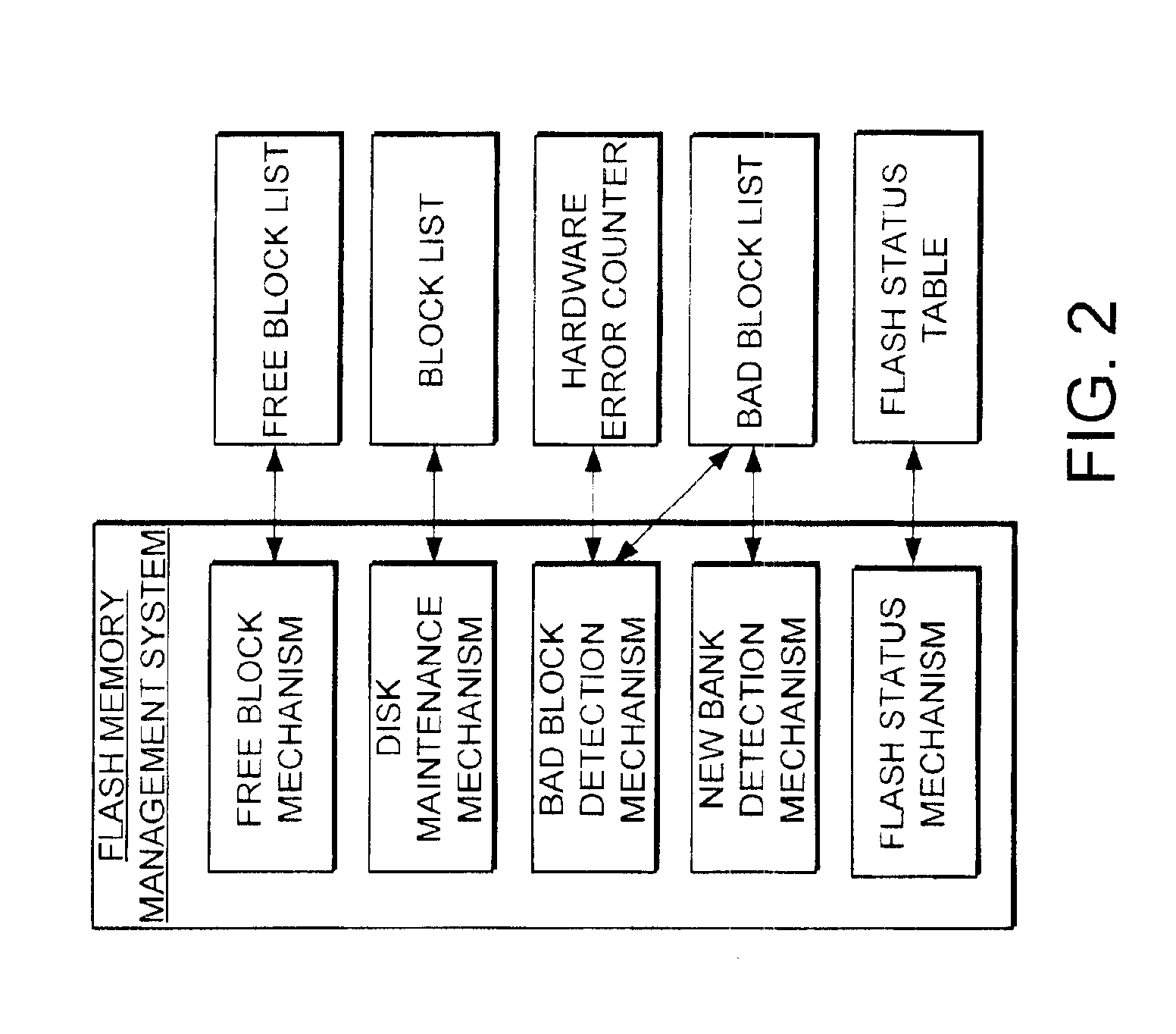

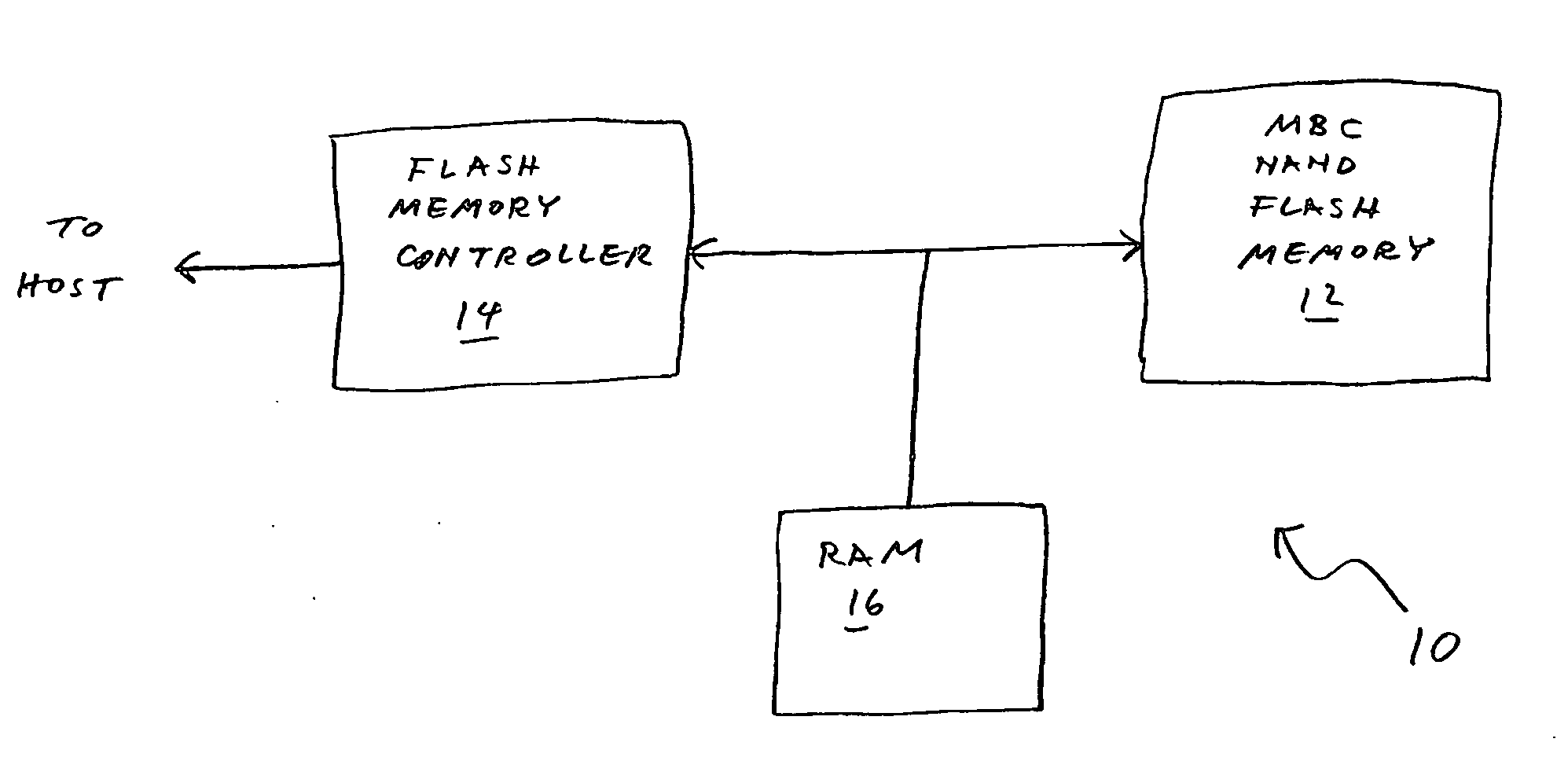

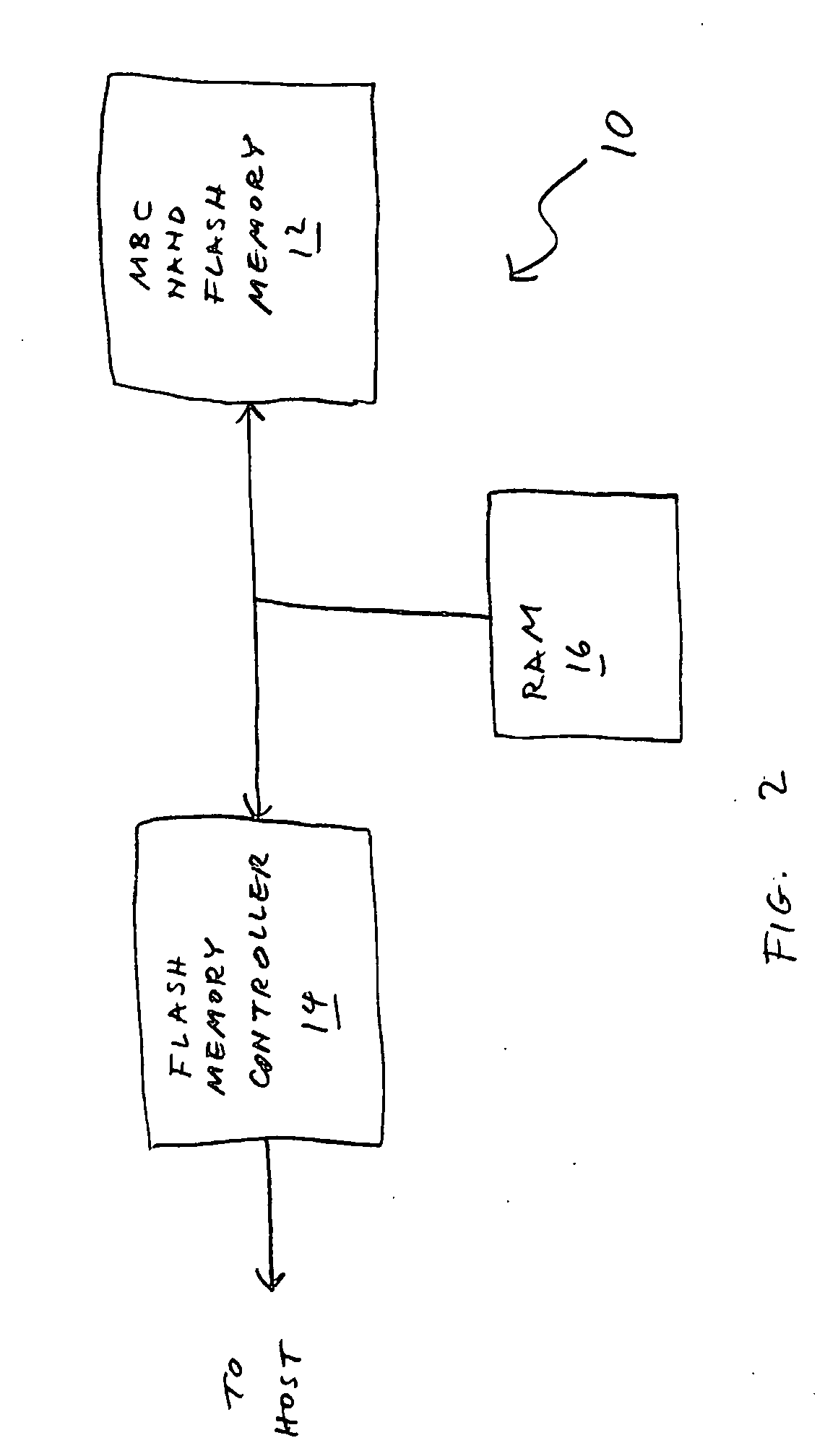

Flash memory management system and method utilizing multiple block list windows

InactiveUS6895464B2Improve performanceImprove reliabilityInput/output to record carriersMemory loss protectionRapid accessBlock detection

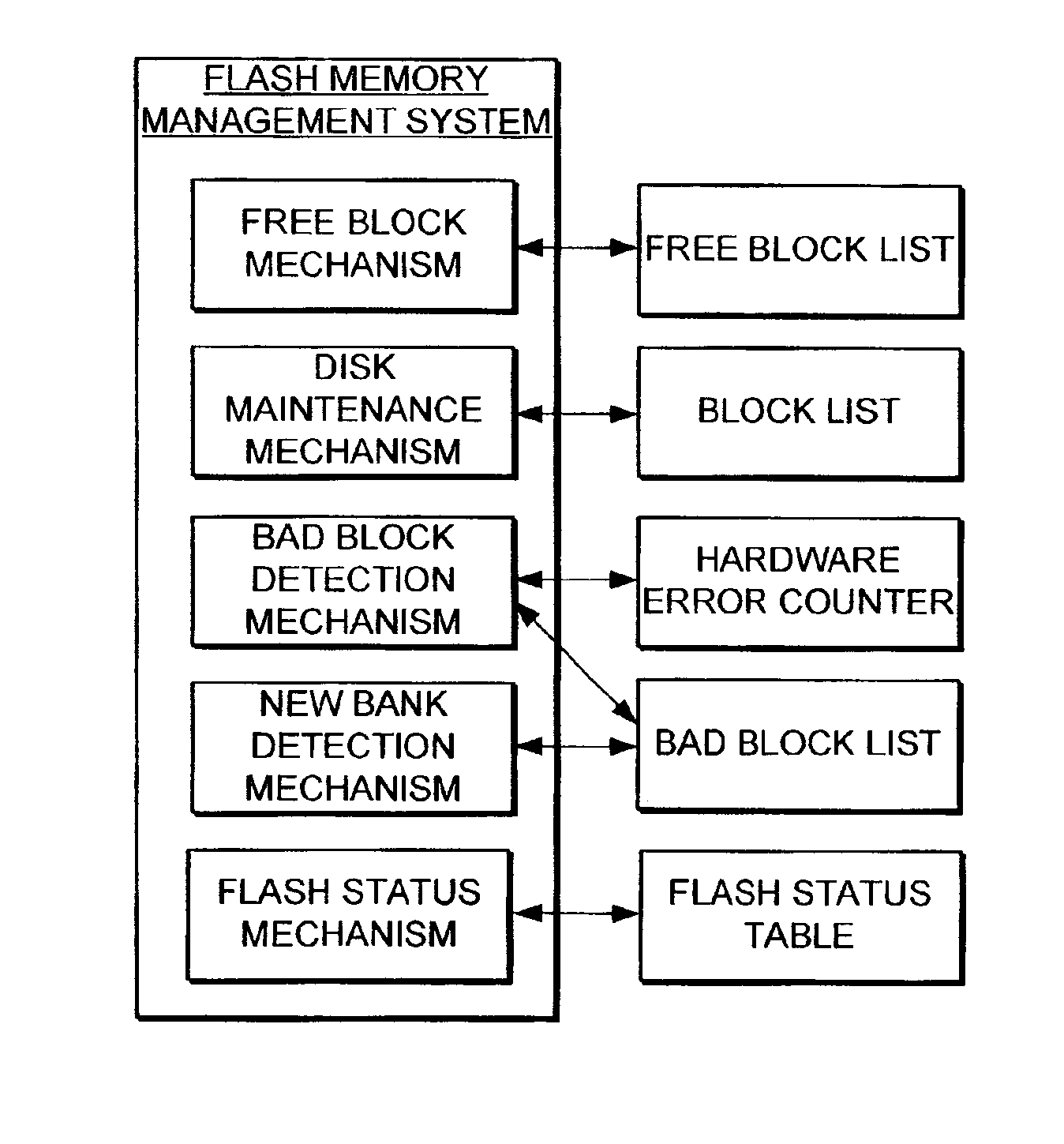

The present invention provides a flash memory management system and method with increased performance. The flash memory management system provides the ability to efficiently manage and allocate flash memory use in a way that improves reliability and longevity, while maintaining good performance levels. The flash memory management system includes a free block mechanism, a disk maintenance mechanism, and a bad block detection mechanism. The free block mechanism provides efficient sorting of free blocks to facilitate selecting low use blocks for writing. The disk maintenance mechanism provides for the ability to efficiently clean flash memory blocks during processor idle times. The bad block detection mechanism provides the ability to better detect when a block of flash memory is likely to go bad. The flash status mechanism stores information in fast access memory that describes the content and status of the data in the flash disk. The new bank detection mechanism provides the ability to automatically detect when new banks of flash memory are added to the system. Together, these mechanisms provide a flash memory management system that can improve the operational efficiency of systems that utilize flash memory.

Owner:III HLDG 12 LLC

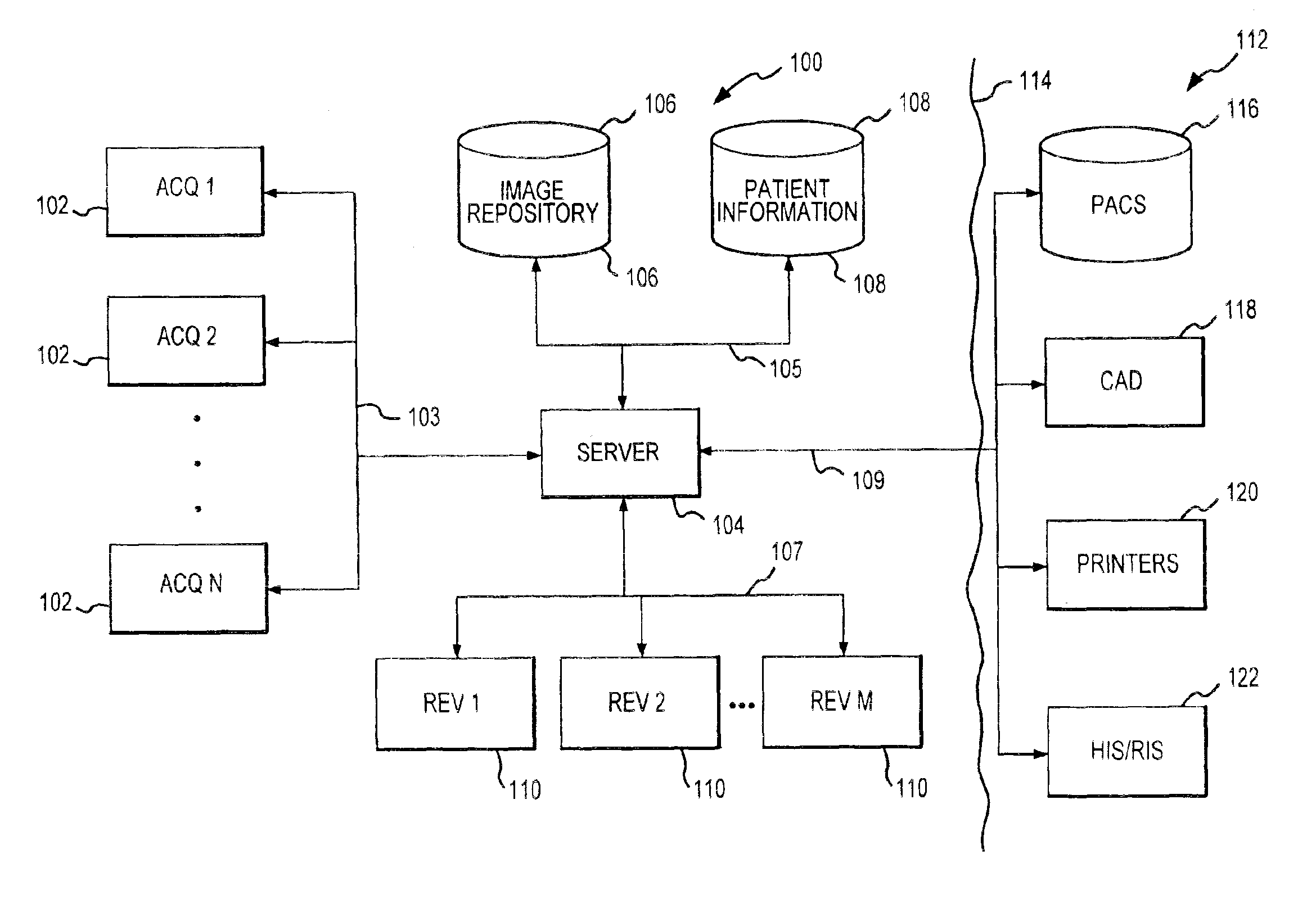

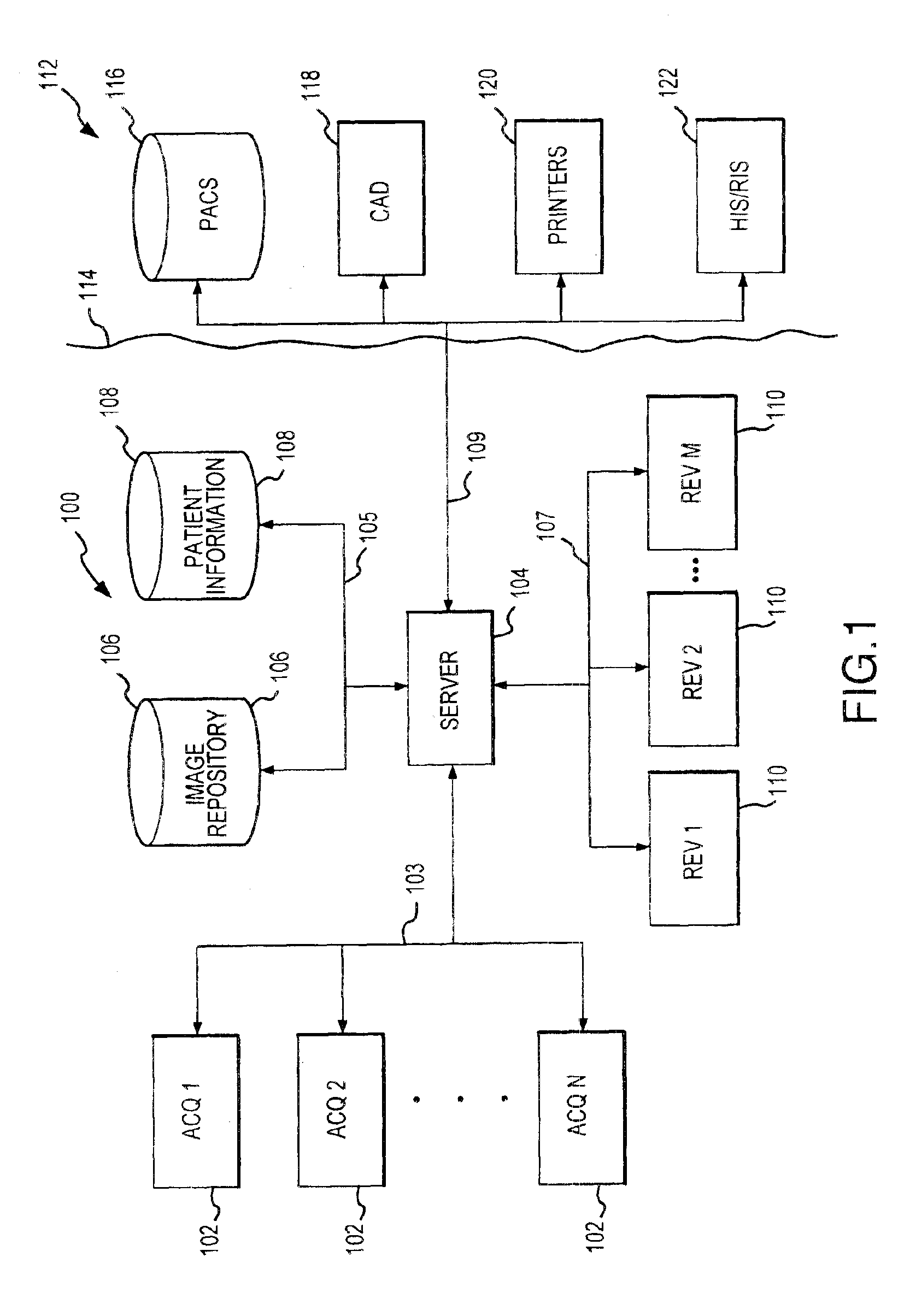

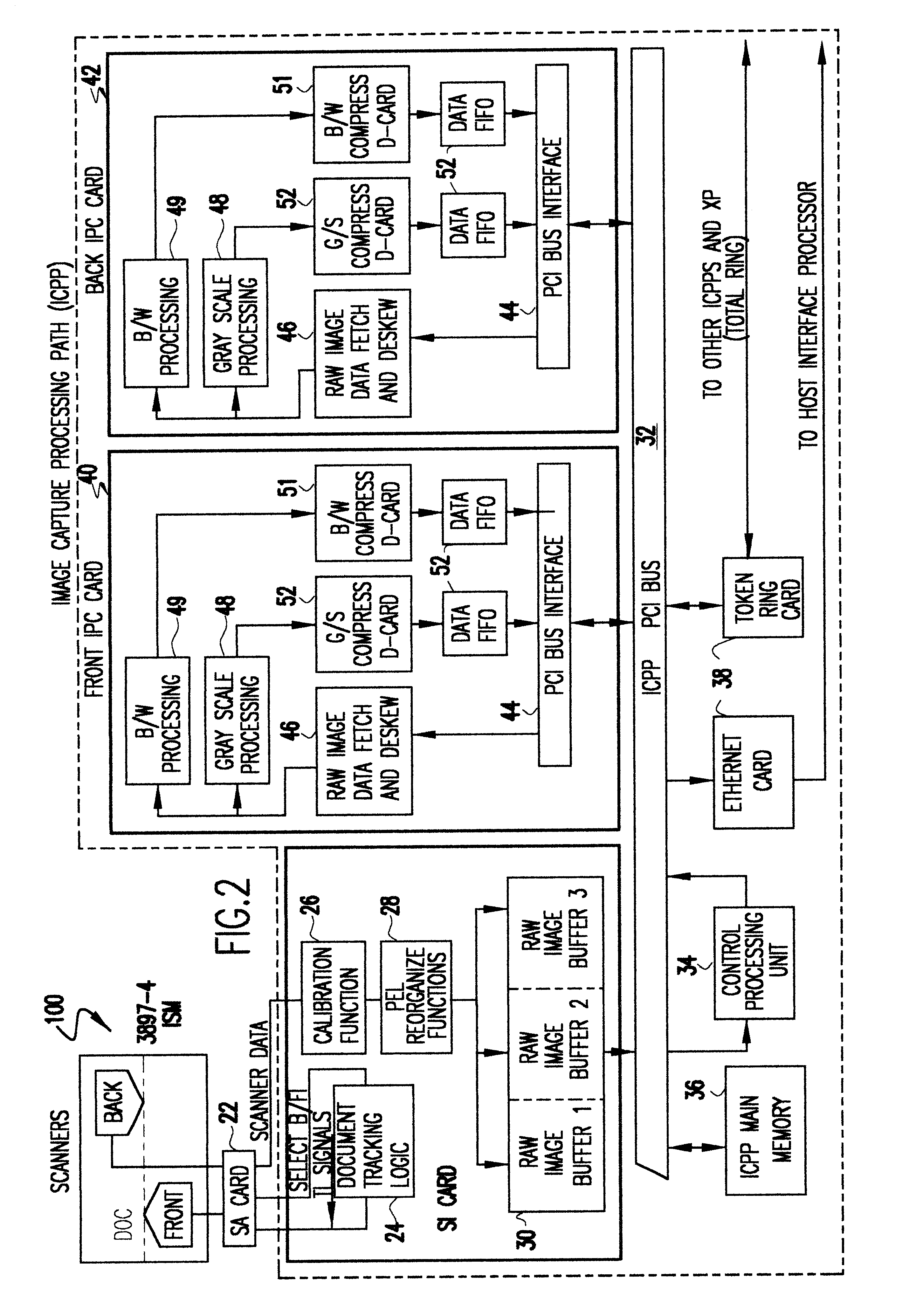

Automated background processing mammographic image data

InactiveUS6891920B1Improve efficiencyQuick displayPatient positioning for diagnosticsCharacter and pattern recognitionRapid accessDigital image

Disclosed is a mammographic imaging system and tools for processing mammographic images to enhance image acquisition and review workflow. The systems and tools enable rapid access to digital image information providing for improved workflow management and identification of images, upon initial review. The system and tools also allow for background processing of image information to reduce workflow delay. Specifically, digital images are processed in the background, i.e., they are automatically processed, free from specific task-orientated direction by a user, using resources that are not otherwise occupied addressing user-directed tasks. Background processing that may be supported includes preprocessing and interim processing. Preprocessing refers to processing of an image that occurs prior to initial review of that image by a physician. Interim processing refers to background processing that occurs during a review session, e.g., in a time period between initial review and a subsequent review of an image.

Owner:HOLOGIC INC

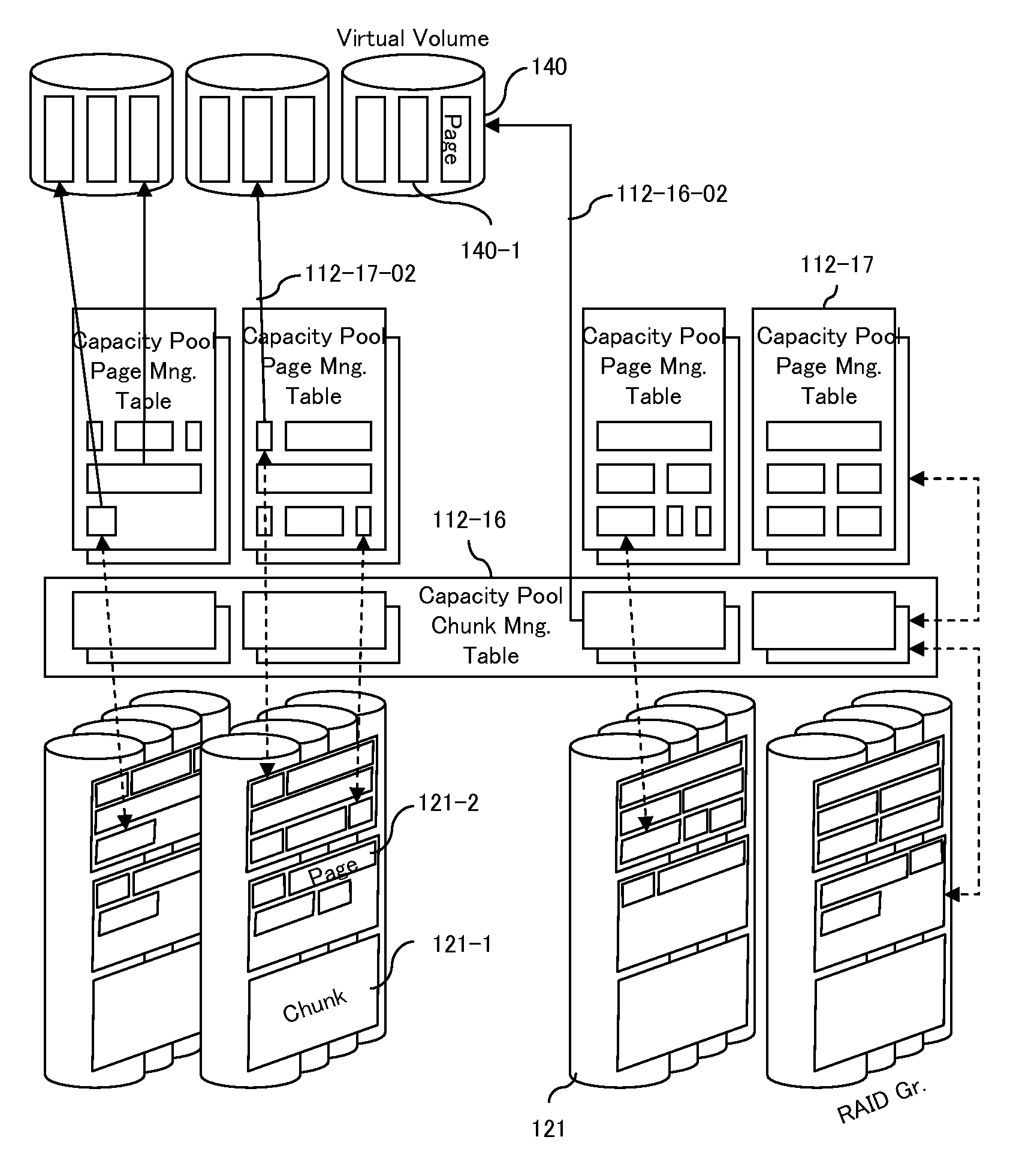

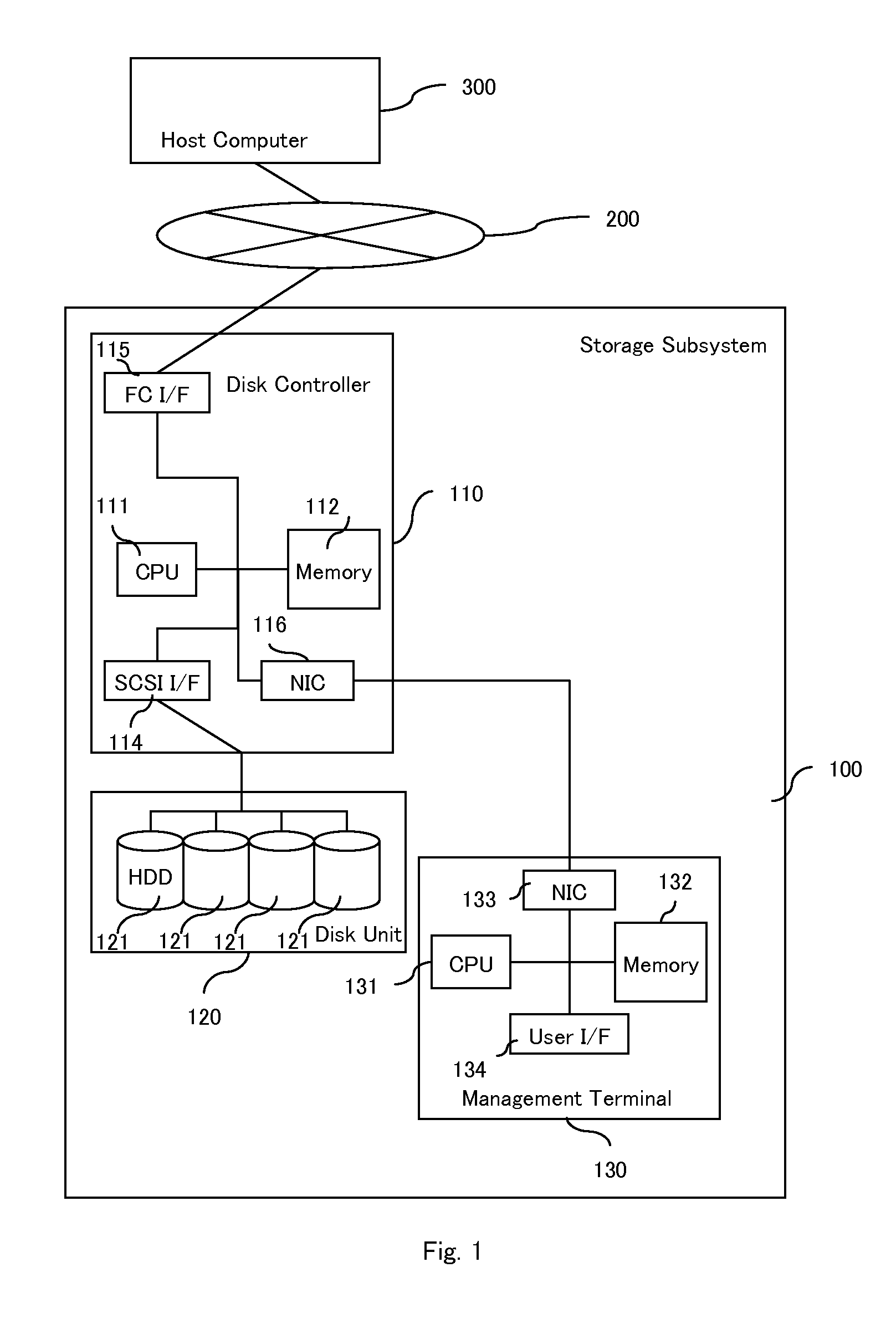

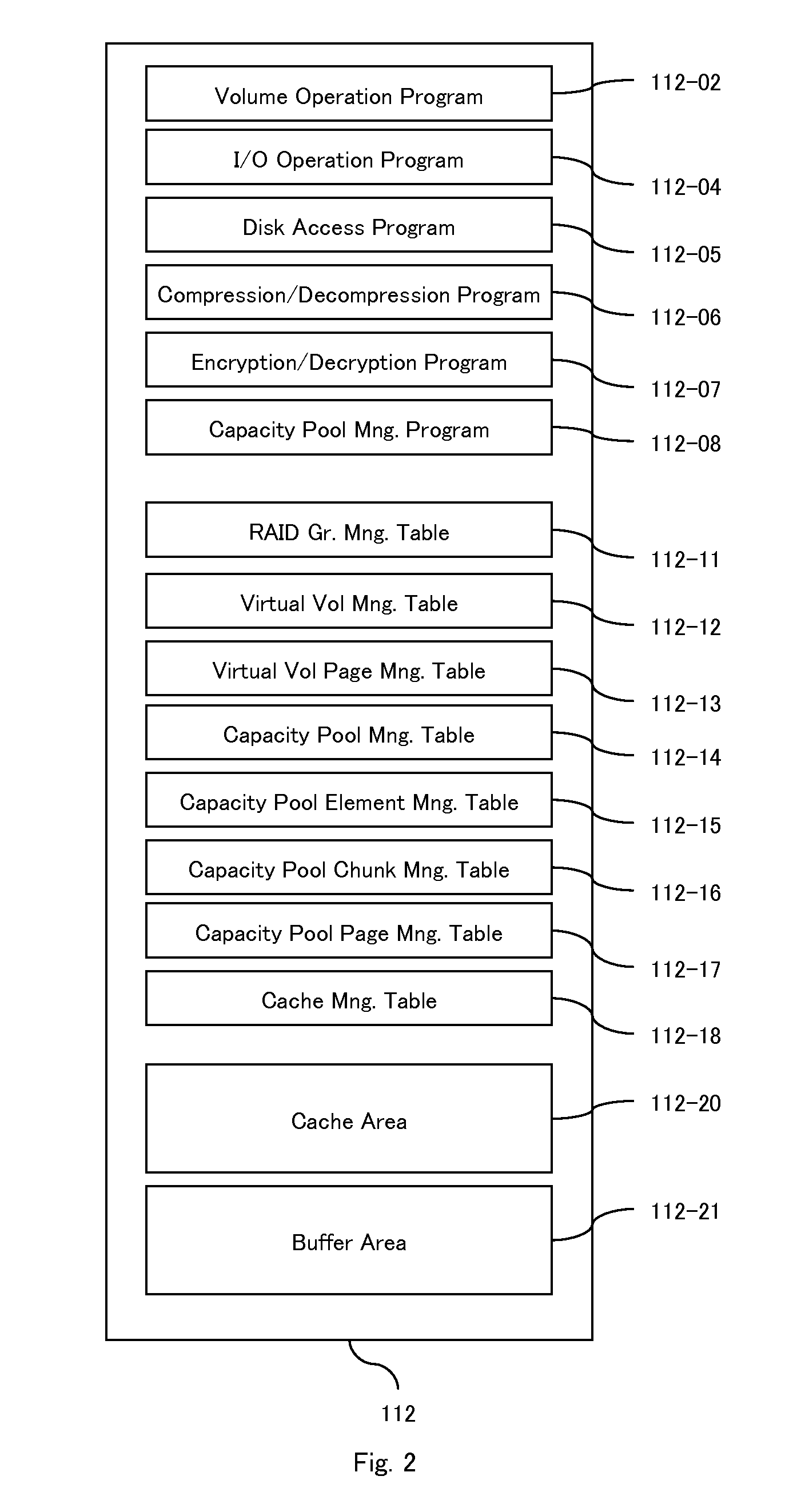

Fast accessible compressed thin provisioning volume

ActiveUS20090144496A1Input/output to record carriersDigital data processing detailsData compressionData management

A computerized data storage system includes at least one storage device including a nonvolatile writable medium; a cache memory operatively coupled to the storage port and including a data storing area and a data management controller and a storage port. The storage port is operable to connect to a host computer, receive and send I / O information required by the host computer. The storage port is also operable to receive a request to read data, and, in response to the request to read data, the storage port is operable to send the data stored in the data storing area of the cache memory. The storage port is further operable to receive a request to write data, and, in response to the request to write data, the storage port is operable to send the write data to the data storing area of the cache memory. The storage system further includes a thin provisioning controller operable to provide a virtual volume having a virtual volume page, a capacity pool having a capacity pool page and manage a mapping between the virtual volume page and the capacity pool page. The storage system further includes a data compression controller operable to perform a compression operation, and a data decompression controller operable to perform a decompression operation.

Owner:HITACHI LTD

Network traffic analyzer

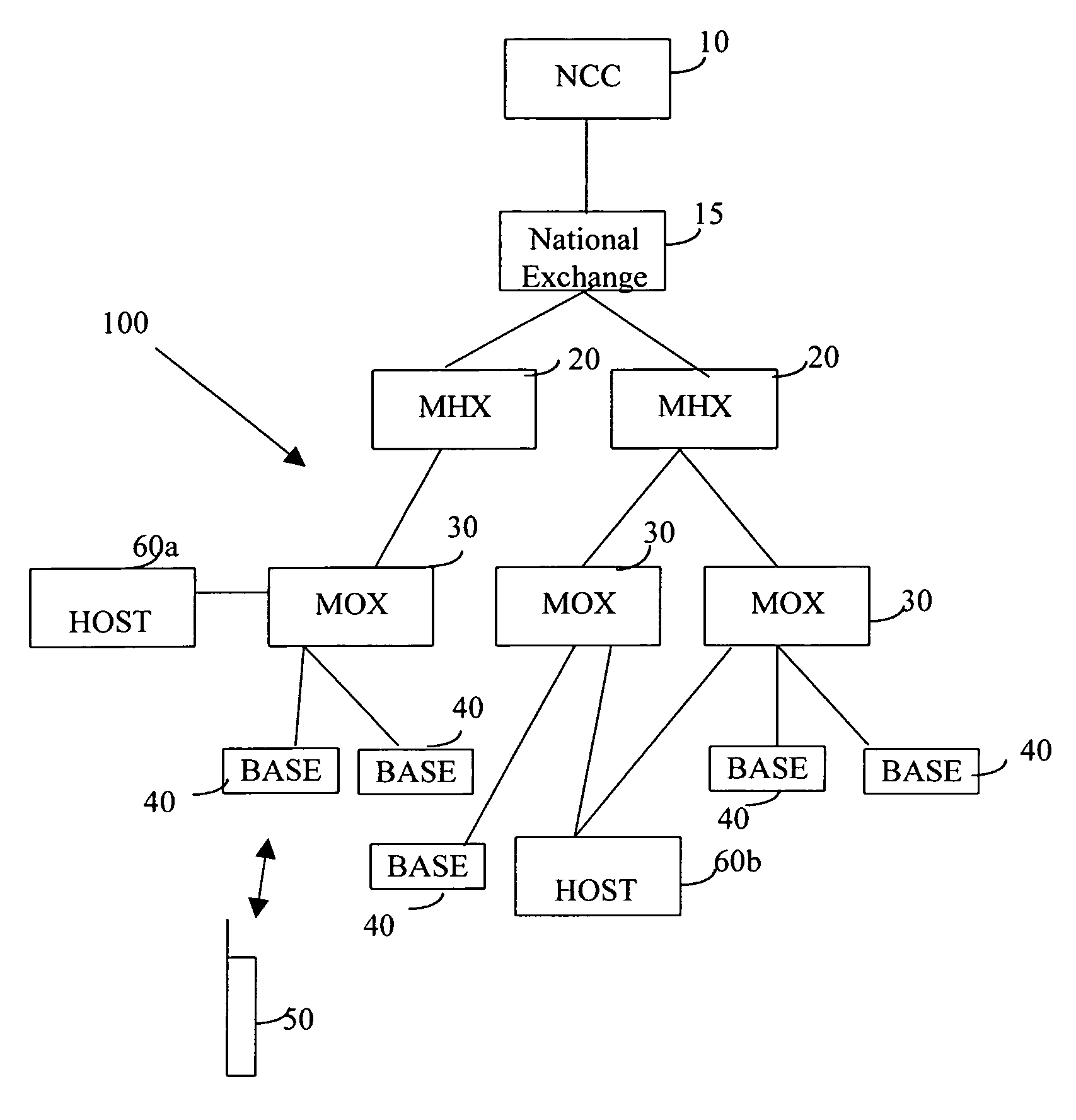

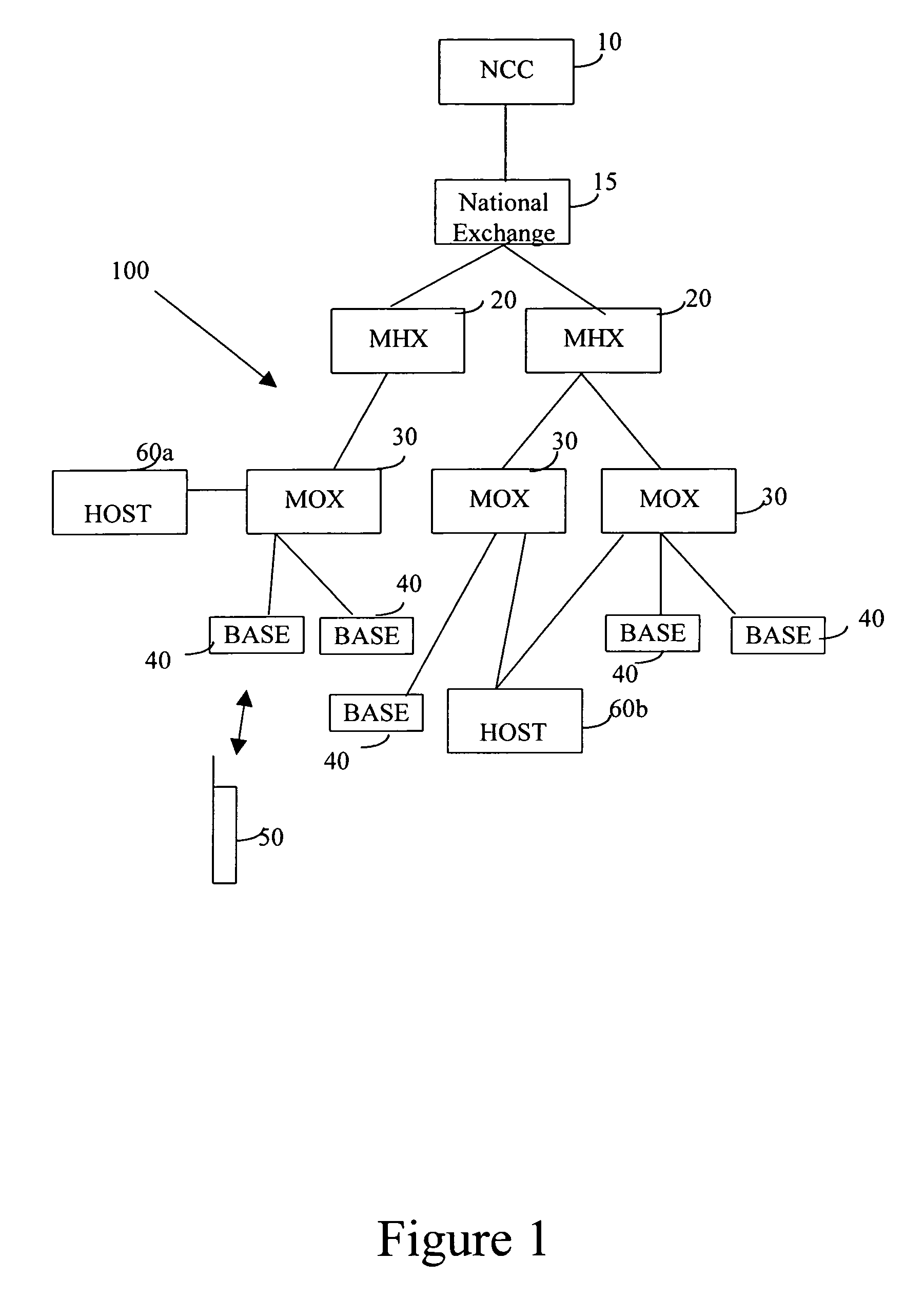

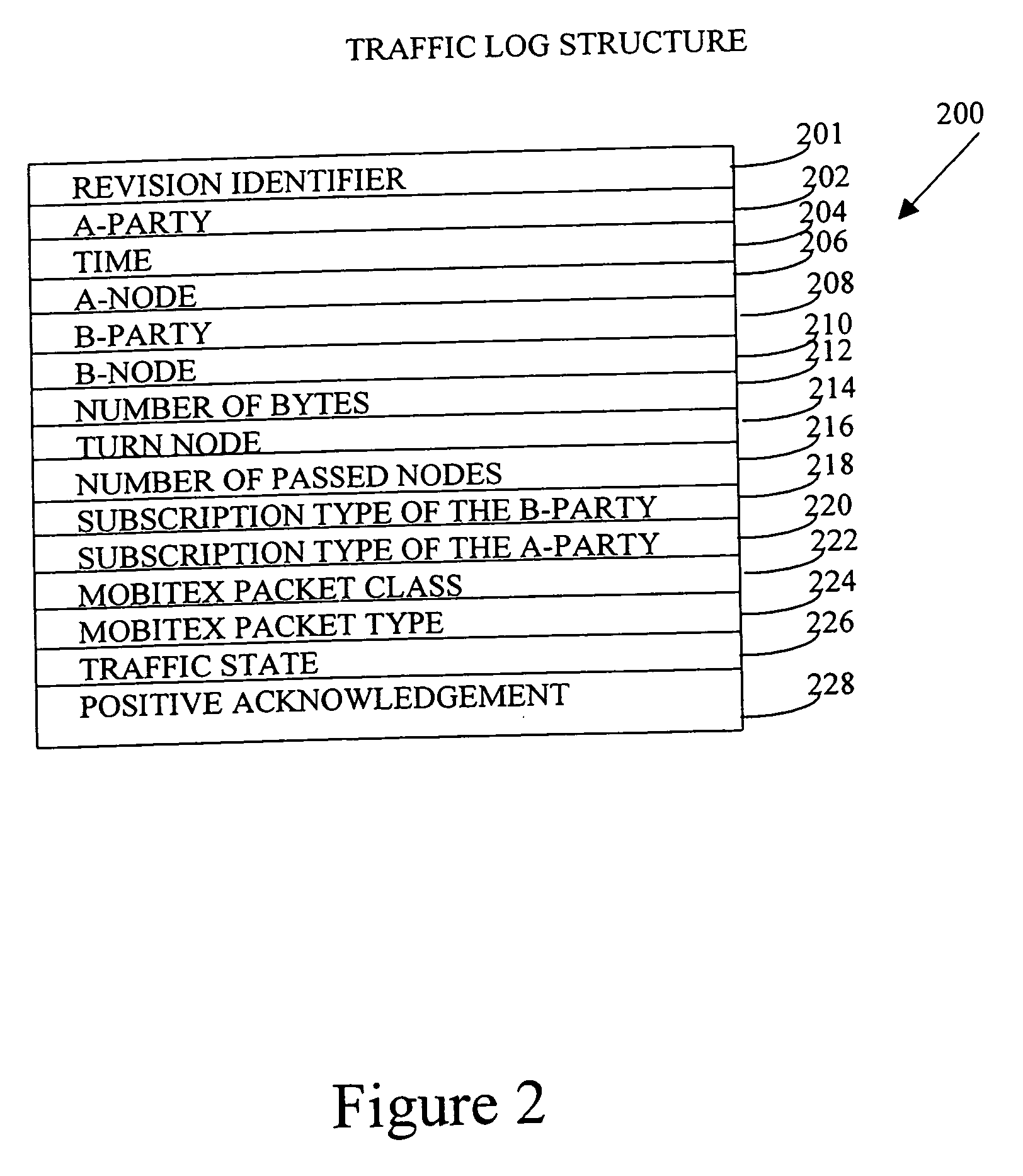

InactiveUS7562134B1Easily gleanedFacilitate trend analysisError preventionFrequency-division multiplex detailsTraffic capacityExchange network

A system for and method of analyzing the performance of a packet-switched network, the network automatically generating a traffic log each time a packet enters or exits the network and each traffic log including at least the time the traffic log was created, the addresses of the packet sender and packet recipient, and the entry and exit network nodes. A server collects a plurality of traffic logs, parses the available information therein and generates a plurality of histograms, each histogram being based on information gleaned from the plurality of traffic logs. The histograms may be representative of packet traffic passing through a host connected to the network, packet traffic passing through a node in the network or the amount of data that travels over a link between two nodes of the network. To increase the delivery speed of the histogram data from the server to a client, the histograms are preferably stored as flat files to achieve direct and rapid access to stored data.

Owner:BELLSOUTH INTPROP COR

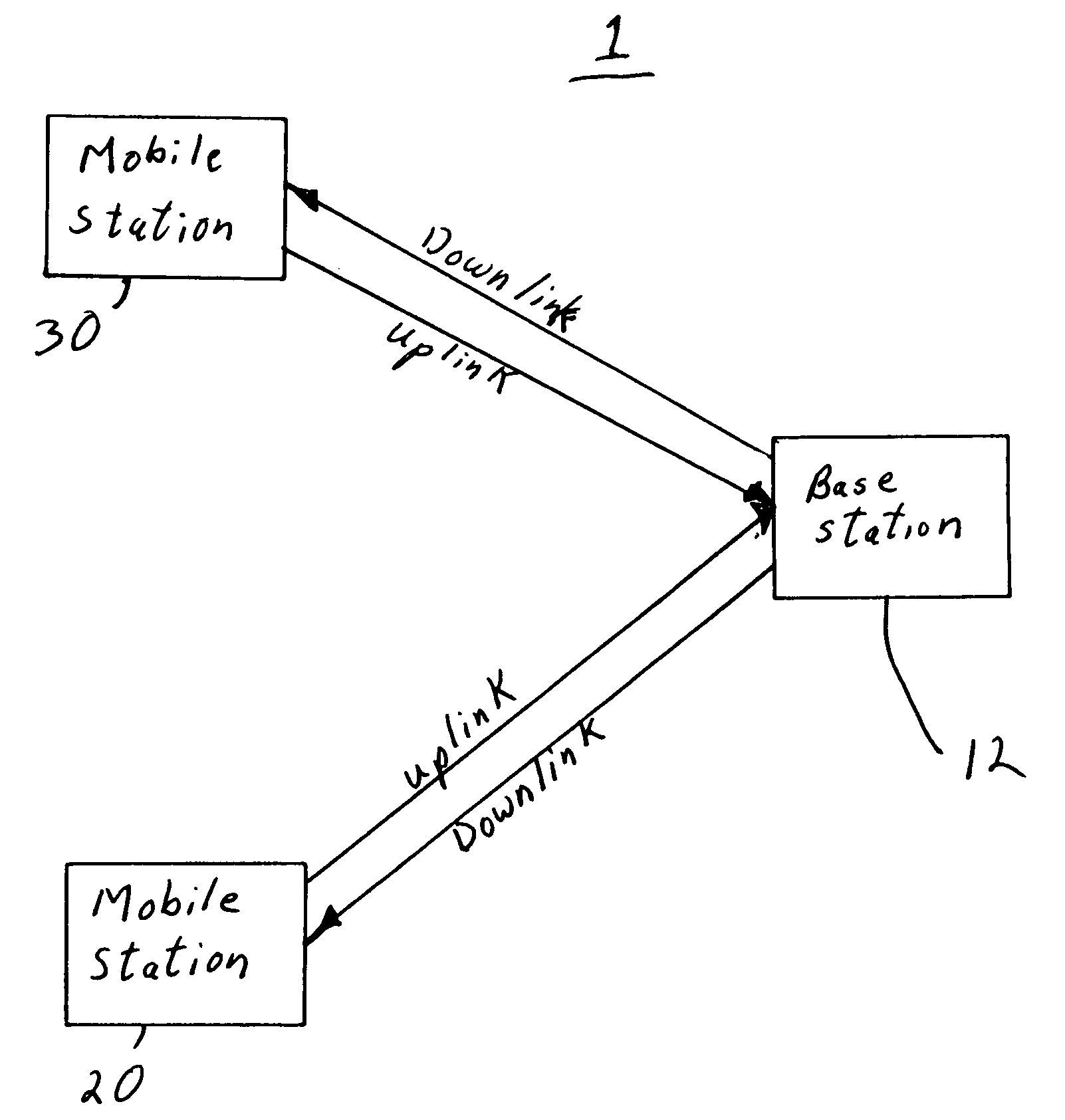

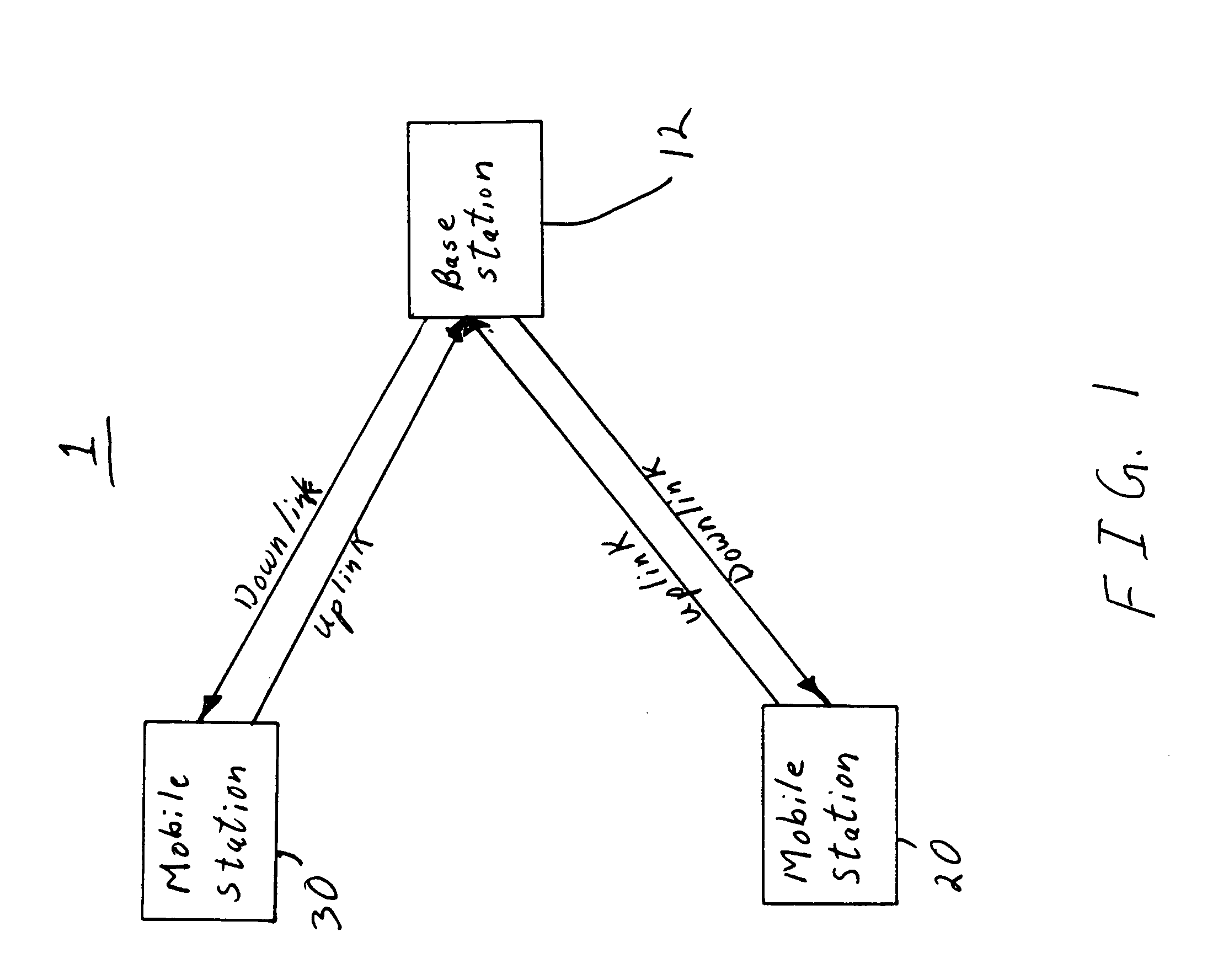

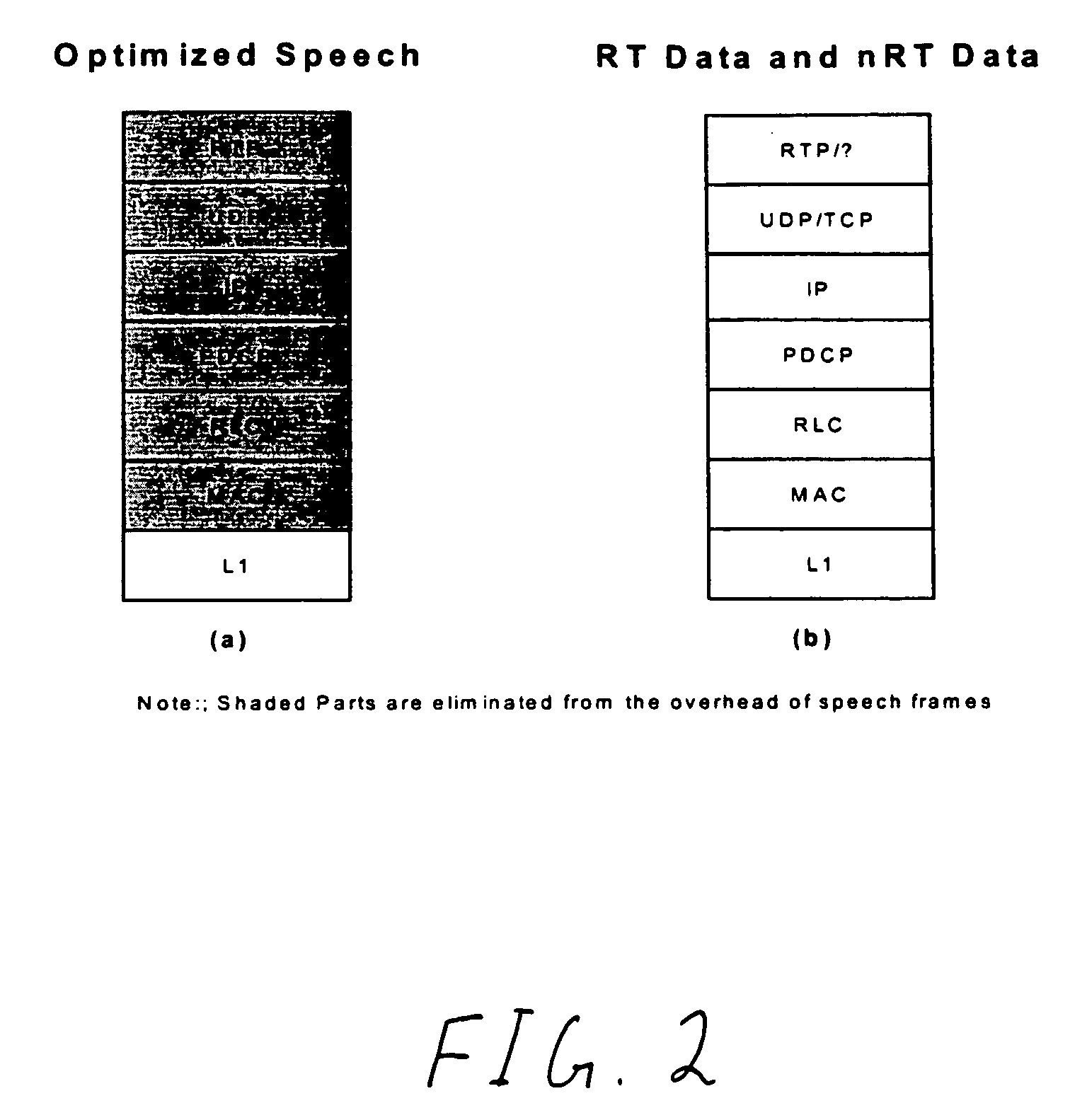

System for statistically multiplexing real-time and non-real-time voice and data traffic in a wireless system

ActiveUS6963544B1Effective movementPower managementFrequency-division multiplex detailsMultiplexingNon real time

A system for providing statistical multiplexing of speech, other real-time data services and non-real-time data services for point to point and point to multipoint communications. The system has fast access and assignment procedures that allow the multiplexing of real-time, delay-critical data services with non-real-time data services. Continuity of periodic control channels across speech talkspurt and silence periods for conversational voice is maintained to carry signal measurement reports, channel quality feedback, and “comfort” noise information between different parts of the system.

Owner:NOKIA TECHNOLOGLES OY

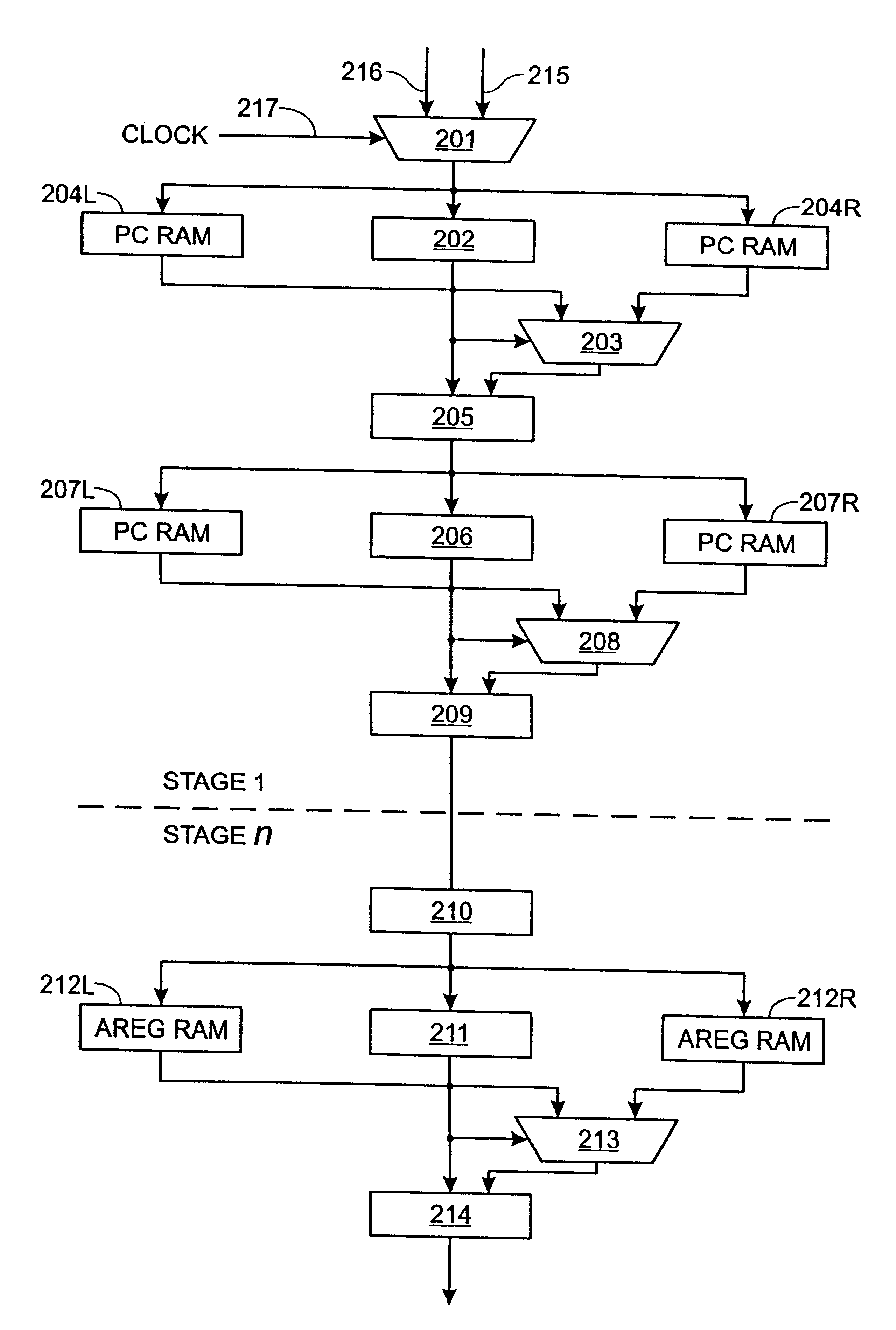

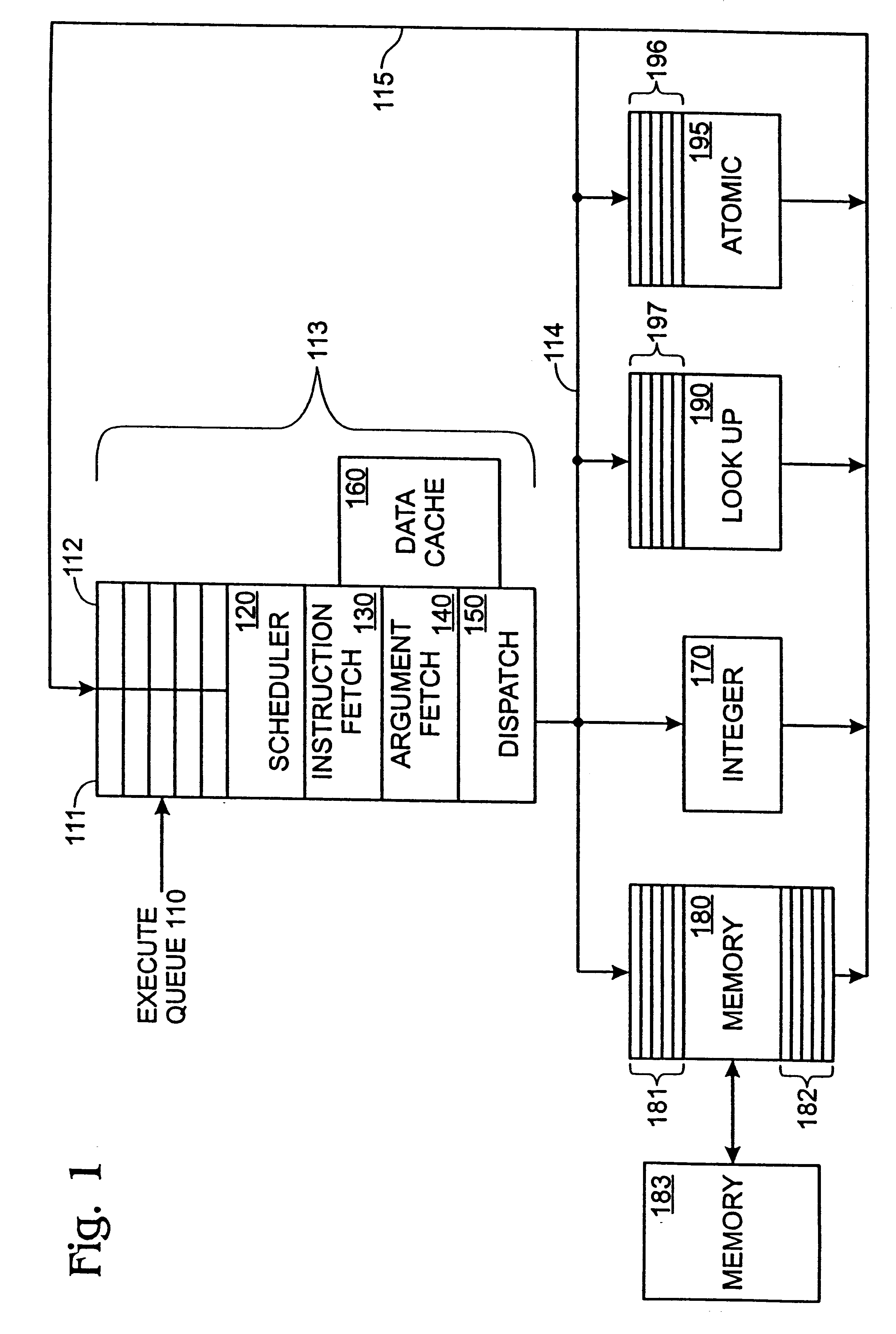

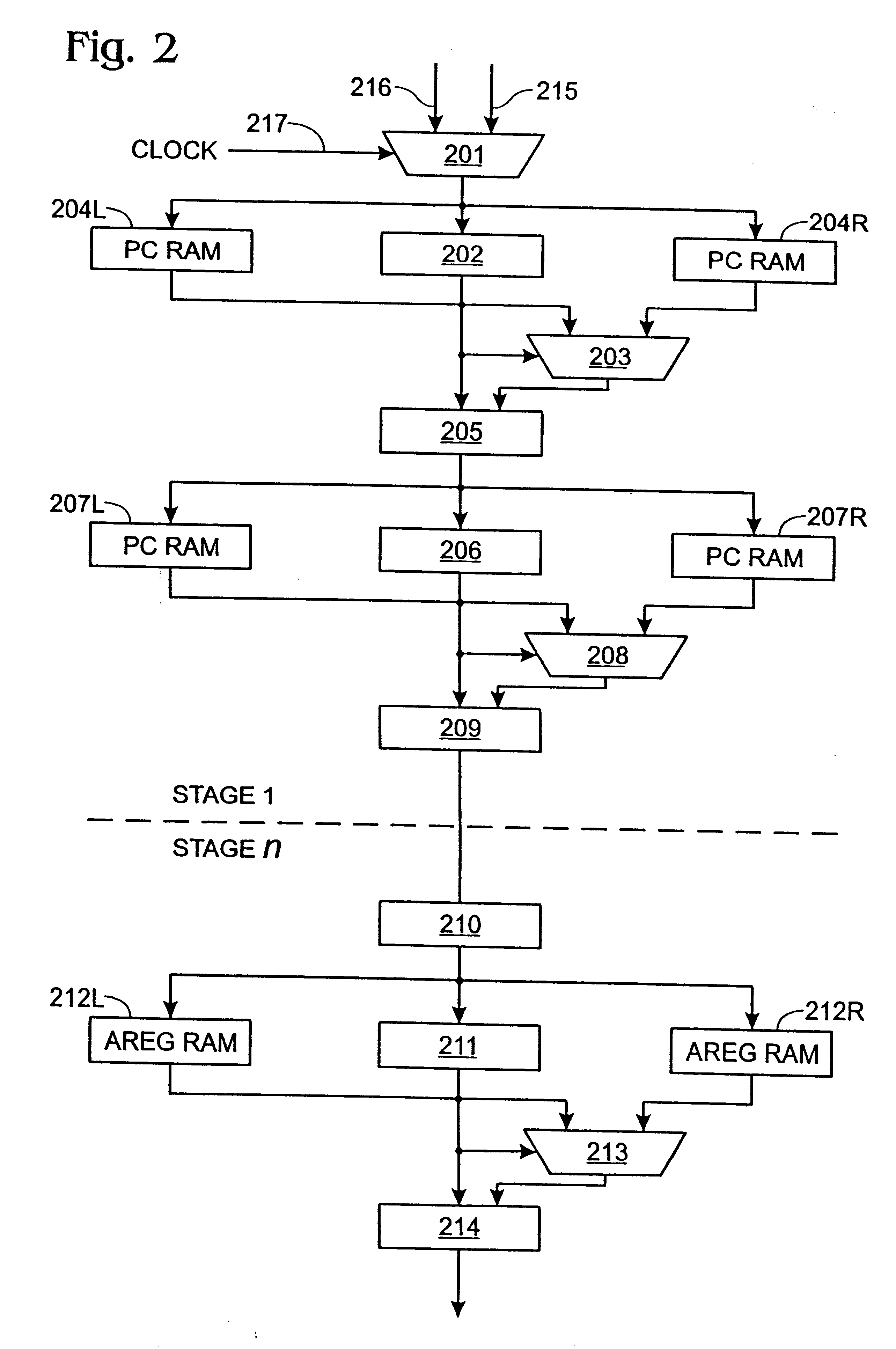

Distributed pipeline memory architecture for a computer system with even and odd pids

InactiveUS6209020B1General purpose stored program computerMultiprogramming arrangementsAccess timeComputerized system

A computer system architecture in which each processor has its own memory, strategically distributed along the stages of an execution pipeline of the processor, to provide fast access to often used information, such as the contents of the address and data registers, the program counter, etc. Memory storage is strategically located in close physical proximity to a stage in an execution pipeline at which memory is commonly or repeatedly accessed. Coupled to the pipeline at various stages are small memory cells for storing information that is consistently and repeatedly requested at that stage in the execution pipeline. The speed of the execution pipeline in a processor is critical to overall performance of the processor and the computer architecture of the present invention as a whole. To that end, the clock cycle time at which the pipeline is operated is increased as much as the operating characteristics of the logic and associated circuitry will allow. Generally, access times for memory are slower than the clock cycle times at which the pipeline logic can operate. Thus, there is a point of diminishing return at which increasing the clock cycle time of the pipeline is less advantageous if the pipeline must wait for memory access to complete. Thus, there is provided two sets of strategically located memory cells distributed along the execution pipeline of a processor, and alternately accesses the memory cells.

Owner:NORTEL NETWORKS LTD

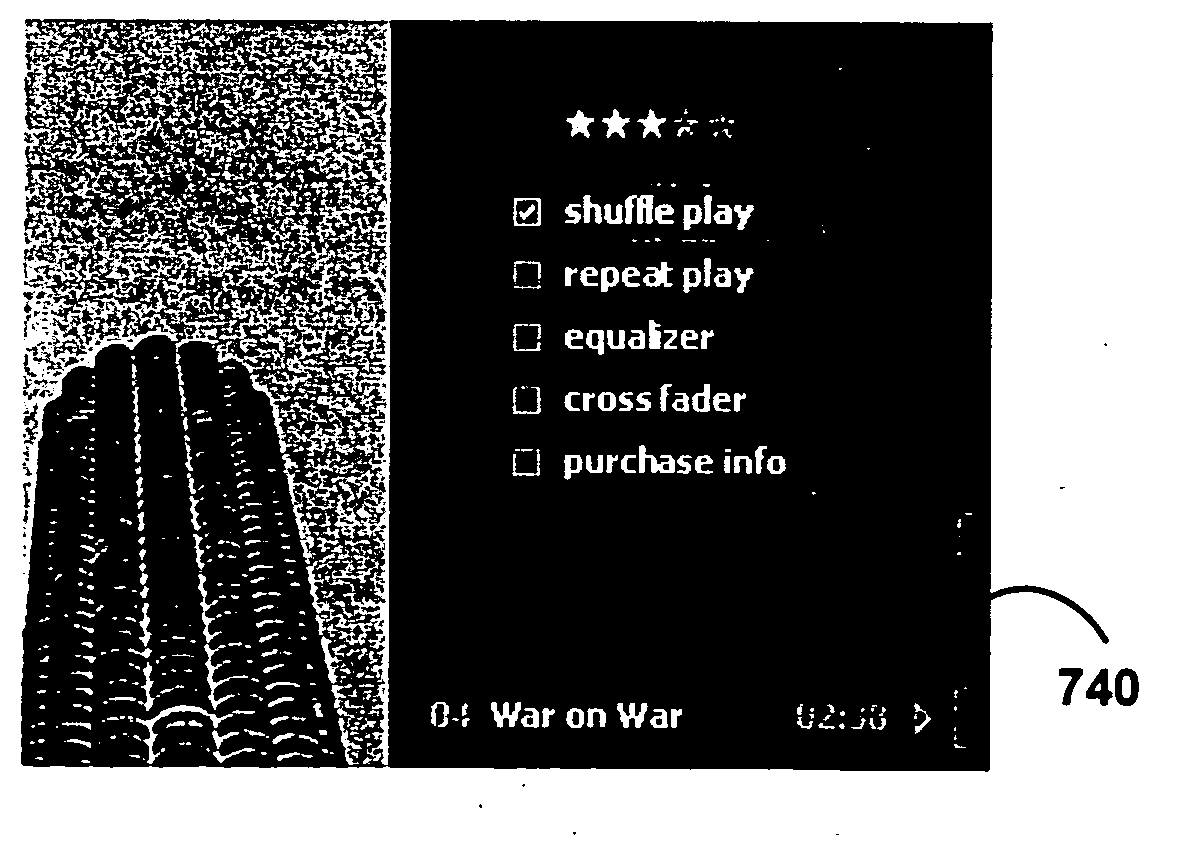

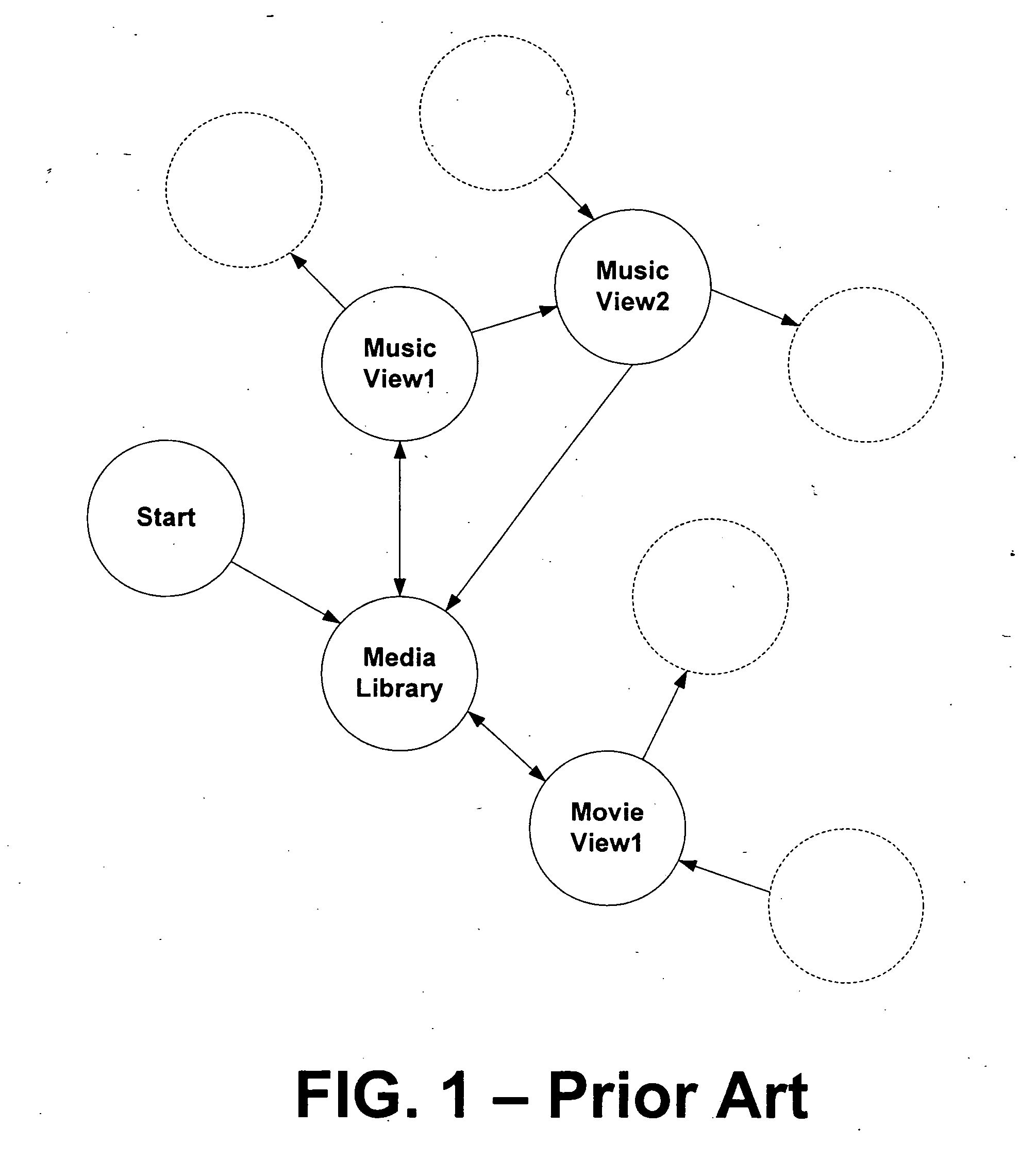

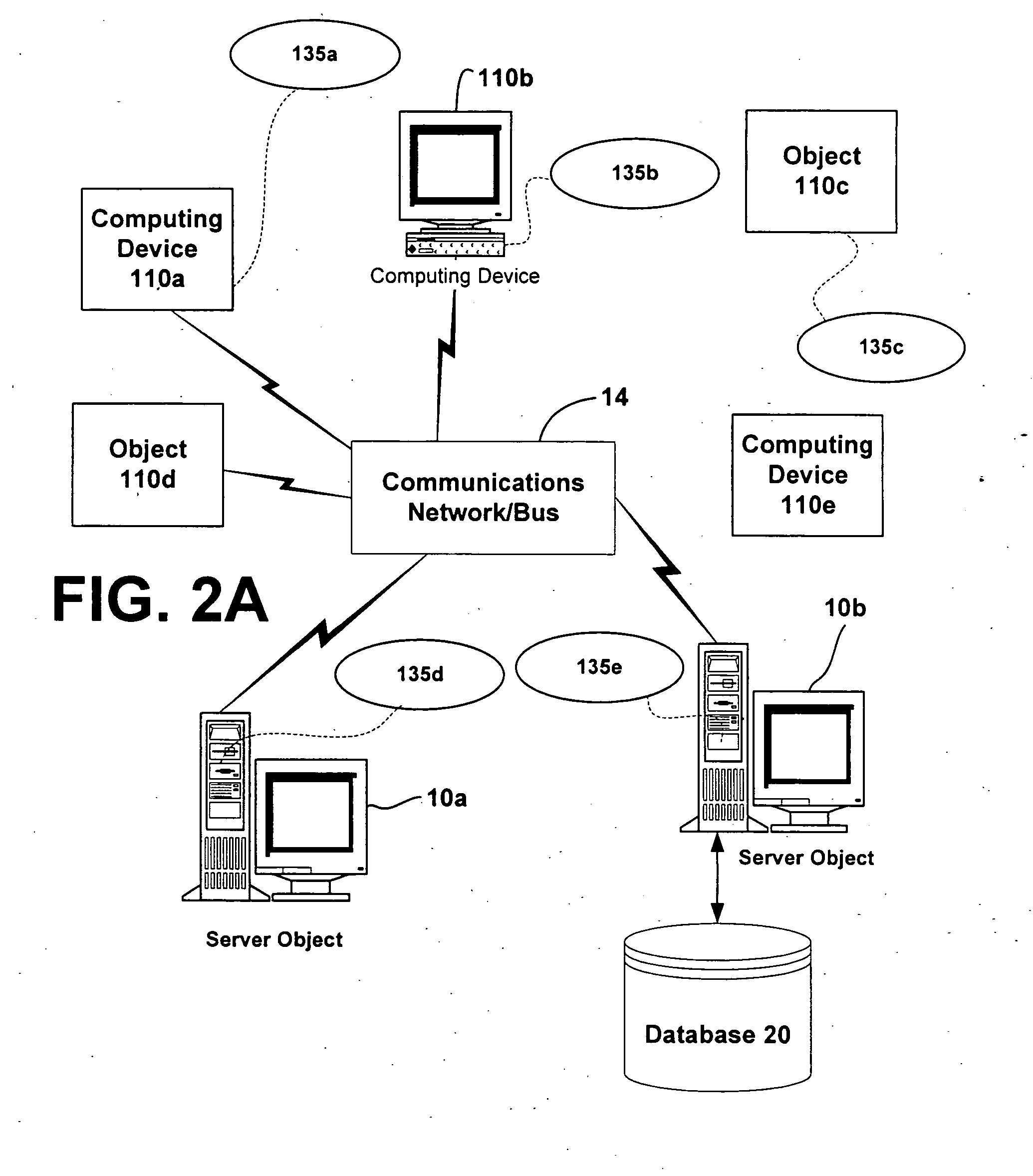

Systems and methods for providing alternate views when rendering audio/video content in a computing system

Systems and methods for transitioning between alternate views when rendering A / V content in a computing system are provided. In various embodiments, a “Now Playing” state is exposed to a user experiencing media on a media device via a user interface, wherein the “Now Playing” state has a plurality of associated “Now Playing” views. The user interface allows the user to change “Now Playing” views based on media type and, if desirable, offer quick access settings. Advantageously, when transitioning between or cycling through the “Now Playing” views, the state of the user interface remains the “Now Playing” state.

Owner:ZHIGU HLDG

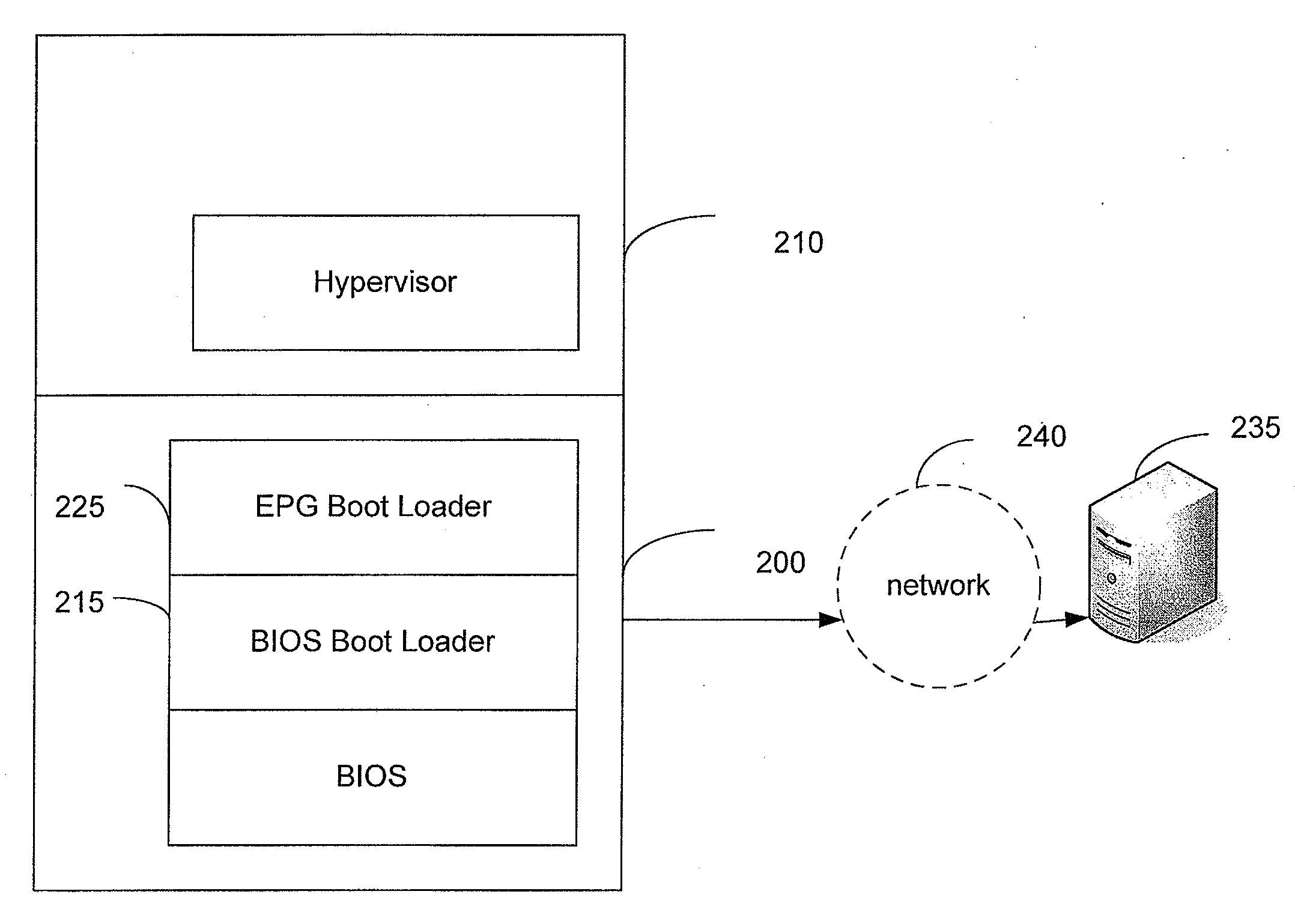

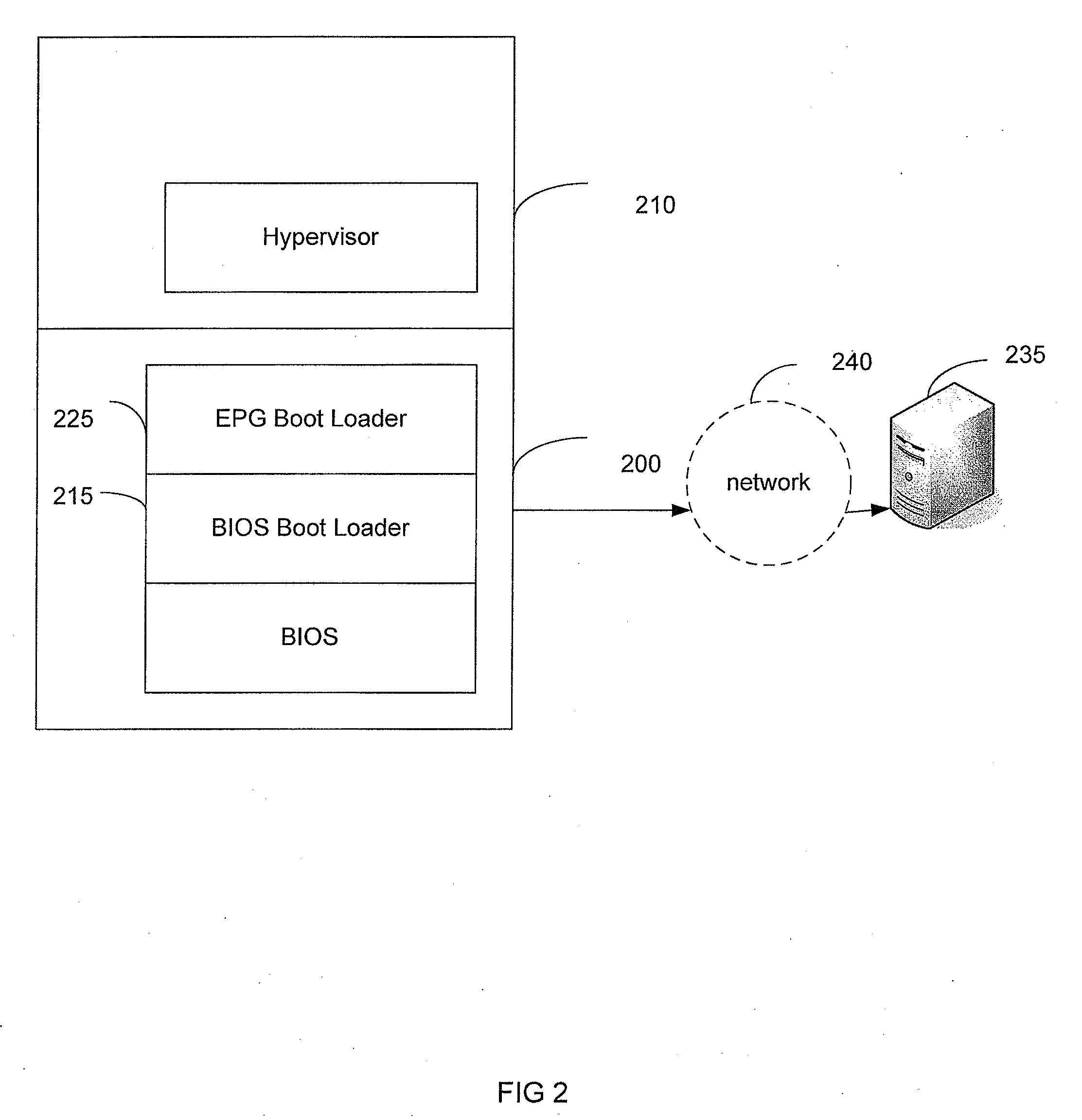

Quick access to virtual applications

InactiveUS20090199132A1Digital computer detailsBootstrappingOperational systemEmbedded operating system

An embedded operating system (OS) displays a user interface (UI) without waiting for the host OS to fully load. In one embodiment, the UI comprises icons for applications, advertisements, and browsers already configured with a URL. In one embodiment, the pre-configured browsers are set by the manufacturer. In another embodiment, the user can specify pre-configured browsers. In one embodiment, the icon owner pays for displaying an icon. The icon can be a static or a dynamic icon. Dynamic icons are downloaded from a file server.

Owner:SPLASHTOP INC

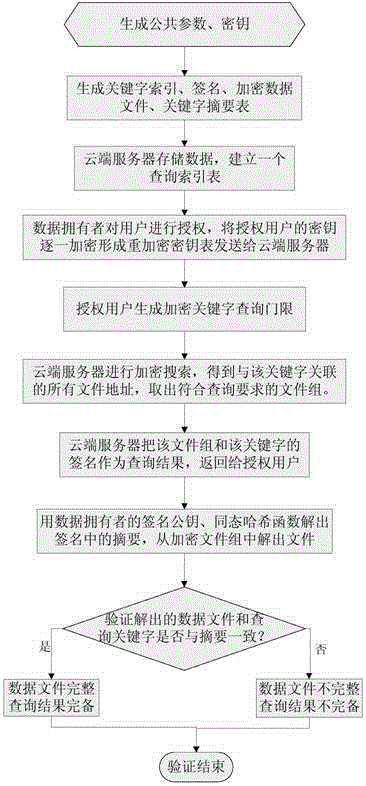

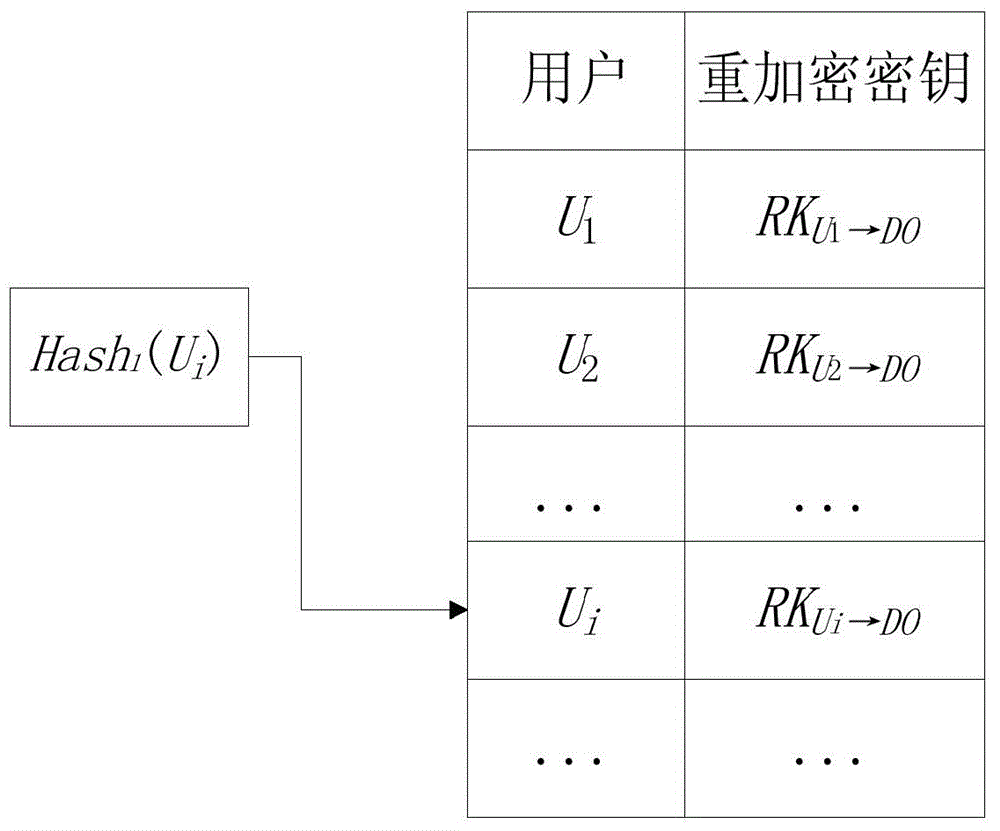

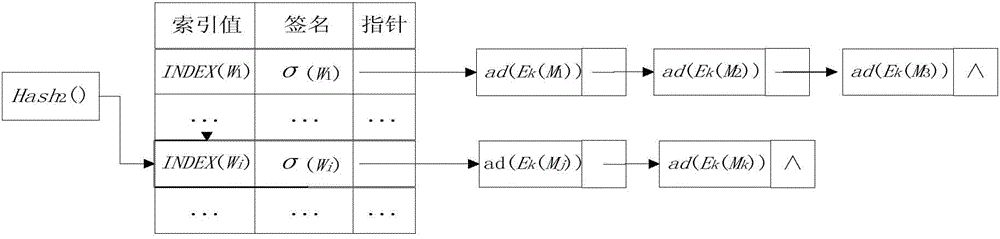

Multi-user cloud encryption keyboard searching method capable of verifying integrity and completeness

ActiveCN104394155AQuery does not affectCompleteness verificationUser identity/authority verificationOther databases queryingData integrityPassword

The invention is mainly used for searching a searchable encryption technology under a public key password system, and discloses a multi-user cloud encryption keyboard searching method capable of verifying integrity and completeness. The method can be used for verifying the search result completeness and the outsourced data integrity under the cloud environment and setting the multi-user authority. The method can be used for realizing the verification of the search result completeness and the outsourced data integrity by using signatures to bind keyword indexes and associated encryption files thereof, realizing multi-user privacy query by using a re-encryption technology and dynamically updating the query authority of the user. Moreover, the index structure and the query mechanism of the encrypted file are further optimized, so that the query efficiency is improved by using hash query in the query process, and the rapid access to the cloud data is realized.

Owner:广州市瑞玛信息技术有限公司 +1

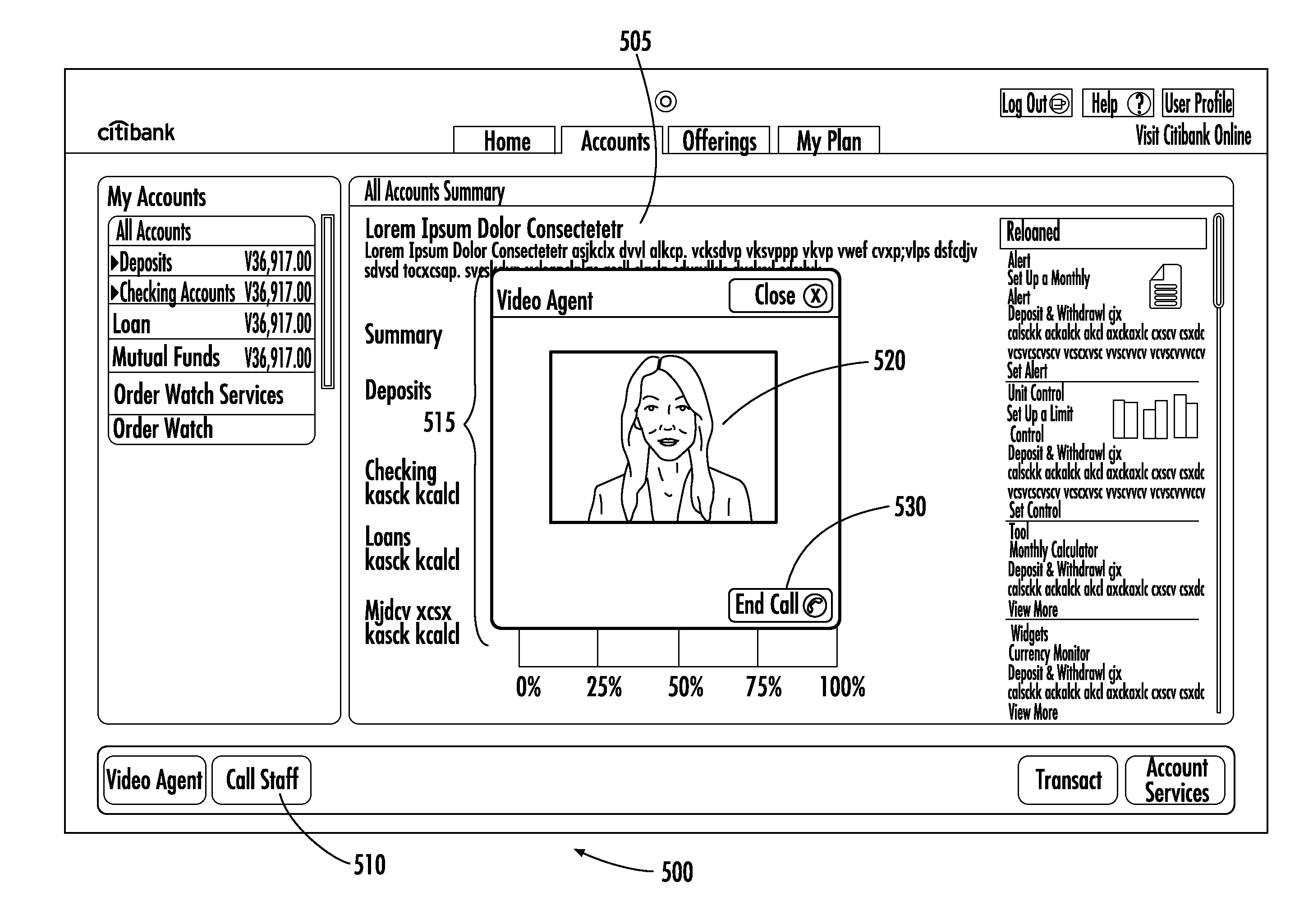

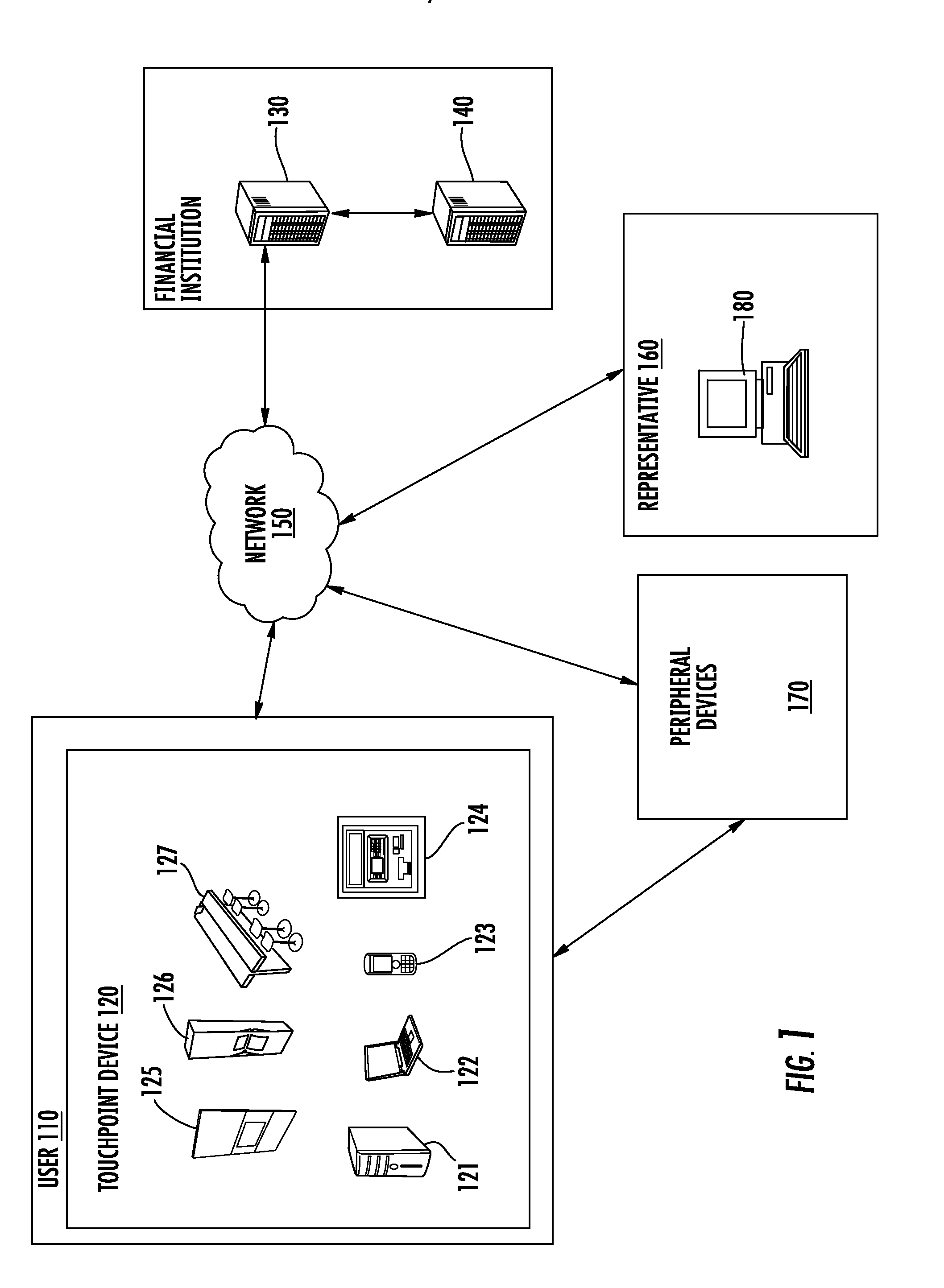

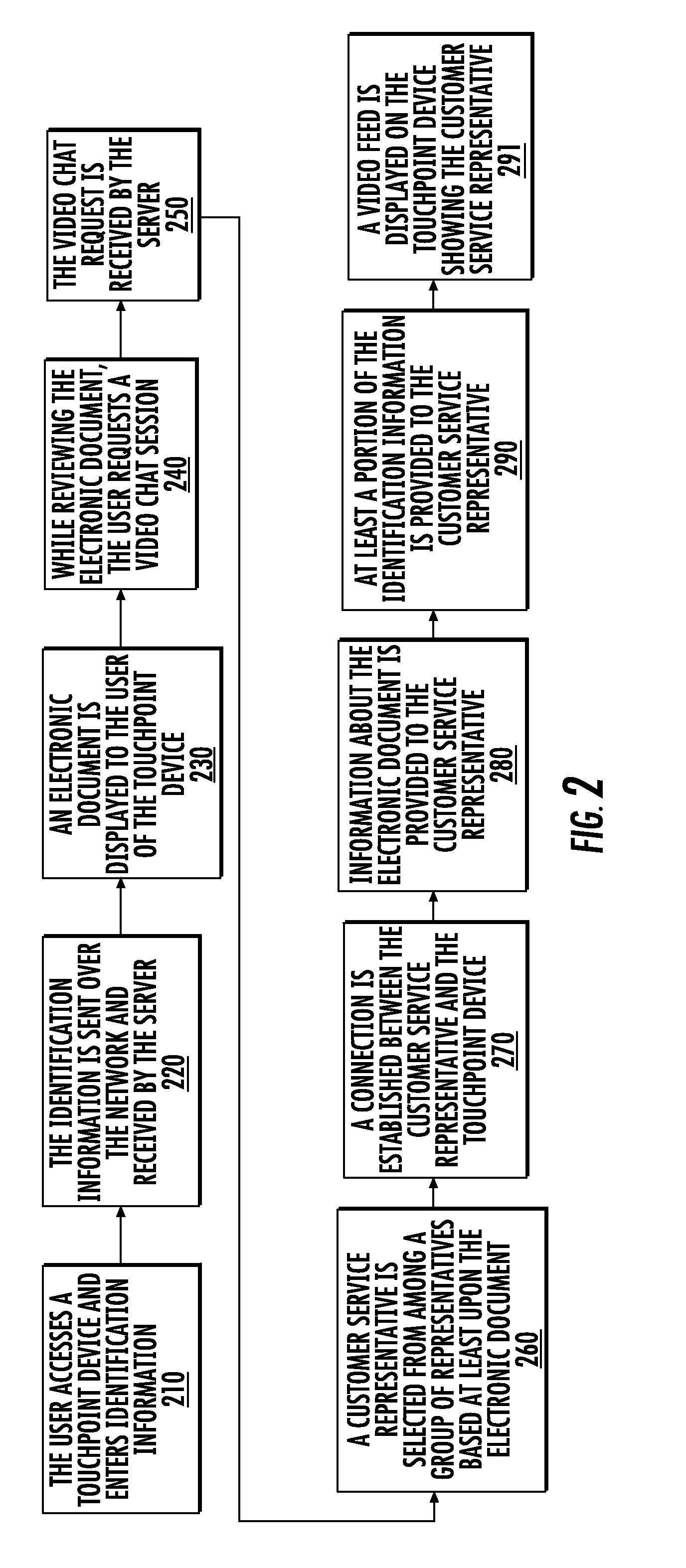

System and Method for Providing Customer Support on a User Interface

ActiveUS20110249081A1Service is often complicatedOvercomes drawbackFinanceManual exchangesElectronic documentRapid access

Embodiments described can more effectively complete complicated service transactions in a more efficient manner by having a team of well-trained professionals who are instantly “streamed” into any location as necessary. A two-way communication system can provide instant or quick access to the right expert at the right point in time, thereby converting what might otherwise be a negative customer experience into a positive sales and service opportunity. A computer implemented method for providing customer support comprises receiving, by a touchpoint device, identification information from a user of the touchpoint device; receiving the identification information; providing an electronic document to the user; receiving an input from the user requesting a session with a representative; selecting a representative based at least in part on the electronic document; providing information about the electronic document to the representative; and establishing a connection between the representative and the touchpoint device.

Owner:CITIBANK

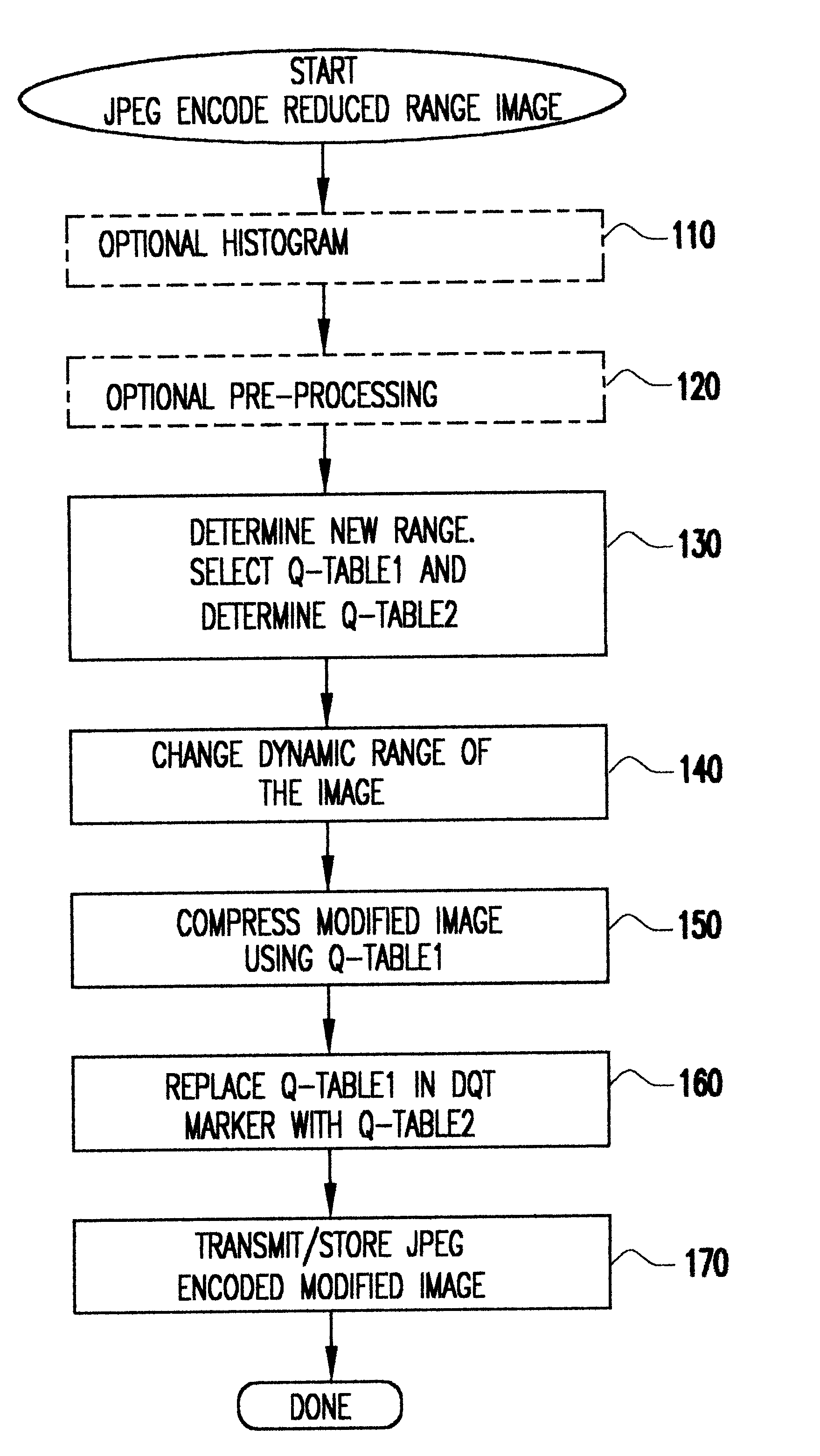

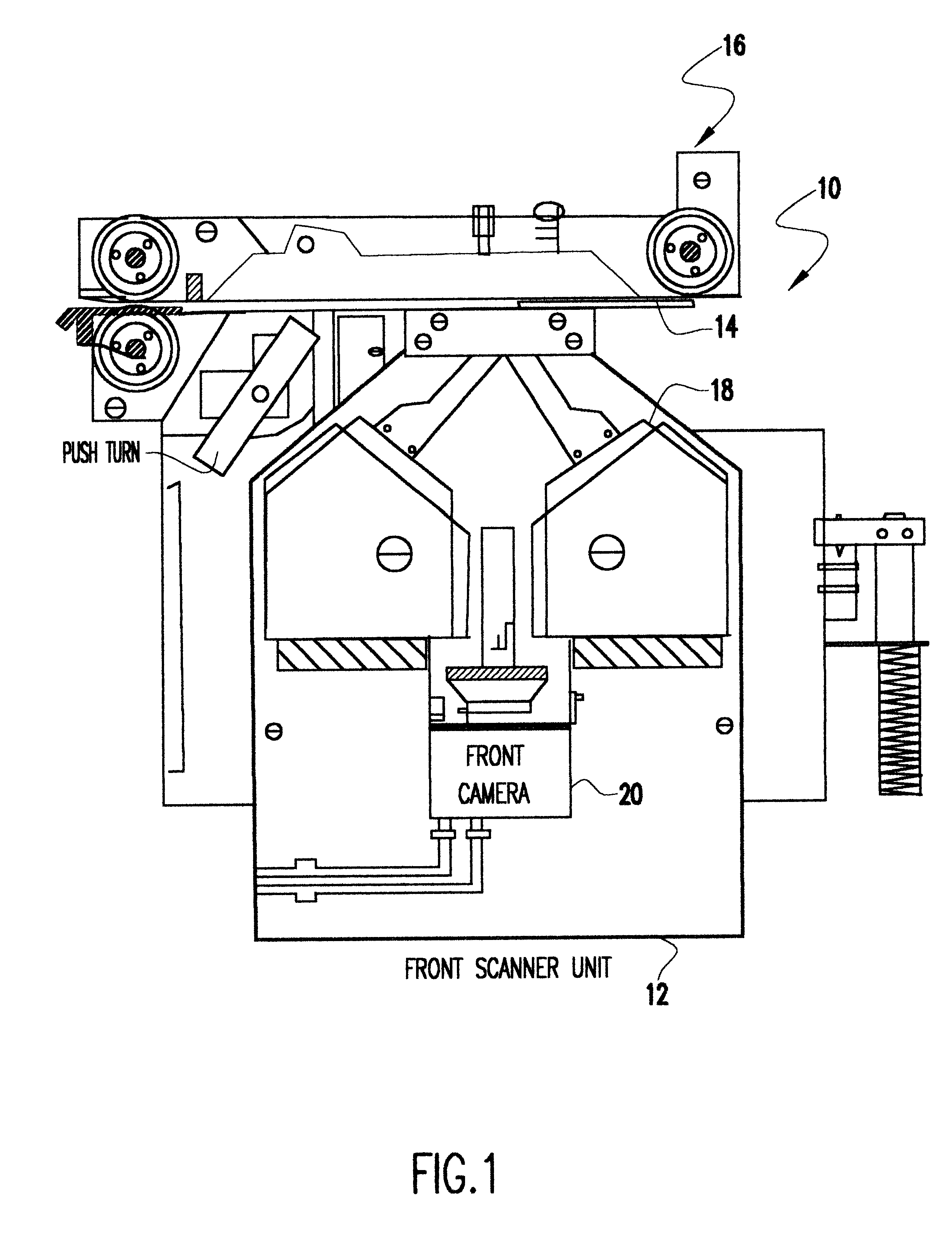

Enhanced compression of documents

InactiveUS6606418B2Reduce storage costsEnhance reconstructed contrastCharacter and pattern recognitionTelevision systemsImaging analysisComputer graphics (images)

Increased and potentially extreme compression of documents is achieved by reducing / remapping the dynamic range of the document image possibly together with further image analysis and pre-processing and storing the document together with a substituted table of values chosen to restore or enhance the dynamic range of the document image. Increased or extreme compression is provided notwithstanding multiple image tones (e.g. colors or grey scale levels) even at low contrast within a document, such as a personal check. Such increased compression allows document images to be maintained in rapid-access memory for extended periods without increased storage costs.

Owner:INT BUSINESS MASCH CORP

Unified interest layer for user interface

ActiveUS7761800B2Assisting understandingInstrument arrangements/adaptationsExecution for user interfacesDashboardGraphical user interface

A user-activatable dashboard (also referred to as a unified interest layer) contains any number of user interface elements, referred to herein as “widgets,” for quick access by a user. In response to a command from a user, the dashboard is invoked and the widgets are shown on the screen. The user can activate the dashboard at any time, causing the dashboard to temporarily replace the existing user interface display on the user's screen. Once the dashboard has been activated, the user can interact with any or all of the widgets, and can configure the dashboard by adding, deleting, moving, or configuring individual widgets as desired. When the user wishes to return to the normal user interface he or she was working with, the user issues a command causing the dashboard to be dismissed. Once the dashboard has been dismissed, the previous user interface state is restored, allowing the user to resume normal interactions with the operating system.

Owner:APPLE INC

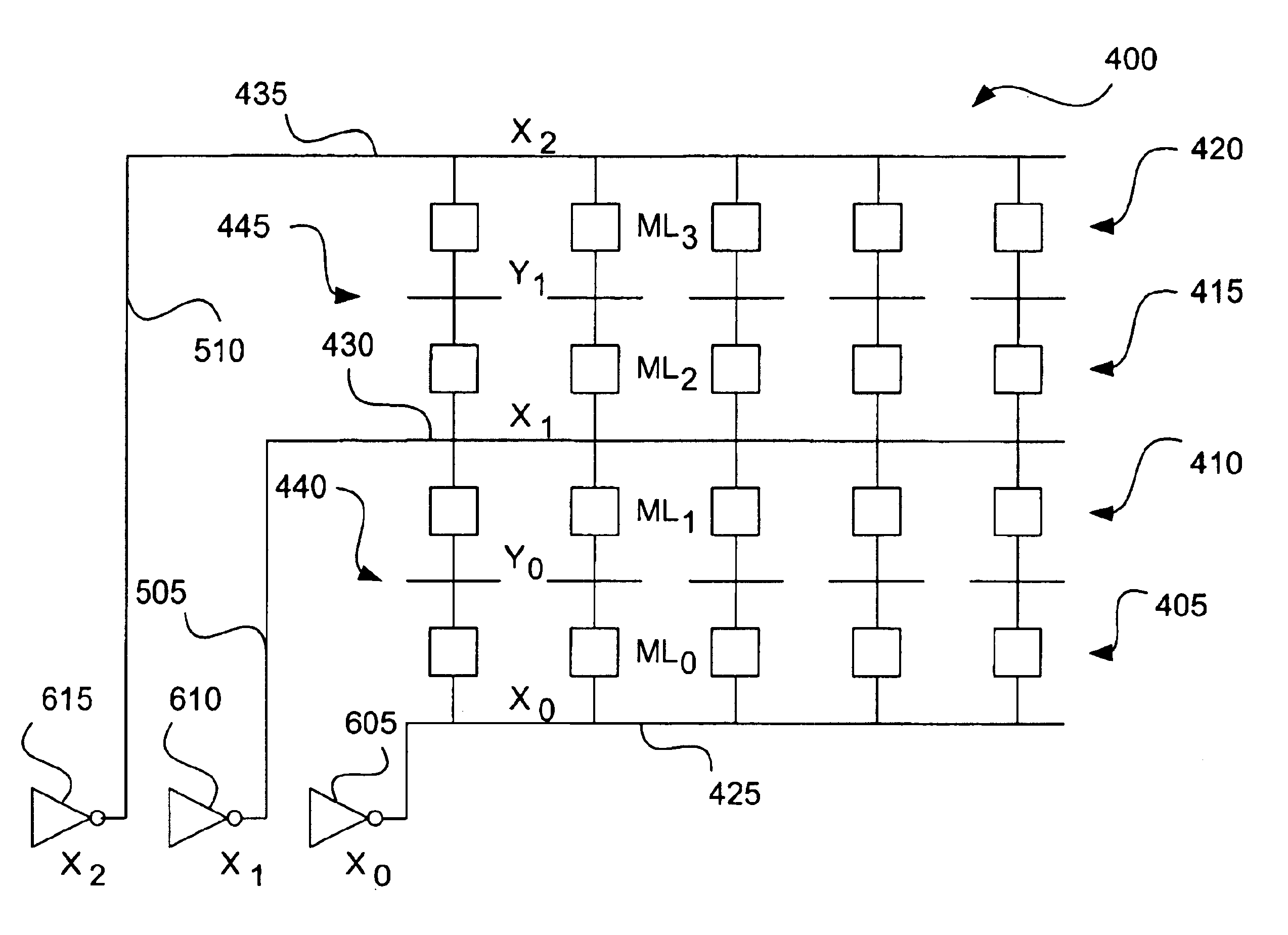

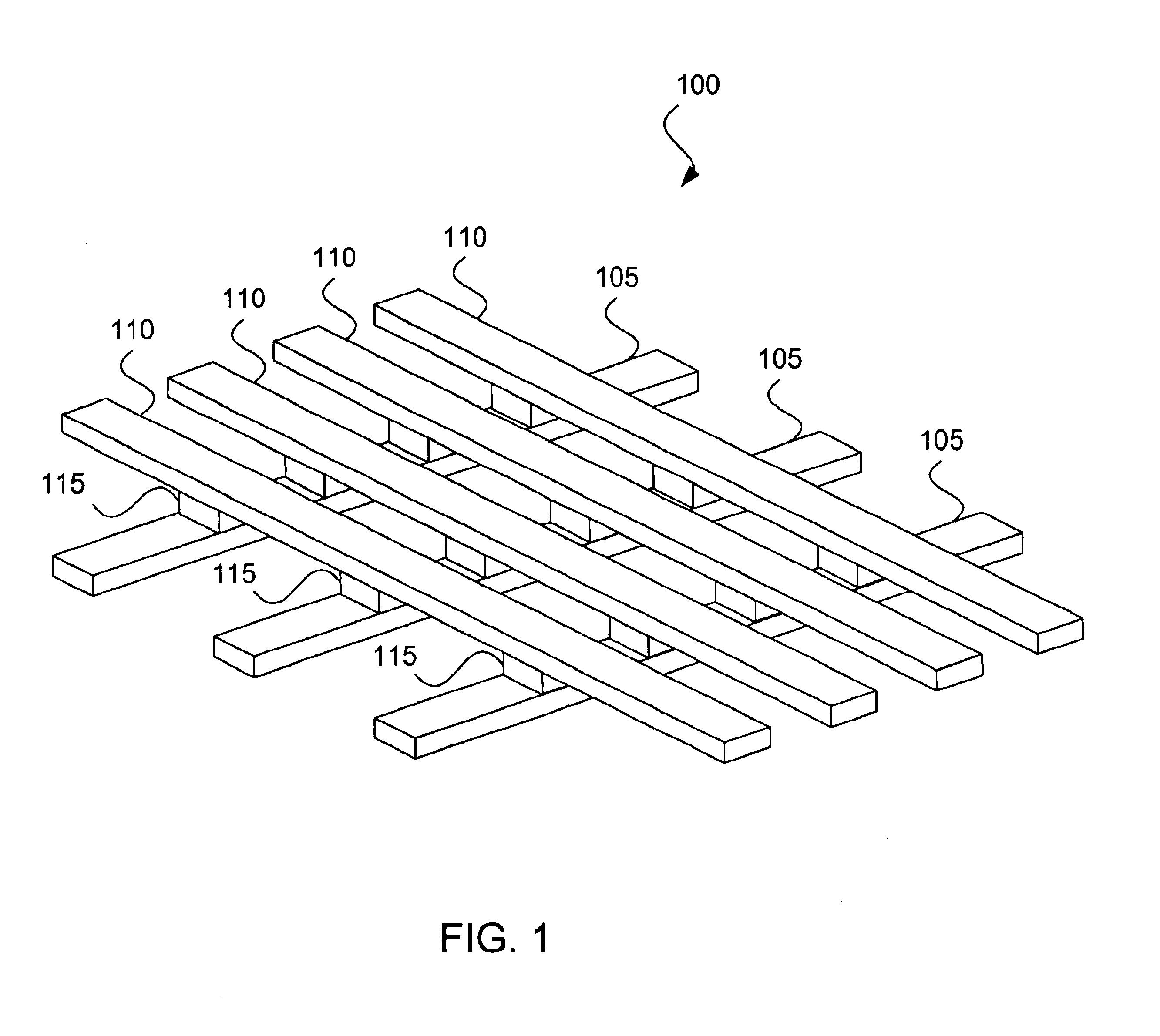

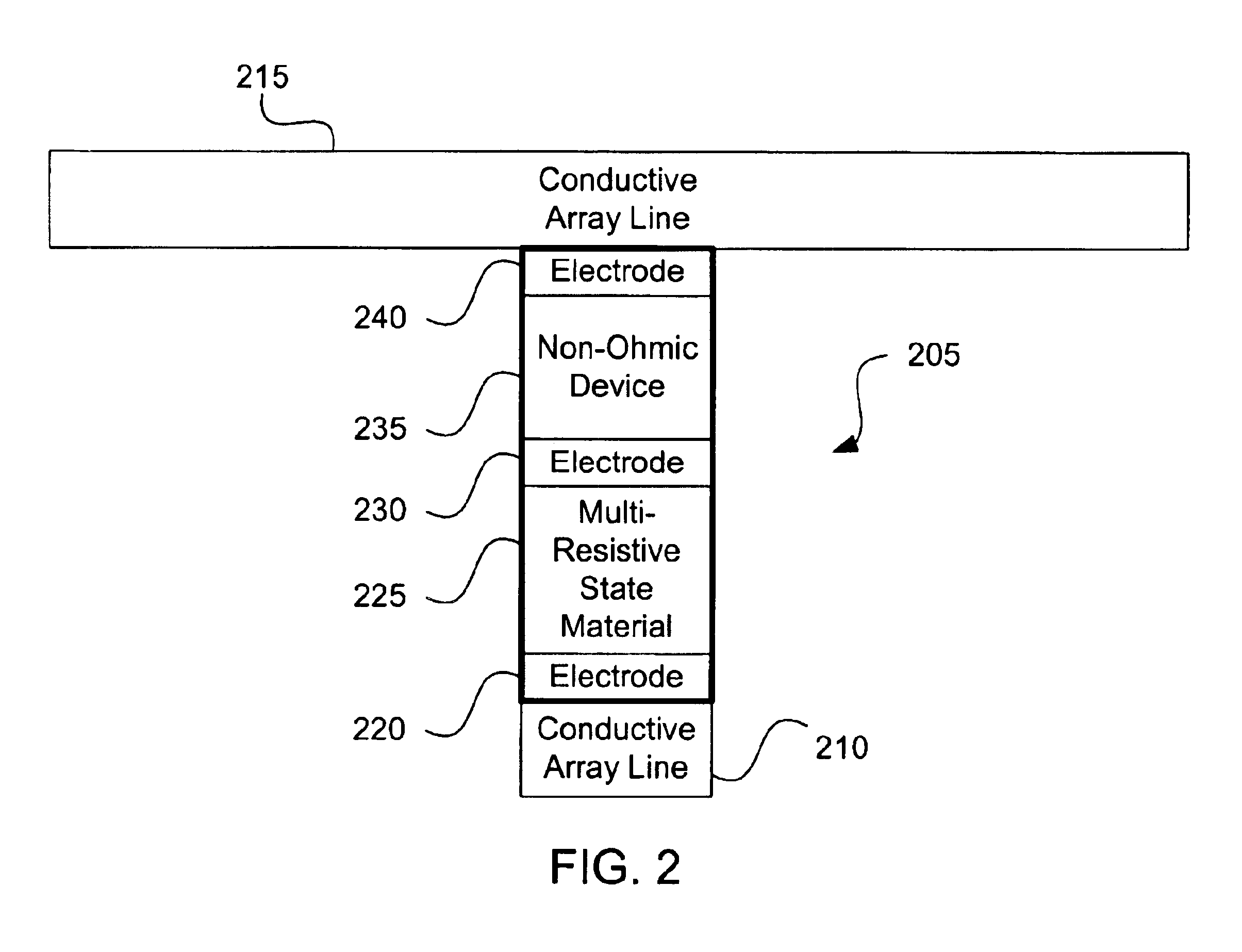

Cross point memory array with fast access time

Cross point array with fast access time. A cross point array is driven by drivers on a semiconductor substrate. The drivers for either a single-layer cross point array or for the bottom layer of a stacked cross point array can be positioned to improve access time. Specifically, if the x-direction drivers are positioned in the middle of the x-direction conductive array lines and the y-direction drivers are positioned in the middle of the y-direction conductive array lines, the access time will be improved.

Owner:UNITY SEMICON

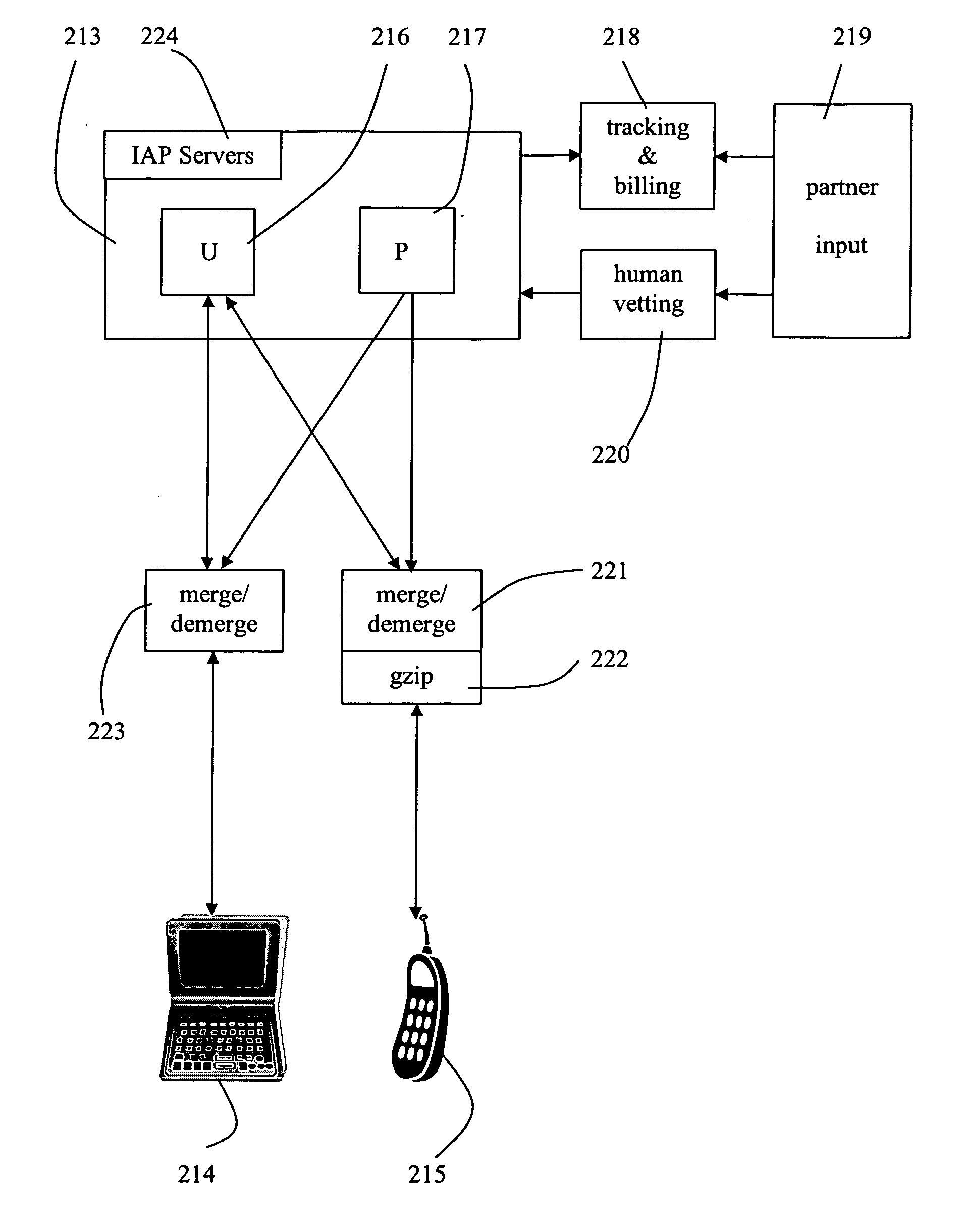

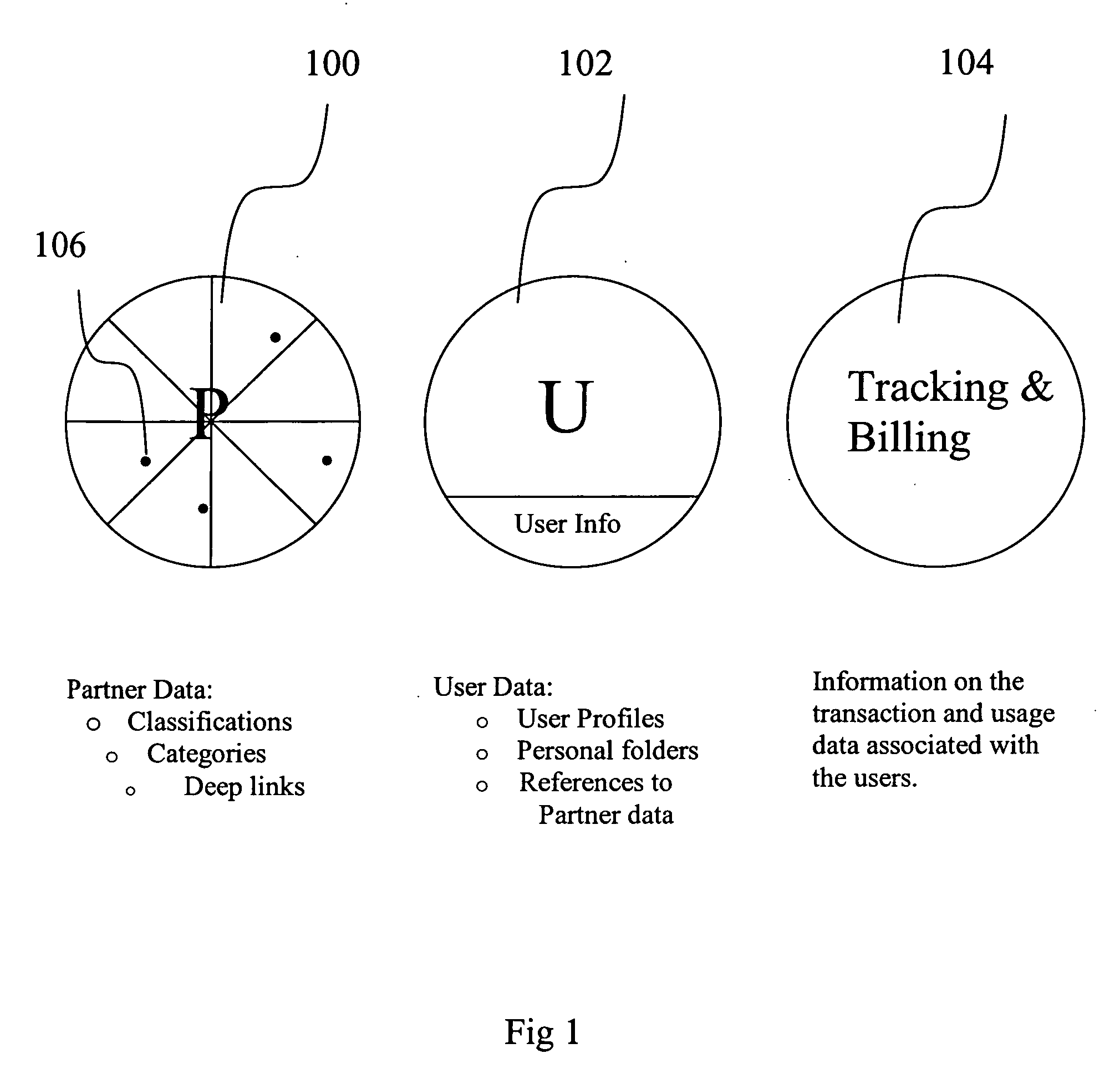

Accessing information

InactiveUS20070198741A1Shorten the timeMultiple digital computer combinationsWebsite content managementWeb siteInternet users

The present invention relates to a method of providing direct access to webpages of an internet website, of the storage of the links to webpages, and to the evaluation of webpages. The present invention also relates to a mobile device. Methods and apparatus both fall within the scope of the invention. In particular, the present invention relates to systems, methods, apparatus and a software solution for providing internet users with a more rapid access to web pages within an internet website by providing users with their own searchable Personal Internet Directory (PID). The directory is preferably tailored to the preferences of individual users or classes of user and is searchable by the user via cached entries local to the user.

Owner:INSTANT ACCESS TECH

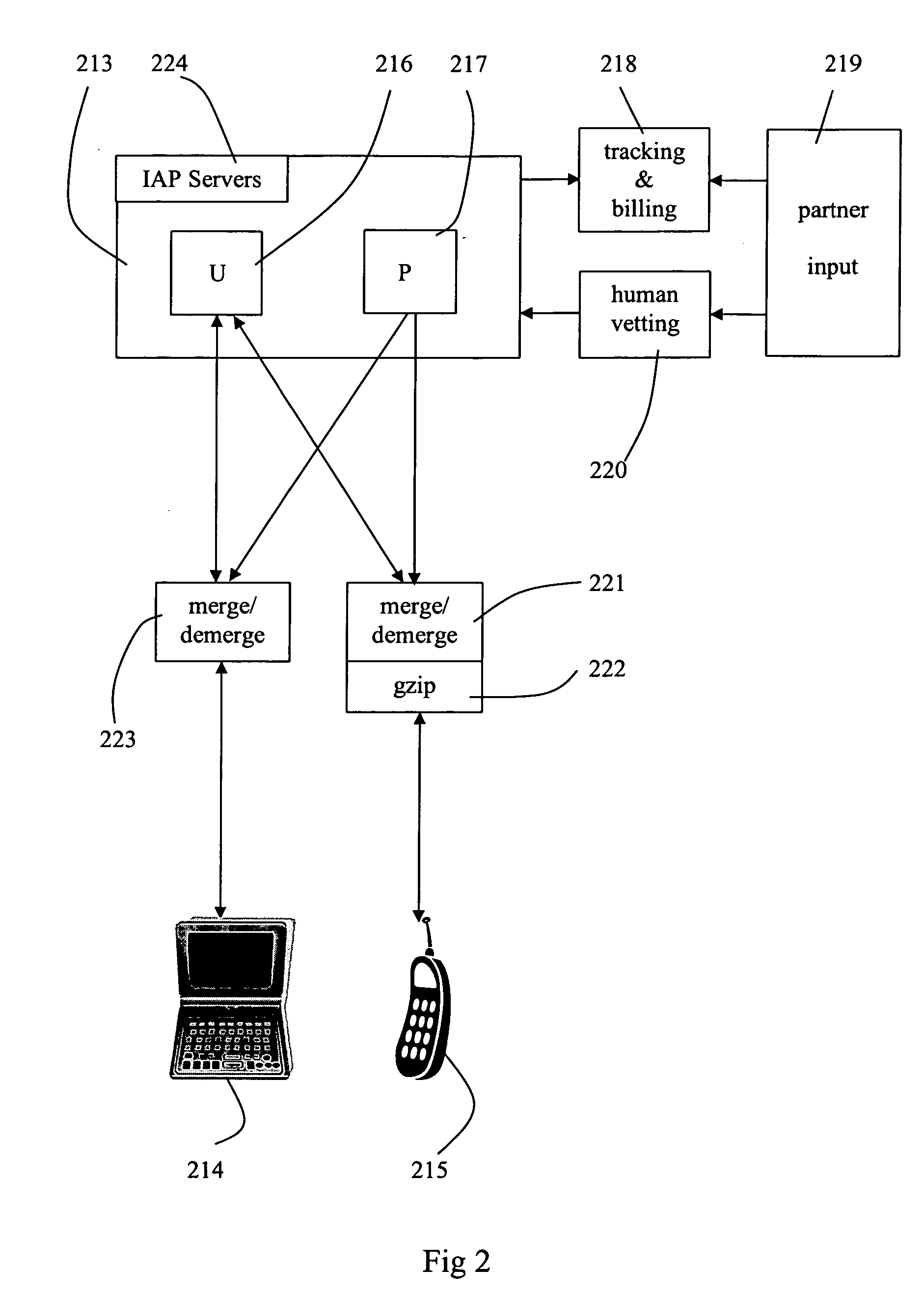

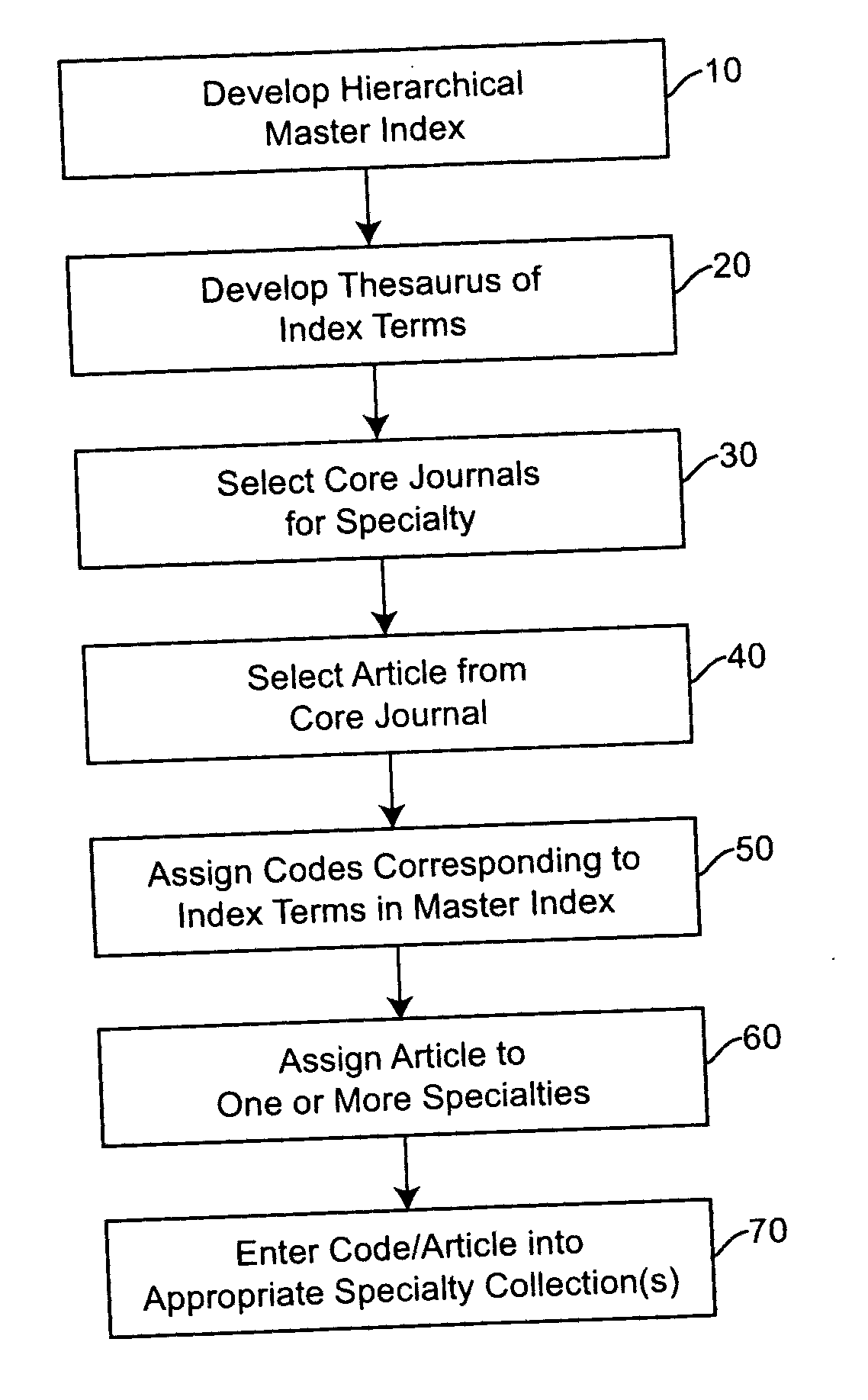

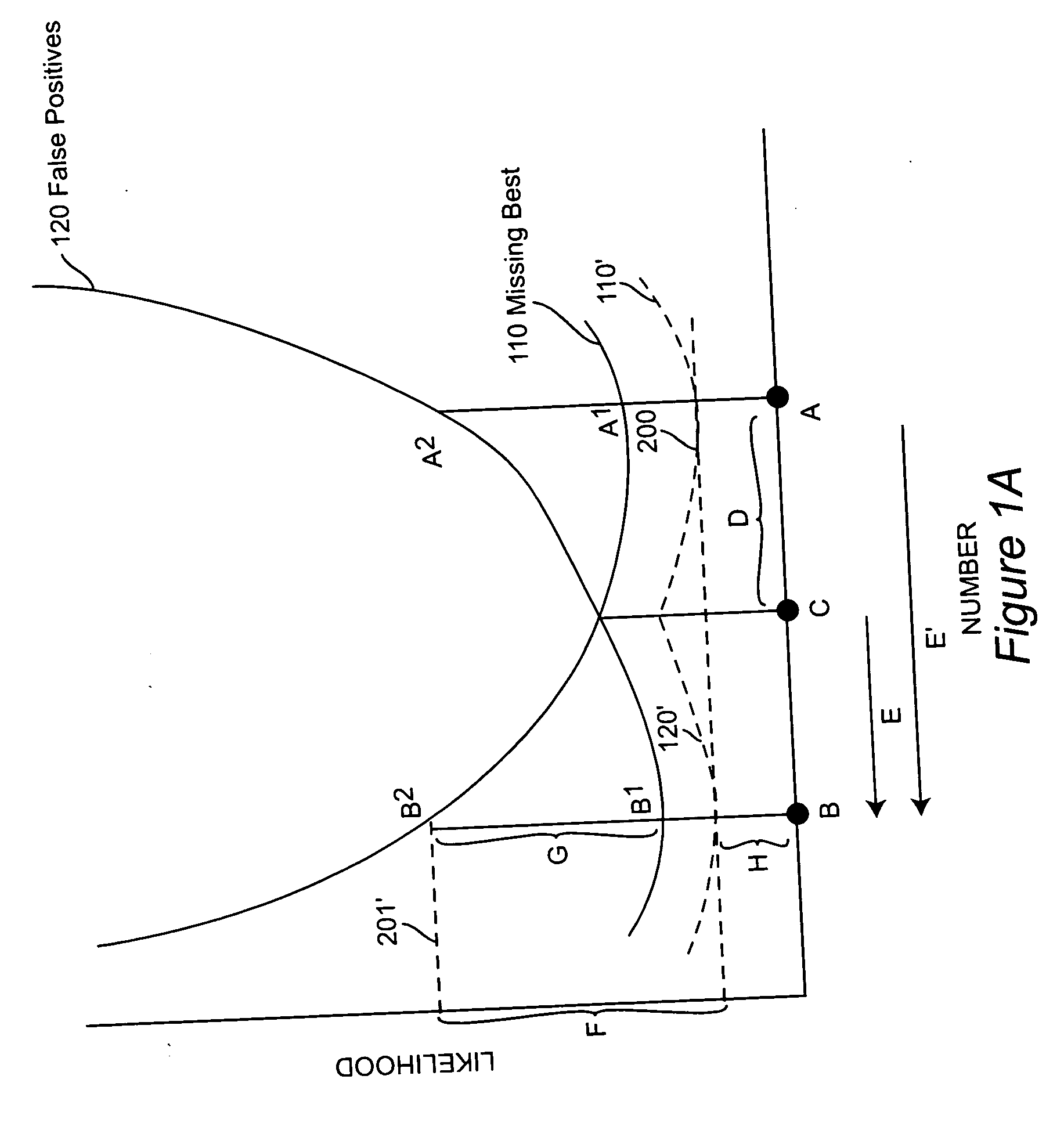

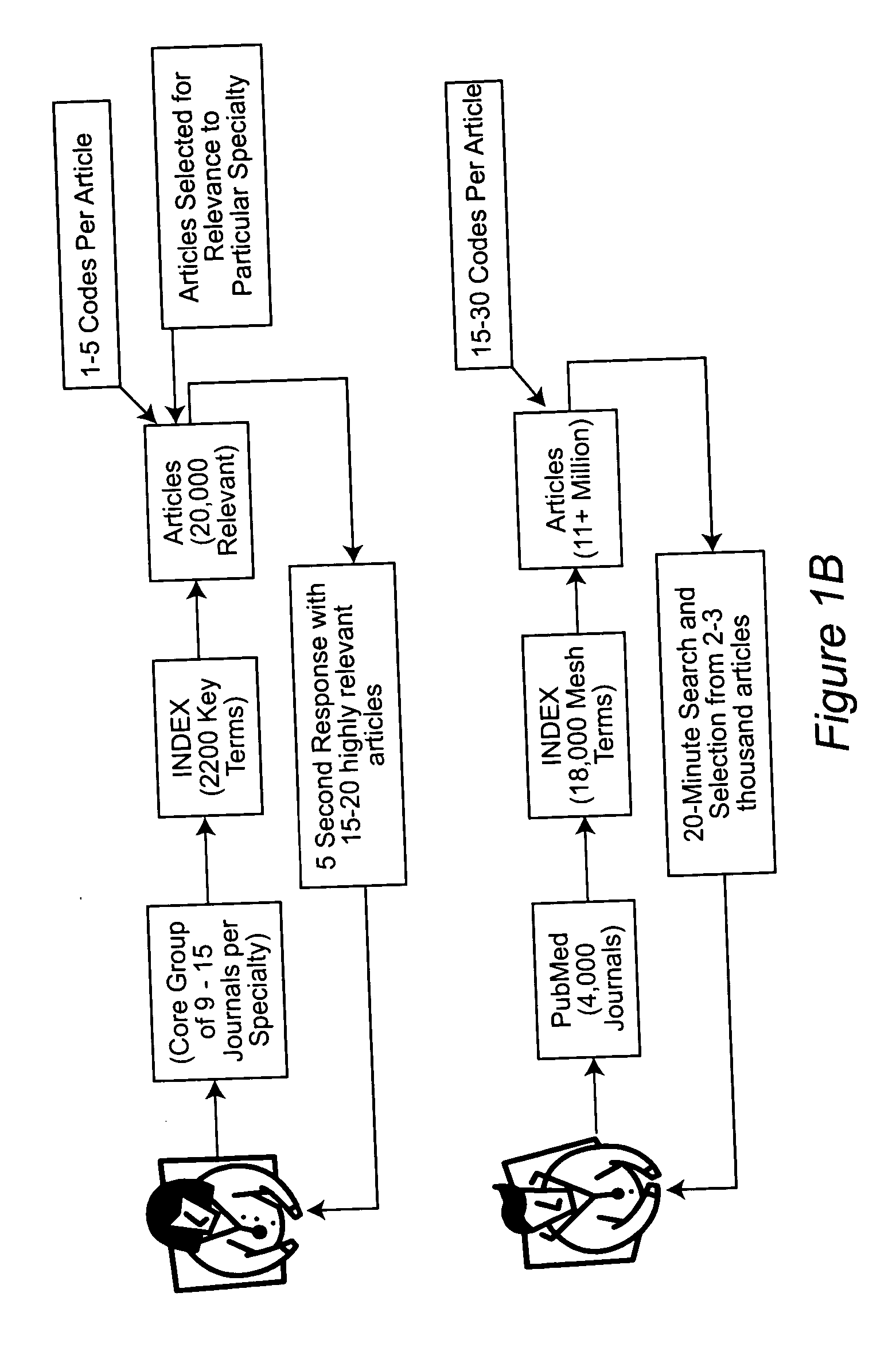

Database and index organization for enhanced document retrieval

ActiveUS20060253441A1Quick searchRemove inclusionsMetadata text retrievalData processing applicationsDocumentation procedureKey articles

A customized, specialty-oriented database and index of a subject matter area and methods for constructing and using such a database are provided. Selection and indexing of articles is done by experts in the topic with which the database is concerned. As a result, articles are indexed in a manner that allows facile, rapid retrieval of highly relevant articles with few or no false positives with much reduced database maintenance cost through frugal limitation of number of documents in the database, number of terms in a Master Index, and number of codes assigned to each document. A thesaurus allows indexing and search in accordance with terminology familiar to different anticipated groups of users (e.g. doctors, patients, nurses, technicians, and the like). Key articles collections and rapid access to documents therein are also provided.

Owner:NELSON INFORMATION SYST

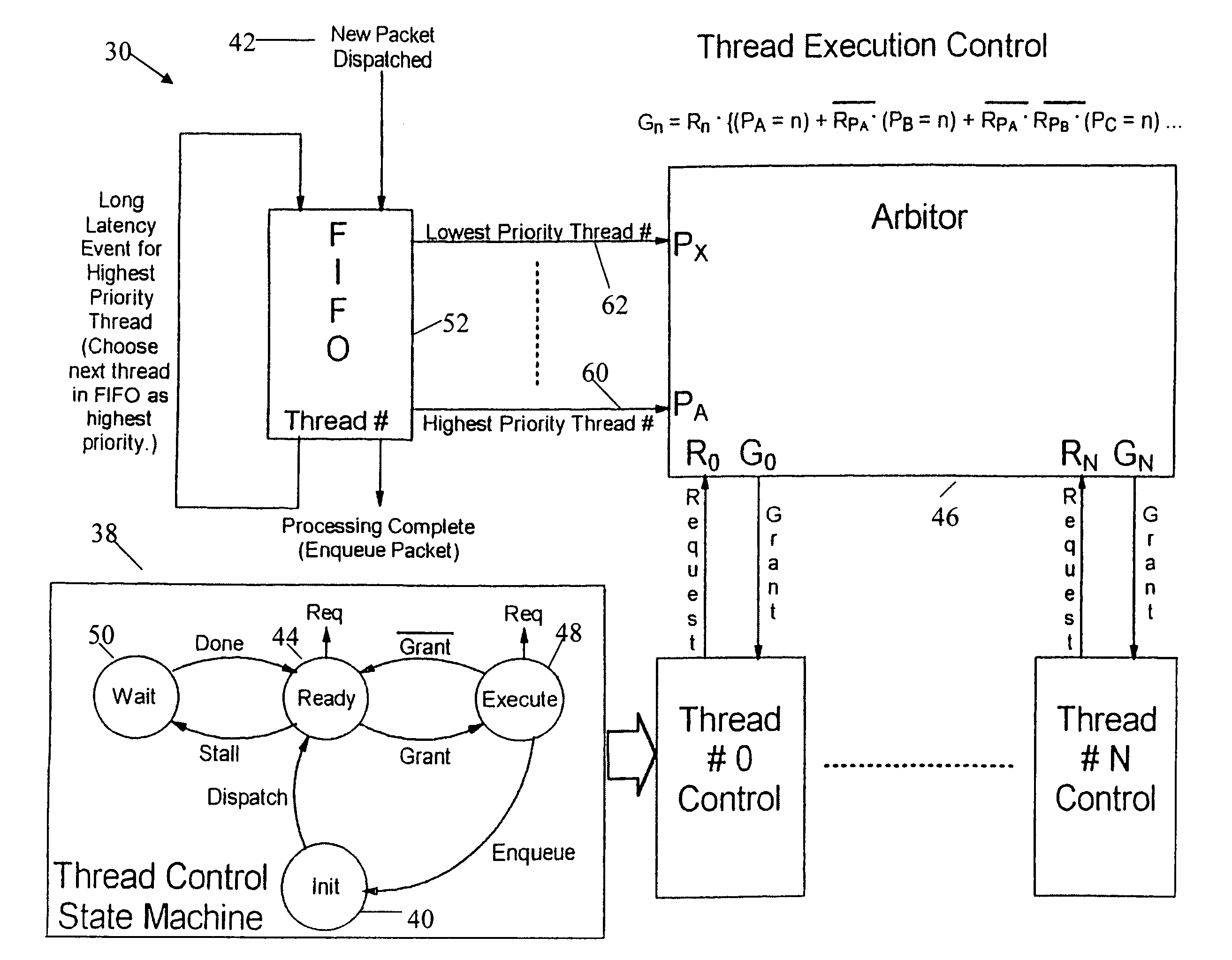

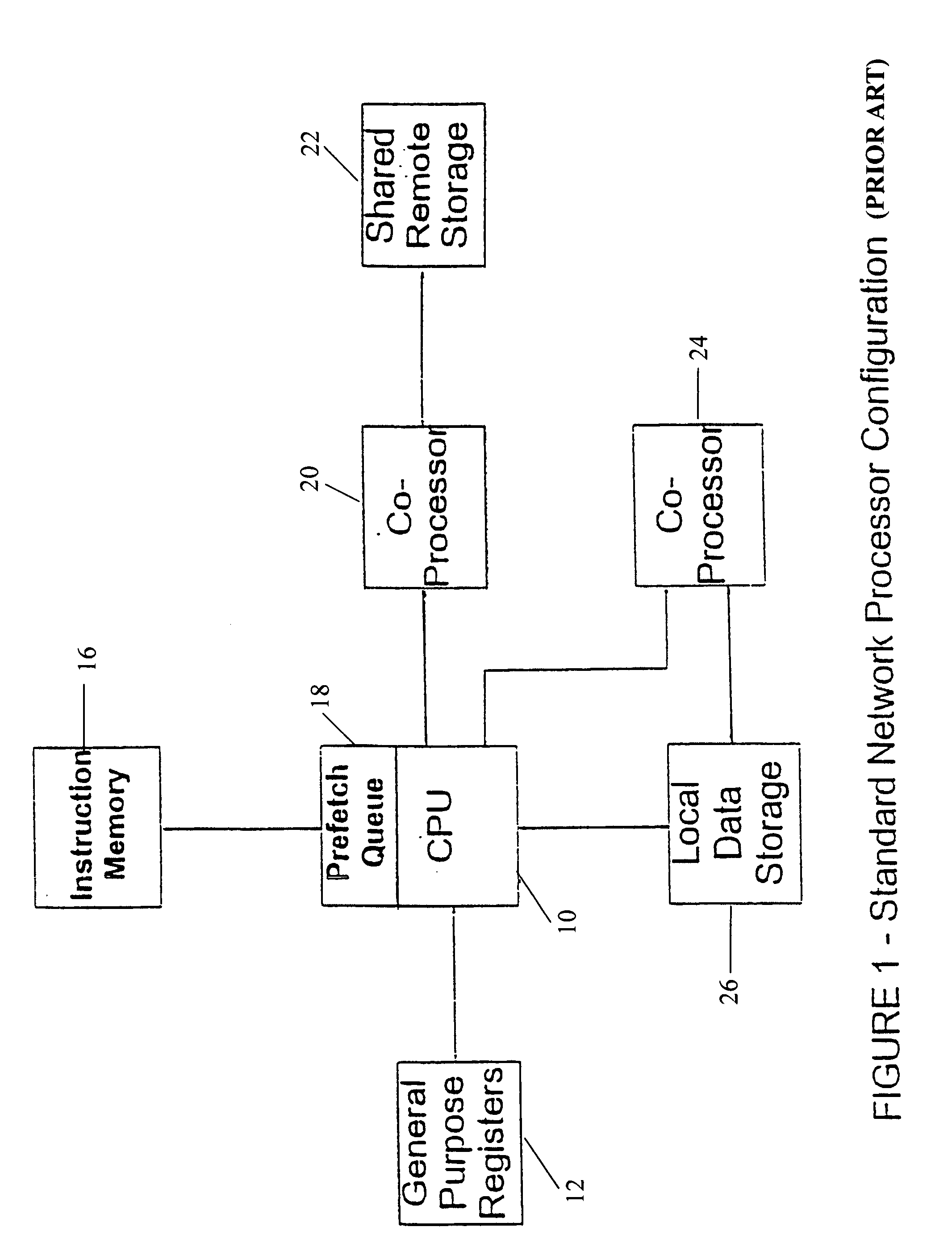

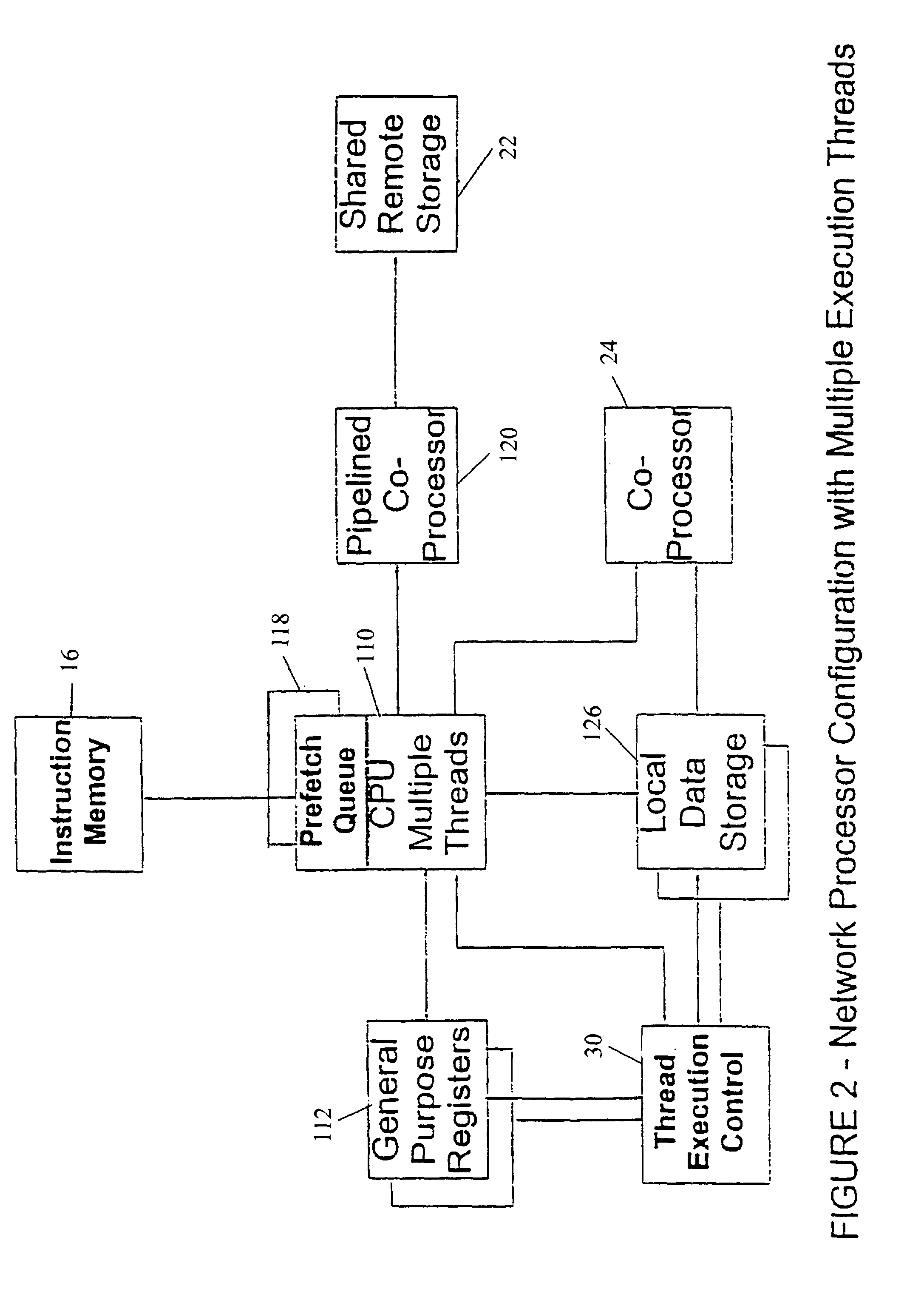

Network processor which makes thread execution control decisions based on latency event lengths

InactiveUS7093109B1Easy to useZero overheadDigital computer detailsMultiprogramming arrangementsLong latencyCoprocessor

A control mechanism is established between a network processor and a tree search coprocessor to deal with latencies in accessing the data such as information formatted in a tree structure. A plurality of independent instruction execution threads are queued to enable them to have rapid access to the shared memory. If execution of a thread becomes stalled due to a latency event, full control is granted to the next thread in the queue. The grant of control is temporary when a short latency event occurs or full when a long latency event occurs. Control is returned to the original thread when a short latency event is completed. Each execution thread utilizes an instruction prefetch buffer that collects instructions for idle execution threads when the instruction bandwidth is not fully utilized by an active execution thread. The thread execution control is governed by the collective functioning of a FIFO, an arbiter and a thread control state machine.

Owner:INTEL CORP

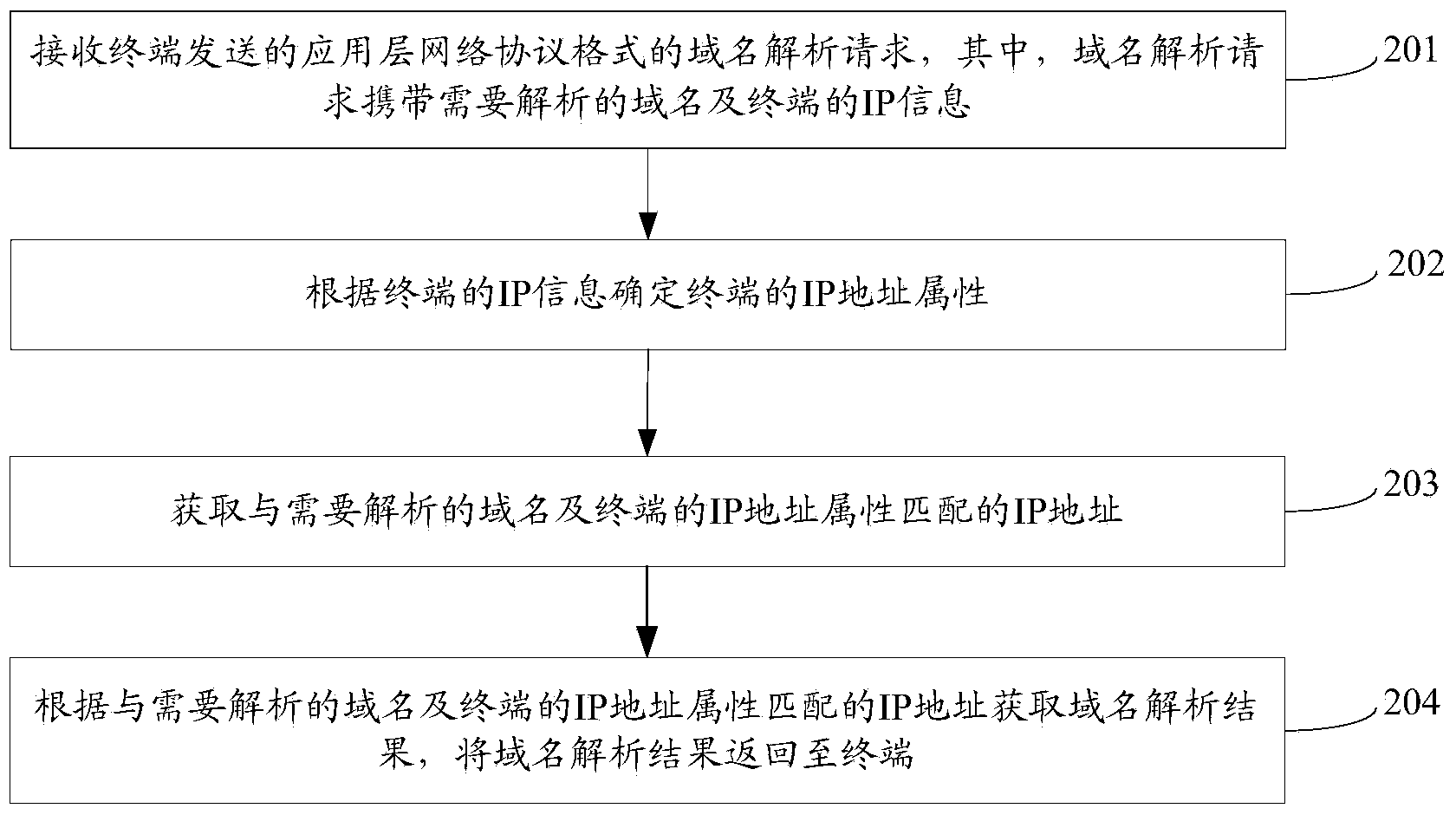

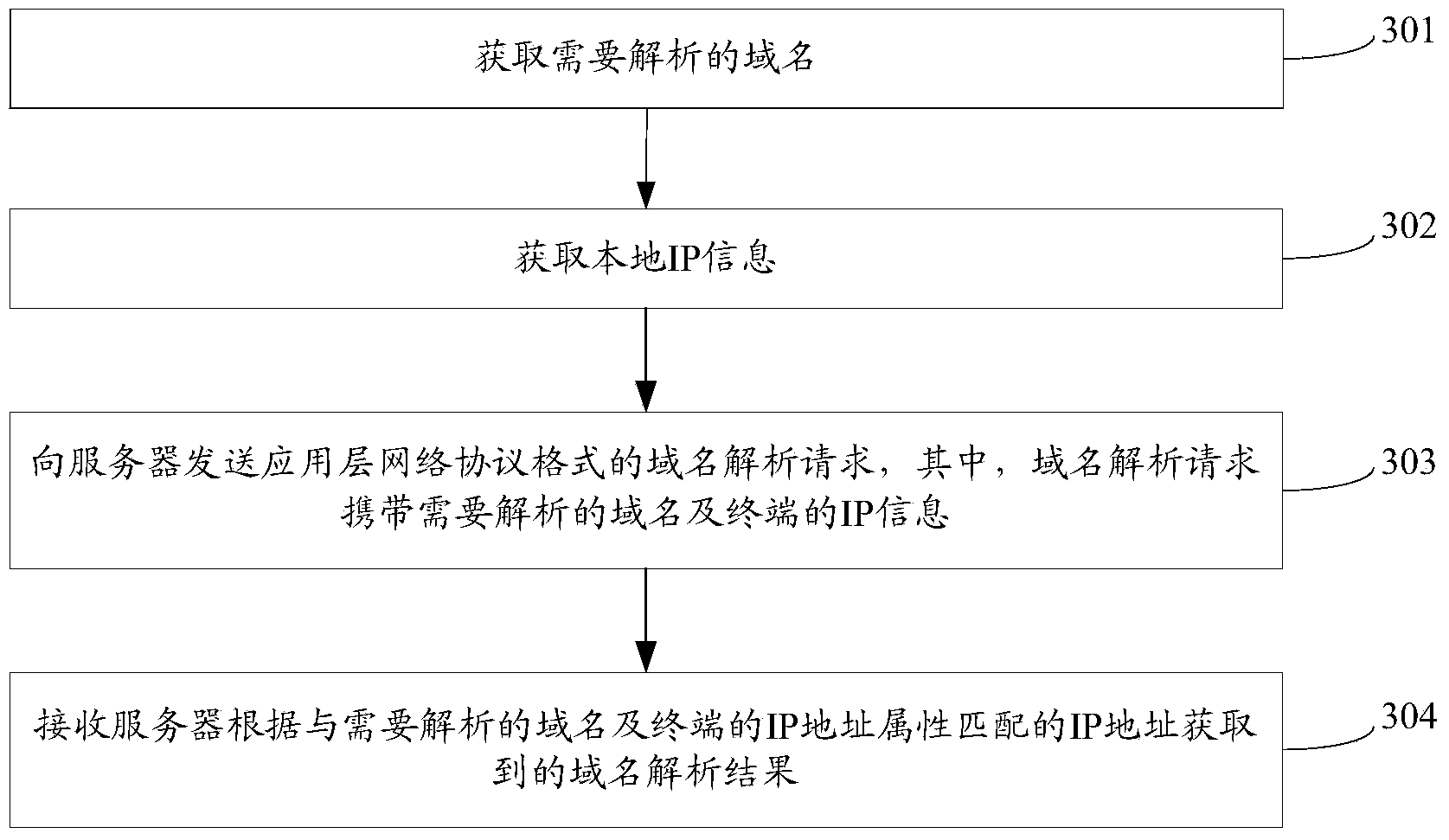

Domain name resolution method, server, terminal and system

ActiveCN104168340AAnalysis method is simpleImprove analysis efficiencyTransmissionDomain nameIp address

The invention discloses a domain name resolution method, a server, a terminal and a system and belongs to the technical field of internet. The method includes the following steps: a domain name resolution request, which carries a domain name which needs to be resolved and IP information of the terminal, sent by the terminal is received; an IP address attribute of the terminal is determined; an IP address which matches the domain name which needs to be resolved and the IP address attribute of the terminal; and according to the IP address which matches the IP address attribute of the terminal, a domain name resolution result is obtained and a domain name resolution result is returned to the terminal. Through reception of the domain name resolution request, which carries the IP information of the terminal, sent by the terminal, and according to the IP information of the terminal, the IP address attribute of the terminal is determined and according to the domain name which needs to be resolved and the IP address attribute of the terminal, the domain name resolution result is obtained. The domain name resolution method is simple and the domain name resolution efficiency can be improved so that the terminal is enabled to access websites rapidly and nearest access is arranged for the terminal according to the IP address attribute of the terminal so that global traffic configuration and refined scheduling of the terminal can be realized.

Owner:TENCENT TECH (SHENZHEN) CO LTD +1

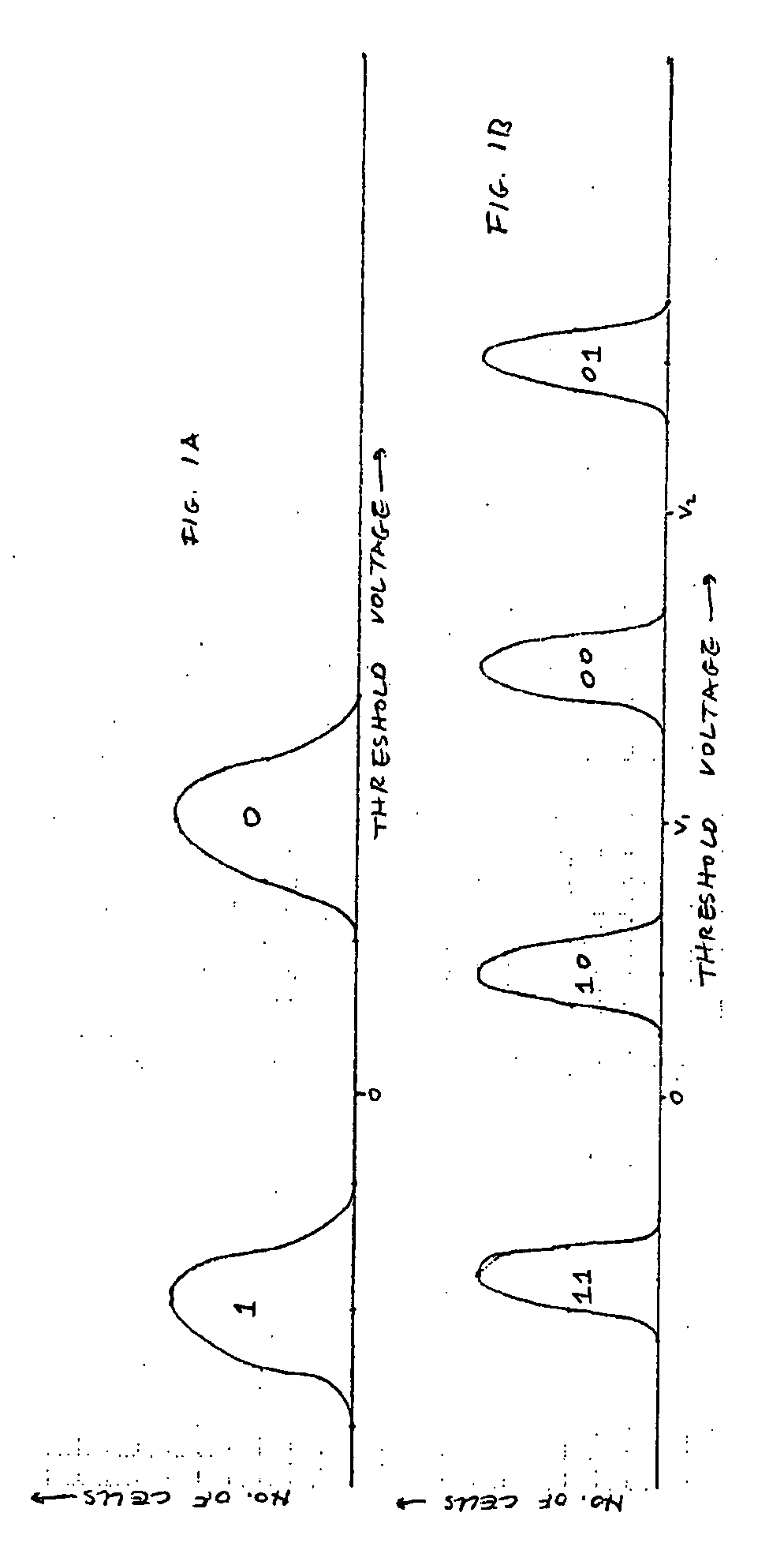

Method of storing data in a multi-bit-cell flash memory

In writing to a block, of a flash memory, that includes pages with different write access or read access speeds, after writing first data to a first page that has fast access, at least one page that has slow access is skipped to write second data to a second page that has fast access.

Owner:WESTERN DIGITAL ISRAEL LTD

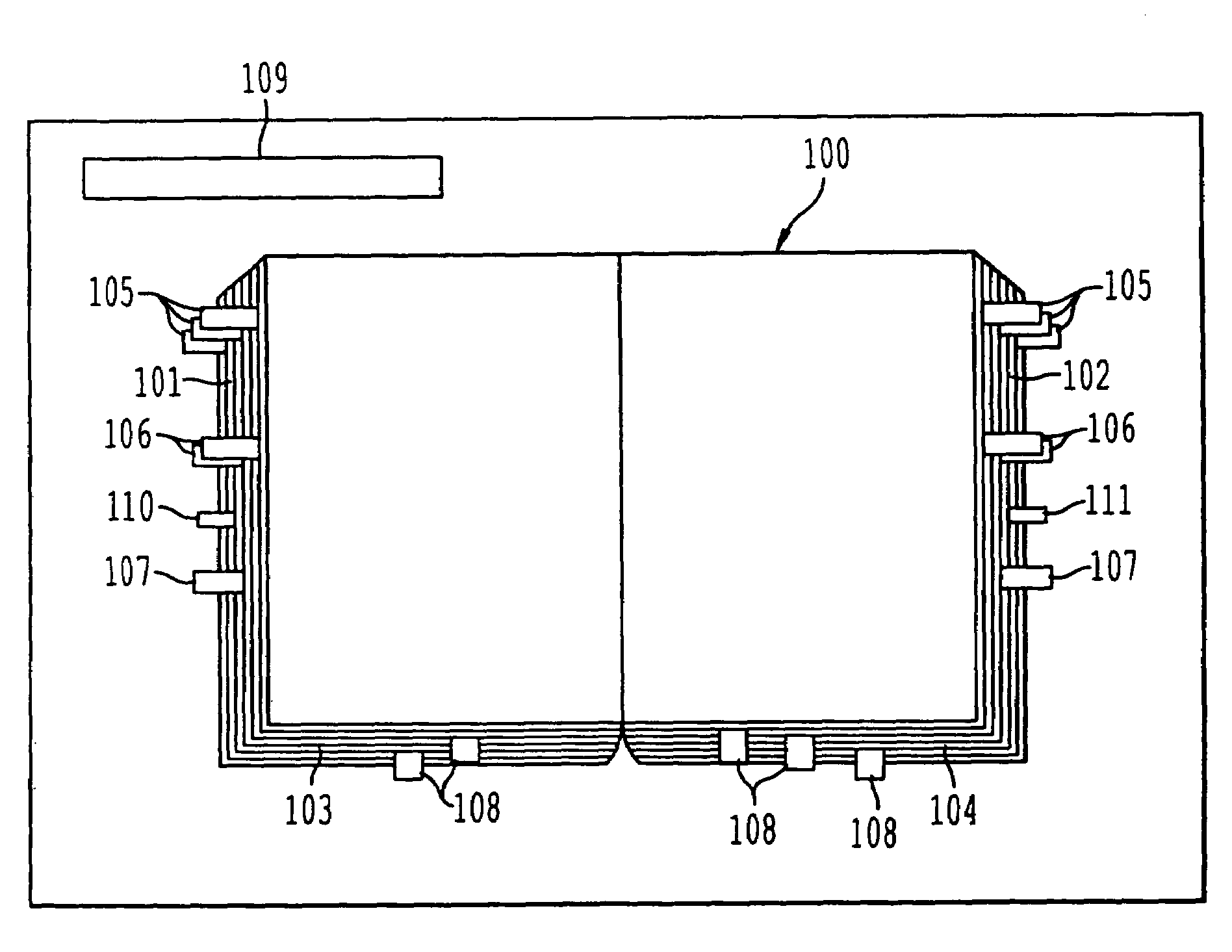

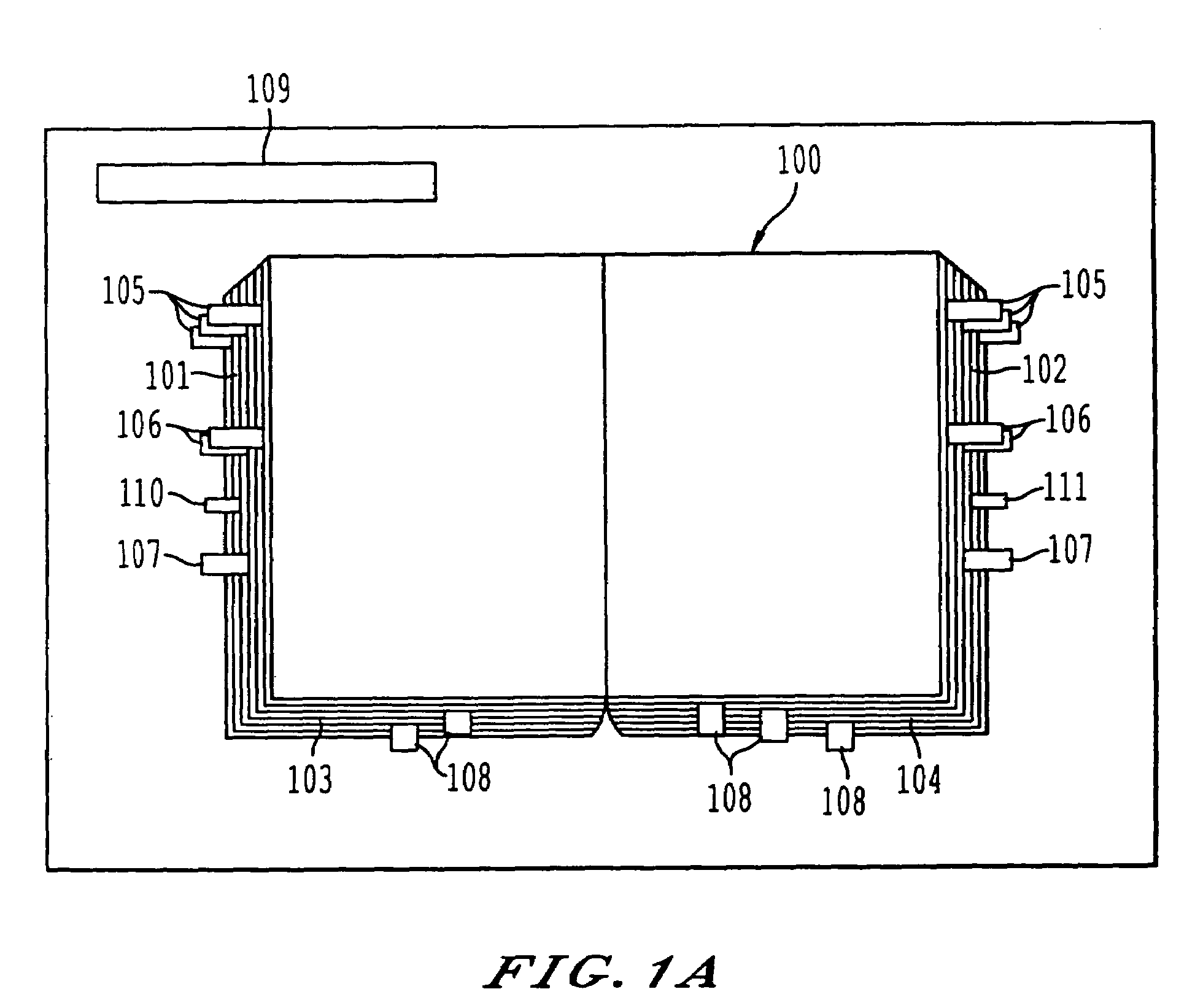

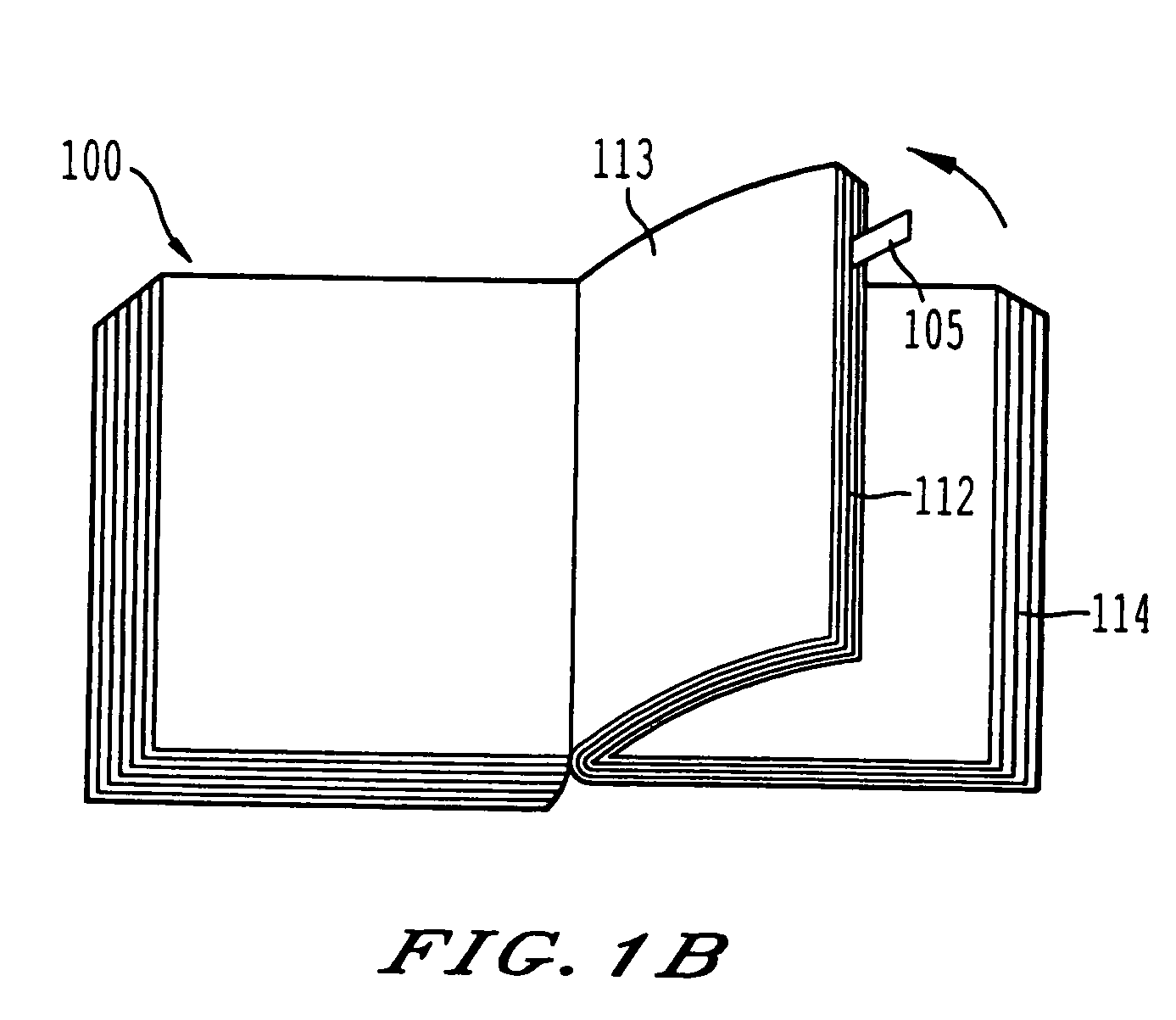

Method, system, apparatus, and computer program product for controlling and browsing a virtual book

InactiveUS7386804B2Effectively and rapidly controlEffectively and rapidly and browseDigital computer detailsCathode-ray tube indicatorsData displayMass storage

A hardware and software system including a controller that can be operatively combined with several methods of display on a display screen under software and hardware control for the purpose of browsing through data stored in a memory device. The browsing of the data stored in a memory device is facilitated in such a way that it allows a rapid view of what contents are present and the organization of the material in the data, as well as rapid access to the items in the data involved. The controllers in the system have specialized functions for effecting various actions on the data displayed on the display screen in such a way that users can rapidly browse through the data involved. The methods of display may include interaction with CD-R, CD-RW, DVD, a portable optical large volume storage disk, a portable large volume non-optical storage medium, a TV, and an HDTV.

Owner:SINO STAR GLOBAL

Grade beam access method and device

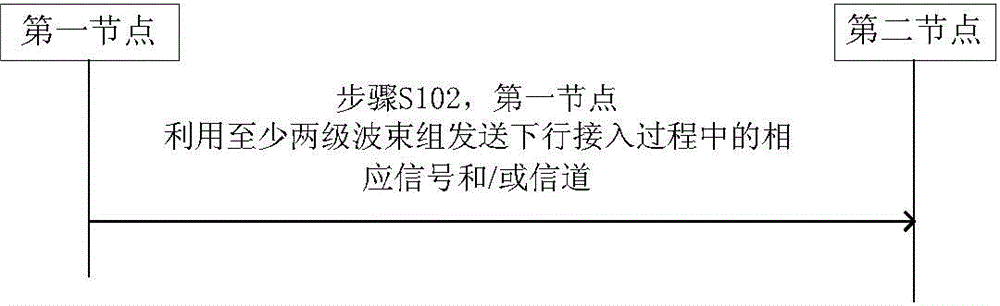

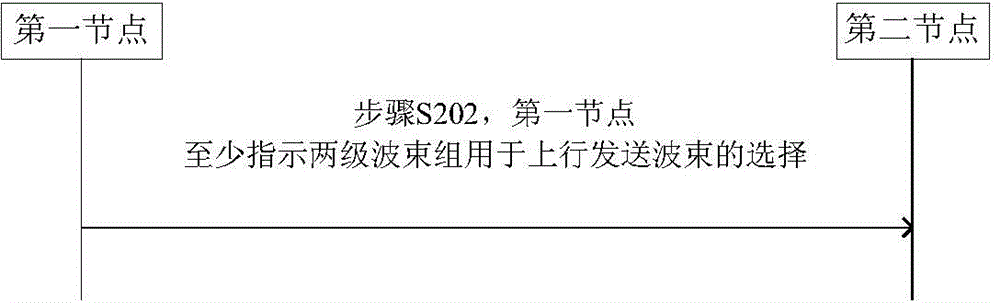

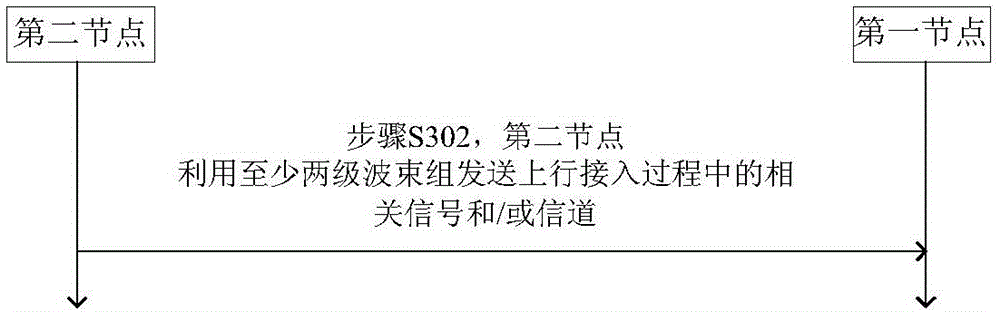

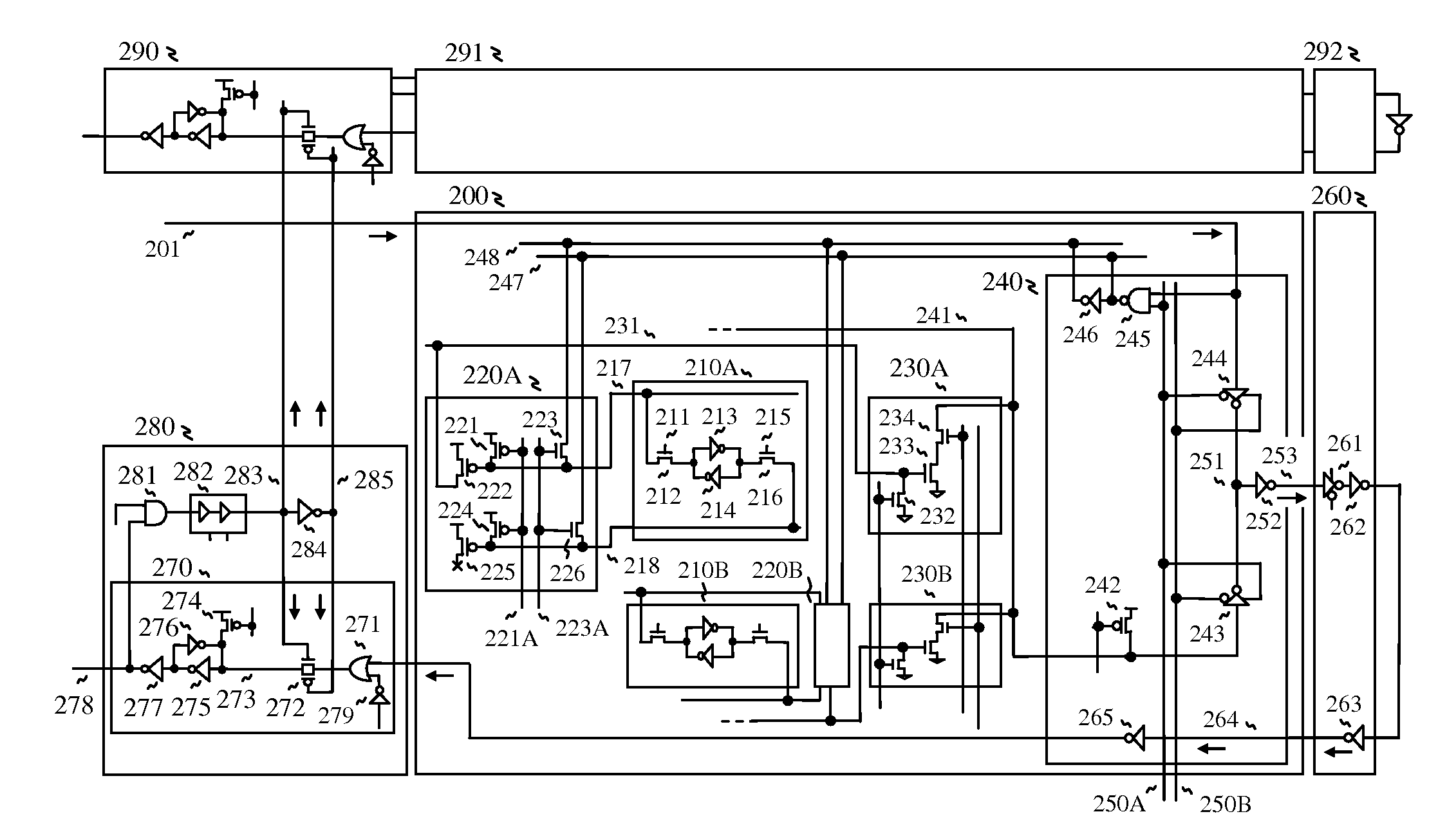

ActiveCN105812035ASolve the problem that the optimal beam cannot be obtained efficientlyDifferent SNRSpatial transmit diversityTransmission control/equalisingSignal-to-noise ratio (imaging)Access method

The invention discloses a grade beam access method and device. The method comprises the step that a first node uses at least two beam groups to send a correlation signal and / or channel in a downlink access process, wherein a beam group consists of one or more beams. According to the invention, the problem that the first node or a second node cannot efficiently acquire an optimal beam in related technologies is solved; different signal to noise ratios are provided for signals and channels; and a reliable and rapid access process is provided.

Owner:ZTE CORP

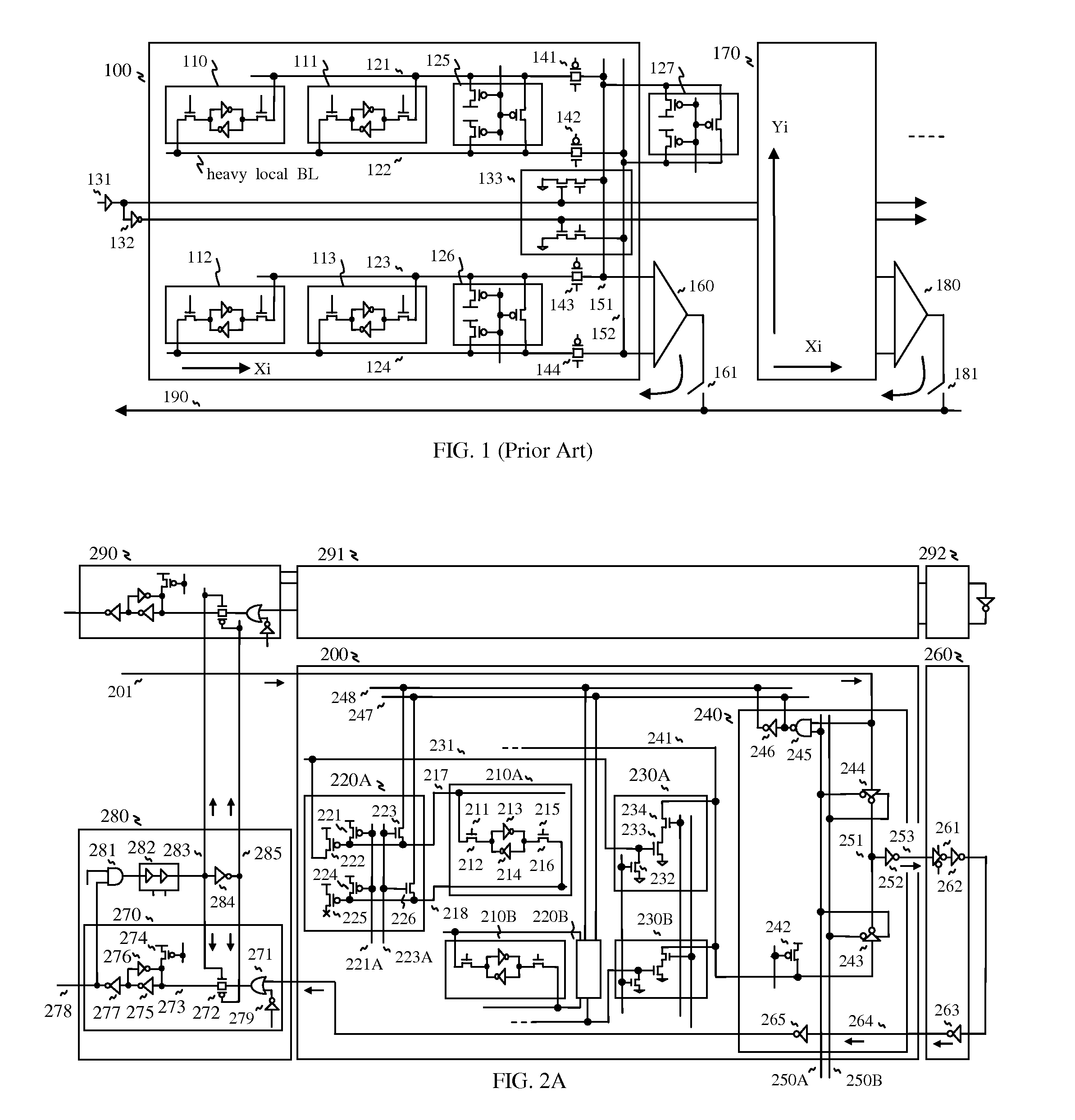

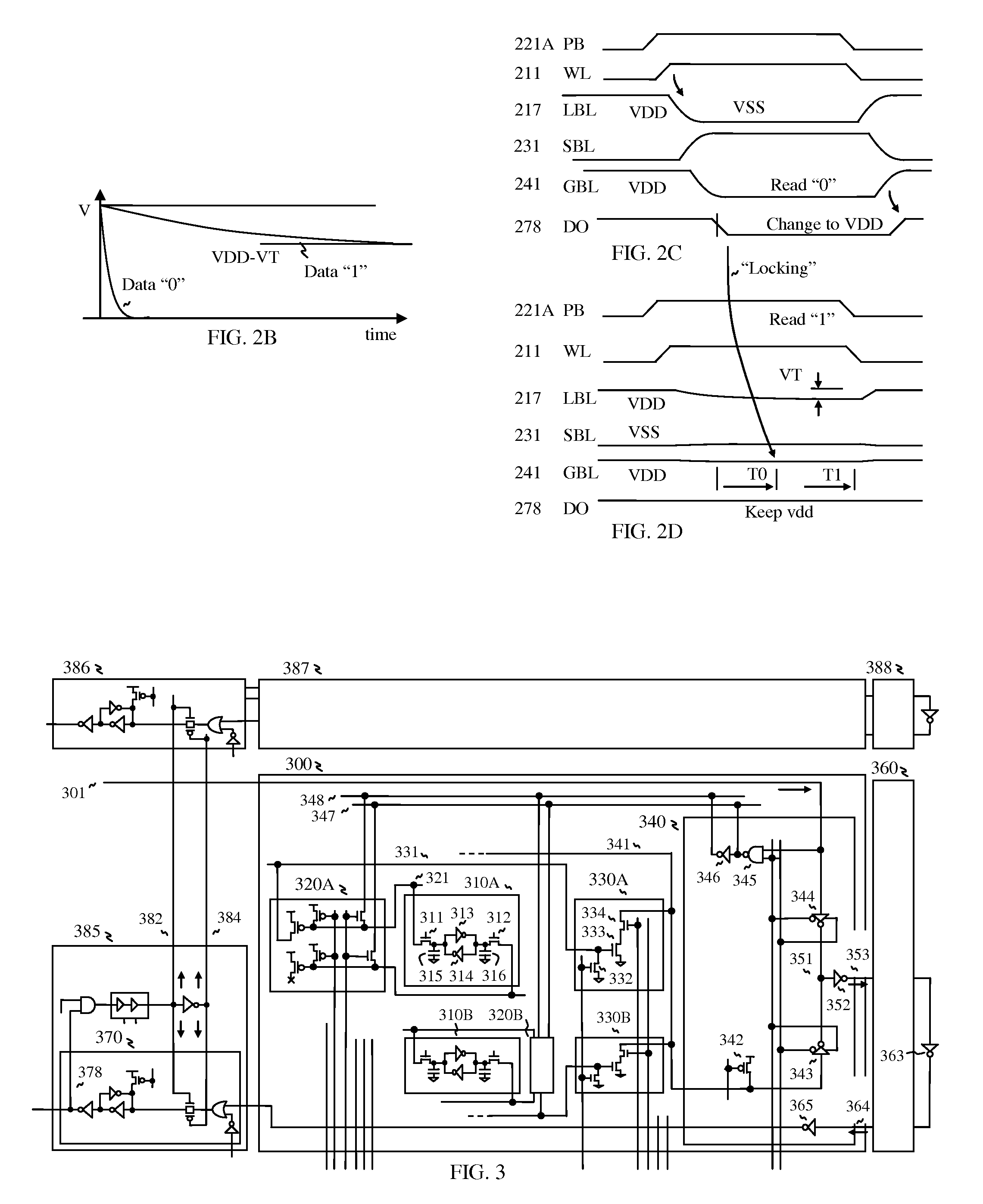

High speed SRAM

InactiveUS20100054011A1Reduce power consumptionEliminating penetration currentDigital storageBit lineAudio power amplifier

High speed SRAM is realized such that a first dynamic circuit serves as a local sense amp for reading a memory cell through a lightly loaded local bit line, a second dynamic circuit serves as a segment sense amp for reading the local sense amp, and a tri-state inverter serves as an inverting amplifier of a global sense amp for reading the segment sense amp. When reading, a voltage difference in the local bit line is converted to a time difference for differentiating low data and high data by the sense amps for realizing fast access with dynamic operation. Furthermore, a buffered data path is used for achieving fast access and amplify transistor of the sense amps is composed of relatively long channel transistor for reducing turn-off current. Additionally, alternative circuits and memory cell structures for implementing the SRAM are described.

Owner:FRONTEON

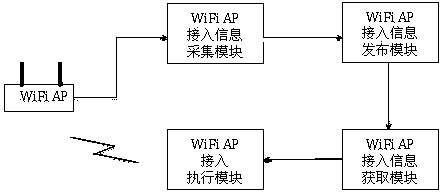

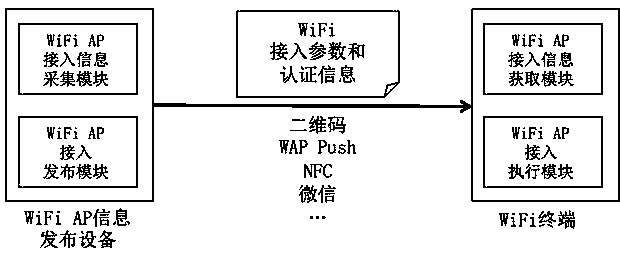

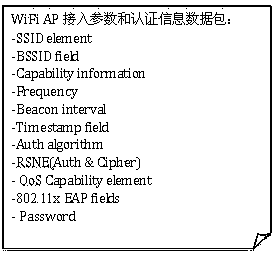

Method and system for enabling WiFi terminal to have rapid access to WiFi AP

InactiveCN103415013AQuick Connect DeploymentEasy to connect and deployAssess restrictionConnection managementComputer networkRapid access

The invention discloses a method and system for enabling a WiFi terminal to have rapid access to a WiFi AP. The method for enabling the WiFi terminal to have rapid access to the WiFi AP comprises the following steps that a WiFi AP network is accessed by means of a WiFi AP information issuing device, and the access parameters and the certification information of the target WiFi AP are obtained and then encapsulated according to a data format; the encapsulated access parameters and the encapsulated certification information of the WiFi AP are issued to the WiFi terminal in an area; after obtaining the encapsulated access parameters and the encapsulated certification information of the WiFi AP, the WiFi terminal analyzes the encapsulated access parameters and the encapsulated certification information and obtains the access parameters and the certification information of the target WiFi AP; according to the access parameters of the target WiFi AP, the target WiFi AP network is accessed, the follow-up certification access process is automatically completed according to the certification information. According to the method and system for enabling the WiFi terminal to have rapid access to the WiFi AP, the WiFi terminal omits the steps of WiFi AP scanning and selection, the certification process is completed automatically, the process that a user uses the WiFi terminal to have access to the WiFi AP in the area where the user stays is accelerated, and the process that the user uses the WiFi terminal to have access to the mobile Internet is improved.

Owner:南京市海聚信息科技有限公司

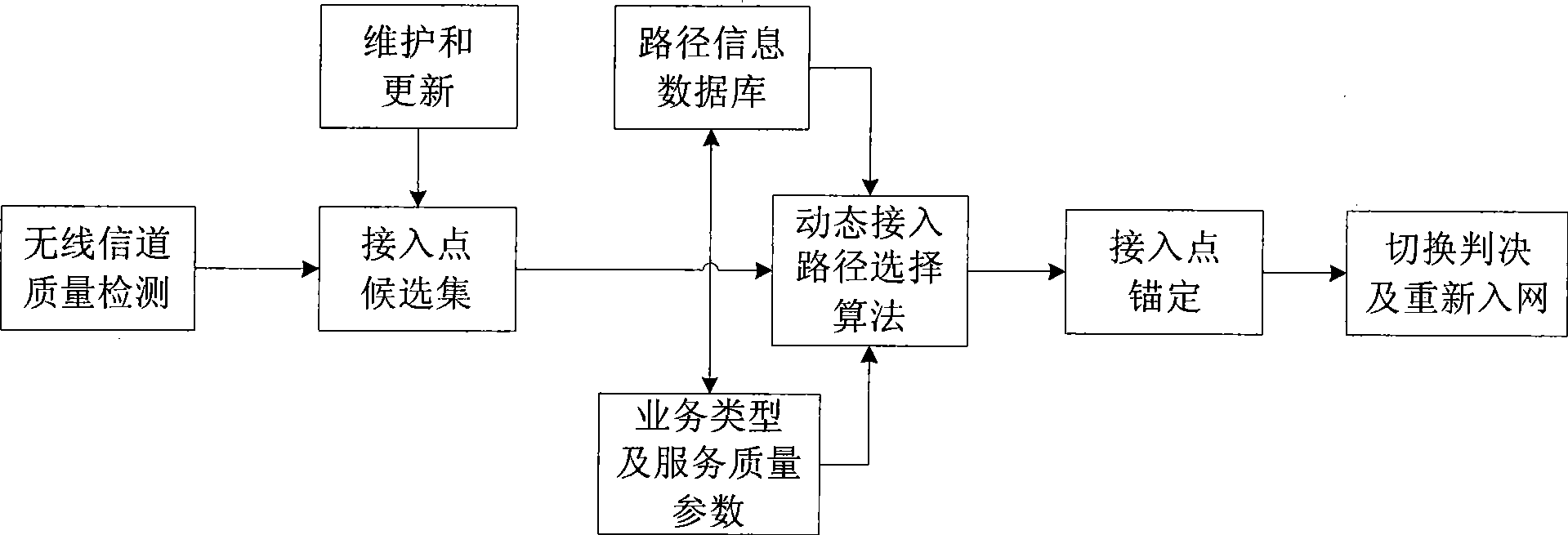

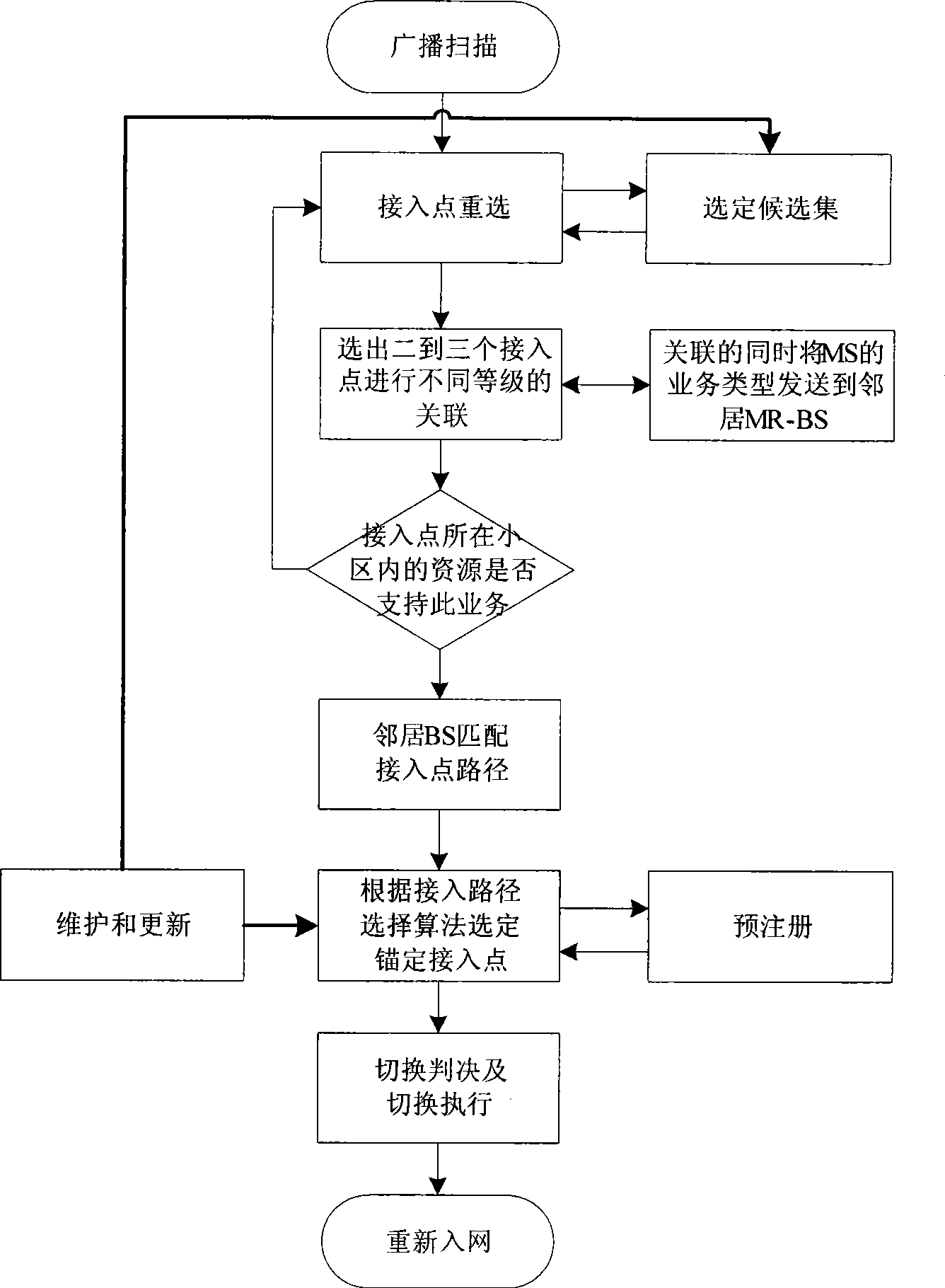

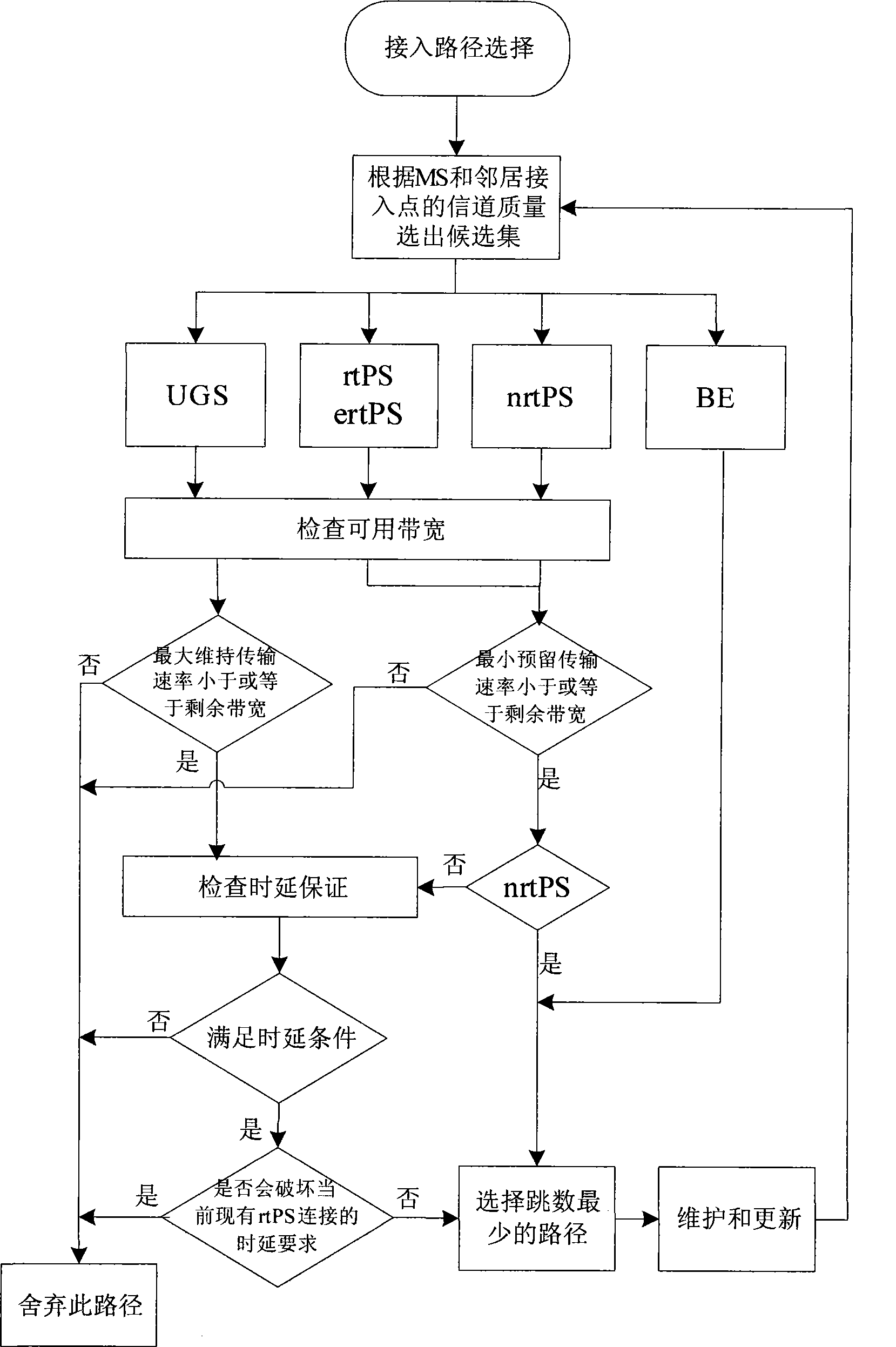

Fast access point switching method based on dynamic access path selection mechanism

InactiveCN101483893AGuaranteed connection qualityReduce switching delayWireless communicationQuality of serviceUser needs

The invention discloses a rapid access point switching method based on a dynamic access path selection mechanism, wherein, in a multi-hop relay broadband radio access network, each district exists a plurality of access points, including a base station and a delay station, a mobile user dynamically and rapidly switches to the access point of an adjacent district in a moving process according to the quality of a current radio channel with the aid of access path selection algorithm. By means of access point reselection, information such as the bandwidth, delay and hop count of a candidate access point path, and the current connection business type of the mobile user and service quality parameter thereof, the method of the invention selects the access path that satisfies current traffic condition from the candidate access points, and according to a best anchoring access point selected from business information obtained beforehand from a reserved network, the best access path is determined. When the mobile user needs switching, a target access point is switched rapidly, and the rapid access point switching method reduces switching delay, and different treatment on business with different priority improves switching connection rate.

Owner:TONGJI UNIV

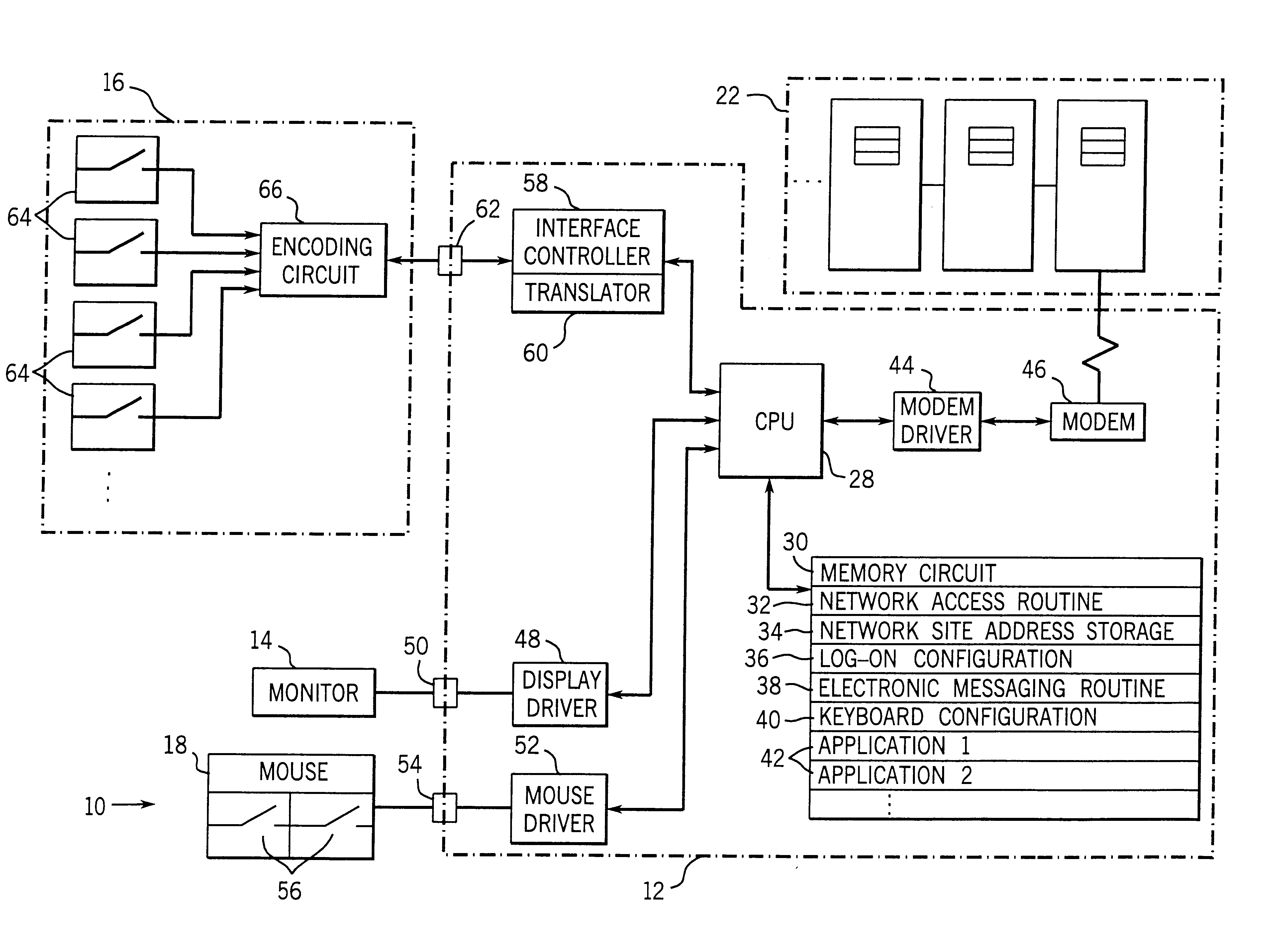

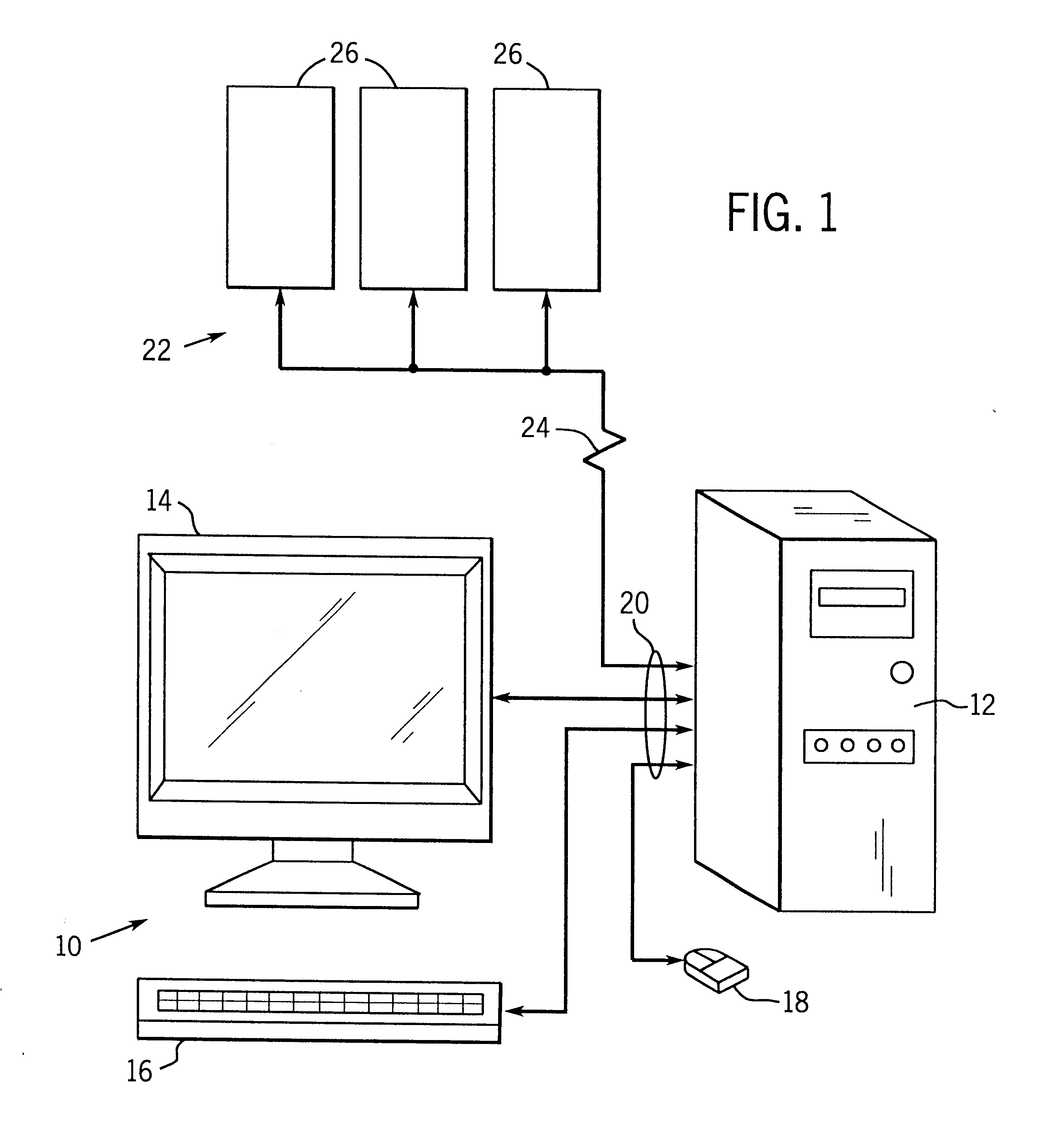

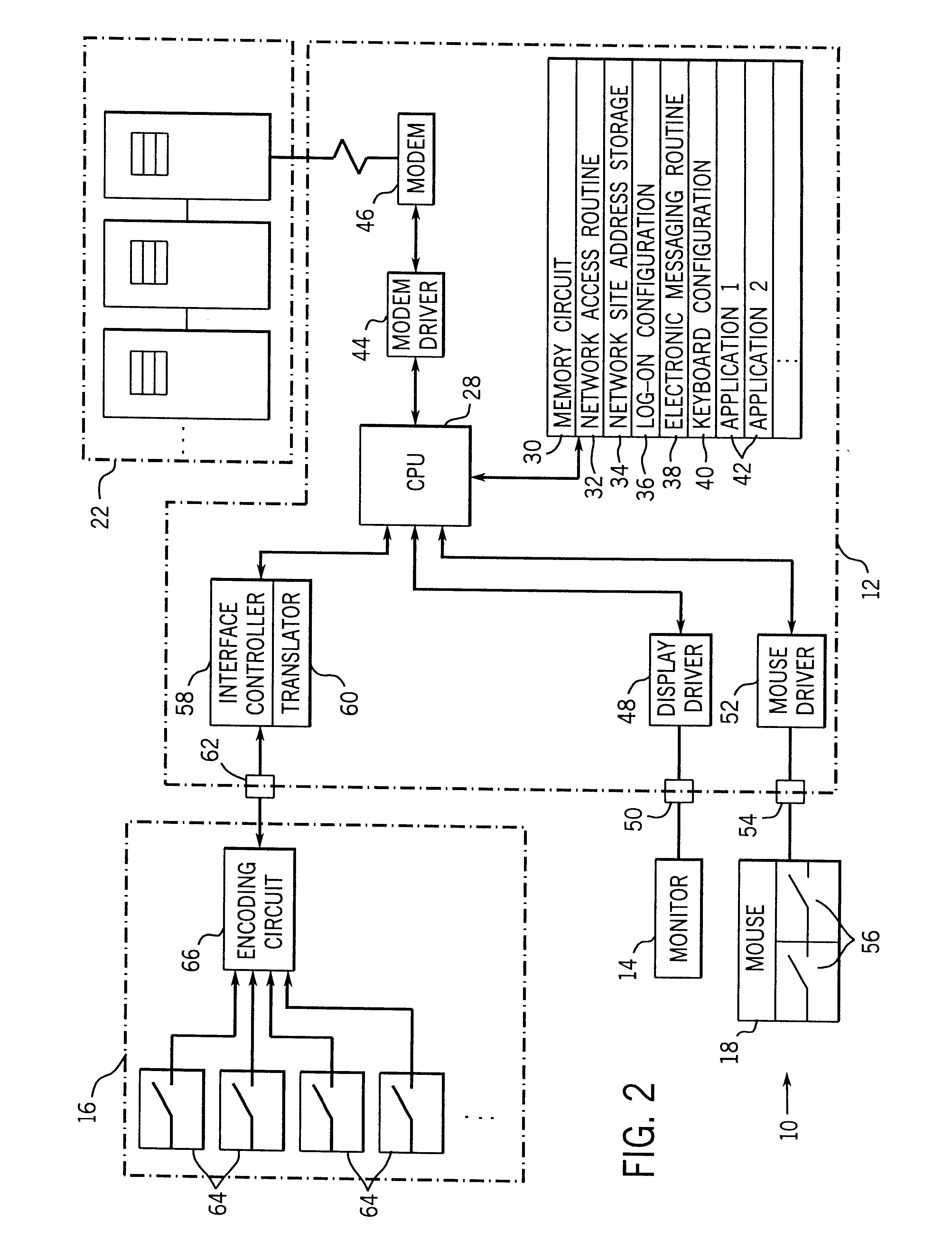

Rapid network access computer system

InactiveUS6625649B1Easy accessInput/output for user-computer interactionDigital computer detailsSignal processing circuitsComputerized system

Owner:HEWLETT PACKARD DEV CO LP

Unified interest layer for user interface

ActiveUS20060150118A1Assisting understandingMultiple digital computer combinationsExecution for user interfacesDashboardOperational system

A user-activatable dashboard (also referred to as a unified interest layer) contains any number of user interface elements, referred to herein as “widgets,” for quick access by a user. In response to a command from a user, the dashboard is invoked and the widgets are shown on the screen. The user can activate the dashboard at any time, causing the dashboard to temporarily replace the existing user interface display on the user's screen. Once the dashboard has been activated, the user can interact with any or all of the widgets, and can configure the dashboard by adding, deleting, moving, or configuring individual widgets as desired. When the user wishes to return to the normal user interface he or she was working with, the user issues a command causing the dashboard to be dismissed. Once the dashboard has been dismissed, the previous user interface state is restored, allowing the user to resume normal interactions with the operating system.

Owner:APPLE INC

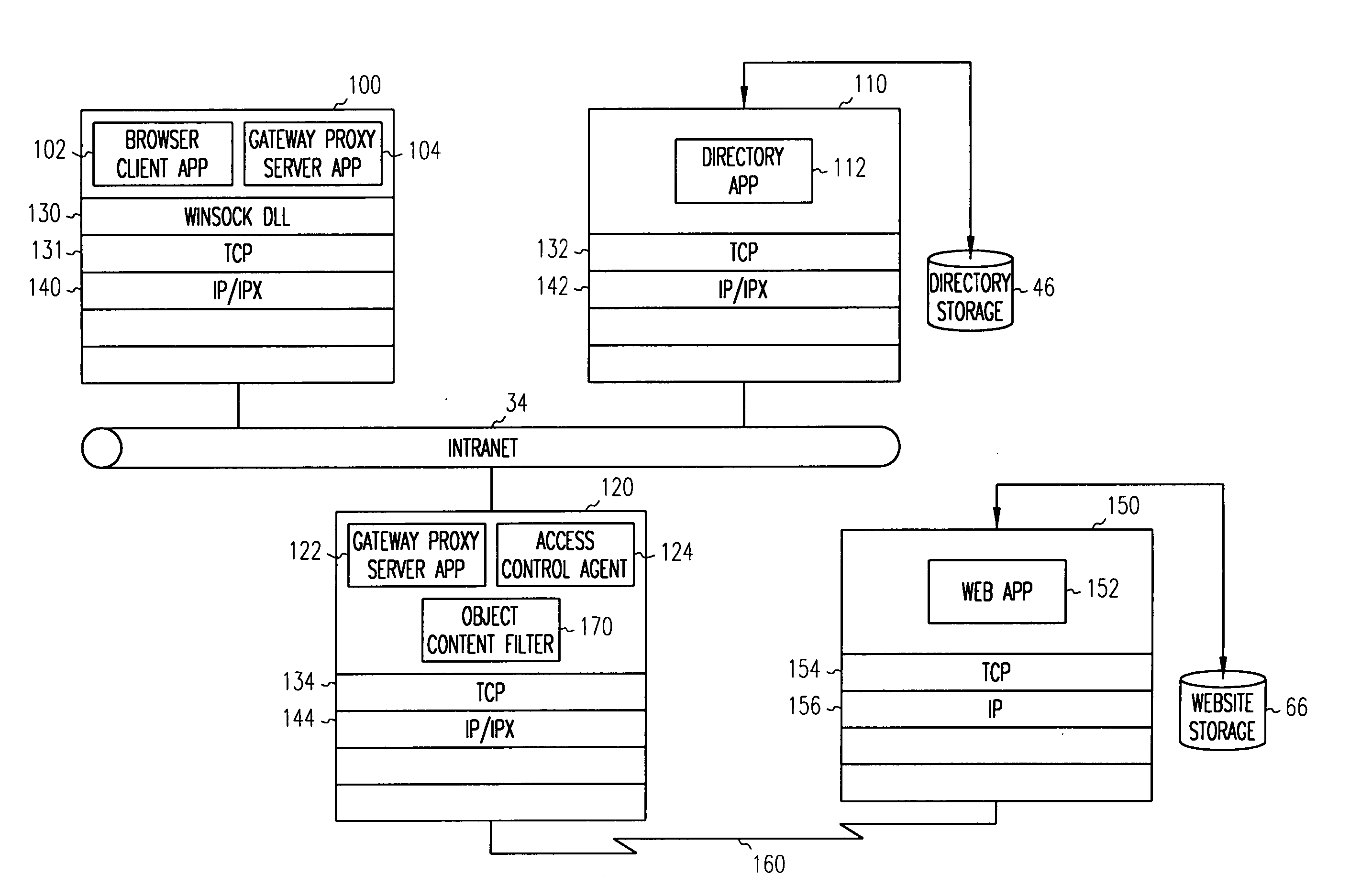

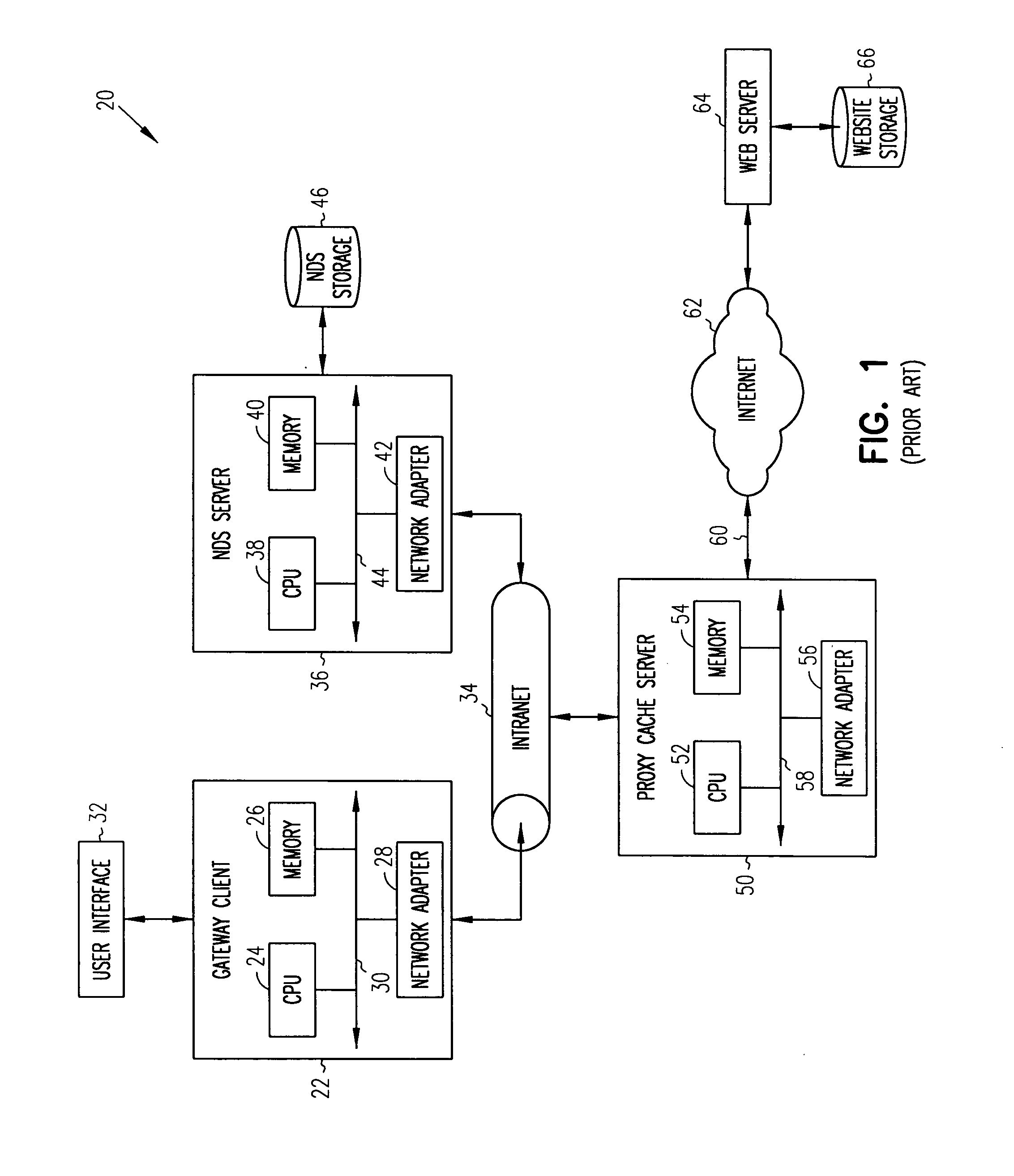

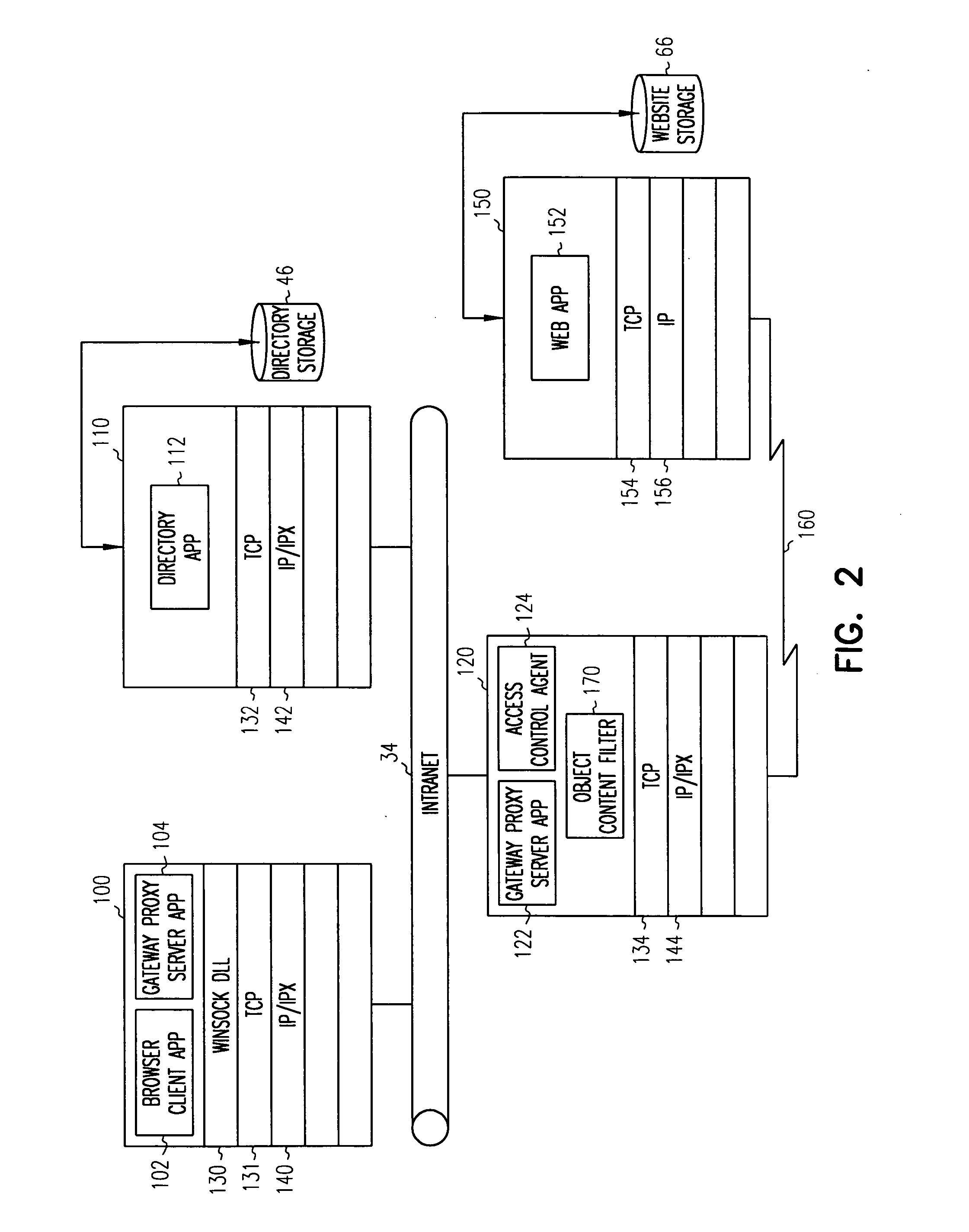

System and method for filtering of web-based content stored on a proxy cache server

InactiveUS20050021796A1Increase speedEfficient of content ratingVoting apparatusDigital data information retrievalThe InternetRapid access

A system and method for filtering of web-based content in a proxy cache server environment provides a local network having a client, a directory server and a proxy cache server that caches predetermined Internet-derived web content within the network. When content is requested, it is vended to the client only if it meets predefined user policies for acceptability. These policies are implemented based upon one or more ratings lists provided by content rating vendors. The lists are downloaded to the network in whole or part, and cached for use in determining acceptability of content by a filter application. Ratings can be particularly based upon predetermined content categories. Caching occurs in a host or object cache for rapid access. Only if current ratings are not found in the host or object caches are ratings caches or vendors accessed for ratings. Ratings on requested content are then placed in the host or object cache for subsequent use. Object parsing or other techniques can be used to screen returned content that is unrated or otherwise allowed to pass to ensure that it is appropriate.

Owner:APPLE INC

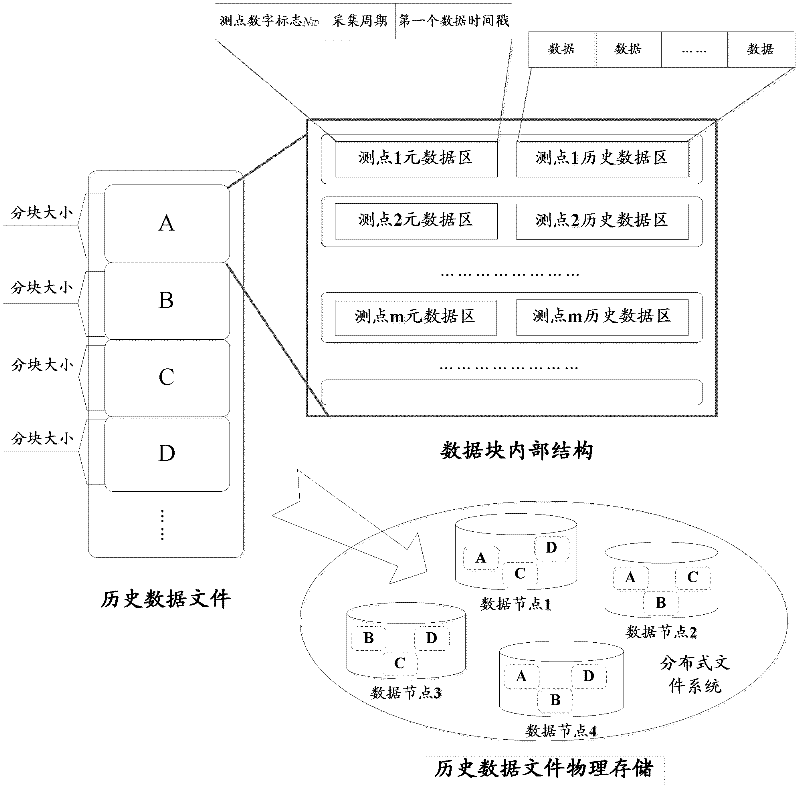

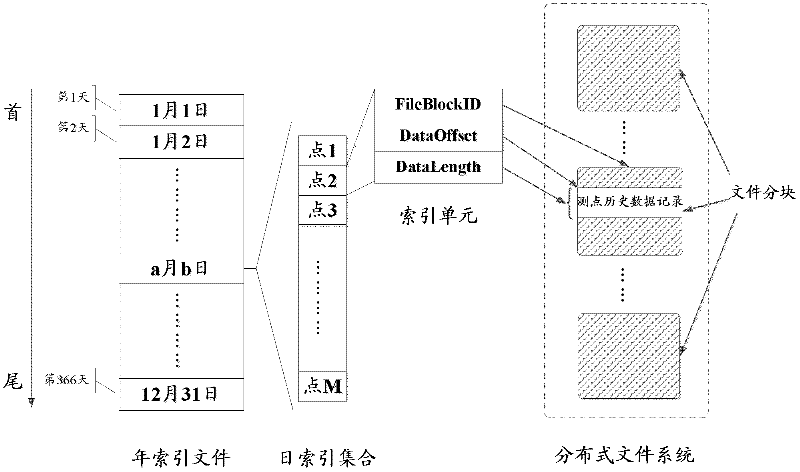

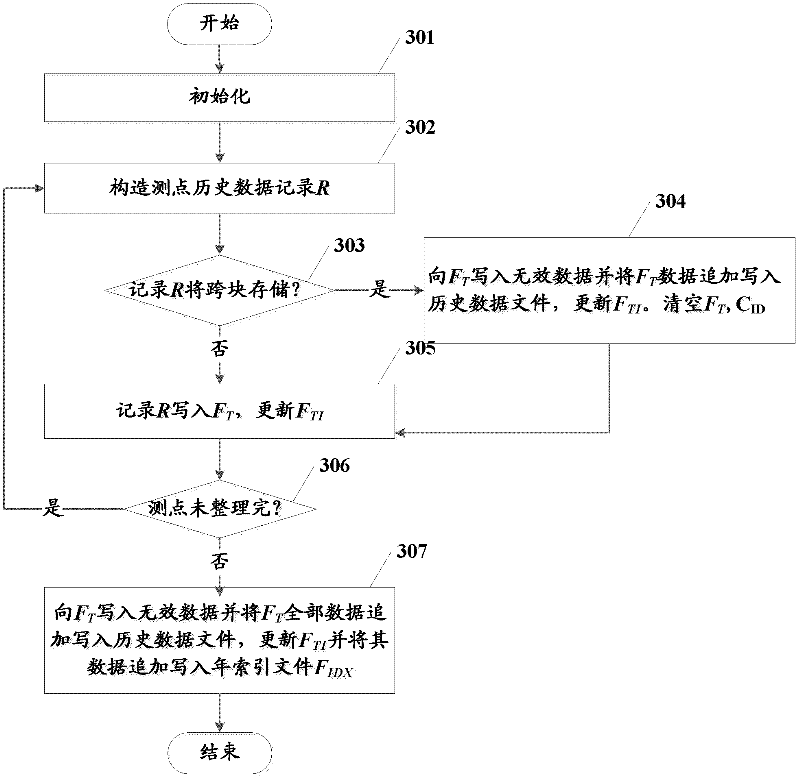

Method for storing and indexing mass historical data

InactiveCN102646130AMeet storage requirementsEasy accessSpecial data processing applicationsFile systemData file

The invention discloses a method for storing and indexing mass historical data, which belongs to the field of a real-time historical database. By the method according to the characteristic that the partitioning storage of big files is carried out by a distributed type file system, a simple high-efficiency method for storing mass historical data files and a high-efficiency distributed type indexing mechanism are provided. According to the storing method, the condition of meeting the requirement of storage of the current mass historical data files can be ensured, and the characteristic of on-line expansion is further ensured; the quick access of the mass historical data can be realized by the indexing mechanism; and meanwhile, after the resource expansion of the system is carried out, i.e. when the change of the physical storage of a bottom layer occurs, the searching function of the data still can be realized by an index under the condition of no need for modification.

Owner:HUAZHONG UNIV OF SCI & TECH

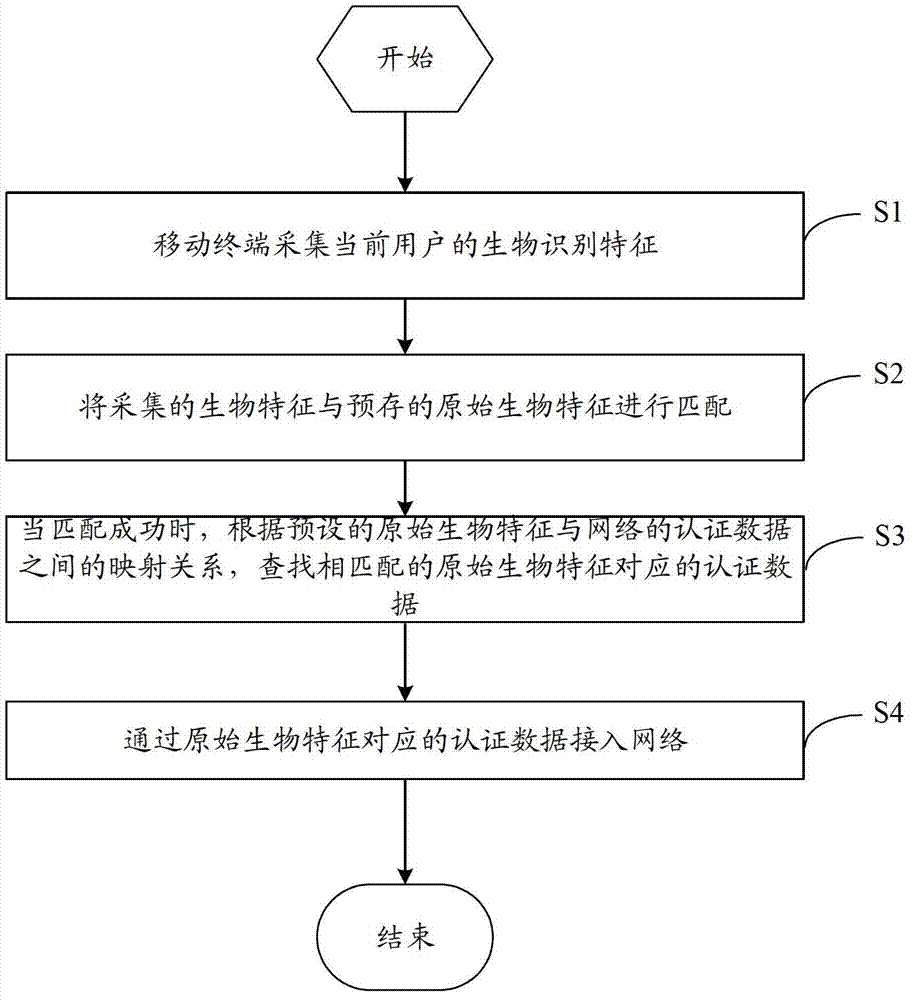

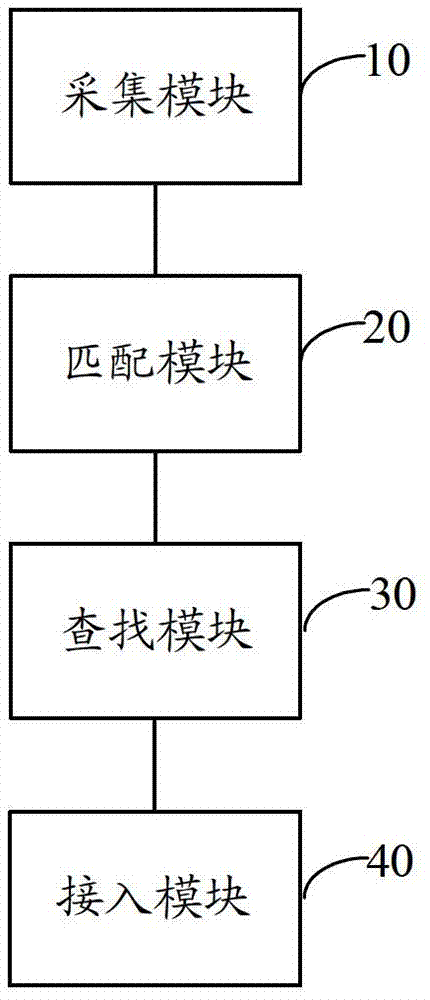

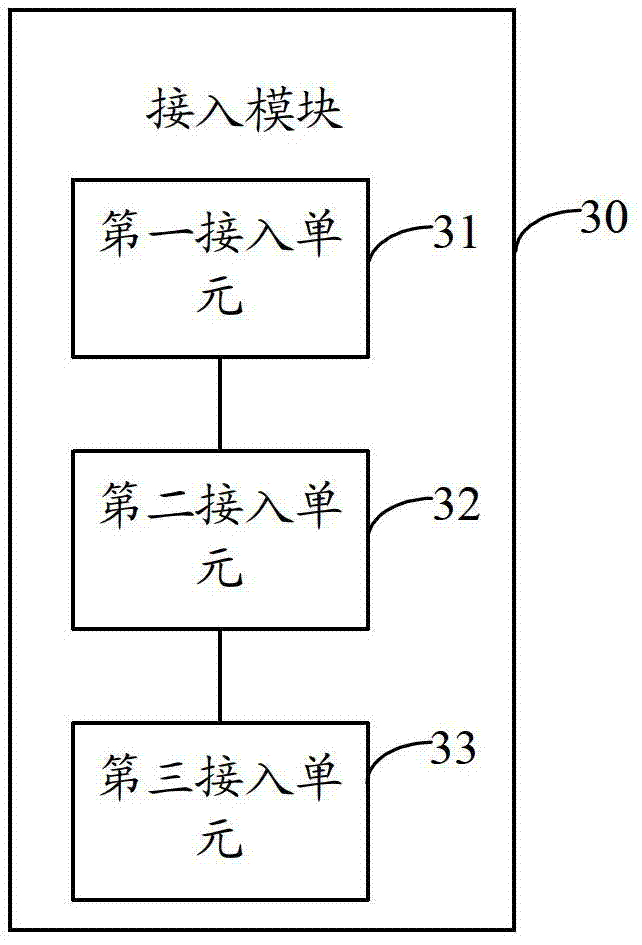

Biological recognition-based rapid access method and device

ActiveCN103402203AImprove experienceLow costUser identity/authority verificationCharacter and pattern recognitionAccess methodEvent trigger

The invention is applicable to the field of communication, and provides a biological recognition-based rapid access method and a biological recognition-based rapid access device. The method comprises the following steps: receiving a login event triggered by a user and acquiring biological features of the current user by a mobile terminal; matching the acquired biological features with the pre-stored original biological features; when the matching is successful, looking up authentication data corresponding to the matched original biological features according to the mapping relation between the preset original biological features and the authentication data of the network, wherein the authentication data comprise a network address, an account and a password; accessing to the network through the authentication data corresponding to the original biological features. According to the method and the device provided by the invention, the user does not need to remember a plurality of accounts or passwords, so that convenience is brought to the user.

Owner:NUBIA TECHNOLOGY CO LTD

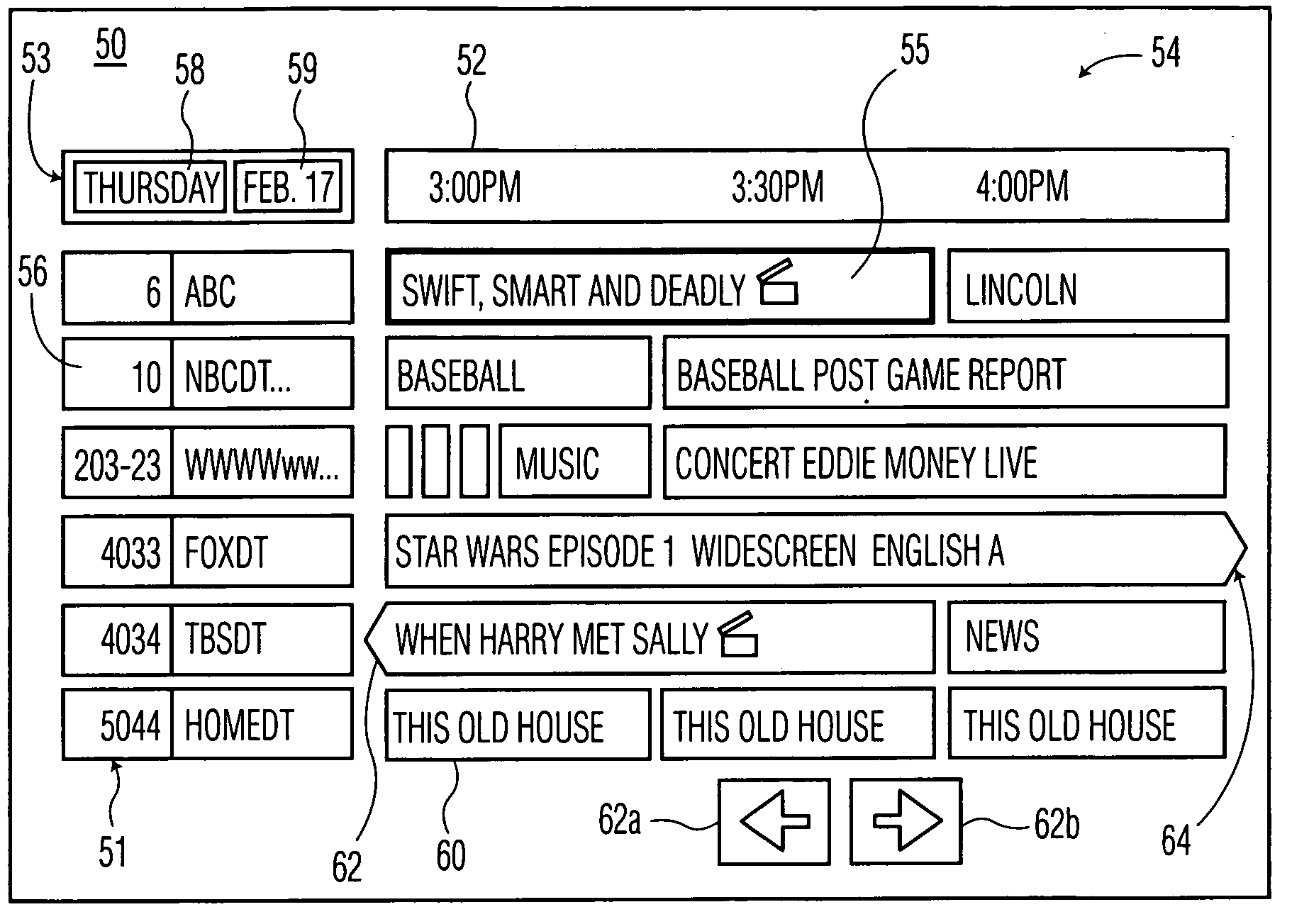

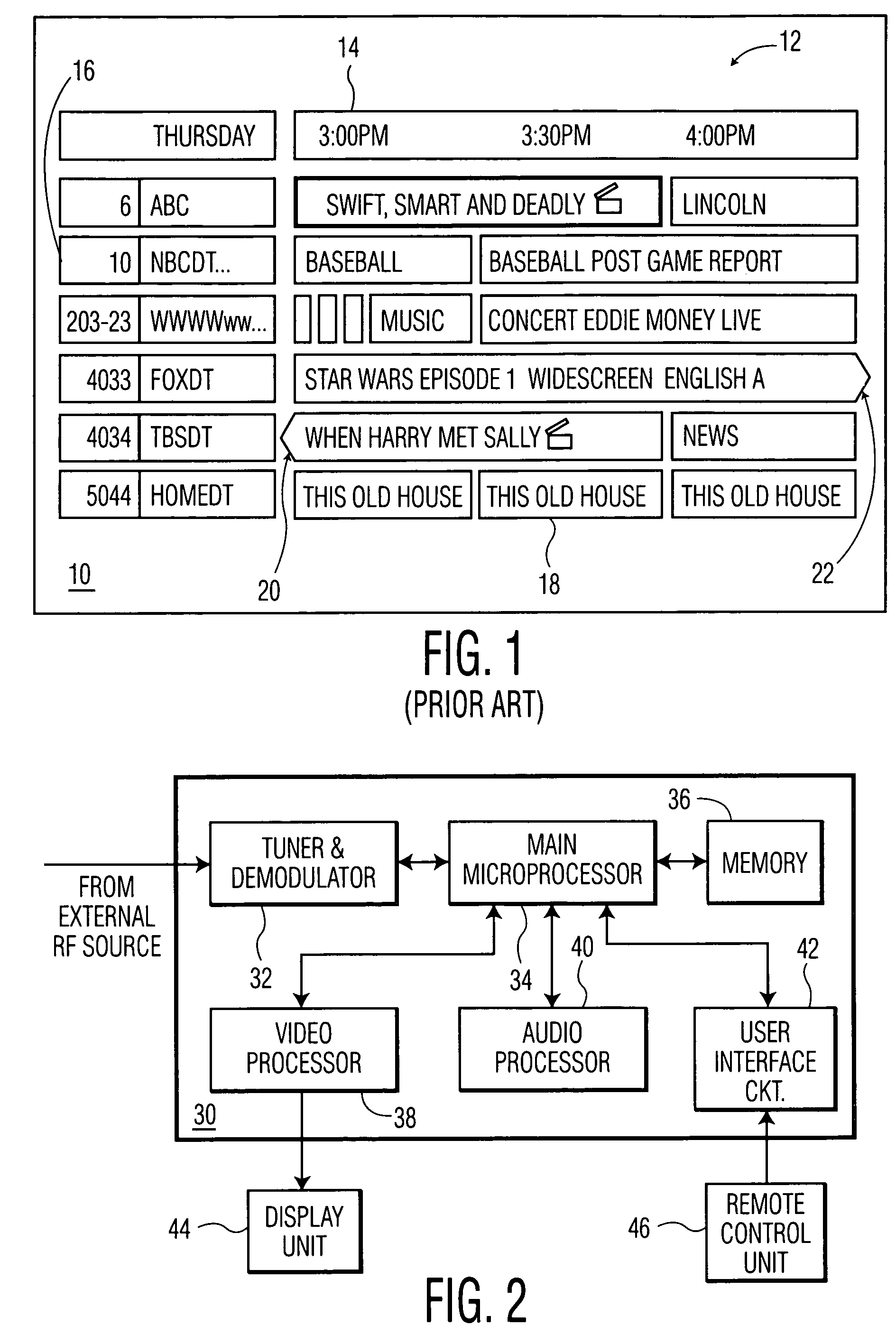

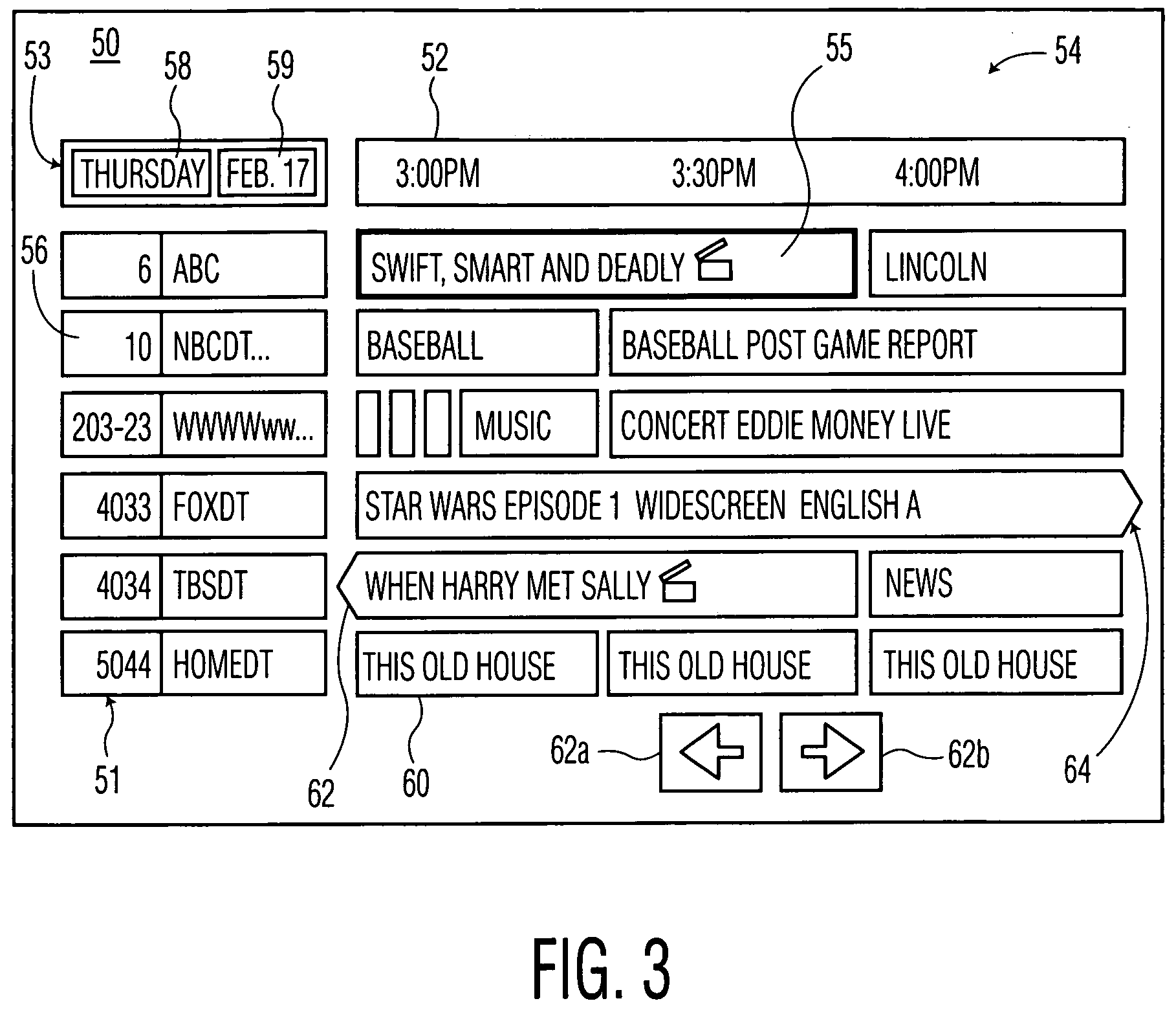

Method and apparatus for rapid access of program guide information

InactiveUS7100184B1Easy accessTelevision system detailsBroadcast with distributionDisplay deviceRapid access

A method for rapidly accessing program guide information is described. The method includes displaying program guide information on a grid showing a channel axis and a time axis, with each program positioned at a location in the grid representing a channel of transmission and a corresponding time of transmission. The method includes the steps of: (a) displaying the program guide information; (b) placing a time selection field on the display; (c) highlighting and activating the time selection field; (d) determining a time index in response to the activating step; (e) calculating a new time of transmission for display based on the time index; and (f) displaying the program guide information at the new time of transmission. The time selection field includes a page field, a day field and a date field. The page field is adapted to provide a six-hour time index, the day field is adapted to provide a 24-hour time index, and the date field is adapted to provide a seven-day time index. The method includes activating the time selection field to index forward in time and backwards in time.

Owner:PANASONIC CORP