Time-sharing digital error correction circuit device of high-speed flow line type analog-digital converter

A technology of analog-to-digital converters and error correction circuits, applied in the direction of analog-to-digital converters, analog/digital conversion calibration/testing, etc., can solve the problems of design complexity, adverse effects of chip area, and increased circuit complexity, and achieve reduction The effect of small circuit design complexity, small amount of computation, and short delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

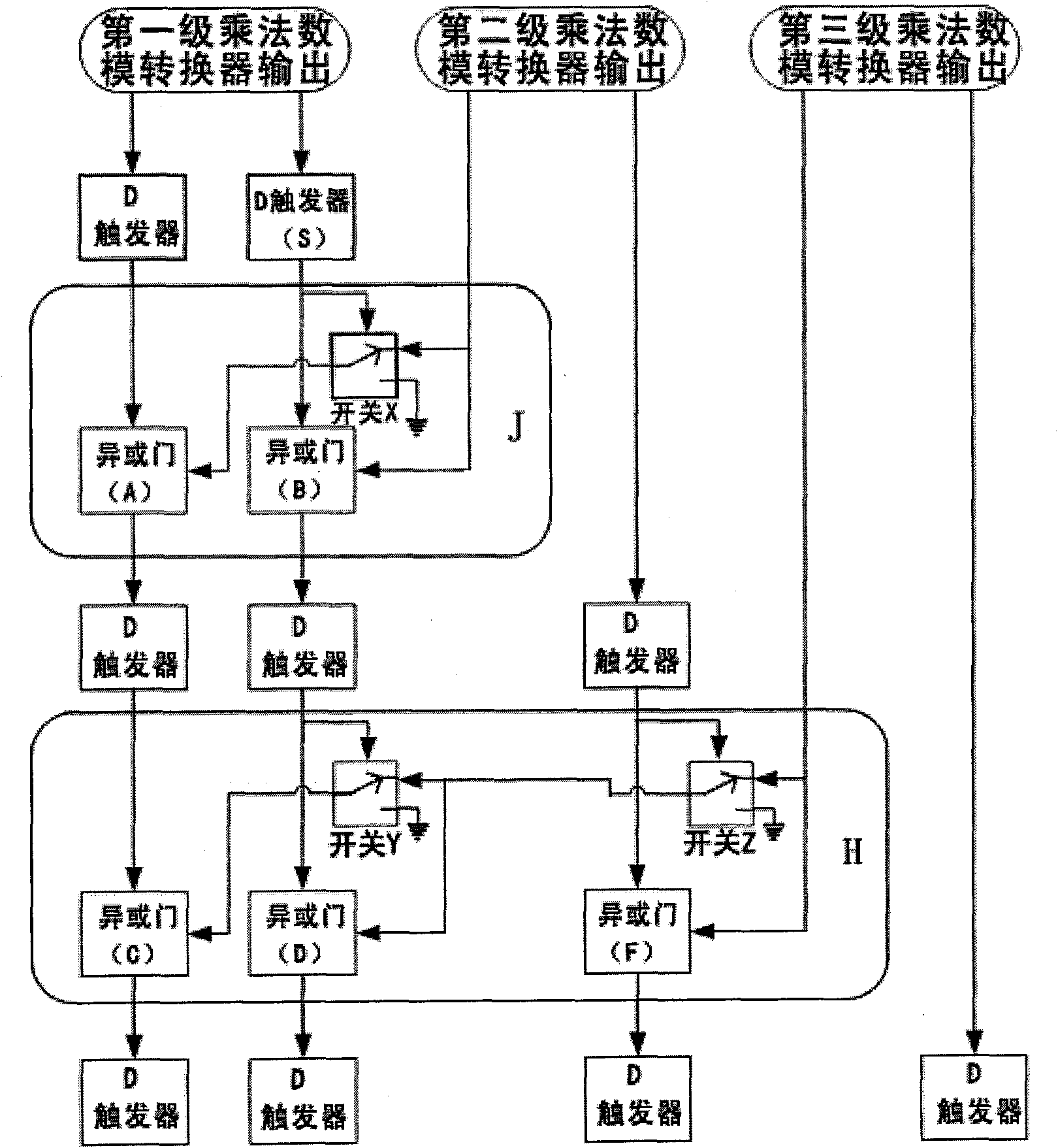

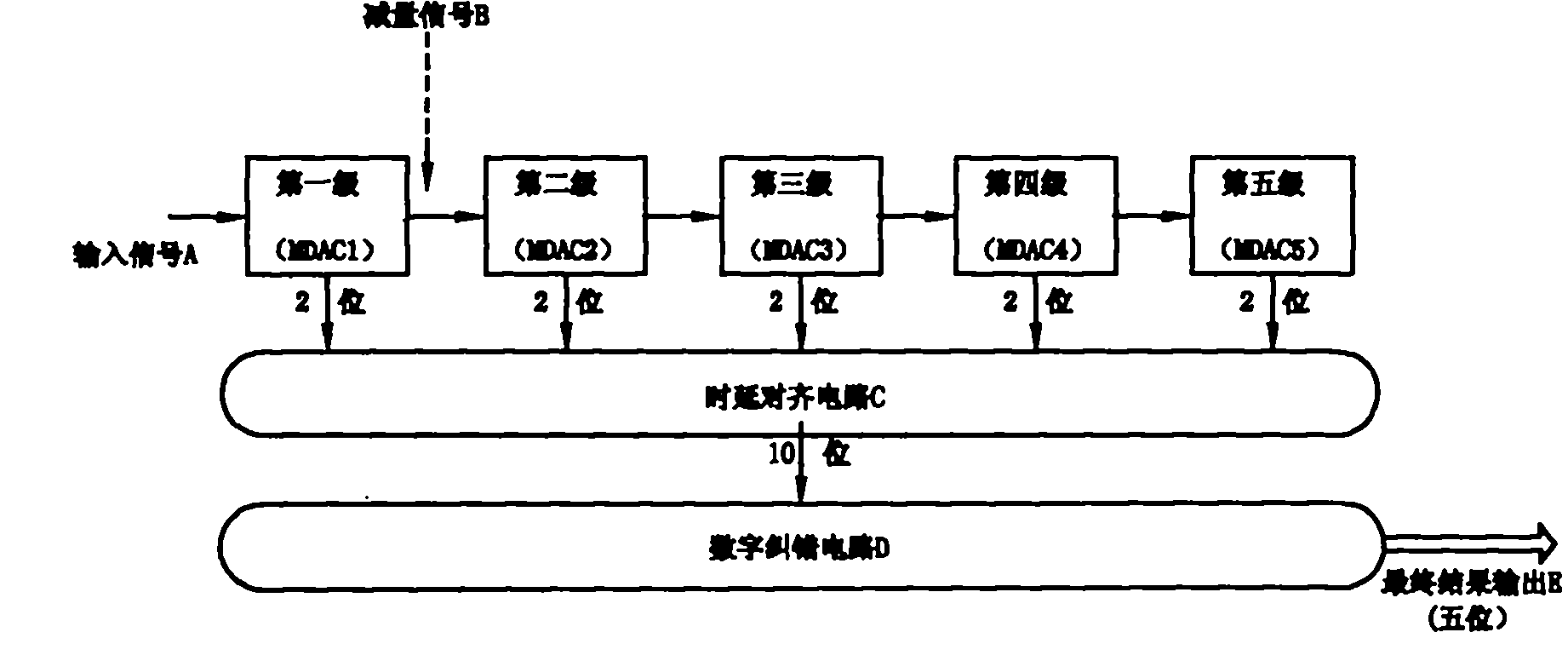

[0019] Specific embodiment one: the time-sharing digital error correction circuit of the analog-to-digital converter of four-bit precision sees image 3 , which includes a three-stage multiplication digital-to-analog converter, the high and low bits of the output of the first-stage multiplication digital-to-analog converter are respectively connected to their corresponding D flip-flops, and the D flip-flops connected to the first-stage high bits are connected to the exclusive OR gate (A) input terminal, the D flip-flop (S) connected to the first-level low-level connection is connected to the input terminal of the exclusive-or gate (B), the high-level output of the second-level multiplication digital-to-analog converter is connected to the input terminal of the exclusive-or gate (B), and the first-level low-level connection After the D flip-flop (S) and the high bit of the output of the second-stage multiplication digital-to-analog converter are respectively connected to the inp...

specific Embodiment 2

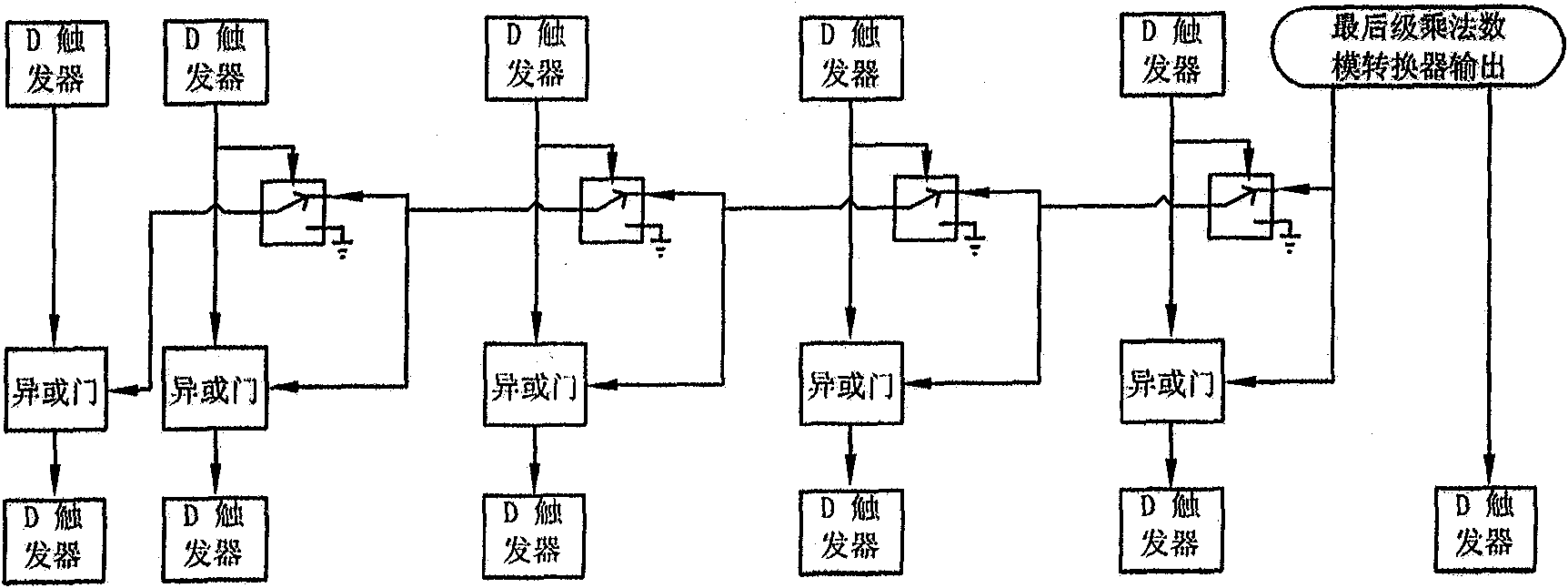

[0022] Specific embodiment two: the last stage of the time-sharing digital error correction circuit of the analog-to-digital converter of six-bit precision sees Figure 4 , which includes the D flip-flop corresponding to the output of the first five bits obtained by the above four-level operation, except that the highest D flip-flop is only connected to the input terminal of the XOR gate, and the flip-flops corresponding to the other four bits are connected to other The input end of the corresponding XOR gate and the input end of the corresponding switch, the output high bit of the final multiplication digital-to-analog converter is connected to the input end of the XOR gate connected to the fifth flip-flop and the input end of the switch, and then The output terminals of the first-level switch are respectively connected to the input terminals of the previous-level switch, the input terminal of the previous-level XOR gate until the next highest level, and the switch output corr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More