A high-precision array analog-to-digital converter for cmos image sensors

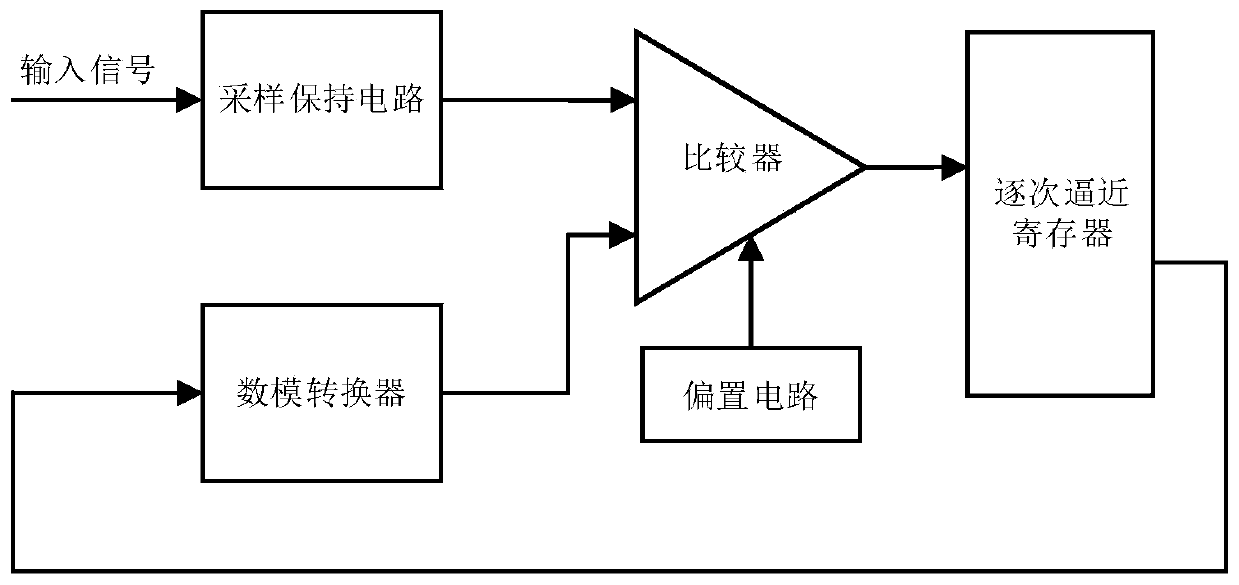

An analog-to-digital converter and image sensor technology, which is applied in the directions of image communication, color TV components, TV system components, etc. Limiting the design of successive approximation analog-to-digital converters and other issues to achieve the effect of reducing dynamic performance degradation and saving capacitor arrays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with the accompanying drawings.

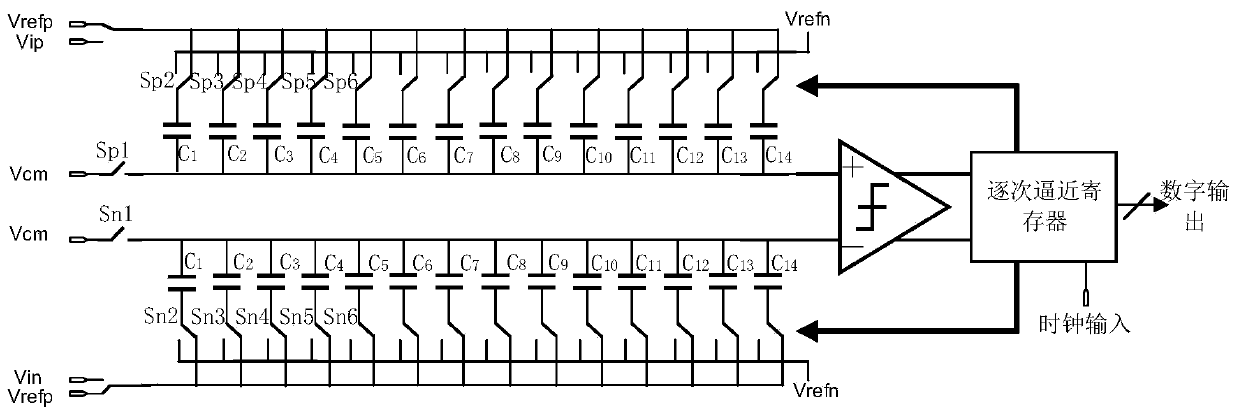

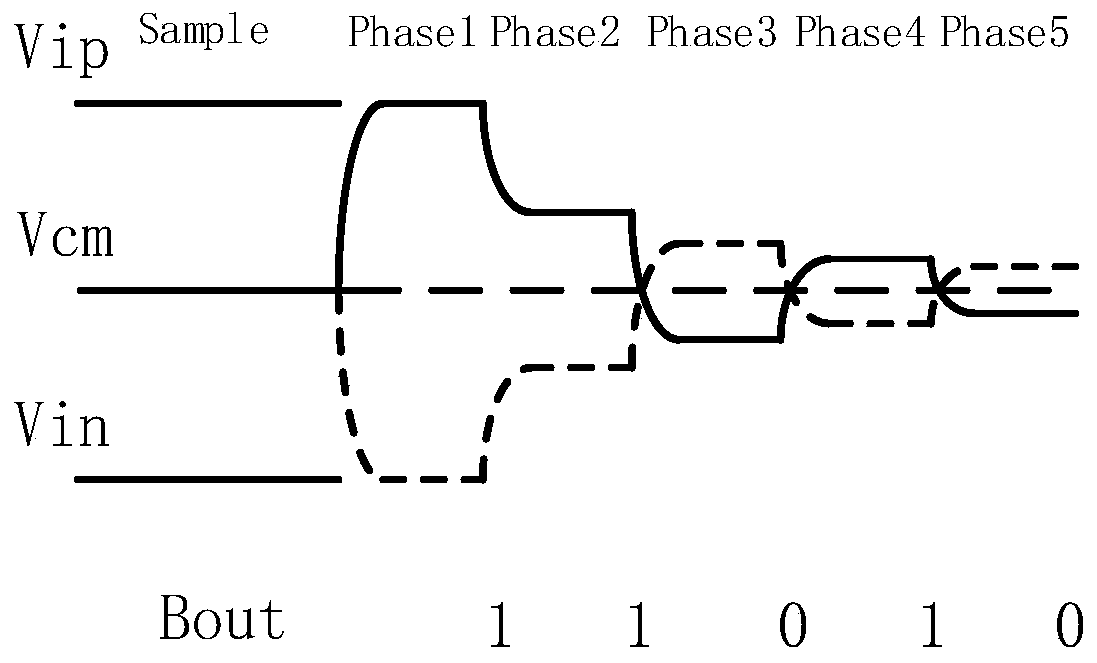

[0031] Such as figure 2 As shown, the SAR ADC adopts a fully differential structure. Take one end as an example: During the sampling phase, the bottom plate of the capacitor is connected to Vip, and the top plate of the capacitor is connected to the common-mode voltage Vcm. Next, the top plate of the highest bit capacitor is converted from the common mode voltage Vcm to Vrefp, and the top plate of other bit capacitors is switched to connect to Vrefn. At this time, the comparator performs the first comparison and outputs the comparison result. If Vip is greater than Vin, the highest bit (MSB for short) value B1 is binary 1, otherwise, it is 0. At the same time, the top plate of the highest bit capacitor is switched to Vrefn. Then the top plate of the sub-high capacitor is connected to Vrefp, and the comparator performs the second comparison and outputs the comparison...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More