Digital error correction

An error correction and error technology, applied in the direction of data representation error detection/correction, error detection/correction, digital transmission system, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

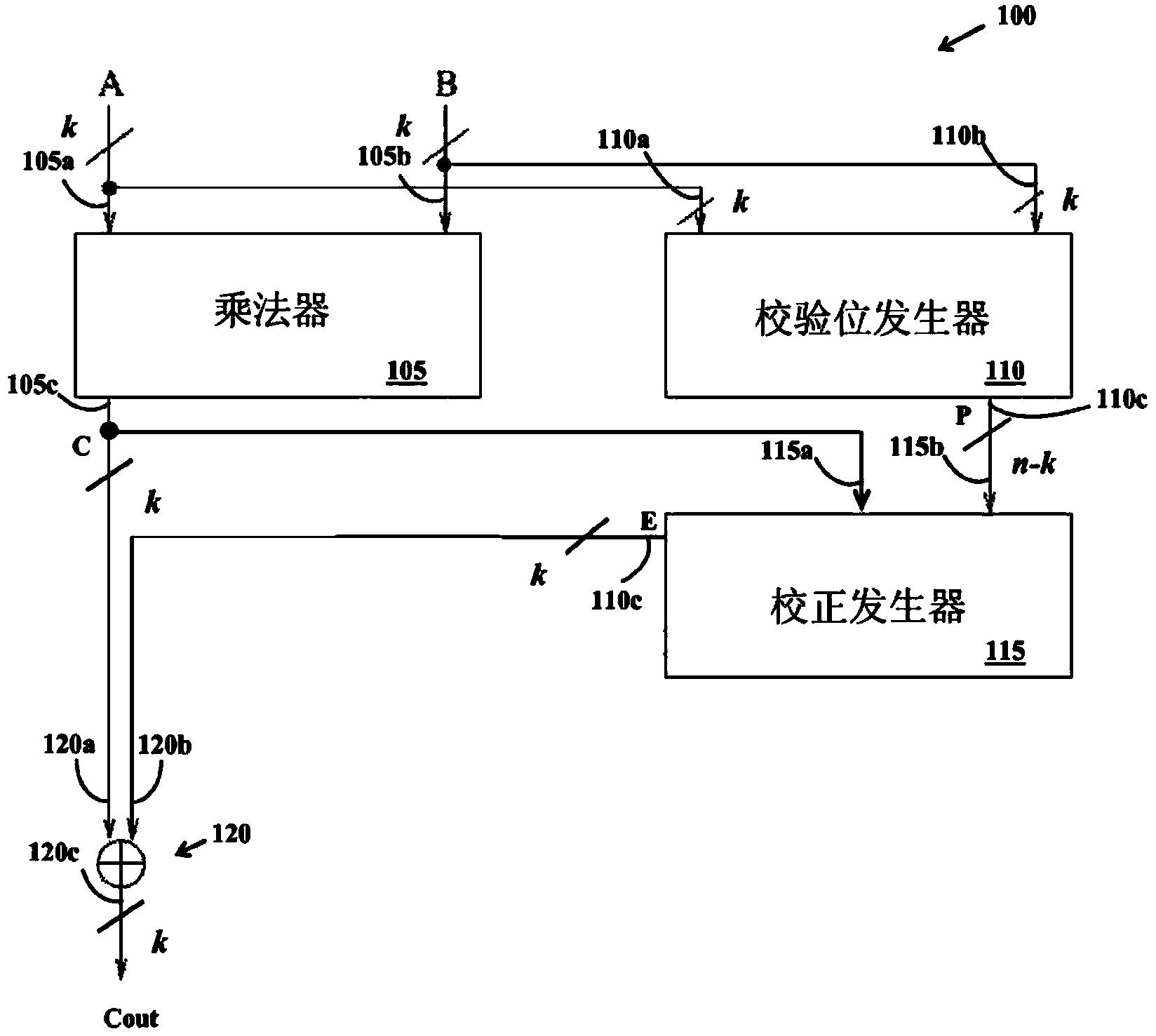

[0052] refer to figure 1 , in a first embodiment of the invention, the circuit 100 comprises a finite field multiplication subcircuit 105 having two parallel inputs 105a, 105b and a parallel output 105c. The multiplication subcircuit 105 is arranged to produce a product C at an output 105c. The product C is the Galois field GF(2 k ) over the field where the two operands are element-wise. The two parallel inputs 105a, 105b and the parallel output 105c are k bits wide, ie each consists of k bits.

[0053] In other embodiments, the finite field multiplication subcircuit 105 may be replaced by circuitry for performing other finite field arithmetic, such as multiplicative inversion or exponentiation (eg, squaring) operations. For example, in some embodiments, finite field multiplication subcircuit 105 may be replaced by circuitry for performing arithmetic other than finite field arithmetic (eg, two's complement binary arithmetic).

[0054] In a first embodiment, the circuit 100...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More