Patents

Literature

277 results about "12-bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, 12-bit integers, memory addresses, or other data units are those that are 12 bits (1.5 octets) wide. Also, 12-bit CPU and ALU architectures are those that are based on registers, address buses, or data buses of that size.

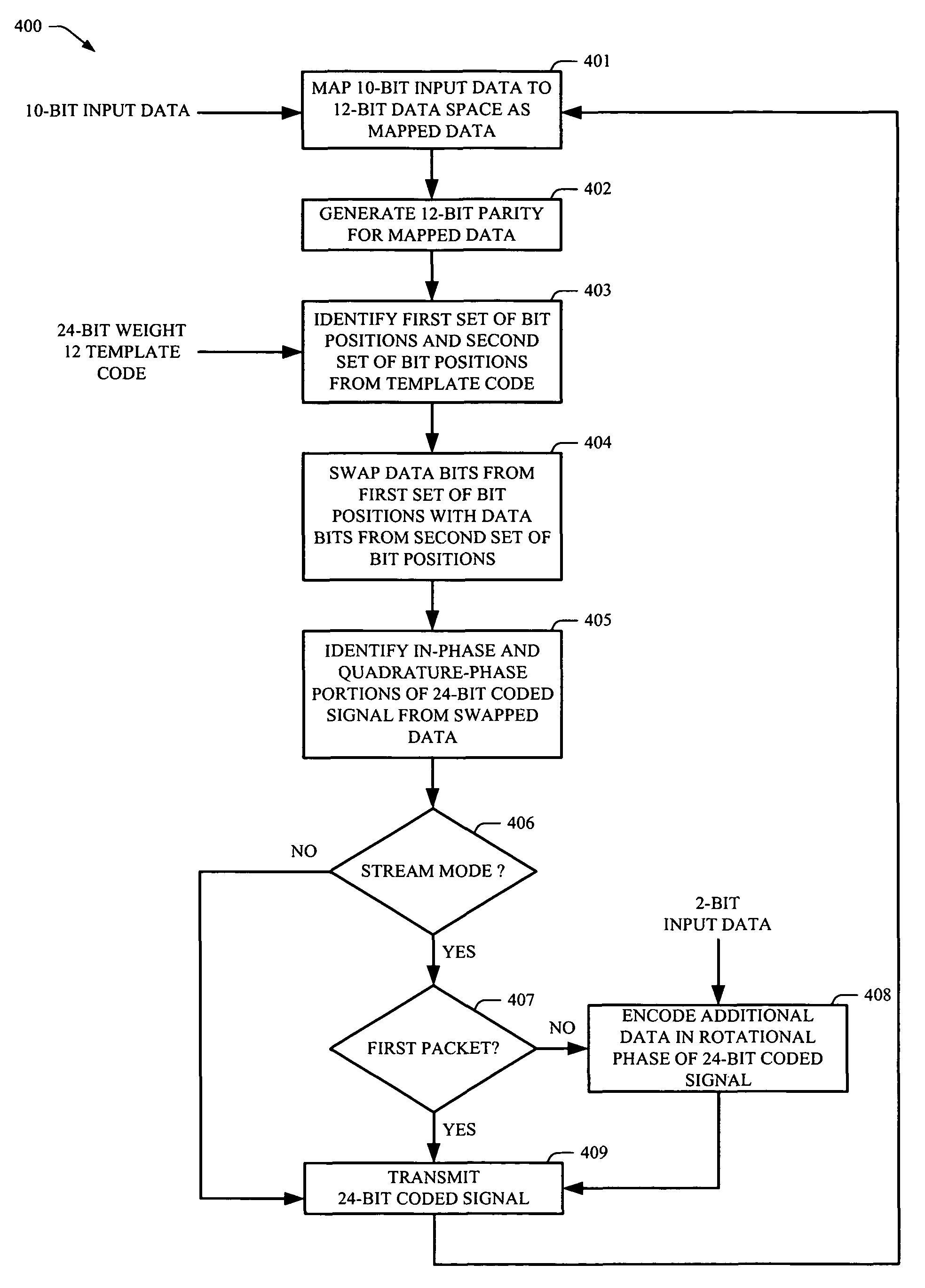

Rotationally invariant non-coherent burst coding

ActiveUS7779332B2Error correction/detection using block single space codingError preventionBit field24-bit

Owner:ALFRED E MANN FOUND FOR SCI RES

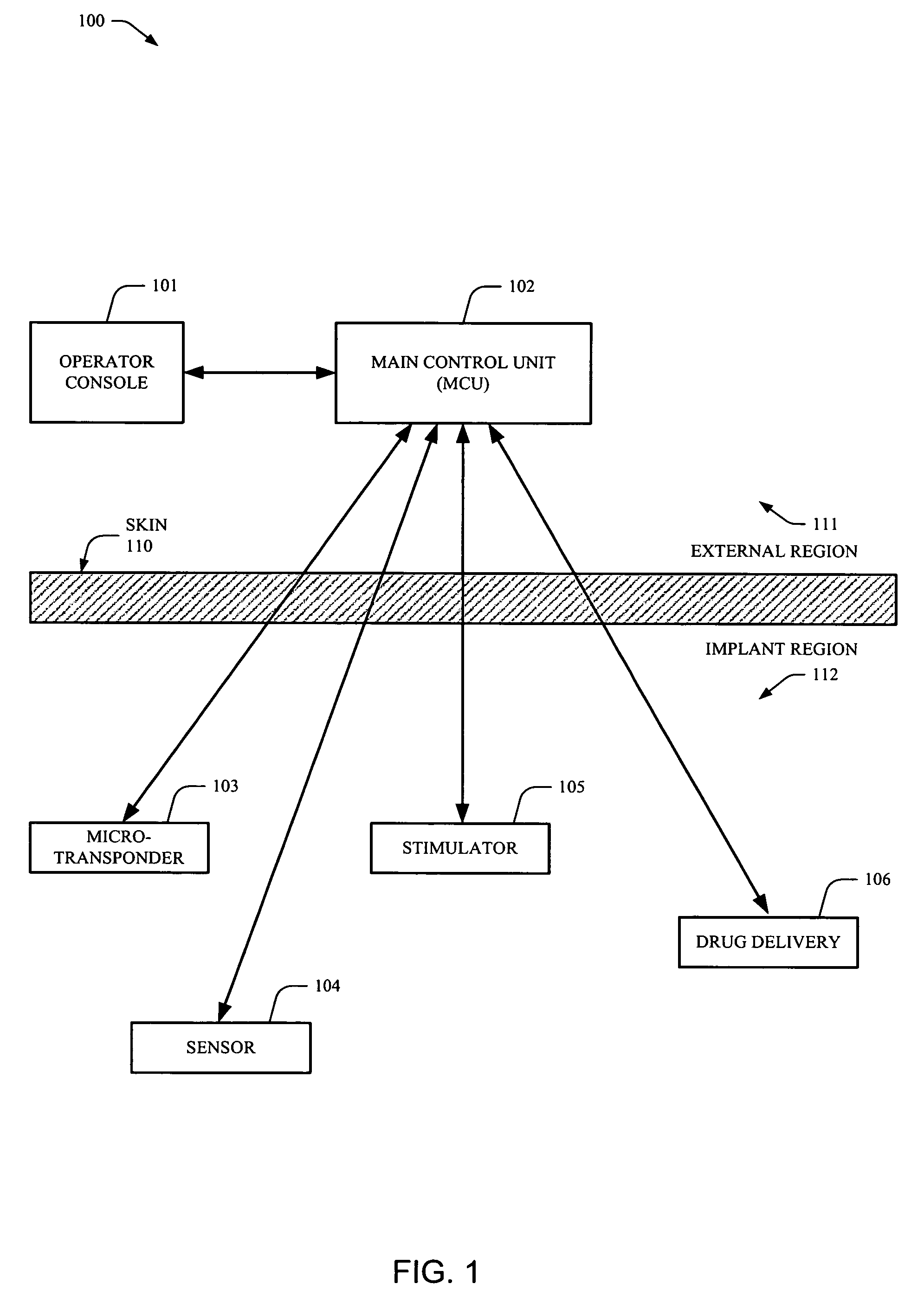

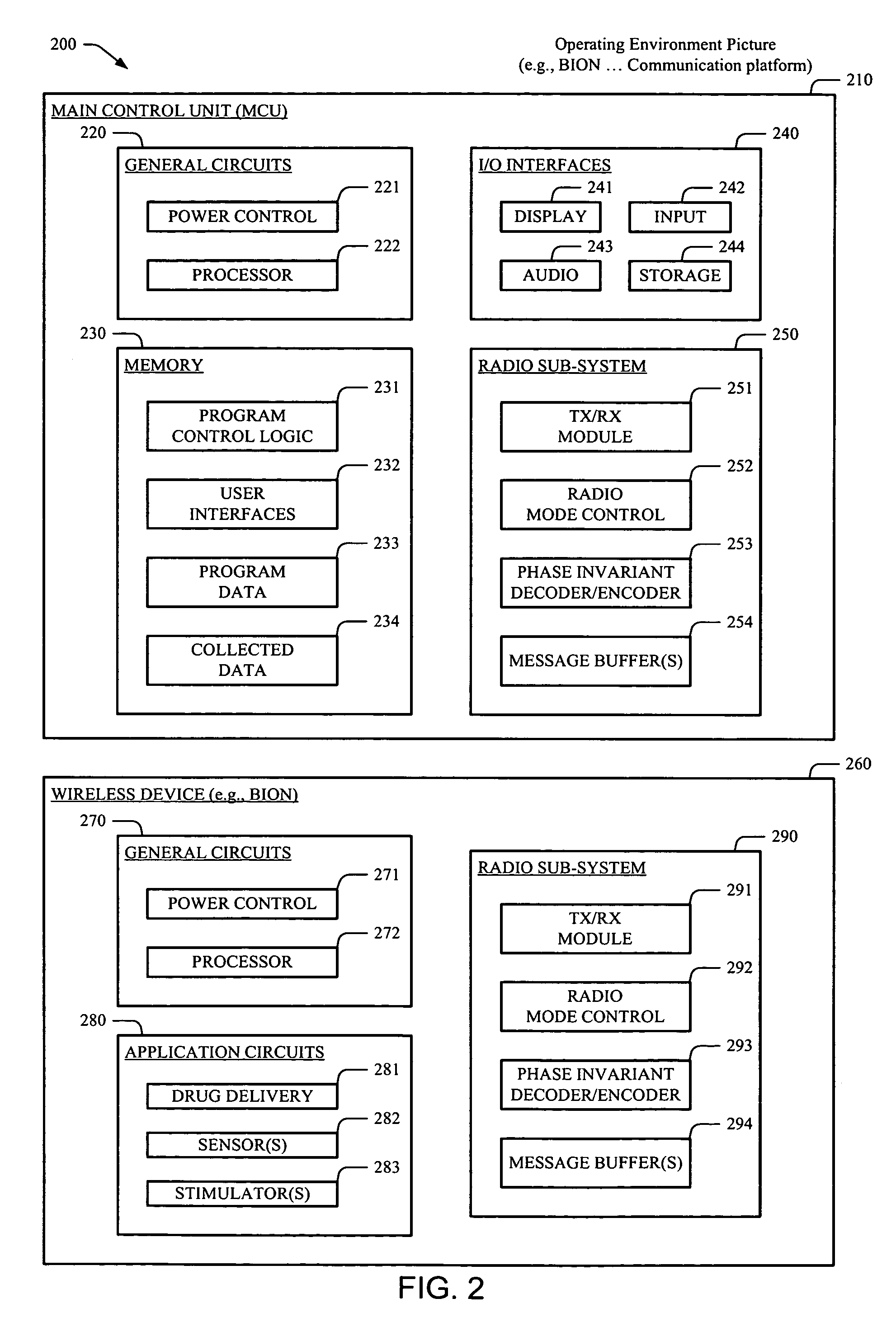

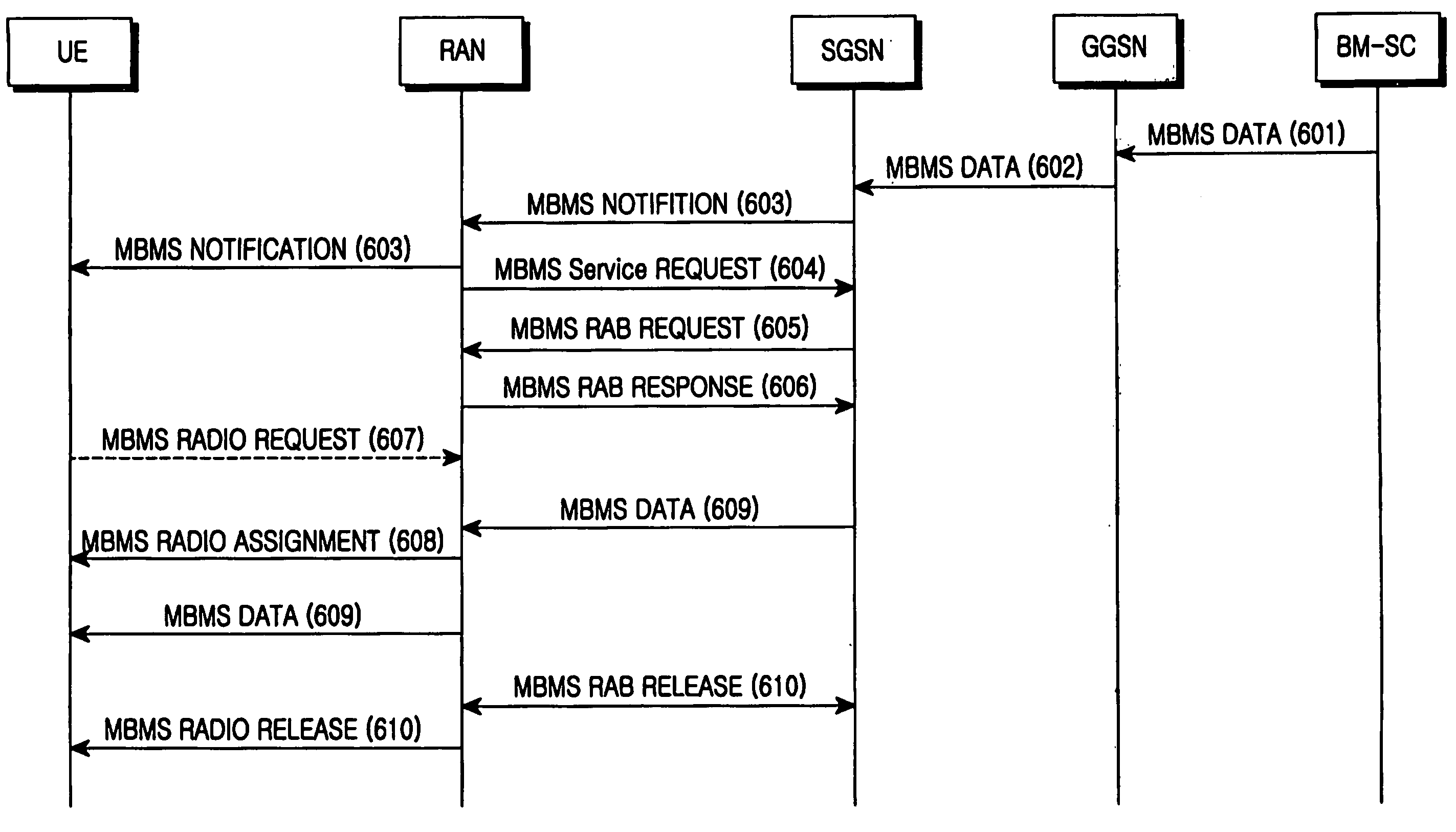

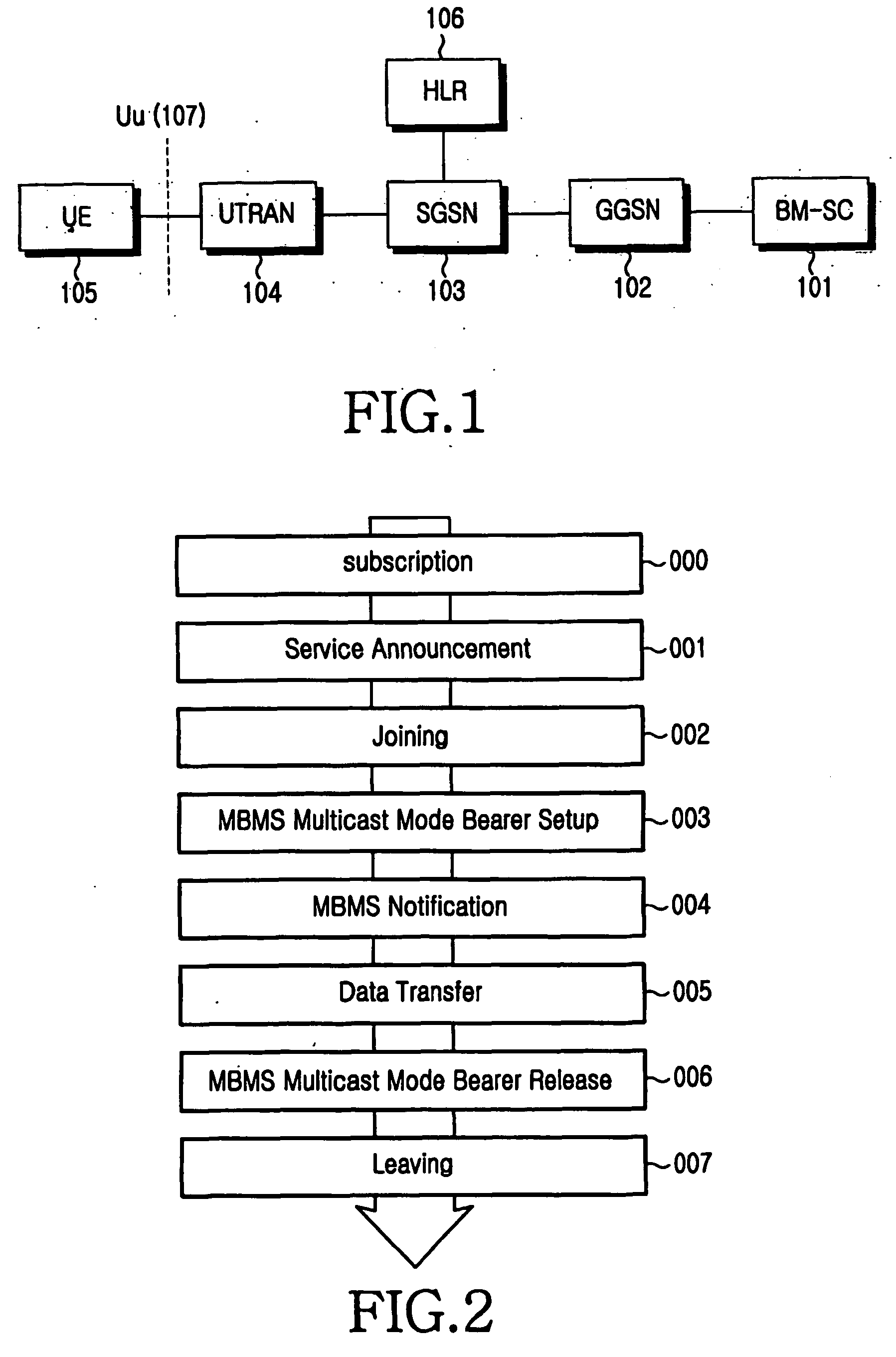

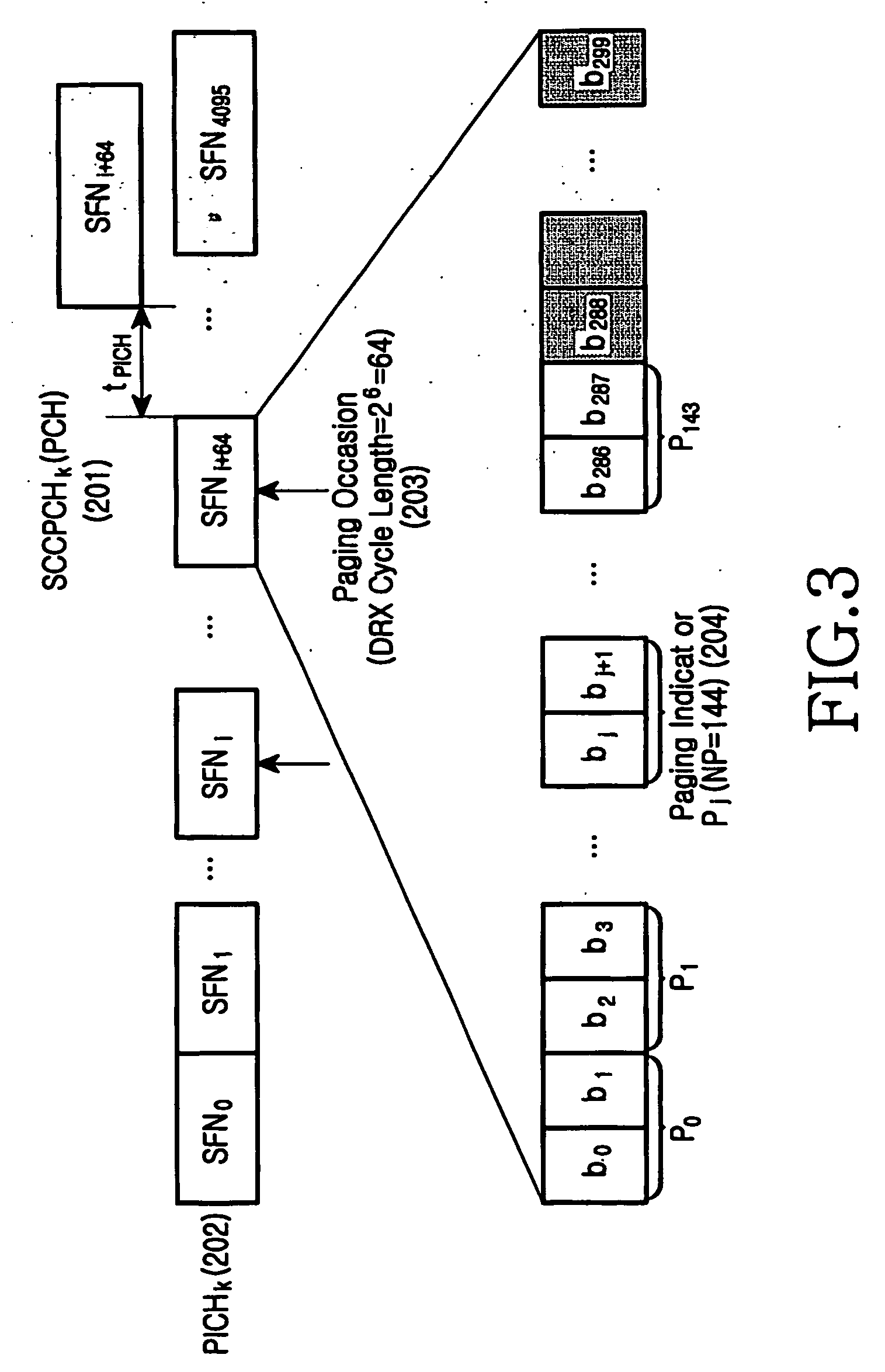

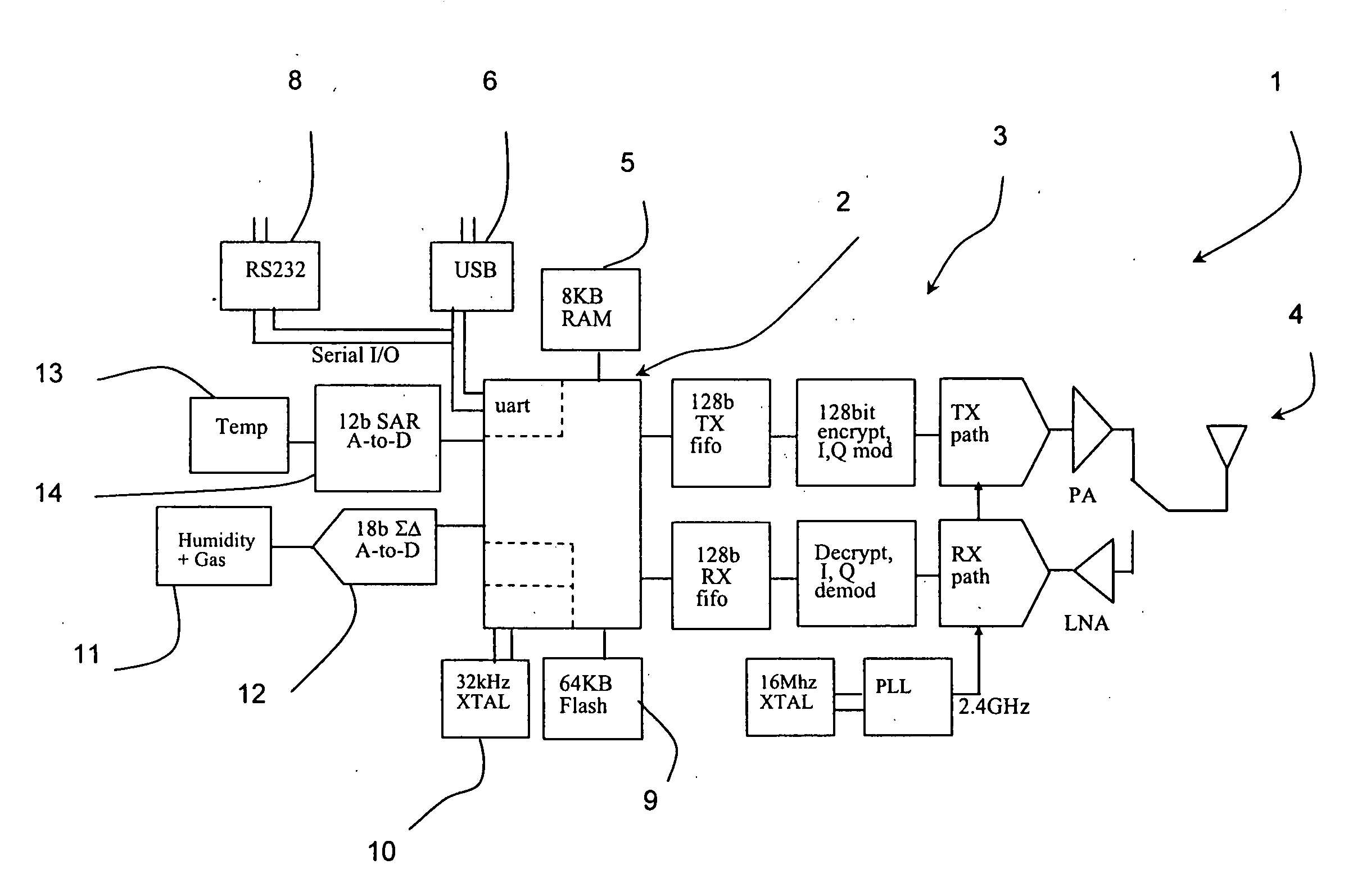

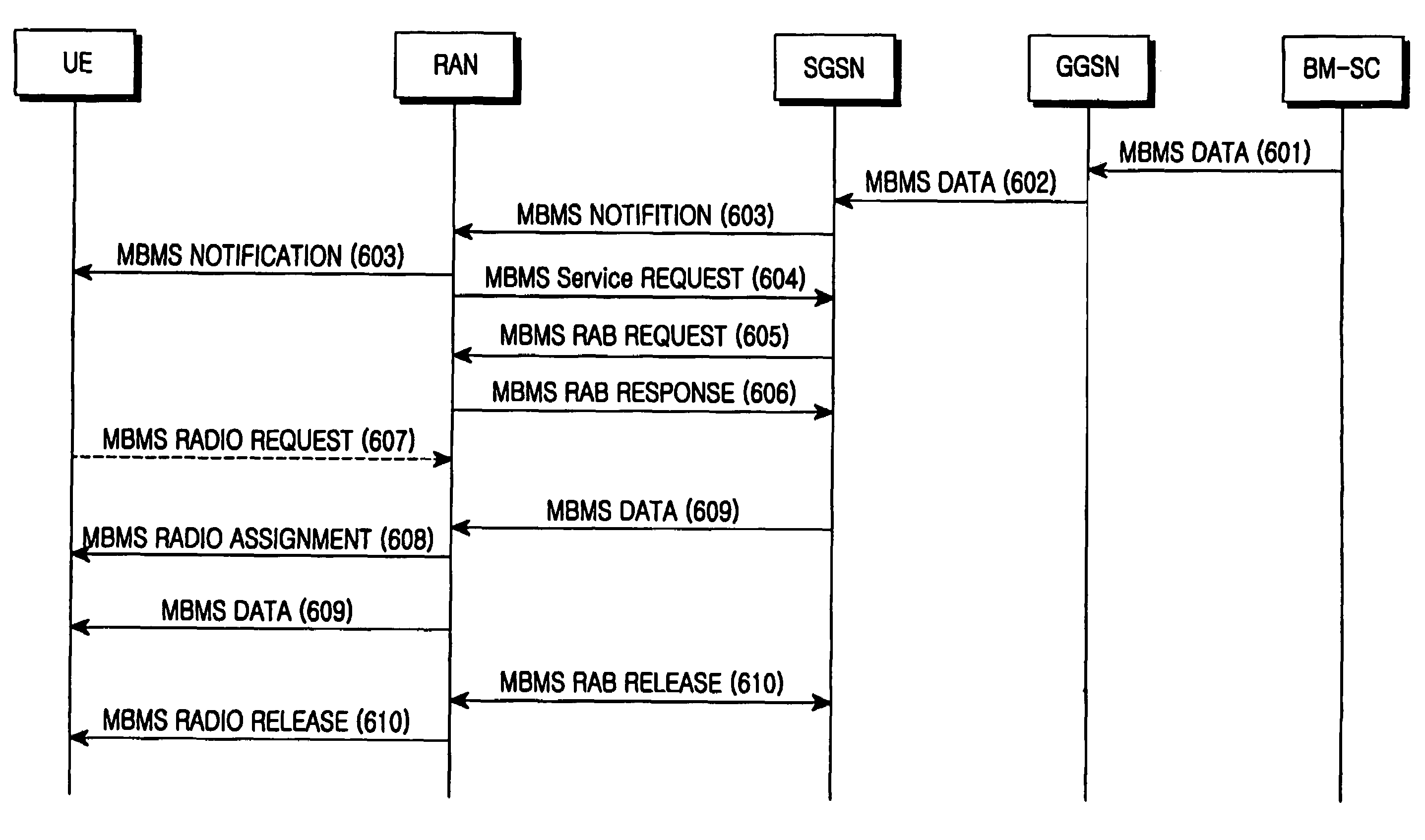

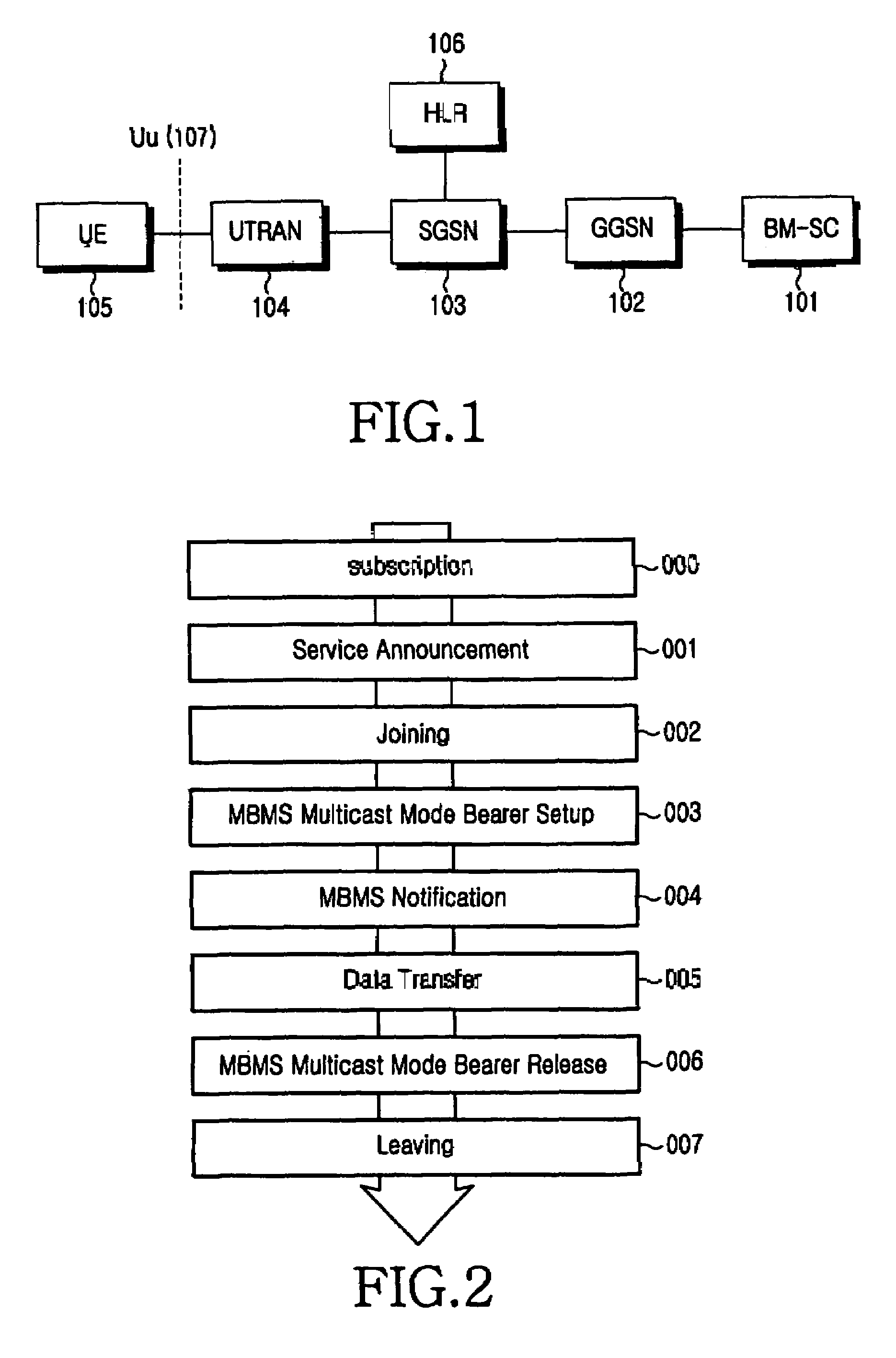

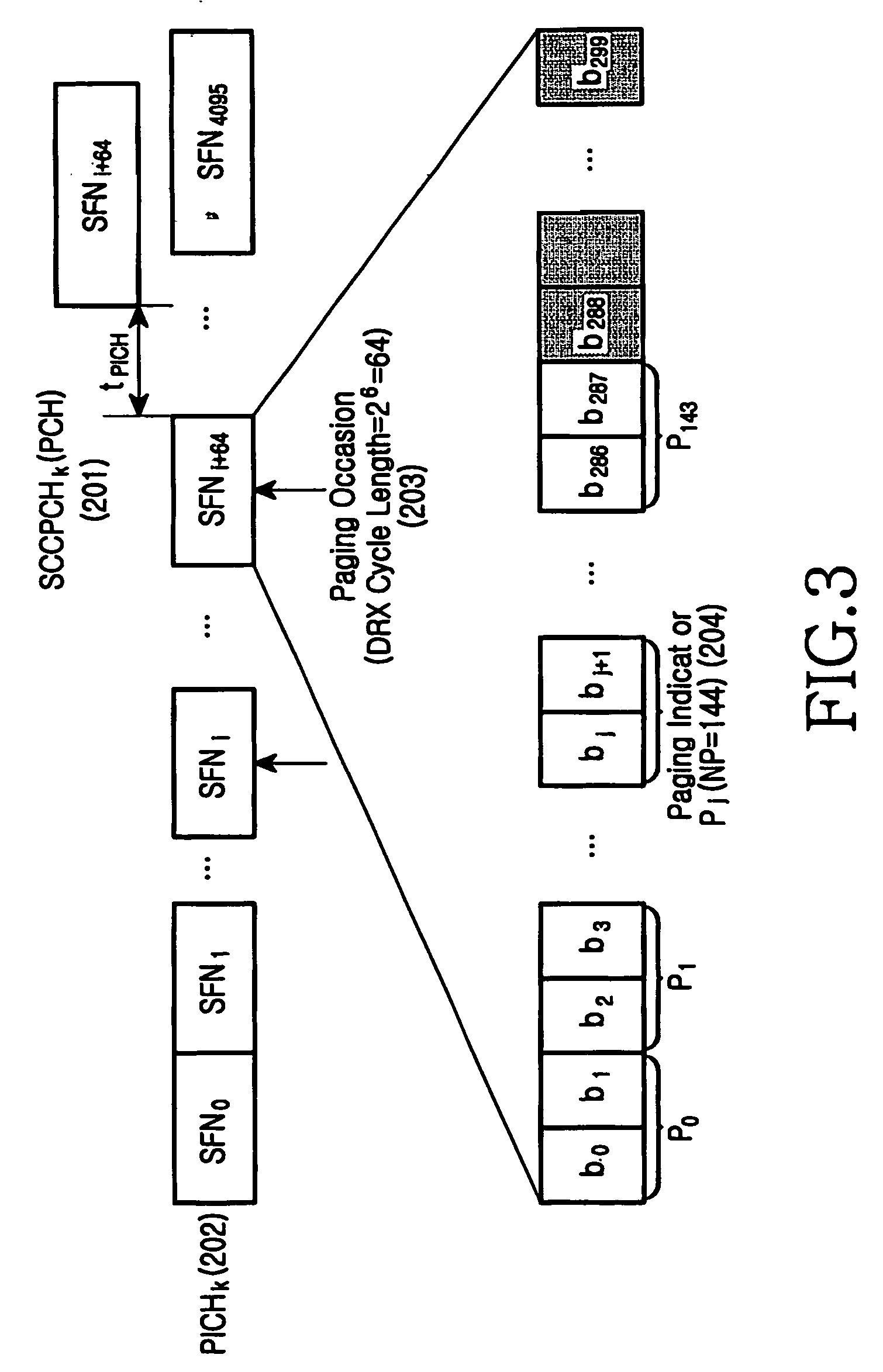

Multimedia broadcast and multicast service paging

ActiveUS20060104225A1Not to wasteLow efficiencySpecial service provision for substationSpatial transmit diversityAir interfaceMobile communication systems

This invention provides a paging method for Multimedia Broadcast / Multicast Service in mobile communication system paging process and radio resource setup process are merged in this method to try to reduce uplink responses. This invention extends existing PCH IubFP frame structure by adding MBMS Indication bit(MI) to PCH IubFP frame. The PCH IubFP frame includes Paging Indication (PI) and Paging Message. Paging message carries MBMS service information. MBMS Service Identity or MBMS Paging Indicator is added to the reserved 12 bits in Paging Indicator Channel (PICH) frame structure. Radio Network Controller (RNC) transfers Paging Indicator Message and paging message to Base Station (Node B) so as to send over the air-interface.

Owner:SAMSUNG ELECTRONICS CO LTD +1

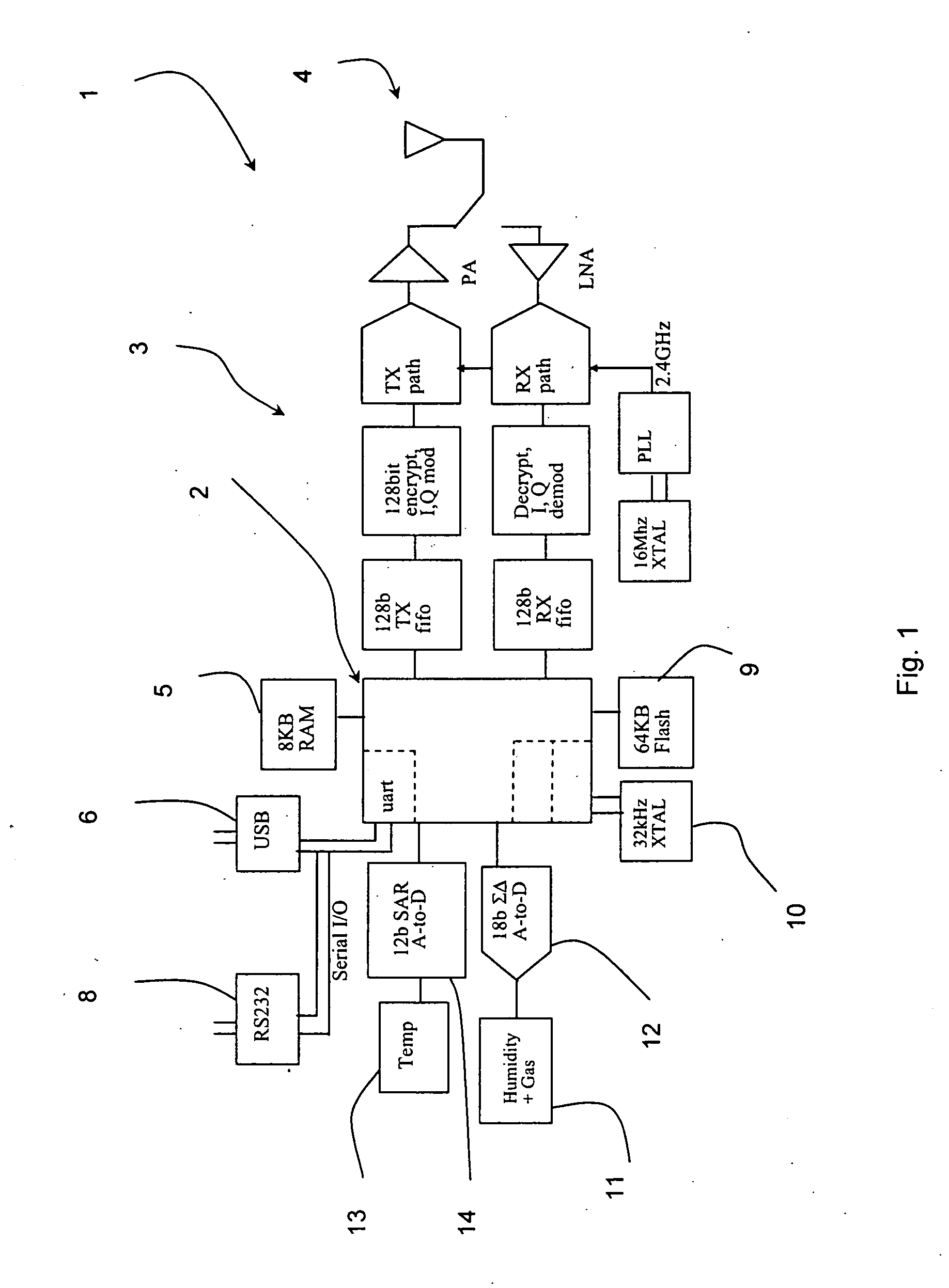

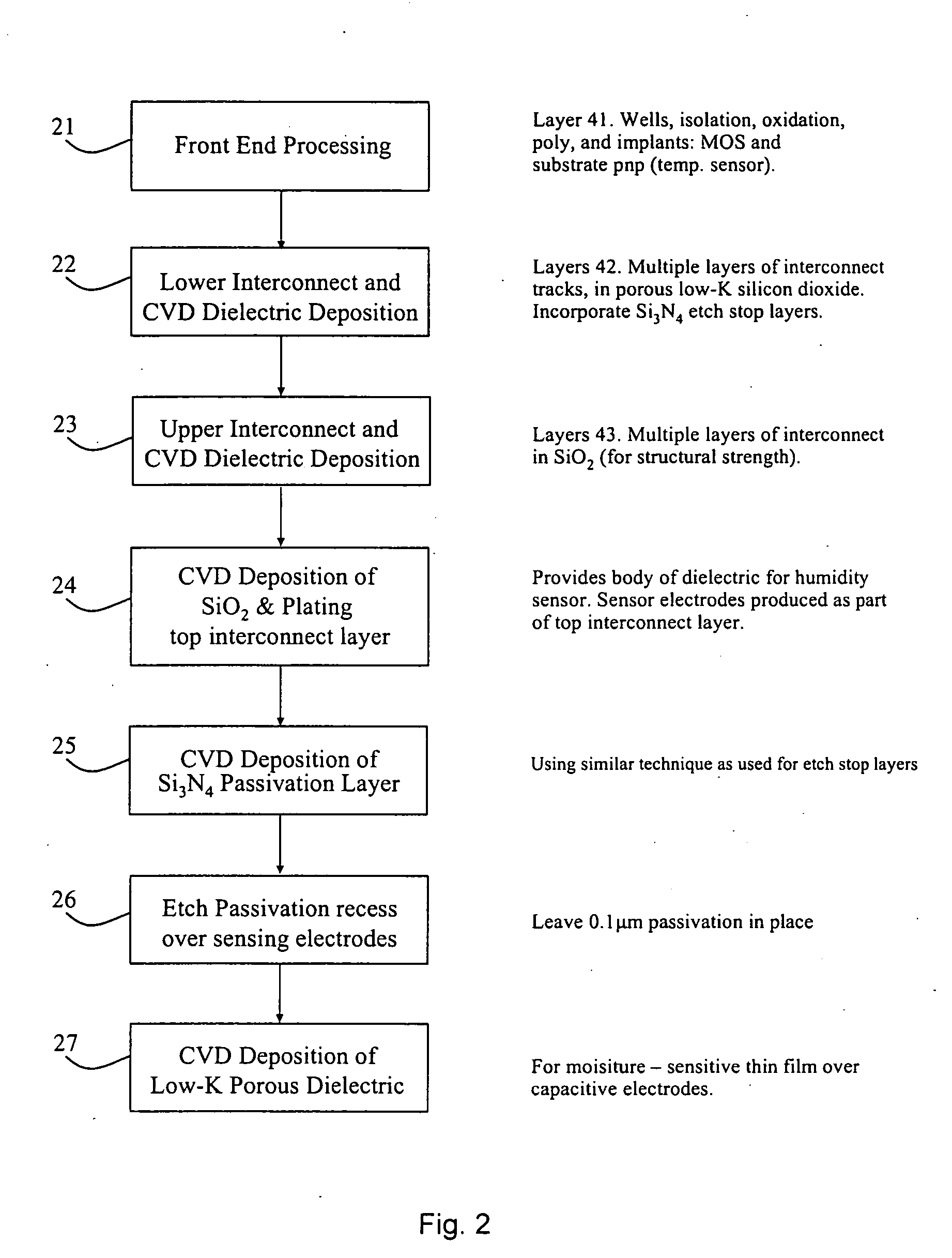

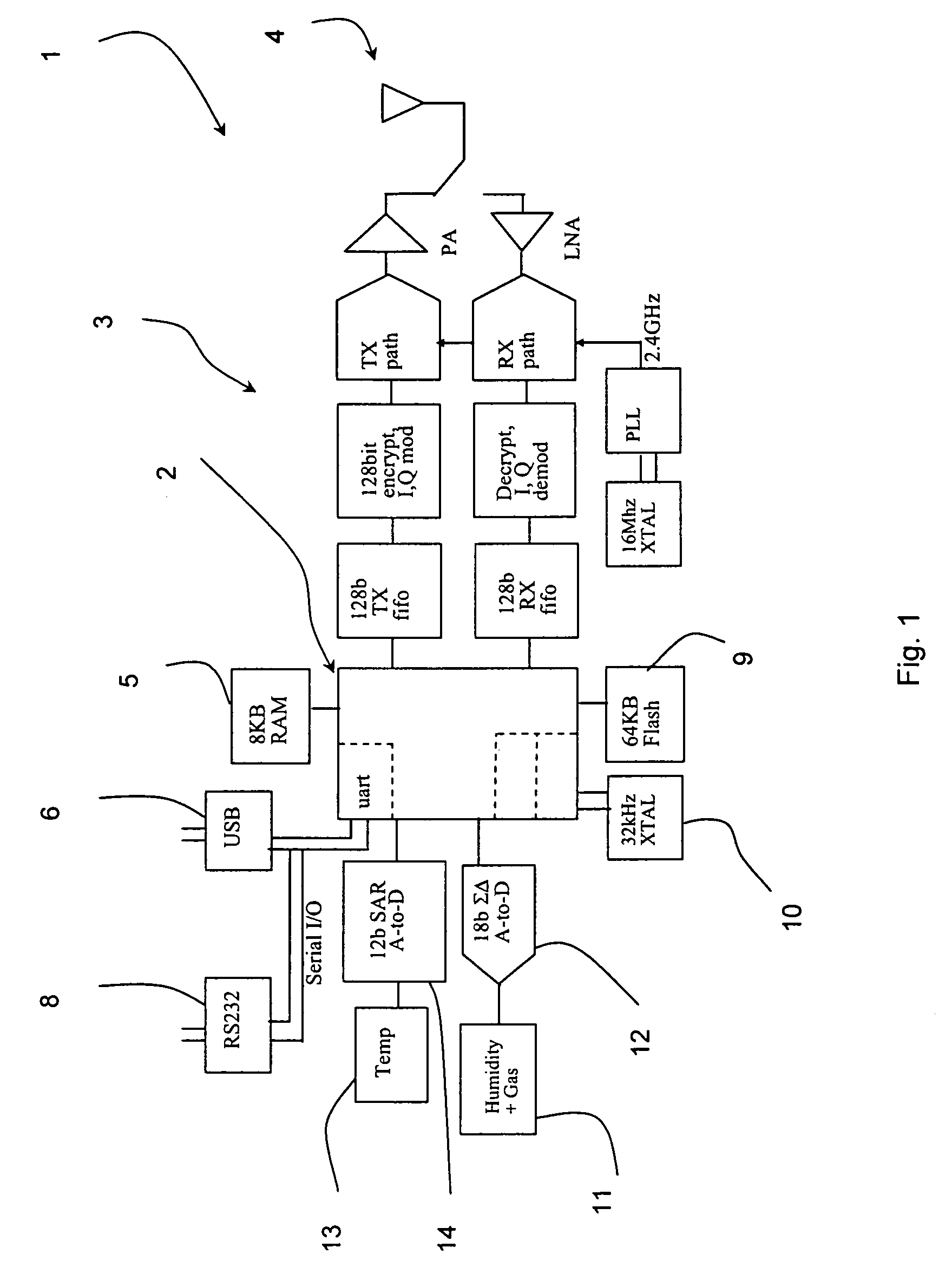

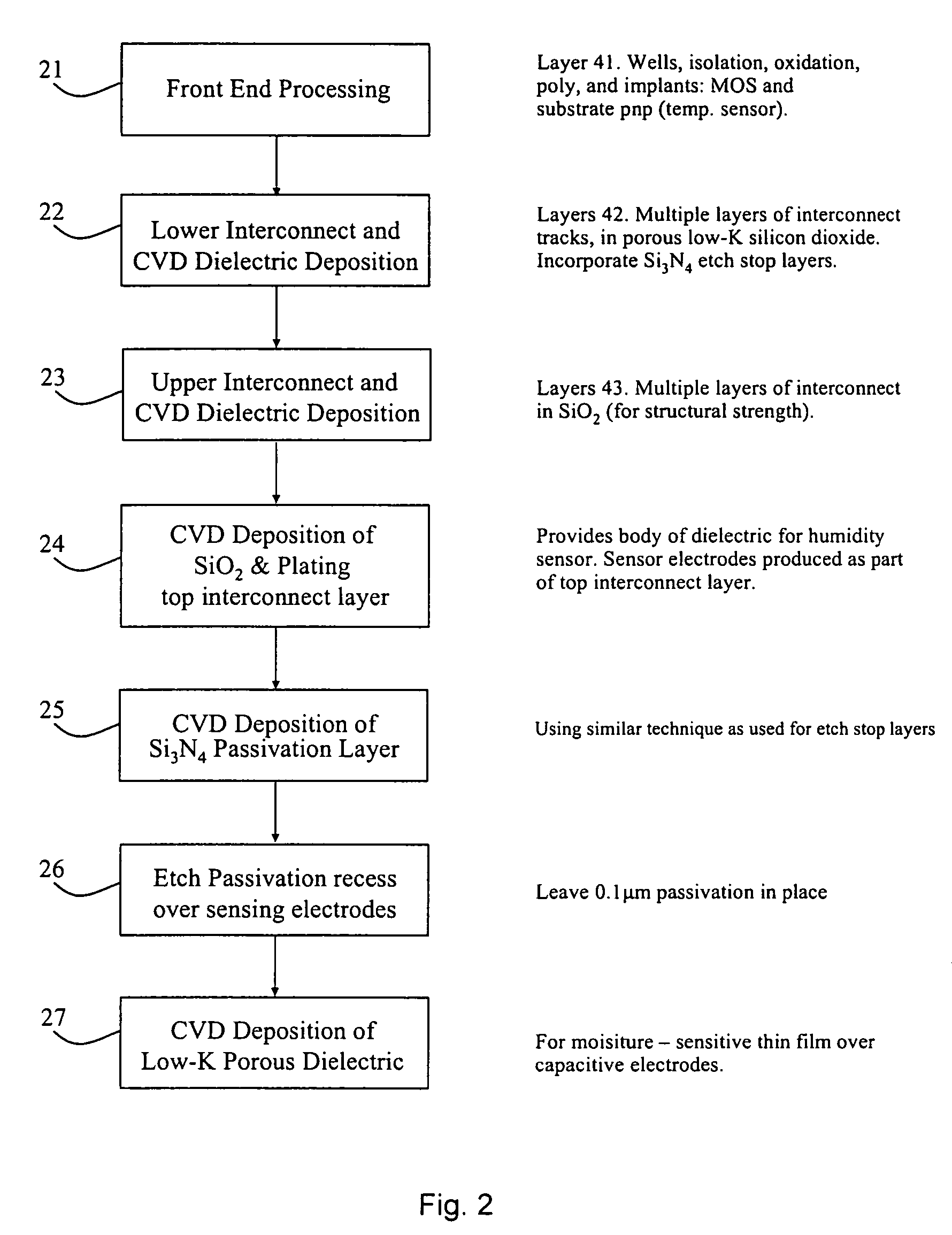

Integrated electronic sensor

ActiveUS20050218465A1Increase productionTransistorSemiconductor/solid-state device detailsMicrocontrollerLine sensor

A single chip wireless sensor (1) comprises a microcontroller (2) connected by a transmit / receive interface (3) to a wireless antenna (4). The microcontroller (2) is also connected to an 8 kB RAM (5), a USB interface (6), an RS232 interface (8), 64kB flash memory (9), and a 32 kHz crystal (10). The device (1) senses humidity and temperature, and a humidity sensor (11) is connected by an 18 bit ΣΔ A-to-D converter (12) to the microcontroller (2) and a temperature sensor (13) is connected by a 12 bit SAR A-to-D converter (14) to the microcontroller (2). The device (1) is an integrated chip manufactured in a single process in which both the electronics and sensor components are manufactured using standard CMOS processing techniques, applied to achieve both electronic and sensing components in an integrated process.

Owner:SILICON LAB INC

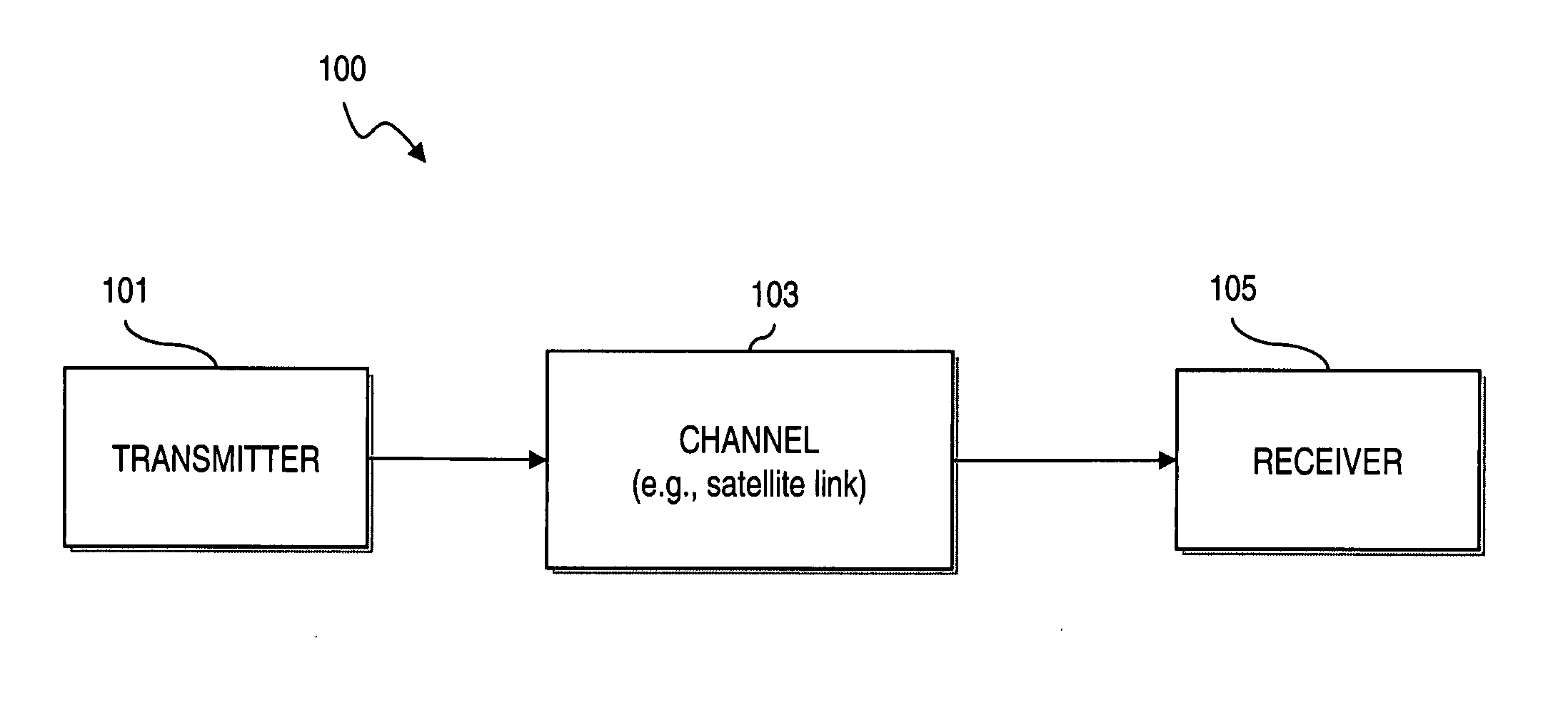

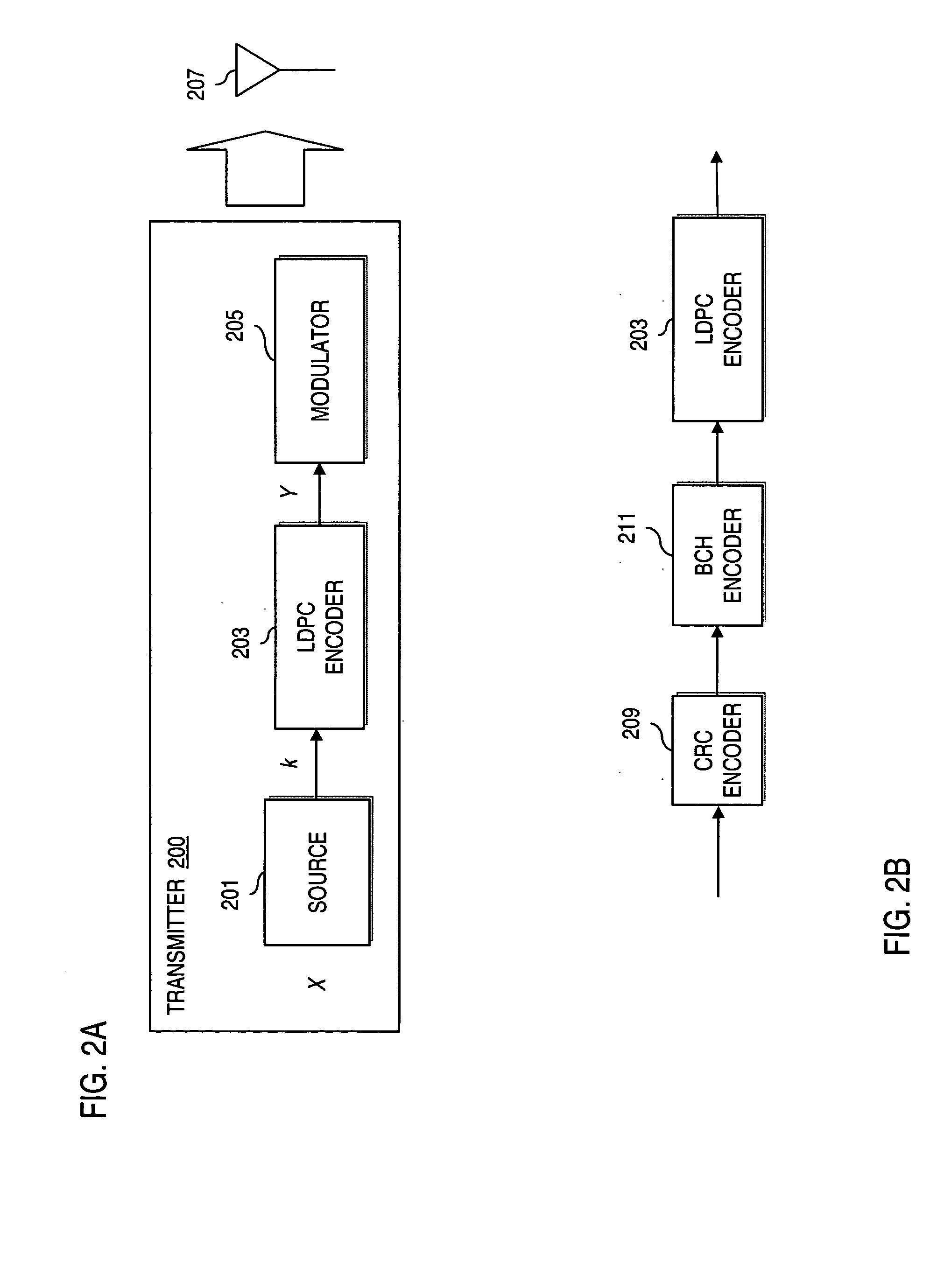

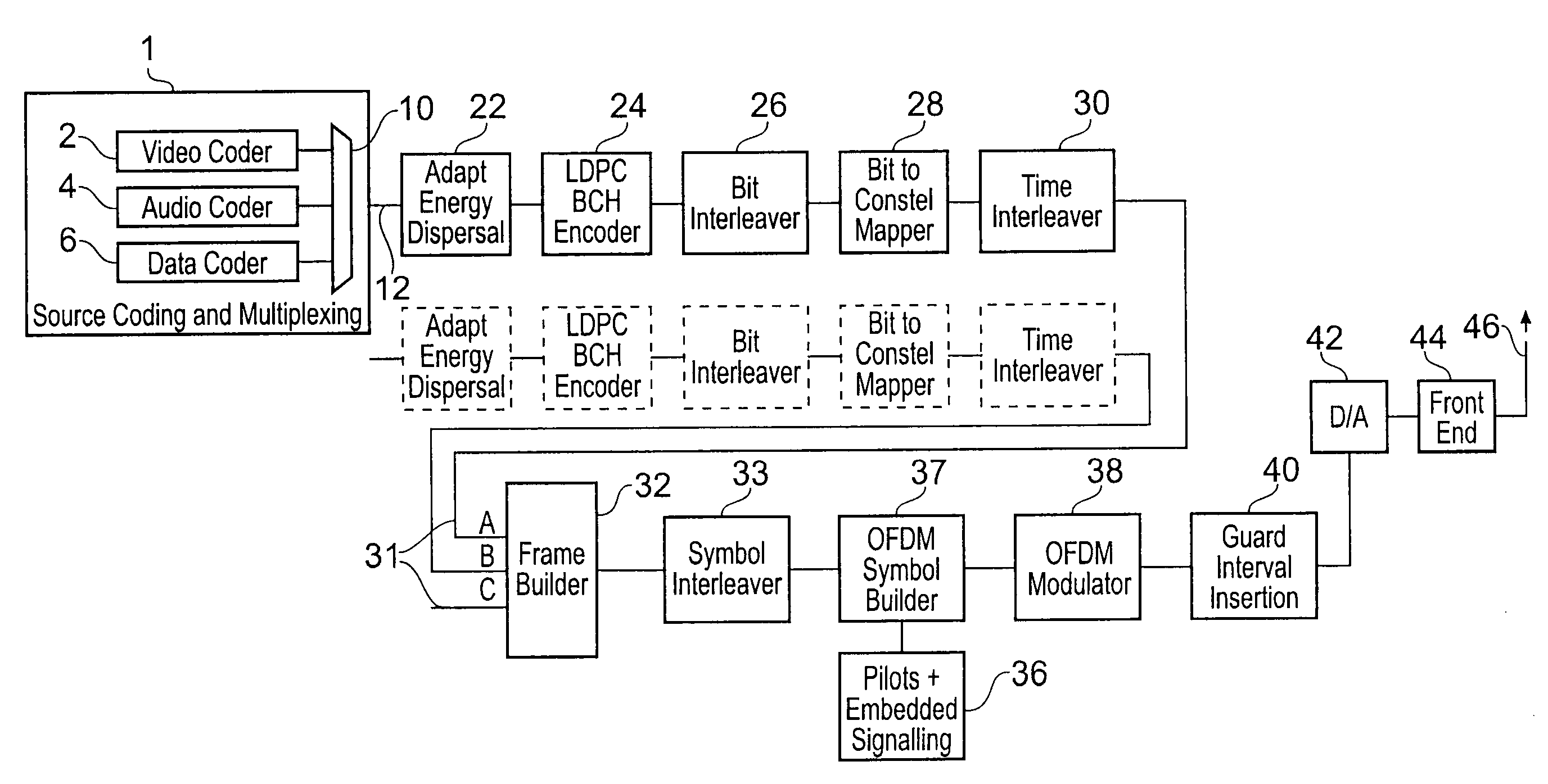

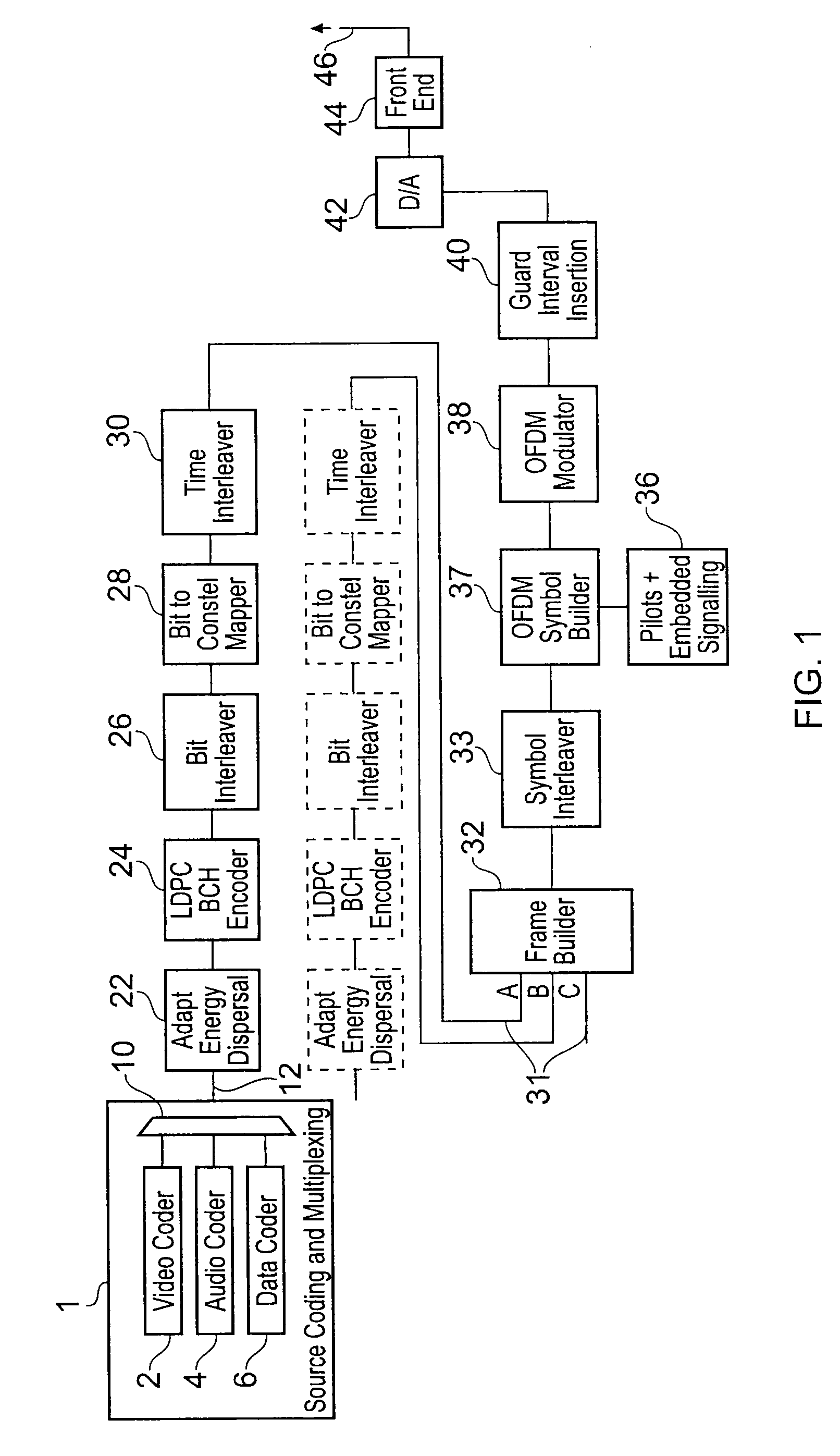

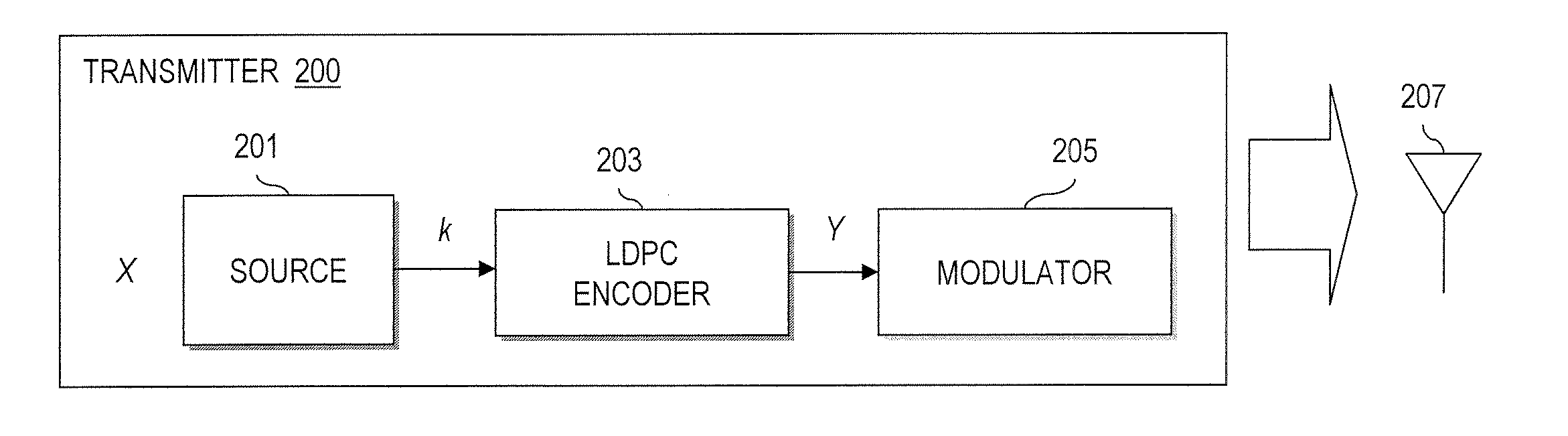

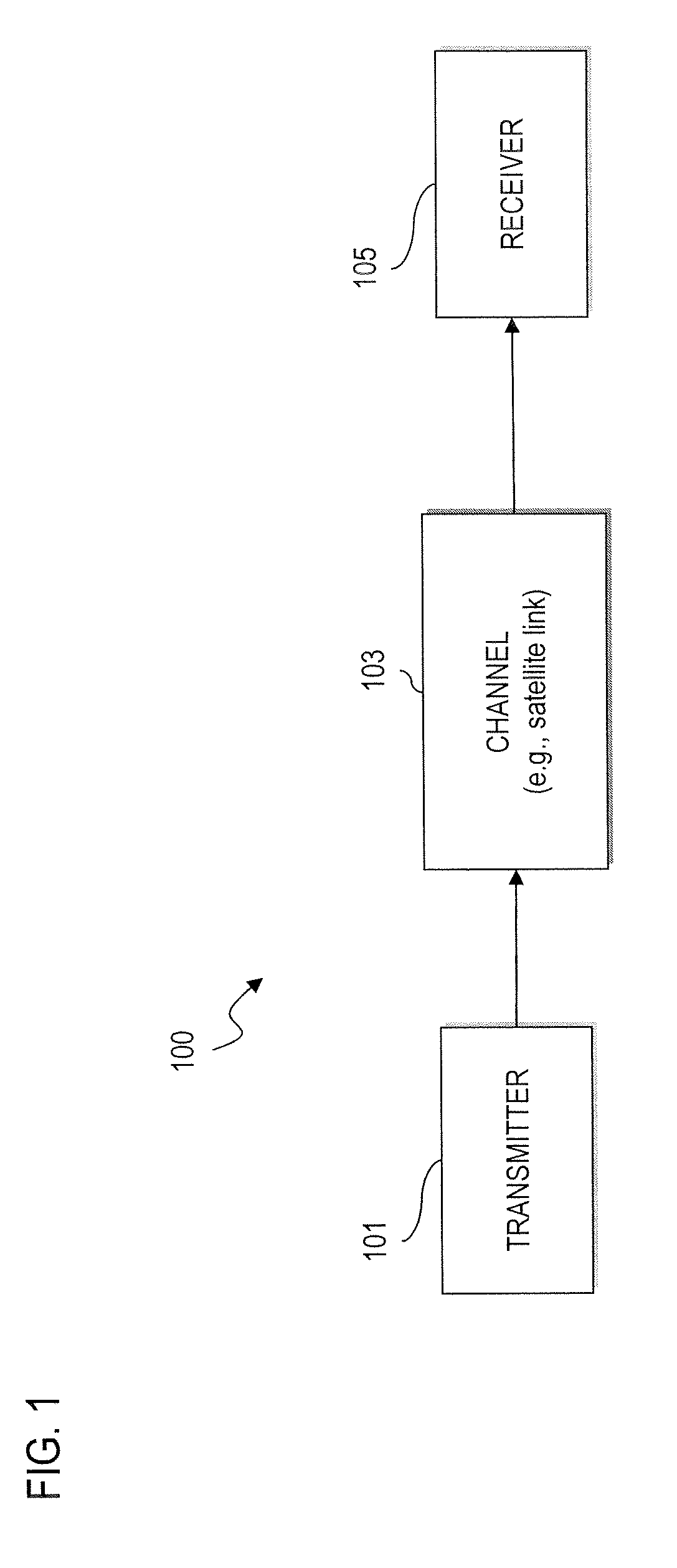

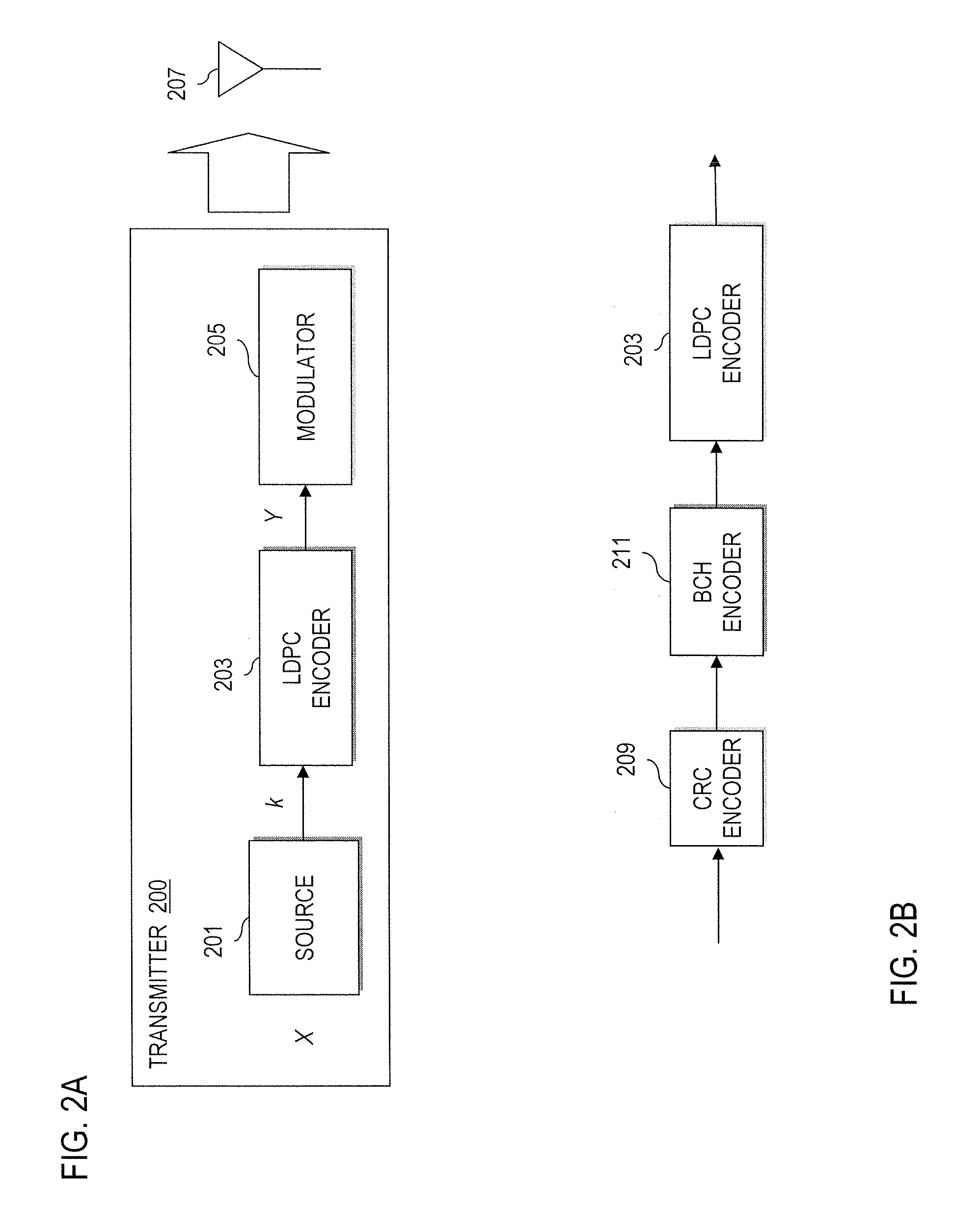

Method and system for providing long and short block length low density parity check (LDPC) codes

ActiveUS20050091570A1Minimizing storageMinimizing processing resourceError preventionCode conversionDigital videoLow density

An approach is provided for generating Low Density Parity Check (LDPC) codes. An LDPC encoder generates a LDPC code with an outer Bose Chaudhuri Hocquenghem (BCH) code. For ⅓ rate, the relevant parameters are as follows: q=120, nldpc=64,800, kldpc=nBCH=21600, kBCH=21408 (12 bit error correcting BCH). For ¼ rate, the LDPC code has the following relevant parameters: q=135, nldpc=64,800, kldpc=nBCH=16200, kBCH=16008 (12 bit error correcting BCH). For ⅖ rate, the following parameters exist: q=108, nldpc=64800, kldpc=nBCH=25920, kBCH=25728 (12 bit error correcting BCH). The above approach has particular application in digital video broadcast services over satellite.

Owner:DTVG LICENSING INC

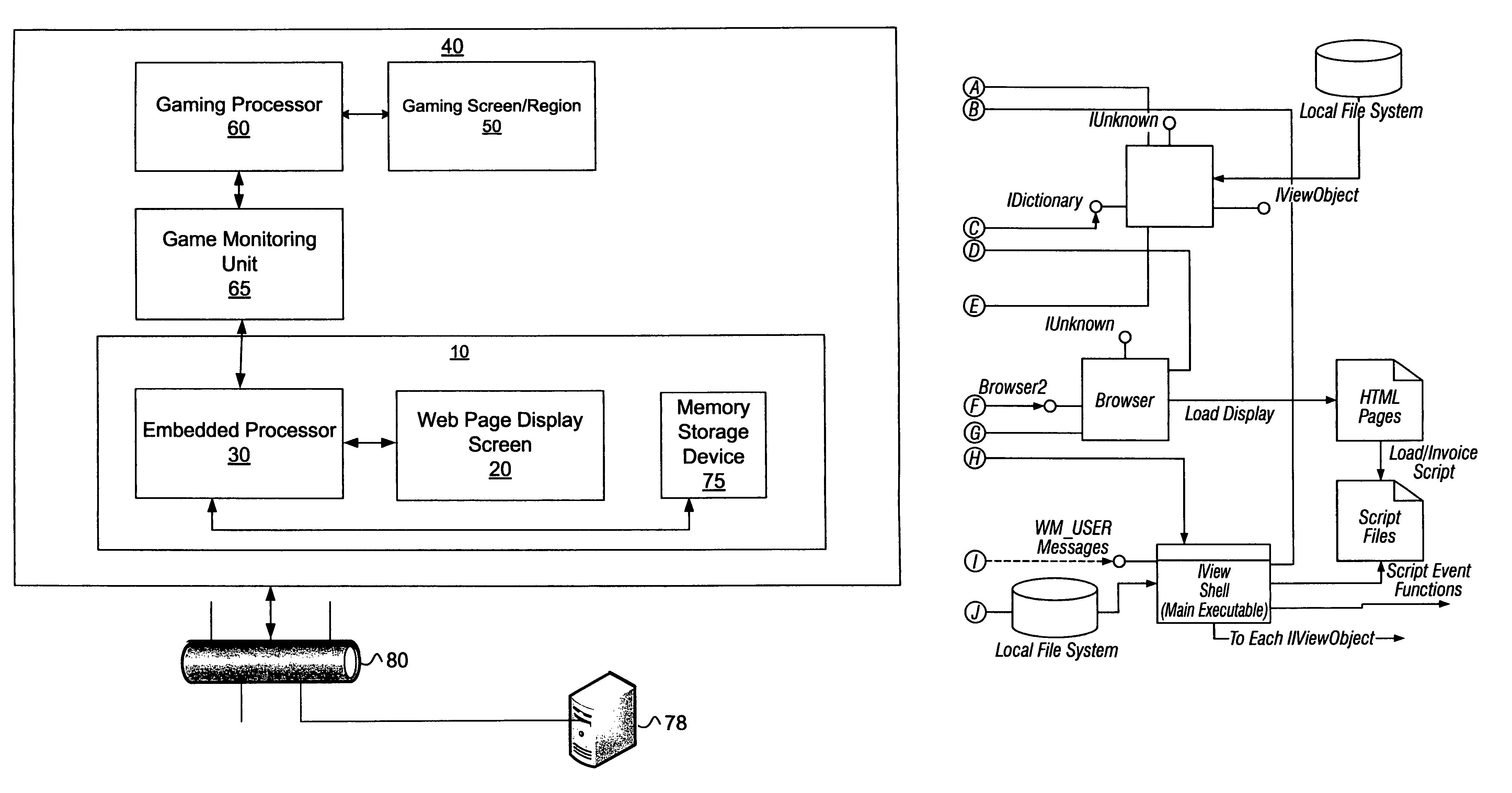

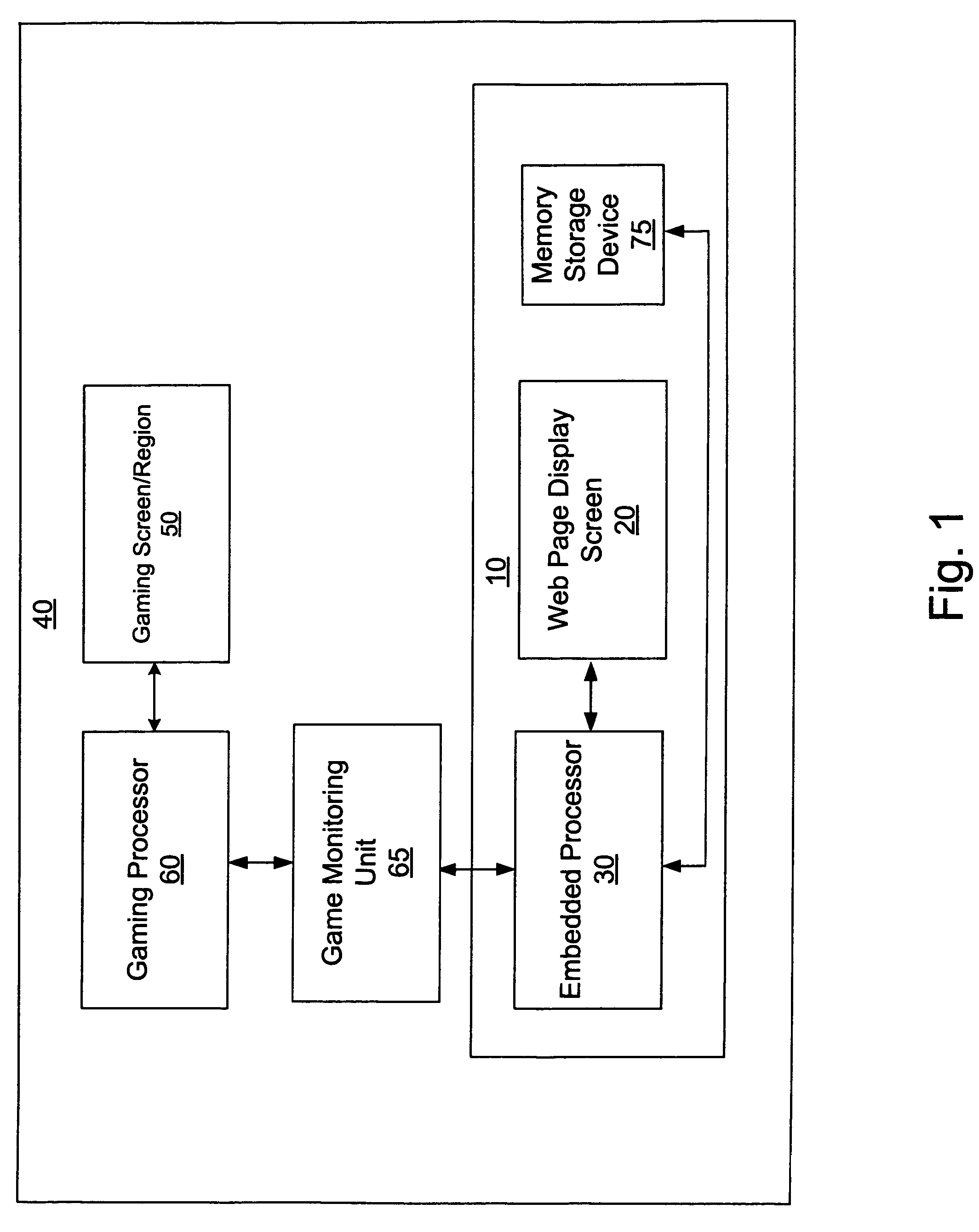

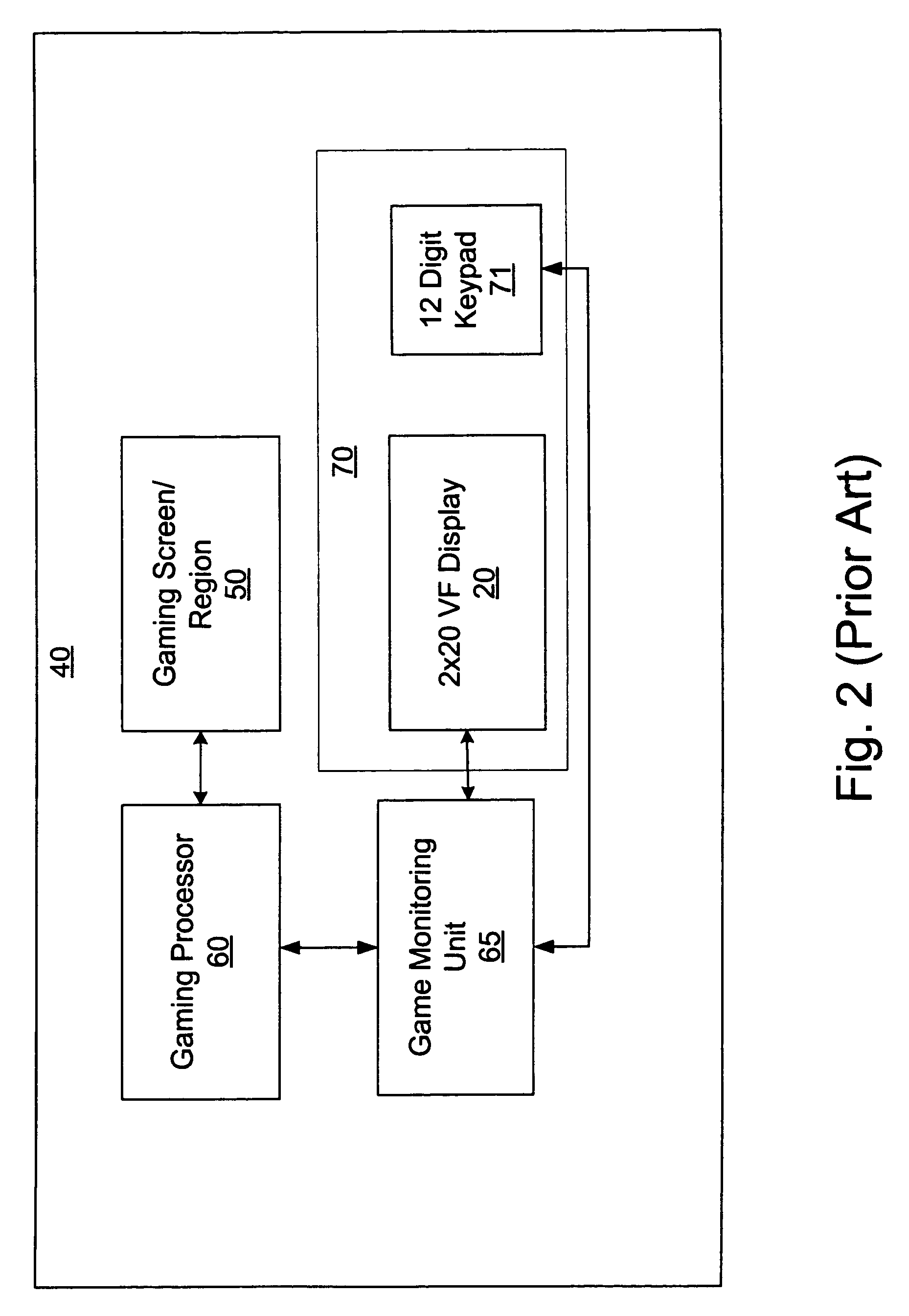

User interface system and method for a gaming machine

InactiveUS7950999B2Increase excitementRicher gaming experienceApparatus for meter-controlled dispensingVideo gamesDisplay deviceInternal os

Owner:BALLY GAMING INC

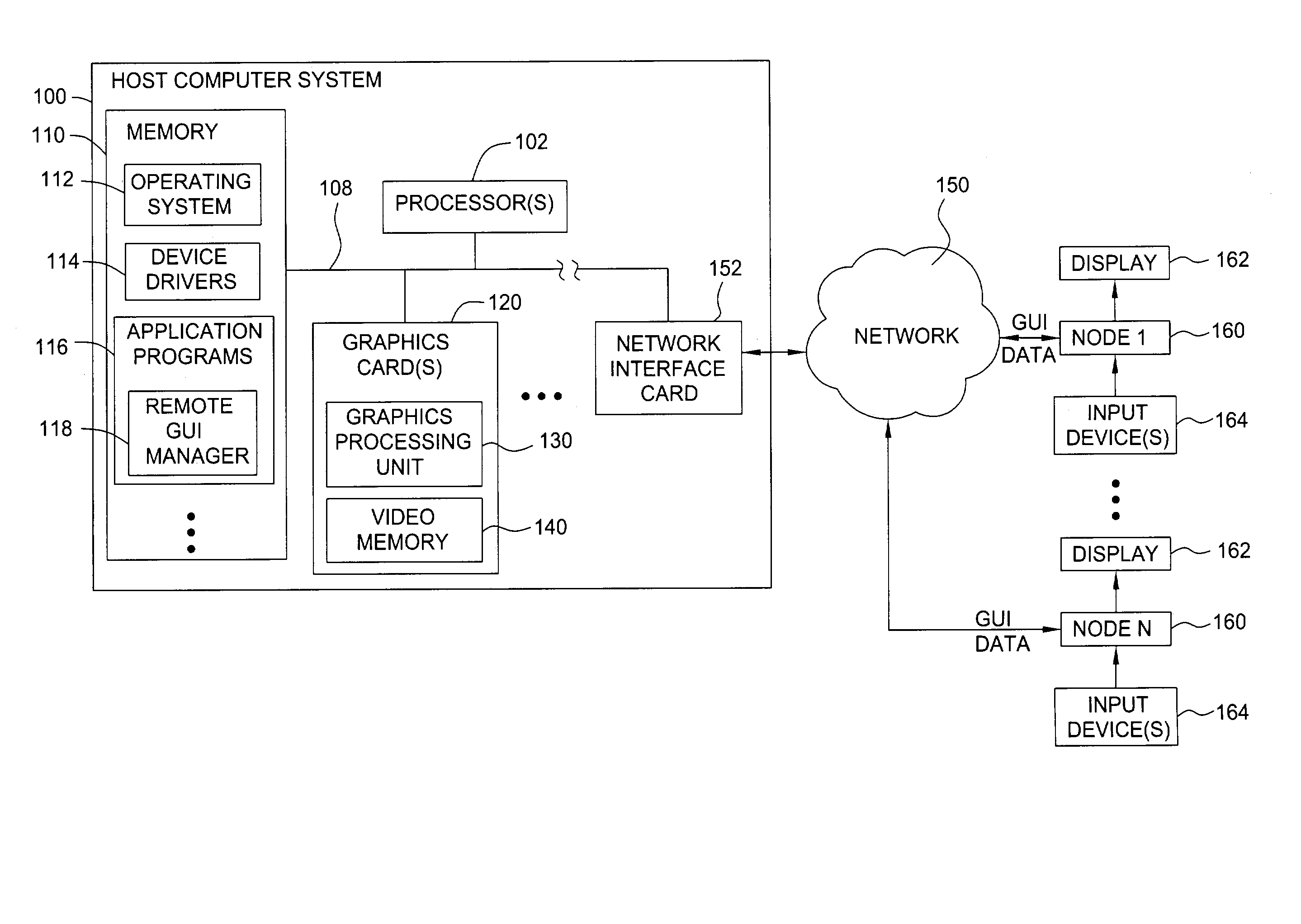

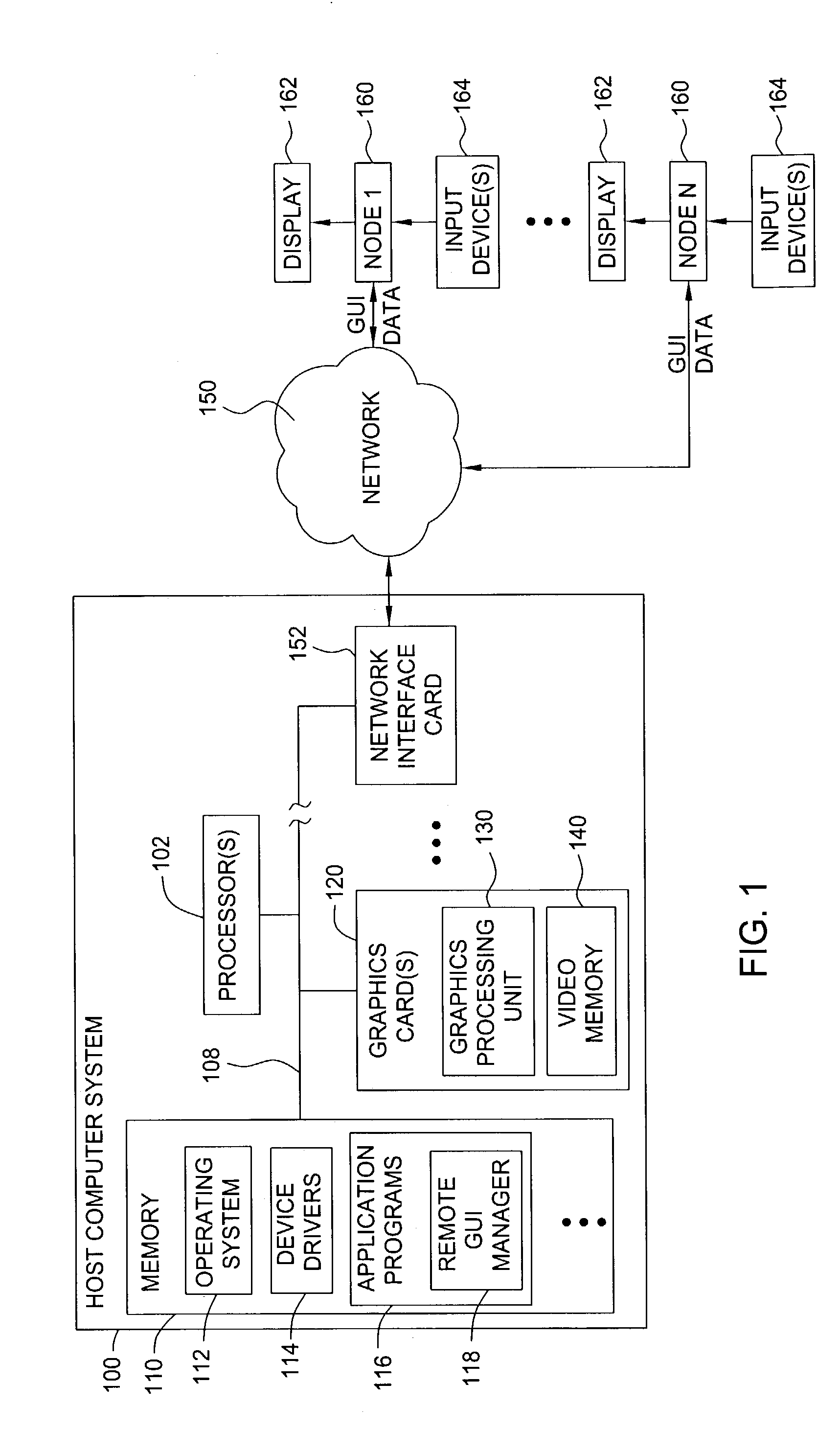

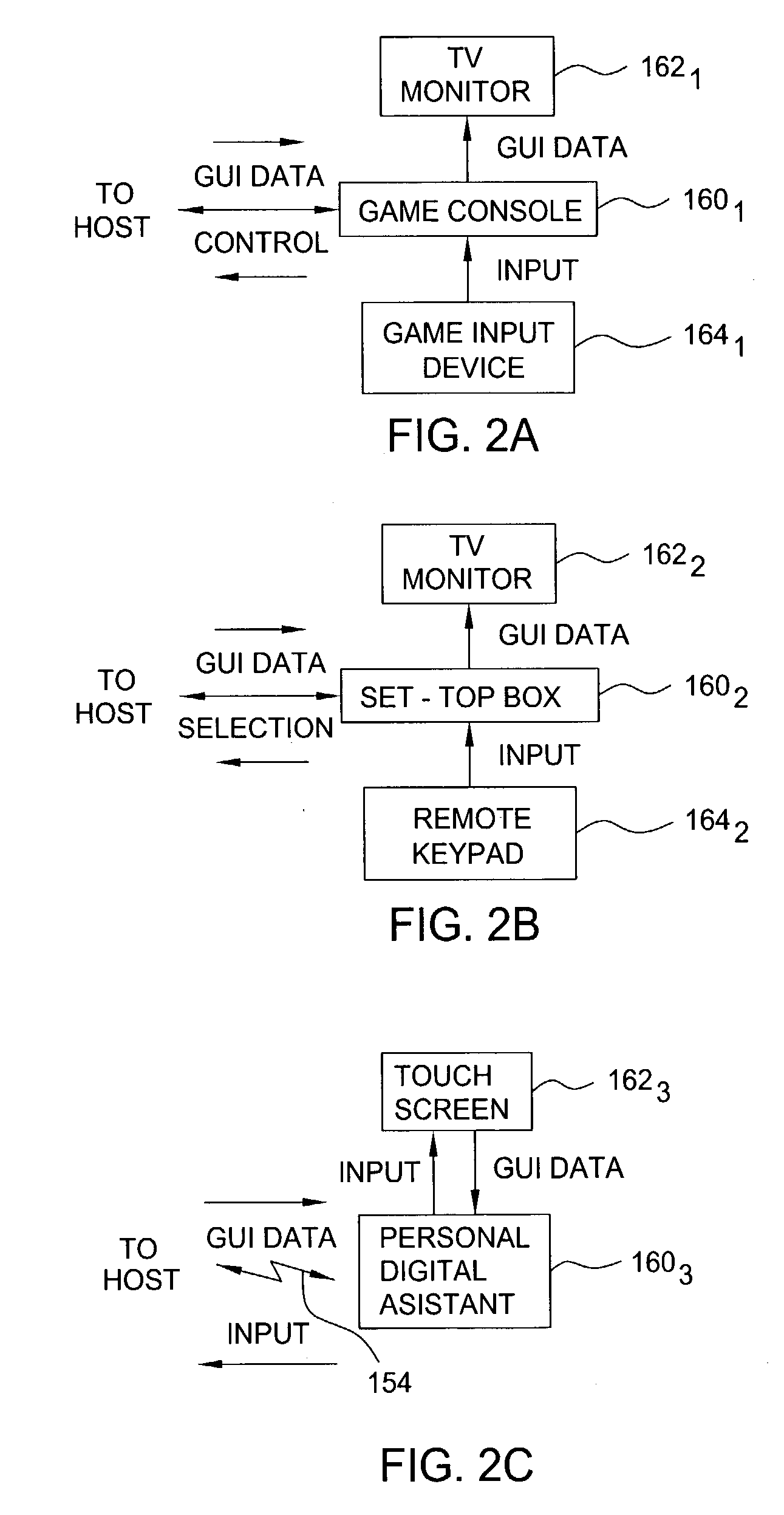

Remote graphical user interface support using a graphics processing unit

ActiveUS7173635B2Few data bitCathode-ray tube indicatorsMultiple digital computer combinationsGraphics24-bit

Methods, apparatus and systems for the display, on a remote node, of a three-dimensional (3D) image rendered on a host system in a first image format are described. In general, the 3D image is transformed into a second image format that is compressed (i.e., uses fewer data bits per pixel) relative to the first image format, (optionally) scaled to a screen size of remote node, and subsequently transferred to remote node for display. In instances, the transformation of the image from the first image format to the second image format and the optional scaling of the image to the screen size of remote node may be done in a graphics processing unit (GPU) on the host system. As an example, the first image format may be an RGB-based format, such as RGBA (32-bits per pixel) or standard RGB (24-bits per pixel) and the second image format may be a YUV-based format, such as YV12 (12-bits per pixel).

Owner:NVIDIA CORP

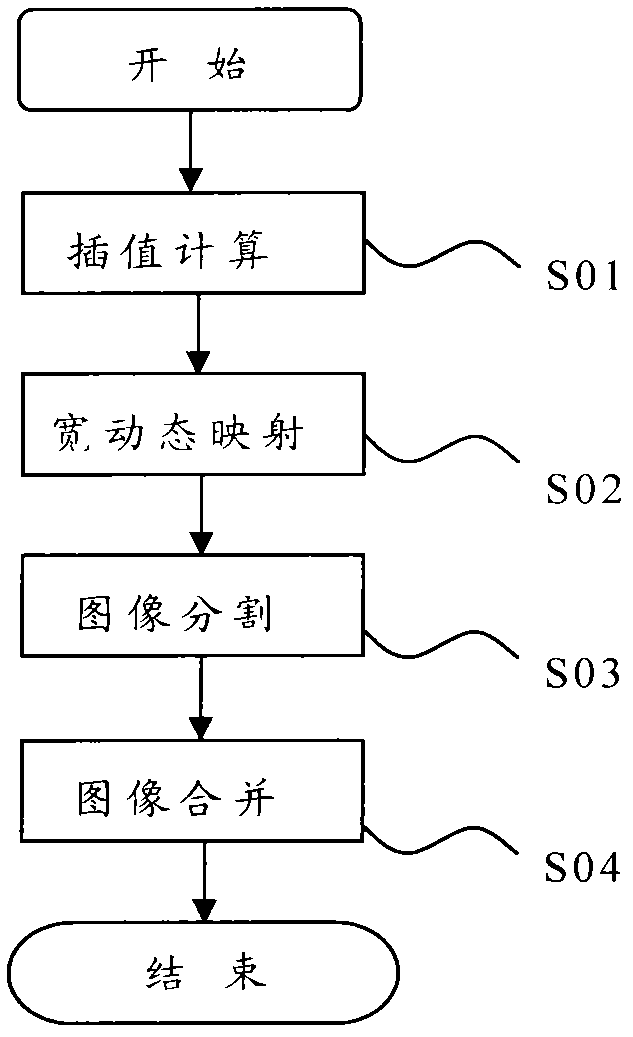

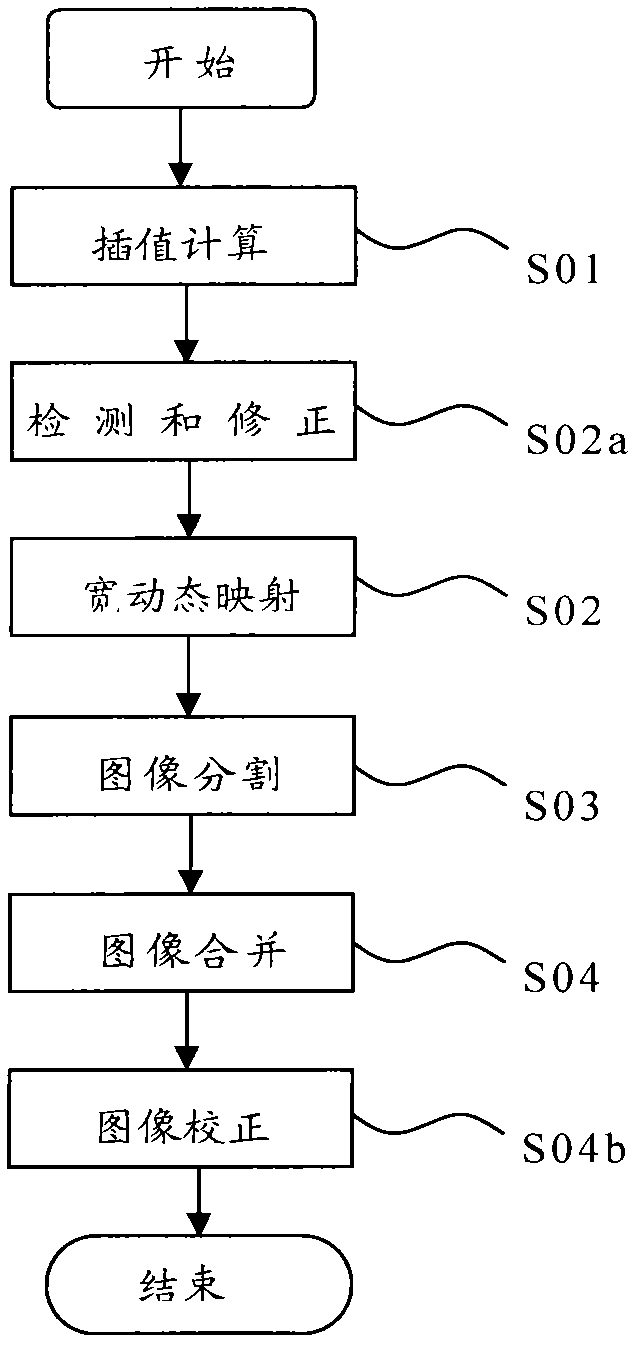

Wide dynamic processing method for single-frame double-exposure image

ActiveCN102075688AQuality improvementSmall amount of calculationTelevision system detailsColor television detailsImaging qualityImage segmentation

The invention discloses a wide dynamic processing method for a single-frame double-exposure image. The single-frame double-exposure image is a 12-bit original image comprising long exposure pixel blocks and short exposure pixel blocks simultaneously, and the method comprises the following steps of: (1) performing interpolation calculation, namely completing values of three channels of red, green and blue (RGB) for each pixel; (2) performing wide dynamic mapping, namely mapping and compressing the interpolated image; (3) segmenting image subjected to wide dynamic mapping to obtain two images only with the long exposure pixels and the short exposure pixels respectively; and (4) combining the two images by using a brightness distribution histogram interval segmenting method. Through the wide dynamic processing method for the single-frame double-exposure image, the pixels in two exposure modes in the single-frame image are combined, so that each part is subjected to proper exposure. Moreover, the single-frame image is only needed to be processed, the calculated quantity is reduced, and the wide dynamic image quality is improved through detection and correction of dead pixels and correction of the image.

Owner:QINGDAO HISENSE TRANS TECH

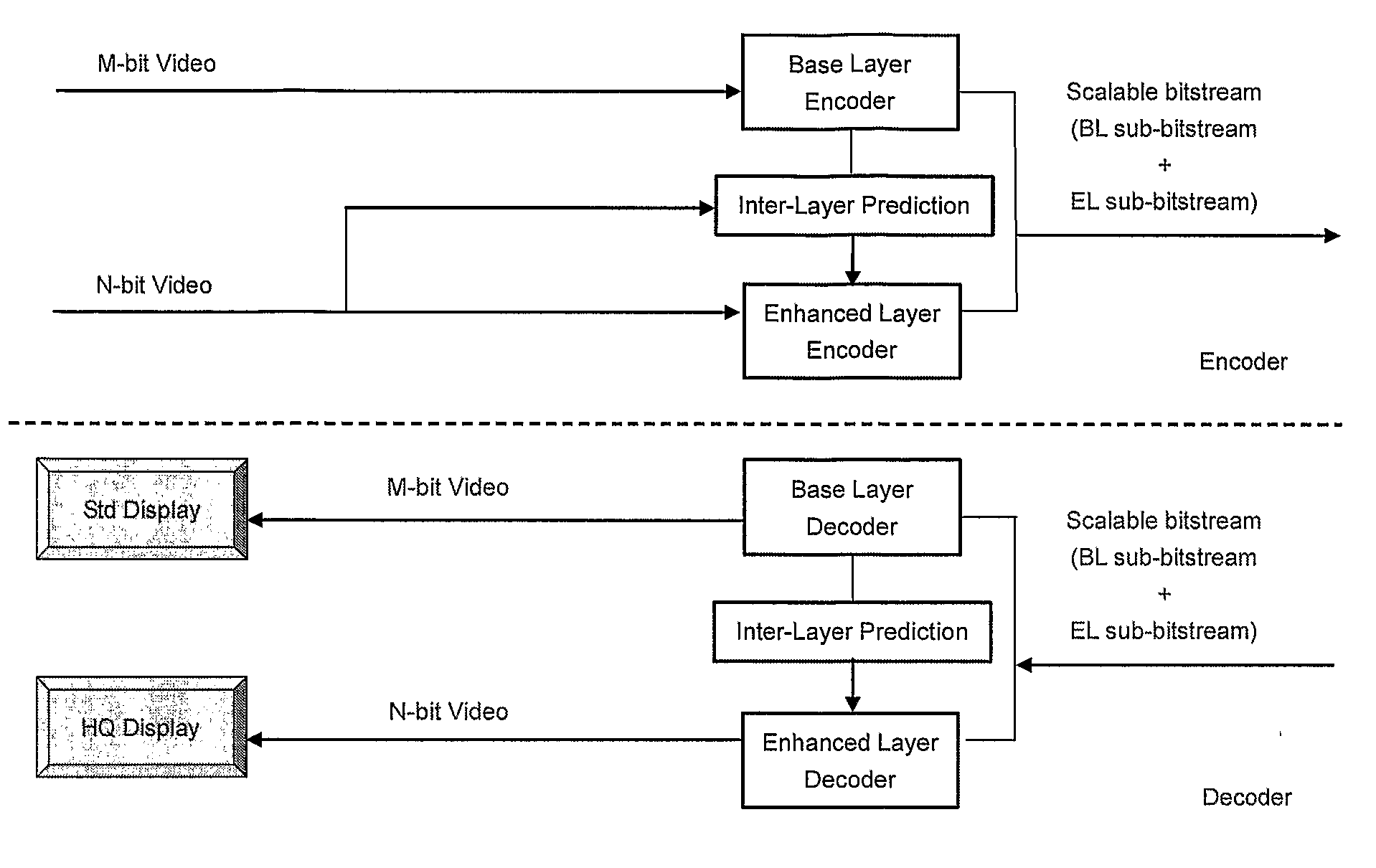

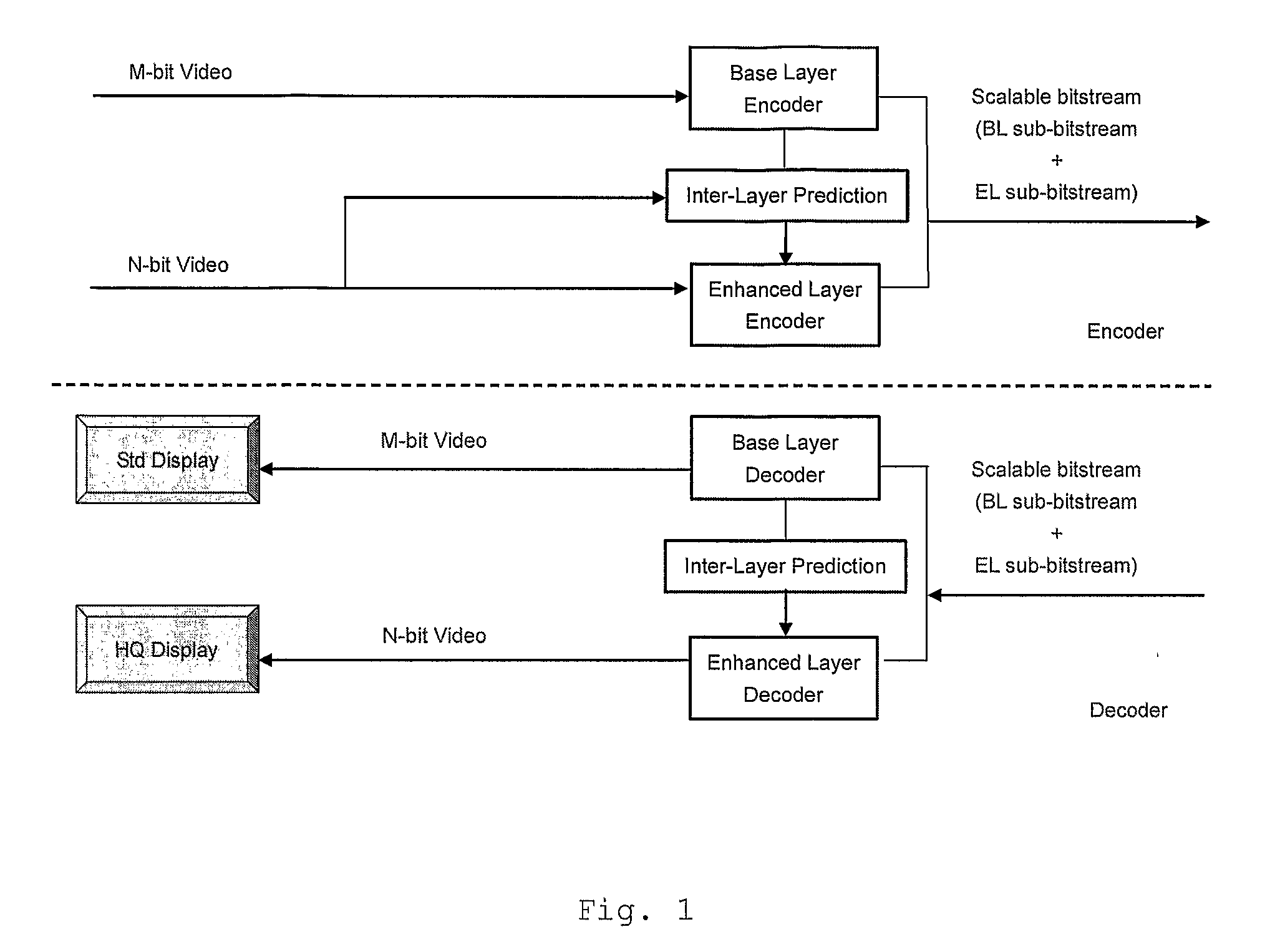

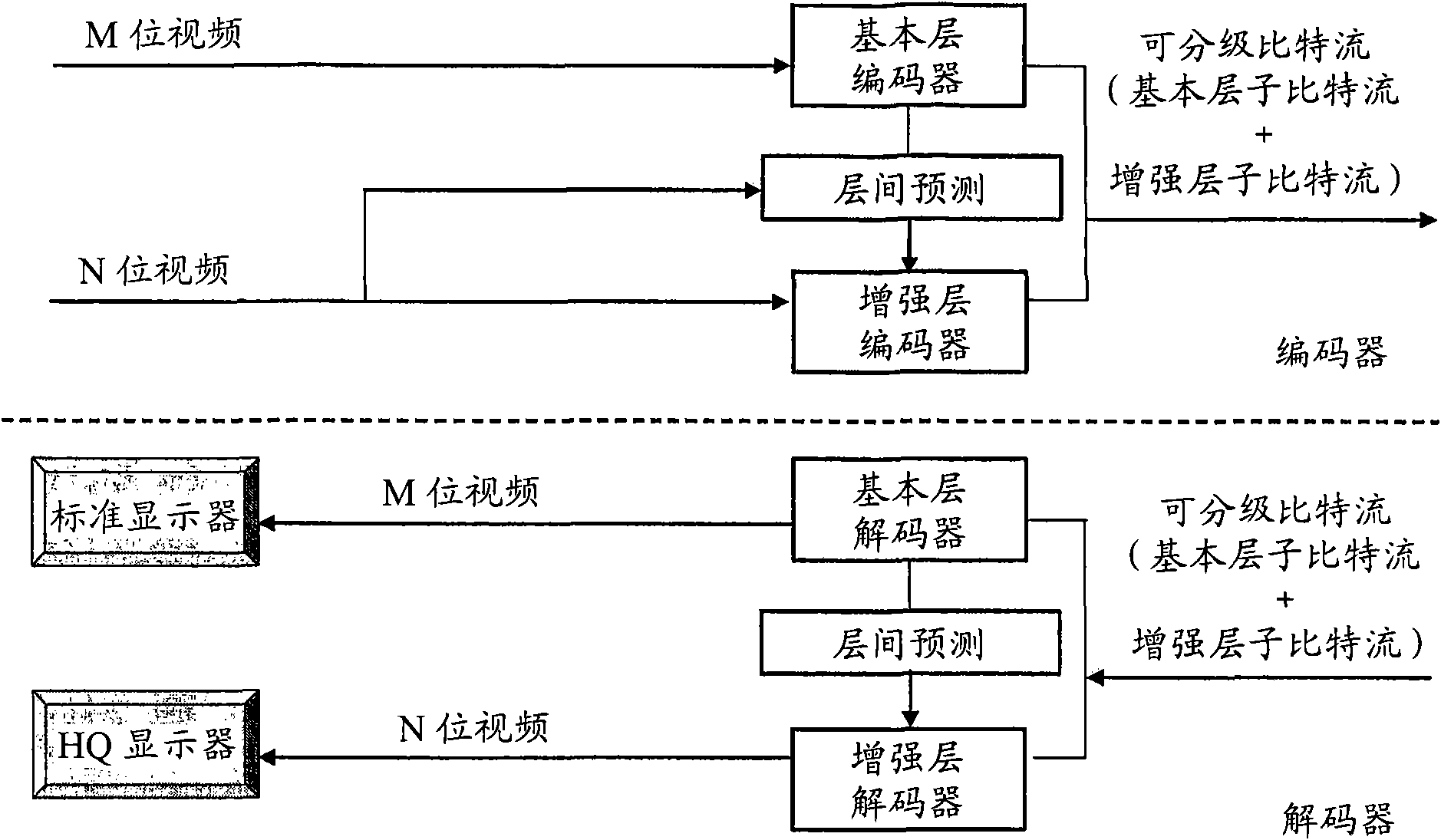

Video encoding method and video decoding method for enabling bit depth scalability

InactiveUS20100091840A1Quality improvementColor television with pulse code modulationColor television with bandwidth reductionVideo encodingDisplay device

The invention presents a scalable solution to encode the whole 12-bit raw video once to generate one bitstream that contains an H.264 / AVC compatible base layer and a scalable enhancement layer. If a color bit depth scalable decoder is available at the client end, both the base layer and the enhancement layer sub-bitstreams will be decoded to obtain the 12-bit video and it can be viewed on a high quality display that supports more than eight bit; otherwise only the base layer sub-bitstream is decoded using an H.264 / AVC decoder and the decoded 8-bit video can be viewed on a conventional 8-bit display. The enhancement layer contains a residual based on a prediction from the base layer, which is either based on bit-shift or based on an advanced bit depth prediction is utilized, wherein the advanced bit depth prediction method is a Smoothed Histogram method or a Localized Polynomial Approximation method.

Owner:THOMSON LICENSING SA

Video encoding method and video decoding method for enabling bit depth scalability

InactiveCN101622878APulse modulation television signal transmissionDigital video signal modificationVideo encodingDisplay device

The invention presents a scalable solution to encode the whole 12-bit raw video once to generate one bitstream that contains an H.264 / AVC compatible base layer and a scalable enhancement layer. If a color bit depth scalable decoder is available at the client end, both the base layer and the enhancement layer sub-bitstreams will be decoded to obtain the 12-bit video and it can be viewed on a high quality display that supports more than eight bit; otherwise only the base layer sub-bitstream is decoded using an H.264 / AVC decoder and the decoded 8-bit video can be viewed on a conventional 8-bit display. The enhancement layer contains a residual based on a prediction from the base layer, which is either based on bit-shift or based on an advanced bit depth prediction is utilized, wherein the advanced bit depth prediction method is a Smoothed Histogram method or a Localized Polynomial Approximation method.

Owner:INTERDIGITAL VC HLDG INC

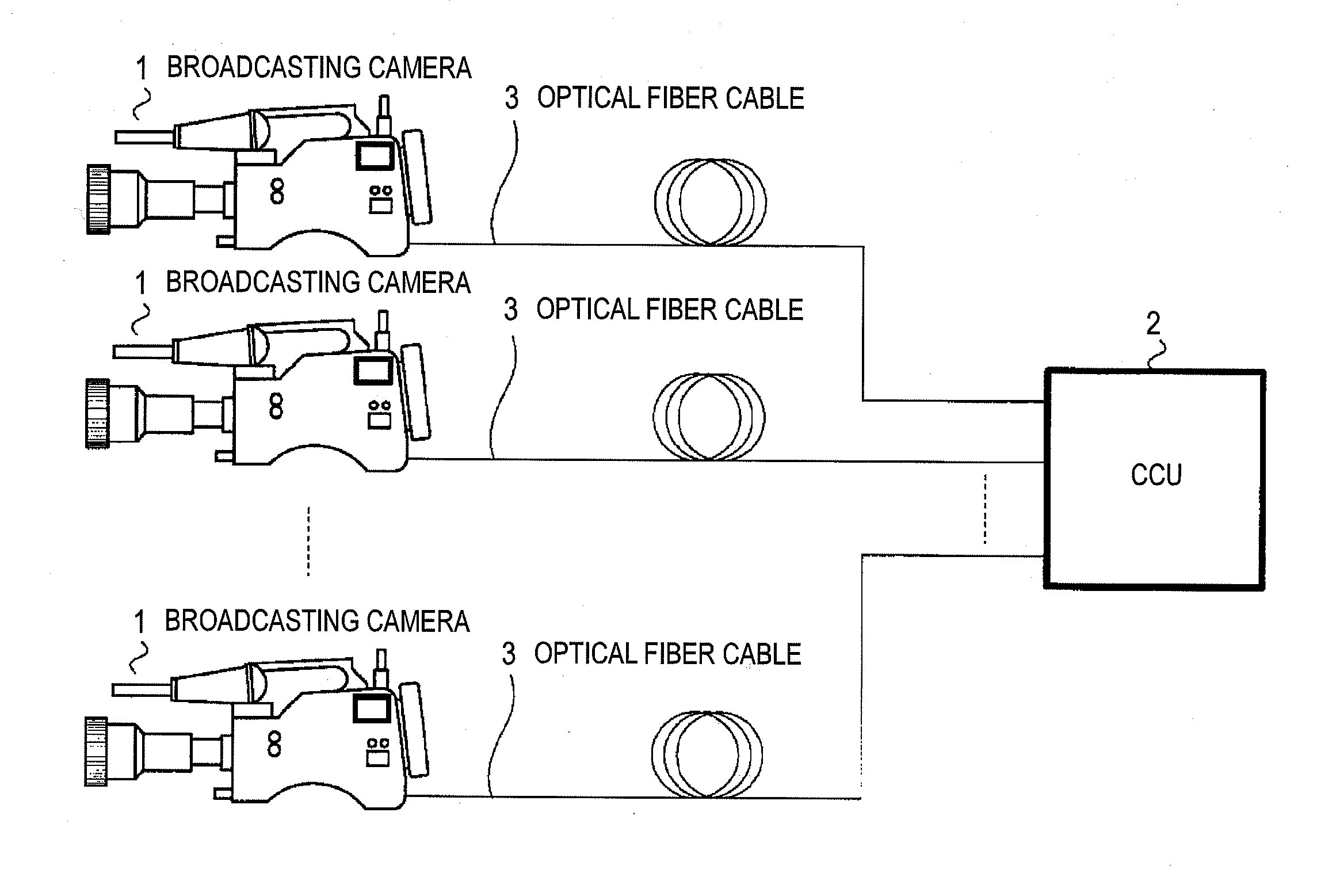

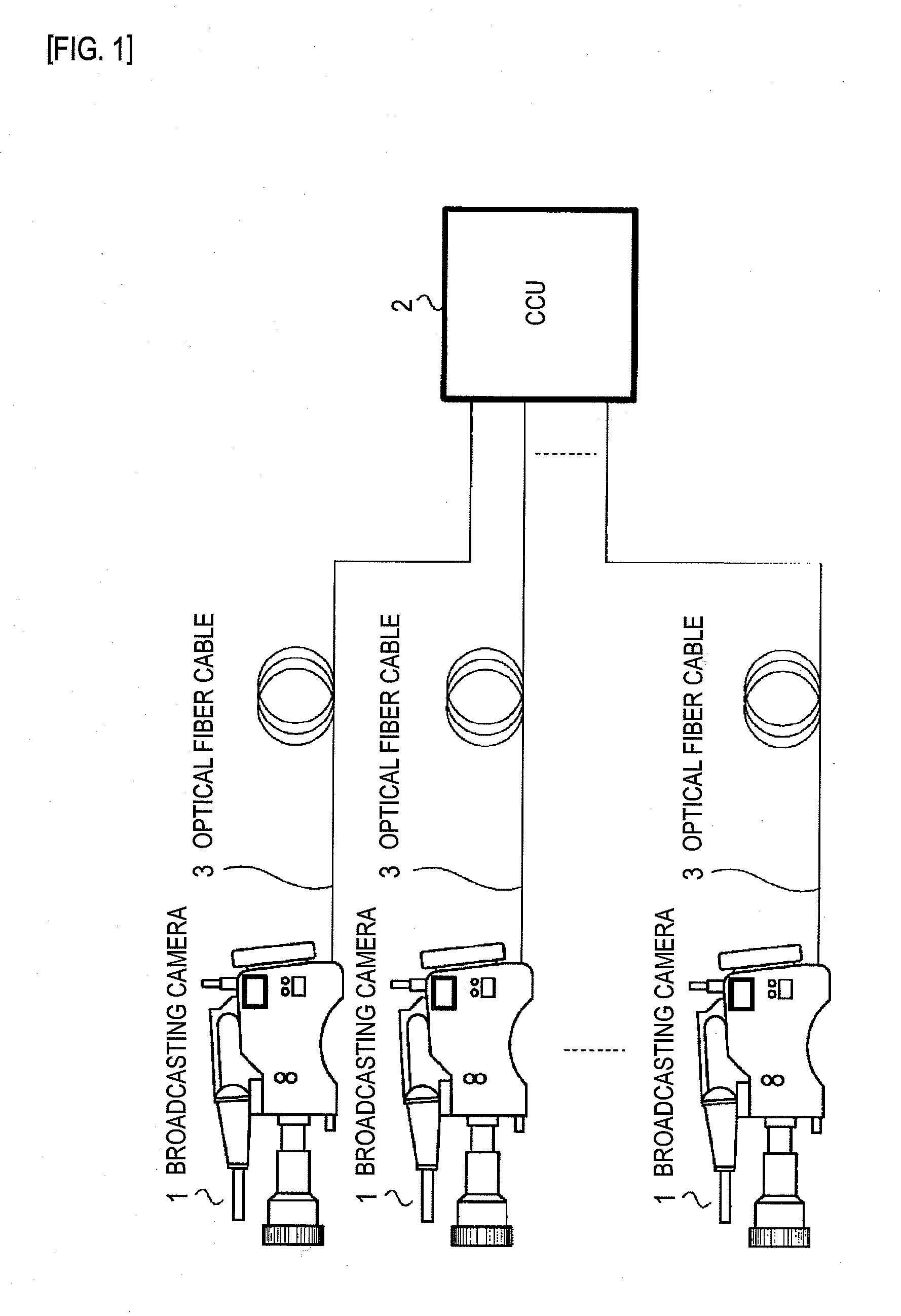

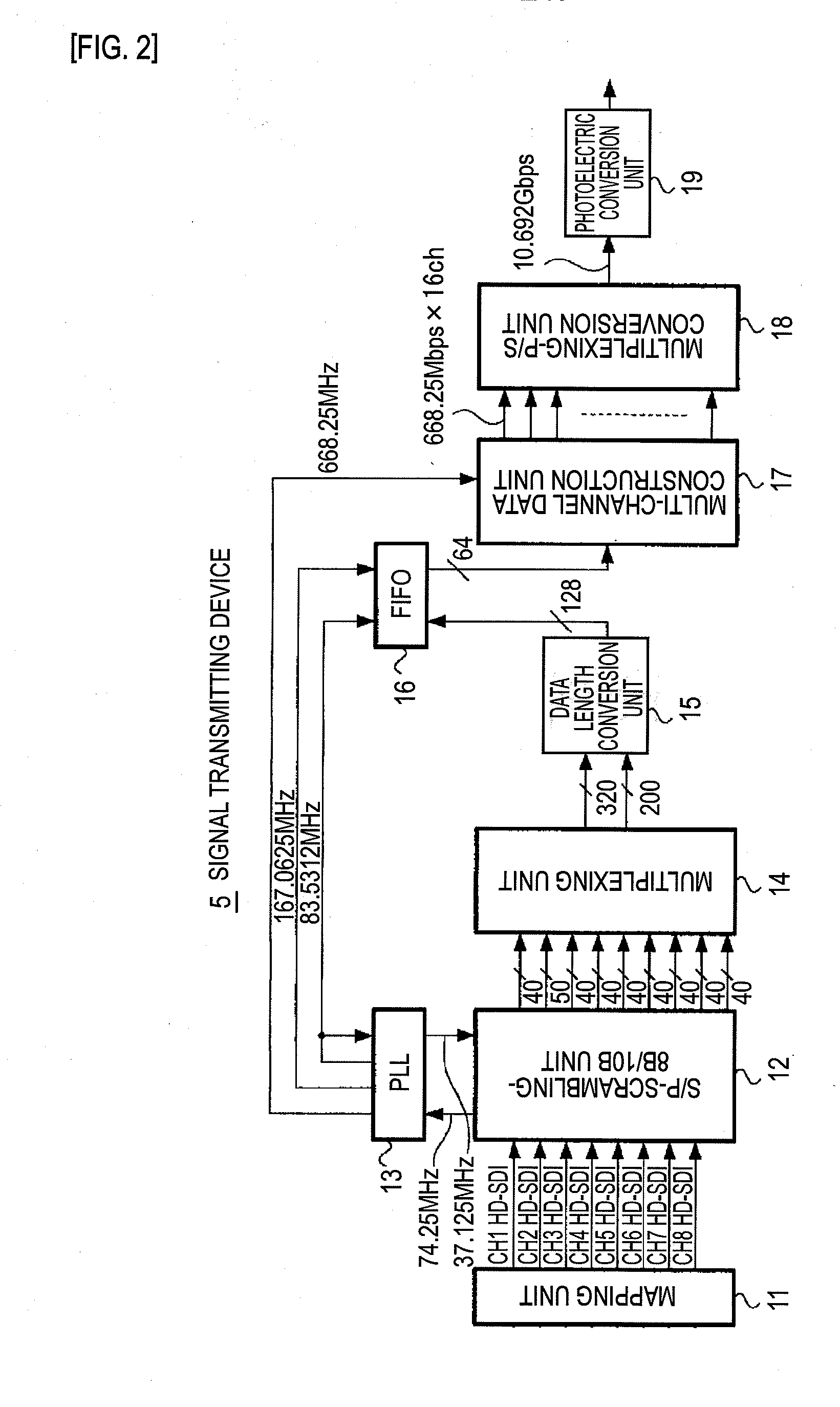

Signal transmitting device, signal transmitting method, signal receiving device, and signal receiving method

ActiveUS20100149412A1Accurately reproduce original dataTelevision system detailsPicture reproducers using cathode ray tubesDigital data12-bit

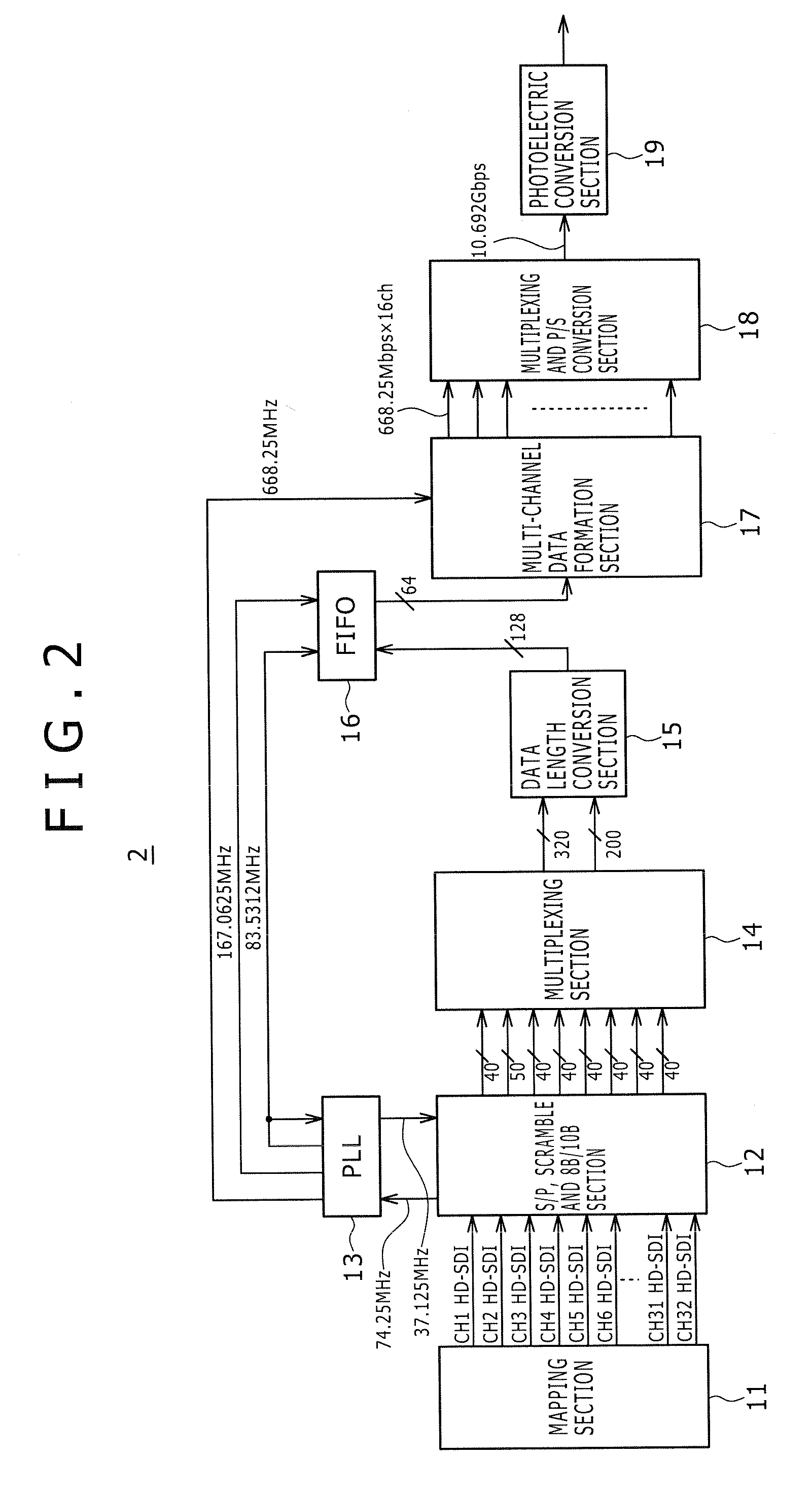

For example, samples included in a frame constituted by a 3840×2160 / 24P,25P,30P / 4:4:4,4:2:2,4:2:0 / 10,12-bit signal are mapped into first to fourth sub-images specified in the HD-SDI format, in units of two adjoining samples. Thus, it is possible to transmit through a transmission constitution for the HD-SDI format. The signal can be converted into serial digital data permitting a bit rate of 10.692 Gbps or the like and transmitted, and the receiving side can accurately reproduce original data.

Owner:SONY CORP

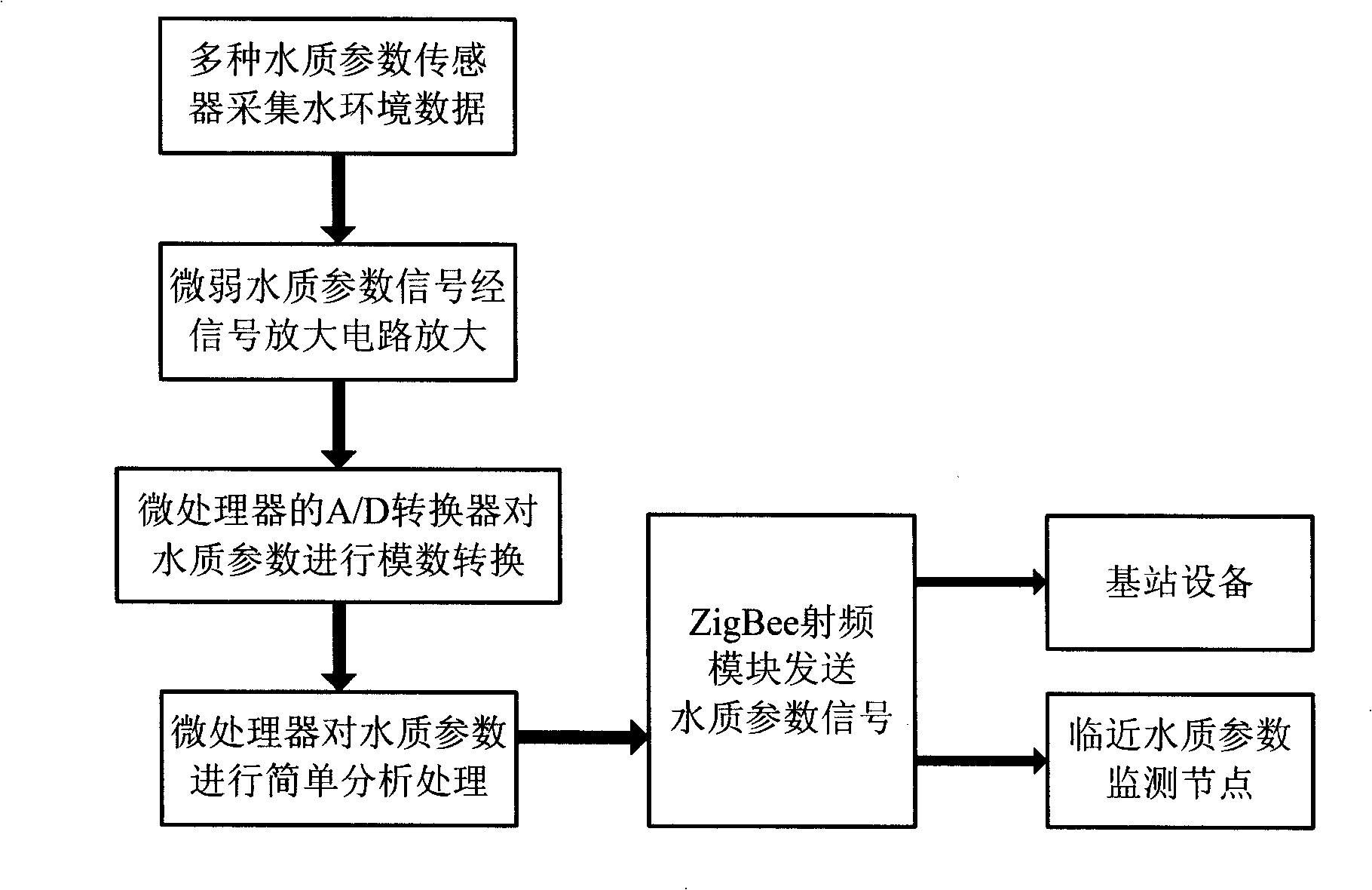

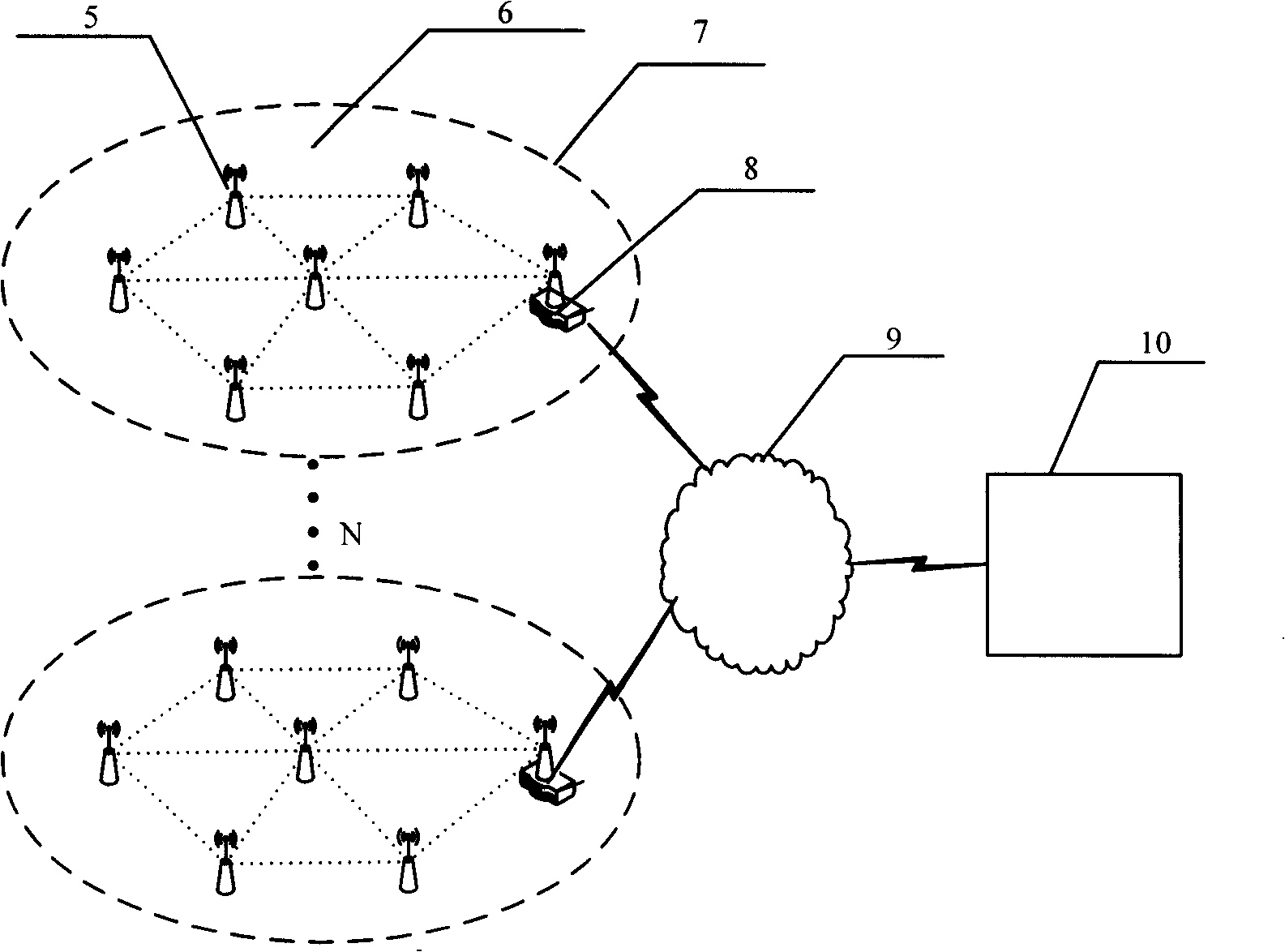

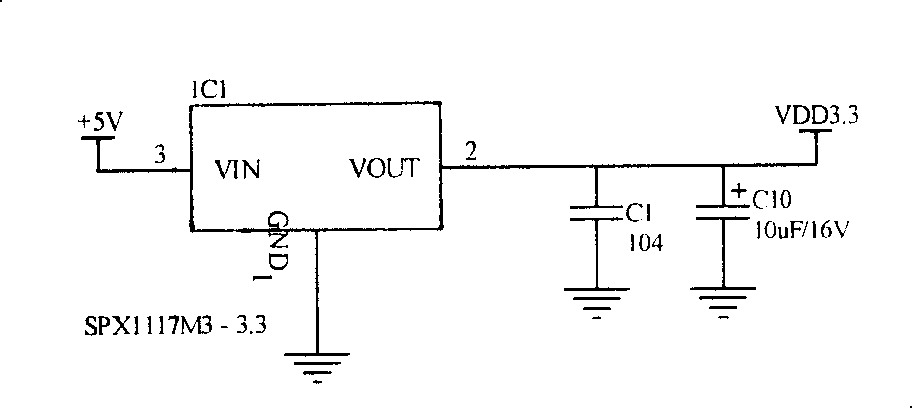

Water environment monitoring node based on ZigBee wireless technique

ActiveCN101281187ALow costReduce power consumptionEnergy efficient ICTNear-field transmissionSupply managementWater quality

The invention relates to a water environment monitoring node based on ZigBee wireless technique. The prior technology has long monitoring period and large work intensity, and cannot reflect dynamic variation of water environment. The invention includes an electric power management module, a water quality parameter acquisition module, an MPU module and a ZigBee radio frequency module. The equipment adopts an MSP430F149 MPU, for analyzing and processing water environmental parameter, and controls the operating status of the ZigBee radio frequency module and the water quality parameter acquisition module. The MSP430F149 processor is interconnected to the water quality parameter acquisition module through a 12 bit A / D converter self integrated with the MSP430F149 processor, and is interconnected to the ZigBee radio frequency module through an SPI serial interface, meanwhile also controls a power supply management module to supply power through an analogue switch, so as to achieve the goal of energy-saving. The invention has low cost, and low power consumption; can be arranged in water environment for a long term, execute multiple parameter real time monitoring to the water environment, and complete the high-efficiency transmission of data, thereby having wide applications prospect in the water environment monitoring.

Owner:JIANGSU SHENXIANG ELECTROMECHANICAL

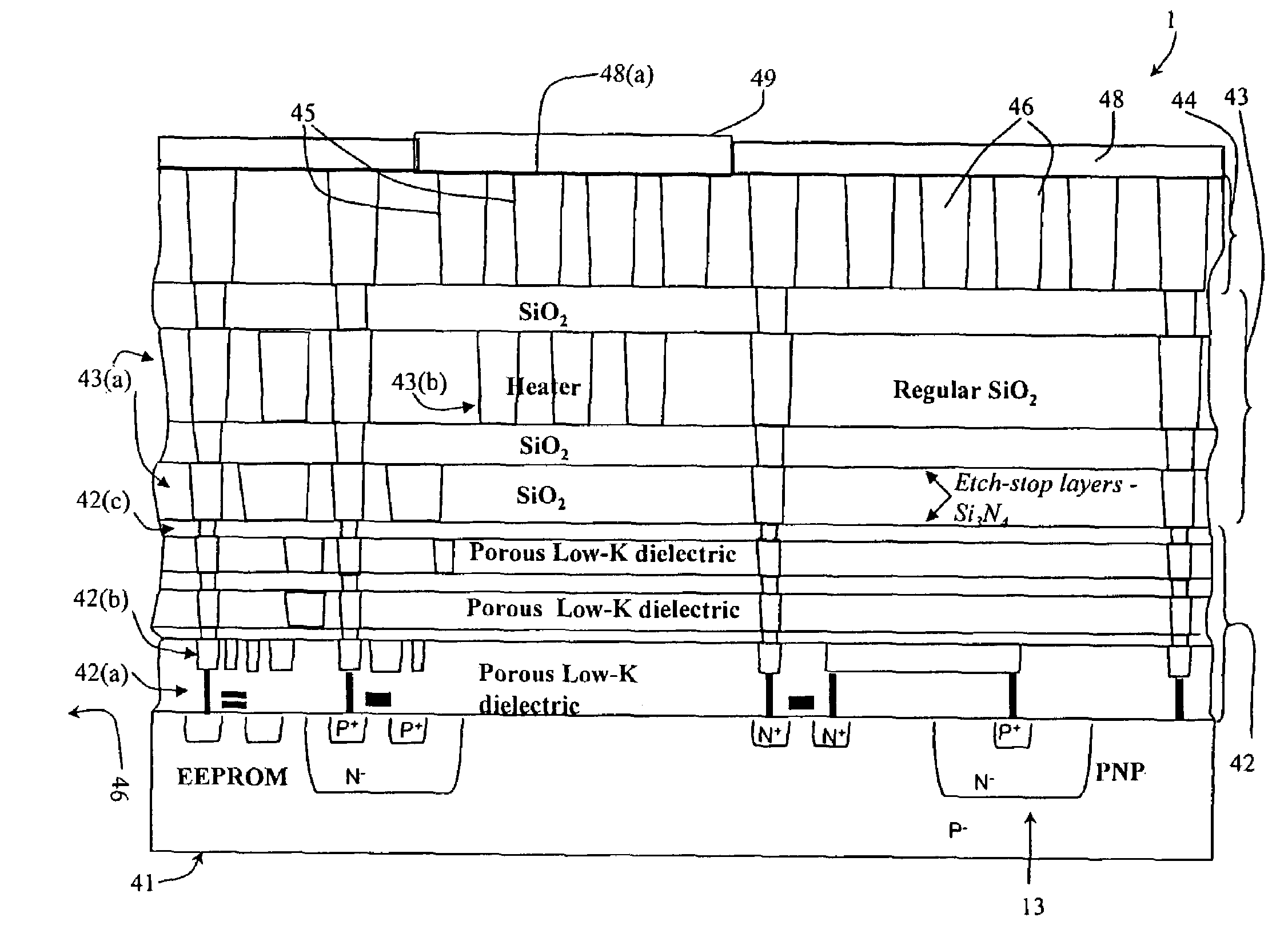

Integrated CMOS porous sensor

ActiveUS7554134B2Increase productionTransistorSemiconductor/solid-state device details18-bitMicrocontroller

A single chip wireless sensor (1) comprises a microcontroller (2) connected by a transmit / receive interface (3) to a wireless antenna (4). The microcontroller (2) is also connected to an 8 kB RAM (5), a USB interface (6), an RS232 interface (8), 64 kB flash memory (9), and a 32 kHz crystal (10). The device (1) senses humidity and temperature, and a humidity sensor (11) is connected by an 18 bit ΣΔ A-to-D converter (12) to the microcontroller (2) and a temperature sensor (13) is connected by a 12 bit SAR A-to-D converter (14) to the microcontroller (2). The device (1) is an integrated chip manufactured in a single process in which both the electronics and sensor components are manufactured using standard CMOS processing techniques, applied to achieve both electronic and sensing components in an integrated process.

Owner:SILICON LAB INC

Multimedia broadcast and multicast service paging

ActiveUS7242919B2WasteLow efficiencySpecial service provision for substationSpatial transmit diversityCommunications systemAir interface

This invention provides a paging method for Multimedia Broadcast / Multicast Service in mobile communication system. The paging process and radio resource setup process are merged in this method to try to reduce uplink responses. This invention extends existing PCH IubFP frame structure by adding MBMS Indication bit(MI) to PCH IubFP frame. The PCH IubFP frame includes Paging Indication (PI) and Paging Message. Paging message carries MBMS service information. MBMS Service Identity or MBMS Paging Indicator is added to the reserved 12 bits in Paging Indicator Channel (PICH) frame structure. Radio Network Controller (RNC) transfers Paging Indicator Message and paging message to Base Station (Node B) so as to send over the air-interface.

Owner:SAMSUNG ELECTRONICS CO LTD +1

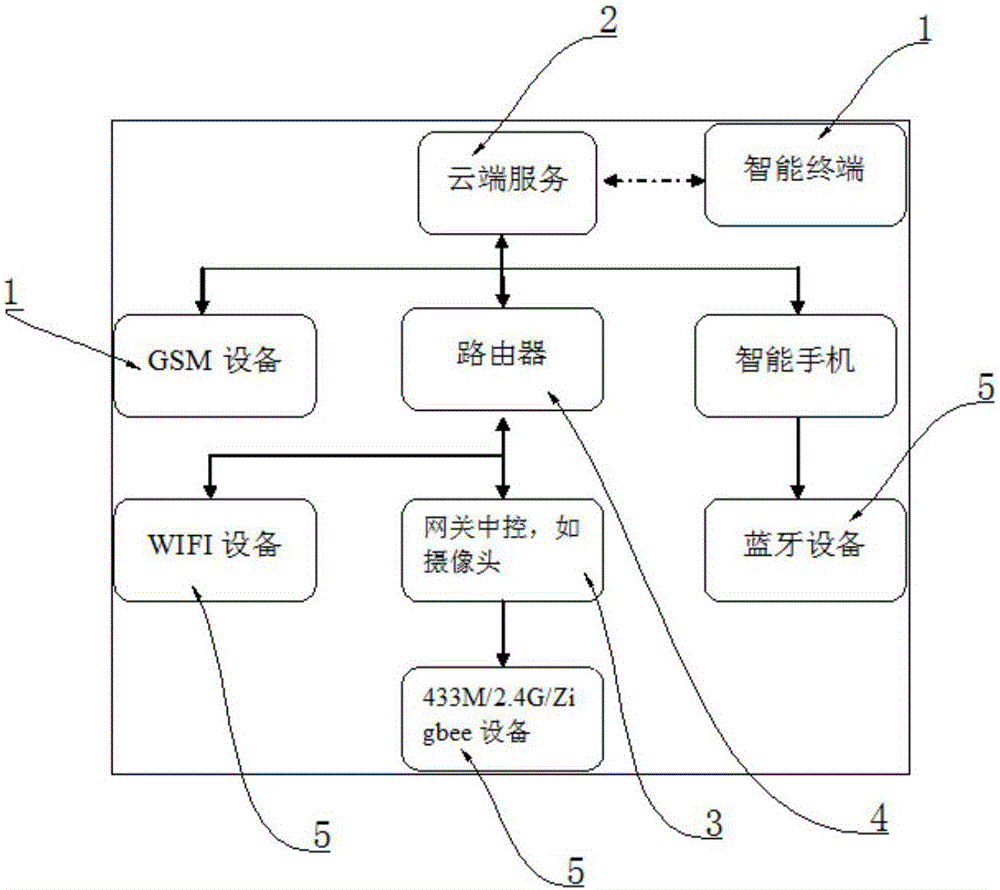

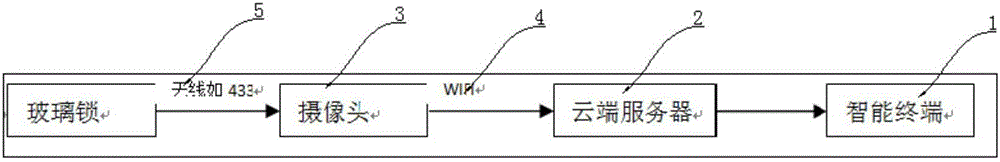

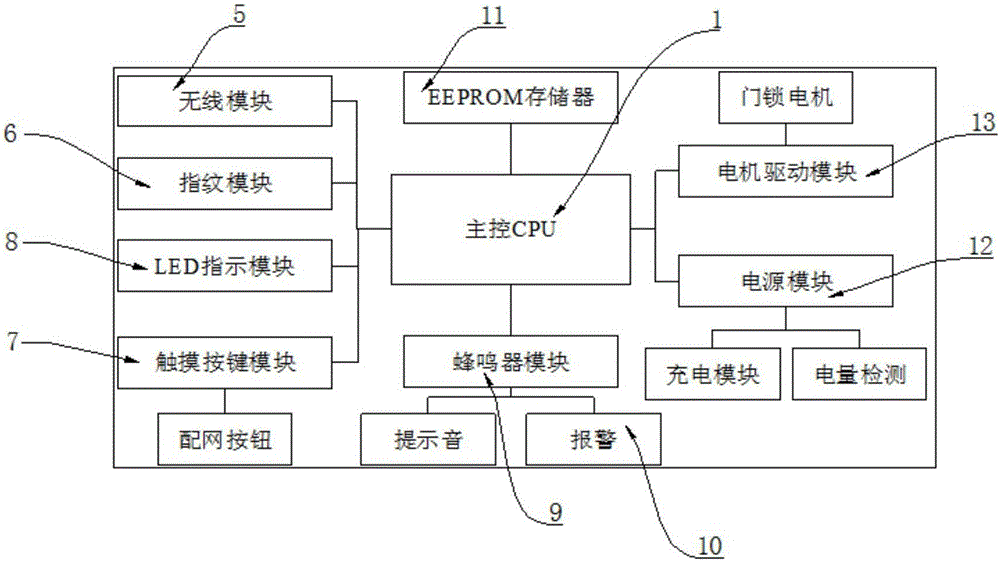

Wireless lock control system based on intelligent terminal and method

InactiveCN106600757AWith on-site alarm functionWith remote alarm functionIndividual entry/exit registersTransmissionKey pressing32-bit

The invention provides a wireless lock control system of an electronic lock based on an intelligent terminal and a method, the wireless lock control system is used in a U type glass door lock / bicycle lock, the wireless lock control system comprises a main control CPU, a wireless module, a fingerprint module, a touch key module, a distribution network button, a LED display circuit, a buzzer module, an alarm circuit, an EEPROM memory, a power supply circuit module and a motor driver circuit module which are connected with the main control CPU, the power supply circuit module includes a rechargeable device; wireless transmission is encrypted by an AES encryption mode, the touch key module can add a 6 to 12 bit password, and a 32 bit virtual password is set; the fingerprint module adopts a semiconductor fingerprint sensor, and can add 100 pieces of user passwords, and a door can be opened by direct pressing of a user fingerprint; the electronic door lock is connected with the wireless main control CPU to realize the real-time monitoring and remote control of a door lock device so as to achieve full intelligent user experience.

Owner:SHENZHEN KAADAS INTELLIGENT TECH CO LTD

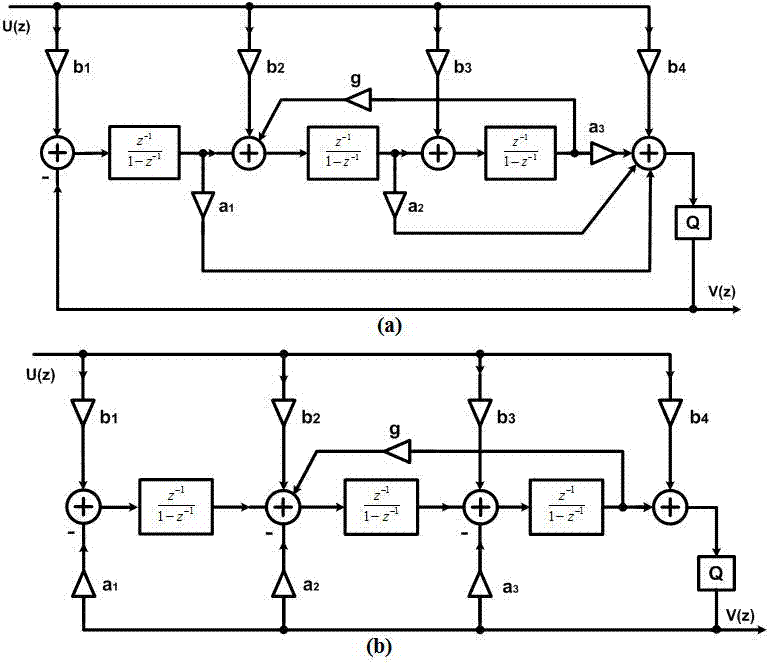

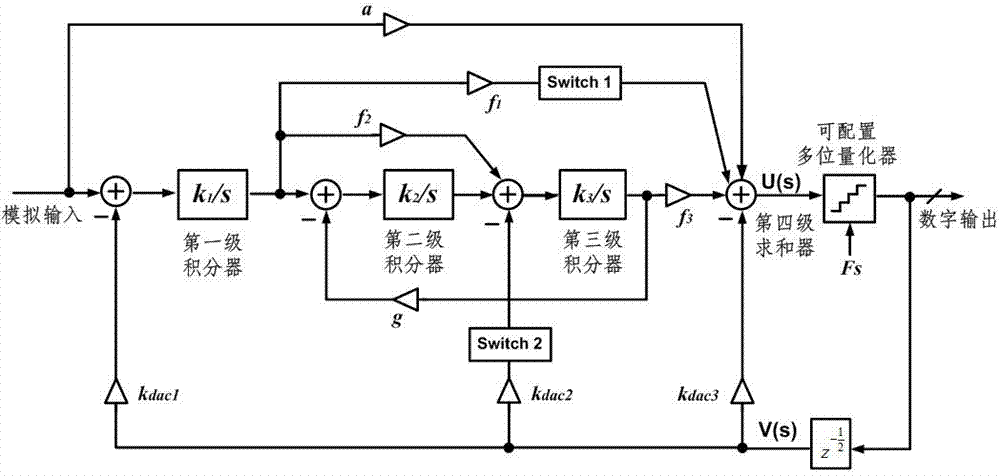

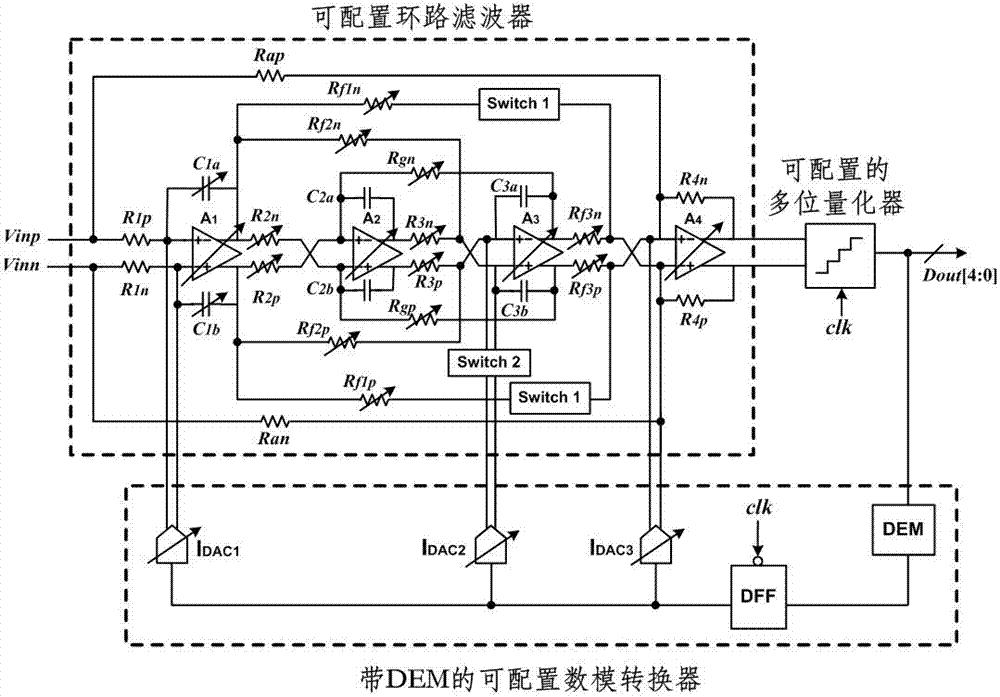

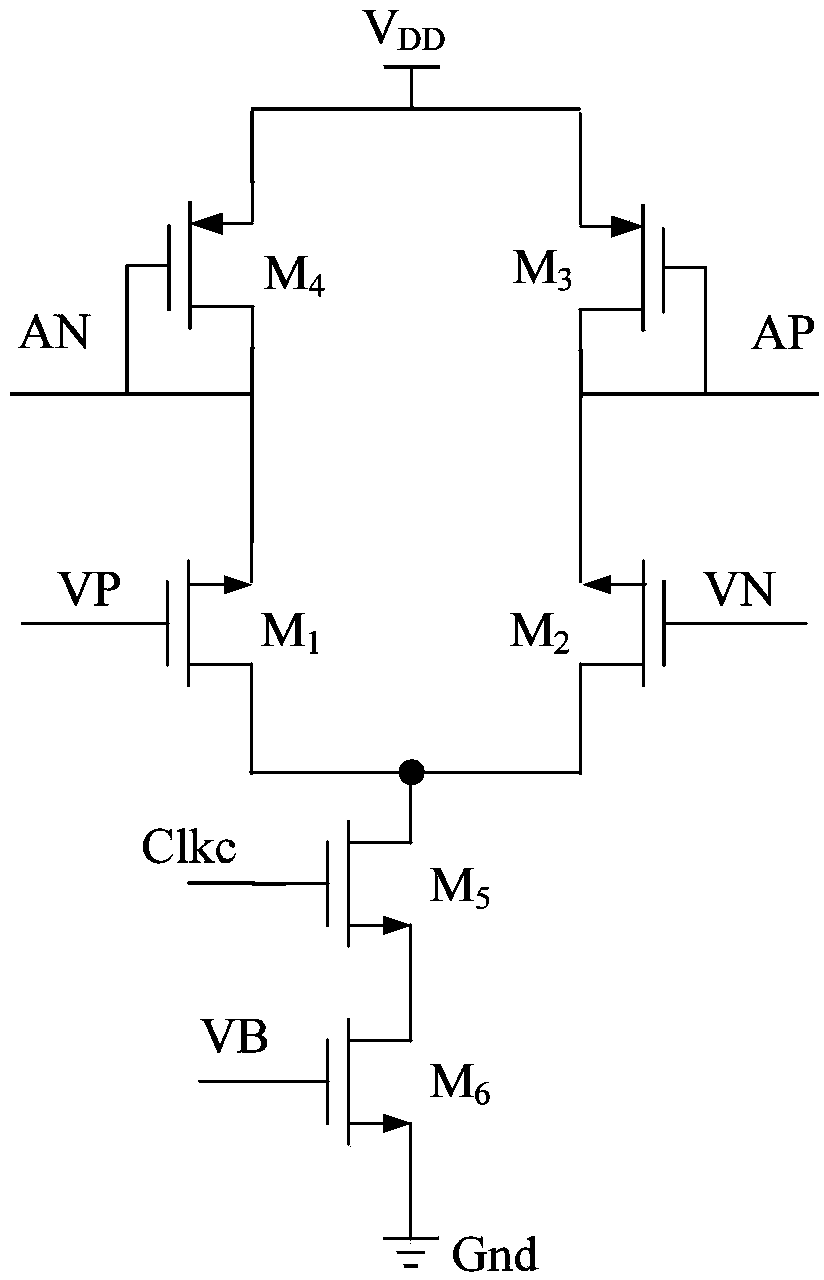

Reconfigurable continuous time type high-speed low-power consumption sigma-delta modulator

InactiveCN102832948AGood precisionImprove energy efficiencyEnergy efficient ICTAnalogue conversionWireless communication protocolEngineering

The invention belongs to the technical field of an integrated circuit, and particularly relates to a reconfigurable continuous time type high-speed low-power consumption sigma-delta modulator. The reconfigurable continuous time type high-speed low-power consumption sigma-delta modulator is formed by a configurable loop filter, a multi-digit quantizer and a feedback ADC (Analog to Digital Converter). According to a circuit structure, the loop filter adopts a third-order active RC (Remote Control) filter structure, the multi-digit quantizer is realized by adopting an interpolating method, and the feedback ADC adopts a high-speed dynamic element matching technology. According to the reconfigurable continuous time type high-speed low-power consumption sigma-delta modulator disclosed by the invention, under different bandwidth modes, the modulator can be switched between a distribution feedforward structure with a harmonic oscillator and a distribution feedback structure with a harmonic oscillator, and the optimization for the accuracy and the energy efficiency in various bandwidth areas can be realized in system level; continuous analog signal inputs can be converted into discrete digital signal outputs by the modulator in 1.2V power supply voltage, signal bandwidths can be configured in four modes of 5MHz, 10MHz, 15MHz and 20MHz, the accuracy can be up to 11-12 bits, and each frequency range of a wireless communication protocol LTE (Long Term Evolution) can be covered.

Owner:FUDAN UNIV

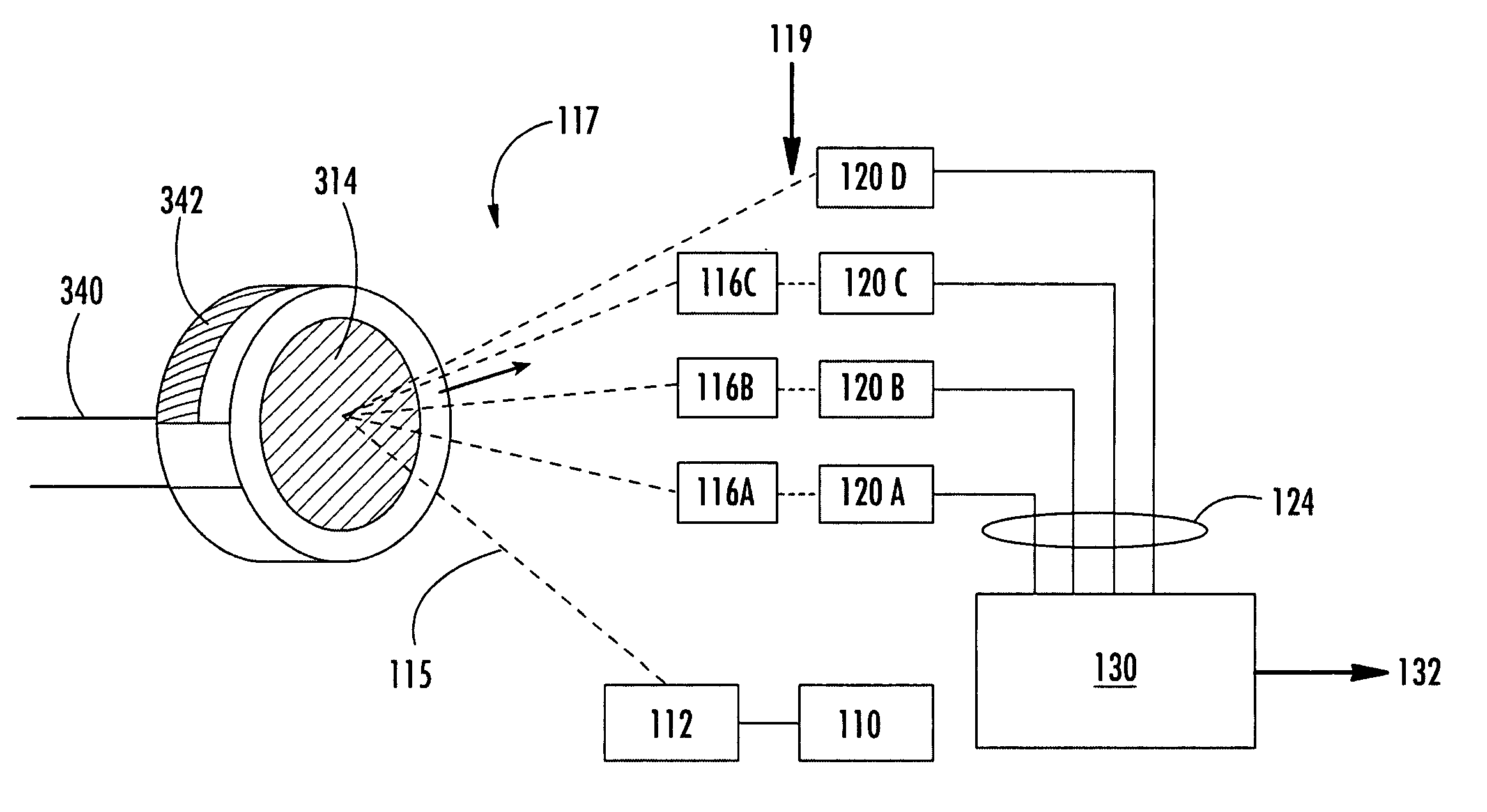

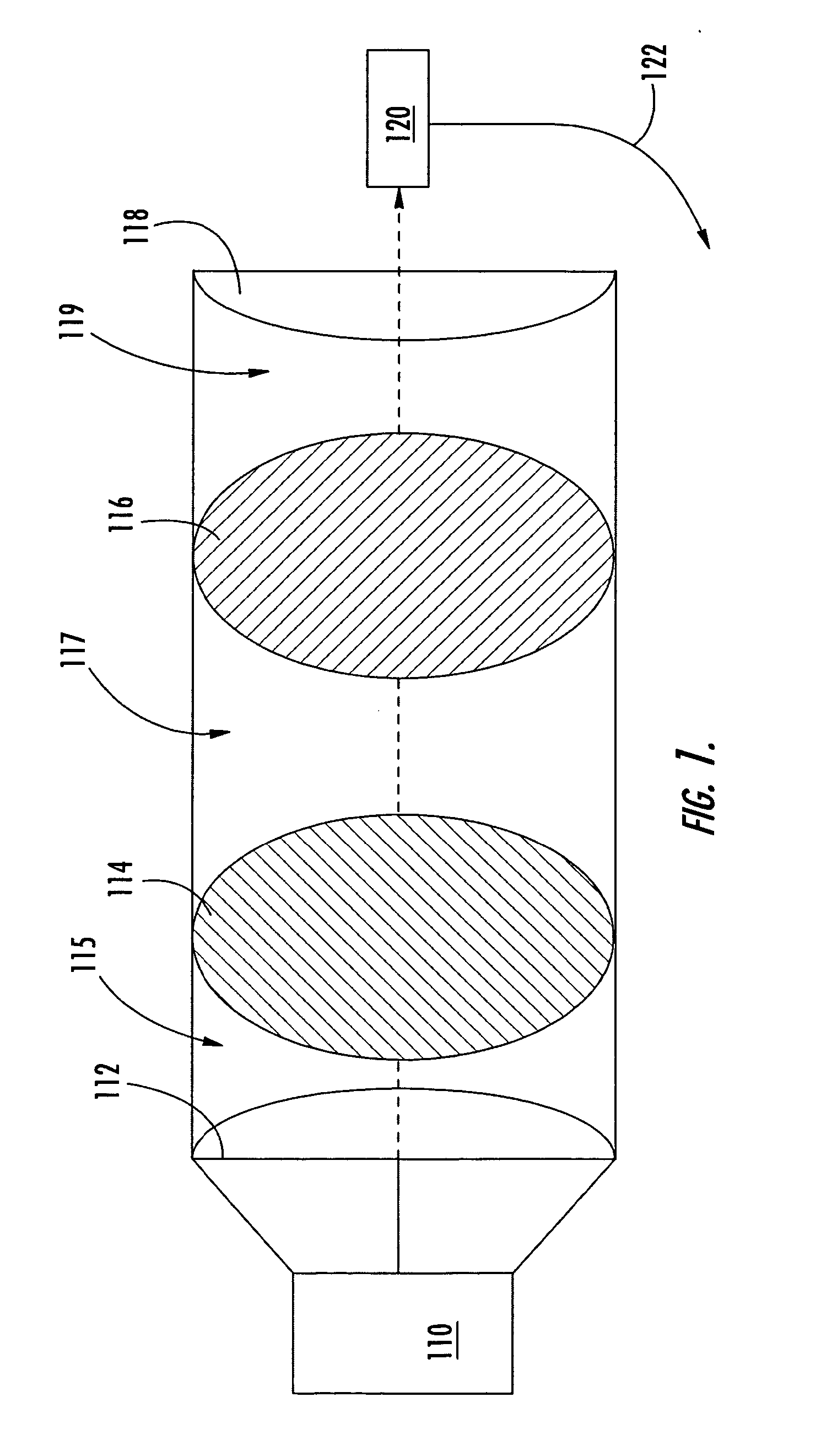

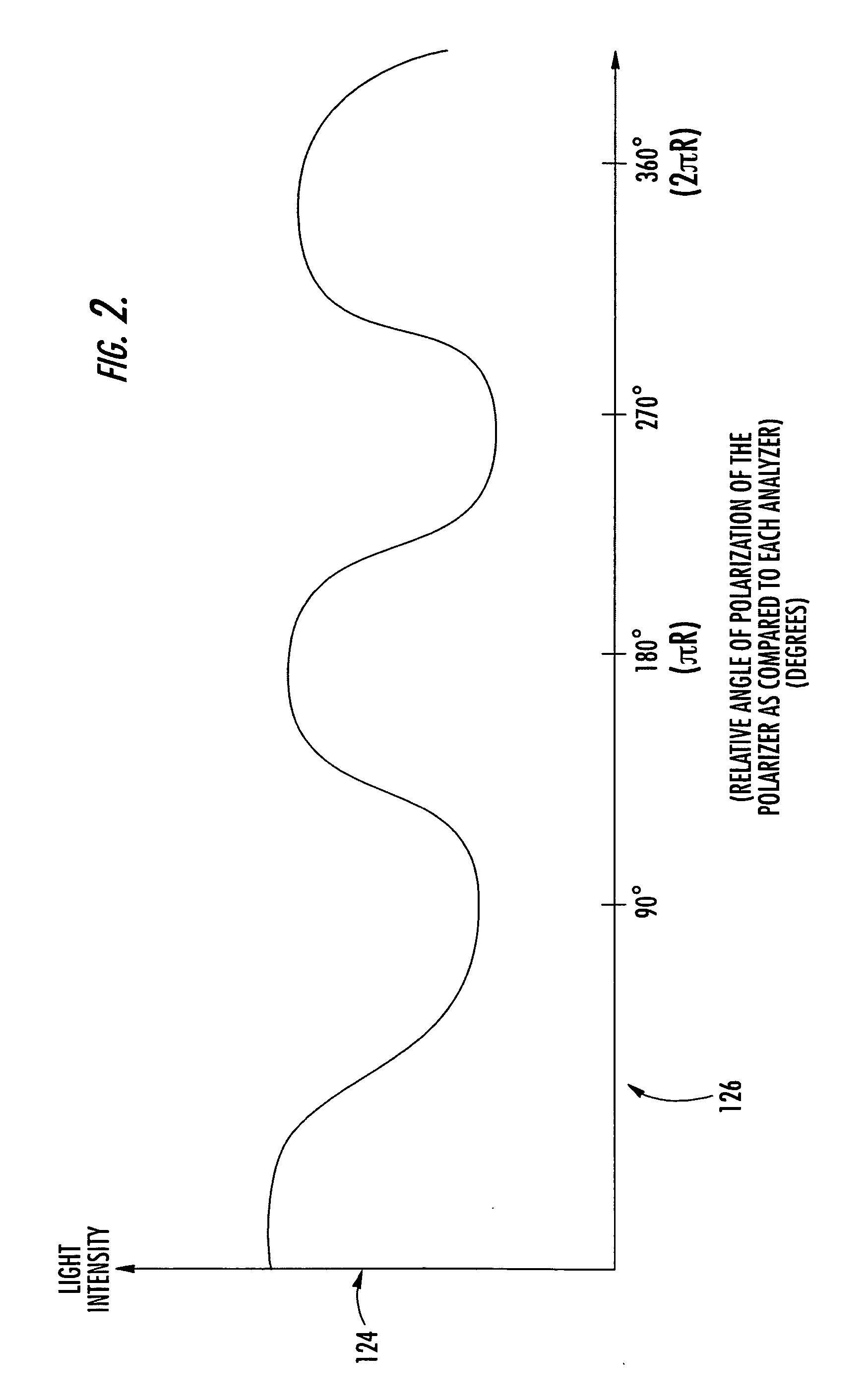

Non-contact optical polarization angle encoder

InactiveUS20050002032A1Improve toleranceHigh frequencyMaterial analysis by optical meansPhotoelectric discharge tubesPolarizerStationary object

An optically coupled rotary encoder that is capable of measuring and encoding the angle of rotation of a rotating or stationary object. A polarizer rotates synchronously with the rotatable object and inputs broadband or single frequency unpolarized light. The polarizer outputs and directs polarized light towards a plurality of fixed analyzers and light detectors. Each fixed analyzer outputs and directs further polarized light towards one of the light detectors. Each light detector outputs an electrical signal to a phase processor based upon one attribute of the further polarized light. The phase processor outputs a phase angle with high resolution (>12 bit) with high accuracy and frequency (5 MHz). The system and method can operate in harsh environments having high temperatures, dirt and debris and is not susceptible to EMI / RFI.

Owner:VISIDYNE

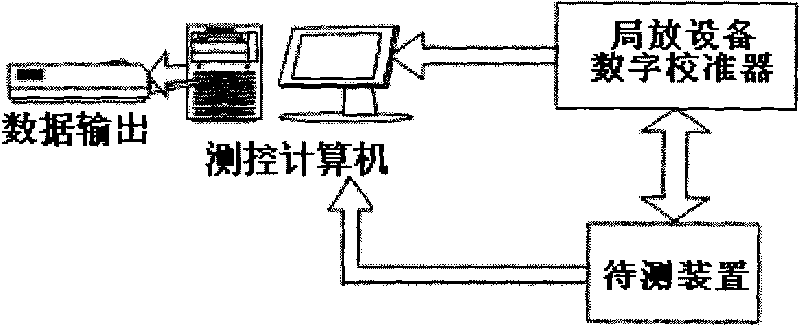

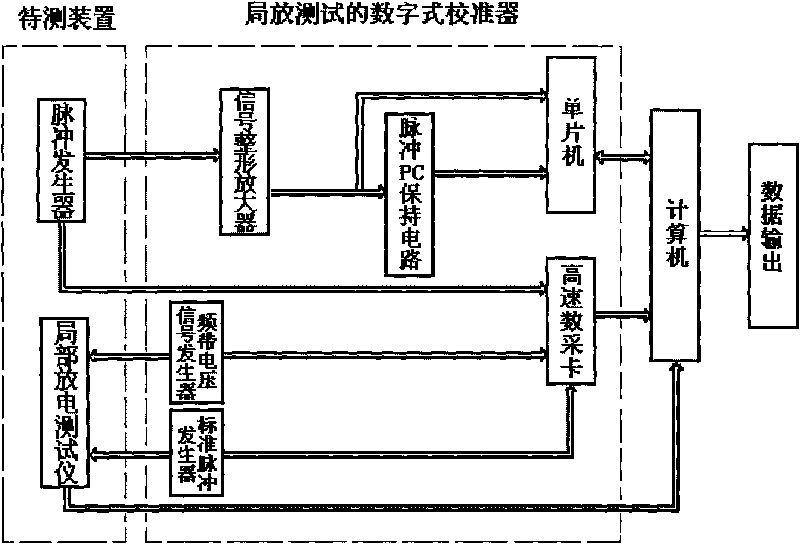

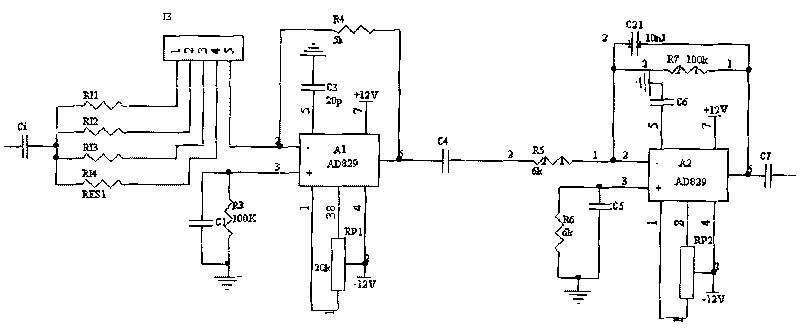

Digital calibration system of partial discharge test equipment

ActiveCN101706563AGo digitalImprove calibration efficiencyElectrical measurementsData acquisitionEngineering

The invention discloses a digital calibration system of partial discharge test equipment. The digital calibration system is characterized in that the system comprises a device to be tested, and a digital calibrator and a measurement and control computer of the partial discharge test equipment which is connected with the device to be tested, wherein the output end of the digital calibrator of the partial discharge test equipment is connected with the measurement and control computer; the measurement and control computer compares the collected waveform and data measured value with the standard value output by the digital calibrator to perform analysis and calculation and obtain the error of the measured value and the standard value, outputs the error value, and measured value and standard value to a data outputting machine so as to realize the calibration of the partial discharge test equipment. In the system of the invention, the wide measuring range which is 1-10000pc, the high accuracy standard pulse calibrator and a high speed data acquisition card with 12 bits of precision are adopted to ensure the calibration accuracy to reach + / -2%.

Owner:XIAN HIGH VOLTAGE APP RES INST CO LTD

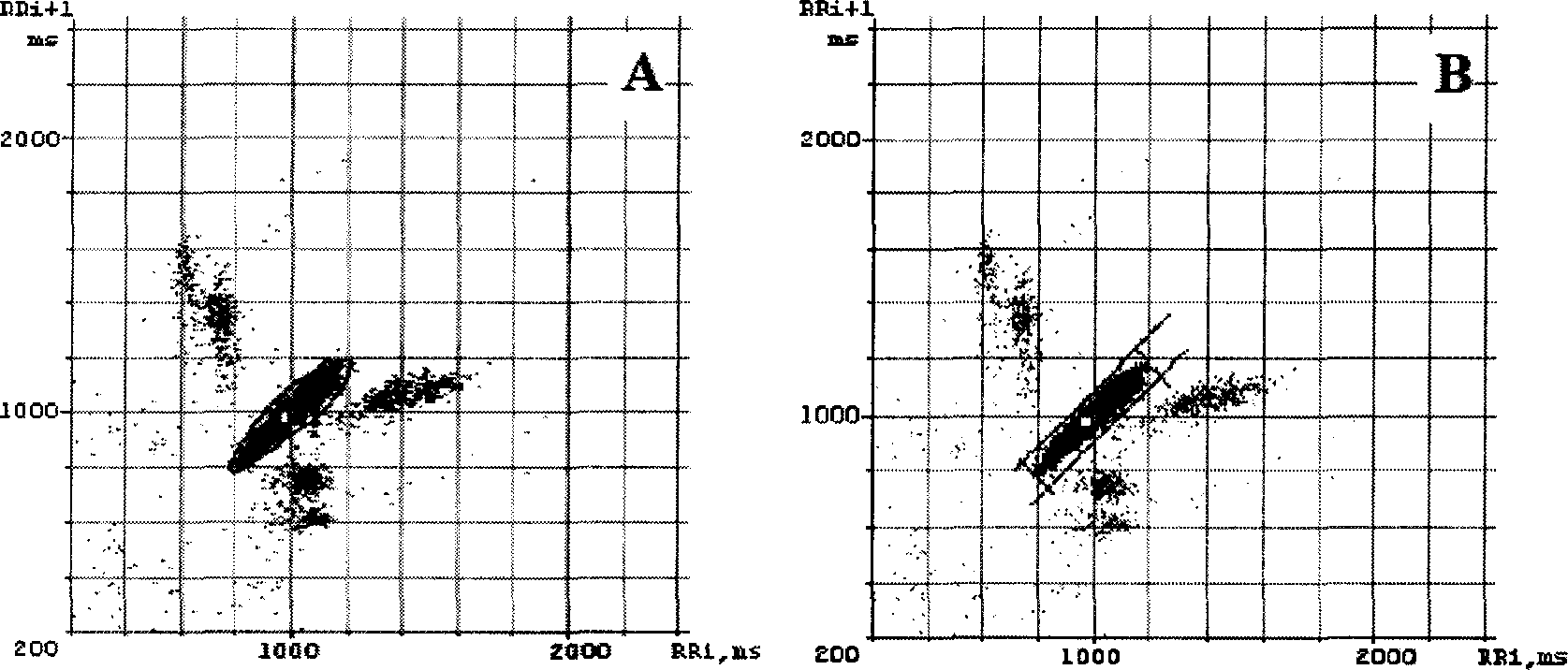

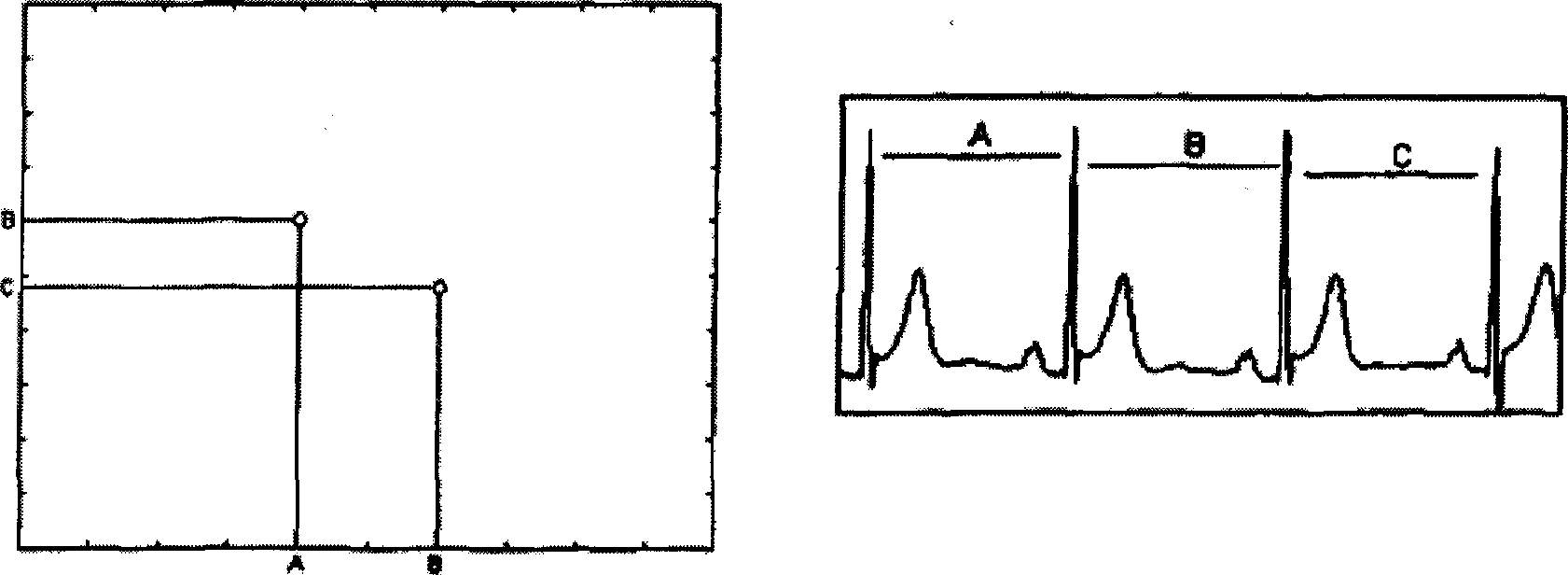

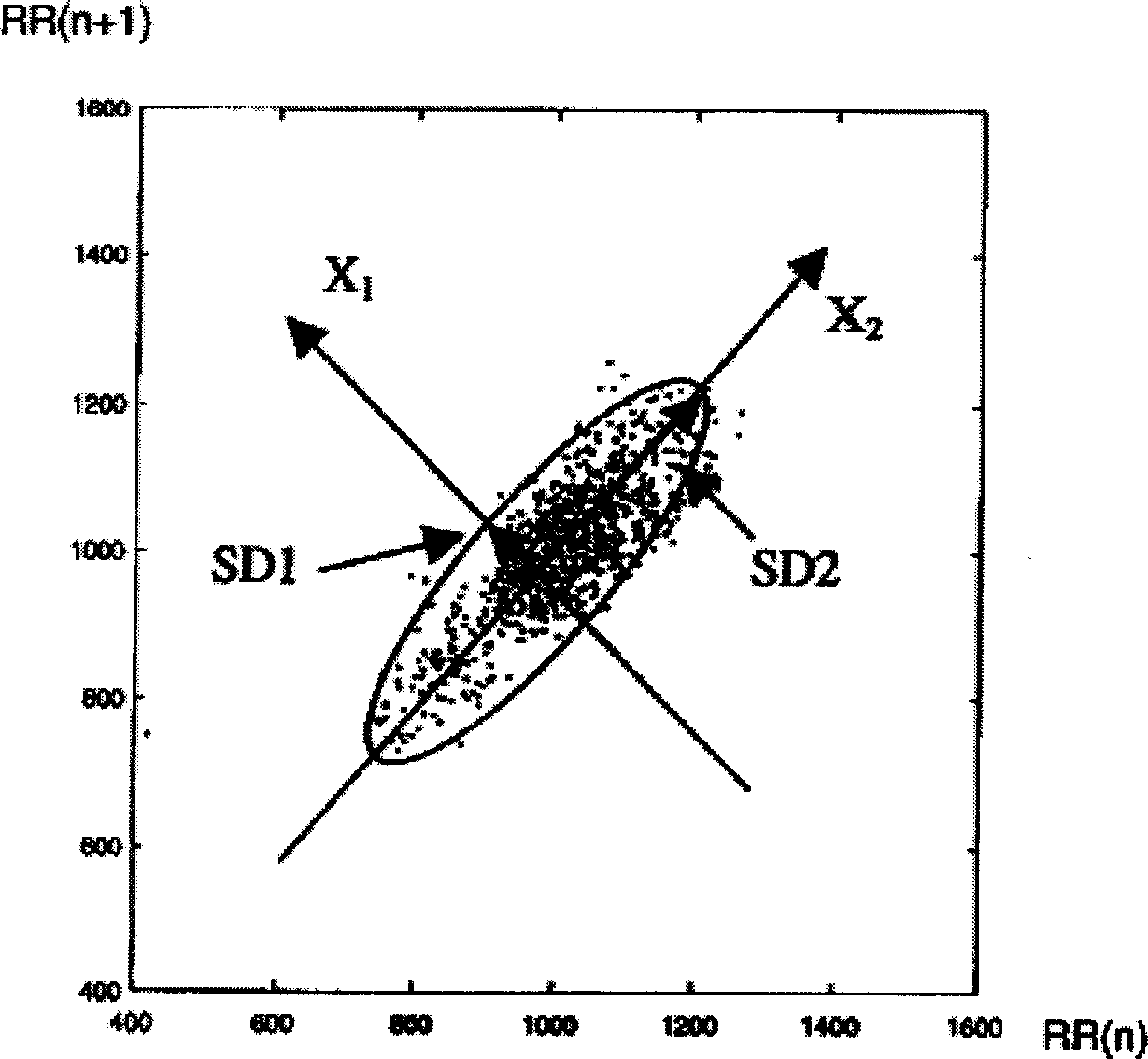

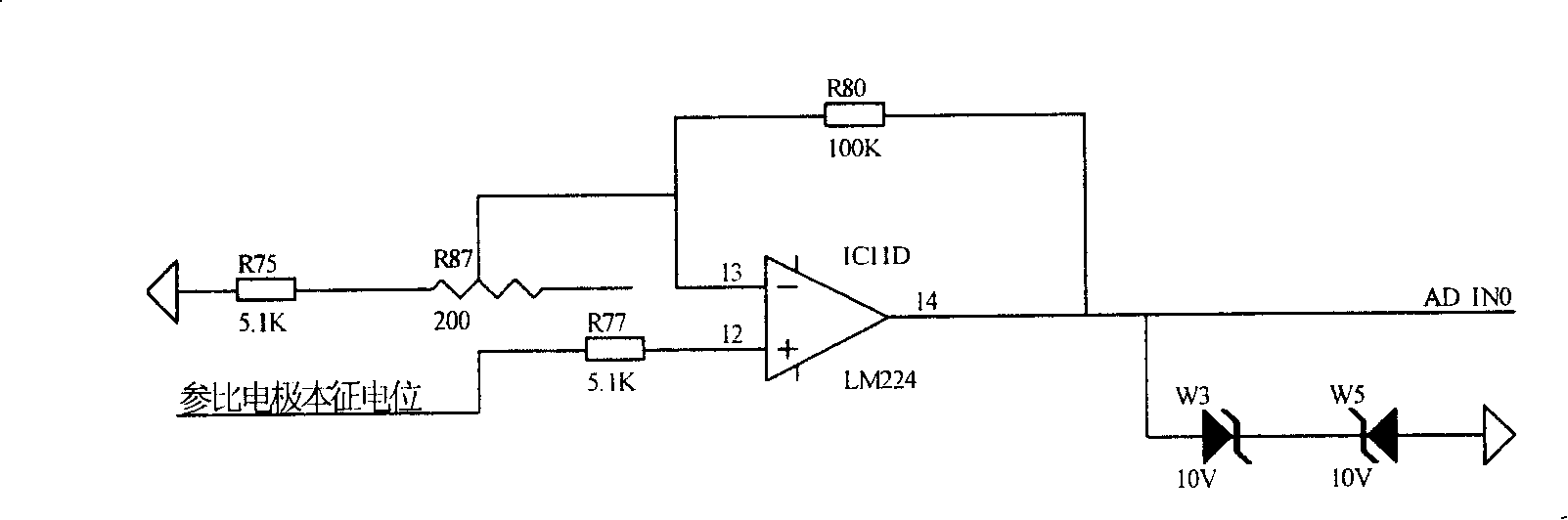

Dynamic characteristic analysis method of real-time tendency of heart state

InactiveCN1887223AHigh input impedanceHigh Common Mode Rejection RatioDiagnostic recording/measuringSensorsFeature parameterFive-dimensional space

The dynamic characteristic analysis method of real-time tendency of heart state includes: obtaining electorcardiac waveform with multipath electorcardiac amplifier and 12-bit A / D converter; forming time sequence related heart rate variation scatter diagram by means of space-time correlation technology and scatter diagram technology; extracting time sequence related characteristic parameters, short time-real time characteristic conversion illustration parameter and quantized space-time parameter indexes of characteristic illustration via automatic and manual interaction; classifying the illustration and quantized space-time parameters in artificial neural network; and describing dynamic characteristics and relevant invariance characteristics of heart rate variation in a nine-dimensional and a five-dimensional space with two independent curve surfaces and their boundary to represent the heart function.

Owner:ZHEJIANG UNIV

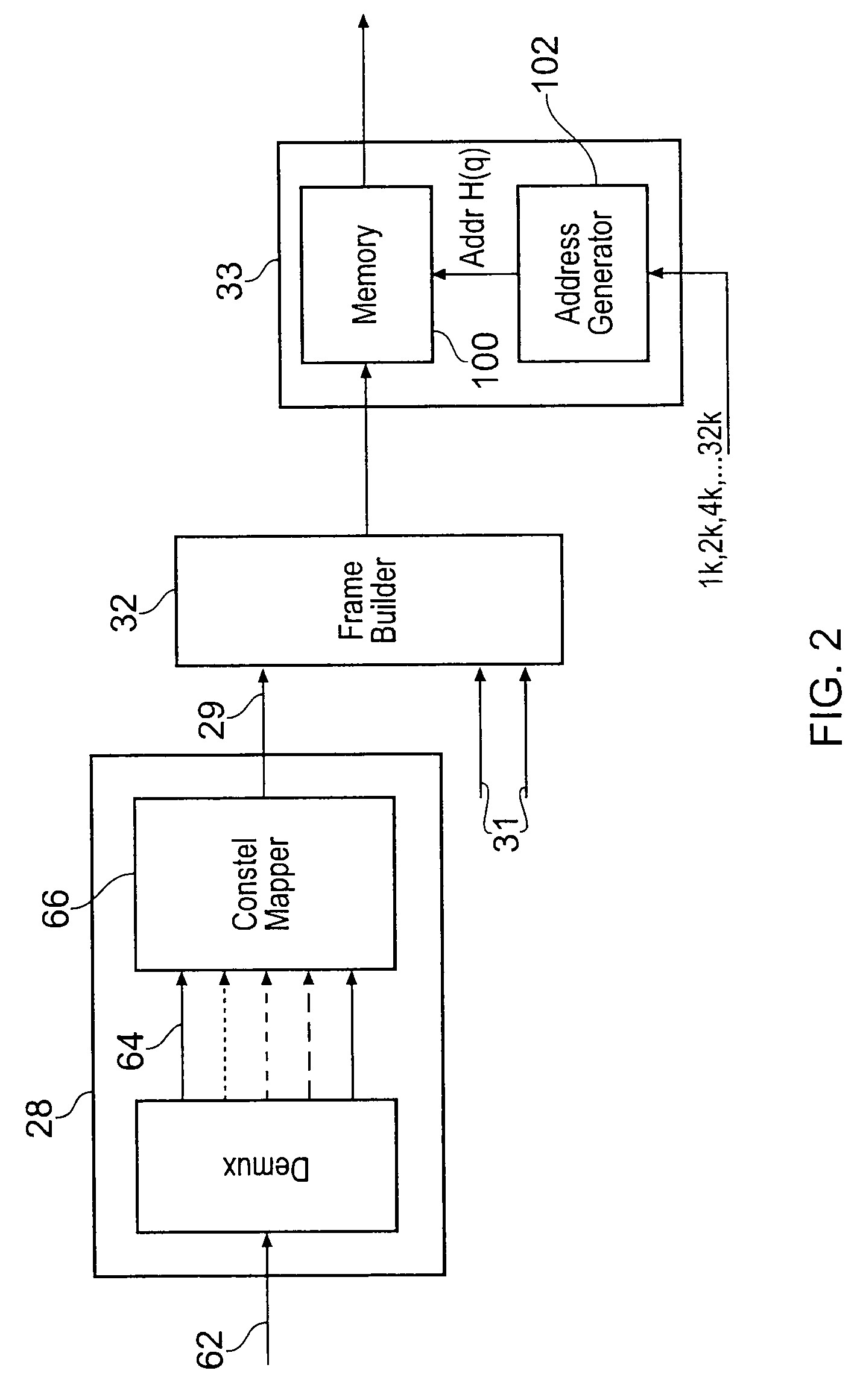

Data processing apparatus and method

ActiveUS20090110097A1Pulse modulation television signal transmissionDigital data processing detailsData streamAddress generator

Owner:SONY CORP

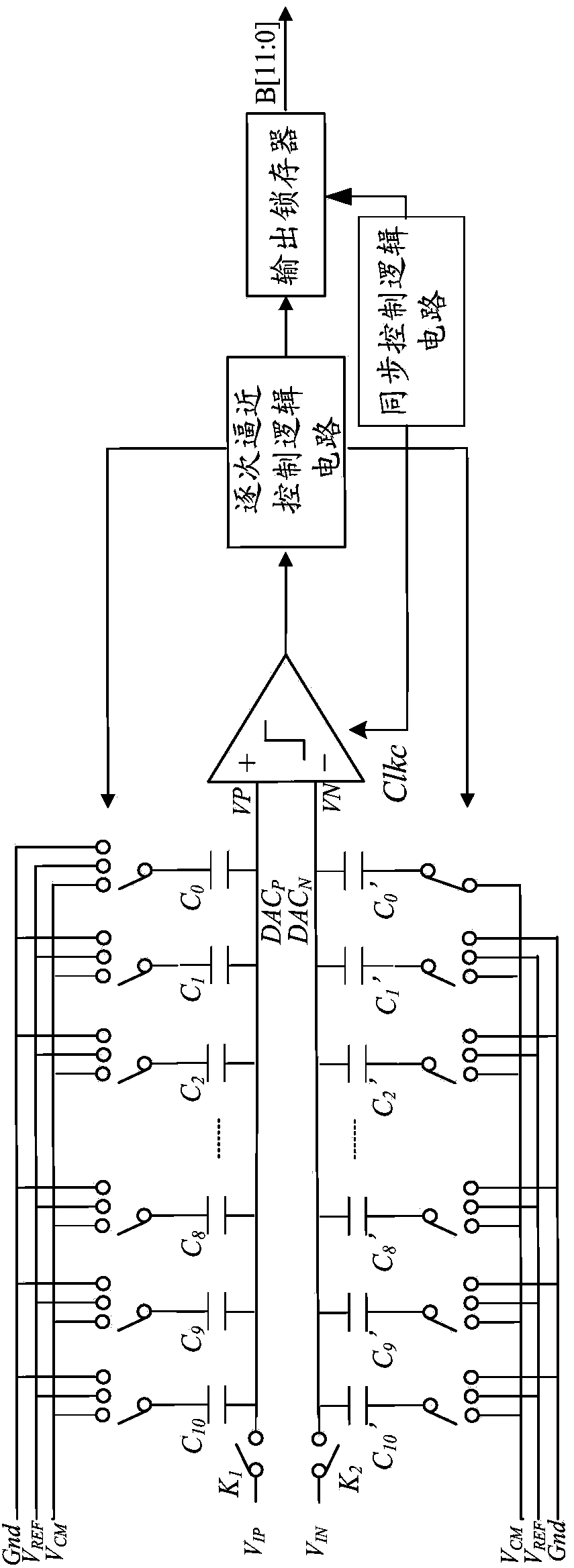

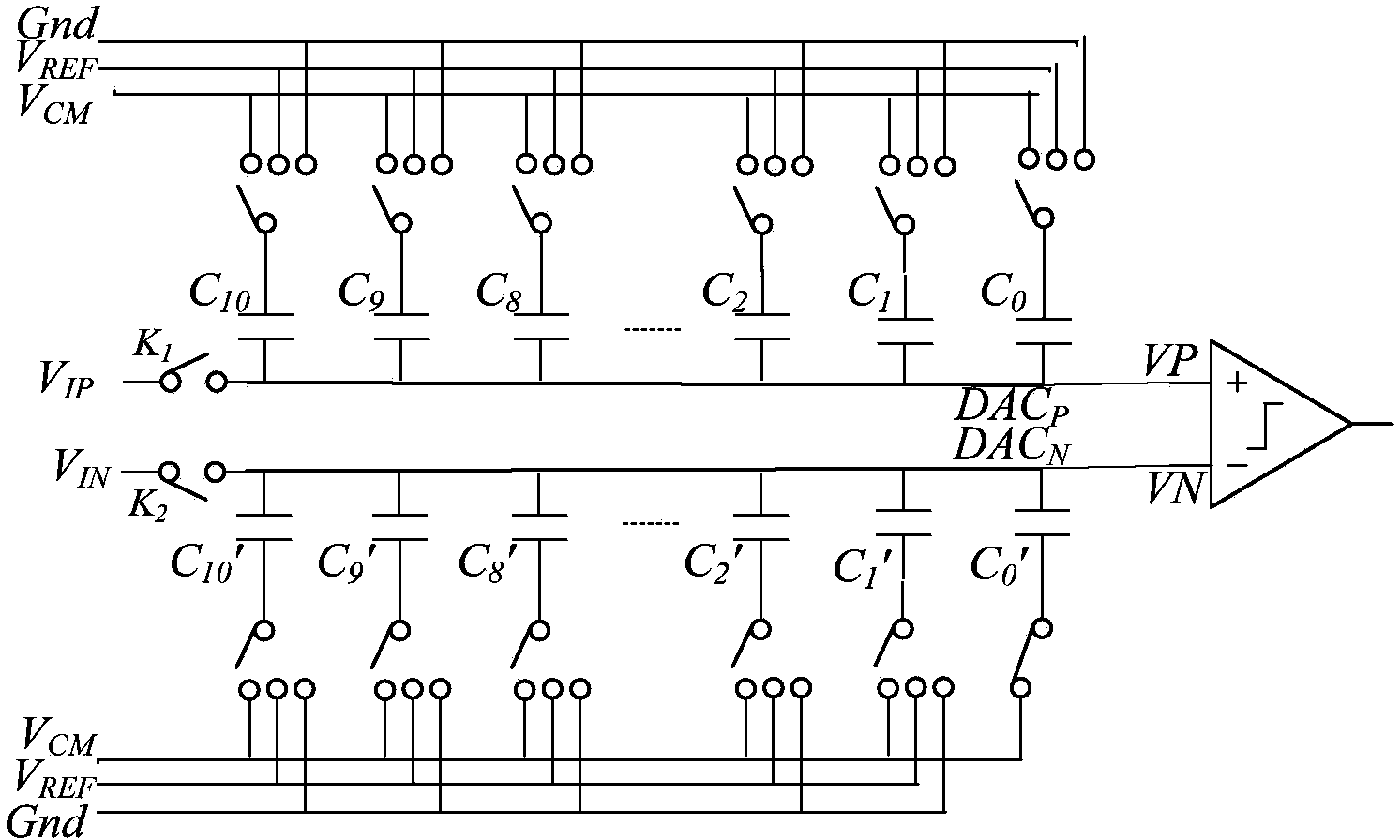

12-bit intermediate-rate successive approximation type analog-digital converter

ActiveCN104113341AArea halvedReduce static power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceNegative phase

The invention provides a 12-bit intermediate-rate successive approximation type analog-digital converter and relates to the field of analog-digital converters. The 12-bit intermediate-rate successive approximation type analog-digital converter comprises a sampling network, a differential capacitor array connected with the sampling network, and a comparator circuit connected with the differential capacitor array, wherein the differential capacitor array comprises a first capacitor array connected with the positive-phase input end of the comparator circuit, and a second capacitor array connected with the negative-phase input end of the comparator circuit; both the first capacitor array and the second capacitor array are composed of 11 groups of binary-structured bit capacitors, and the bottom plates of the redundant capacitors of the second capacitor array are constantly connected with a common-mode voltage VCM. The 12-bit intermediate-rate successive approximation type analog-digital converter solves the problems of large capacitor area and high power consumption of a traditional binary capacitor type structure.

Owner:XIDIAN UNIV

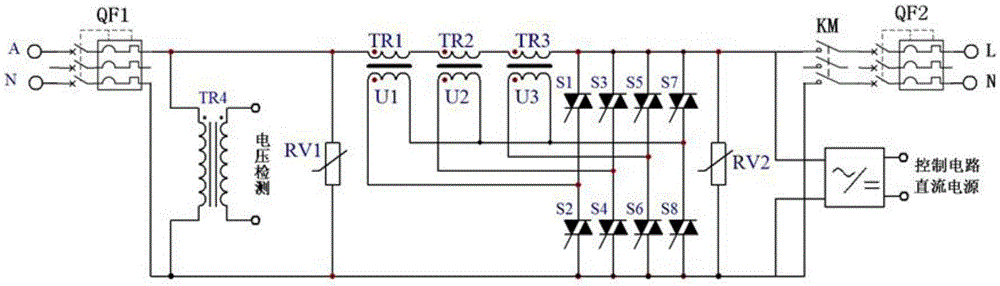

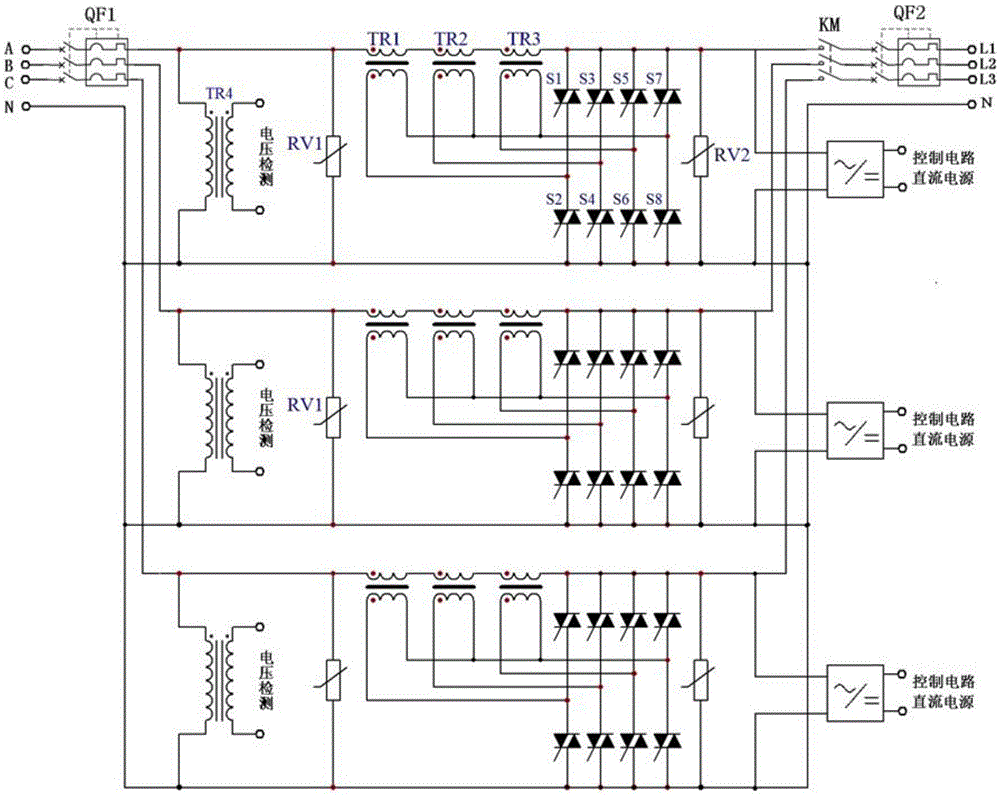

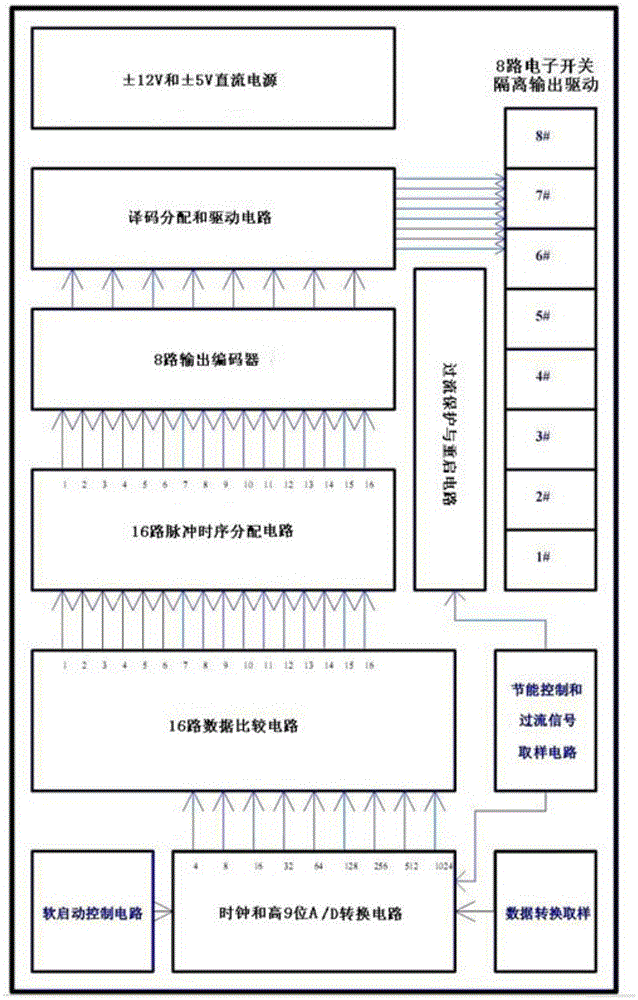

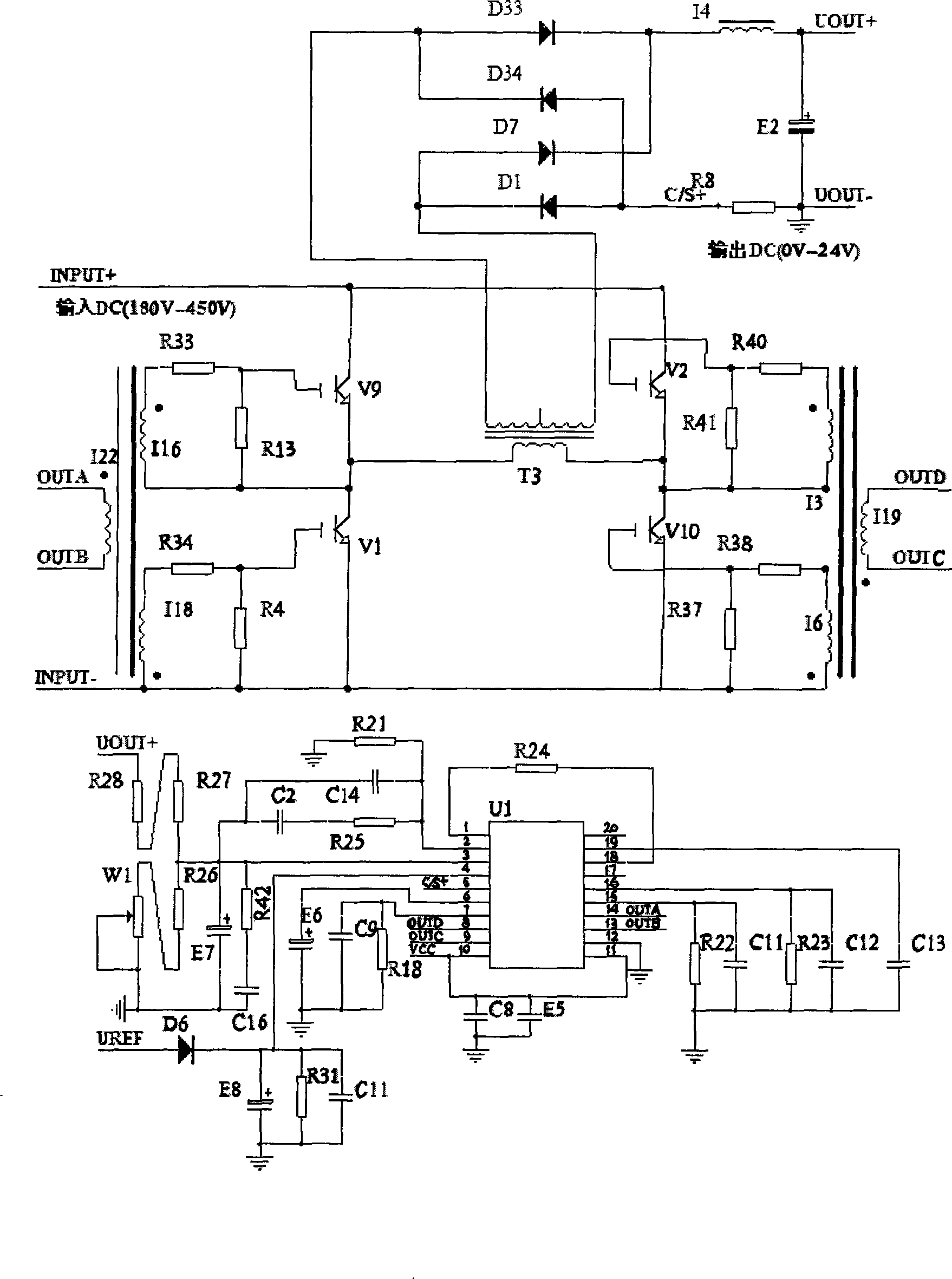

Combined single-phase/three-phase alternating current voltage stabilizer based on digital circuit control

InactiveCN105429475ALow powerReduce capacityConversion without intermediate conversion to dcTransformerAlternating current

The invention relates to a multi-single-phase / three-phase alternating current voltage stabilizer based on digital circuit control. The voltage stabilizer comprises: an input terminal is connected with three compensation transformers of a power grid, an output terminal is connected to an input terminal of electrical equipment via series connection of primary windings of the three transformers, and secondary winding terminals of the three transformers are connected to an output voltage terminal via 8 bidirectional thyristors, a TR4 transformer at an input voltage side provides real-time voltage detection signals, alternating current effective value detection is conducted via a 12-bit high-precision A / D converter, single-phase alternating current work voltage is monitored in real time, obtained high 9-bit digital signals and a set coding amount value are compared, the 8 bidirectional thyristors are determined, combined, and triggered via a decoding driving circuit according to a hardware logic programming regulation, the employed group number of secondary windings of the transformers and the voltage direction are changed via different combinations of turn-on and turn-off of the bidirectional thyristors, different compensation combinations for measuring the voltage at one step are finally achieved, and the output voltage is guaranteed to be stabilized in a given voltage range.

Owner:SKILL TRAINING CENT STATE GRID JIBEI ELECTRONICS POWER COMPANY +2

PCI bus utilization diagnostic monitor

The present invention provides a PCI Bus Diagnostic Monitor which eliminates the need to hook up a logic analyzer and manually analyze the data passing on the PCI Bus. The present invention provides an accurate analysis of the PCI Bus master's utilization and / or latency time to acquire the PCI Bus by controlling a 12-bit counter and analyzing count values at appropriate times, e.g., between the time the PCI Bus request is output and the time that the data transfer begins, and the time between when the data transfer begins and when the data transfer ends. The data corresponding to a large number of data transfers may be buffered and analyzed to provide performance statistics relating to the PCI Bus. The analysis can be performed in lightly loaded, typically loaded, and heavily loaded PCI bus situations to fully and accurately test real-world capabilities of new peripherals, particular combinations of peripherals, and statistics relating to customized usage of a host system. The accurate statistics relating to the performance of the PCI Bus will also allow a system designer to assign and / or reassign PCI Bus priorities for various bus agents or peripherals.

Owner:LUCENT TECH INC

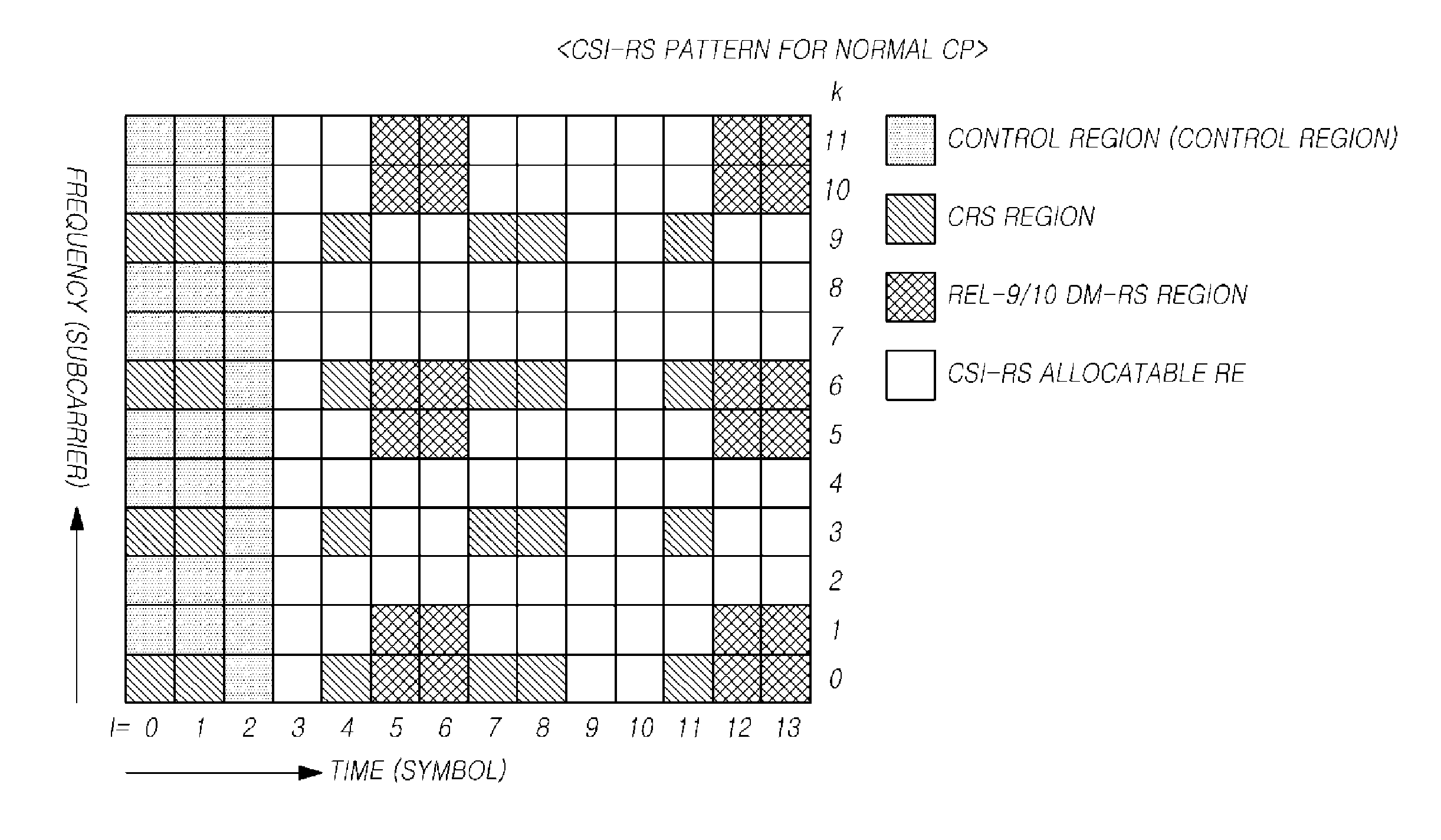

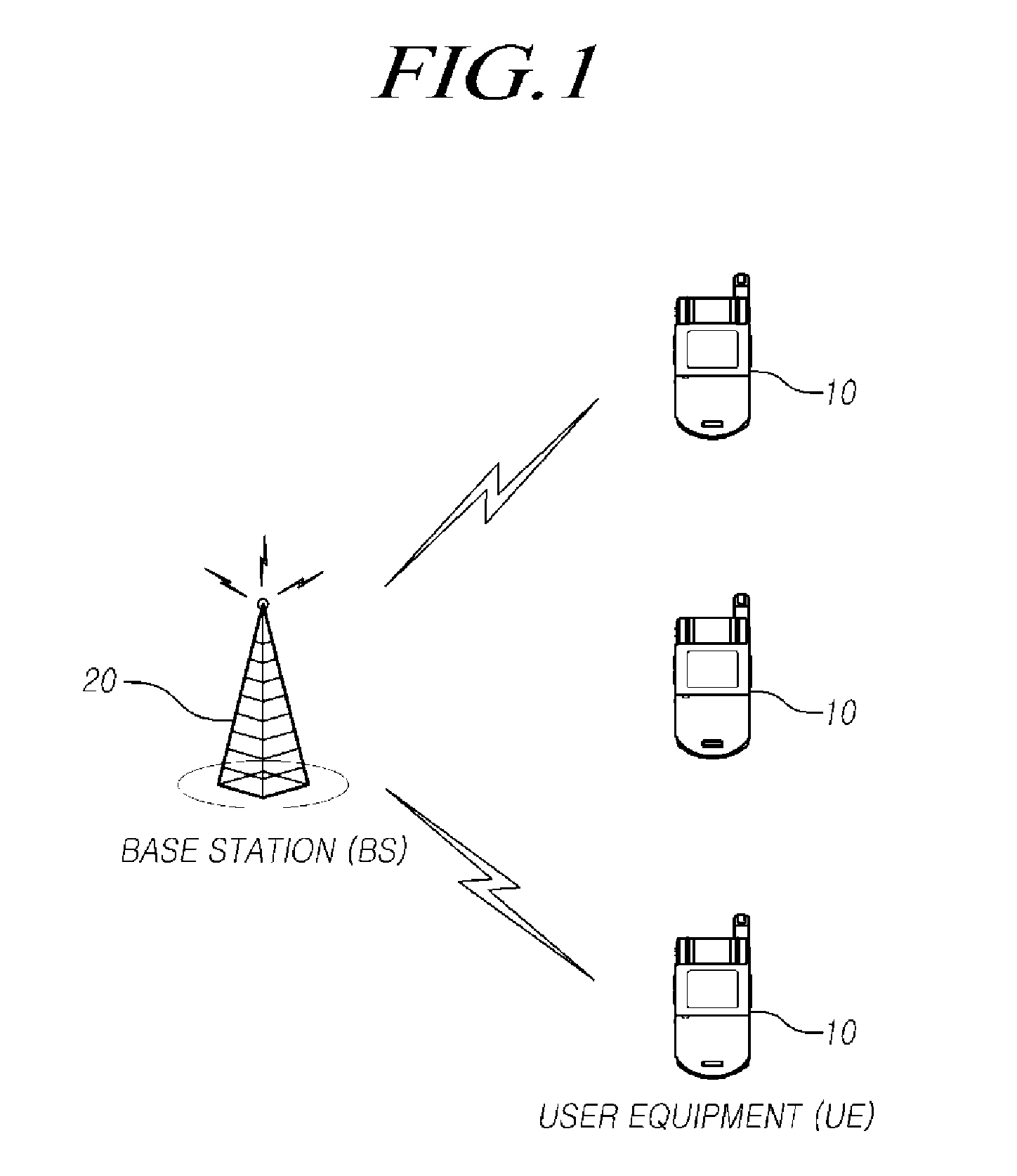

Apparatus and method for transmitting muting information, and apparatus and method for acquiring channel state using same

The present disclosure relates to an apparatus and a method for transmitting muting information in a wireless communication system, and to an apparatus and a method for acquiring channel state using same. In an exemplary embodiment, muting information includes: a first data field, having a serving cell for receiving from peripheral cells in a multi-cell environment, at least one of a CSI-RS pattern, the number of CSI-RS antenna ports, a CSI-RS duty cycle, and CSI-RS transmission subframe offset information, and using same for expressing the cycle and the offset of muting subframes, which pertain to information on a resource block that can generate interference between the peripheral cells and CSI-RS; and a second data field for expressing a specific muting pattern, which must be muted within the muting subframes, having either 12 bits or 28 bits that display muting application in a bitmap format.

Owner:PANTECH CORP

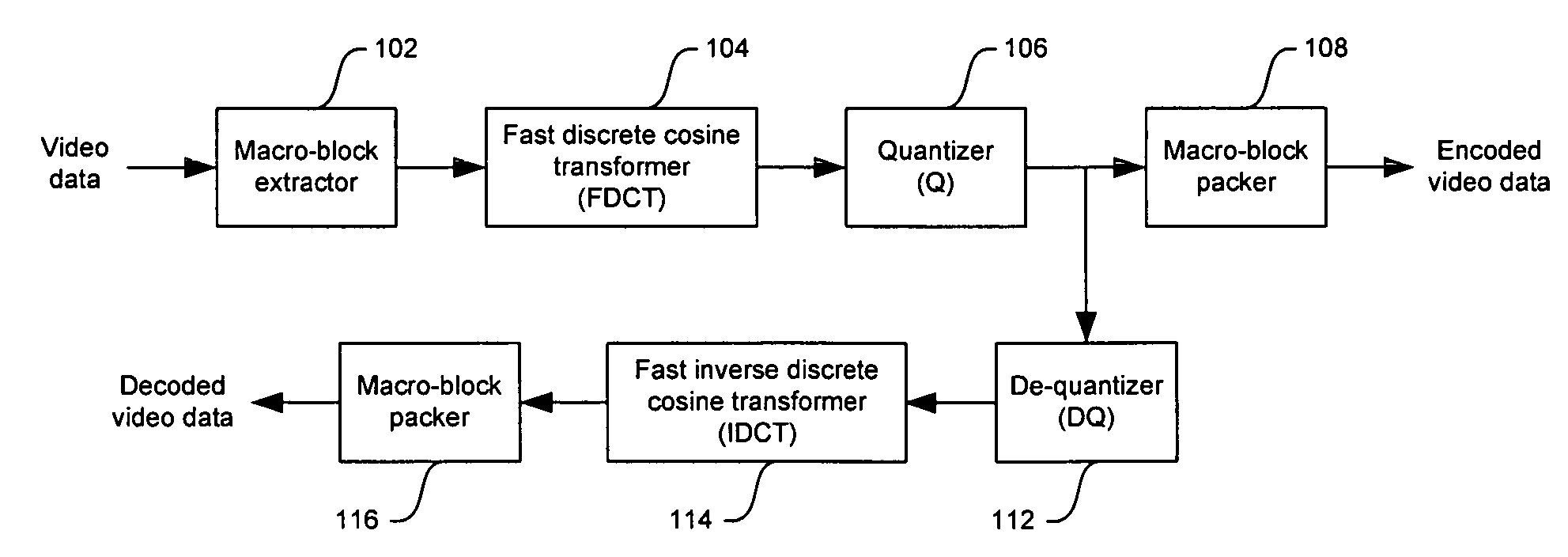

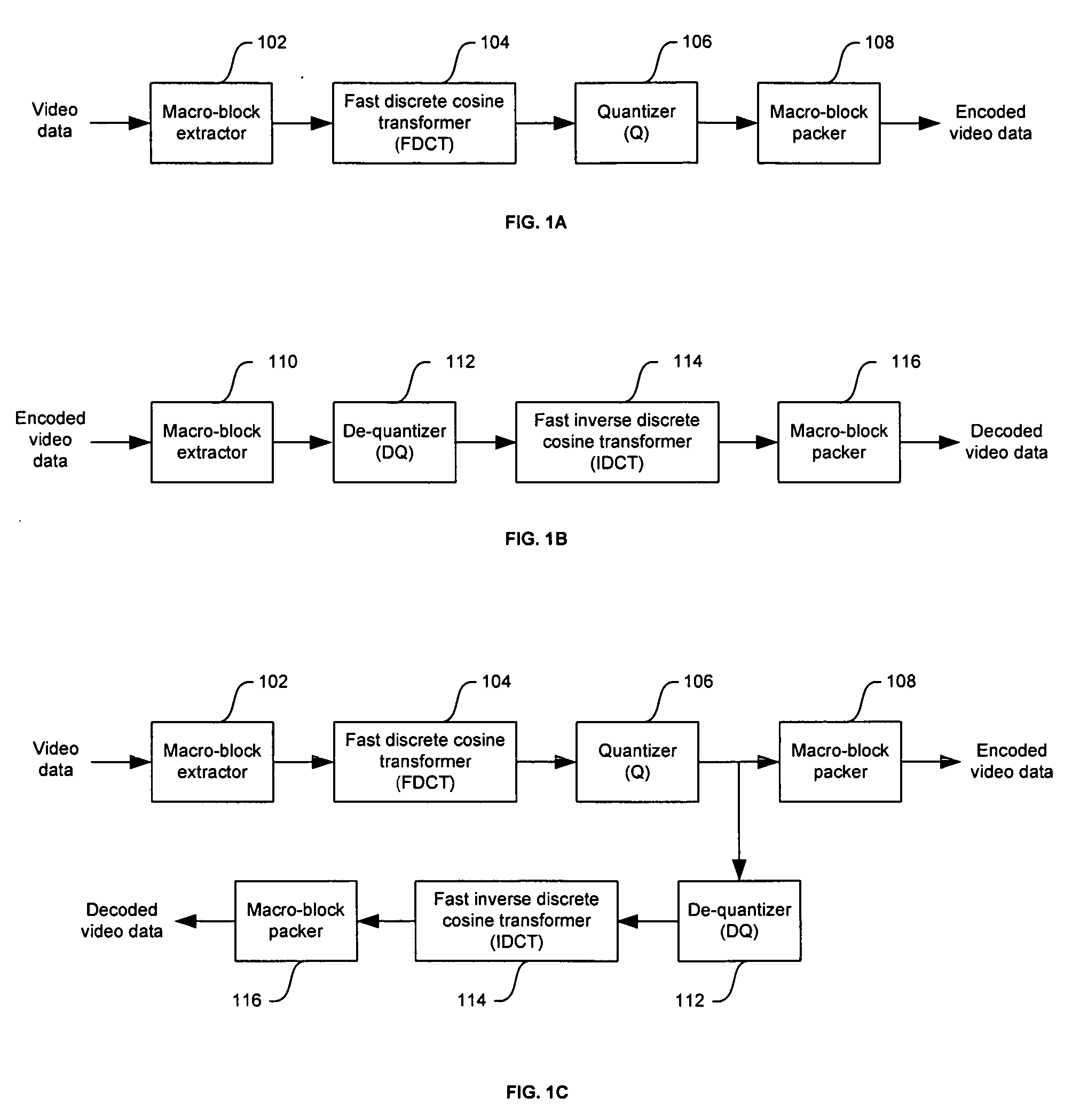

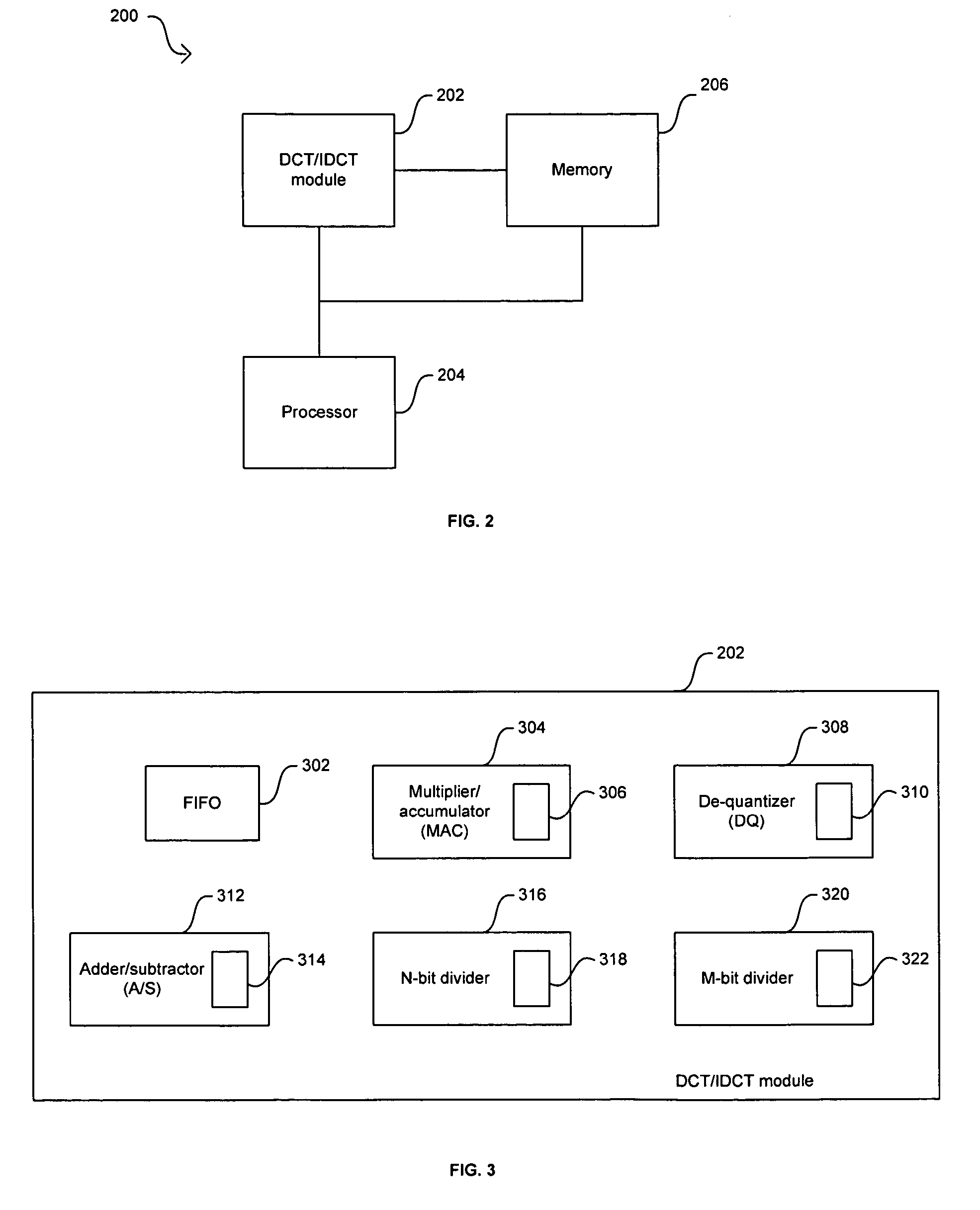

Method and system for dynamically configurable DCT/IDCT module in a wireless handset

ActiveUS20050281331A1Color television with pulse code modulationColor television with bandwidth reductionComputer architectureVideo processing

In a video processing system, a method and system for dynamically configurable DCT / IDCT module in a wireless handset are provided. A processor may be used to configure a quantization scheme and video format mode of operation and to configure a processing network in a DCT / IDCT module. The mode of operation may depend on whether the received video signal is in JPEG, MPEG, and / or H.263 format. The processing network may be configured into a DCT processing network configuration or an IDCT processing network configuration based on whether the received video signal is to be encoded or decoded respectively. The DCT / IDCT module may comprise a FIFO, an adder / subtractor, a multipler / accumulator, a plurality of digital dividers, and a de-quantizer. The plurality of digital dividers may comprise a 12-bit divider and an 7-bit divider. The mode and configuration modifications may be dynamically performed during operation of the wireless handset.

Owner:AVAGO TECH INT SALES PTE LTD

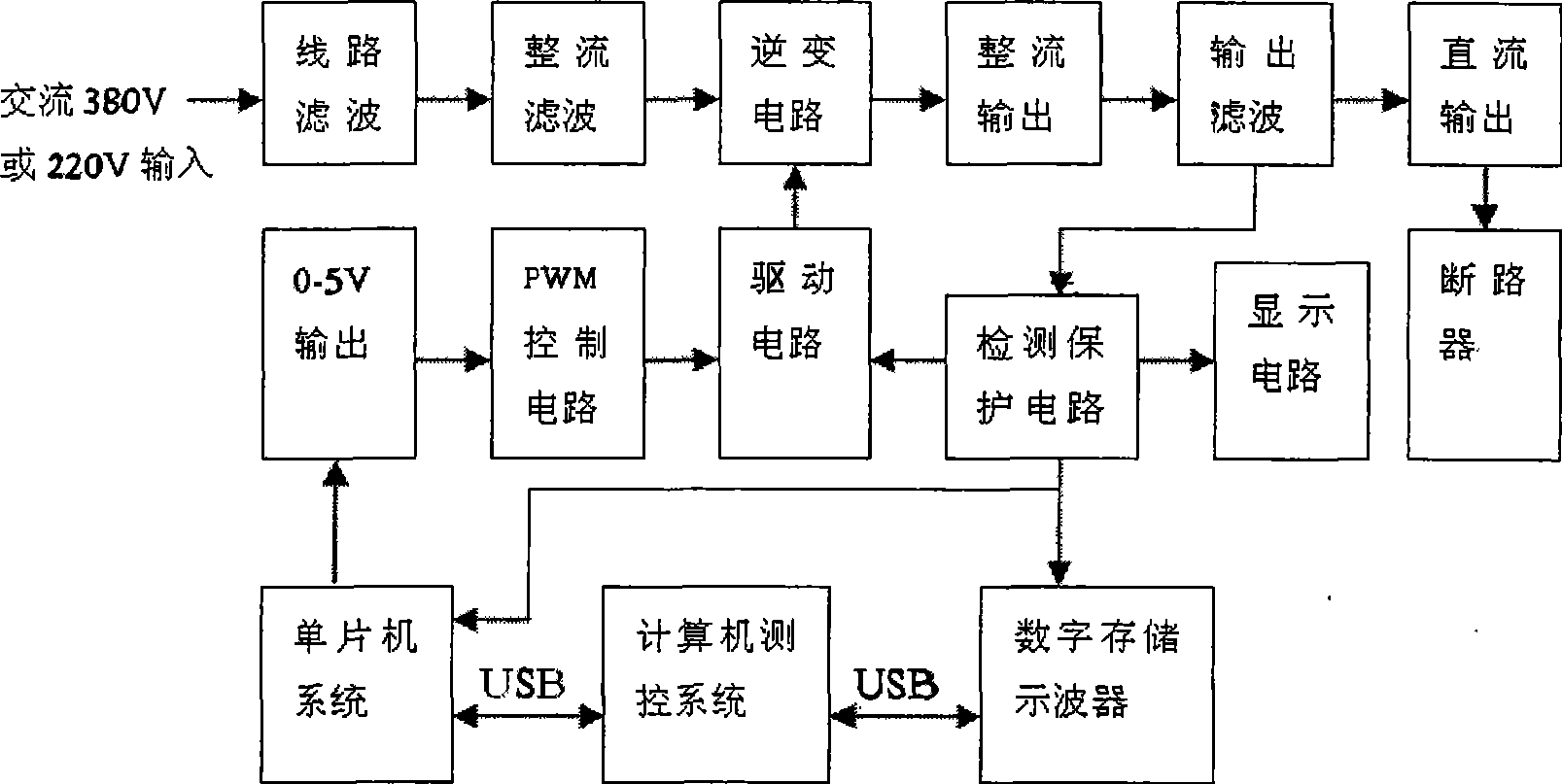

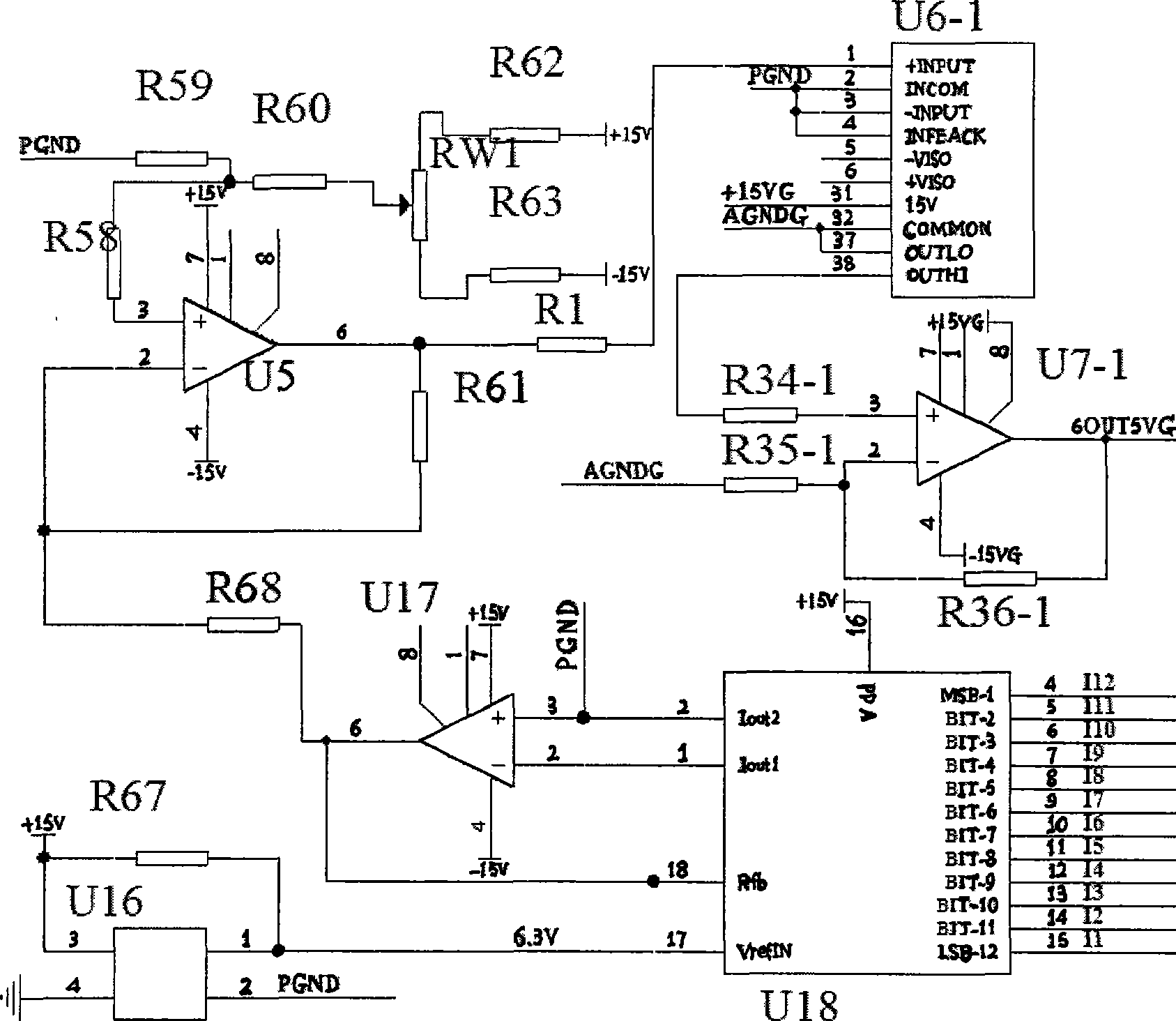

Automatic test system of dc circuit breaker characteristic parameter

InactiveCN101509955ARealize on-site integrated testingImprove accuracyCircuit interrupters testingDc currentFull bridge

The invention discloses an automatic testing system of characteristic parameters of a direct-current breaker, which consists essentially of an analyzing and managing system controlled by a computer, a digital storage oscillograph and a program-controllable direct-current power source. 12-bit digital values that are output by a single chip microcomputer output 0 to 5V voltage through a digital-to-analog converting circuit, and the voltage is output to a phase-shifting-control full-bridge zero-voltage switching and a pulse modulation converting circuit through an isolating amplifier as well as to an EA+ end of a main chip, thus changing output current. The electromagnetic tripping action time is measured by a waveform breaking method and taking the largest constant short-circuit current in electromagnetic instantaneous acting tripping as the starting point of timing, thus having the advantages of high accuracy, efficiency and reliability.

Owner:STATE GRID SICHUAN ELECTRIC POWER CORP ELECTRIC POWER RES INST

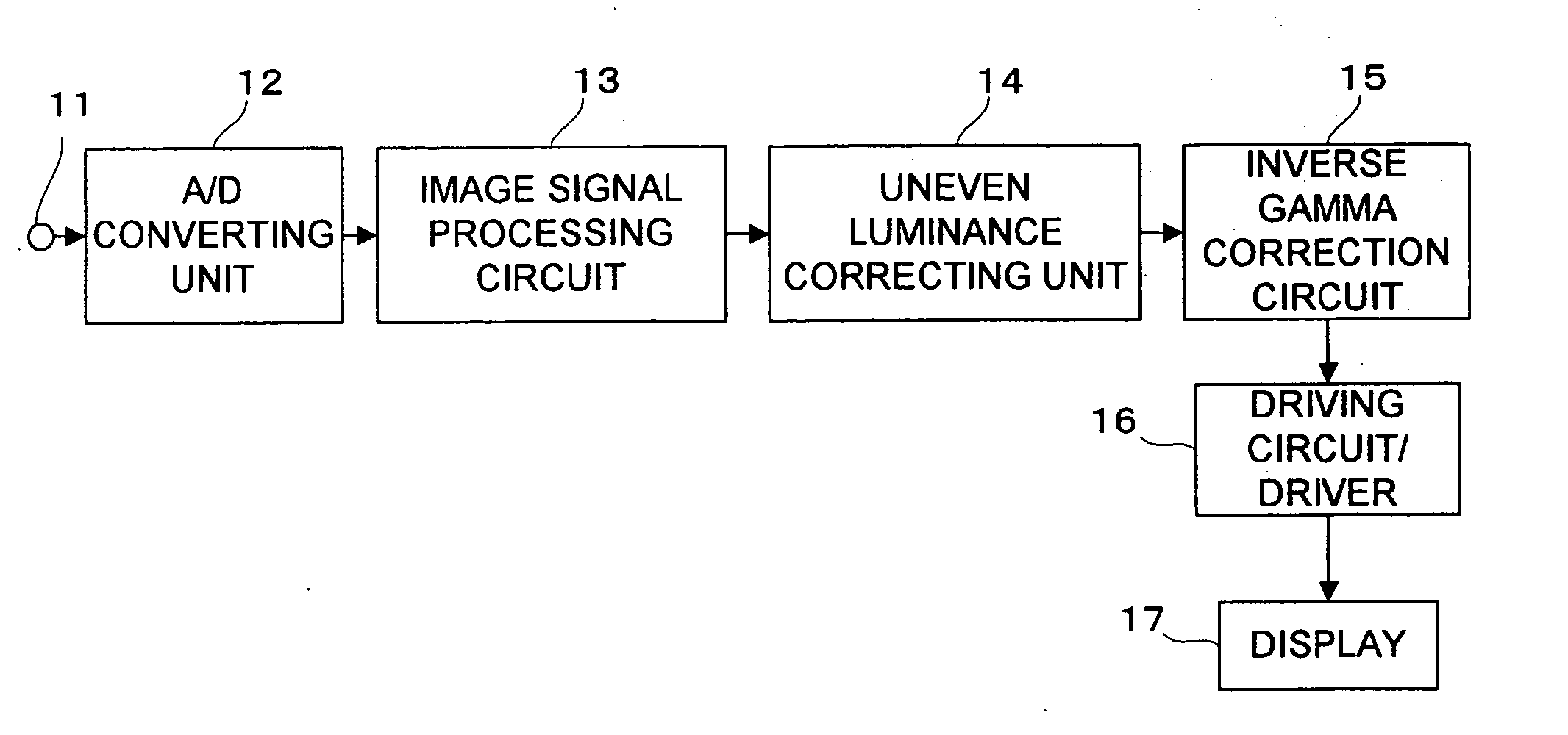

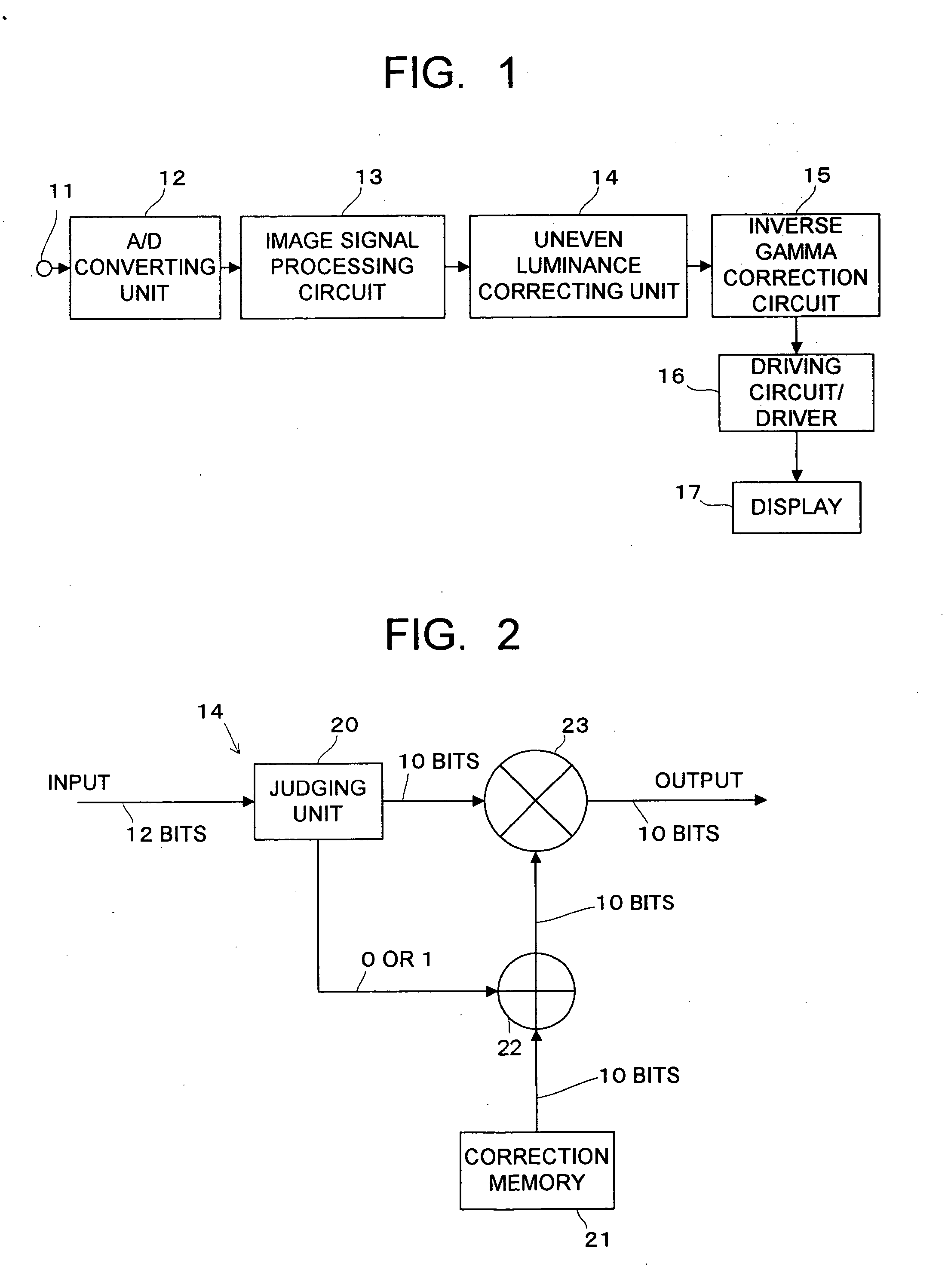

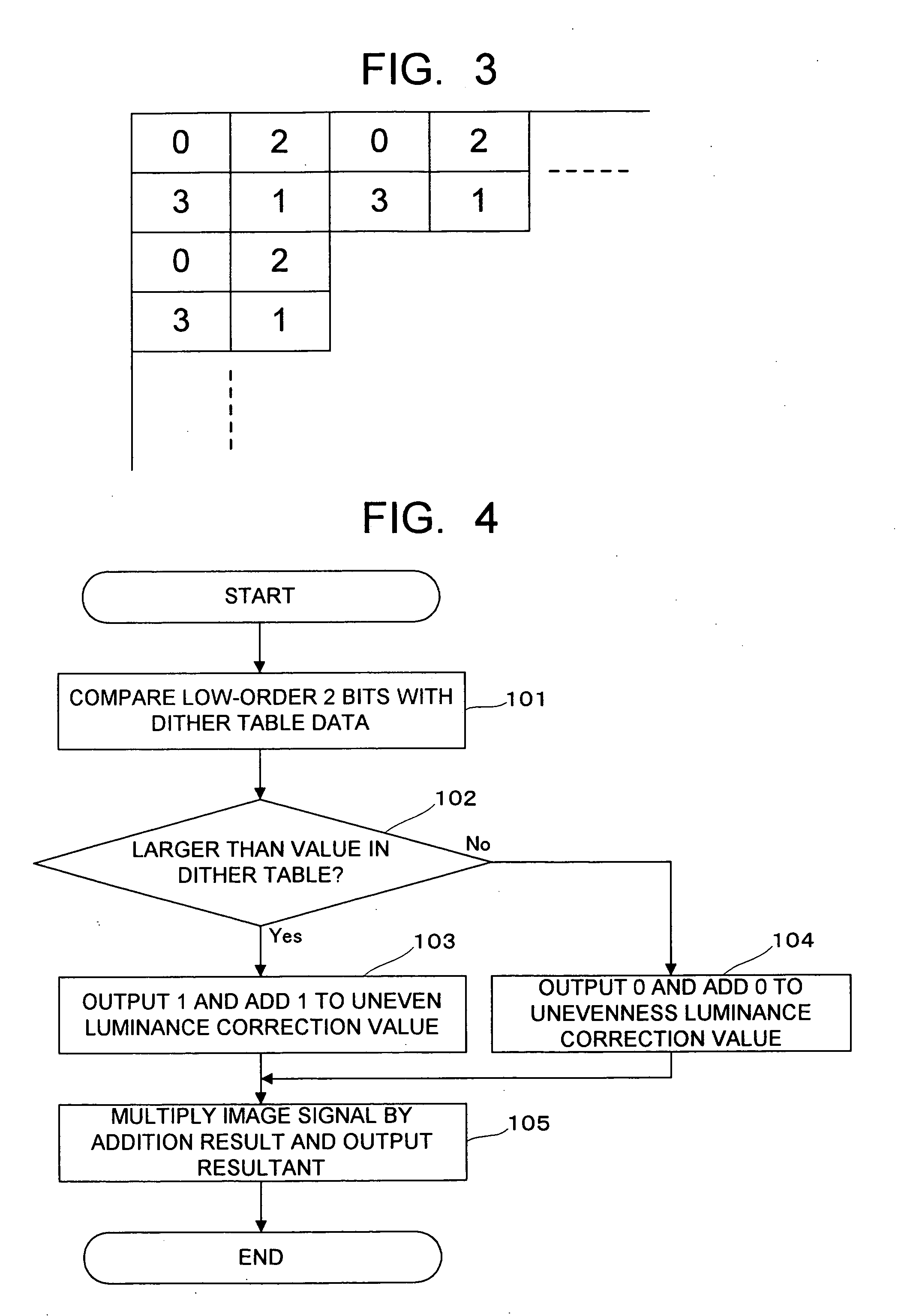

Image display device and image signal processing device

InactiveUS20060066643A1Cathode-ray tube indicatorsInput/output processes for data processing12-bitComputer science

A judging unit compares data in a dither table for each display pixel with a numerical value of low-order 2 bits of an input signal (12 bits) and outputs 1 to an adder when the numerical value of the low-order 2 bits of the input signal is larger than the data in the dither table, while outputting 0 to the adder in other cases. The adder adds the value outputted from the judging unit to an uneven luminance correction value read from a correction memory, so that the uneven luminance correction value is corrected. A multiplier multiplies the input signal by the uneven luminance correction value after the correction.

Owner:KK TOSHIBA

Transmission apparatus, transmission method, reception apparatus, reception method and signal transmission system

InactiveUS20110205428A1Improve conveniencePicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanning12-bitComputer science

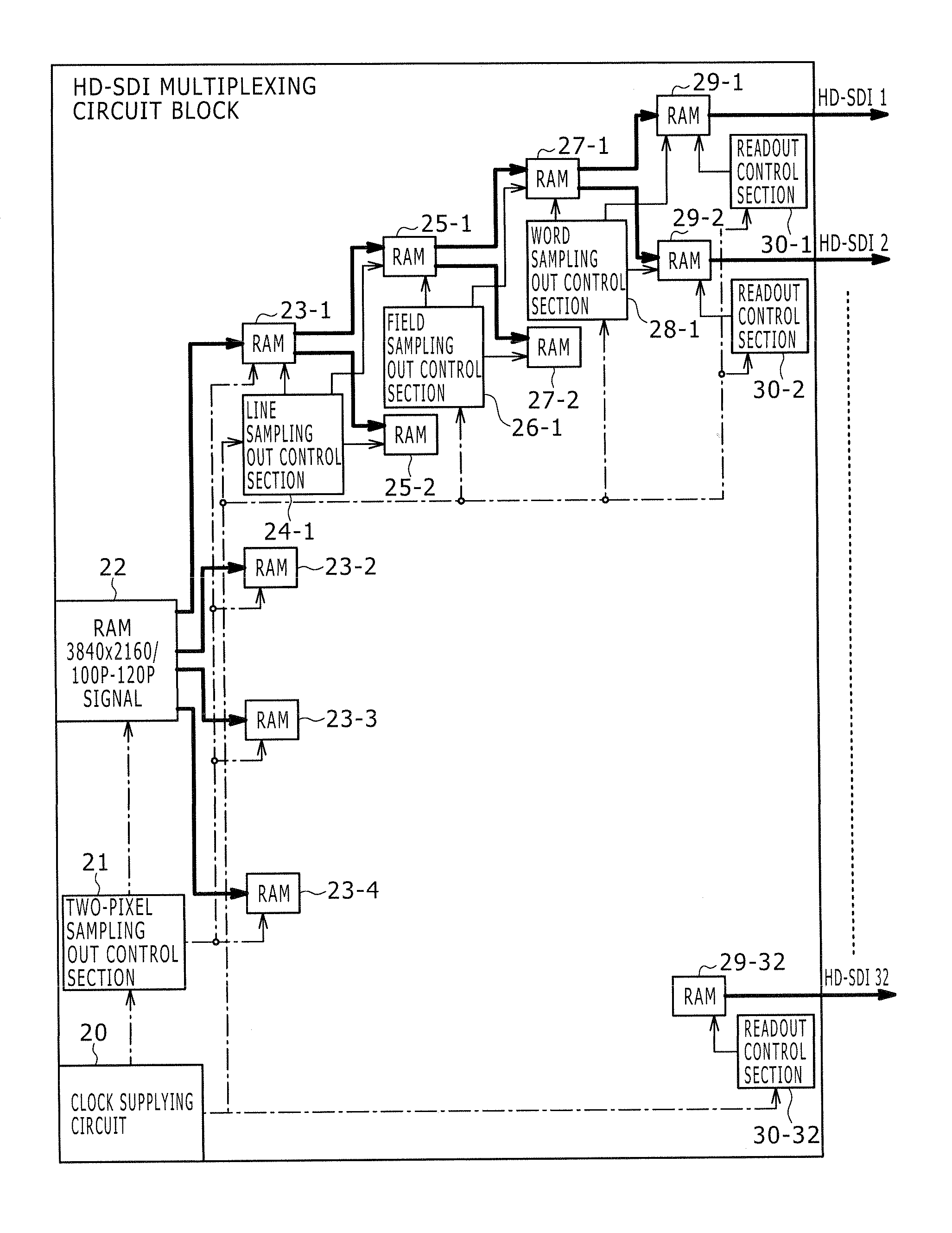

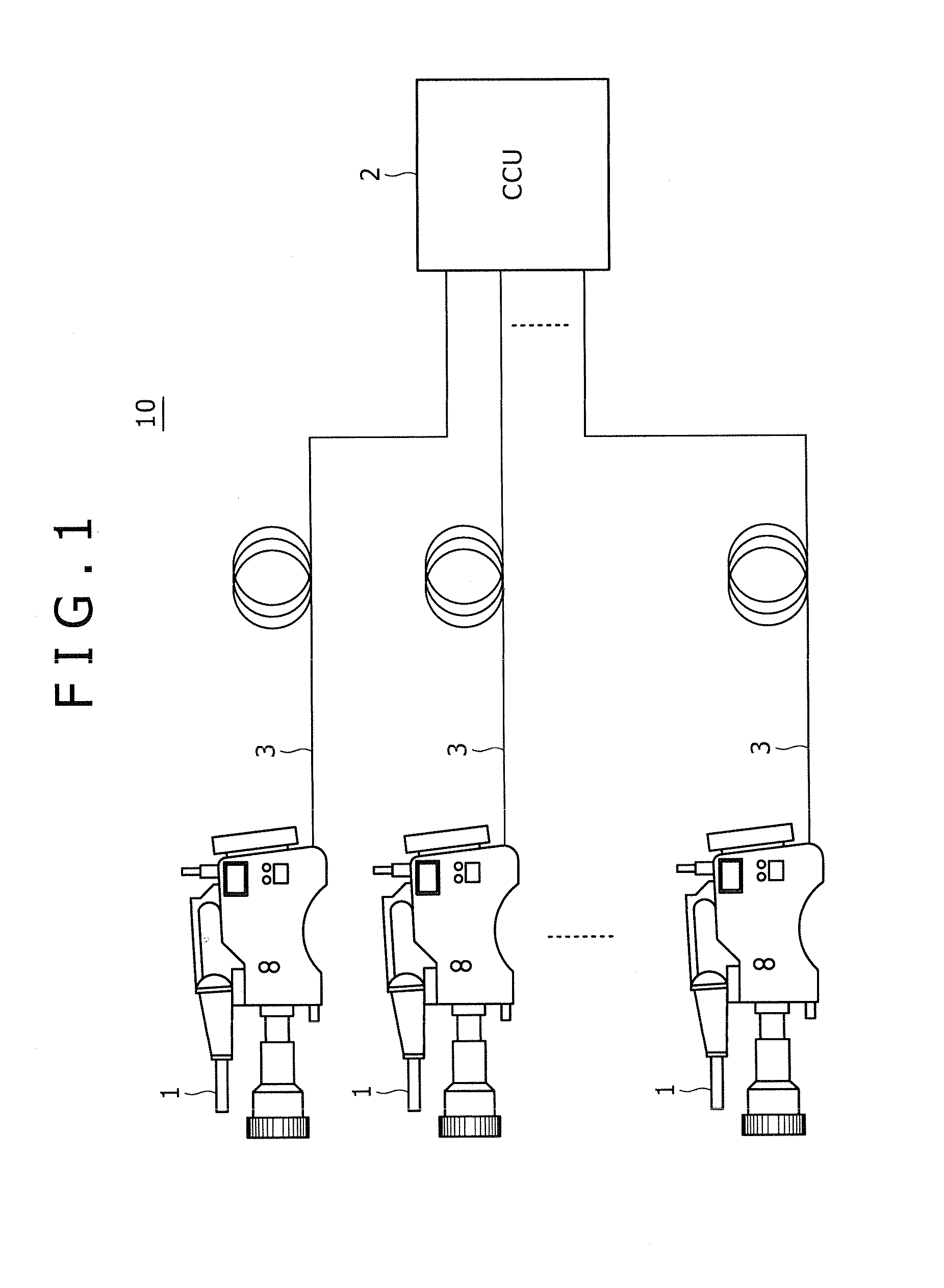

Disclosed herein is a signal transmission apparatus, including: a two-pixel sampling out control section adapted to sample out, from among pixel samples extracted from a class image defined by a 3840×2160 / 100P, 119.88P, 120P / 4:4:4, 4:2:2, 4:2:0 / 10-bit, 12-bit signal of the UHDTV1 wherein the pixel number of one frame exceeds a pixel number prescribed by the HD-SDI format, two pixel samples adjacent each other on the same line such that the pixel samples on each odd-numbered line of each frame are sampled out to a first sub image and a second sub image from among first to fourth sub images and the pixel samples on each even-numbered line of each frame are sampled out to the third sub image and the fourth sub image; a line sampling out control section; a field sampling out control section; a word sampling out control section; and a readout control section.

Owner:SONY CORP

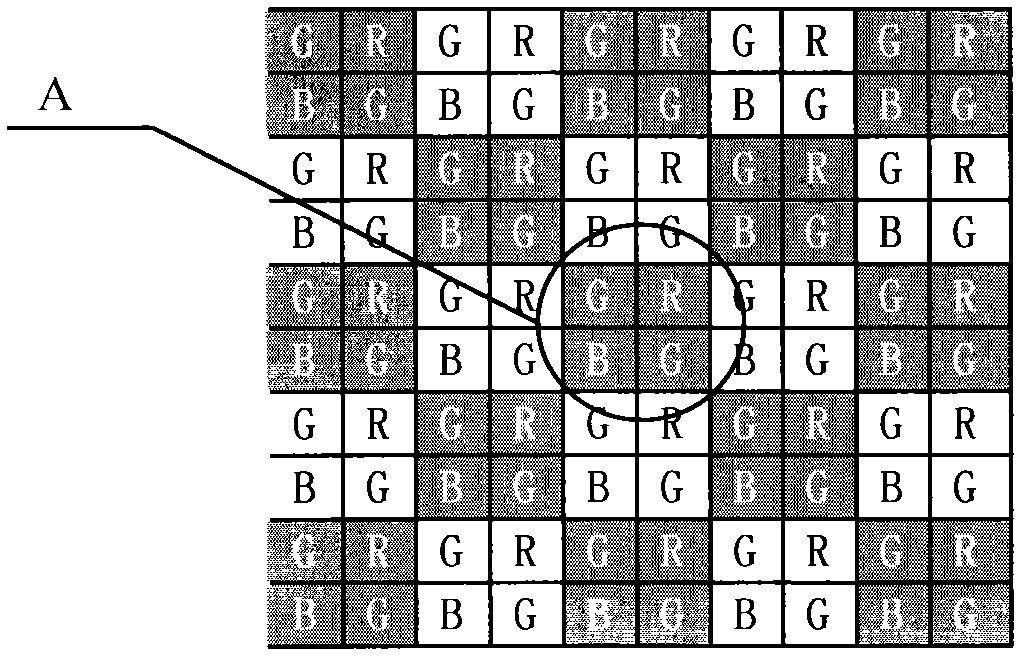

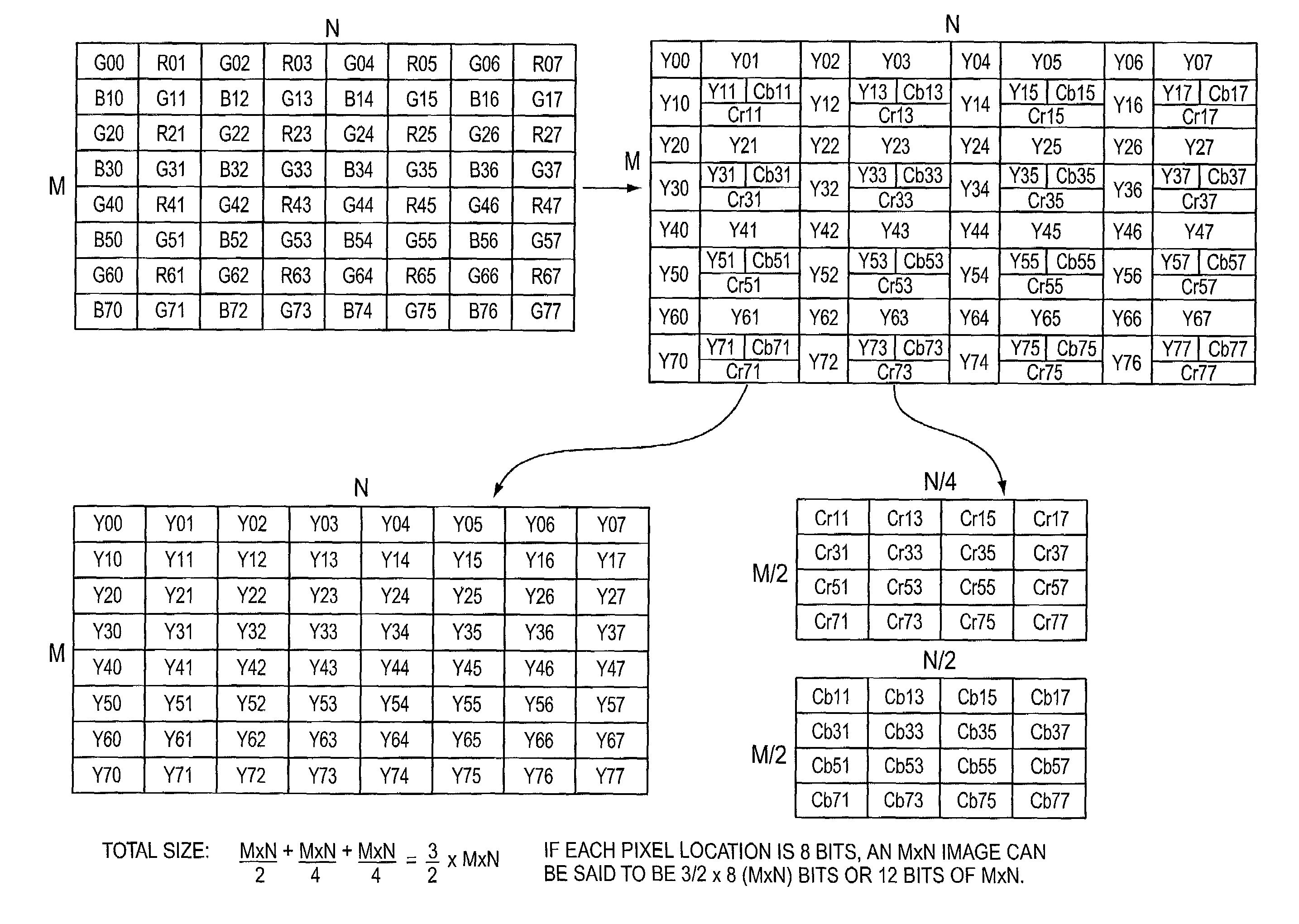

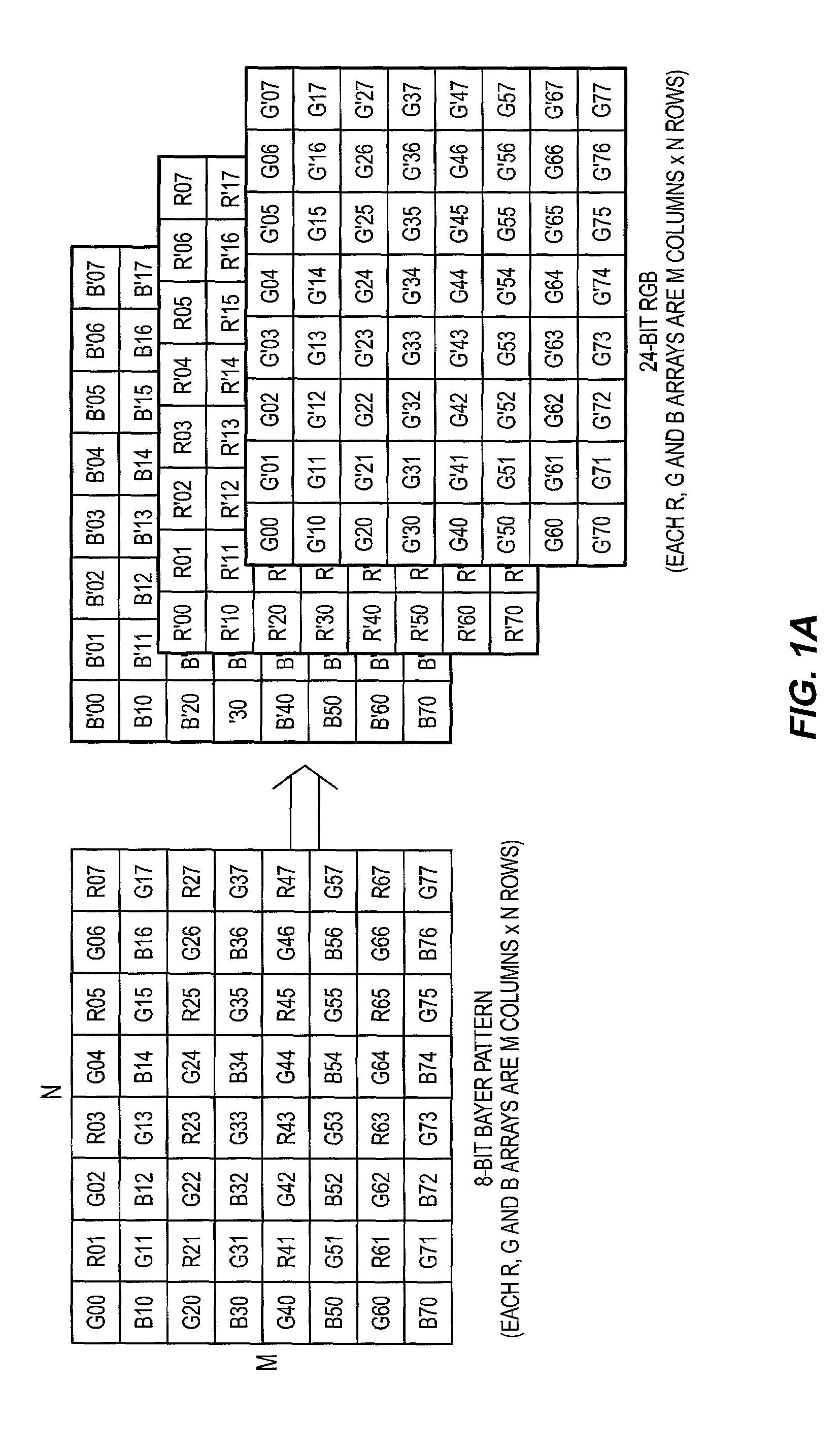

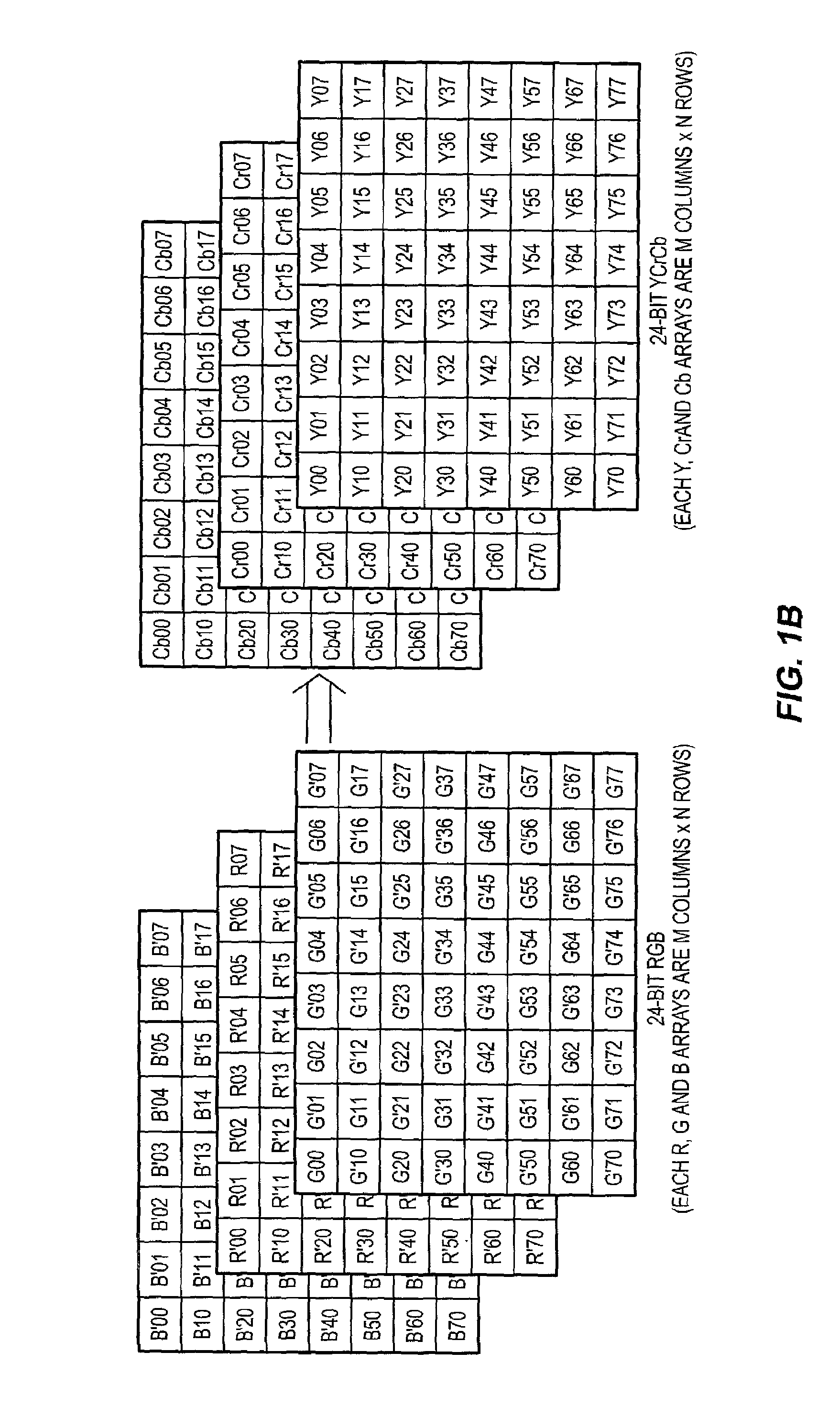

Integrated color interpolation and color space conversion algorithm from 8-bit Bayer pattern RGB color space to 12-bit YCrCb color space

InactiveUS7015962B2Television system detailsColor signal processing circuitsImage resolutionColor interpolation

An integrated color interpolation and color space conversion technique and apparatus. A raw image that is arranged in a Bayer pattern where each pixel has only one of the color components needed to form a full color resolution pixel may be converted using this technique directly to a YCrCb image space without any intermediate conversion or interpolation steps. Specifically, in one instance, an 8-bit Bayer pattern raw image may be converted directly to a 12-bit YCrCb space in a single step approach. Such an integrated technique may more readily and inexpensively implemented in hardware such as on a digital camera, or in software.

Owner:INTEL CORP

Method and system for providing long and short block length low density parity check (LDPC) codes

ActiveUS20080065972A1Low ParityMinimize resourceError preventionError correction/detection using multiple parity bitsDigital videoLow density

An approach is provided for generating Low Density Parity Check (LDPC) codes. An LDPC encoder generates a LDPC code with an outer Bose Chaudhuri Hocquenghem (BCH) code. For ⅓ rate, the relevant parameters are as follows: q=120, nldpc=64,800, kldpc=nBCH=21600, kBCH=21408 (12 bit error correcting BCH). For ¼ rate, the LDPC code has the following relevant parameters: q=135, nldpc=64,800, kldpc=nBCH=16200, kBCH=16008 (12 bit error correcting BCH). For ⅖ rate, the following parameters exist: q=108, nldpc=64800, kldpc=nBCH=25920, kBCH=25728 (12 bit error correcting BCH). The above approach has particular application in digital video broadcast services over satellite.

Owner:DTVG LICENSING INC

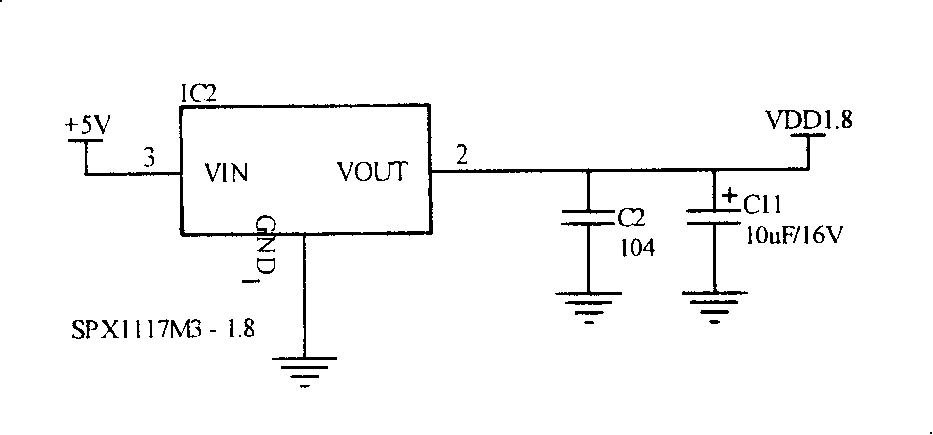

Device for monitoring stray current of novel subway

InactiveCN101226682ARealize the function of online automatic monitoringImprove accuracyElectric signal transmission systemsElectrical batteryHardware modules

Novel subway stray current automatic monitoring system comprises that a plurality of stray current online automatic monitoring devices which are utilized as local monitoring slave machines are connected with a remote monitoring main machine. A switch power module, a data collecting module, an Ethernet communication module, an auxiliary hardware module and a man-machine interactive module are arranged on the same PCB printing circuit board around the processor of the system. The switch power module is internally-equipped with an EMC filter with high-performance. A / D transformation circuit employs bipolar and 12 bit A / D transducer MAX197 which is internally equipped with 8 ways sample-taking passages. The auxiliary hardware module comprises an EEPROM secondary permanent storage module, a hardware watchdog circuit, a self-contained battery calendar clock module and a serial port communication interface circuit. The invention simplifies the structure of the system, enables data sharing, information fusion and synergic observation among slave machines, which greatly strengthens the accuracy and tightness of the monitoring of the stray current, additionally, the cost of the monitoring device is reduced.

Owner:TONGJI UNIV