Patents

Literature

46 results about "18-bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, 18-bit integers, memory addresses, or other data units are those that are 18 bits (2.25 octets) wide. Also, 18-bit CPU and ALU architectures are those that are based on registers, address buses, or data buses of that size.

Integrated electronic sensor

ActiveUS20050218465A1Increase productionTransistorSemiconductor/solid-state device detailsMicrocontrollerLine sensor

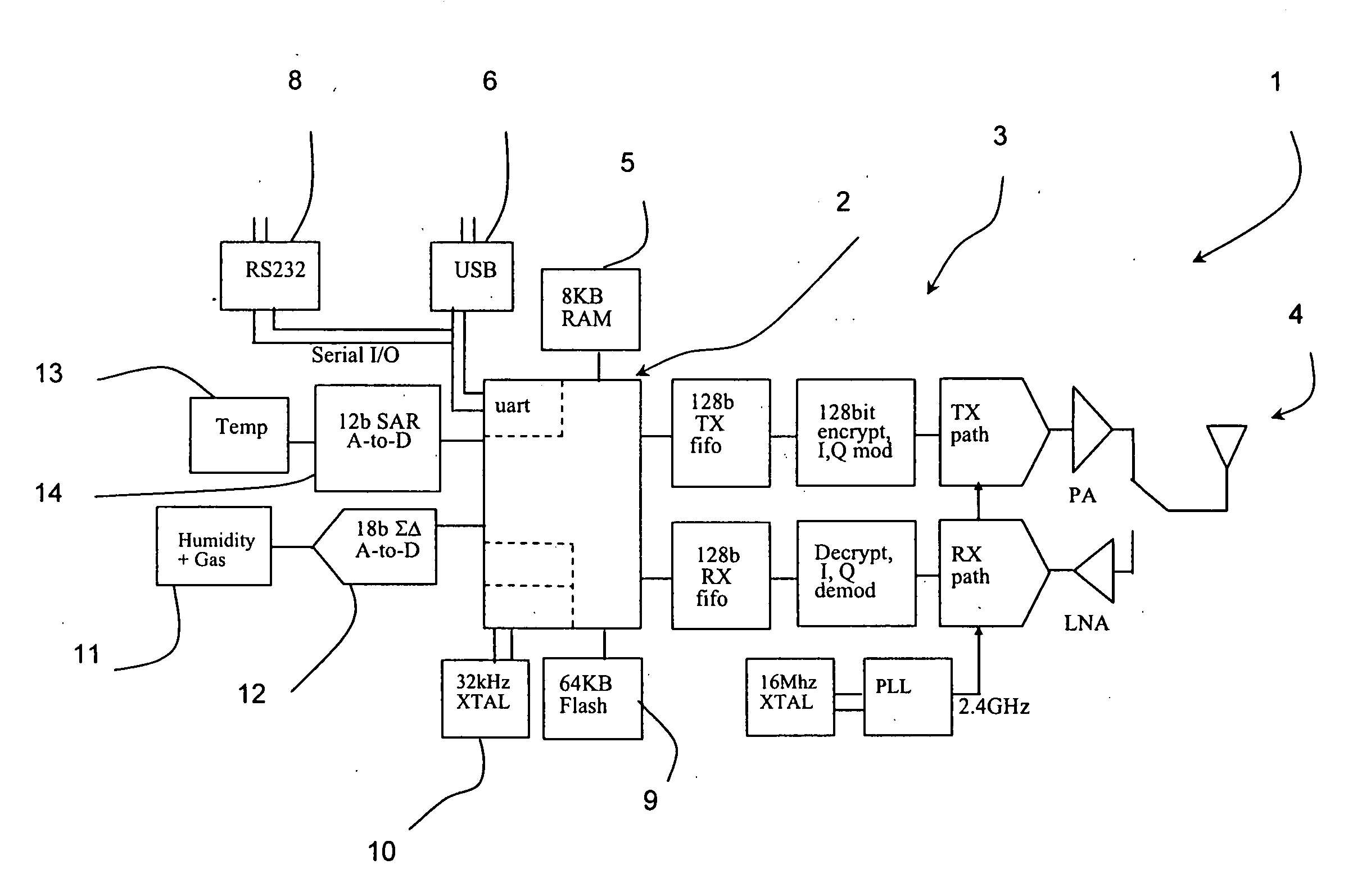

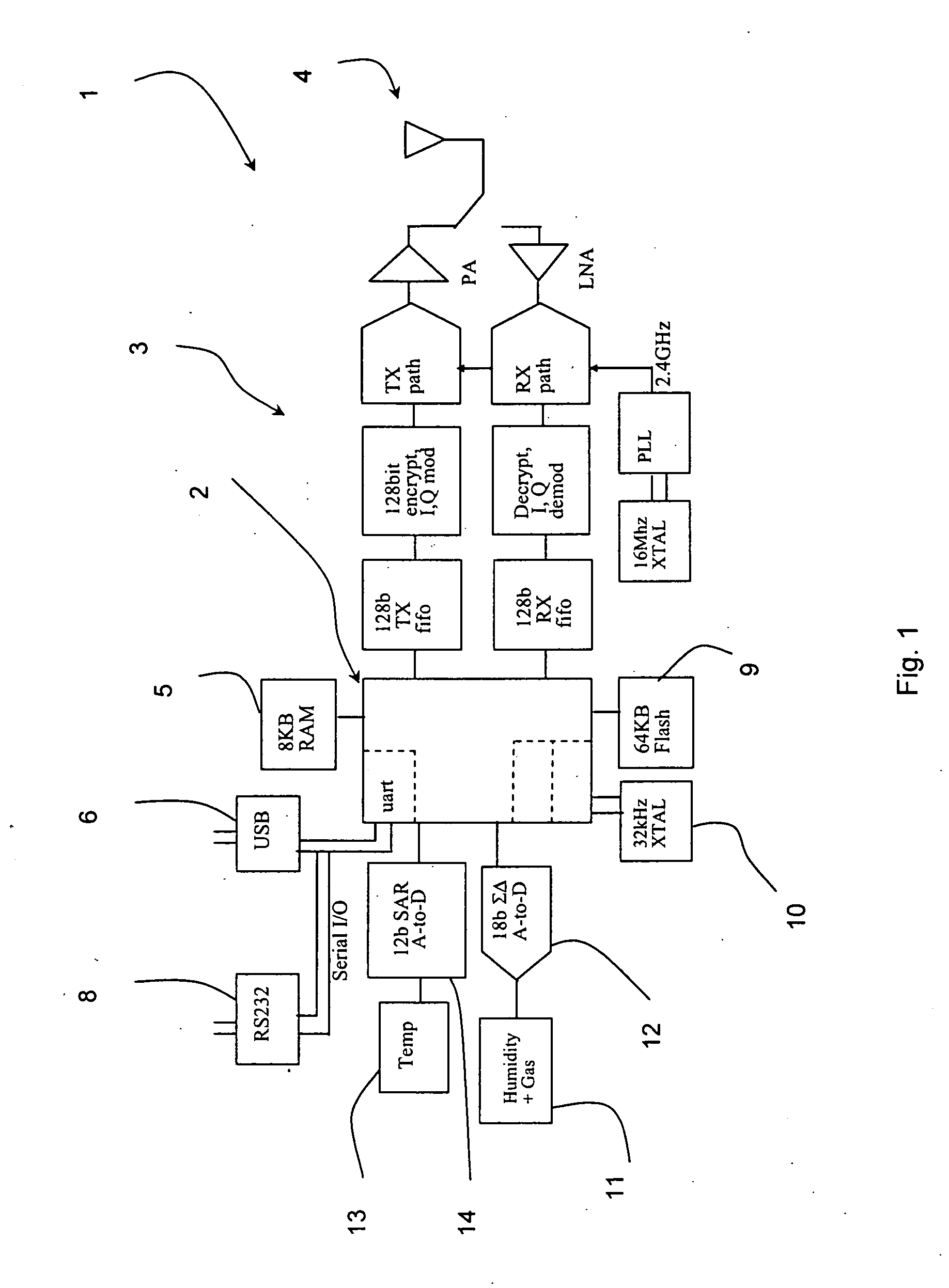

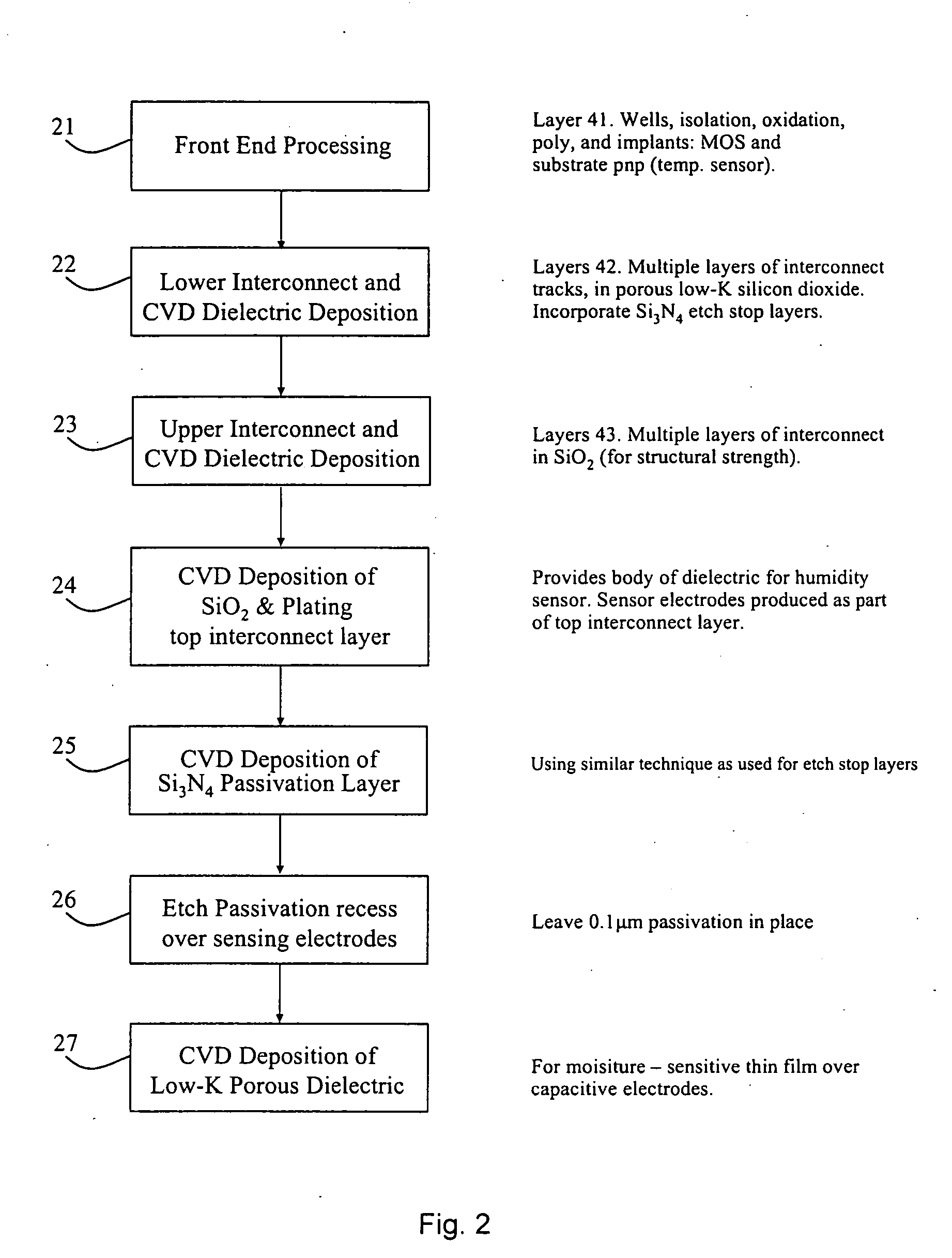

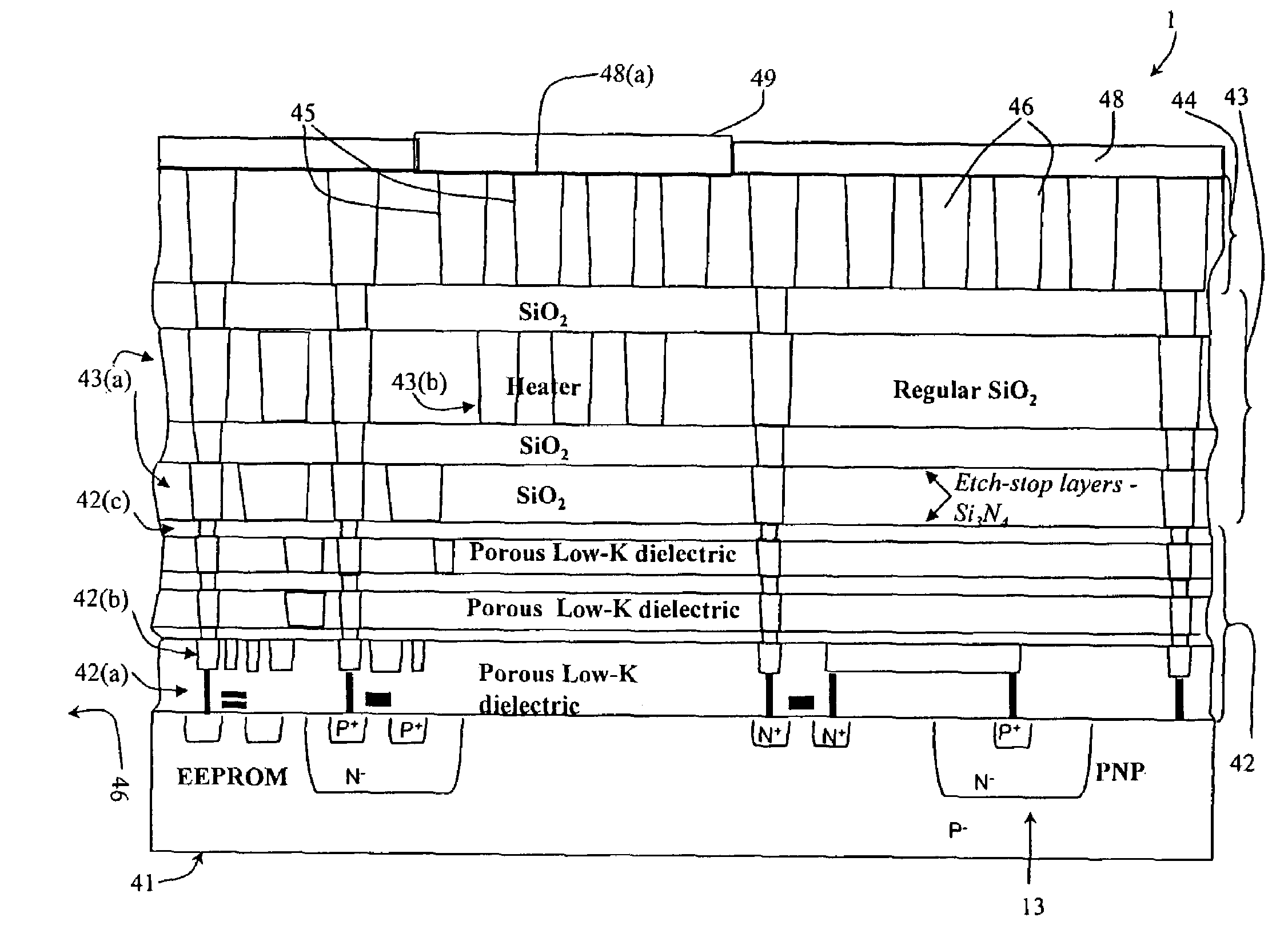

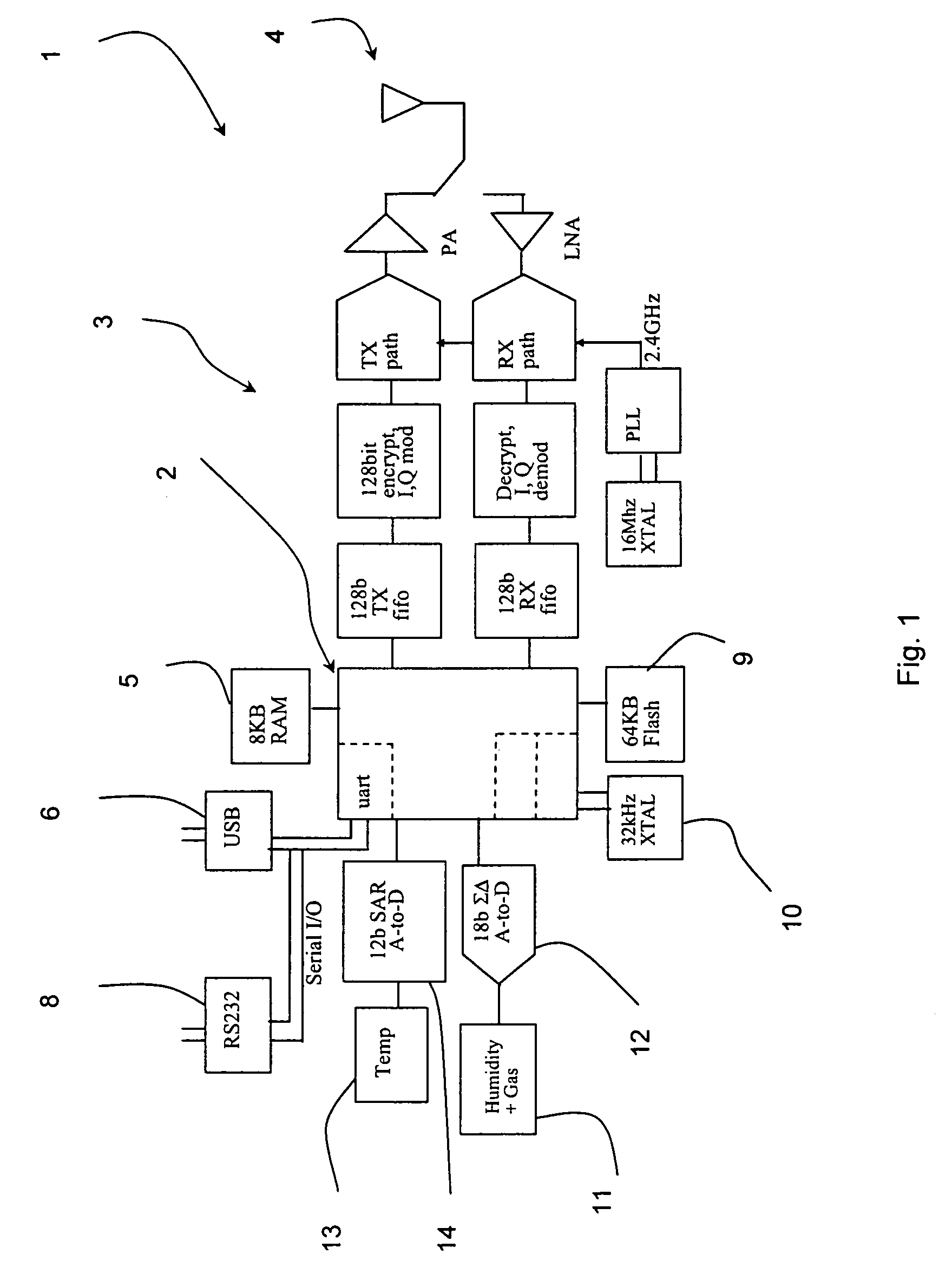

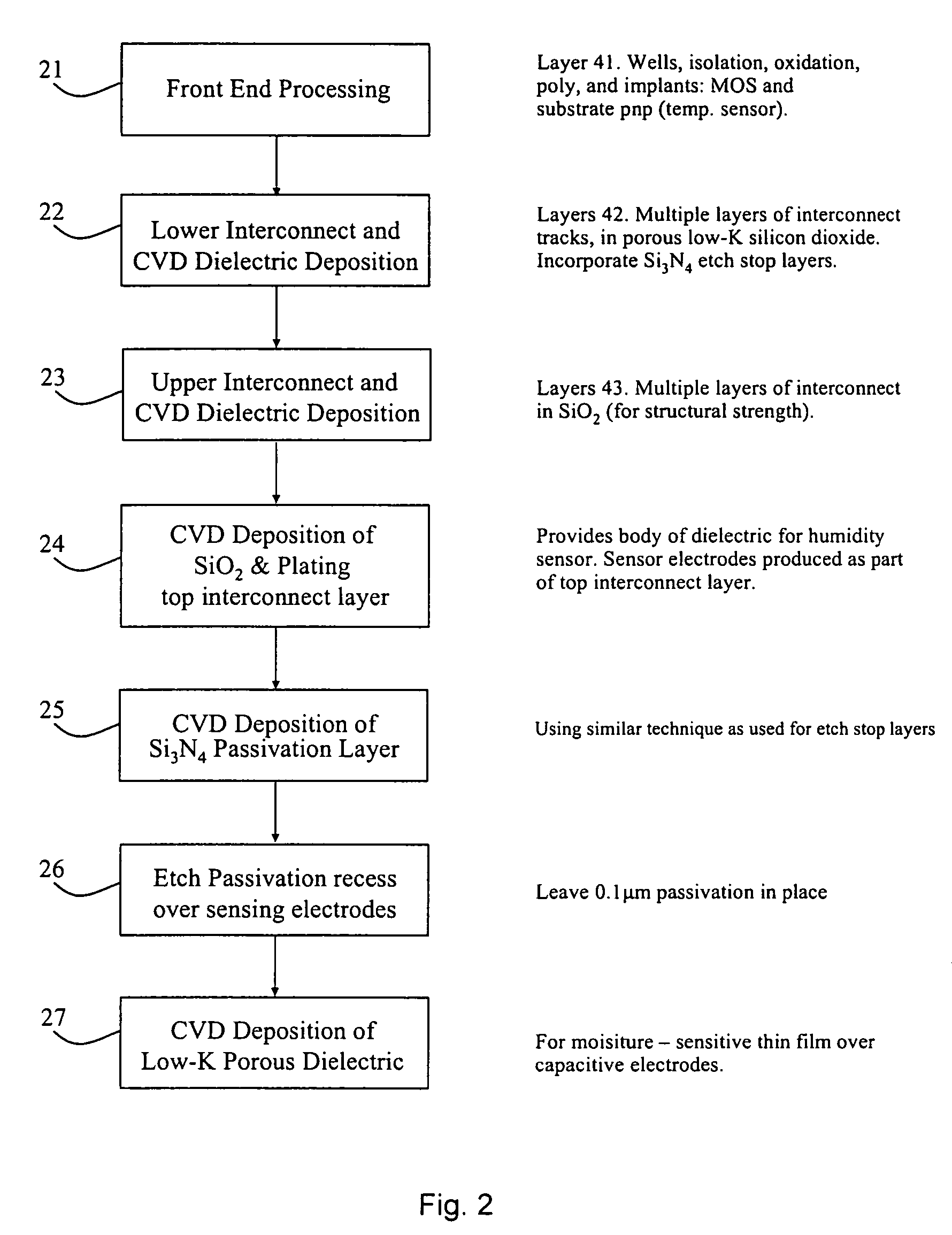

A single chip wireless sensor (1) comprises a microcontroller (2) connected by a transmit / receive interface (3) to a wireless antenna (4). The microcontroller (2) is also connected to an 8 kB RAM (5), a USB interface (6), an RS232 interface (8), 64kB flash memory (9), and a 32 kHz crystal (10). The device (1) senses humidity and temperature, and a humidity sensor (11) is connected by an 18 bit ΣΔ A-to-D converter (12) to the microcontroller (2) and a temperature sensor (13) is connected by a 12 bit SAR A-to-D converter (14) to the microcontroller (2). The device (1) is an integrated chip manufactured in a single process in which both the electronics and sensor components are manufactured using standard CMOS processing techniques, applied to achieve both electronic and sensing components in an integrated process.

Owner:SILICON LAB INC

Integrated CMOS porous sensor

ActiveUS7554134B2Increase productionTransistorSemiconductor/solid-state device details18-bitMicrocontroller

A single chip wireless sensor (1) comprises a microcontroller (2) connected by a transmit / receive interface (3) to a wireless antenna (4). The microcontroller (2) is also connected to an 8 kB RAM (5), a USB interface (6), an RS232 interface (8), 64 kB flash memory (9), and a 32 kHz crystal (10). The device (1) senses humidity and temperature, and a humidity sensor (11) is connected by an 18 bit ΣΔ A-to-D converter (12) to the microcontroller (2) and a temperature sensor (13) is connected by a 12 bit SAR A-to-D converter (14) to the microcontroller (2). The device (1) is an integrated chip manufactured in a single process in which both the electronics and sensor components are manufactured using standard CMOS processing techniques, applied to achieve both electronic and sensing components in an integrated process.

Owner:SILICON LAB INC

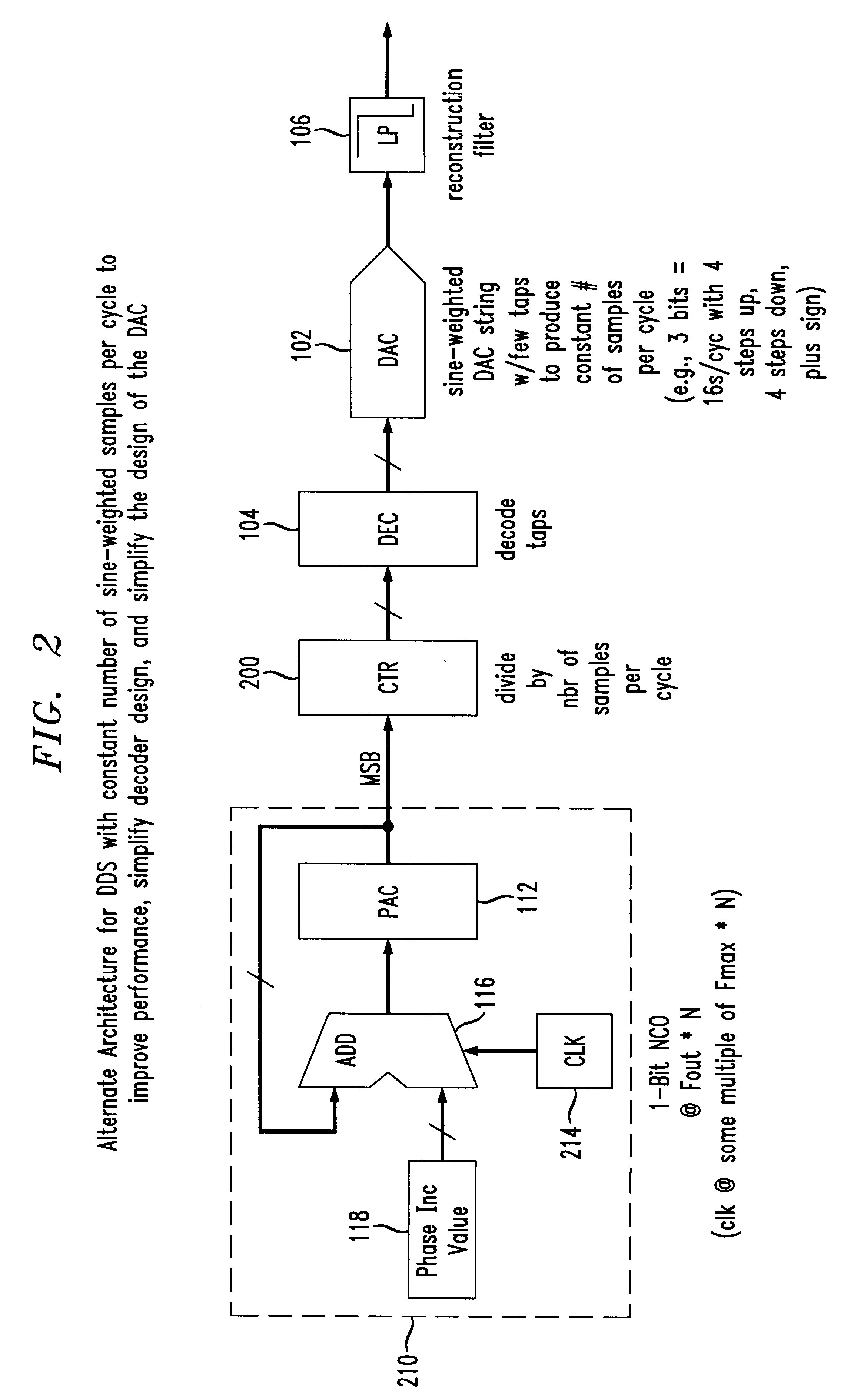

Direct digital synthesis using a sine weighted DAC

InactiveUS6281823B1Electric signal transmission systemsPulse automatic control18-bitImage resolution

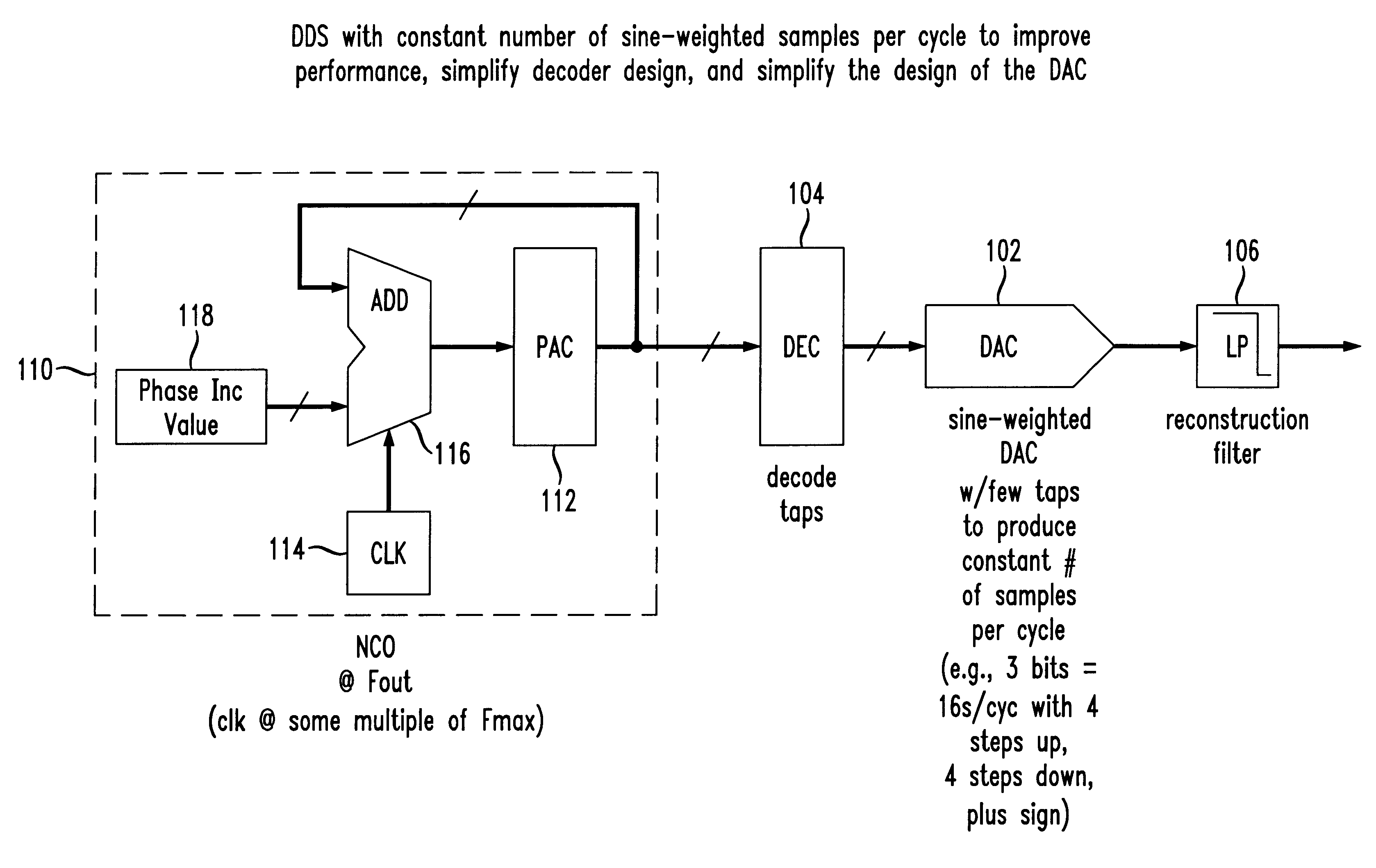

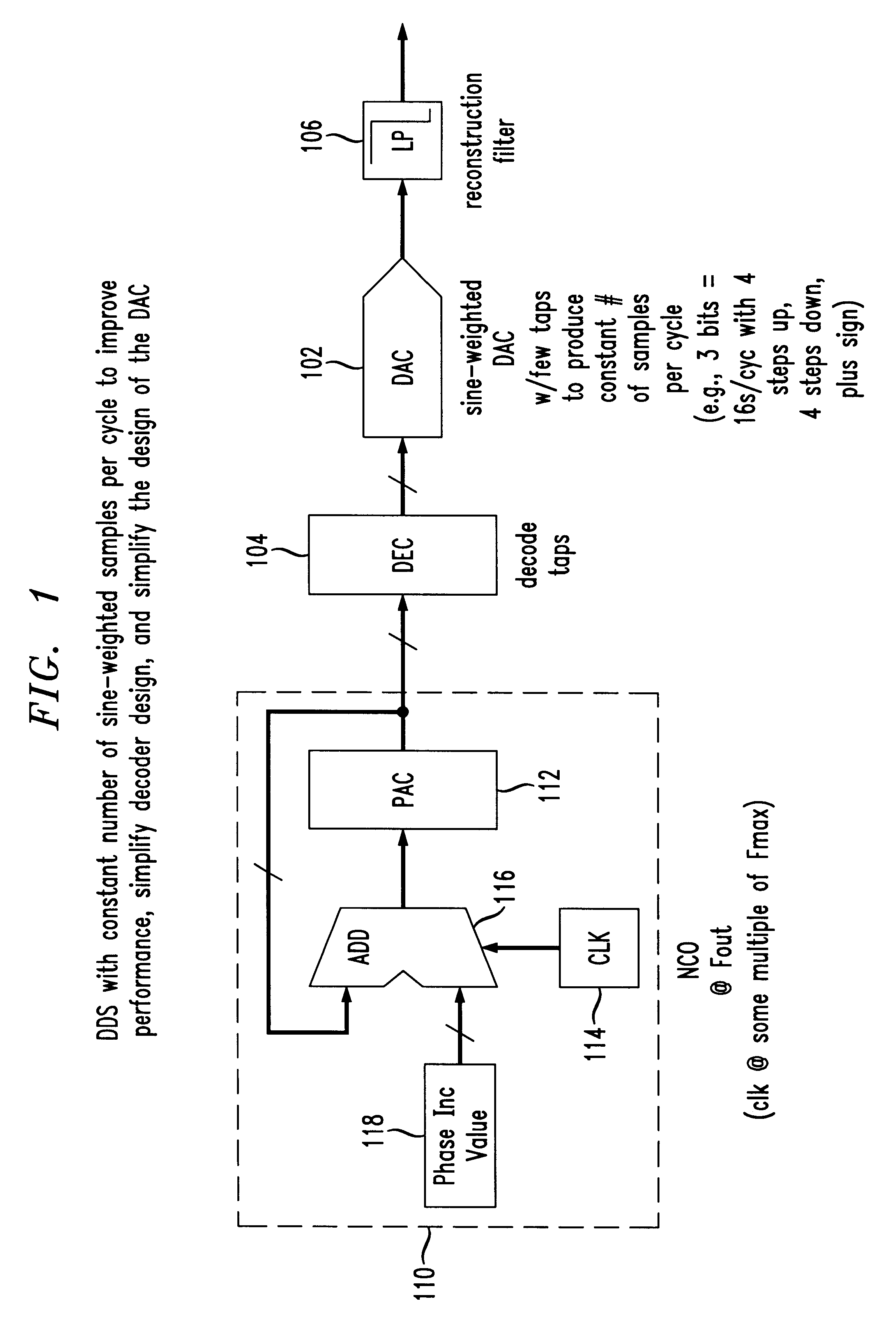

The present invention provides a novel direct digital synthesis system architecture which employs a numerically-controlled oscillator (NCO), some decoding logic, and a sine-weighted digital-to-analog converter (DAC) with significantly fewer output values required than conventional DDS systems to provide improved spurious performance (relative to the number of bits of resolution required of the DAC), extended frequency of operation, reduced chip area, and reduced power consumption relative to conventional DDS techniques. The output of the decoder is input to a sine-weighted digital-to-analog converter (DAC). Importantly, the sine-weighted DAC outputs a constant number of samples per cycle using a relatively few number of taps. Although there are significantly fewer taps in the sine-weighted DAC as compared to the linear DAC in conventional DDS systems, each tap of the sine-weighted DAC has a high degree of accuracy, e.g., 16-18 bits. Accordingly, a constant number of sample values are repetitively used in the stepped approximation of a sine wave, regardless of output frequency, significantly reducing the number of discrete output values that a digital-to-analog converter (DAC) is otherwise required to produce. Unlike conventional direct digital synthesis (DDS) architectures which use linear digital-to-analog converters having many bits of resolution, the present invention provides a sine-weighted digital-to-analog converter having relatively few taps to produce a constant number of samples per cycle, eliminating the conventional need for a memory-based sine wave look-up table.

Owner:LUCENT TECH INC

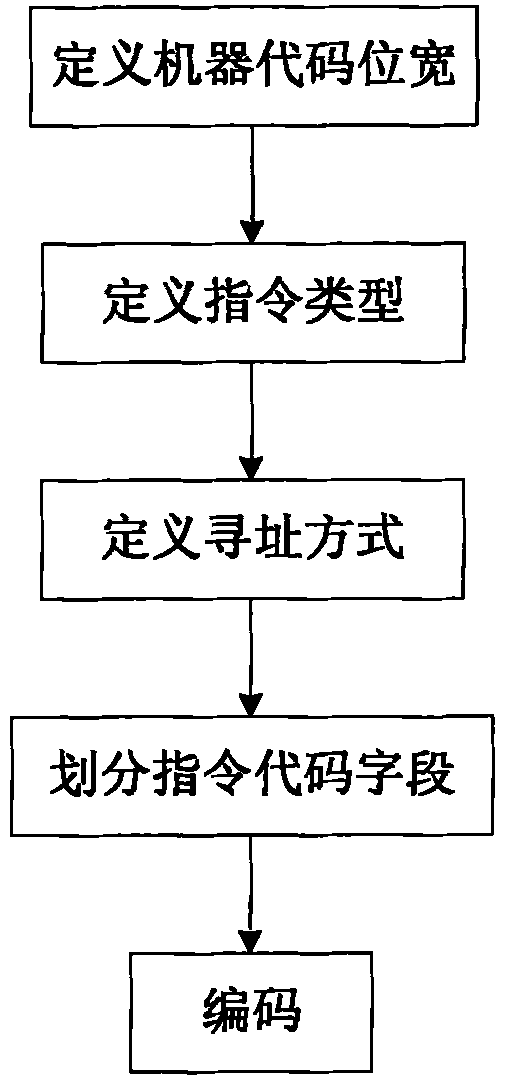

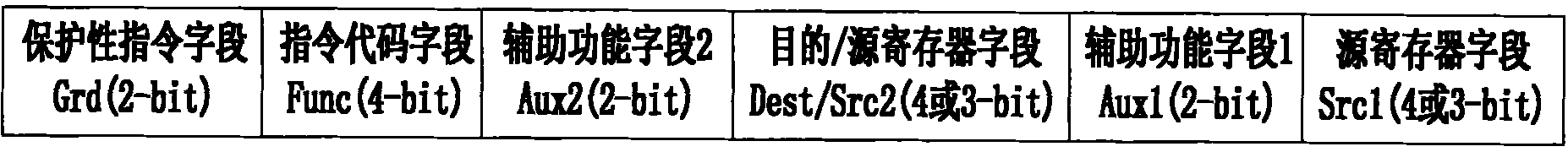

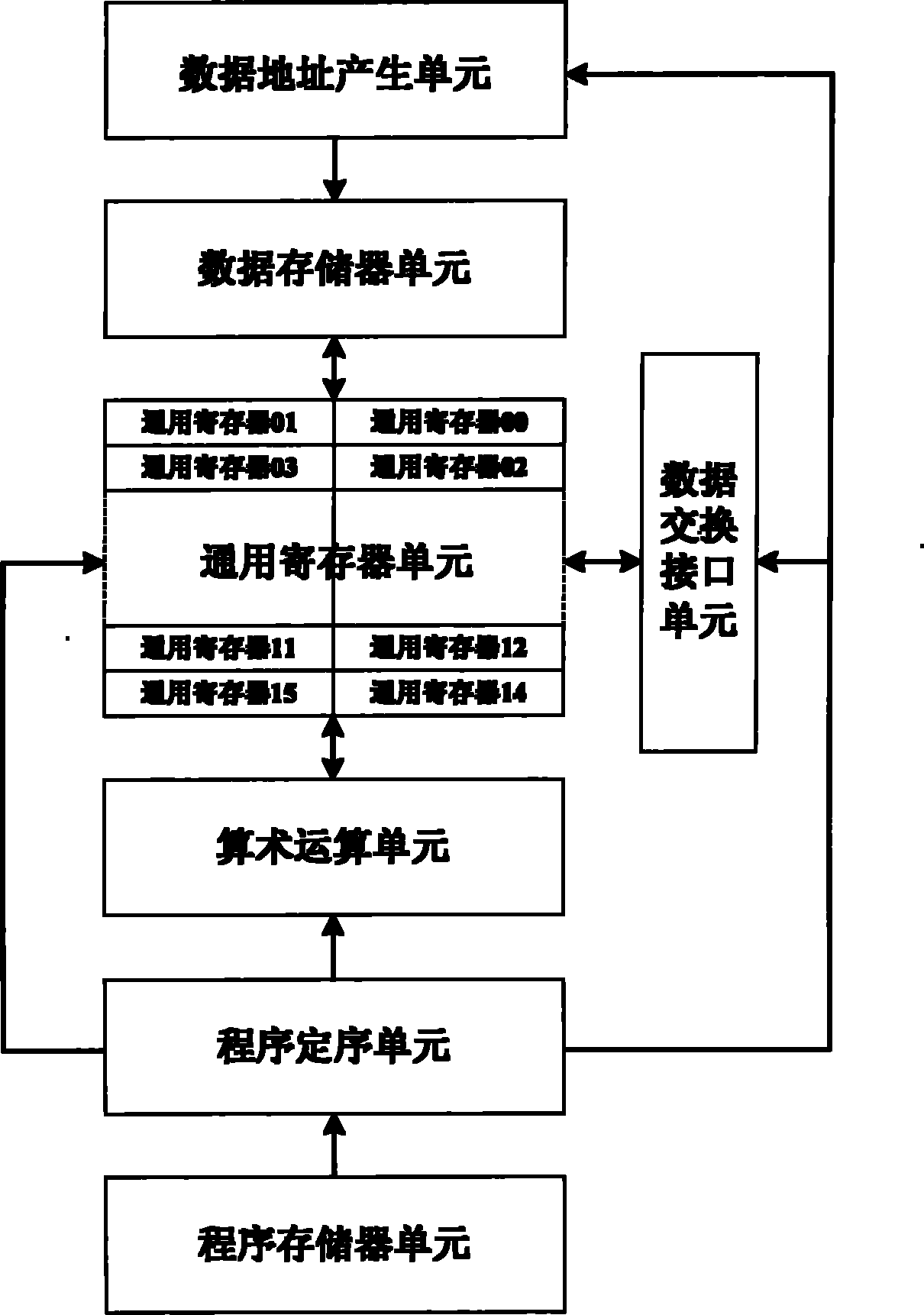

Instruction set encoding method based on embedded special instruction set processor

ActiveCN102221987AImprove utilization efficiencyGuaranteed uptimeConcurrent instruction execution18-bitInternal memory

The invention provides an instruction set encoding method based on an embedded special instruction set processor, comprising five steps of: defining machine code bit wide, defining instruction type, a defining addressing mode, a dividing instruction code filed and encoding. The instruction set is optimized according to the characteristic that both an internal memory and a data bus resource of a Field Programmable Gate Array (FPGA) take 18 bits as basic bit wide. The instruction set comprises 16 pieces of multifunctional instructions in the types of arithmetic and logic operation, data interchange and program sequencing, wherein the instructions comprise protective instruction fields required for constructing a single instruction stream-multiple data stream concurrent processing system with instruction independency capability. The instruction set disclosed by the invention has integral and simplified application models; under the two application models, the code length of an instruction machine can be respectively shortened to 16-bit and 14-bit so that the utilization efficiency of an internal circuit resource of the FPGA and the instruction execution speed of a processor are greatly improved.

Owner:XIDIAN UNIV

Quasi-lossless image compression and decompression method of wireless endoscope system

The invention belongs to field of medical digital picture compression technique, which is a picture compression and decompression method based on compression first and color interpolation later, removing the high-frequency component of the picture with low-pass filter before compression, controlling the filtered wave picture dot percentage of the whole picture with mass controlling factor to improve the picture quality, determining the pixel area directly for coding without compression with interesting area to guarantee the picture quality in interesting area. The compression without damage is coded with JPEG-LS compression. The hardware diagram is relatively provided. Compressing the seven natural picture in the standard picture database for experiment, realizing the continuously adjustment of signal-to-noise ratio from 46.37 dB to infinity, the relevant compression rate changing in range of from 3.3 bit / pixel point to 6.9 bit / pixel point; if compressing the wireless endoscope picture, we can get the average picture compression rate of 2.18 bit / pixel point and PSNR larger than 47.57dB.

Owner:TSINGHUA UNIV

Methods and apparatus for constant-weight encoding and decoding

InactiveUS6844833B2Lower latencyError correction/detection using convolutional codesOther decoding techniques18-bitDriver circuit

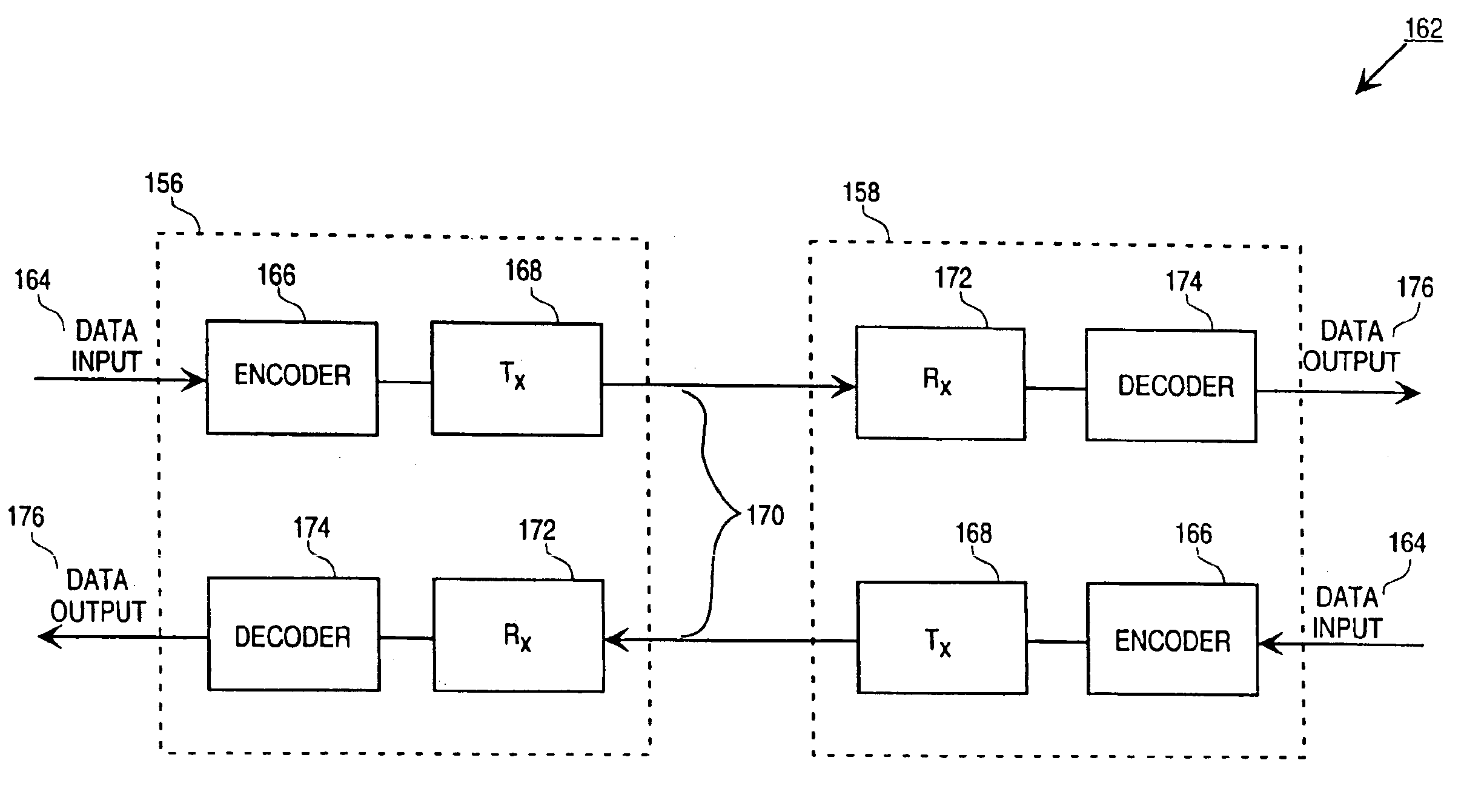

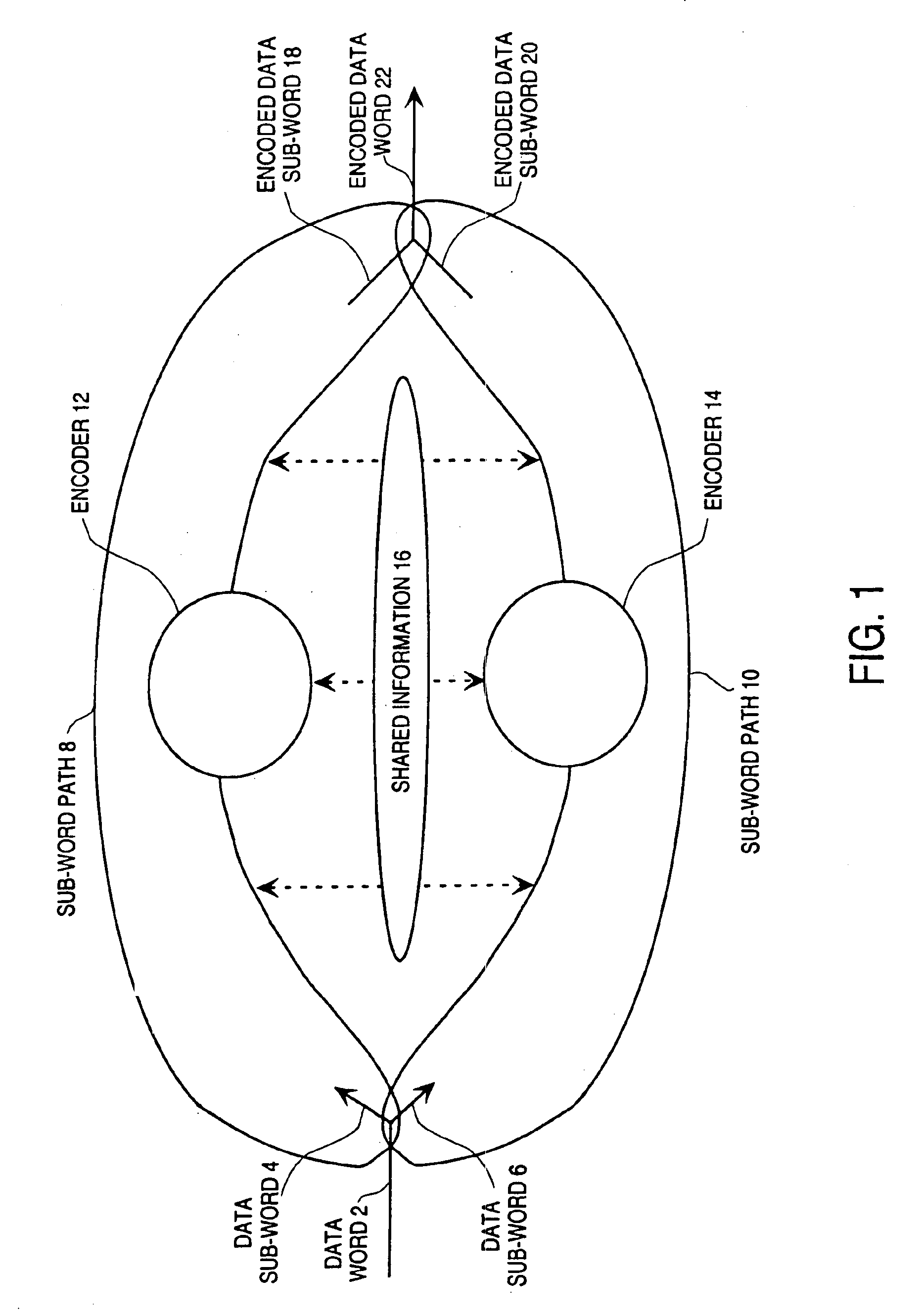

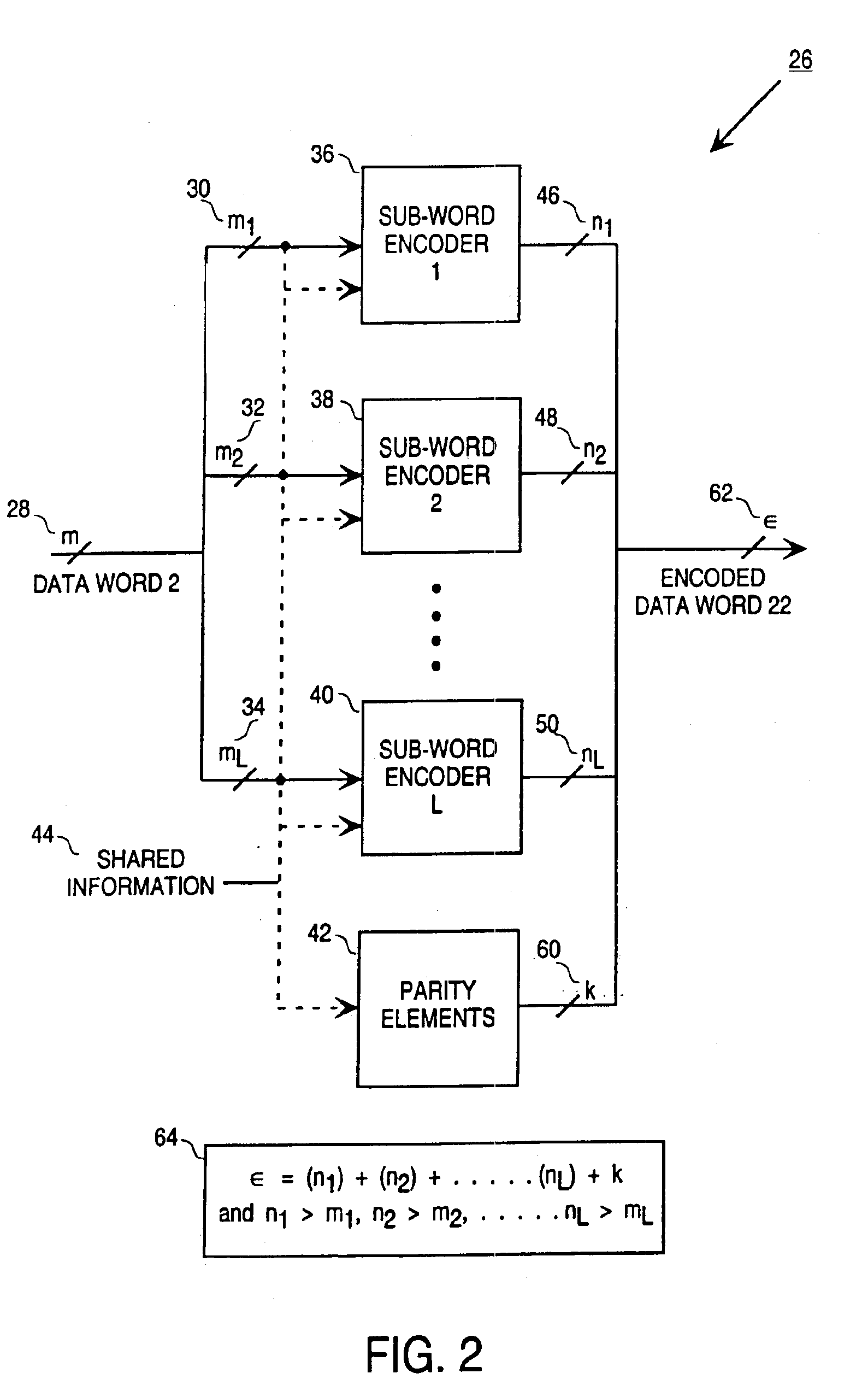

Methods and apparatus for spreading and concentrating information to constant-weight encode of data words on a parallel data line bus while allowing communication of information across sub-word paths. In one embodiment, data transfer rates previously obtained only with differential architectures are achieved by only a small increase in line count above single ended architectures. For example, an 18-bit data word requires 22 encoded data lines for transmission, where previously, 16 and 32 lines would be required to transmit un-coded data with single-ended and differential architectures respectively. Constant-weight parallel encoding maintains constant current in the parallel-encoded data lines and the high and low potential driver circuits for the signal lines.

Owner:APPLE INC

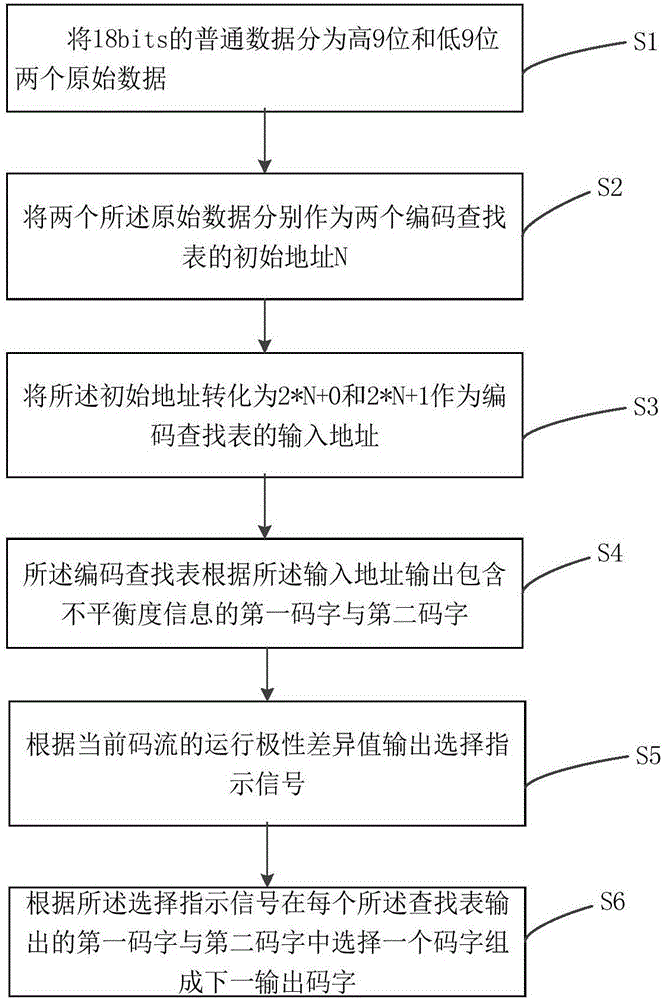

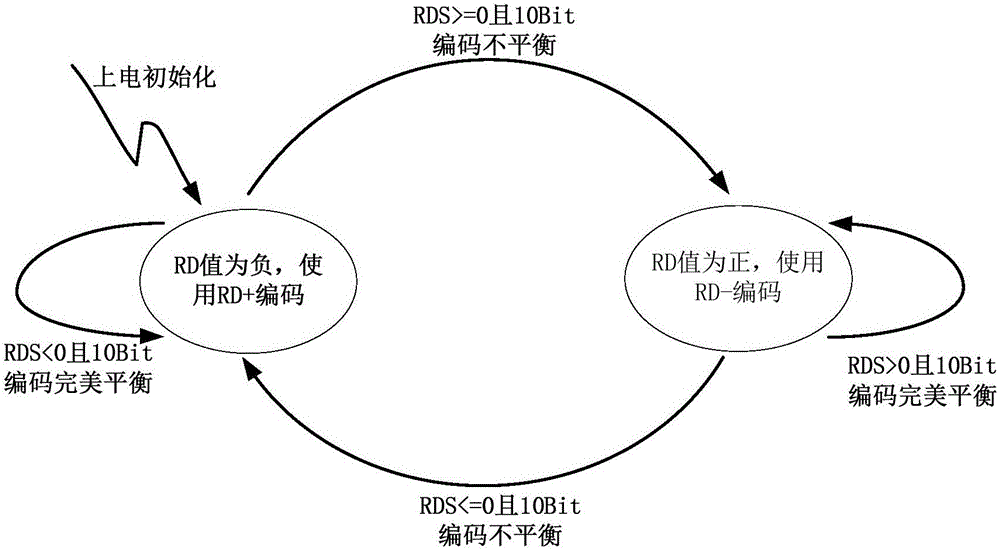

Encoding and decoding method and device of serial communication system based on SerDes technology

InactiveCN106411322AGood DC balanceImprove transmission performanceCode conversion18-bitOriginal data

The present invention provides an encoding and decoding method and device of a serial communication system based on the SerDes technology. The method comprises an encoding step which comprises a step of dividing 18-bit common data into two 9-bit original data, a step of taking the two original data as the initial address N of two code lookup tables and converting the initial addresses N as 2*N and 2*N+1 as the input address of the code lookup table, a step of outputting a first code word and a second code word comprising imbalance information according to the input addresses, wherein the number of '1' in a first code word is larger than or equal to the number of '0', and the number of '0' in the second code word is larger than or equal to the number of '0', a step of outputting a selection indication signal according to the motion polarity difference value of a current code stream, and a step of selecting a code word from the first code word and second code word outputted by each lookup table according to the selection indication signal to form a next output code word. The encoding process of the scheme is the inverse process of encoding, and the realization method is similar to the encoding process. According to the method and the device, while the target of direct current balance of the output code stream is achieved, the transmission performance is improved.

Owner:SHENZHEN GRENTECH CORP LTD

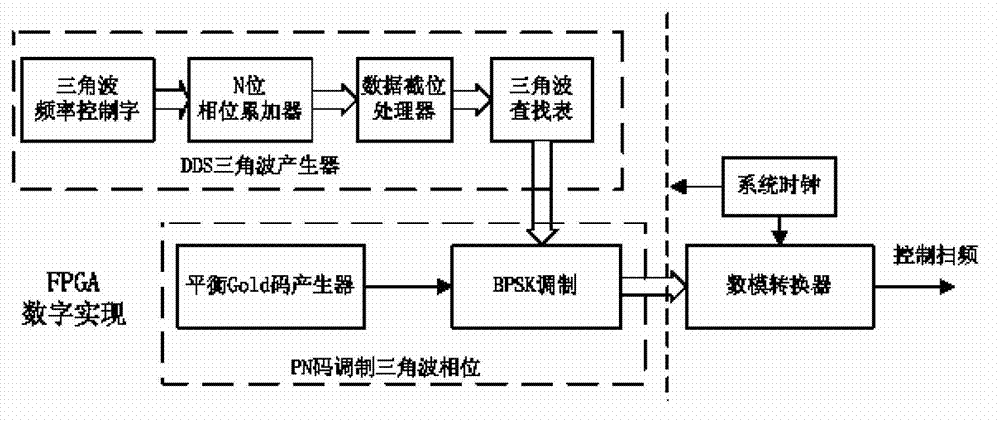

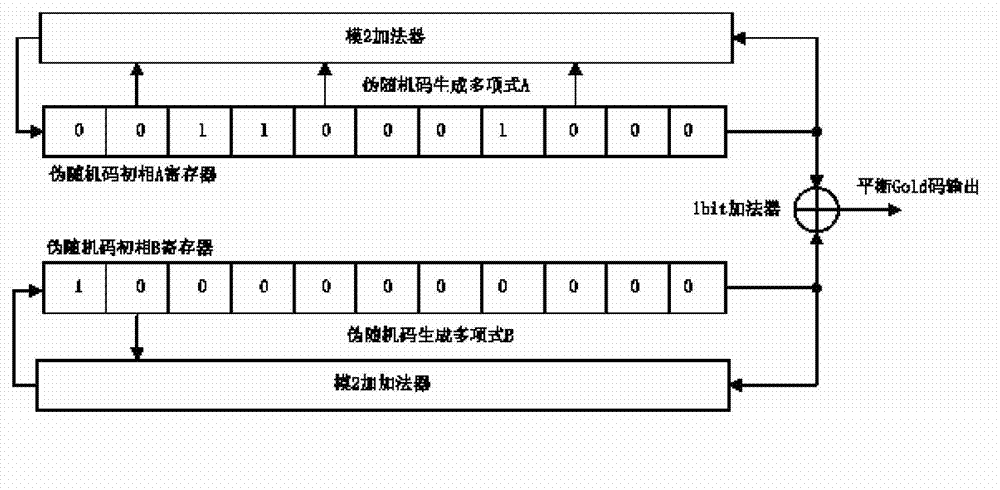

Implementation method for preventing forwarding interference of frequency modulation radio fuze

InactiveCN103095334AFlexible change of fuze action distanceIncrease lethalityTransmission18-bitInterference resistance

The invention provides an implementation method for preventing forwarding interference of a frequency modulation radio fuze and aims to provide a digitalized interference prevention fuze implementation method with which triangular wave frequency can be flexibly adjusted, fuze operating distance can be changed, and forwarding interference prevention capacity of fuze equipment can be improved. The implementation method is realized by the following technical scheme. A triangular wave generator formed by a triangular wave frequency control word, an N-bit phase accumulator, a data bit cut processor and a triangular wave phase lookup table in sequence and a BPSK (Binary Phase Shift Keying) modulator crosslinked between a balance GOLD code generator and a digital-to-analog converter are designed in a programmable gate array chip FPGA (Field Programmable Gata Array). After the triangular wave generator frequency is given, the computational formula of the triangular wave frequency control word is adopted in the DDS triangular wave generator. The calculated triangular wave frequency control word is sent to the N-bit phase accumulator to be accumulated, the lower 18 bits of the data are cut and the higher 14 bits of the data are maintained. The data is sent to the triangular wave lookup table, and phase-to-range conversion of triangular wave signals is achieved.

Owner:10TH RES INST OF CETC

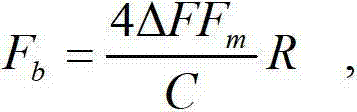

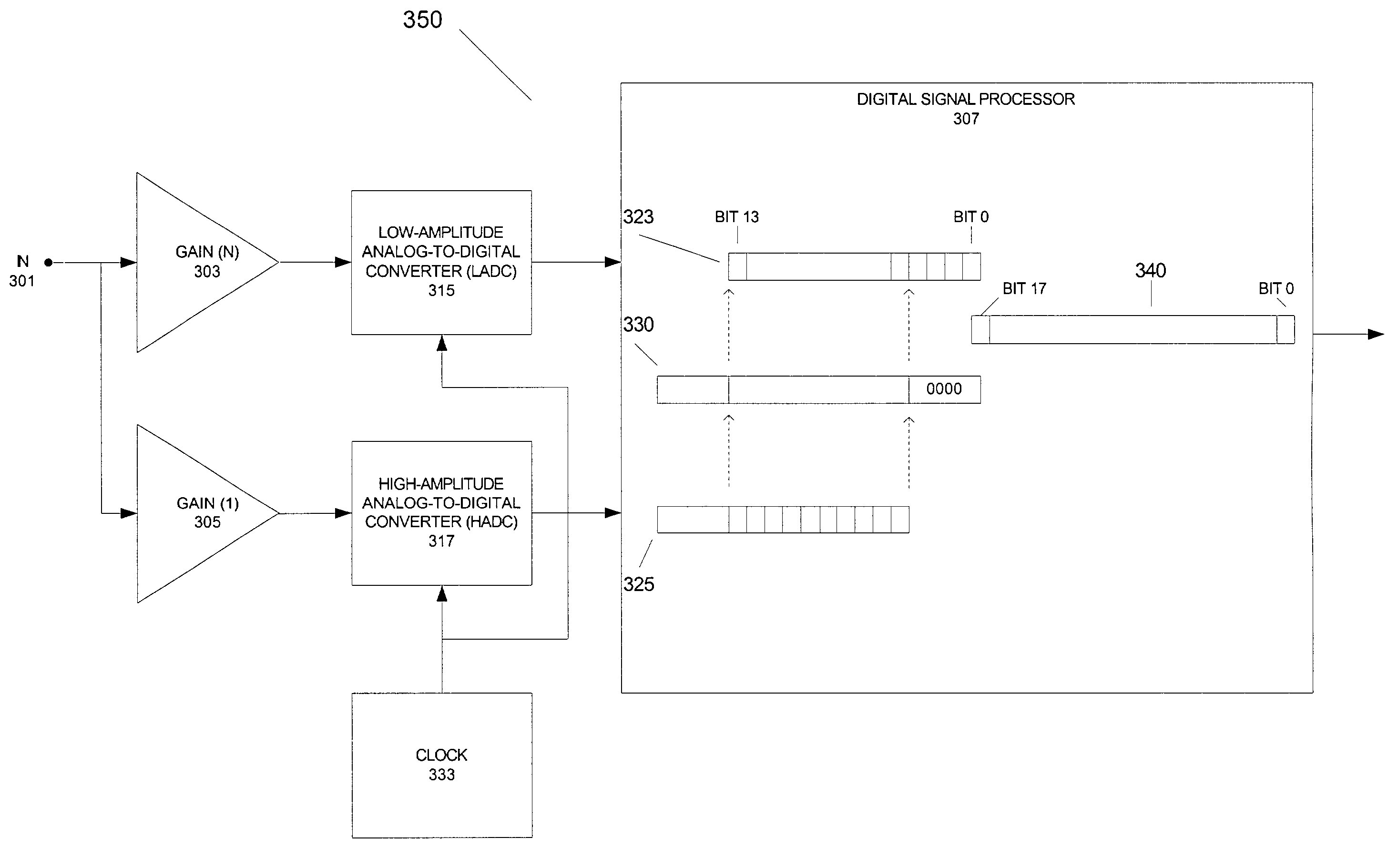

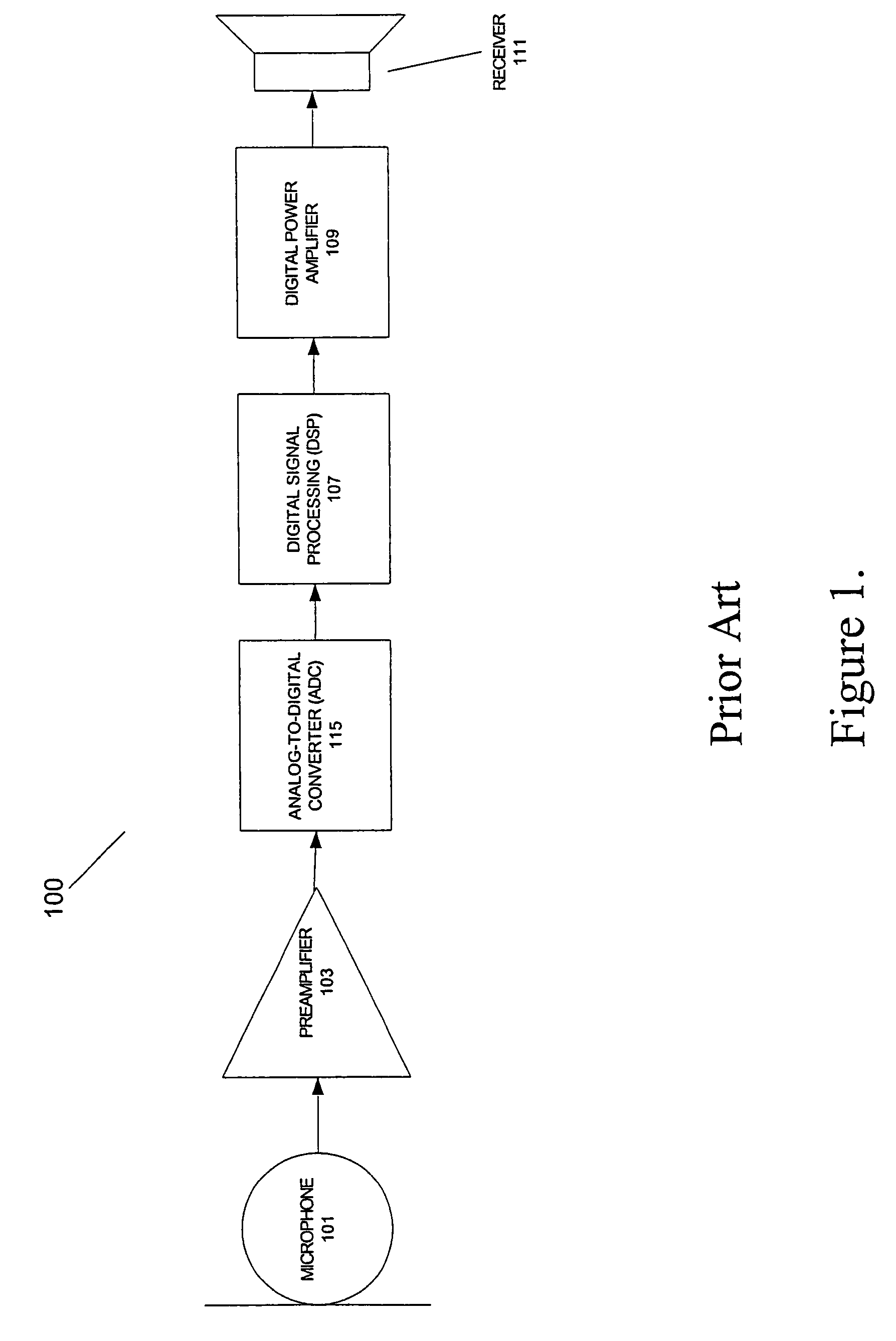

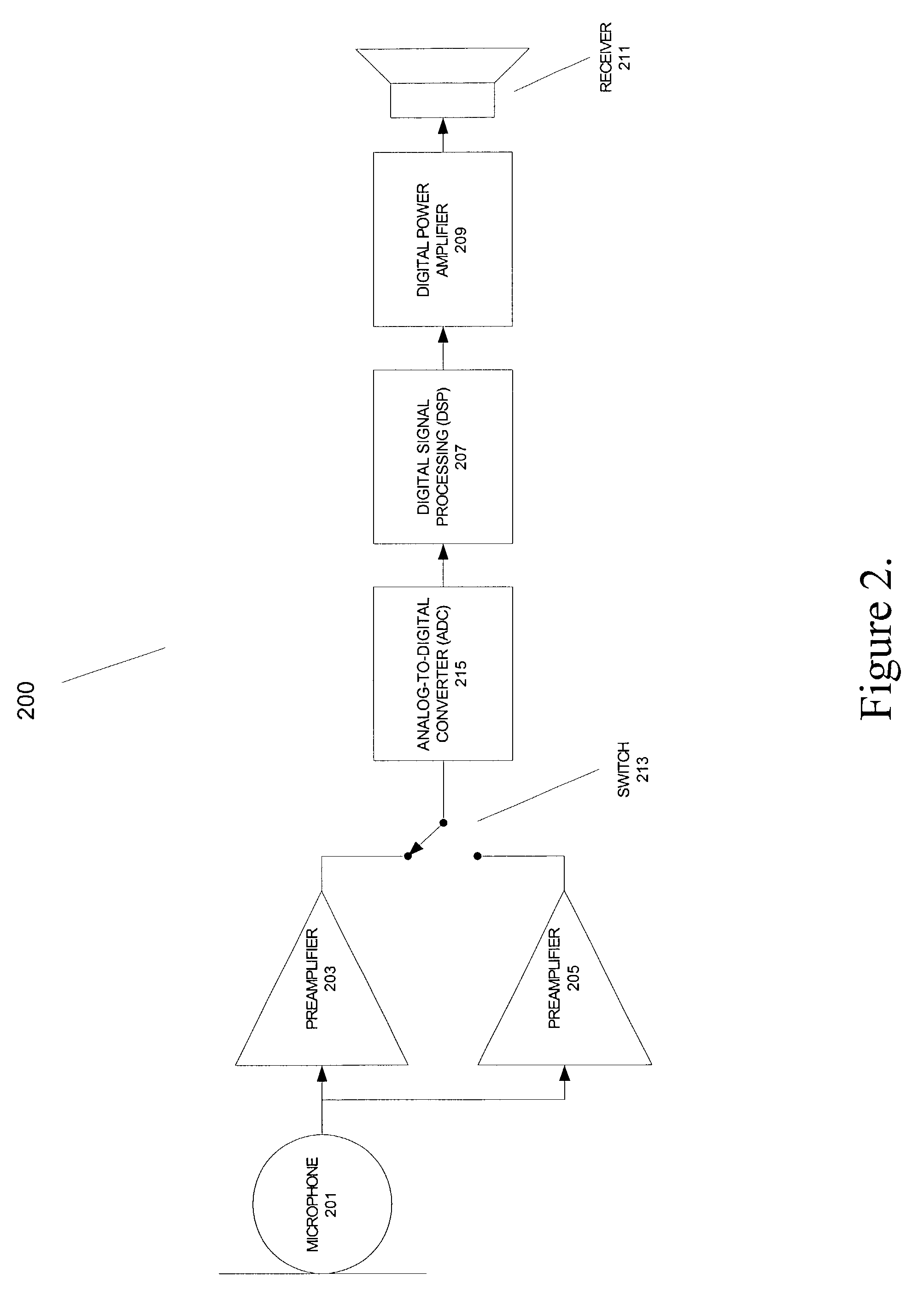

Dynamic range analog to digital converter suitable for hearing aid applications

InactiveUS7003126B2Improve dynamic rangeAnalogue/digital conversionDeaf-aid sets18-bitDigital down converter

An improved analog-to-digital converter device suitable for use in digital hearing aids, and methods for operating such a device are disclosed. Aspects of the present invention may provide a full 16–18 bits (96–108 dB) of dynamic range in a digital hearing aid circuit using 14-bit analog-to-digital converters typically available for hearing aid use. An embodiment of the present invention may use two analog-to-digital converters that are clocked by the same sampling trigger. One of the converters may be preceded by an amplifier having, for example, 24 dB of gain, while the other converter may be preceded by an amplifier having 0 dB of gain. The output of the first converter or the output of the second converter may be used, or a combination of the two outputs may be used to produce audio for the hearing aid user, depending upon input signal level.

Owner:ETYMOTIC RES

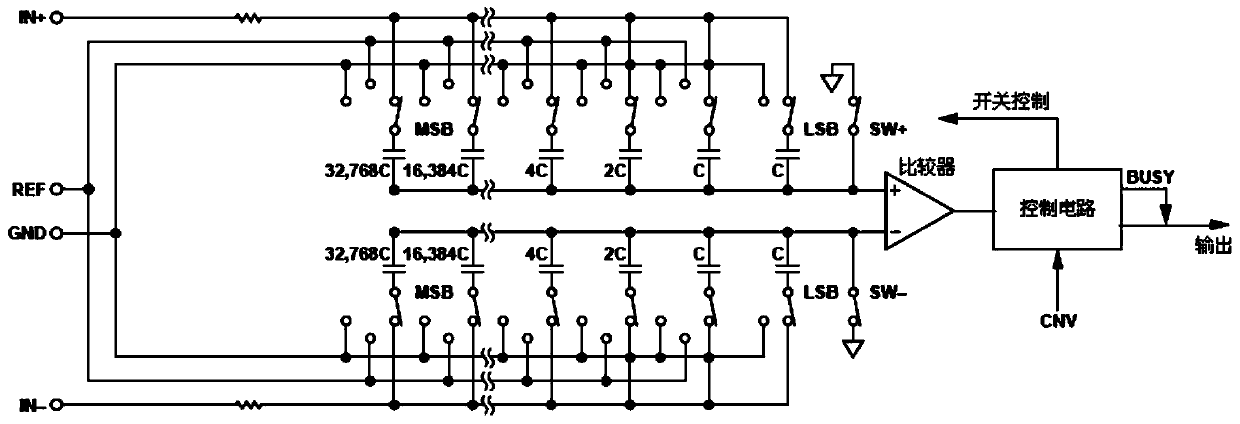

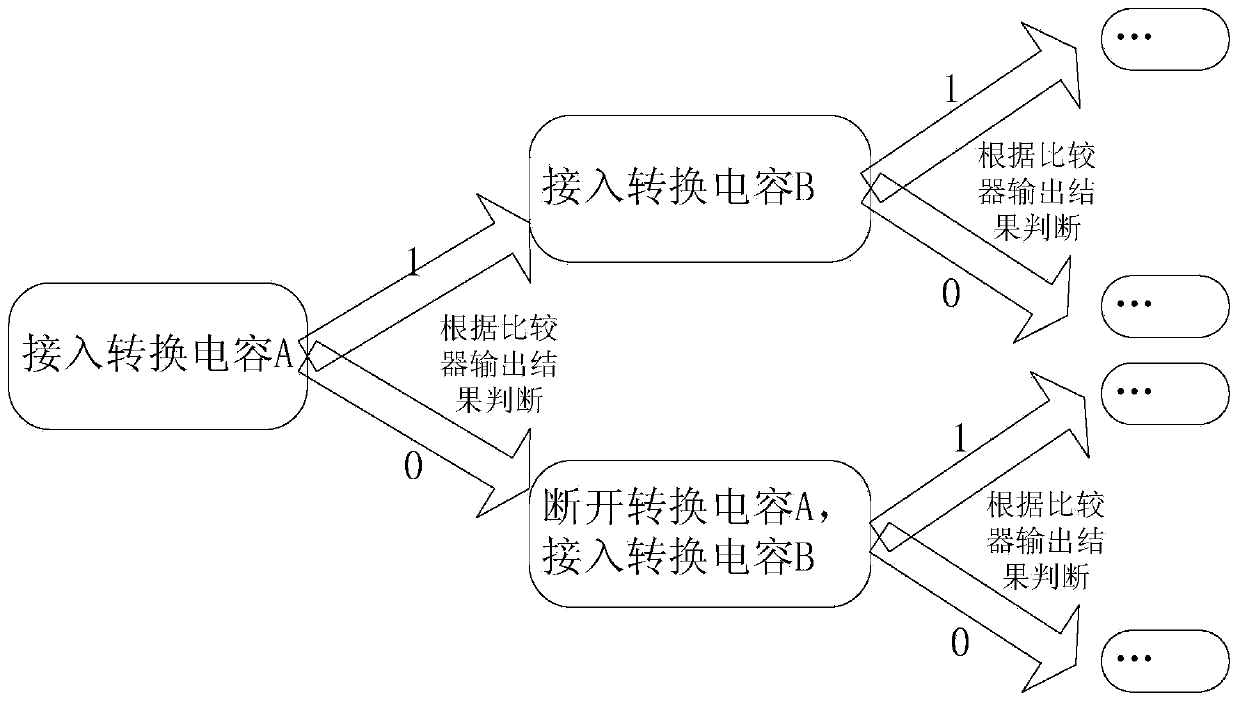

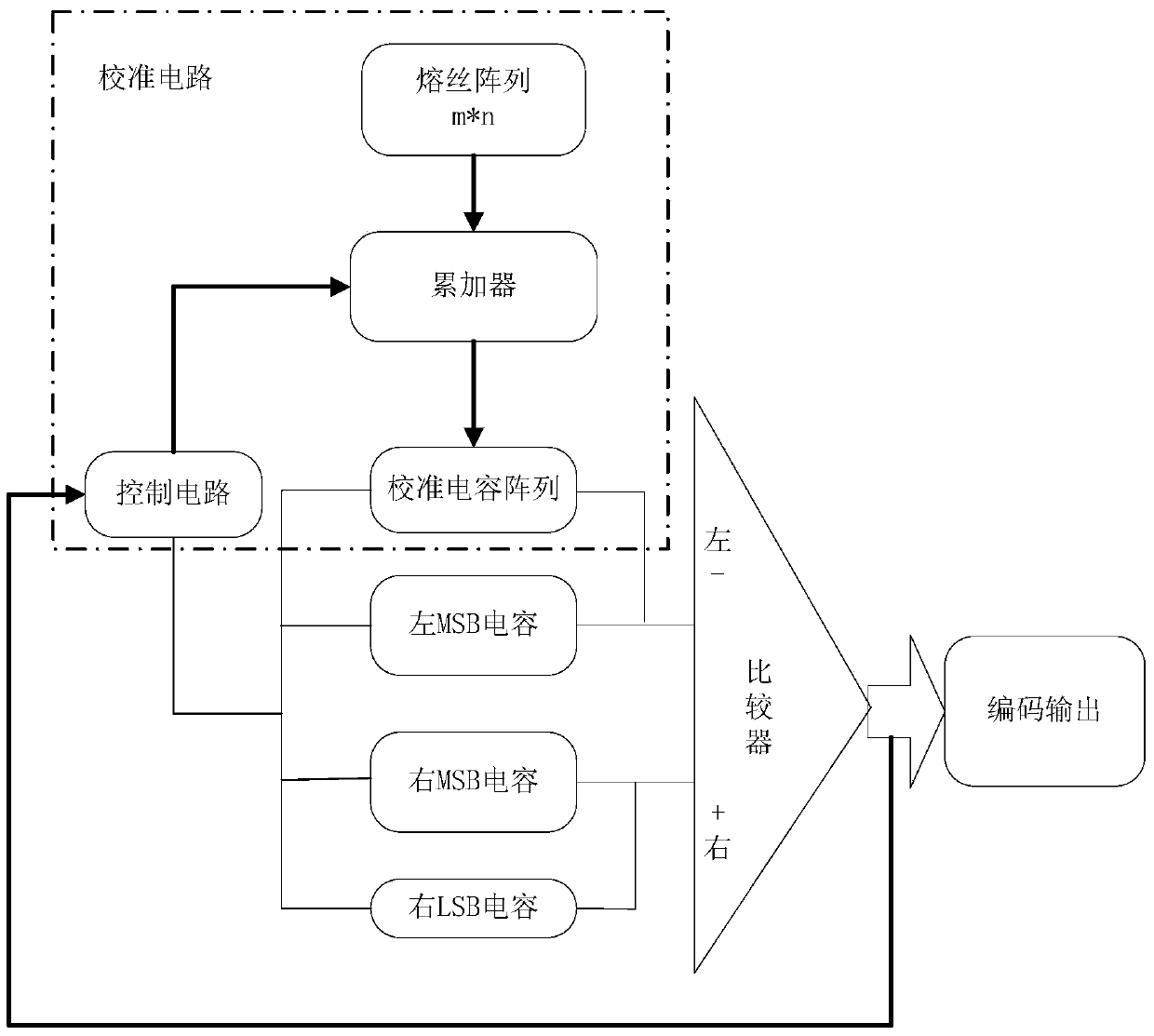

Calibration circuit eliminating capacitor mismatch error

InactiveCN103746693AGuaranteed symmetryReduce layout areaPhysical parameters compensation/prevention18-bitCapacitance

The invention provides a calibration circuit eliminating a capacitor mismatch error. The calibration circuit comprises a fuse array, an accumulator, a control circuit and a calibration capacitor array. Data fuses in the fuse array store mismatch error data. The calibration capacitor array is a left LSB capacitor array in a differential capacitor array. The accumulator reads data fuse values in turn. Connection or disconnecton of capacitors in the calibration capacitor array is controlled under the effect of the control circuit according to output results of a comparator so that capacitor calibration and conversion are completed. The calibration capacitor array and the left LSB capacitor array are combined as one so that layout area is greatly saved. Error information of each high-order capacitor is expressed by using one row of data fuses, and the error information of multiple low-order capacitors is expressed by using one row of data fuses so that contradiction of compensation precision and fuse array scale is compromised. With application of the calibration method, precision of a successively approximate type analog-to-digital converter is enhanced from a conventional 12bit to 16bit and even 18bit.

Owner:BEIJING MXTRONICS CORP +1

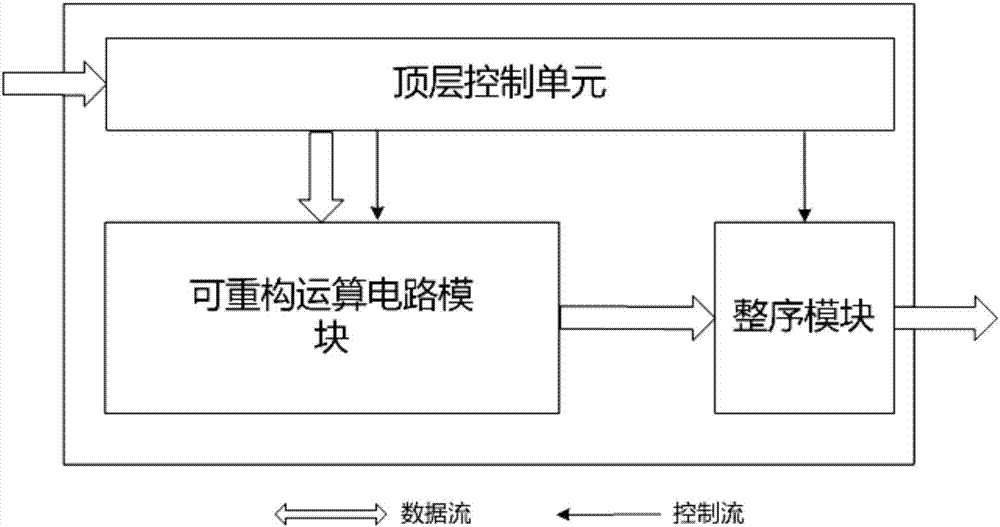

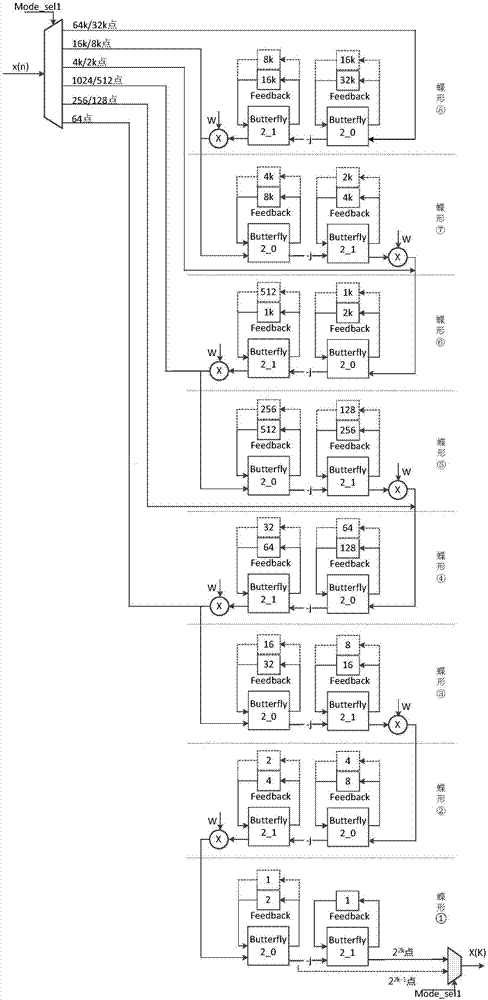

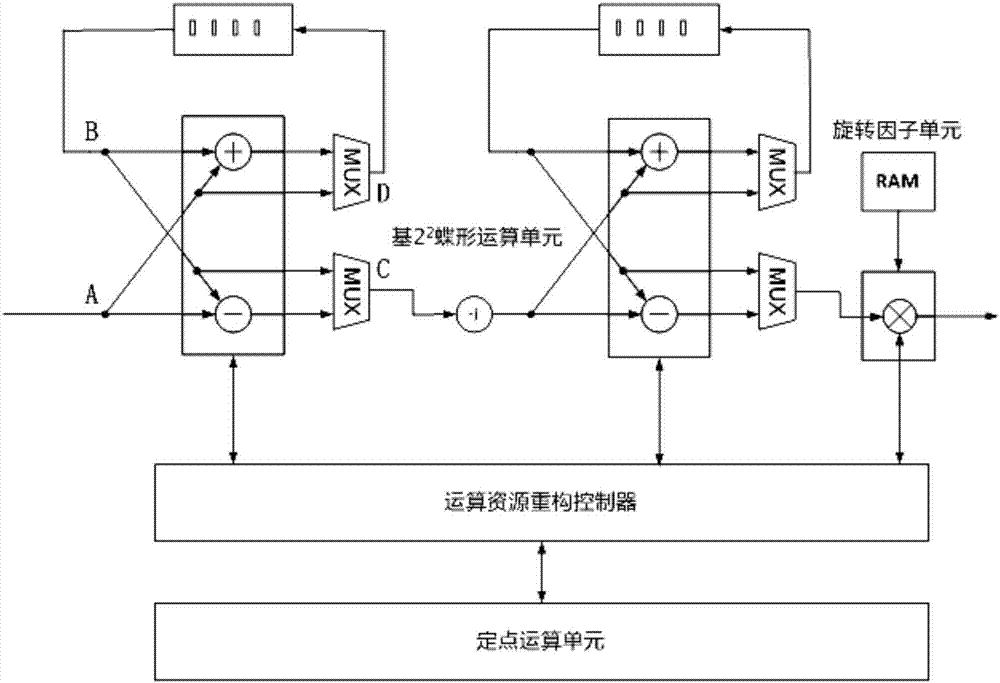

Reconfigurable universal fixed floating-point FFT processor

InactiveCN106951394AImprove versatilitySave resourcesDigital data processing detailsComplex mathematical operations18-bitComputer architecture

The invention provides a reconfigurable universal fixed floating-point FFT processor, which can realize not only 18-bit fixed-point FFT operation but also 32-bit single-precision floating-point FFT operation. According to the processor, a fixed-point arithmetic device (comprising a multiplier and an adder) is separated from a main body structure and can be reconfigured as a single-precision floating-point arithmetic device. A processor main body finishes fixed-point or floating-point FFT operation by calling the fixed-point arithmetic device or the single-precision floating-point arithmetic device formed by reconfiguration. The processor adopts a mixed base flow water structure and supports not only fixed floating-point calculation but also a configurable calculation point number, so that the universality of the processor is effectively improved under the condition of ensuring accuracy and data throughput.

Owner:NANJING UNIV

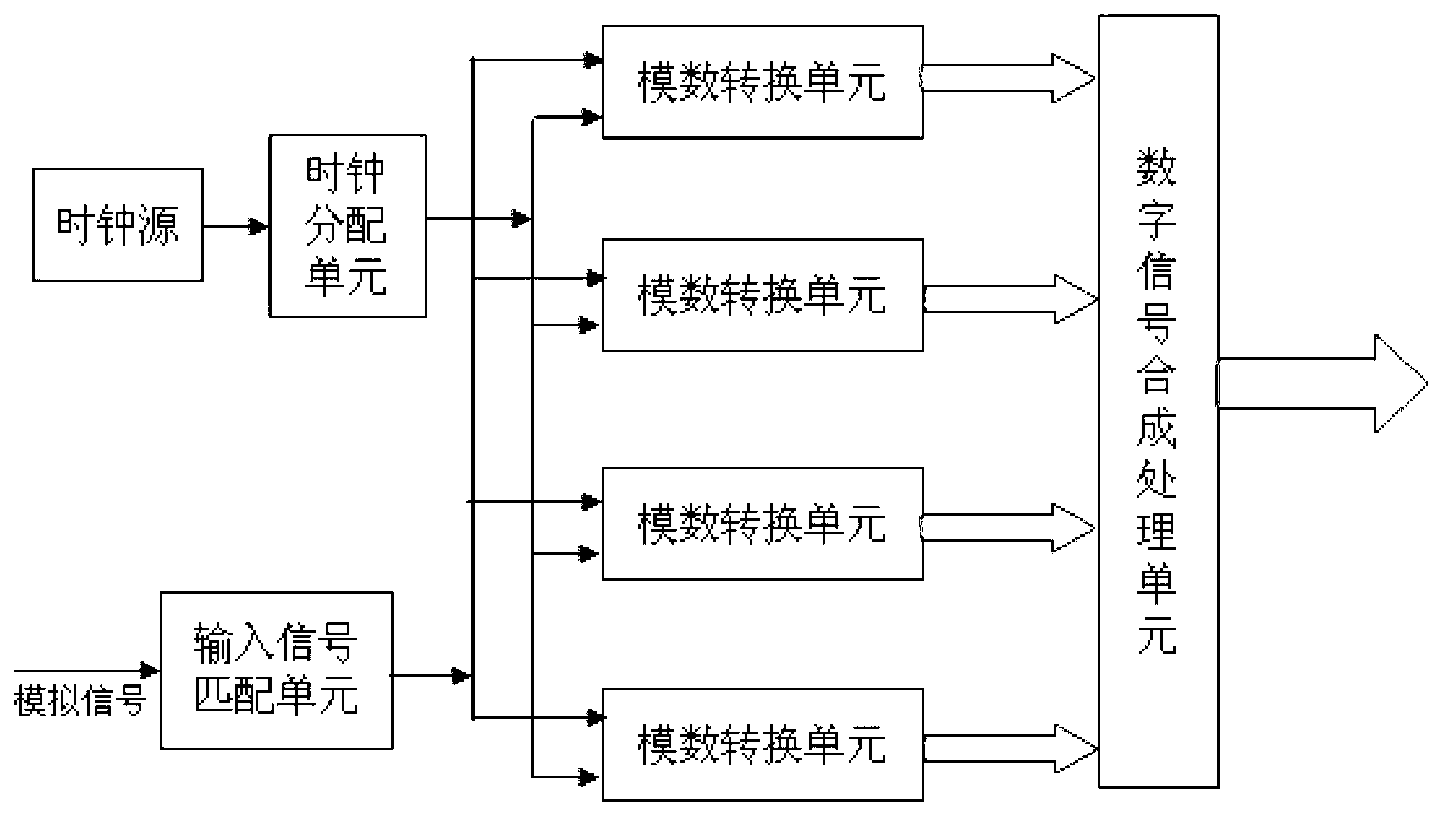

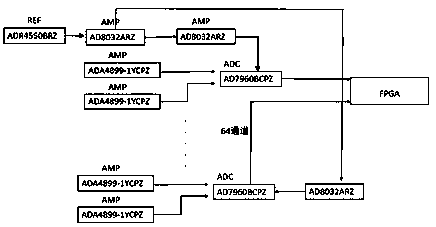

Large dynamic medium-high frequency analog signal digitization conversion circuit

InactiveCN103067005ASolve electromagnetic interferenceReduce spurious signalsPhysical parameters compensation/prevention18-bitVoltage source

The invention provides a large dynamic medium-high frequency analog signal digitization conversion circuit which comprises four identical analog-to-digital conversion units and a unified voltage source. Four conversion chips are identical high-speed 16-bit analog-to-digital conversion chips. Two circuit boards are arranged in a vertically and horizontally symmetrical mode. Clock signals of a clock distribution unit after being controlled and processed by a phase are accessed to the four analog-to-digital conversion chips in a difference mode. Sampling clock phases of the adjacent conversion chips differ by 180 degrees respectively. Analog difference signal lines of an input signal matching unit are accessed to the four analog-to-digital chips for parallel sampling, finish analog-to-digital conversion in a parallel mode, output 4*16-bit parallel digitization signals to a digital signal combination processing unit, and finally output high-speed digitization signals of 18-bit equivalent quantization. The four signal lines are parallel to each other and distributed in a symmetrical mode, complementary-producing magnetic field effects lower mutual electromagnetic interference degree among the chips, the number of output stray signals and noise bases is lowered, and conversion dynamic range is improved by 10-15 data bases compared with the single chip.

Owner:NO 34 RES INST OF CHINA ELECTRONICS TECH GRP

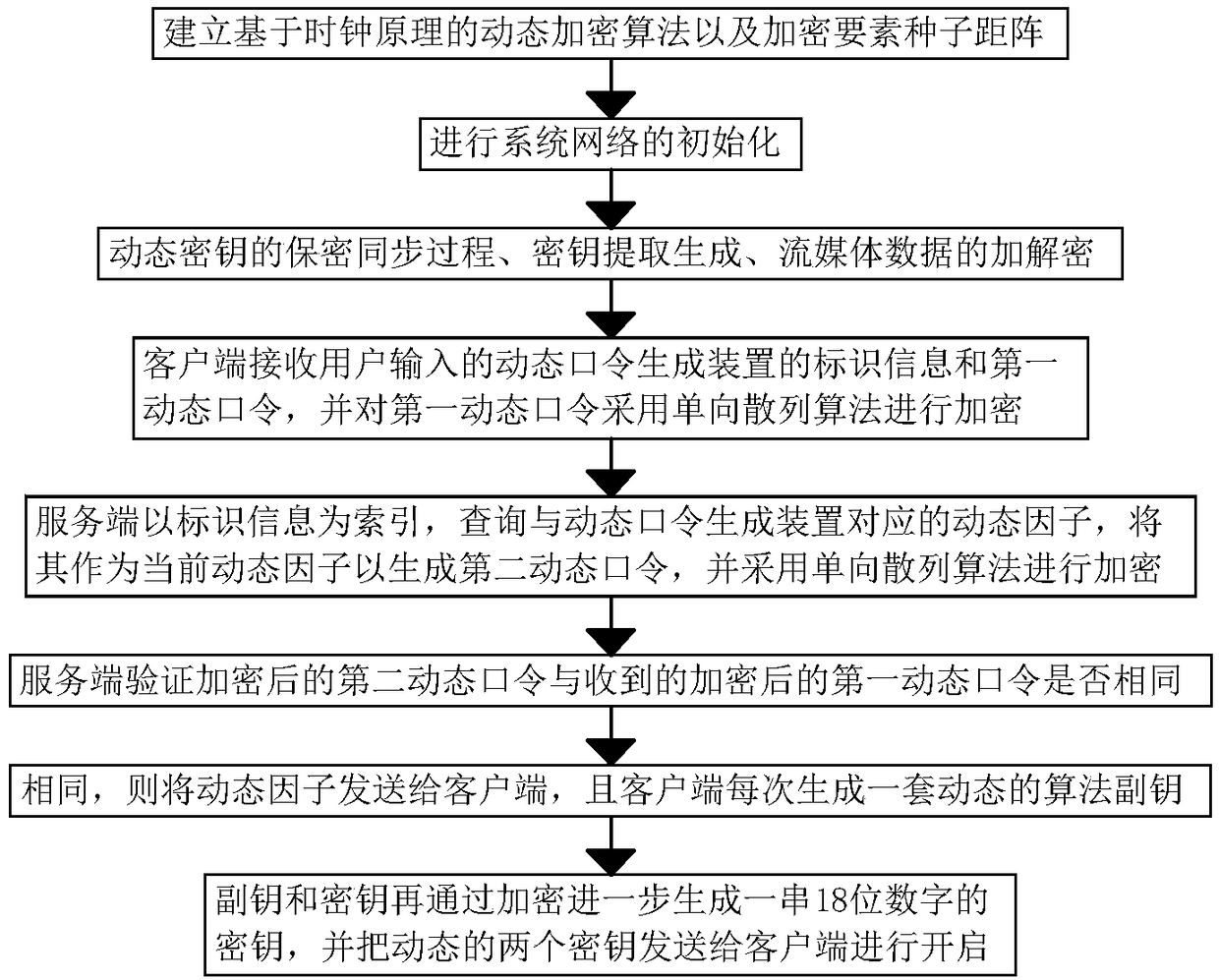

Dynamic double-key algorithm

InactiveCN108400870AEnsure safetyKey distribution for secure communicationMultiple keys/algorithms usage18-bitPassword

The invention discloses a dynamic double-key algorithm. The algorithm comprises the following steps: step A, establishing a dynamic encryption algorithm based on a clock principle and an encryption element seed array; step B, performing initialization of a system network; step C, performing a confidentiality and synchronization process of a dynamic key, key extraction and generation, and encryption and decryption of streaming media data; and step D, receiving a dynamic password input by a user by a client, generating identifier information and a first dynamic password of a device, and encrypting the first dynamic password by adopting a one-way hash algorithm. According to the dynamic double-key algorithm provided by the invention, the dynamic encryption algorithm based on the clock principle is adopted, so that the keys of each time are different; meanwhile, a set of dynamic algorithm auxiliary keys are generated every time, and the auxiliary keys and keys are processed by encryption to further generate a string of keys with 18-bit numbers, and two dynamic keys are sent to the client to be opened; and since the keys can only be used once, after the keys are intercepted by a hacker,the keys are written into equipment, and the equipment has no reaction, so that the use safety of a Bluetooth lock circuit is effectively guaranteed.

Owner:浙江易云物联科技有限公司

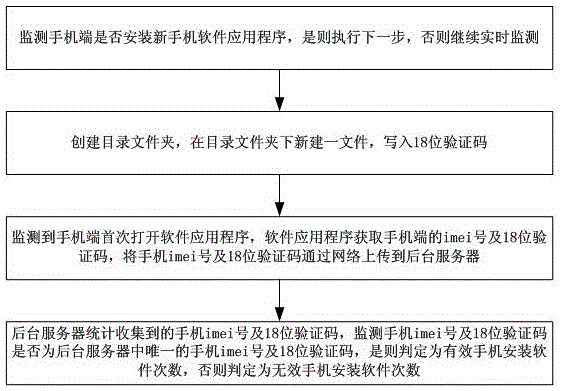

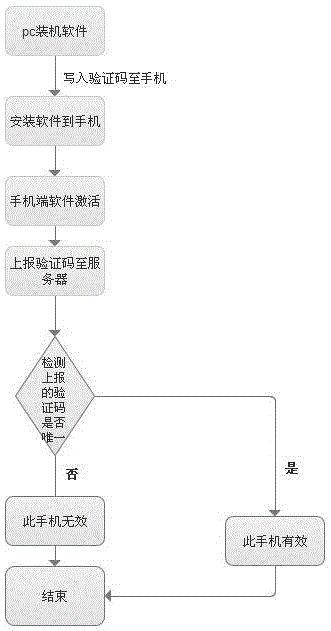

Monitoring method and system for preventing generating flow of cell phone software

ActiveCN105119770ASave on promotion costsImprove experienceSubstation equipmentData switching networks18-bitApplication software

The invention discloses a monitoring method for preventing generating the flow of cell phone software. The monitoring method includes a first step of monitoring whether a new cell phone software application program is installed on a cell phone end, if yes executing the next step, otherwise monitoring continuously on a real-time basis; a second step of creating a directory folder, creating a new file under the directory folder and writing an 18-bit identifying code; a third step of the software application program obtaining the imei number and the 18-bit identifying code when the cell phone end first starts the software application program, and updating the imei number and the 18-bit identifying code to a background server; a fourth step of the background server calculating the imei number and the 18-bit identifying code collected, monitoring whether the imei number and the 18-bit identifying code is unique in the background server, if yes, the software installation time is effective, otherwise, the software installation time is ineffective. The monitoring method and system prevent repeatedly charging, save software promotion fee, and improve user experience.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

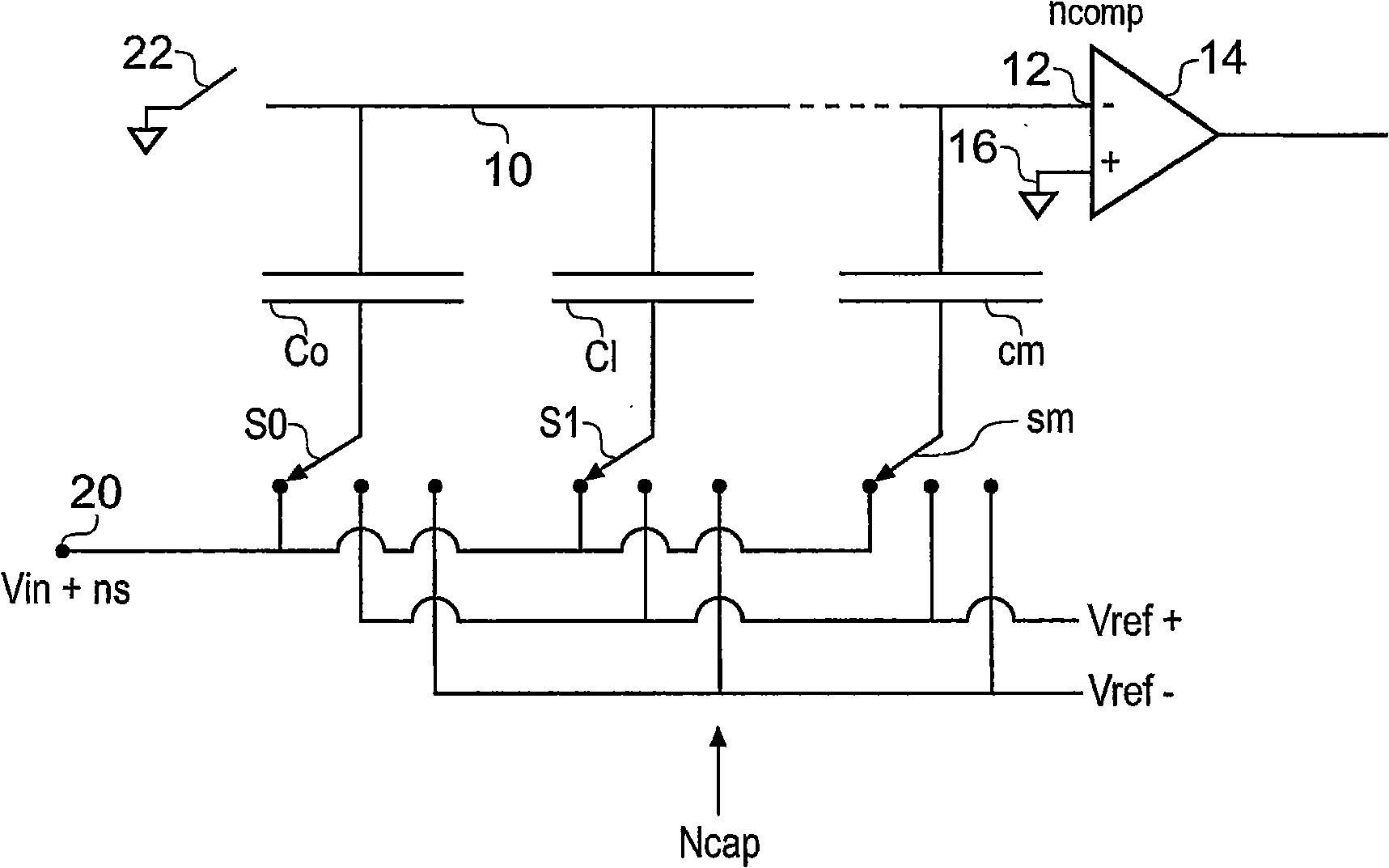

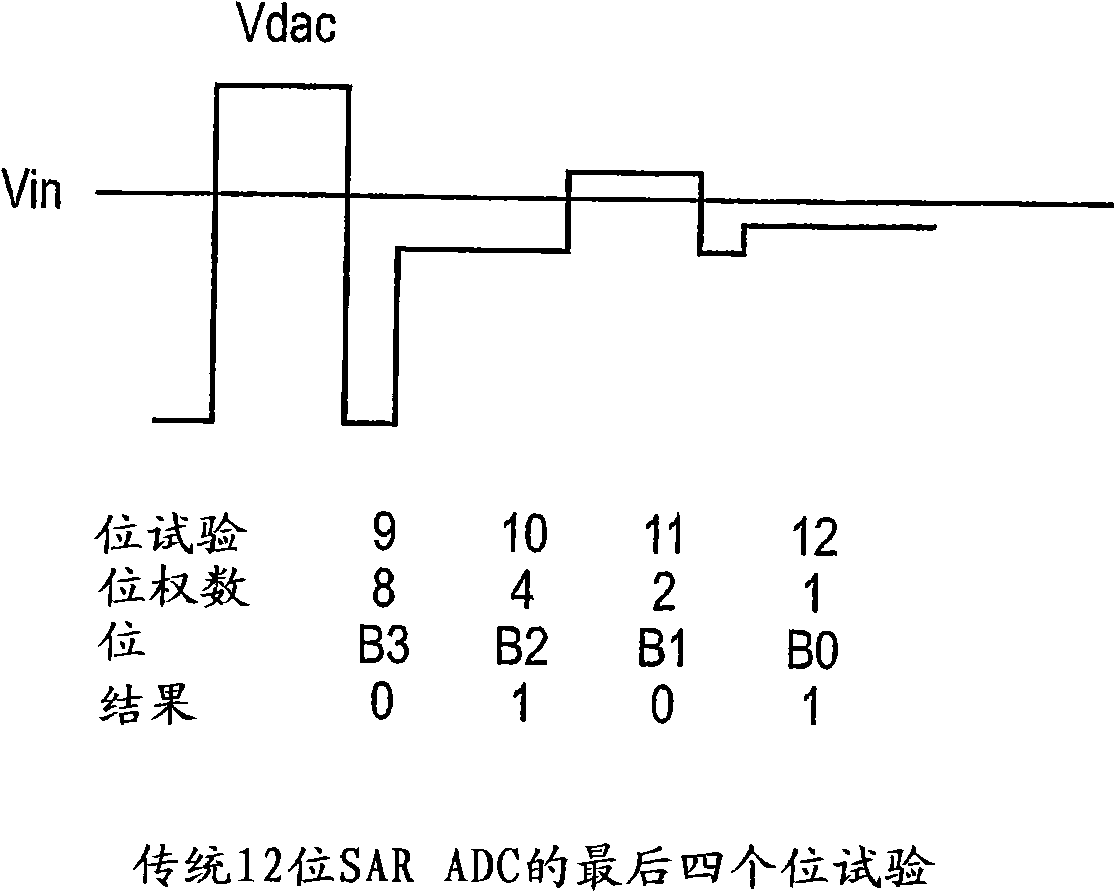

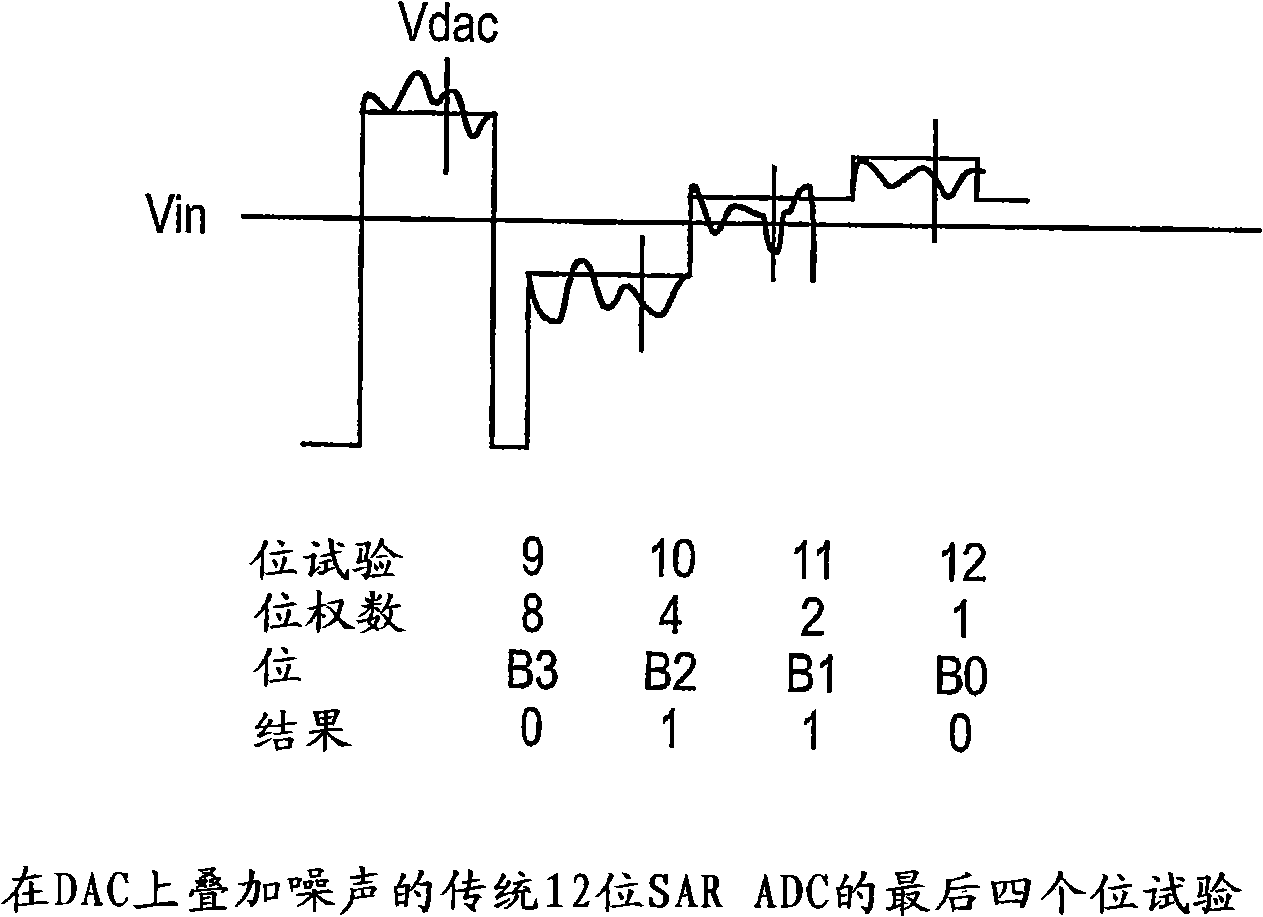

Analog-to-digital converter

InactiveCN101263656AElectric signal transmission systemsPhysical parameters compensation/prevention18-bitDigital down converter

When the least significant bit LSB is confirmed, the normal SAR conversion is completed. A first test is represented. In the invention, N additional bits are also confirmed. Each additional bit represents a correction test. The result obtained by adding the result after each additional correction test to the conversion result after a (first) bit test when the last bit is normal is taken as the effective result. The last result is obtained by adding N+1 results together. Because the N+1 results are confirmed in different conditions, the effect of the noise of the comparator is reduced. The additional benefit of the method is obtaining a higher resolution result. For an example, the 16-bit converter which has three additional + / -0.5 bit correcting bit tests can generate a 18-bit conversion result when four results are added.

Owner:ANALOG DEVICES INC

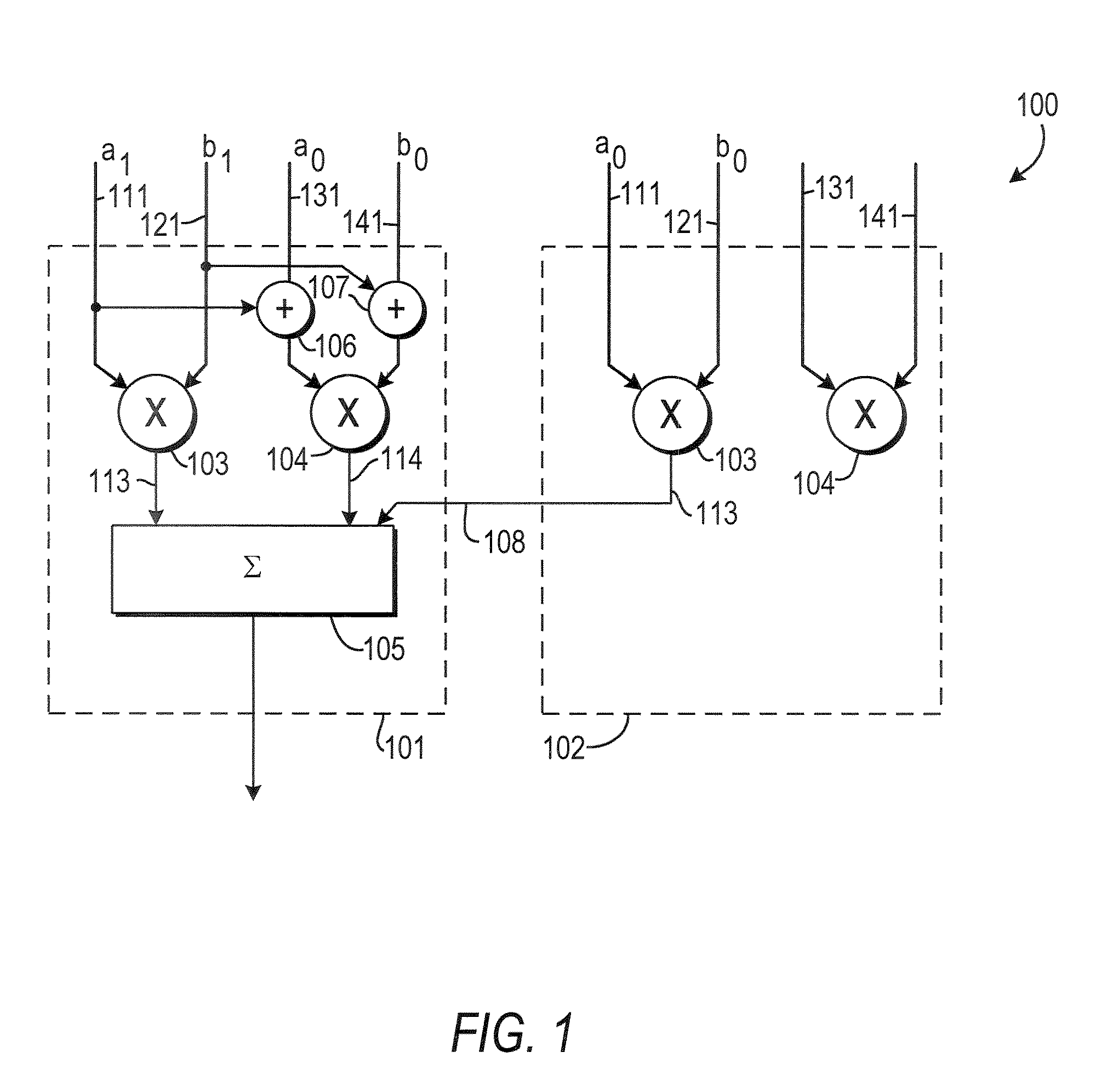

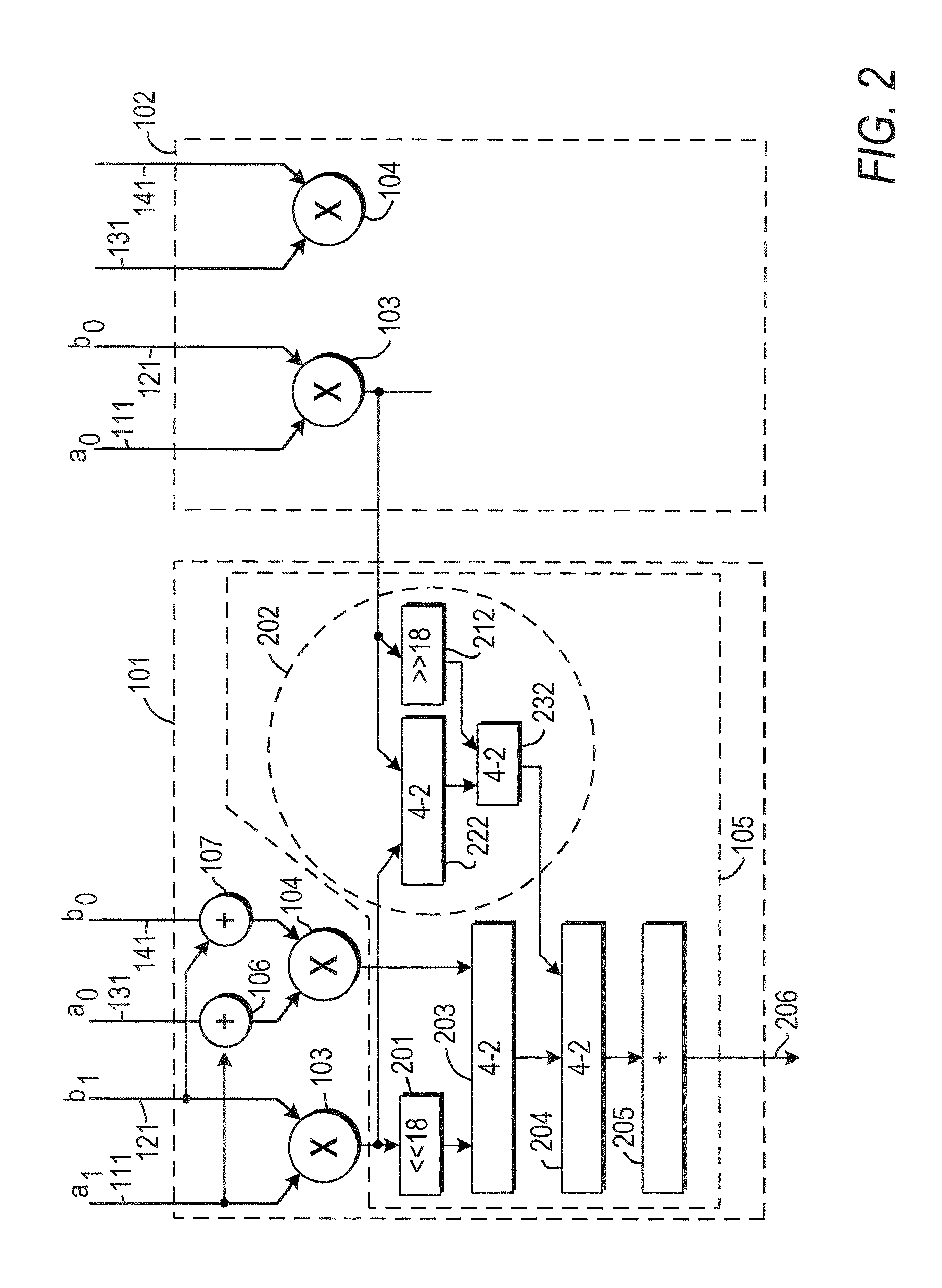

Implementing multipliers in a programmable integrated circuit device

InactiveUS8468192B1Reduce in quantityComputation using non-contact making devicesIntegrated circuit18-bit

The number of multipliers of a particular size that are required to perform a multiplication larger than that size is reduced. In the example of a 36-bit-by-36-bit multiplication, the number of 18-bit-by-18-bit multipliers required may be reduced from four to three. This may be achieved by using recursive decomposition techniques. As discussed in more detail below, if for each of two 36-bit numbers, the “digits” of each respective 36-bit number are added together, and then the two sums are multiplied, the resulting term can be combined additively with the product of the least-significant group of bits of the two 36-bit numbers and the product of the most-significant group of bits of the two 36-bit numbers to provide the desired product. A specialized processing block includes structures to facilitate the recursive decomposition technique.

Owner:ALTERA CORP

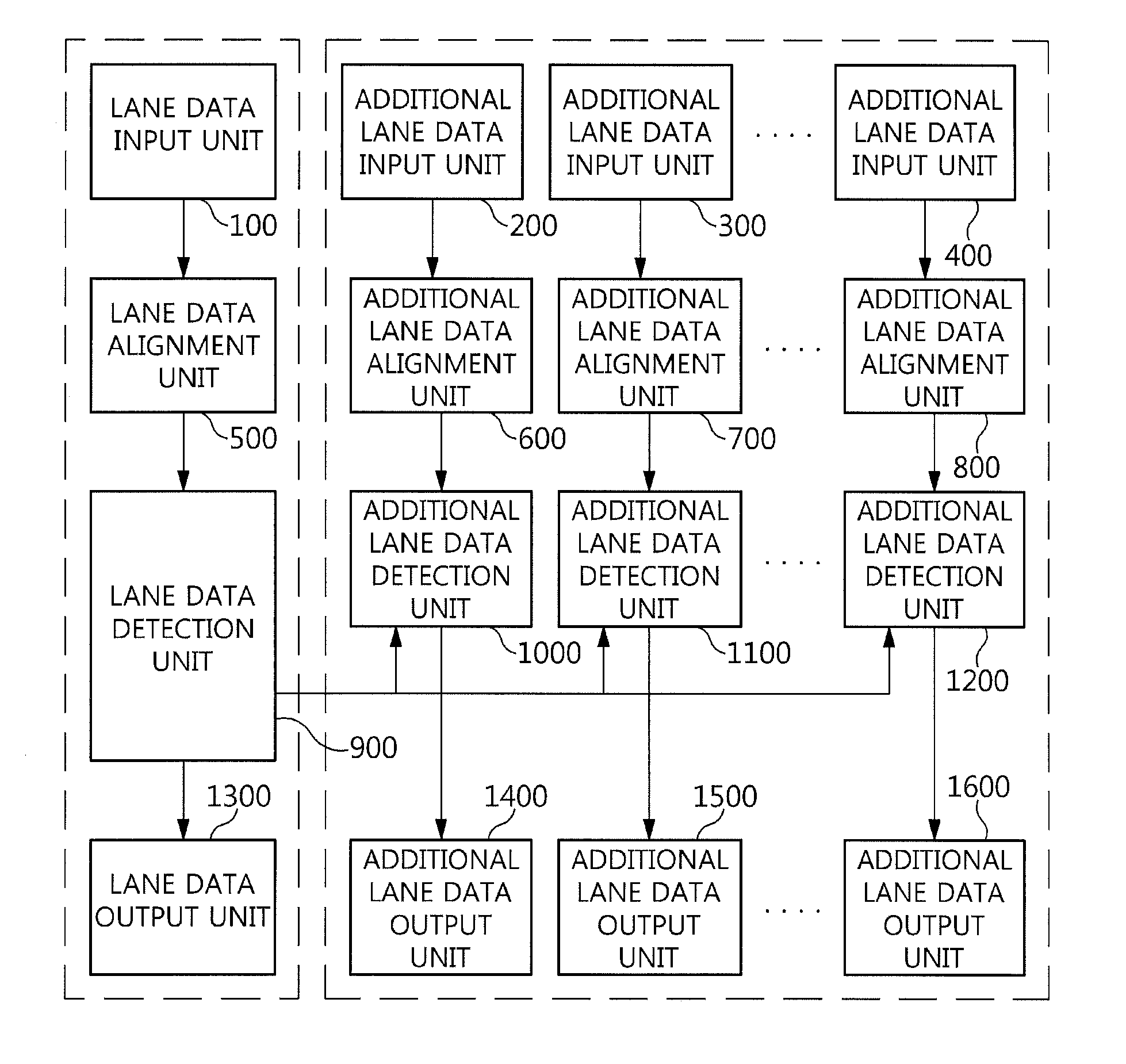

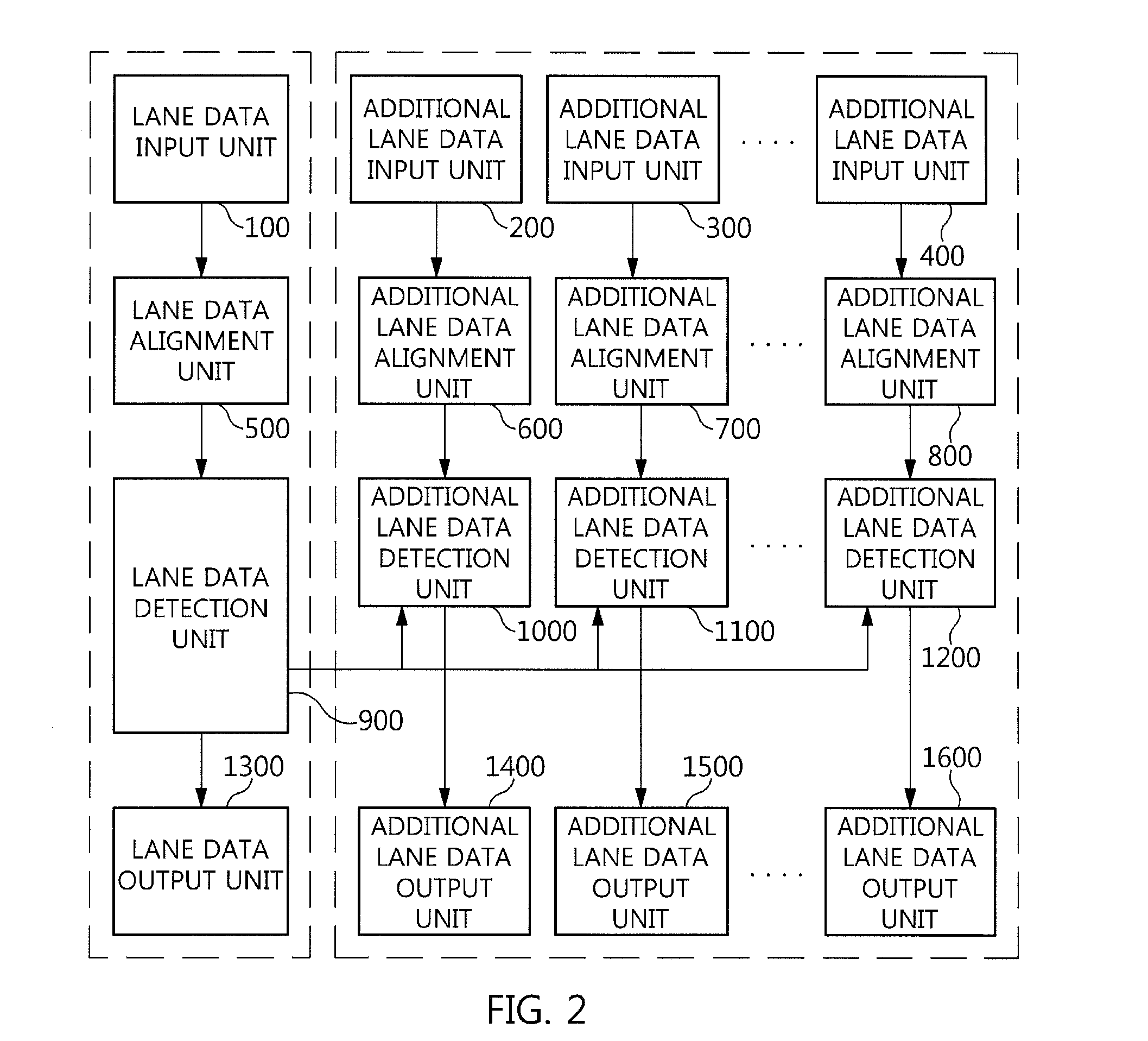

Deskew apparatus and method for peripheral component interconnect express

InactiveUS9058266B2Detect changeCompensation differenceTime-division multiplexRecord information storage18-bitPCI Express

Owner:ELECTRONICS & TELECOMM RES INST

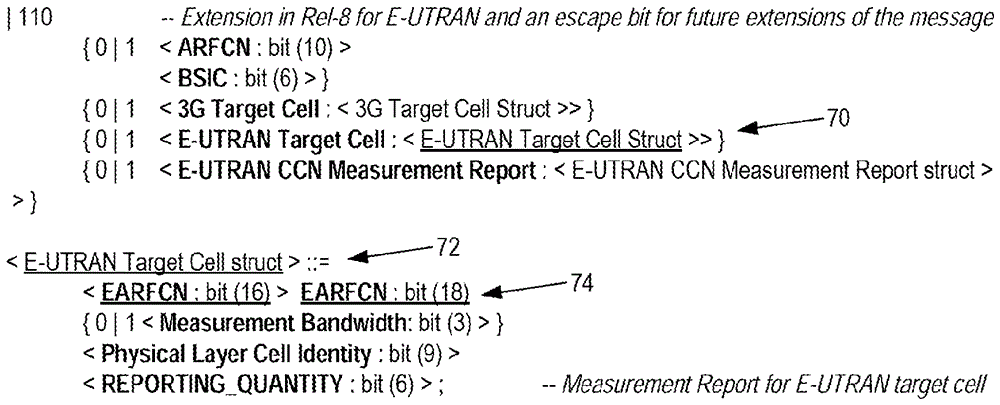

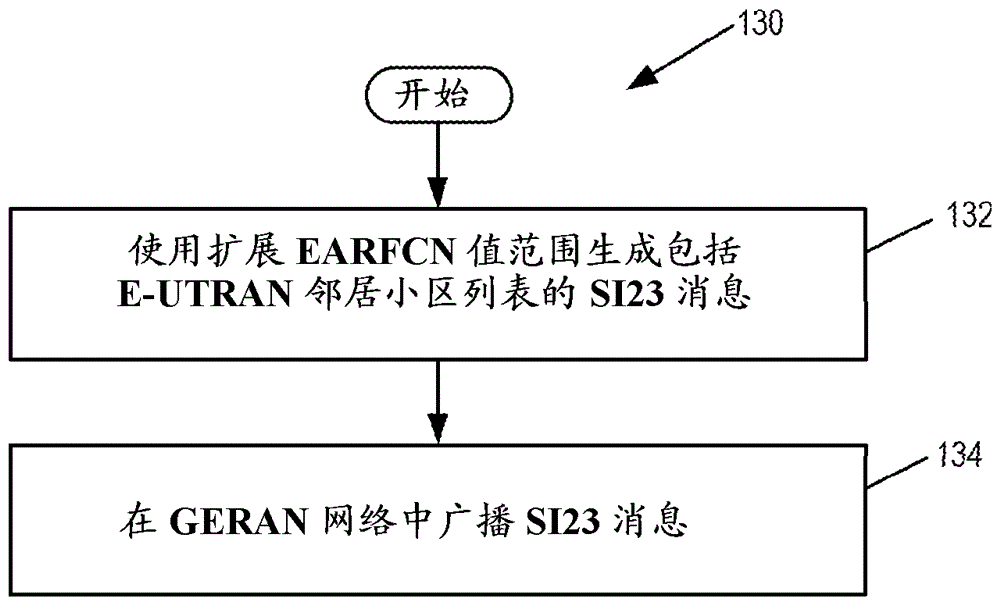

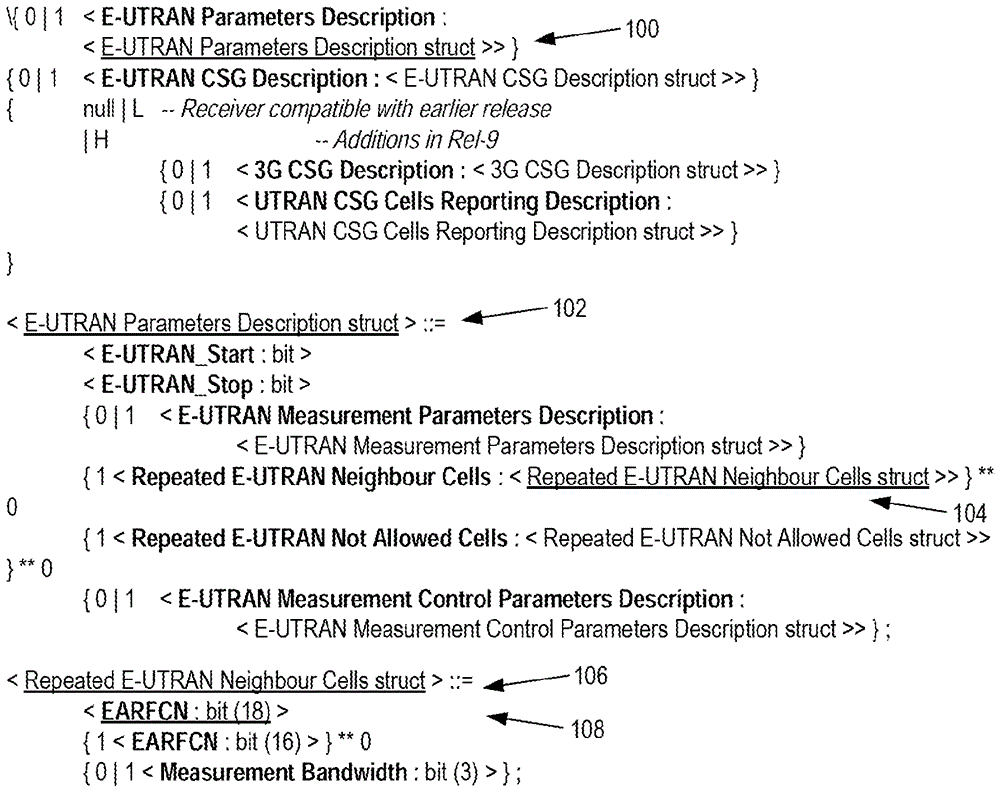

Extending EARFCN value range in GERAN

The invention relates to extending EARFCN value range in GERAN. An E-UTRAN neighbor cell (12, 14, 16) list is broadcast in a GERAN network (10) using the extended EARFCN value ranges (i.e., 18 bits). Extending the EARFCN value ranges in GERAN (10) and signaling EARFCN values within the extended EARFCN value range to inter-RAT-capable UEs (20) that camp in GERAN (10) allows GERAN (10) to support continued inter- RAT mobility between GERAN (10) and E-UTRAN (18) networks. E-UTRAN neighbor cell (12, 14, 16) information may be communicated to UEs (20) in the GERAN network (10) by System Information message broadcasts using the extended EARFCN value ranges.

Owner:TELEFON AB LM ERICSSON (PUBL)

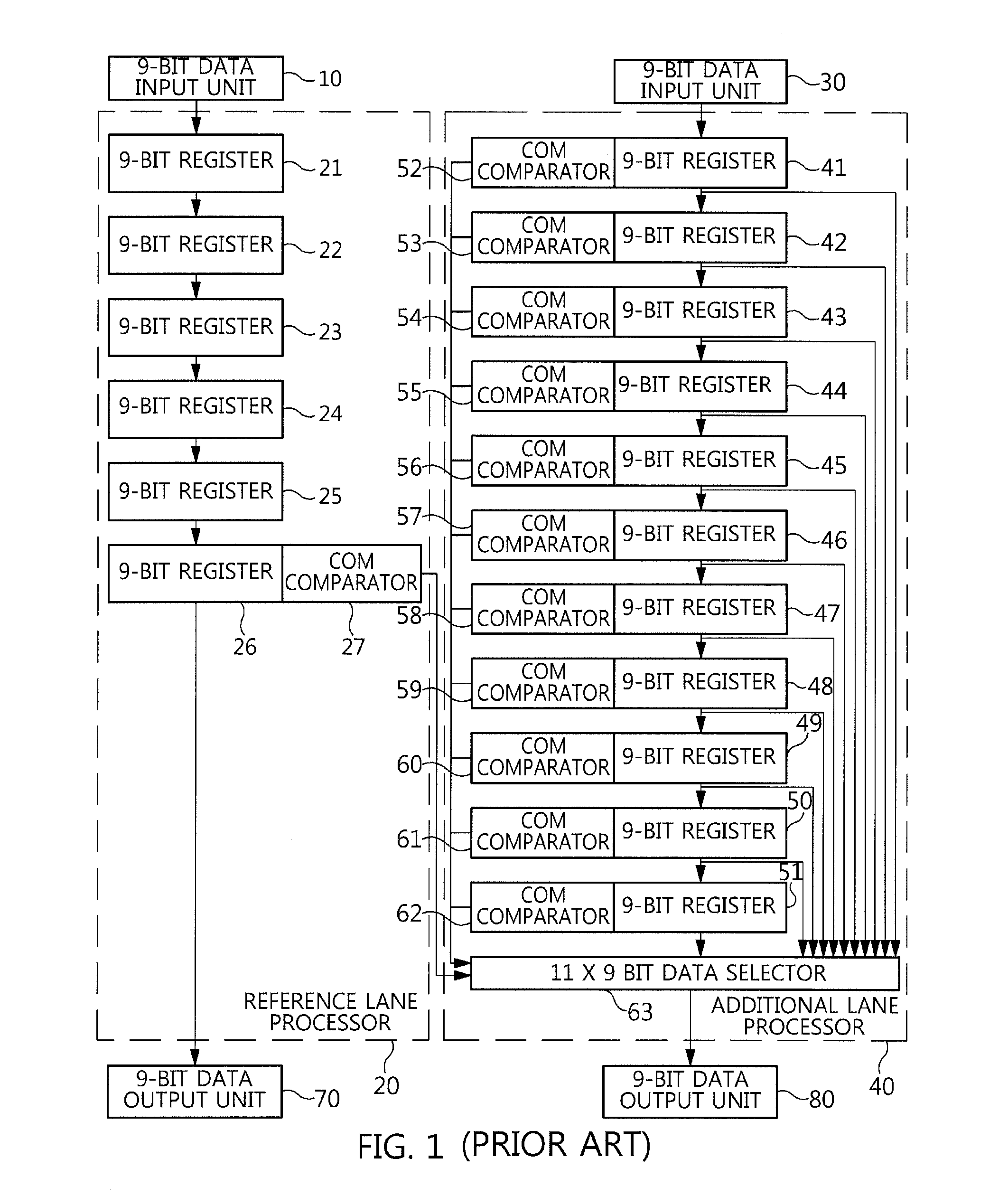

Interleaver memory access apparatus and method of CDMA system

InactiveUS6965557B2Reduce power consumptionImprove data access speedUnequal/adaptive error protectionMultiplex code generationShift registerQuadrature modulator

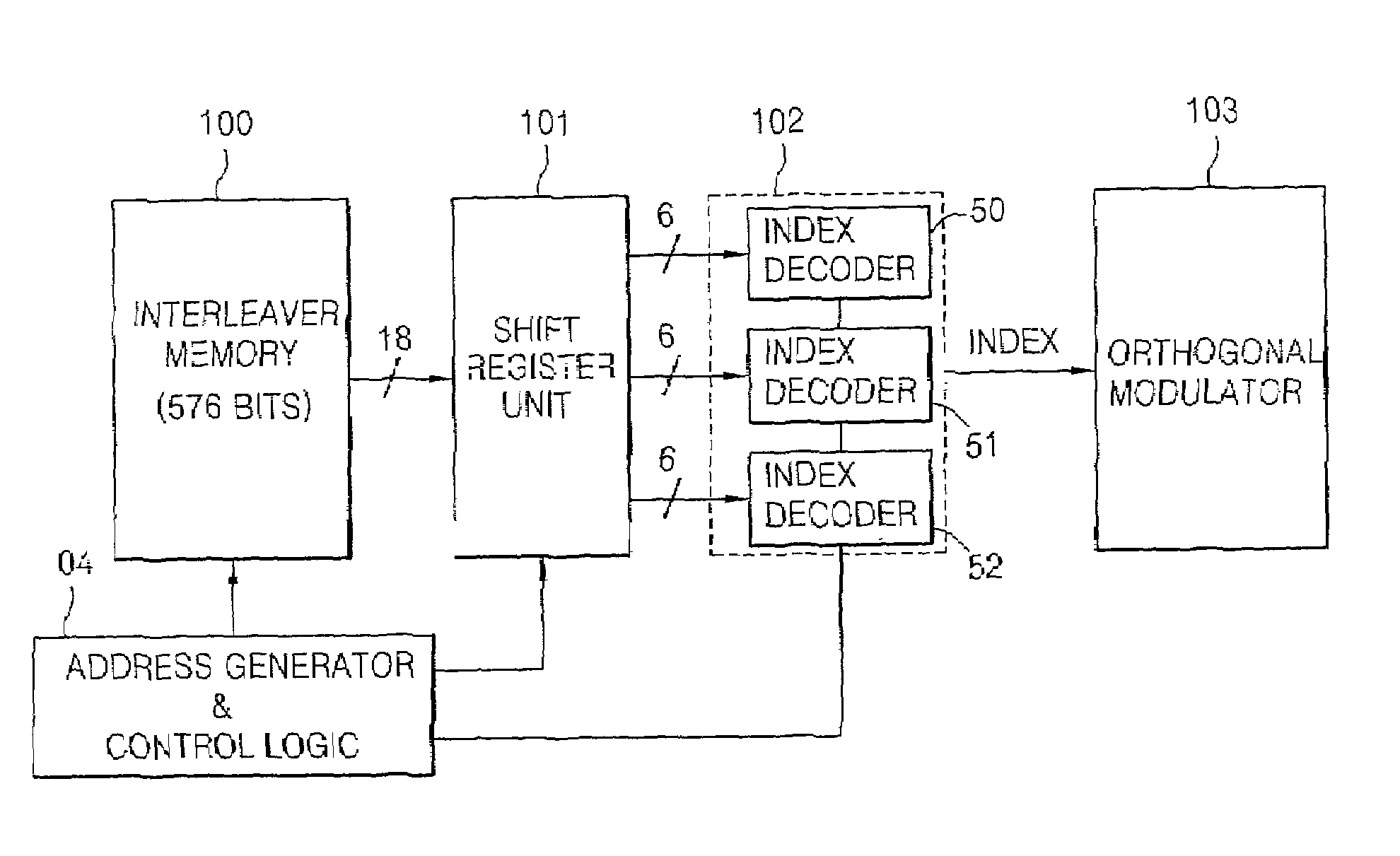

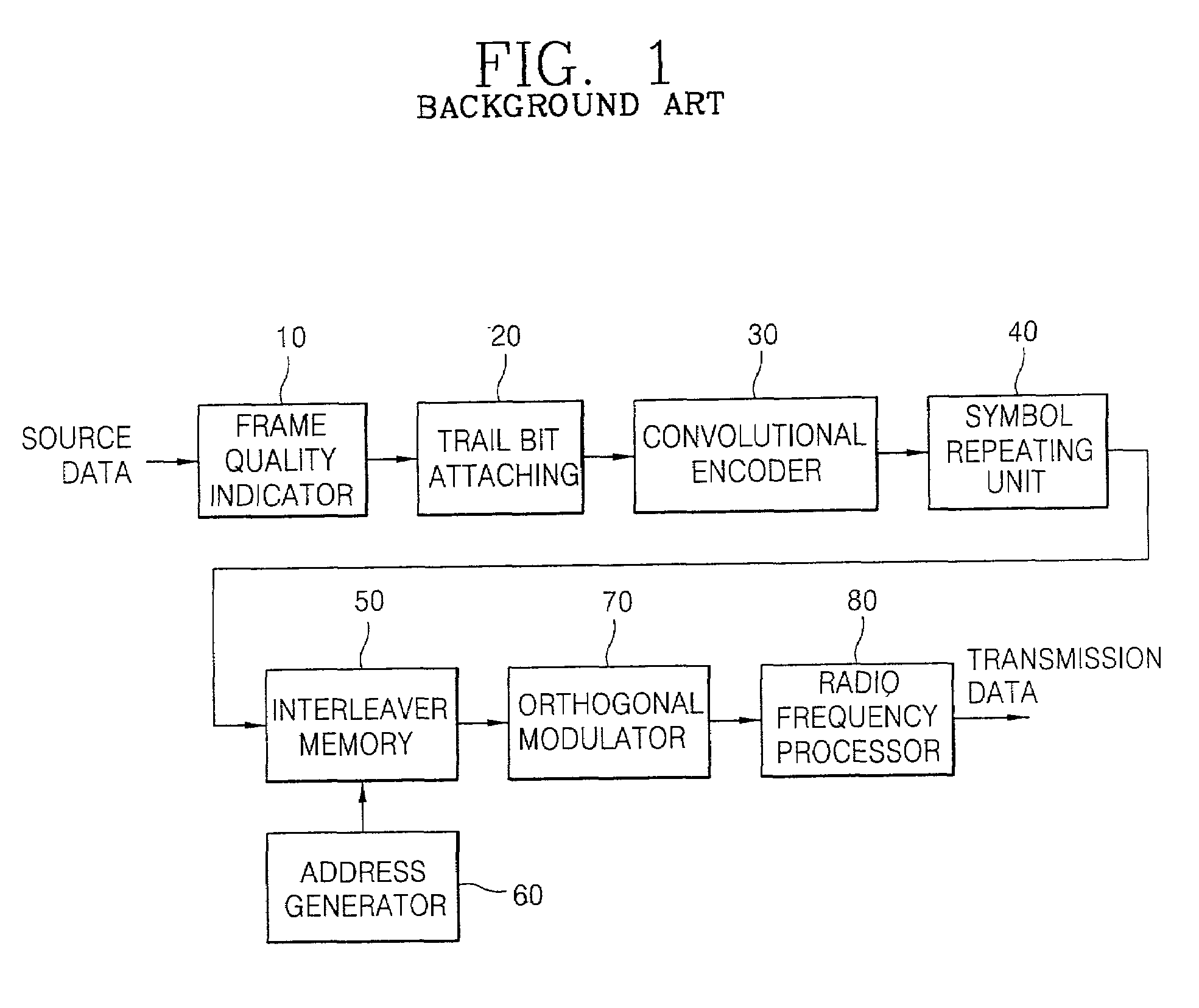

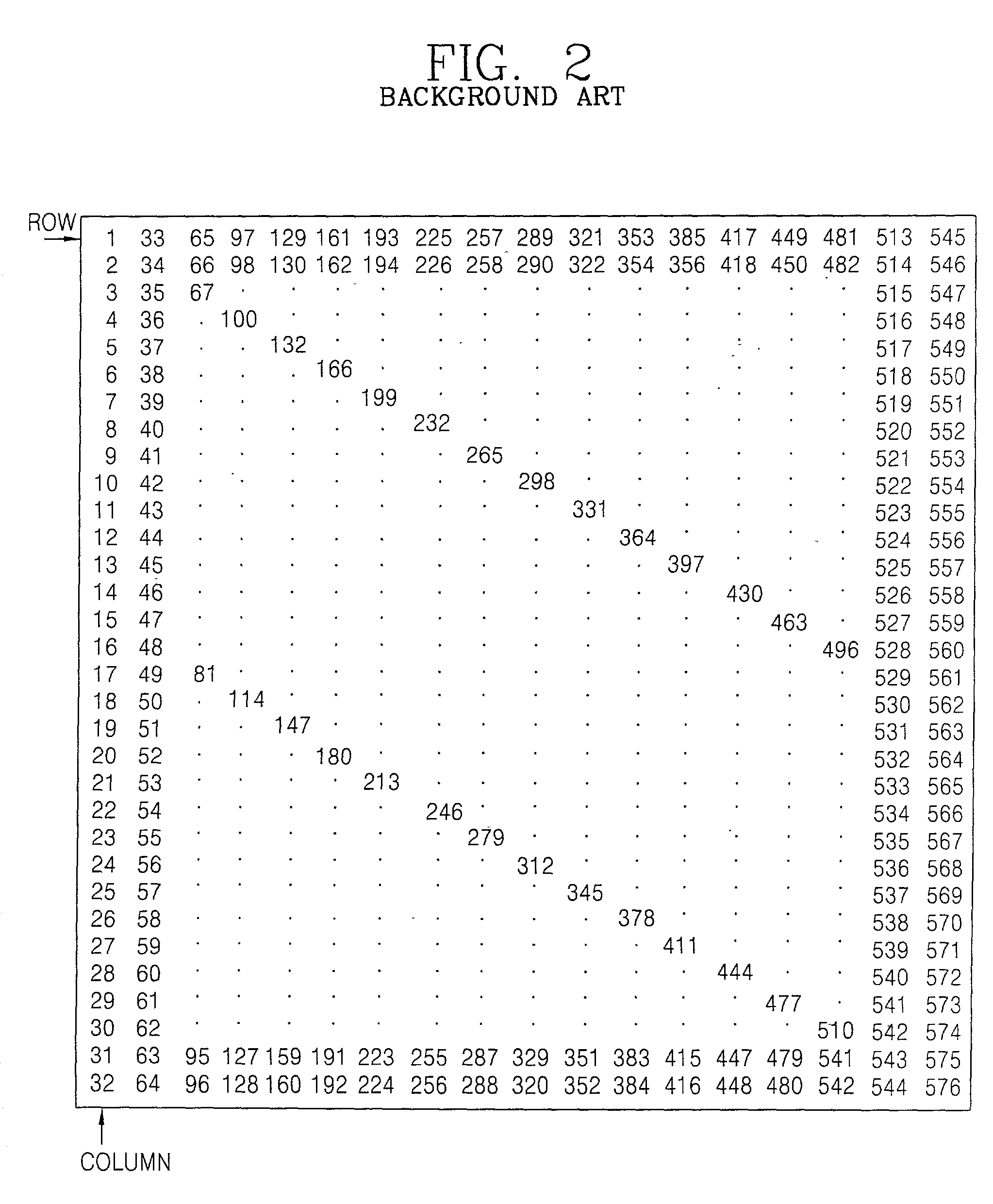

An interleaver memory access apparatus of a CDMA system including an interleaver memory for storing code symbols to be transmitted; a shift register unit for simultaneously receiving 18 bit code symbols from the interleaver memory and outputting the 18 bit code symbols in three sets of 6 bit code symbols; an index decoding unit for decoding the 6 bit code symbols outputted from the shift register unit and generates a Walsh bit index; an address generator and control logic for controlling an access operation of the interleaver memory and the input and output operation of the shift register unit and the index coding unit; and an orthogonal modulator for outputting 64 bit Walsh codes based on the Walsh bit index outputted from the index decoding unit.

Owner:LG ELECTRONICS INC

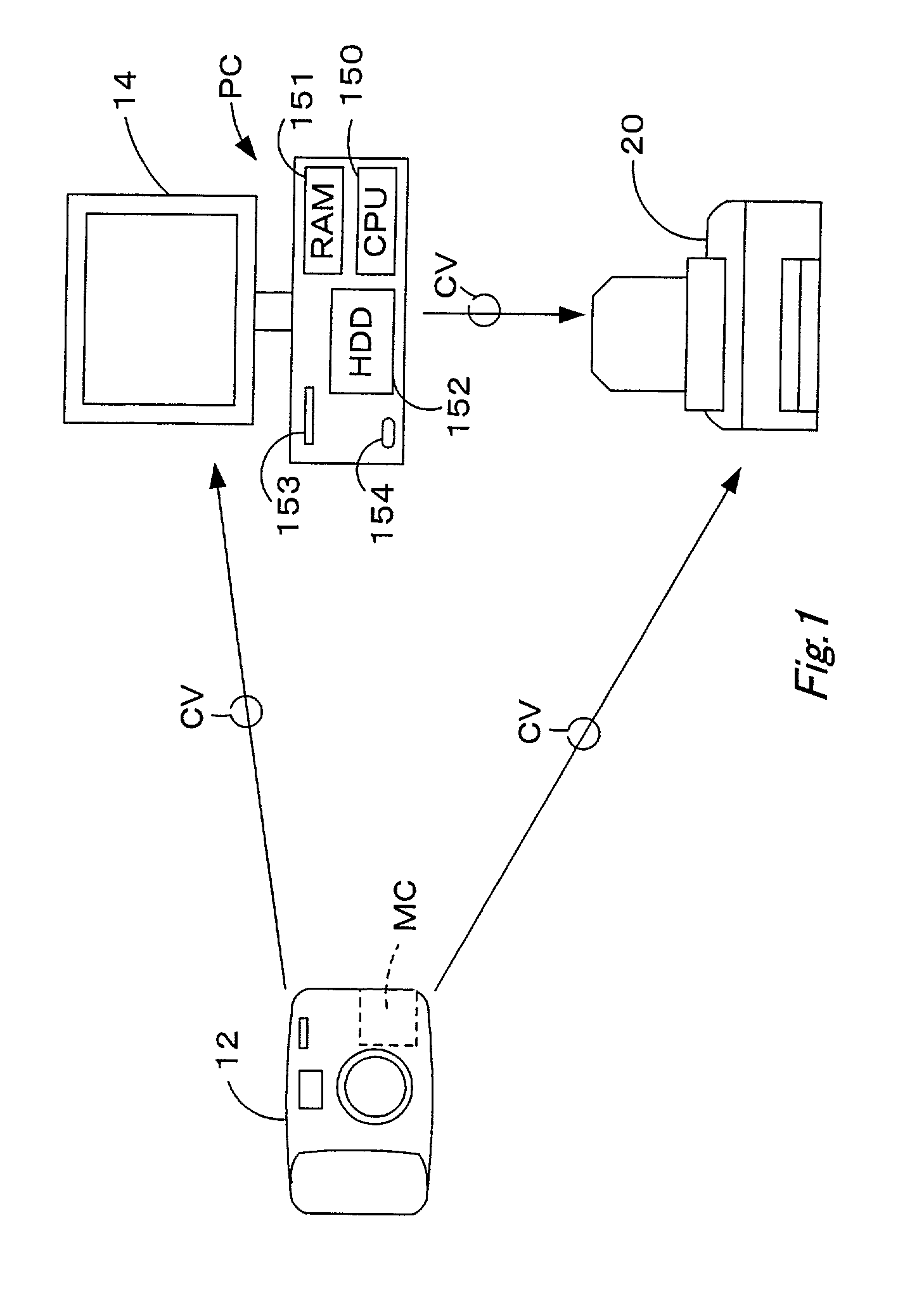

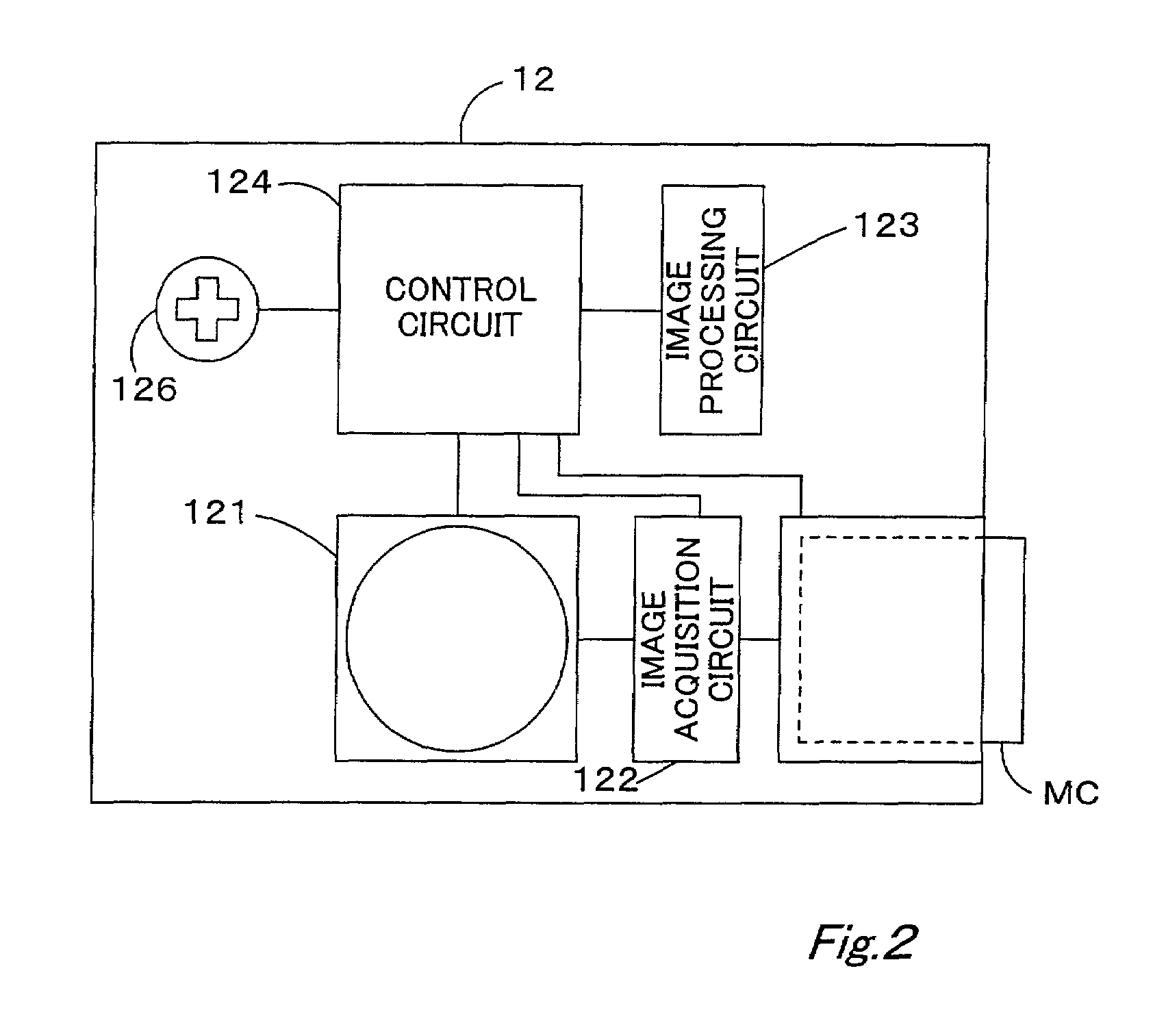

Image processing apparatus

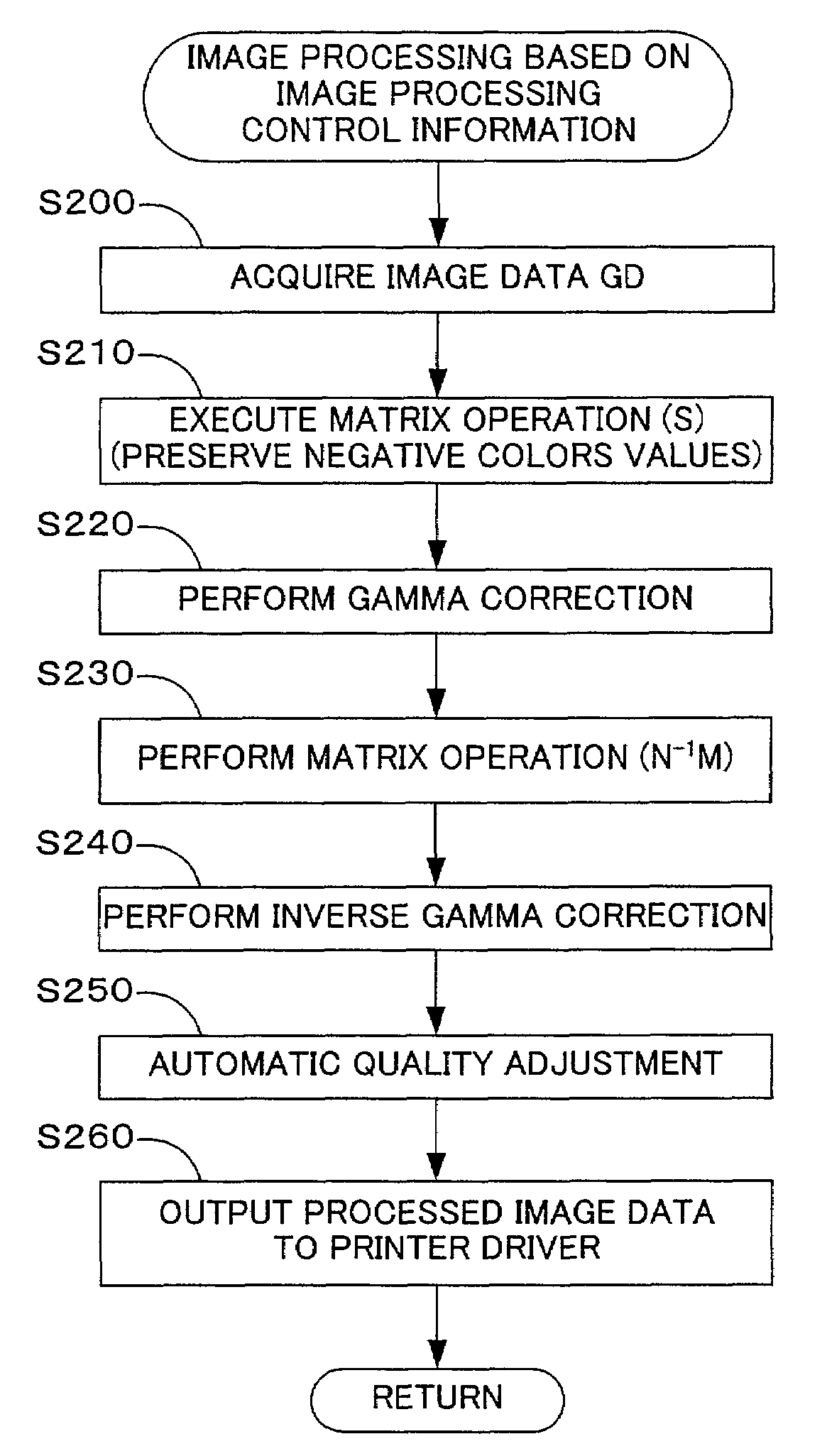

InactiveUS7253923B2Excellent toneReduce colorDigitally marking record carriersDigital computer details18-bitTO-18

CPU 150 performs a matrix operation on image data GD, and then increases the effective digit place number of the color values of the image data GD to increase the tone number of the image data GD from 8-bit tone to 18-bit tone. CPU 150 performs a gamma correction process, a matrix operation N−1M, and an inverse gamma correction process, and then restores the tone number of the image data GD to the original 8-bit tone, and performs automatic quality adjustment. As a result, the 8-bit tone of the original image data GD is preserved throughout image processing, and reproductive color number of the image data GD is preserved as well.

Owner:SEIKO EPSON CORP

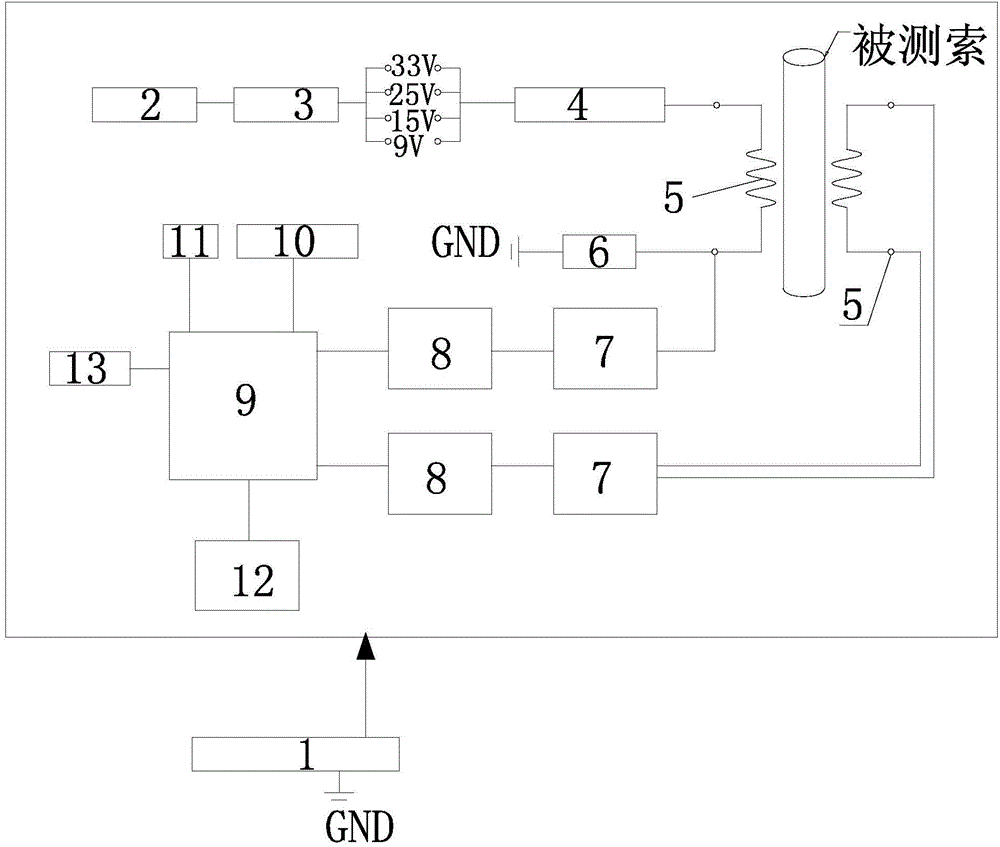

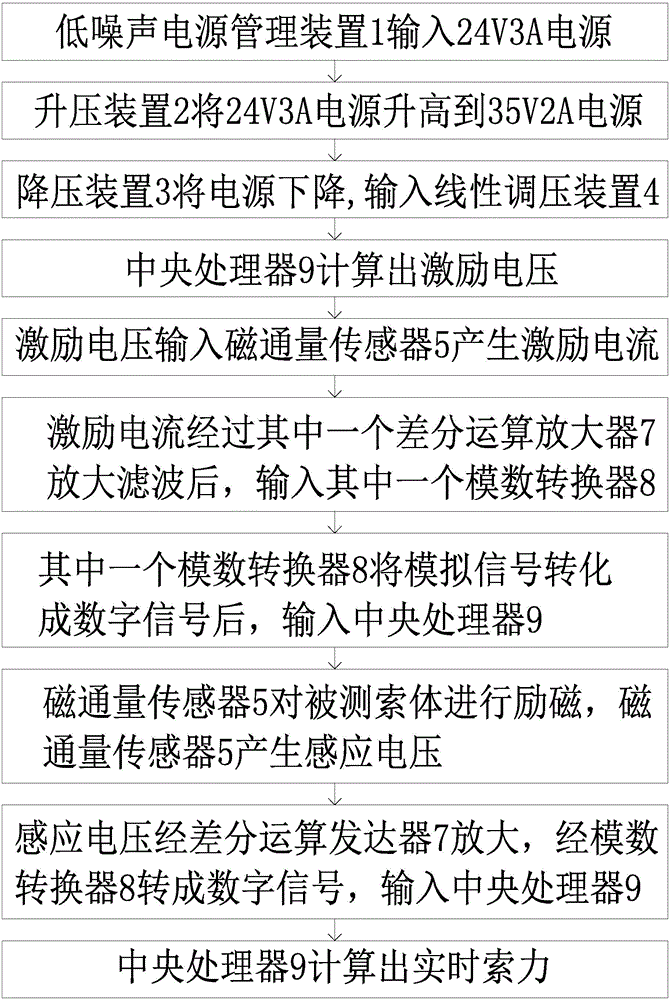

High-precision cable force testing instrument of magnetic permeability cable and test method thereof

InactiveCN104807585AIncreased durabilityHigh precisionApparatus for force/torque/work measurementLow noise18-bit

The invention discloses a high-precision cable force testing instrument of a magnetic permeability cable and a test method thereof. The testing instrument comprises a low-noise power source management device, a boost device, a voltage drop device, a linear voltage adjustment device, a magnetic flux sensor, an MOS (Metal Oxide Semiconductor) tube, two differential operational amplifiers, two analog-digital converters, a central processor, a 485 isolation circuit, a network card and a SD (Security Digital) memory card storage. A cable body to be tested does not need clear boundary conditions, nearly all the magnetic permeability cable can be used, and the application range is particularly wide; the durability of each element is good, and long-term field application can be realized; 18-bit high-speed AD is adopted, so the precision is high and the measurement is accurate; an industrial grade magnetic coupling isolation 485 special chip is adopted, isolation voltage reaches 5000 V, and 15kV electrostatic interference can be resisted; a 10 / 100Mb / s self-adaption industrial grade network card chip is adopted, and error-free transmission can reach 150 m.

Owner:SHANGHAI TONGLEI CIVIL ENG TECH +1

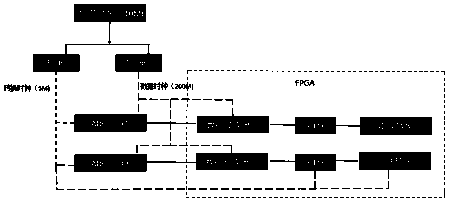

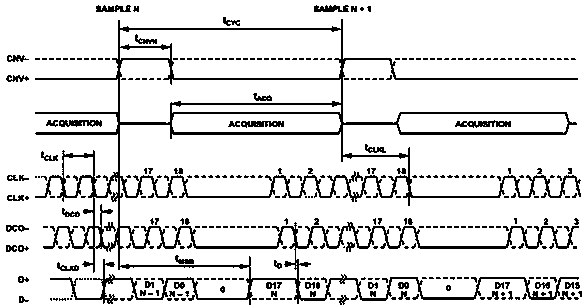

High-speed signal sampling system

InactiveCN109412590ASave global clock resourcesConvenient verificationPulse automatic controlAnalogue-digital converters18-bitAnalog signal

The invention discloses a high-speed signal sampling system. The high-speed signal sampling system comprises a clock generation module, a frequency division unit, a frequency multiplication unit, an ADC module and an FPGA module; a clock signal output end of the clock generation module is connected to the frequency division unit and the frequency multiplication unit separately; a conversion clocksignal output end of the frequency division unit and a data clock signal output end of the frequency multiplication unit are connected to an analog signal input end of the ADC module; a digital signaloutput end of the ADC module is connected to the FPGA module; and the FPGA module includes two data channels, each of which is composed of a data receiving unit, a FIFO storage unit, and a serial-to-parallel conversion unit that are sequentially connected; the data clock signal output end is connected to the data receiving unit of each data channel separately, and the conversion clock signal output end is connected to the FIFO storage unit and the serial-to-parallel conversion unit separately. The high-speed signal sampling system is expanded to 16 channels through a dual channel sampling method, and finally the 64 channel 18 bit 5 MSPS acquisition system is reached; so that the sampling system has a high sampling rate, high contrast and high sampling accuracy.

Owner:CHENGDU GOLDTEL IND GROUP

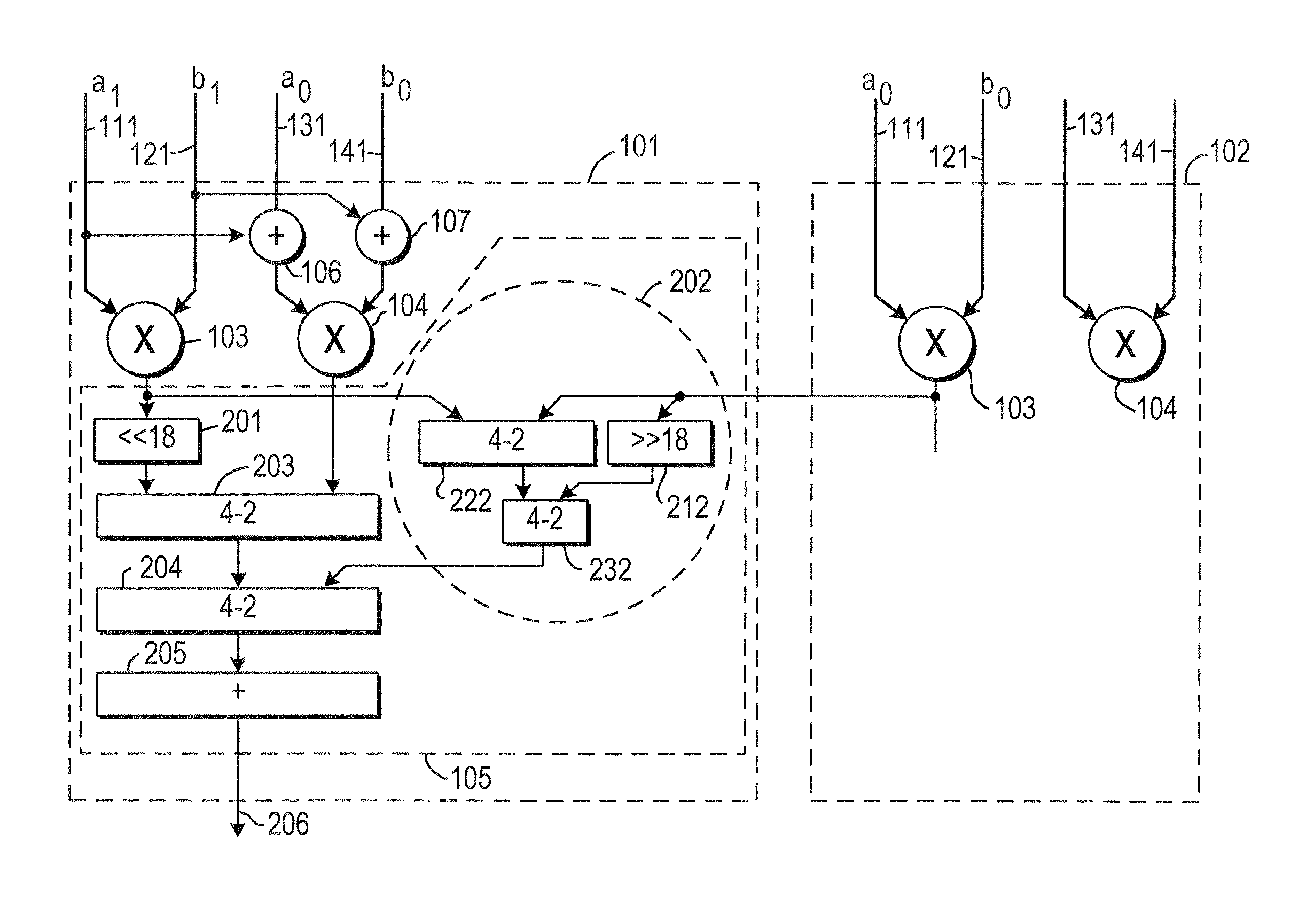

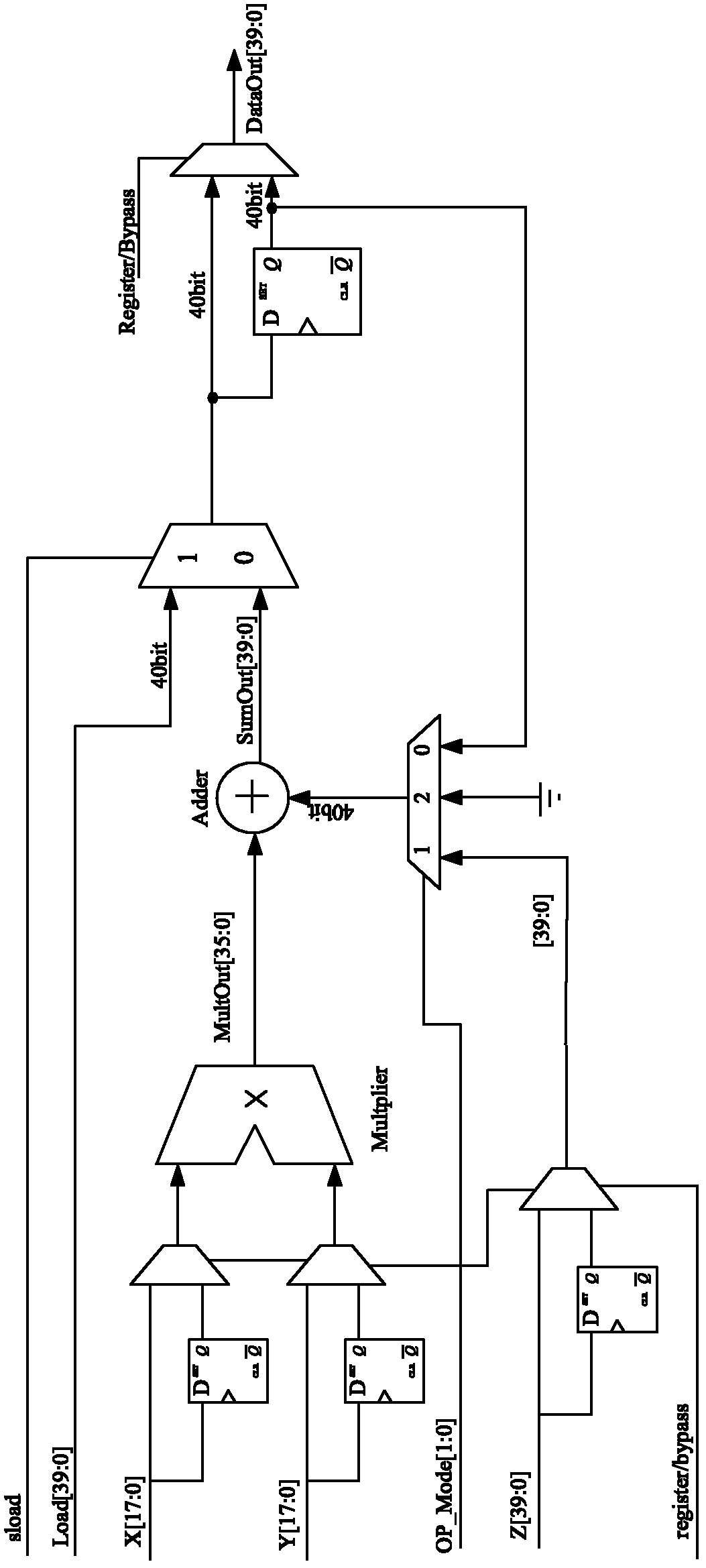

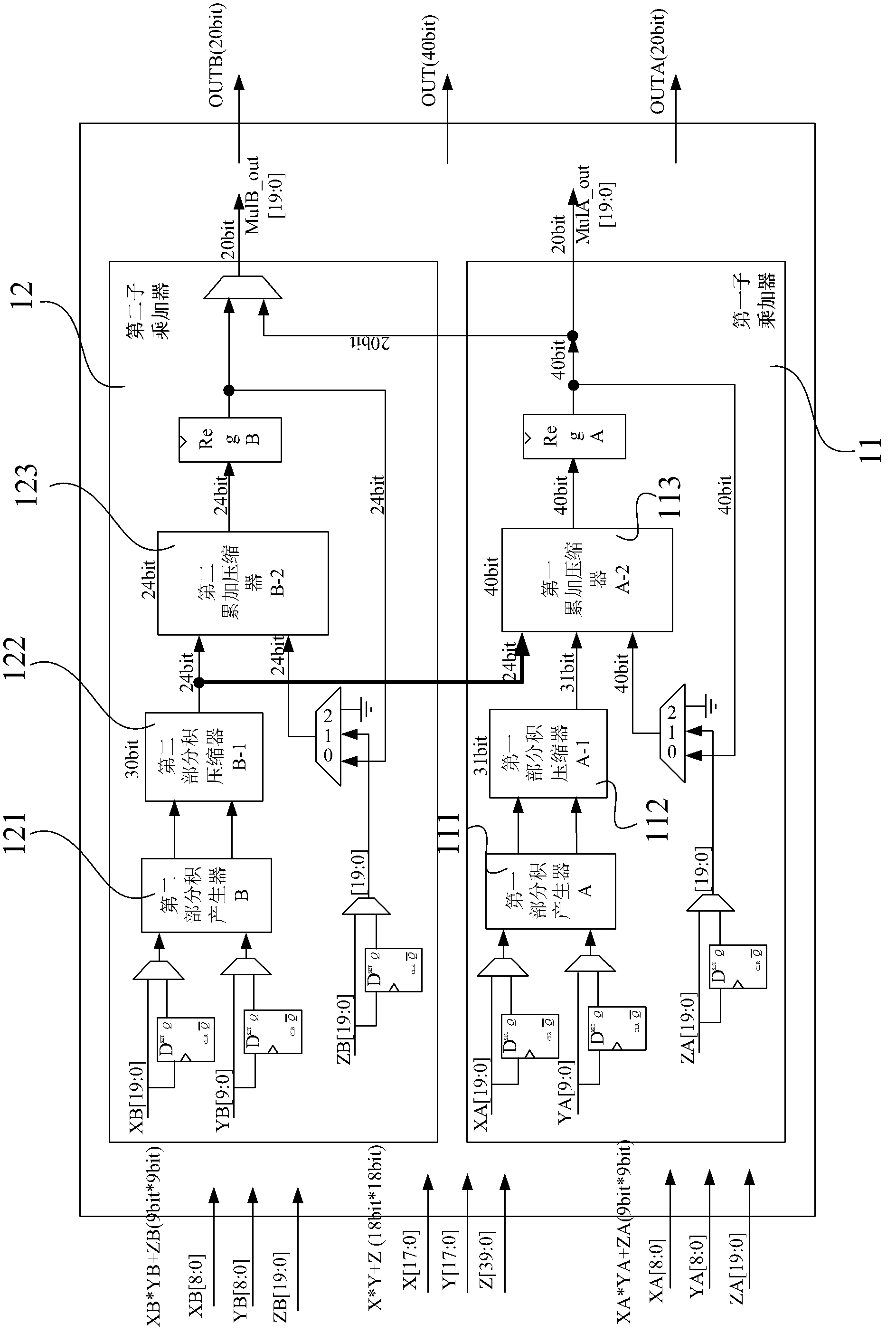

Multiply add accumulator

ActiveCN103257845AIncrease profitFast operationDigital data processing details18-bitResource utilization

The invention relates to a multiply add accumulator which comprises more than one auxiliary multiply add accumulators. The multiply add accumulator comprises two auxiliary multiply add accumulators, wherein each auxiliary multiply add accumulator particularly comprises a partial product generator, a partial product compressor and an accumulation compressor. The partial product generator is used for multiplying a multiplier smaller than a first-digit threshold value by a multiplicand smaller than the first-digit threshold value to obtain partial product data; the partial product compressor is used for compressing the partial product data to obtain partial product compression data; and the accumulation compressor is used for compressing data of partial products and accumulating addition data to obtain summation data. The multiply add accumulator can achieve one 18*18 bit or two parallel 9*9 bit multiplication, addition and accumulation operation, is high in resource utilization rate, improves the arithmetic speed in operating large bit-width data and improves resource utilization rate when operating small bit-width data.

Owner:CAPITAL MICROELECTRONICS

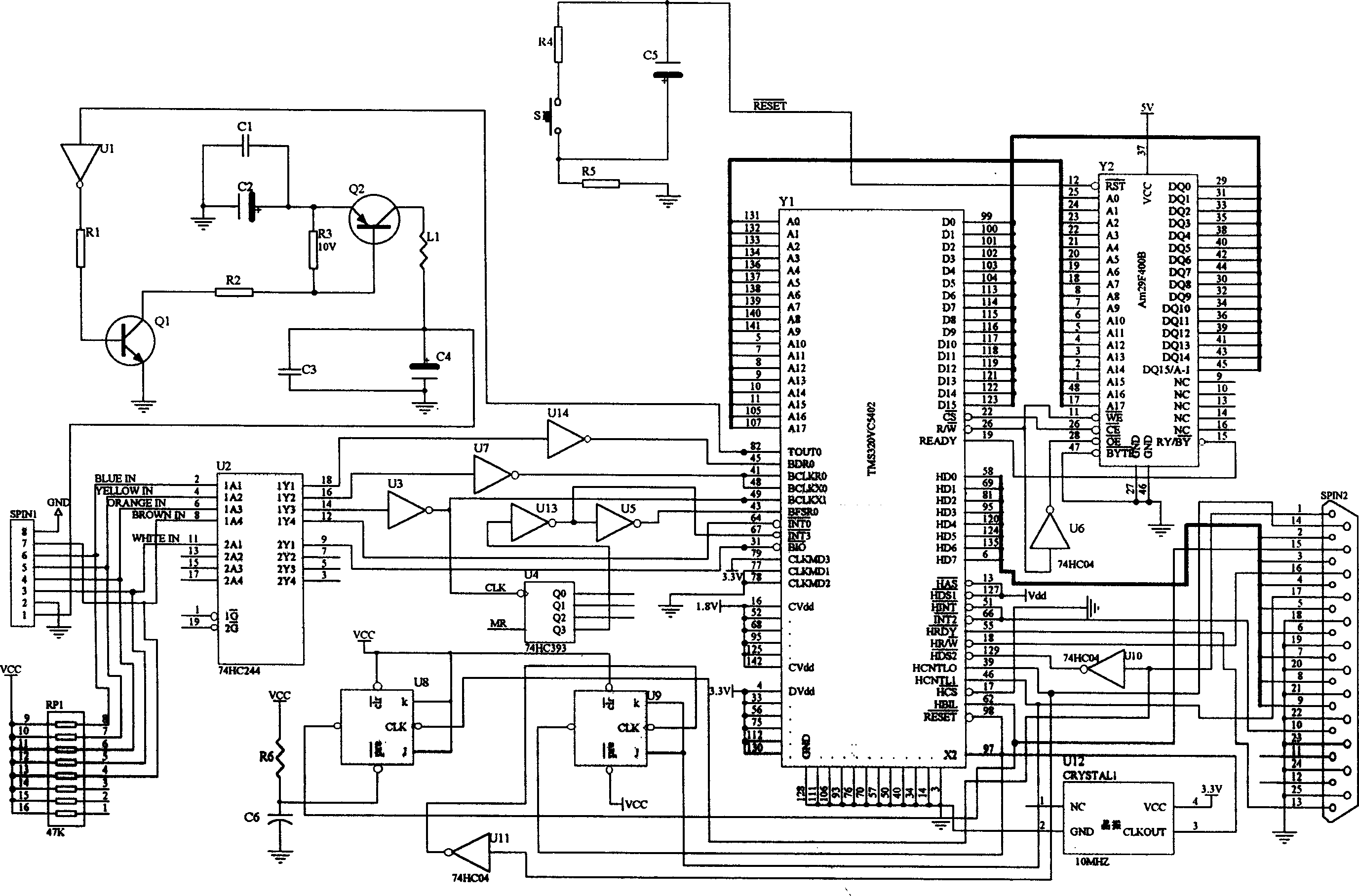

High speed portable scanner based on DPS

InactiveCN1480897AObvious superiorityWide range of changesCharacter and pattern recognition18-bitTO-18

The scanner is composed of scanning head and control circuit. The character is that DSP digital signal processor is utilized. The storage unit includes DSP supplied 18 bits address line and 16 bits data line connected to 18 bits address line and 16 bits data line of flash memory Am29F400B. Buffer 74HC244 reshapes electrical level of signal unit of the scanning head. Serial CCD image signal of reshaped output is sent to BDR0 multichannel-buffered serial receiving pins. DSP converts the said serial signal to 16 bits parallel signal, which is received in DMA mode and temporary stored in RAM. Finally, data in the RAM are sent to data bus D0-D15. The invented scanner can complete scanning operation independently without computer, and features high adaptability, and high quality.

Owner:ANHUI UNIVERSITY

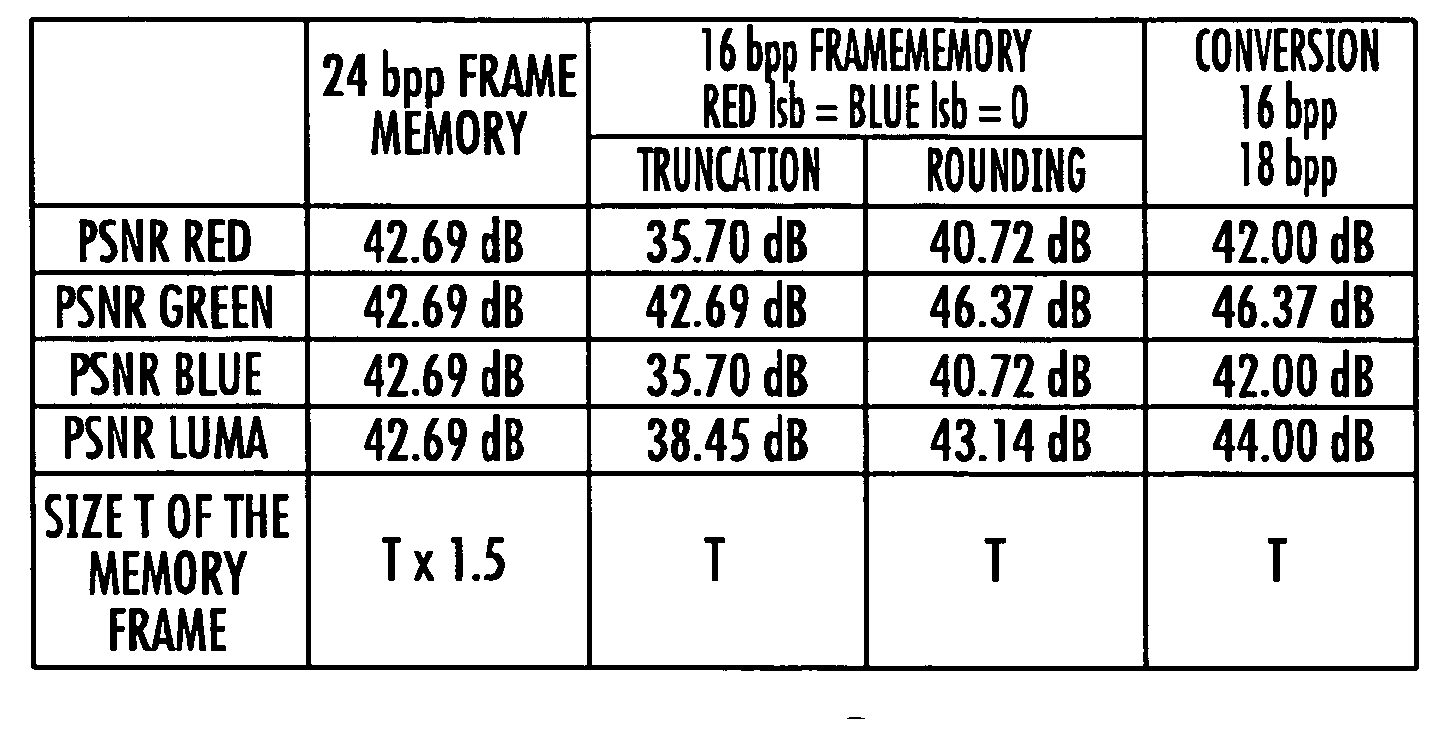

Image processing method and device

InactiveUS20060181724A1Quality improvementReduce capacityDigitally marking record carriersDigital computer details18-bitImaging processing

This image processing method for the conversion of an image with a first number of bits per pixel, for example 16 bits per pixel, into an image with a second number of bits per pixel, for example 18 bits per pixel, includes generating additional coding bit values for the components (Ri, Gi, Bi) of each pixel starting from the component values of adjacent pixels and generating the converted signal from the additional coding bits.

Owner:ST ERICSSON SA

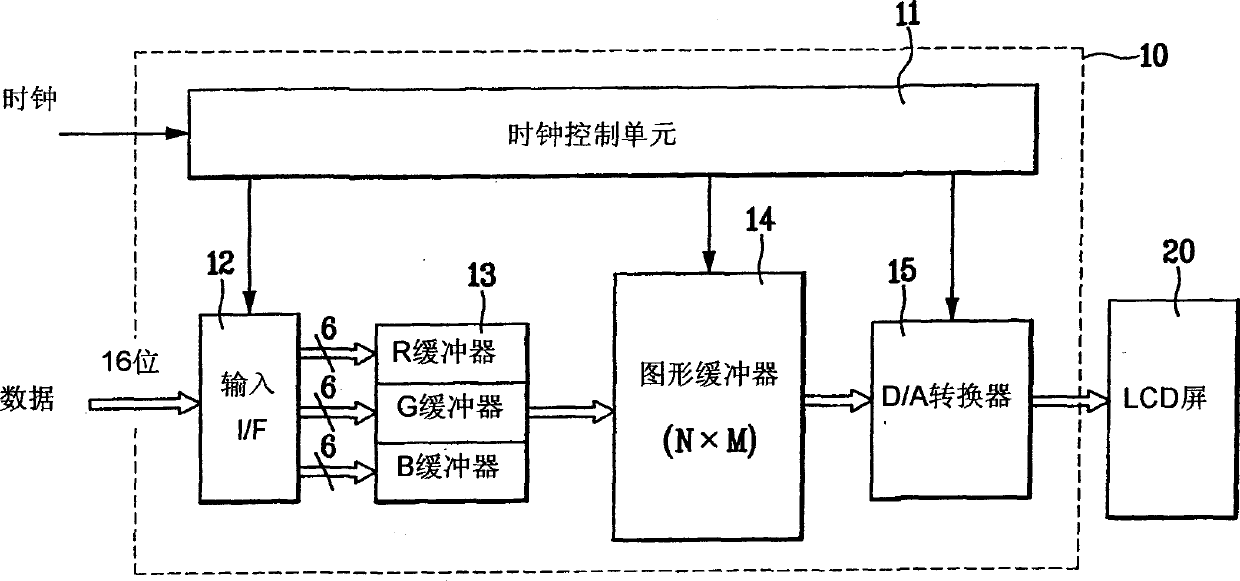

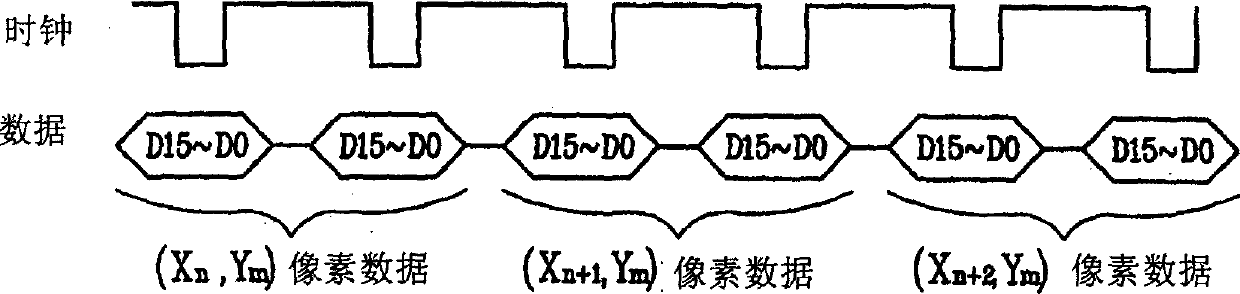

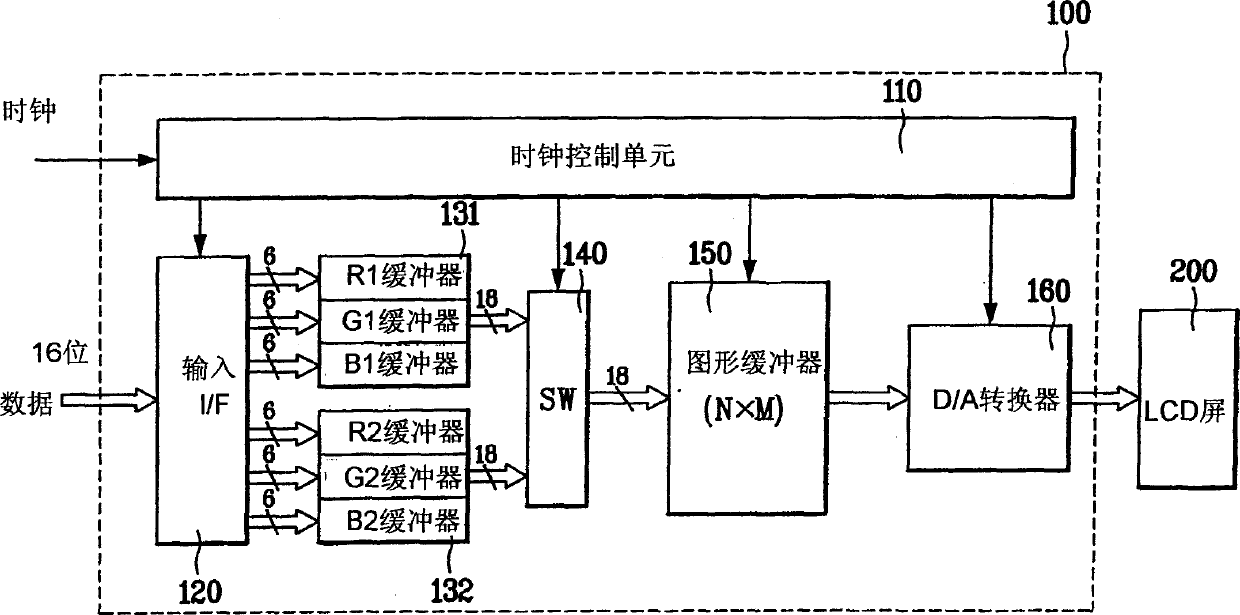

Apparatus for controlling color liquid crystal display and method thereof

An apparatus for controlling a color liquid crystal display and method thereof are disclosed, by which data transfer efficiency is raised in a manner of changing an input interface type of an LCD controller, by which a same-sized video can be outputted with a smaller number of clocks, and by which practical applicability of CPU is enhanced. The present invention includes a clock control unit providing a clock for operating each module, an interface unit receiving 16-bit data each clock according to a control signal of the clock control unit, a pair of 18-bit RGB buffers storing data transferred via the interface unit, a graphic buffer storing graphic data provided from a pair of the RGB buffers, a switching block storing data signals provided from a pair of the RGB buffers in the graphic buffer, and a digital / analog converting unit converting digital R / G / B data stored in the graphic buffer to an analog signal to output.

Owner:LG ELECTRONICS INC

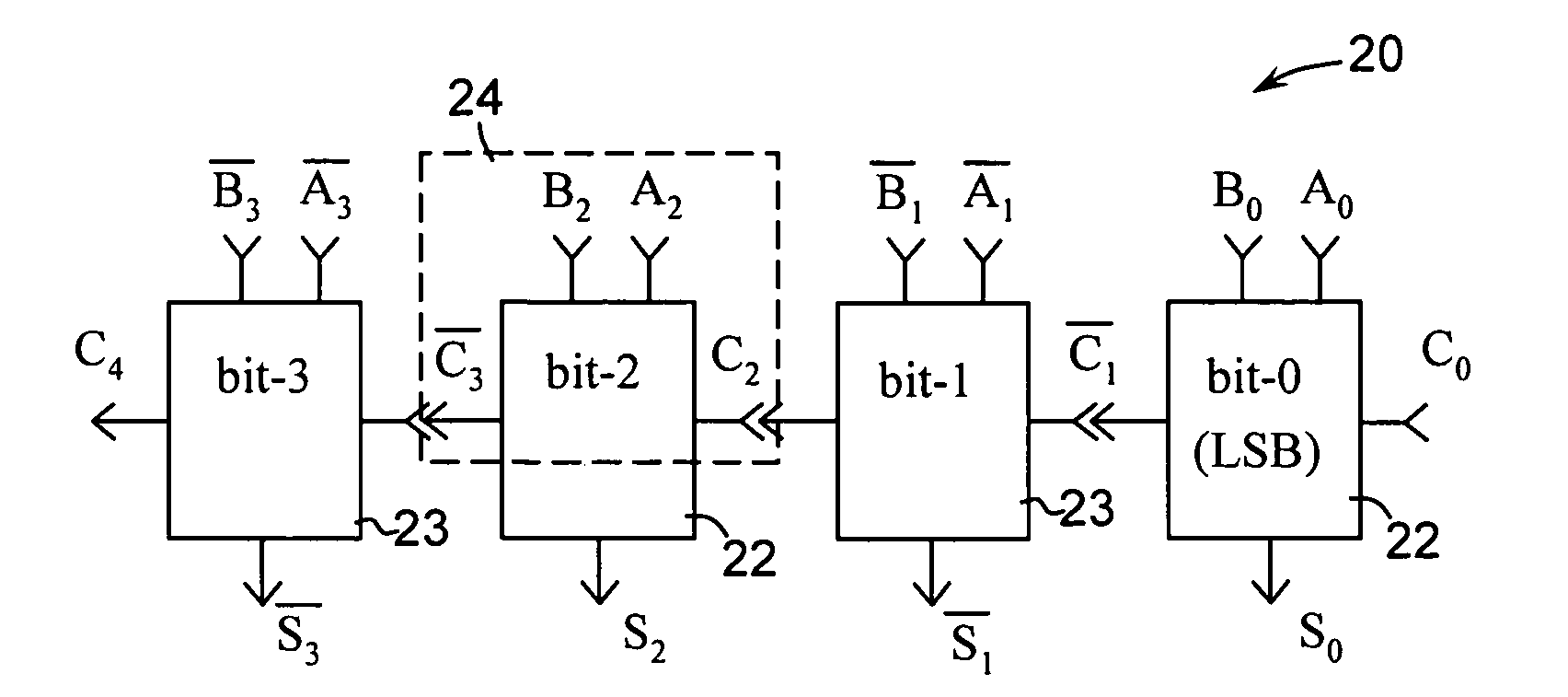

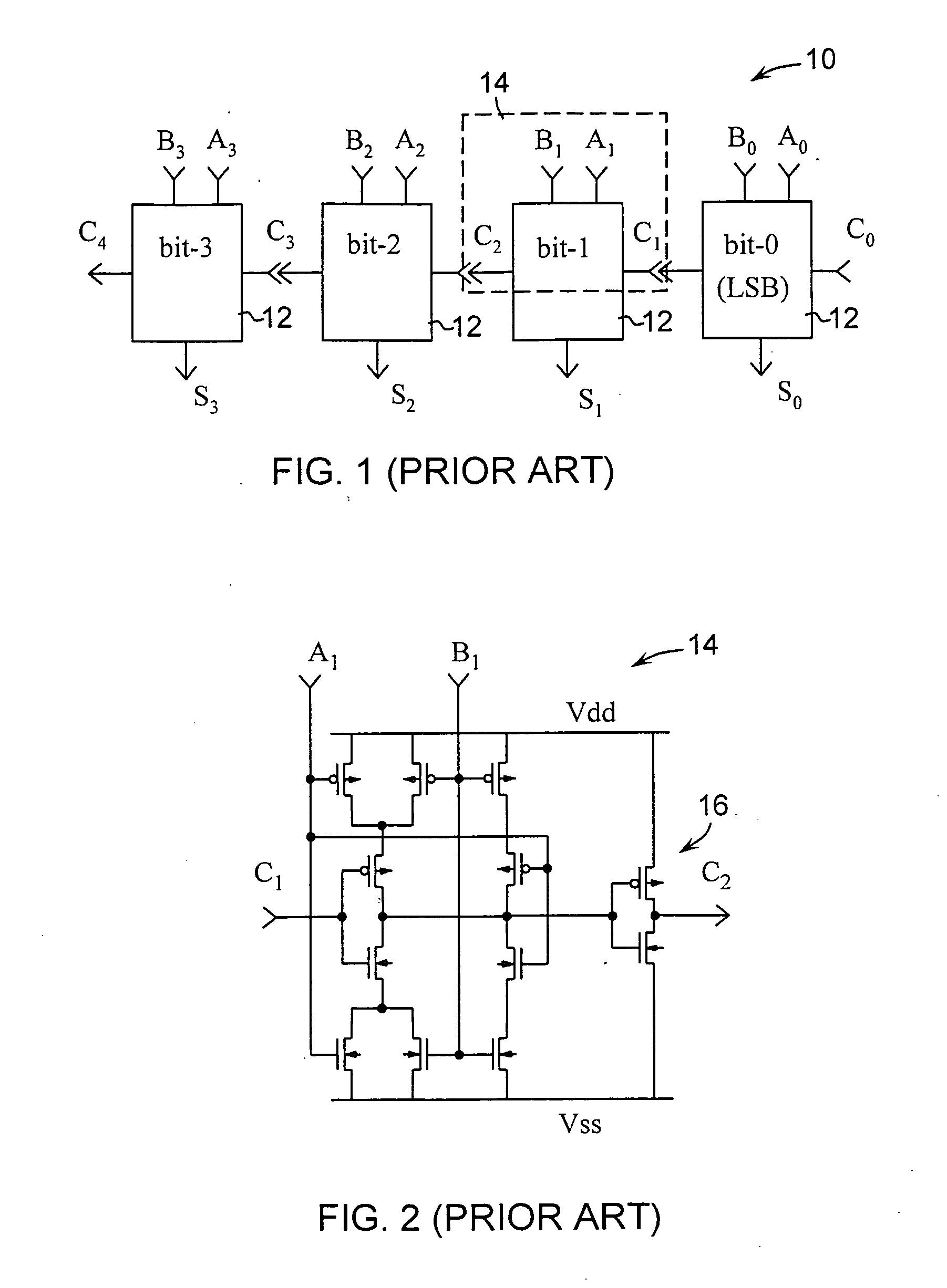

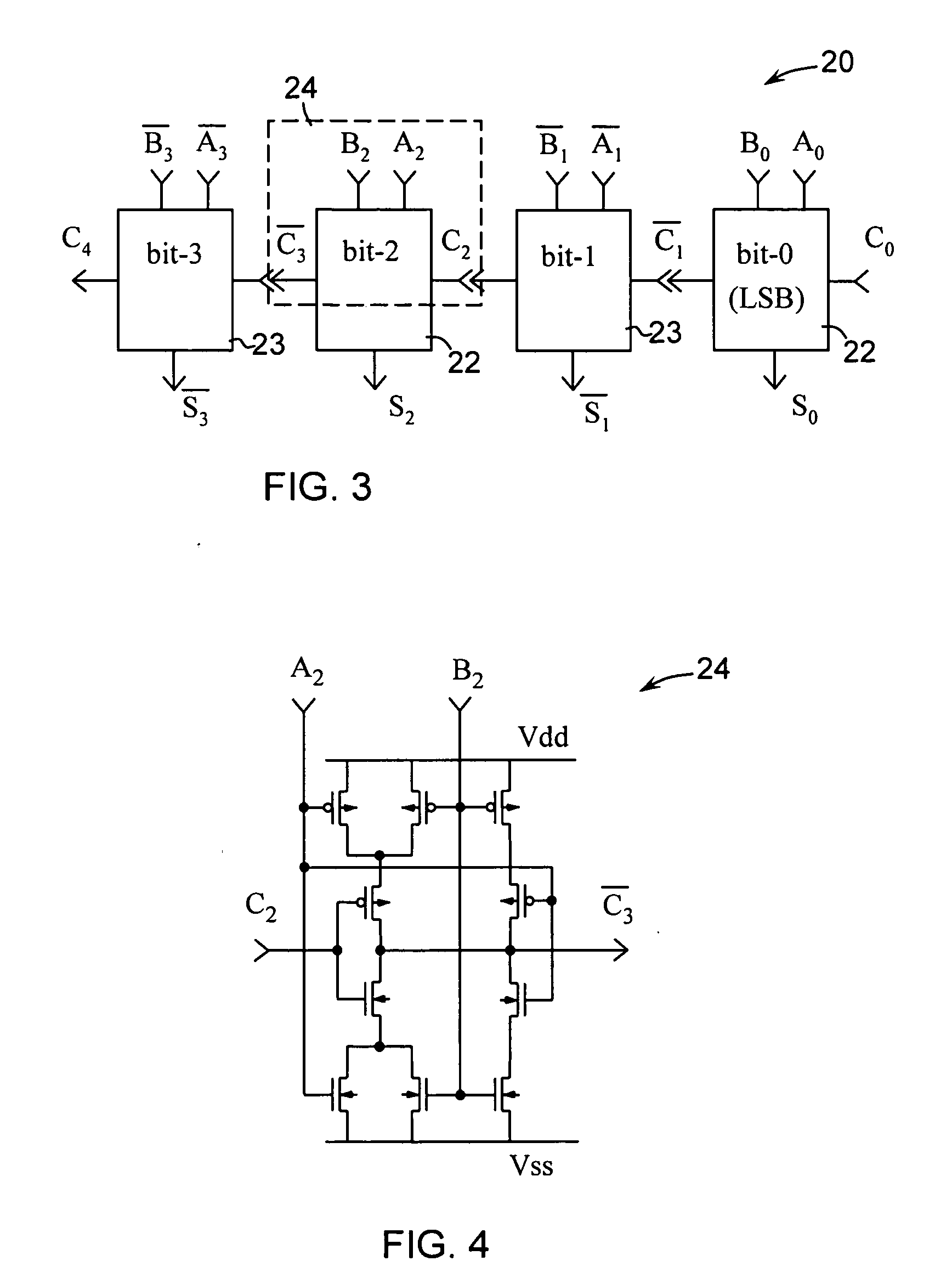

Inversion of alternate instruction and/or data bits in a computer

InactiveUS20080177817A1Addressing slow performancePerformed quicklyComputations using contact-making devicesComputation using non-contact making devices18-bitProcessor register

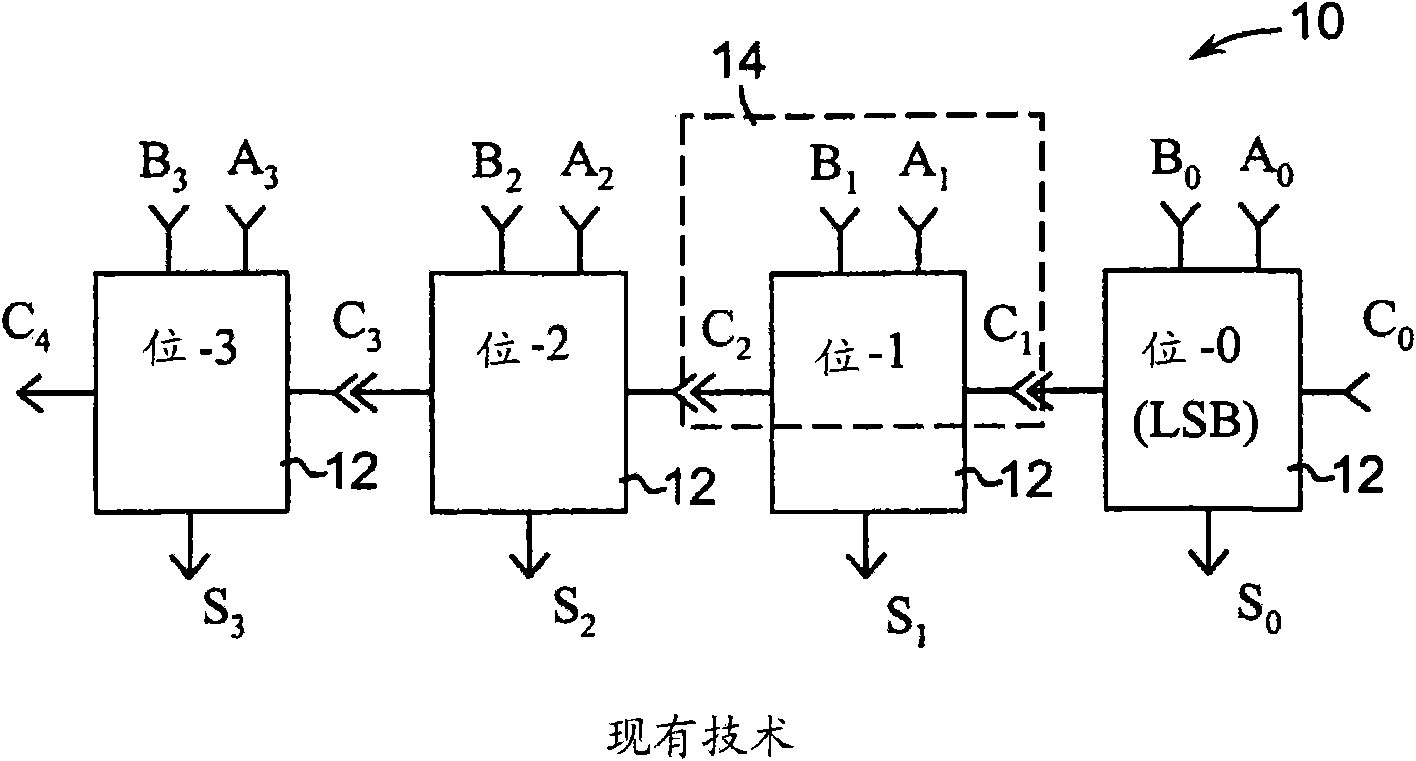

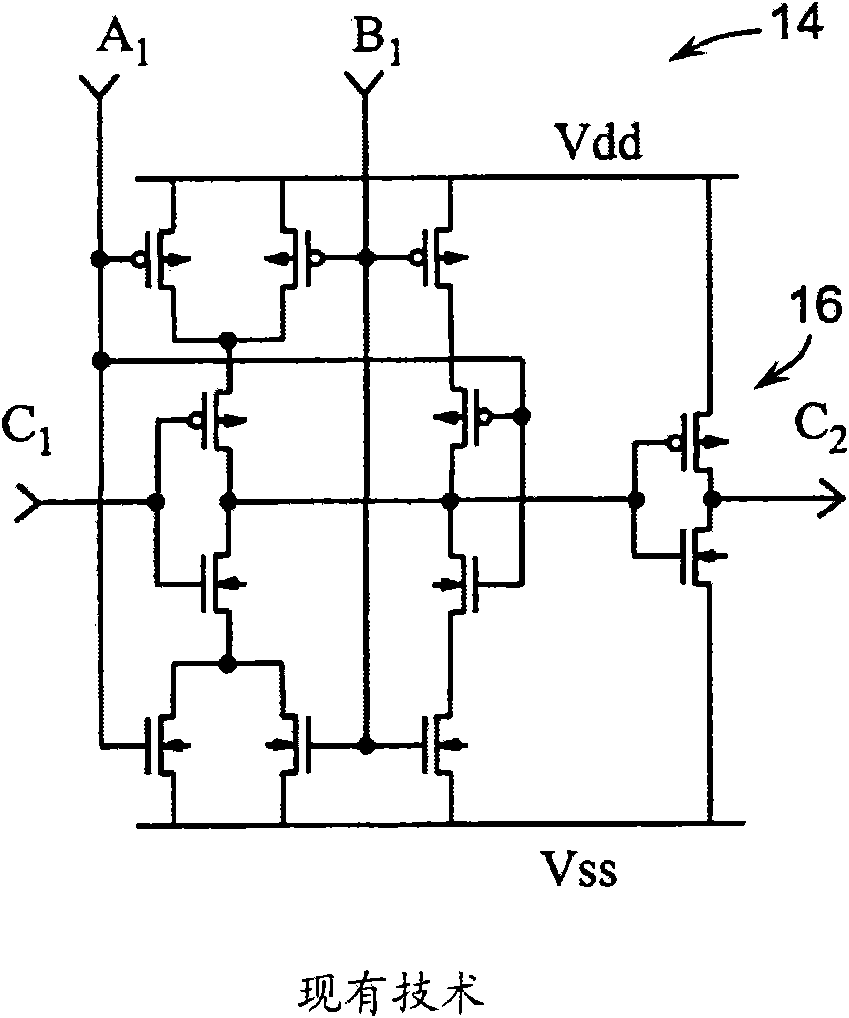

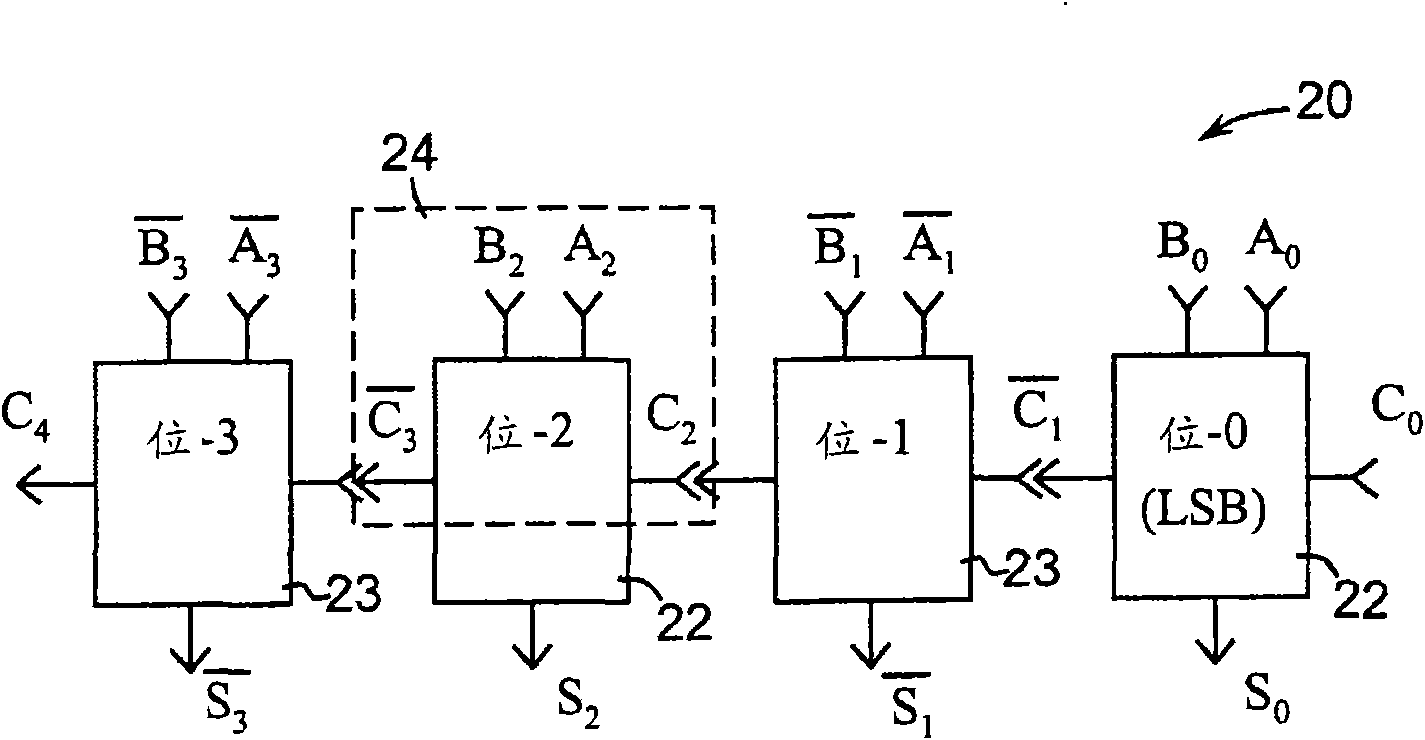

A basic computer circuit (30) with alternate bits inverted. Two 18-bit registers (32, 34) are connected to ALU (36) to perform ripple-carry addition, wherein 1-high number representation is implemented in the circuit portions corresponding to odd-numbered bit positions, and inverse representation, in even-numbered bit positions. Owing to alternate bit inversion, carry calculation for 1-bit addition can be performed in only one inverter latency, resulting in a fast 18-bit adder with small die area. Inverted number representation in alternate bit positions can be used in other combinatorial circuits, where an extra inverter stage is conventionally required to adjust the logic level, to reduce latency of operation and die area.

Owner:VNS PORTFOLIO LLC

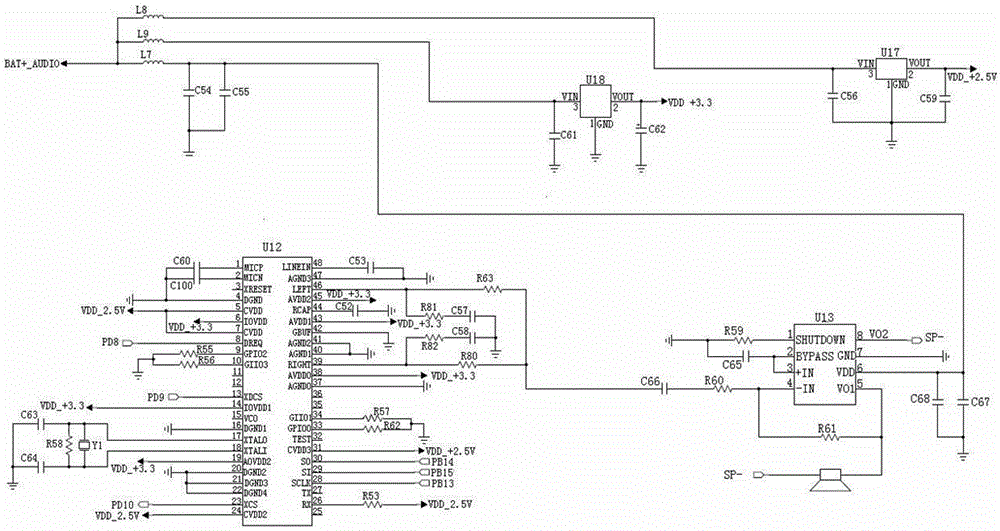

Speech circuit of smart key

The invention discloses a speech circuit of a smart key. The speech circuit comprises an audio decoding chip U12, an audio power amplifier chip U13 and voltage stabilizing chips U18 and U17. The audio decoding chip U12 comprises forty-eight pins, and the audio power amplifier chip U13 comprises eight pins. The speech circuit receives FLASH bit streams through a serial port of the audio decoding chip U12, inputted bit streams are decoded, a 18-bit oversampling multi-bit epsilon-delta DAC is reached through a digital volume controller to output decoded audio signals, the decoded audio signals are sent to the audio power amplifier chip U13 for audio power amplification, and the amplified signals are outputted by pins VO1 and VO2 of the audio power amplifier chip U13 to drive loudspeakers, so that speech output is realized.

Owner:重庆桦哲科技有限公司

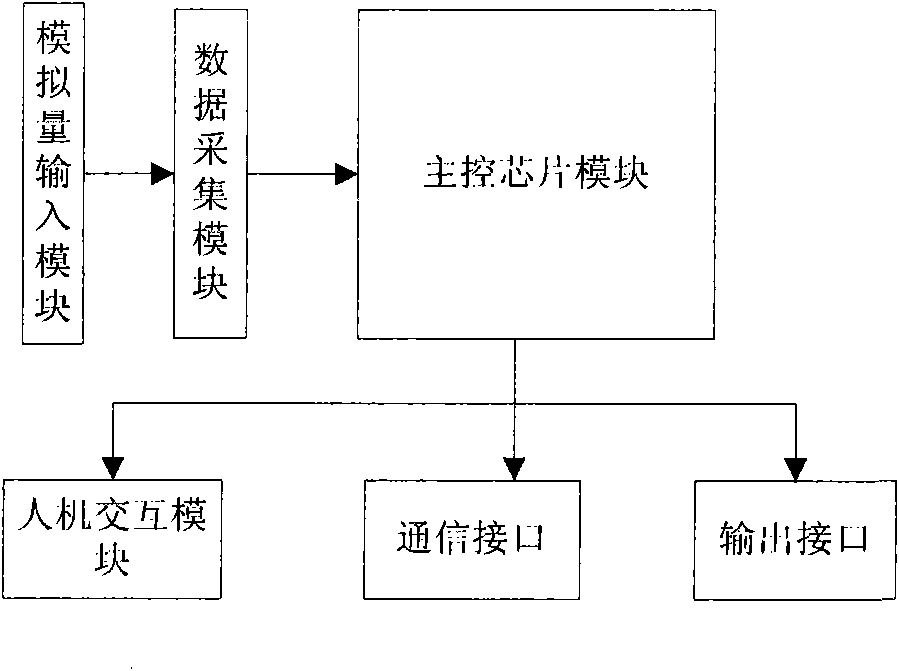

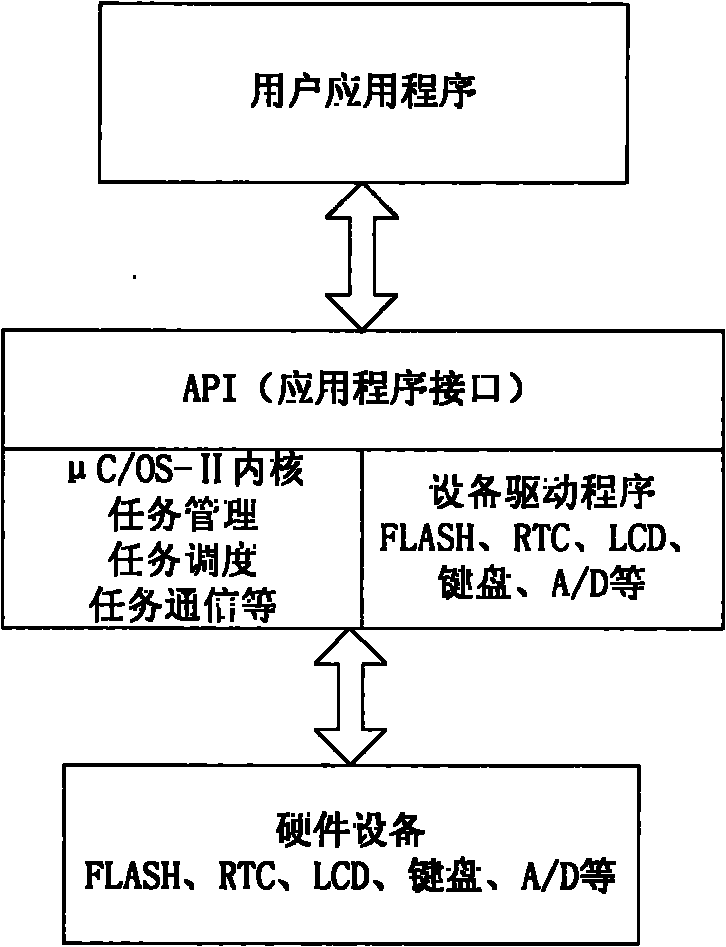

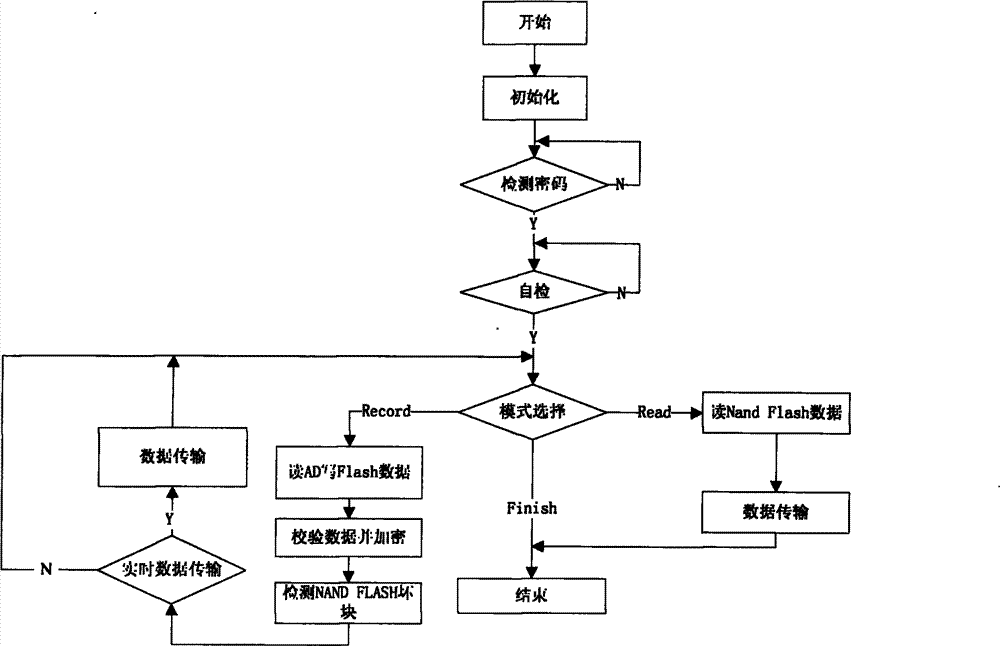

Task scheduling method of small multi-channel data recorder

ActiveCN102261929BReduce distractionsReal-time encryptionRecording measured values18-bitMulti machine

The invention relates to a task scheduling method of a data recorder. An ARM920T core processor is used as a master control chip of the data recorder; an 18-bit A / D chip is used for acquiring sensor data output by as many as 32 paths of analogue signals at the most and inputting the acquired signals into a CPU (central processing unit); the sensor data is encrypted and resolved in real time in the CPU; and the data recordercan run independently with an own power supply when an external power supply is failed, and also can perform autonomous multi-machine communication. The data recorder provided by the invention can acquire and store the data of multiple sensors on industrial instruments, provide comprehensive data for researching running conditions of the instruments, simultaneously facilitate detection and maintenance of devices, improve production level and provide effective running recording and control measures for related manufacture factories.

Owner:BEIJING INFORMATION SCI & TECH UNIV +1

Inversion of alternate instruction and/or data bits in a computer

InactiveCN101681250AComputation using non-contact making devicesMachine execution arrangements18-bitProcessor register

A basic computer circuit (30) with alternate bits inverted. Two 18-bit registers (32, 34) are connected to ALU (36) to perform ripple-carry addition, wherein 1-high number representation is implemented in the circuit portions corresponding to odd- numbered bit positions, and inverse representation, in even-numbered bit positions. Owing to alternate bit inversion, carry calculation for 1 -bit addition can be performed in only one inverter latency, resulting in a fast 18-bit adder with small die area. Inverted number representation in alternate bit positions can be used in other combinatorial circuits, where an extra inverter stage is conventionally required to adjust the logic level, to reduce latency of operation and die area.

Owner:VNS业务有限责任公司