Large dynamic medium-high frequency analog signal digitization conversion circuit

A high-frequency analog and conversion circuit technology, applied in the direction of physical parameter compensation/prevention, etc., can solve the problems of reducing small signal processing capability, increasing chip power consumption, increasing chip noise, etc., to improve quantization resolution, expand processing range, Effects of spurious signals and noise floor reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

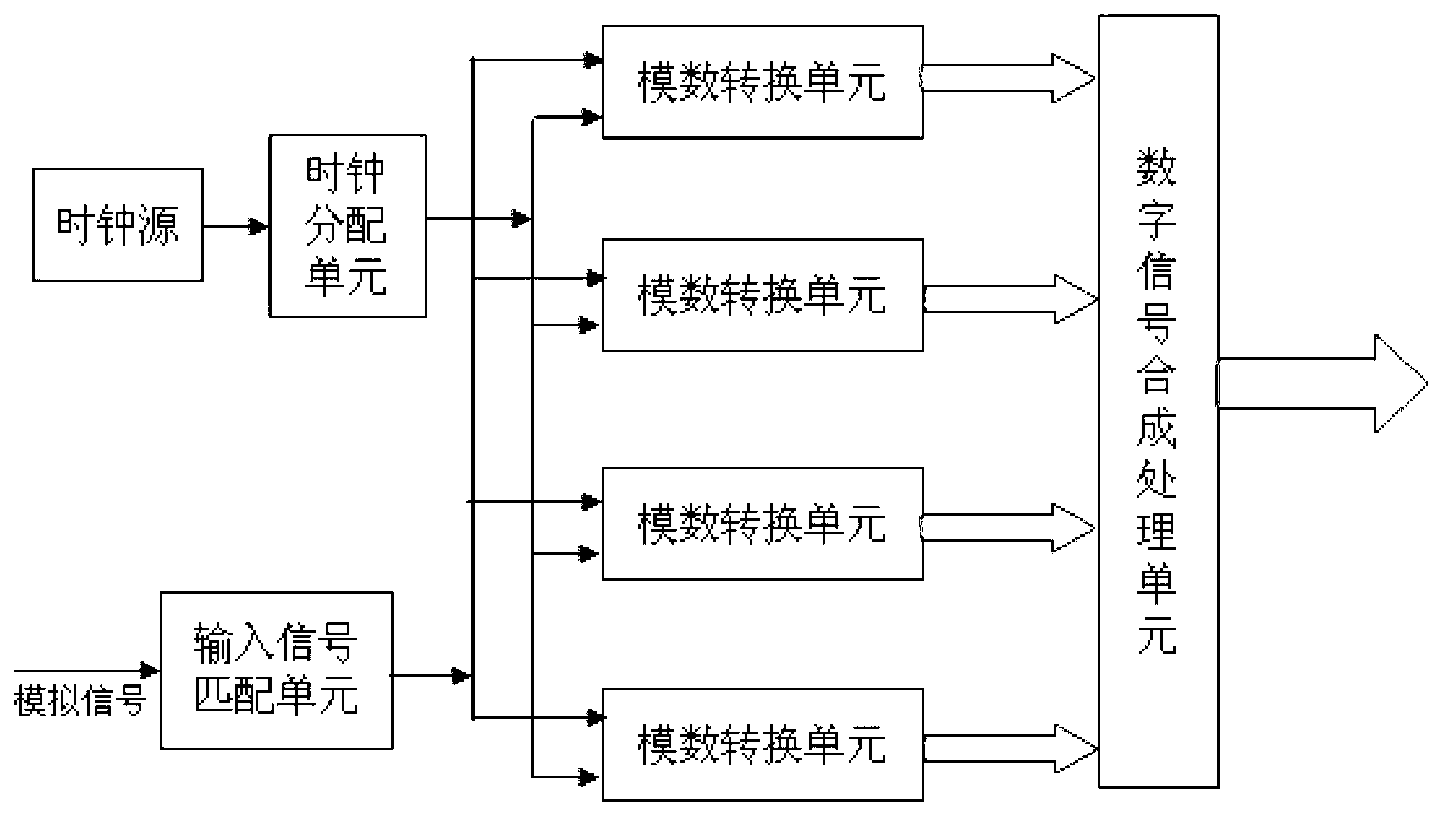

[0025] The schematic block diagram of the circuit design of this embodiment of the large dynamic medium and high frequency analog signal digitization conversion circuit is as follows: figure 1 as shown,

[0026] The clock source 6 is connected to the clock distribution unit 7. In this example, a 100MHz original frequency clock chip with low jitter and low phase noise is selected, and the spurious output spectrum is lower than -90dBm. The clock distribution unit 7 includes a clock distribution chip and its cooperating RC components. The dedicated clock processing chip in this example is a highly stable clock distribution chip with fs jitter.

[0027] 4 identical analog-to-digital conversion units, each containing an analog-to-digital conversion chip 4, a unified external voltage reference source and its matching resistance-capacitance components, and the four analog-to-digital conversion chips 4 are the same high-speed 16-bit analog-to-digital conversion chip. In this example...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More