Multiply add accumulator

A multiplier-adder and multiplier technology, which is applied in the field of multiplier-adder with bit width configuration resources, can solve problems affecting performance, etc., and achieve the effect of improving computing speed, improving resource utilization, and high resource utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

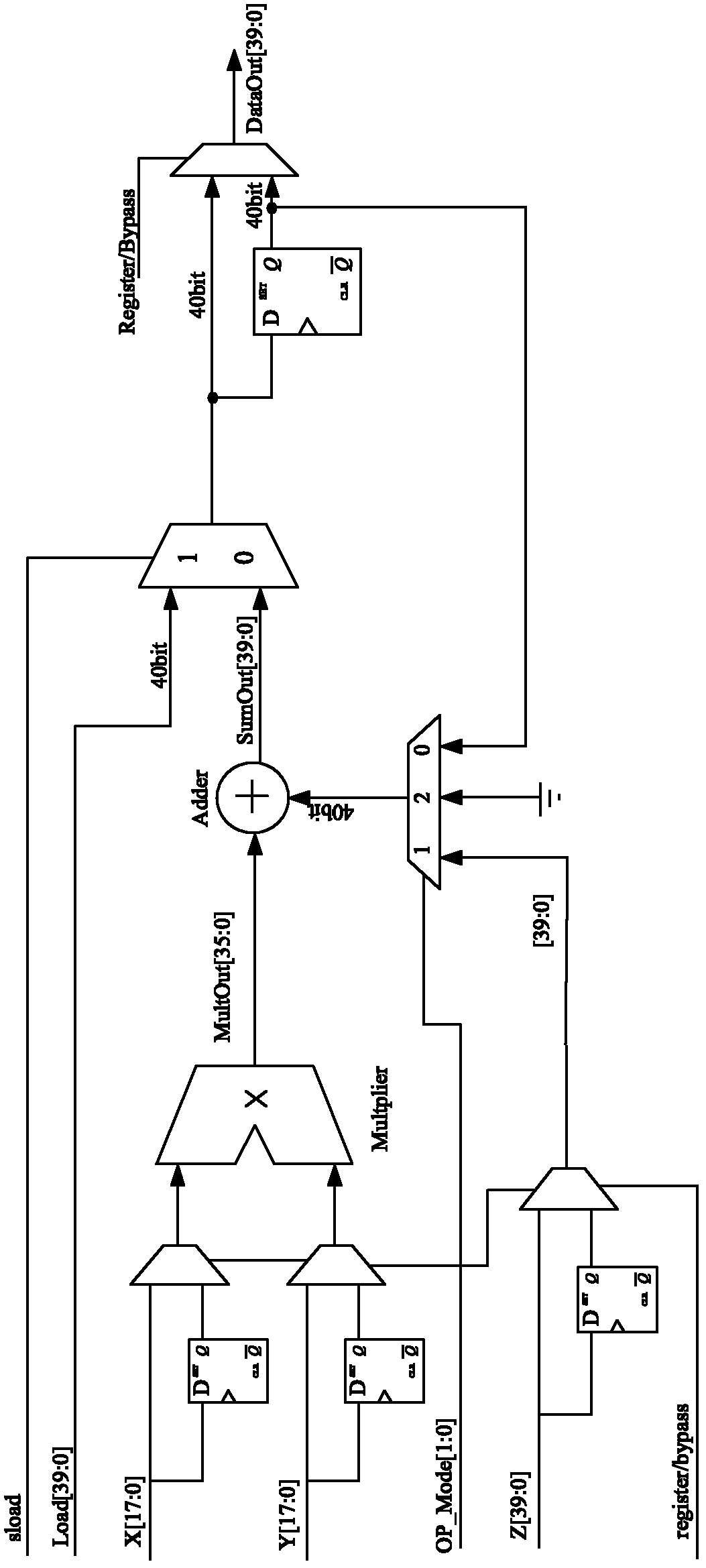

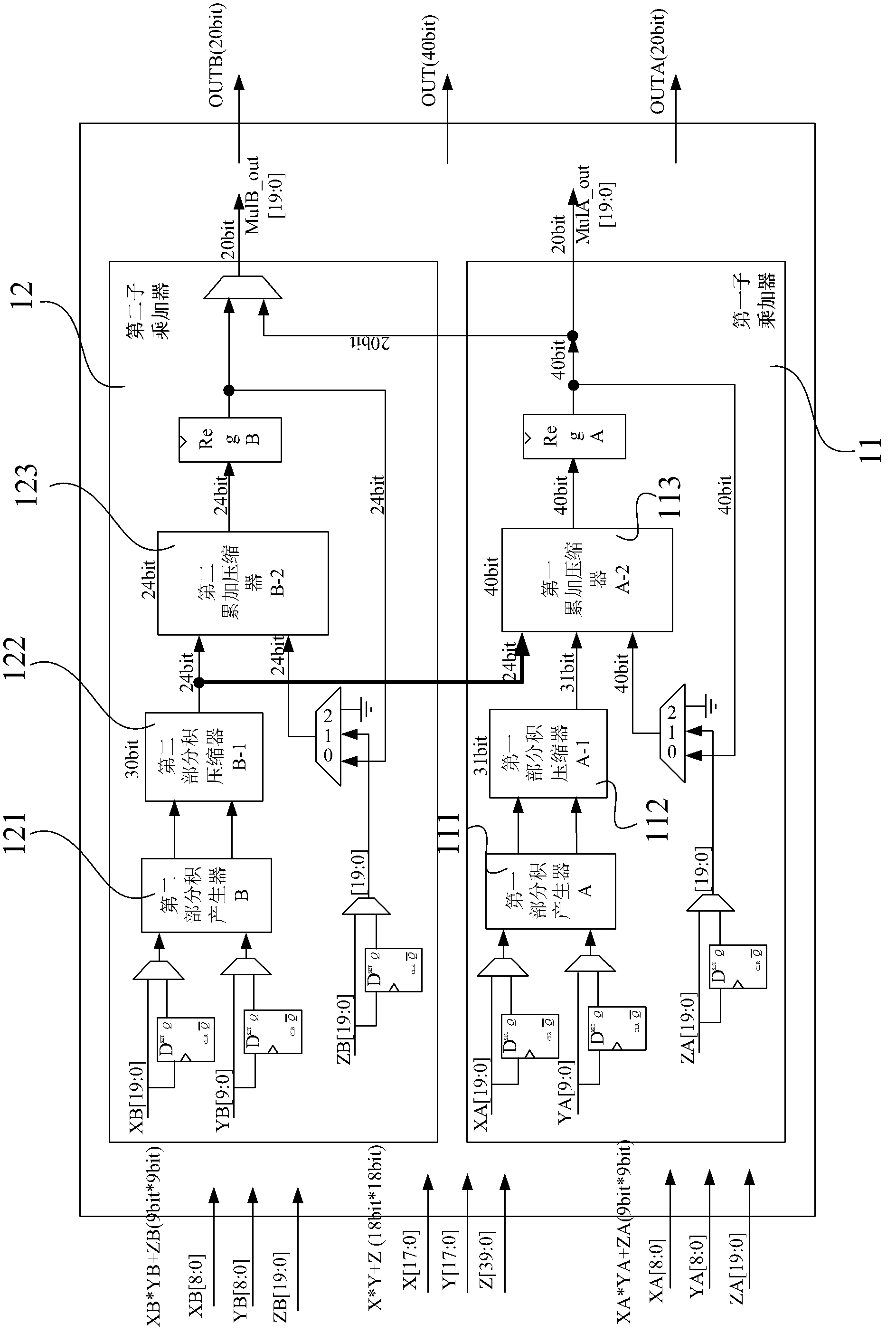

[0021] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

[0022] The multiplier-adder (MAC IP) of the present invention can realize a first digit threshold (first digit), such as 18*18bit (including Below) with 40bit accumulation operation, can also realize 2 parallel second digit thresholds (second digit), such as 9*9bit (including below) and with 20bit accumulation operation, support signed or unsigned number.

[0023] In MAC IP, in order to save the area and improve the operation speed, the Modified Radix-4booth Multipliers algorithm is adopted. At the same time, when the partial product (Partial Product) is accumulated, the compression technique in the algorithm is fully utilized, and the compression task is assigned to two compressors. The parallel implementation of the processor improves the operation speed. In addition, on the same IP resource, one 18*18bit or two 9*...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More