Calibration circuit eliminating capacitor mismatch error

A capacitance mismatch and calibration circuit technology, which is applied in the field of calibration circuits, can solve the problems of adding calibration DACs, not being able to compensate mismatch errors, and increasing circuit costs, so as to save layout area, maintain symmetry, and improve accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

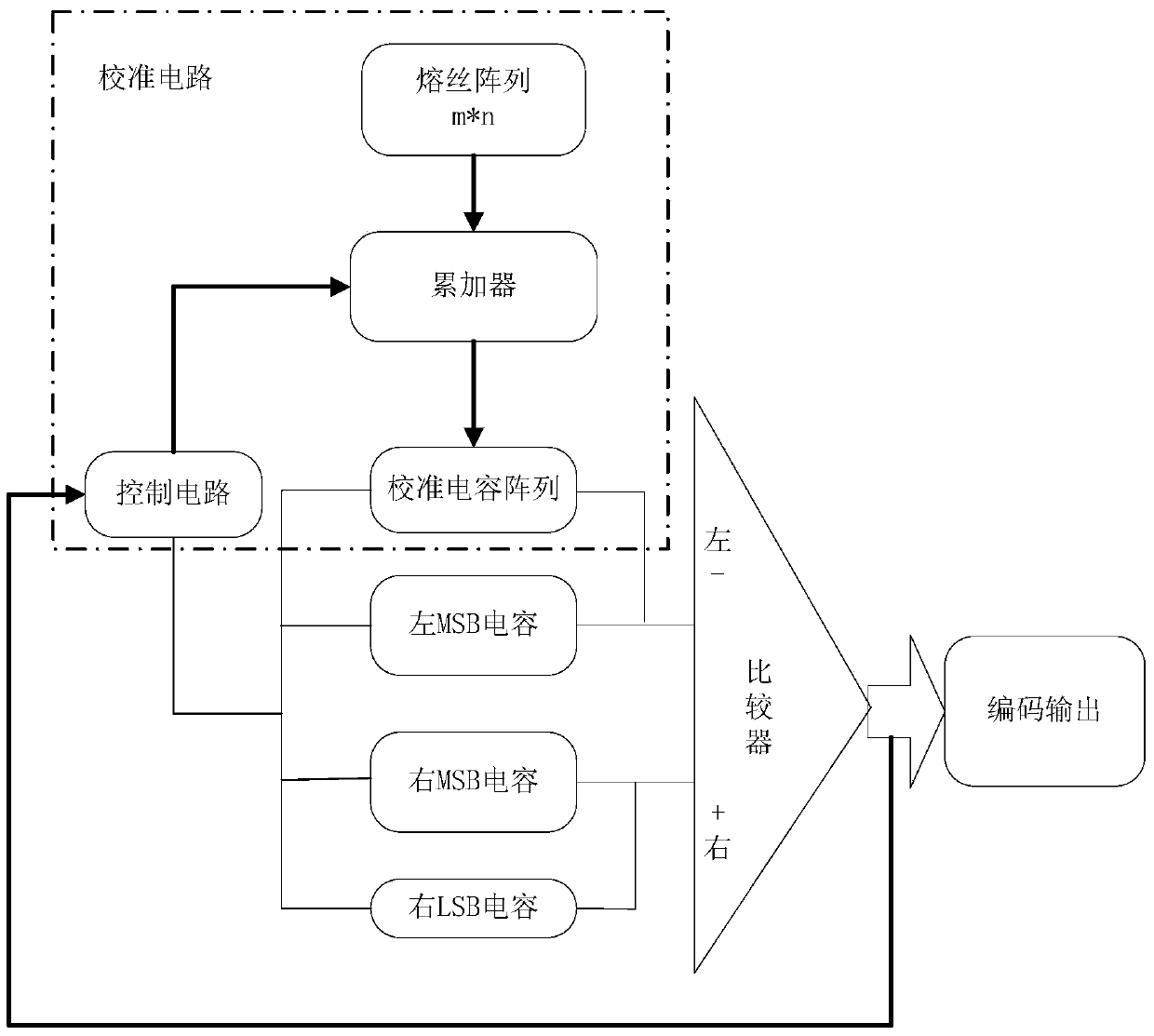

[0024] The calibration circuit of the present invention that adopts the fuse trimming technology to eliminate the capacitance mismatch error includes a fuse array, an accumulator, a control circuit and a calibration capacitor array.

[0025] The fuse array is composed of m times n fuses, m is the number of rows of the fuse array, n is the number of columns of the fuse array, where x acts as a data fuse, m, n, and x are all natural numbers, and x is less than m , The values of m and n and the proportion of data fuses in the fuse array should be determined according to the needs of specific circuits. The mismatch error data that needs to be adjusted is stored in the data fuse; the accumulated result of each row of data fuse represents the error information that needs to be compensated, and the data of each row of data fuse is read out in its corresponding clock cycle and sent to The input of the accumulator is compensated.

[0026] When debugging the circuit, you can adjust t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More