Instruction set encoding method based on embedded special instruction set processor

A technology of special instructions and encoding methods, which is applied in the computer field, can solve problems such as reducing the execution speed of instructions, long machine code words in the instruction set, and no protective instructions, etc., to overcome the complexity of addressing methods, improve execution efficiency, and improve The effect of execution speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in further detail below in conjunction with the accompanying drawings.

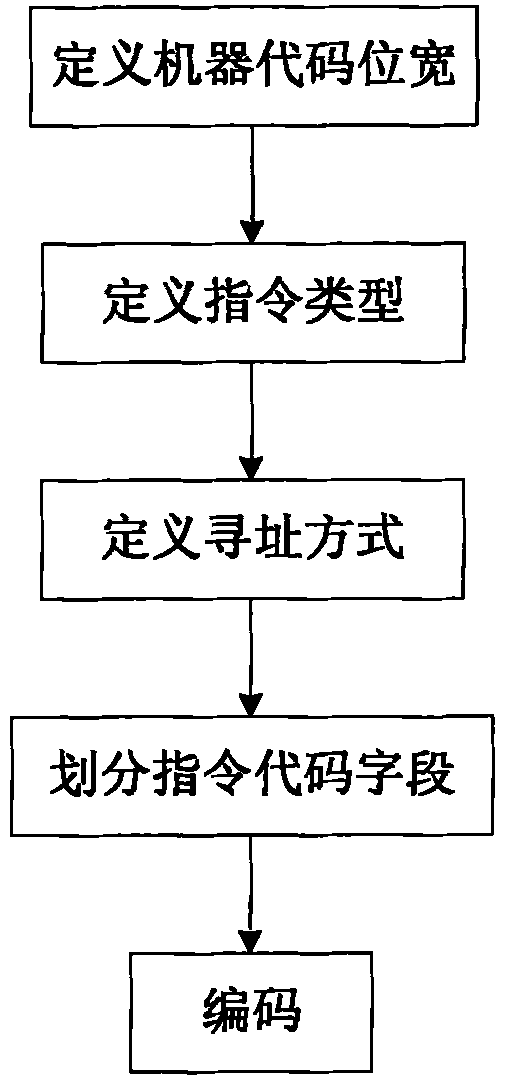

[0024] refer to figure 1 , the concrete steps of the present invention are as follows:

[0025] Step 1: Define the machine code bit width. According to the structural characteristics that the FPGA internal memory and the data bus are all based on 18-bit as the basic bit width, the data memory unit and the program memory unit bus of the embedded special instruction set processor are set to 18-bit and 16-bit, and the The bit width of the machine code of each instruction is limited to 18 or 16-bit. In the two application modes of complete application and simplified application, the bit width of the machine code is defined as 18 and 16-bit respectively. This can make full use of FPGA’s features such as large circuit scale, rich on-chip resources and reconfigurability, especially in FPGA, it is relatively easy to integrate multiple ASIP processing units (PE) in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More