Novel fourteen-bit assembly line-successive approximation type analog-to-digital converter

An analog-to-digital converter, successive approximation technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve problems such as conversion rate limitation, improve conversion rate, reduce design difficulty and power consumption, and realize power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

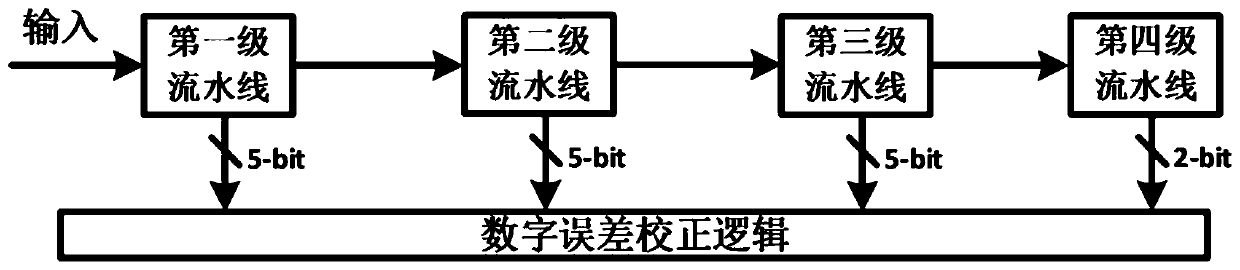

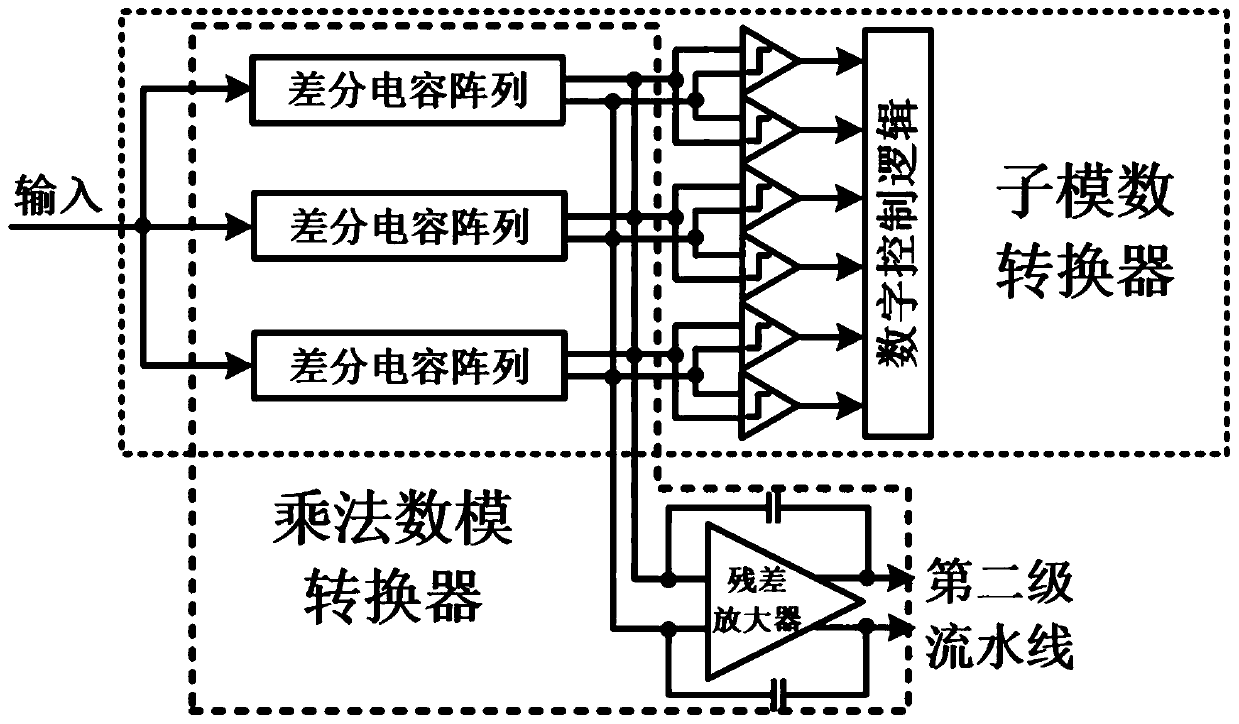

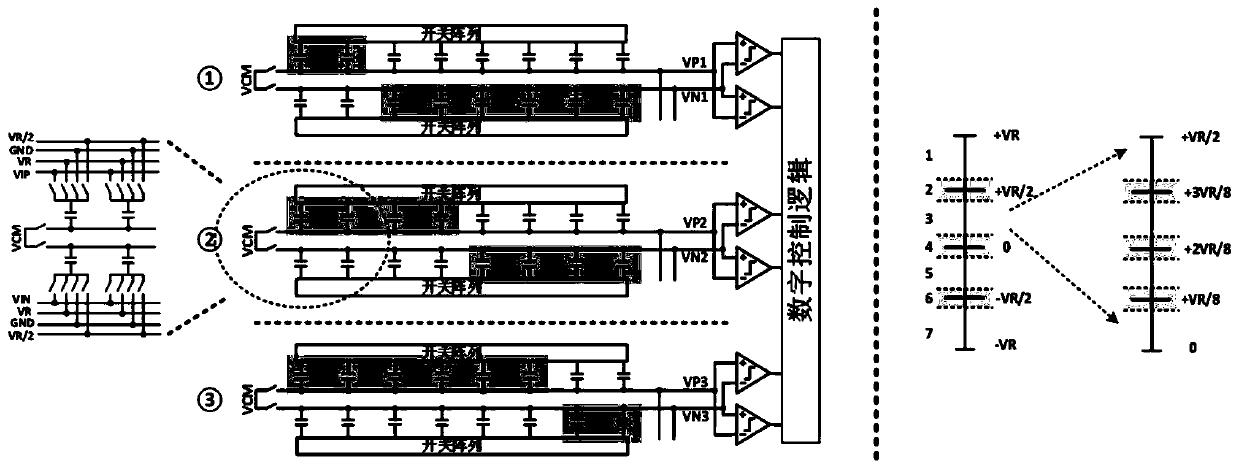

[0025]This embodiment implements a novel 14-bit pipeline-successive approximation analog-to-digital converter. The 14-bit pipeline-successive approximation analog-to-digital converter (14-bit Pipeline-SAR ADC) architecture proposed in this embodiment is suitable for high-speed and high-precision applications. The overall structure mainly includes four-stage pipeline and digital error correction logic (DigitalError Correction). In order to increase the conversion rate of the successive approximation analog-to-digital converter (SAR ADC) in the pipeline, a new 2.5-bit / cycle capacitor array is used to realize the conversion.

[0026] figure 1 It is a general structure diagram of a new 14-bit pipeline-successive approximation analog-to-digital converter. Such as figure 1 Shown in this embodiment is an overall architecture of a novel 14-bit pipeline-successive approximation analog-to-digital converter (14-bit Pipeline-SAR ADC), which mainly includes a four-stage pipeline and dig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More