Dual-channel time interleaved asynchronous assembly line flash analog-to-digital converter

An analog-to-digital converter and time-interleaved technology, applied in the direction of analog-to-digital conversion, code conversion, instruments, etc., can solve the problem of increased power consumption of operational amplifiers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to better understand the technical content of the present invention, specific embodiments are given together with the attached drawings for description as follows.

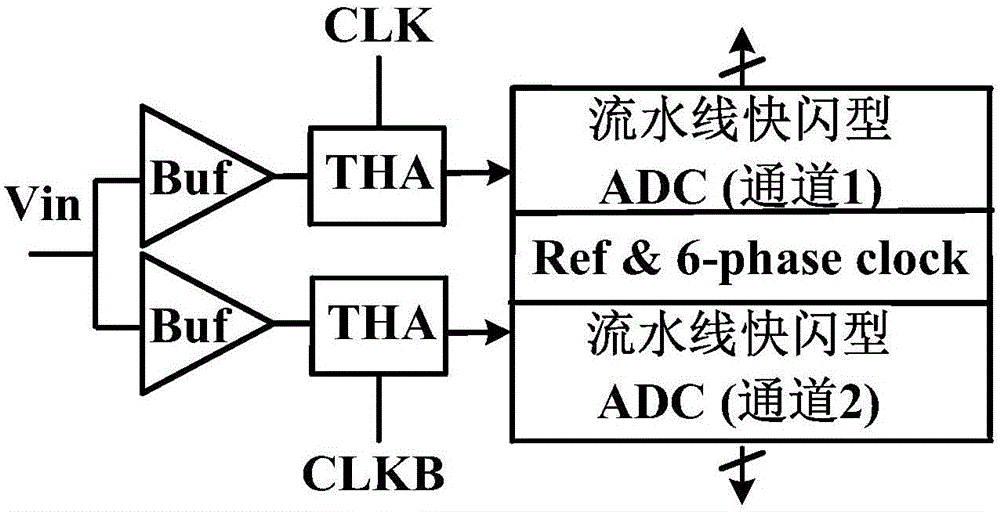

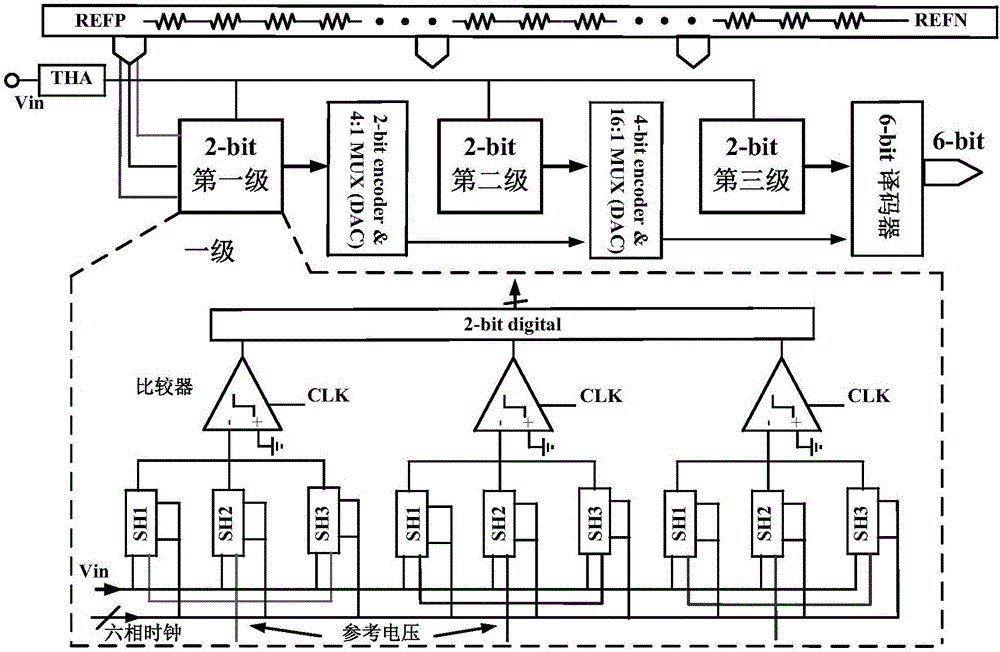

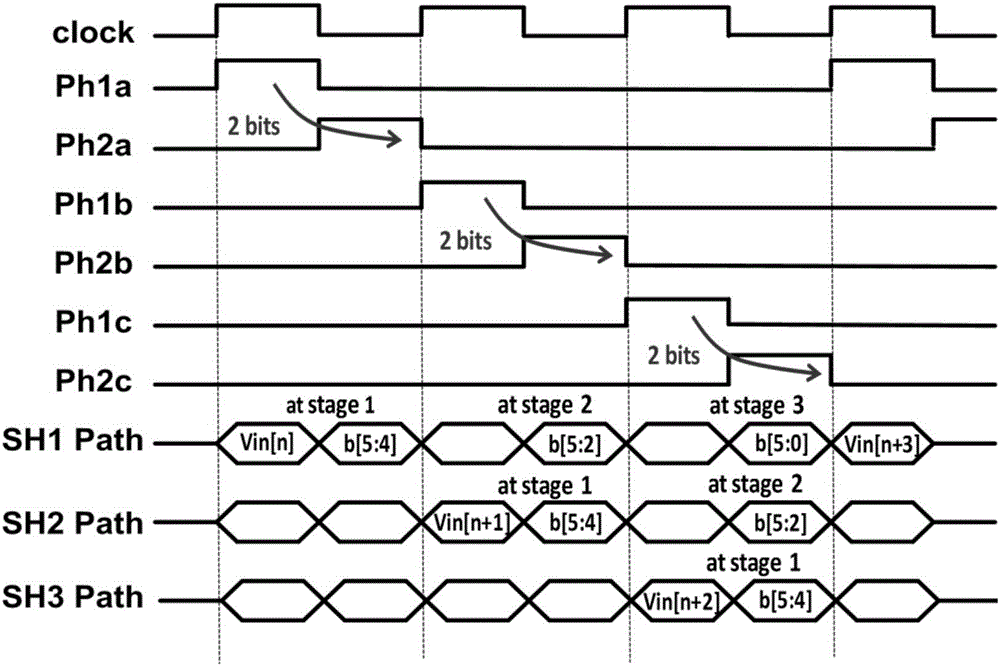

[0017] figure 1 It is a two-channel time-interleaved asynchronous pipeline flash ADC structure. By multiplexing parallel ADC technology, time interleaving can well increase the effective conversion rate. The structure of the dual-channel time-interleaved asynchronous pipeline flash ADC is as follows: figure 1 As shown, the structure includes the first buffer, the second buffer, the first track and hold circuit, the second track and hold circuit, the first single-channel 6-bit asynchronous pipeline flash ADC, and the second single-channel 6-bit asynchronous pipeline flash ADC Flash ADC, the input of the first tracking and holding circuit and the second tracking and holding circuit are respectively connected to the first buffer and the second buffer, the 6-bit asynchronous pipeline flash ADC of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More