2-phase gain calibration and scaling scheme for switched capacitor sigma-delta modulator using a chopper voltage reference

A voltage reference and modulator technology, applied in the direction of analog conversion, code conversion, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

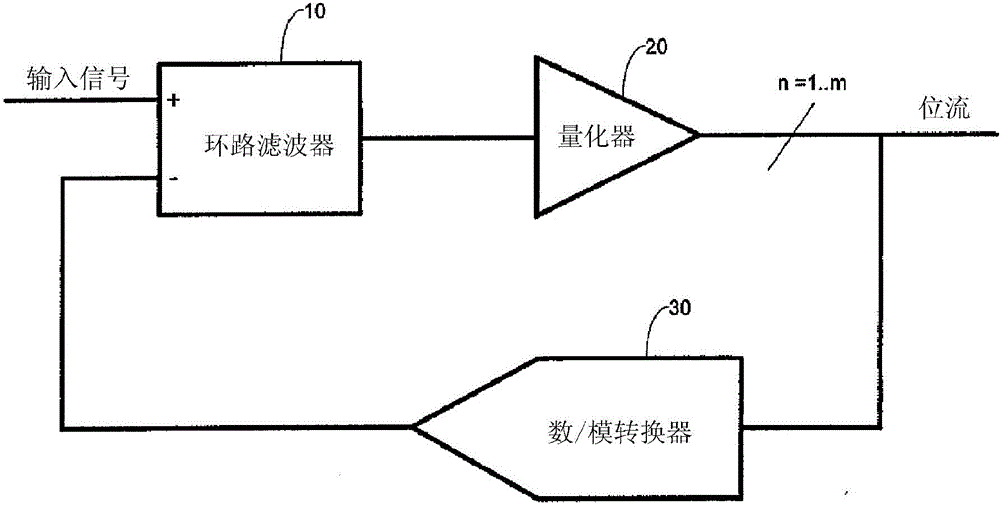

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

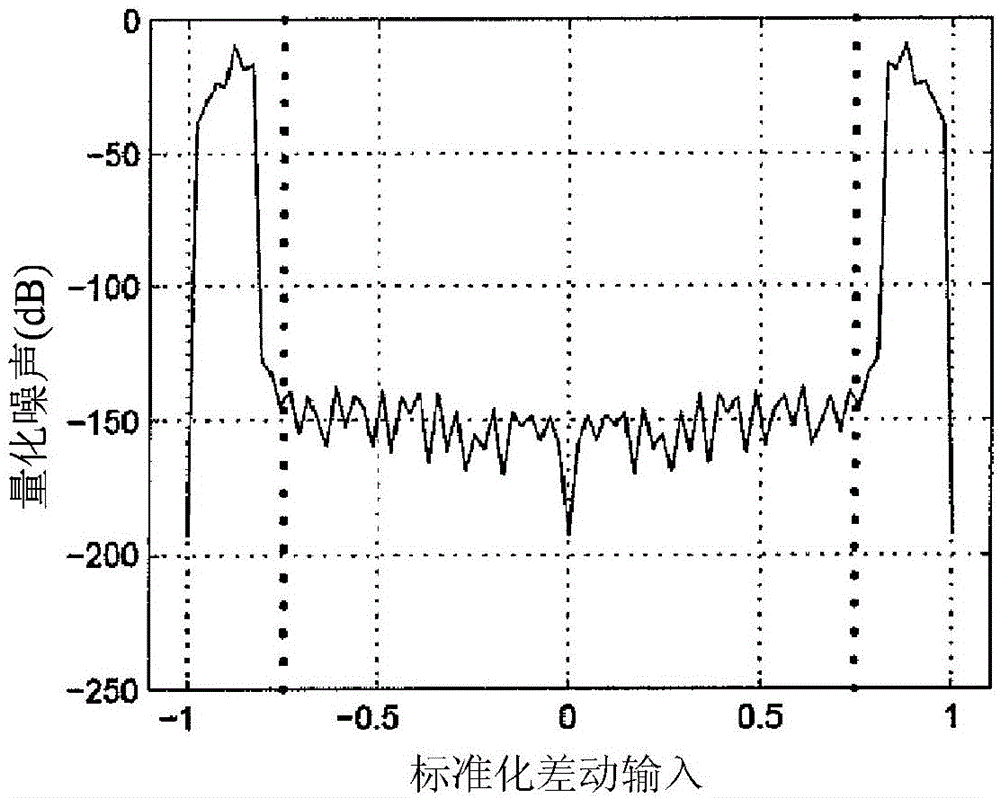

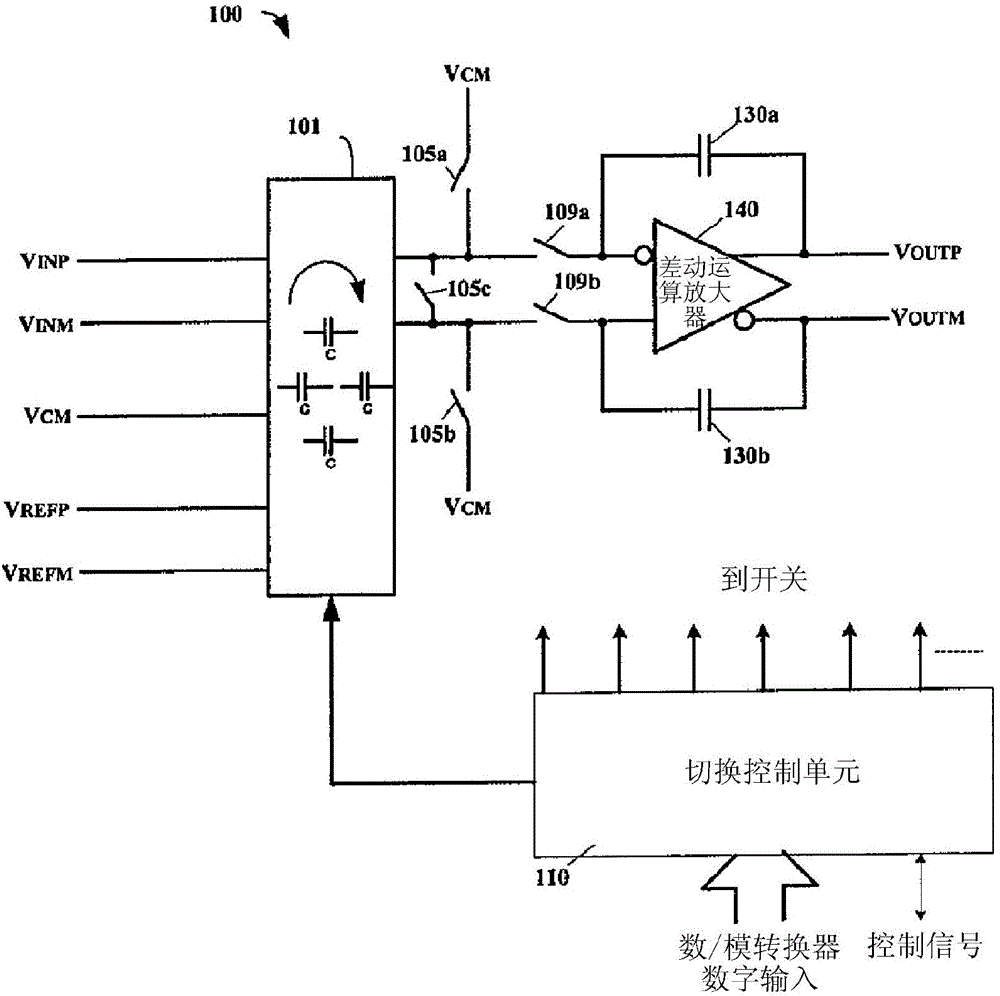

[0027] According to various embodiments, the mismatch can be averaged by simultaneously sampling the DAC signal and the input signal in parallel on different sets of capacitors in the front-end stage of the modulator, and by using a defined algorithm to rotate the capacitors at each sample error, while achieving that while each sample can use only two stages instead of four with less power consumption (due to less stringent requirements on the bandwidth of the amplifier present in the modulator) Sigma-Delta modulator that maintains very low gain error in the ppm range.

[0028] Simultaneously sampling the DAC signal and the input signal in parallel enables a reduction from four stages to two, and the rounding algorithm ensures proper gain error cancellation after a certain number of samples via integration in the modulator loop.

[0029] In accordance with the teachings of the present invention, rotating capacitors at each sample means assigning different sets of capacitors to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More