2-phase gain calibration and scaling scheme for switched capacitor sigma-delta modulator using a chopper voltage reference

a sigma-delta modulator and switched capacitor technology, applied in the field of analog-to-digital converters, can solve problems such as large errors, modulators giving erroneous results, and modulators becoming unstabl

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

sible states for each stage (in this representation the number of input stages is limited to 5);

[0021]FIG. 7 shows an example of a rotation algorithm to perform the 2-phase gain scaling and gain error cancellation which is not depending on the DAC input states;

[0022]FIGS. 8a and b show another example of a rotation algorithm to perform the 2-phase gain scaling and gain error cancellation, but which is depending on the DAC input states;

[0023]FIG. 9 shows the state diagram for the rotation algorithm that is depending on the DAC states (DAC input dependent algorithm) and that performs gain scaling and gain error cancellation;

[0024]FIG. 10 shows a block diagram of a chopper voltage reference; and

[0025]FIG. 11 shows an example of yet another rotation algorithm when a chopped voltage reference is used.

DETAILED DESCRIPTION

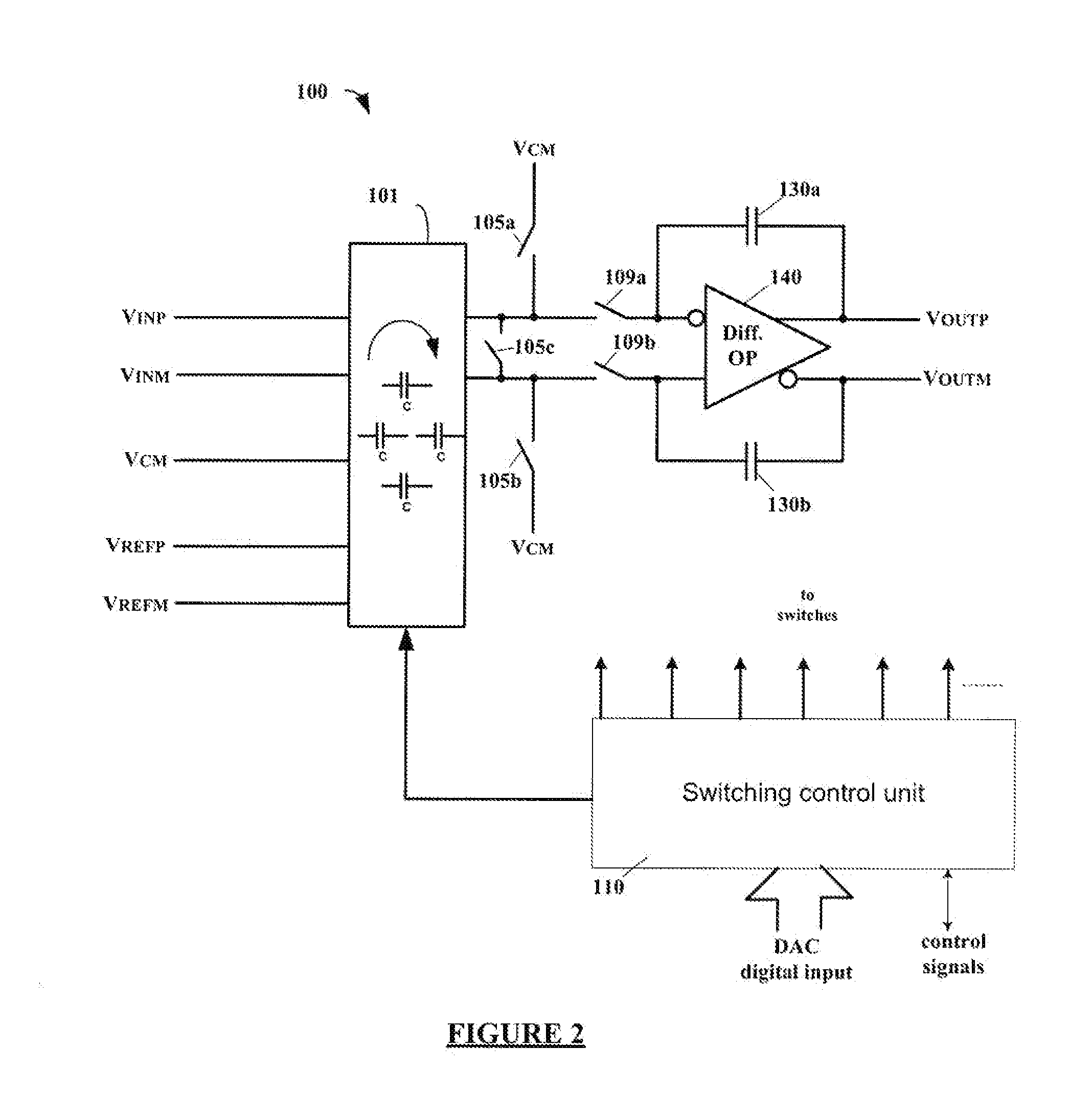

[0026]According to various embodiments, a sigma-delta modulator that can use only two phases instead of four per each sample with less power consumption (due to less stri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More