Power MOS device

A MOS device and power technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of growth, large specific on-resistance, and increase in chip area, etc., to reduce specific on-resistance, reduce device size, Easy to Integrate Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

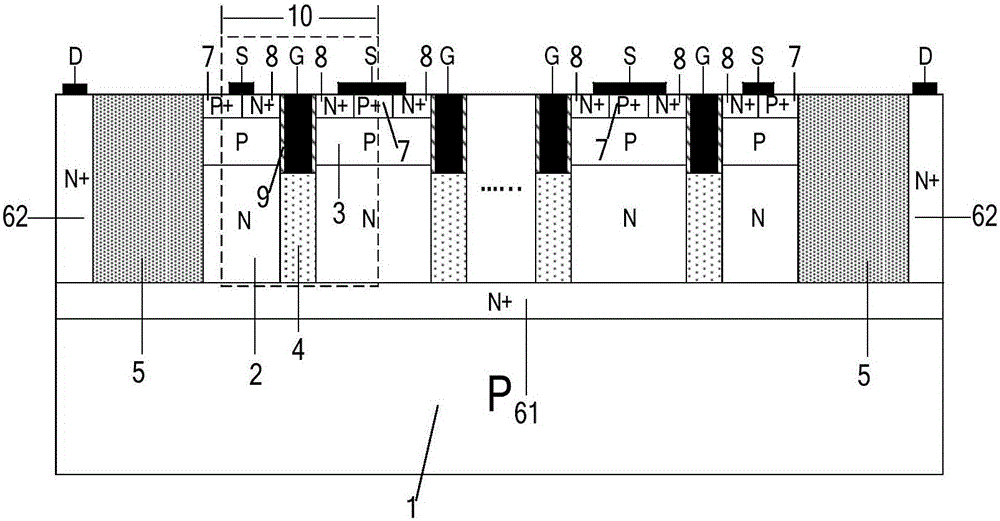

[0033] Such as figure 1 As shown, it includes a second conductivity type semiconductor substrate 1 and a first conductivity type heavily doped semiconductor drain region 61 located on the upper surface of the second conductivity type semiconductor substrate 1; the first conductivity type heavily doped semiconductor drain region 61 There are first conductivity type heavily doped semiconductor drain extension regions 62 at both ends of the upper surface; there are multiple parallel cell structures between the first conductivity type heavily doped semiconductor drain extension regions 62; the first conductivity type heavy There is a dielectric groove 5 between the doped semiconductor drain extension region 62 and the cellular structure, and the dielectric groove 5 is filled with a first dielectric layer; the cellular structure includes a gate structure, a first conductivity type semiconductor drift region 2 and The second conductivity type semiconductor body region 3; the first c...

Embodiment 2

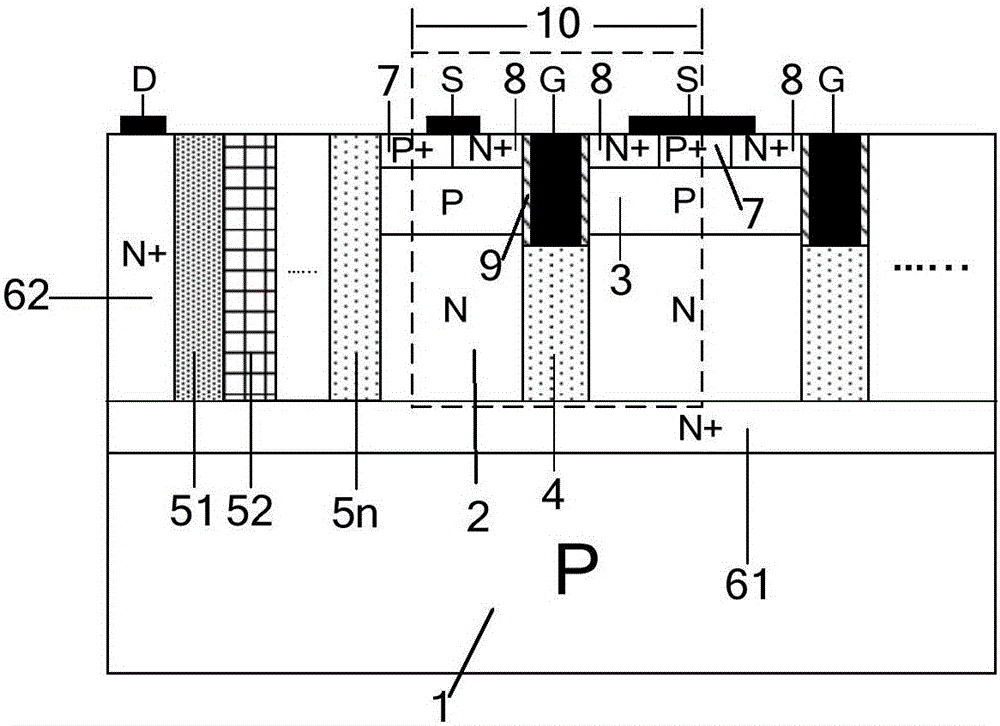

[0036] Such as figure 2As shown, the structural schematic diagram of the integrated power MOS device adopting the variable K-slot medium in this example is different from that in Embodiment 1 in that the first dielectric layer is composed of multiple media, and the dielectric constant of the media is determined by the first The heavily doped semiconductor drain extension region 62 of a conductivity type gradually increases toward the cell structure 10 side. In this embodiment, the dielectric with a high dielectric constant can enhance the auxiliary depletion of the drift region 2, optimize the distribution of equipotential lines on one side of the dielectric tank, and improve the withstand voltage of the device.

Embodiment 3

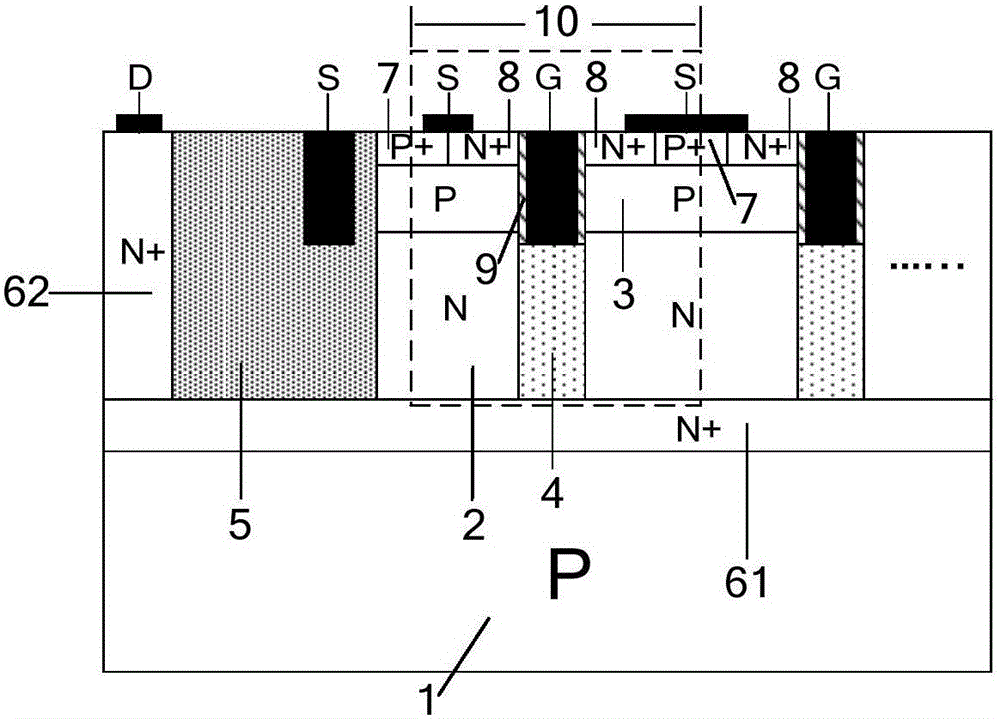

[0038] Such as image 3 As shown, the structure schematic diagram of the integrated power MOS device with the source field plate of this example is different from that of Embodiment 1 in that the dielectric trench 5 has a metallized source, and the two sides of the metallized source and The bottom is in contact with the first dielectric layer. The metallized source acts as a source field plate, which can assist in depleting the drift region 2, optimize the distribution of equipotential lines, and improve the withstand voltage of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More