Super junction device and manufacturing method thereof

A super-junction device and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing device cost, increasing device specific on-resistance, etc., achieve device performance assurance, and improve softness factor effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example approach

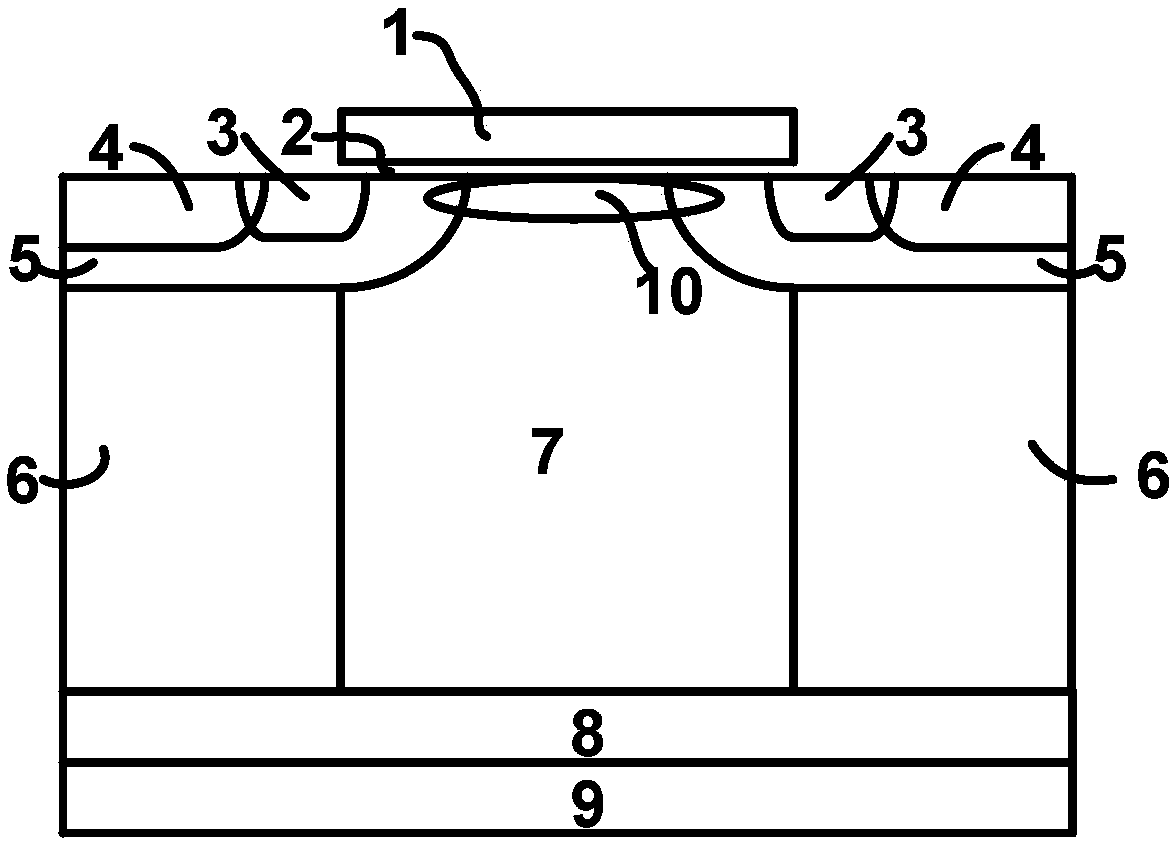

[0096] The method for manufacturing a super junction device according to the first embodiment of the present invention is used to manufacture such as image 3 The device of the first embodiment of the present invention shown, the method of the first embodiment of the present invention includes the following steps:

[0097] Step 1, such as Figure 5A As shown, an N-type epitaxial layer is provided, and the N-type epitaxial layer is formed on an N-type heavily doped semiconductor substrate 9 . The thickness of the N-type epitaxial layer includes the thicknesses of the subsequent buffer layer 8 and N-type pillars 7 . The semiconductor substrate 9 is usually a wafer structure, so it is also called a wafer.

[0098] Step two, such as Figure 5A As shown, a hard mask layer 12 is formed on the surface of the N-type epitaxial layer, and the hard mask layer 12 in the trench formation area is removed by photolithography, and all the hard mask layers outside the trench formation area ...

no. 2 example approach

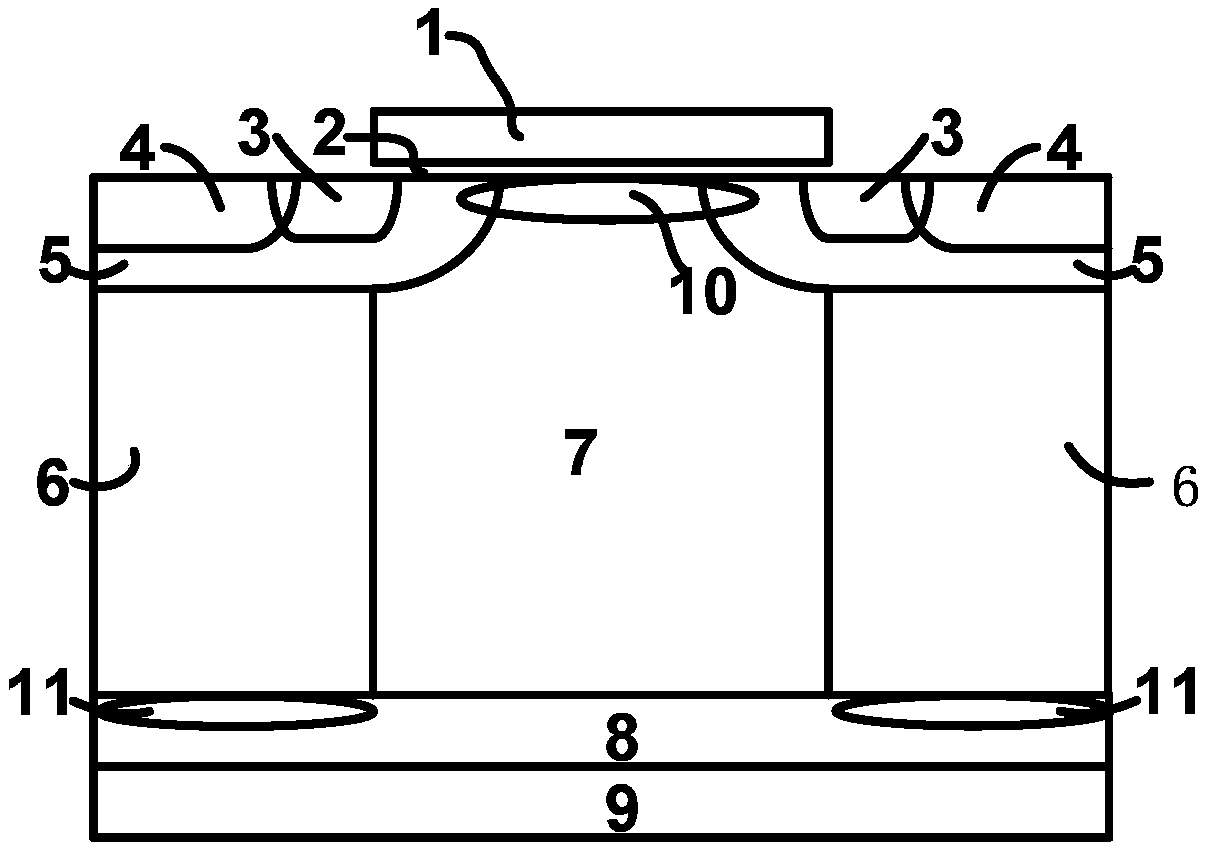

[0118] The manufacturing method of the super junction device according to the second embodiment of the present invention is used to manufacture such as Figure 4 The device of the second embodiment of the present invention shown, the method of the second embodiment of the present invention includes the following steps:

[0119] Step 1, such as Figure 6A As shown, a first epitaxial sublayer 8 with N-type doping is provided, and the first epitaxial sublayer 8 is formed on an N-type heavily doped semiconductor substrate 9 . The first epitaxial sublayer 8 is used to form a buffer layer 8 , which are all marked with 8 .

[0120] Step two, such as Figure 4 As shown, multiple epitaxy is carried out and a photolithography definition and P-type ion implantation are performed after each epitaxy process to form corresponding P-type sub-columns 13a, 13b and 13c, and the P-type sub-columns formed after each epitaxy Vertical stacking forms P-shaped columns 6 .

[0121] The epitaxial l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More