A lateral MOS type power semiconductor device and a preparation method thereof

A technology of power semiconductors and semiconductors, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as increased cost, increased chip area, and increased power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

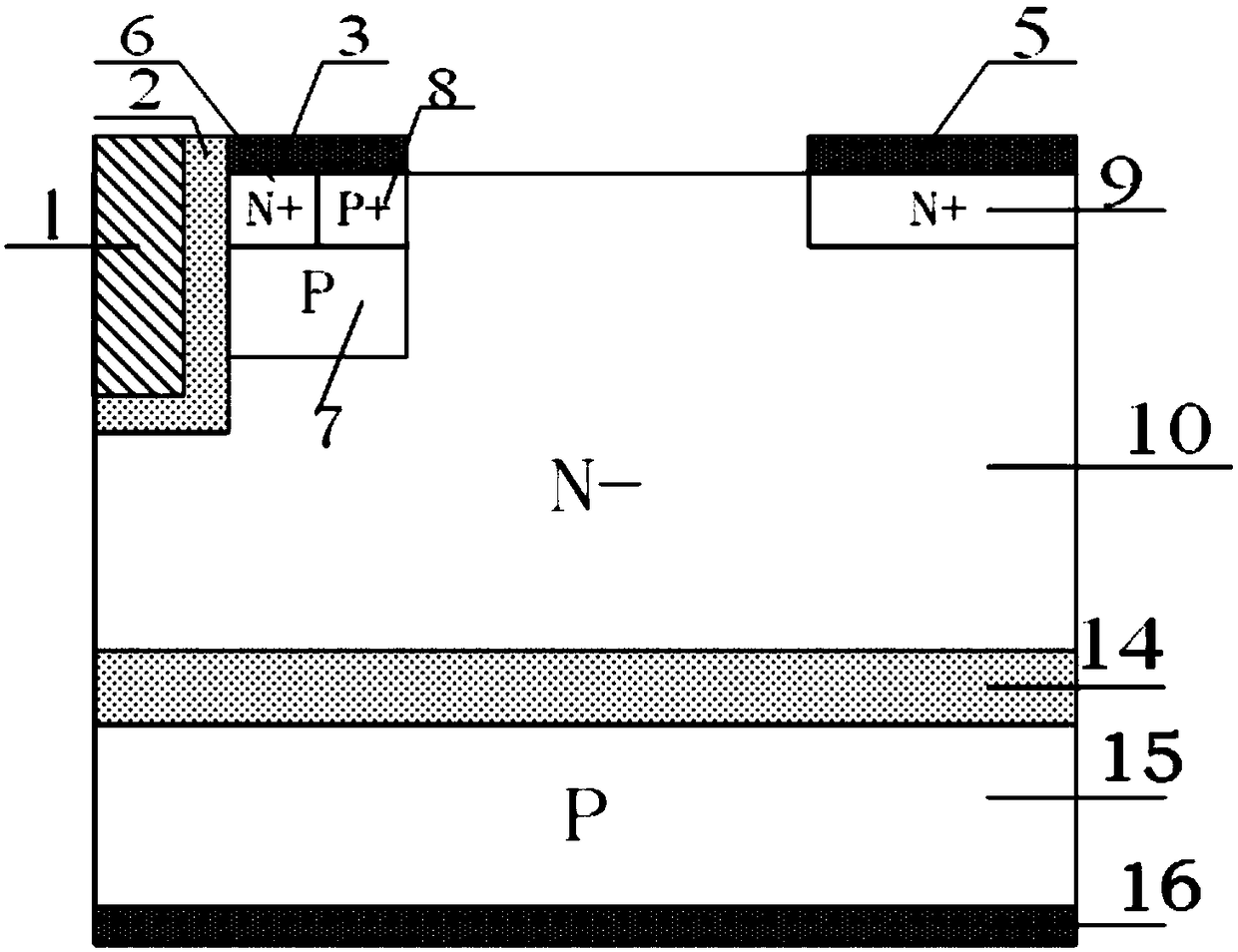

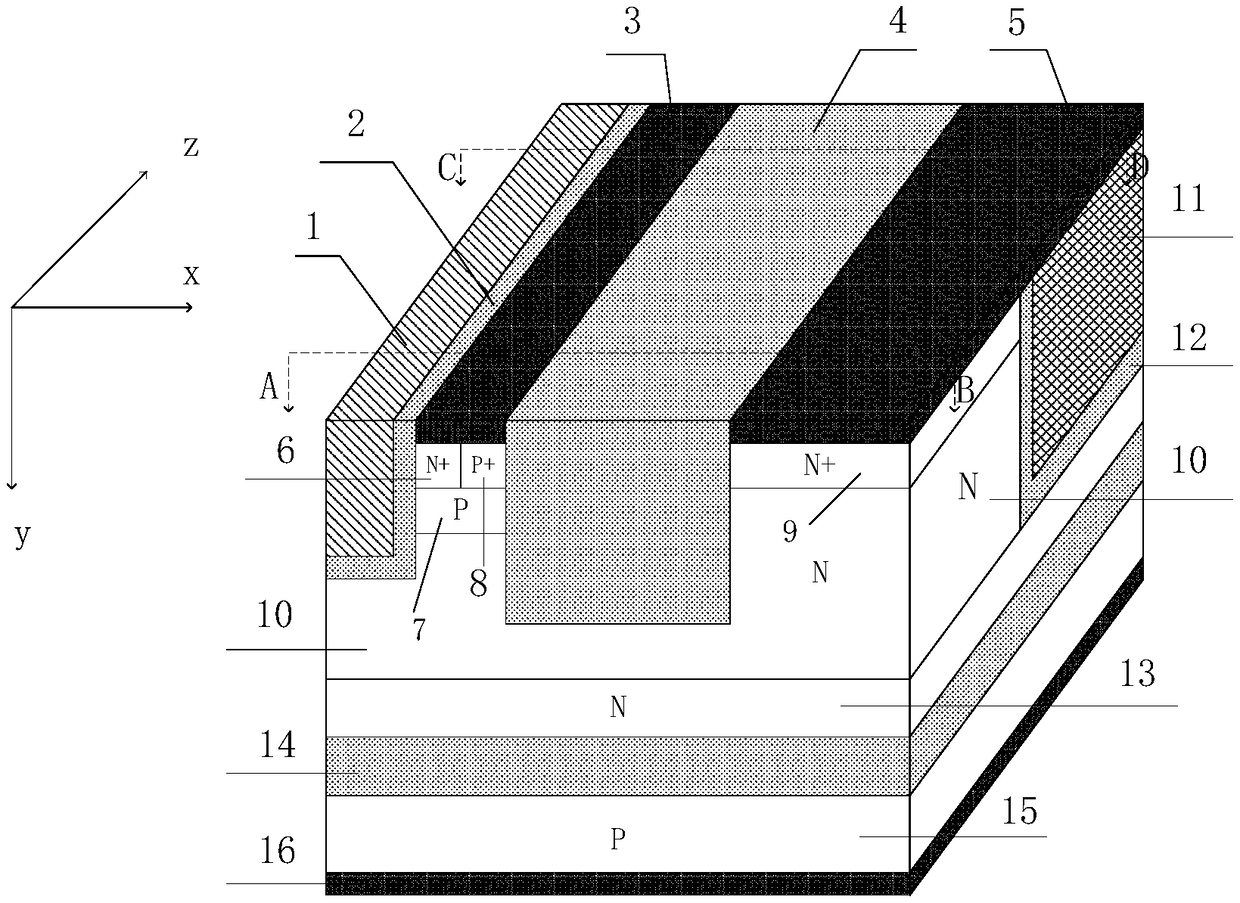

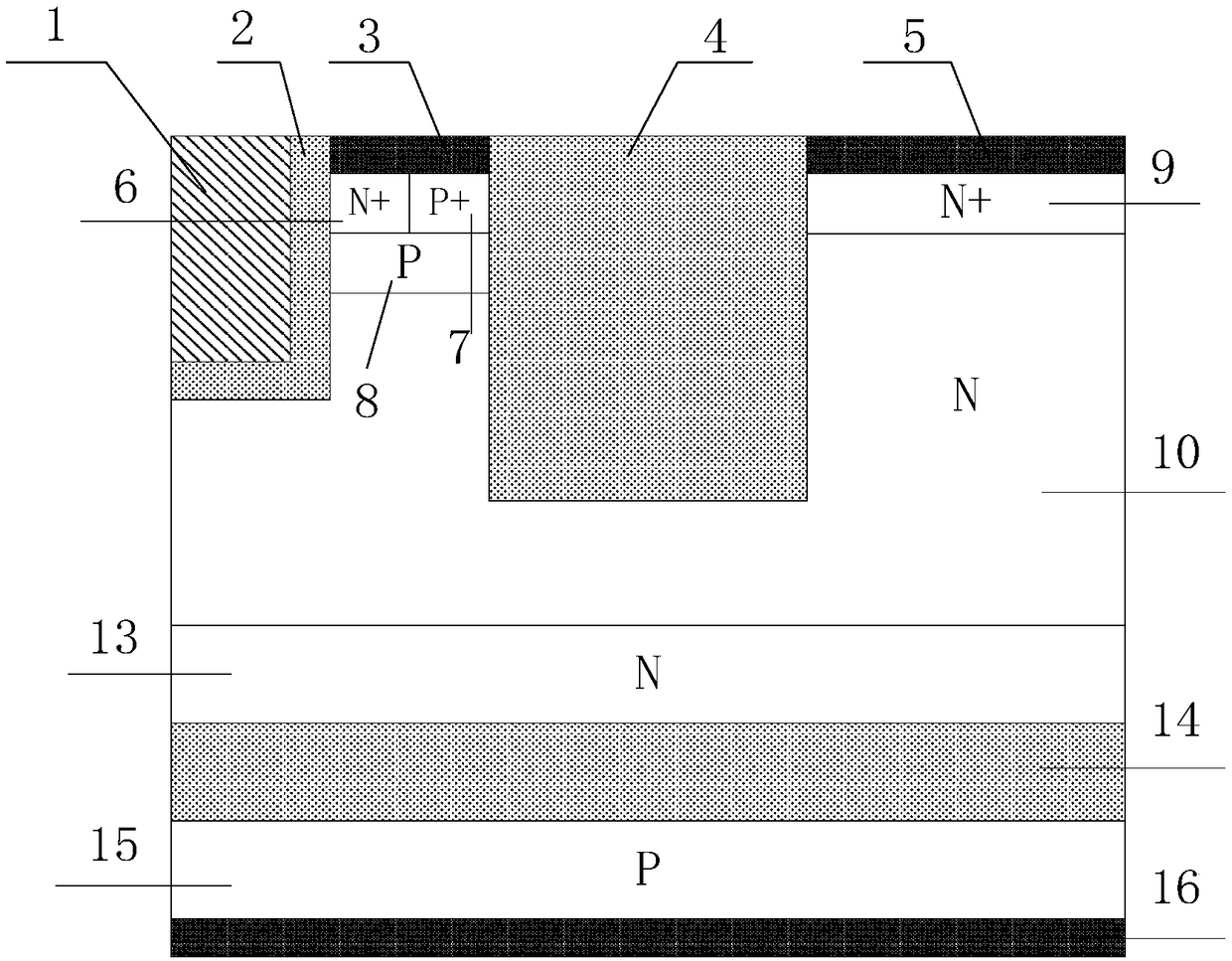

[0086] This embodiment provides an LDMOS device, the cell structure of which is as follows figure 2 as shown, figure 2 The schematic diagrams of the cross-sectional structure of the cellular structure along the AB line and the CD line are shown in Fig. image 3 and 4 shown, combined with Figures 2 to 4 From the point of view, the cellular structure includes: a substrate electrode 16 stacked vertically from bottom to top, a P-type semiconductor layer 15, a buried oxide layer 14, an N-type buffer layer 13, and an N-type drift region 10; the N-type drift region 10 One side of the surface is provided with an N-type drain region 9; the other side of the surface of the N-type drift region 10 is provided with a MOS structure, and the MOS structure includes a P-type body region 7, an N+ source region 6, a P+ contact region 8, a trench gate Structure and source electrode 3, wherein the trench gate structure includes a trench gate electrode 1 and a trench gate dielectric layer 2 a...

Embodiment 2

[0090] This embodiment provides an LDMOS device, the cell structure of which is as follows Figure 5 as shown, Figure 5 The schematic diagrams of the cross-sectional structure of the cell structure along the AB line, CD line and EF line are shown in Fig. Figure 6 , 7 and 8, combined with Figures 5 to 8 From the point of view, this embodiment is based on Embodiment 1, and a P-type column region 17 is provided on the side of the N-drift region 10 relatively away from the semi-insulating polysilicon column 11, and the lower surface of the P-type column region 17 is connected to the N-type column region. - the buffer layer 13 is in contact; the P-type pillar regions 17 are parallel to the N-drift regions 10 along the lateral extension direction of the deep dielectric trench 4 and are arranged alternately to form a super junction structure. In this embodiment, the width of the P-type column region 17 along the z-axis direction is 0.5-1.5 μm, the longitudinal depth along the y...

Embodiment 3

[0092] This embodiment provides an LDMOS device, the cell structure of which is as follows Figure 9 as shown, Figure 9 The schematic diagrams of the cross-sectional structure of the cell structure along the AB line, CD line and EF line are shown in Fig. Figure 10 , 11 As shown in and 12, this embodiment is based on embodiment 2, in the N-type drift region 10 and the P-type column region 17 below the N-type drain region 9, the side N close to the side wall of the deep dielectric trench 4 is set. The doping concentration of the N-type buffer layer 18 on the side is not less than the doping concentration of the N-type drift region 10 . The doping concentration of the side N-type buffer layer 18 can be uniform doping, or decreasing from top to bottom. The introduction of the side N-type buffer layer 18 can suppress the influence of auxiliary depletion on the charge balance between the N-type drift region 10 and the P-type column region 17 due to the different potentials on b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More