Groove-gate semiconductor power device

A technology for power devices and semiconductors, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as the inability to play the role of high-K dielectrics, and achieve the effect of alleviating the problem of charge imbalance, improving withstand voltage, and large flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

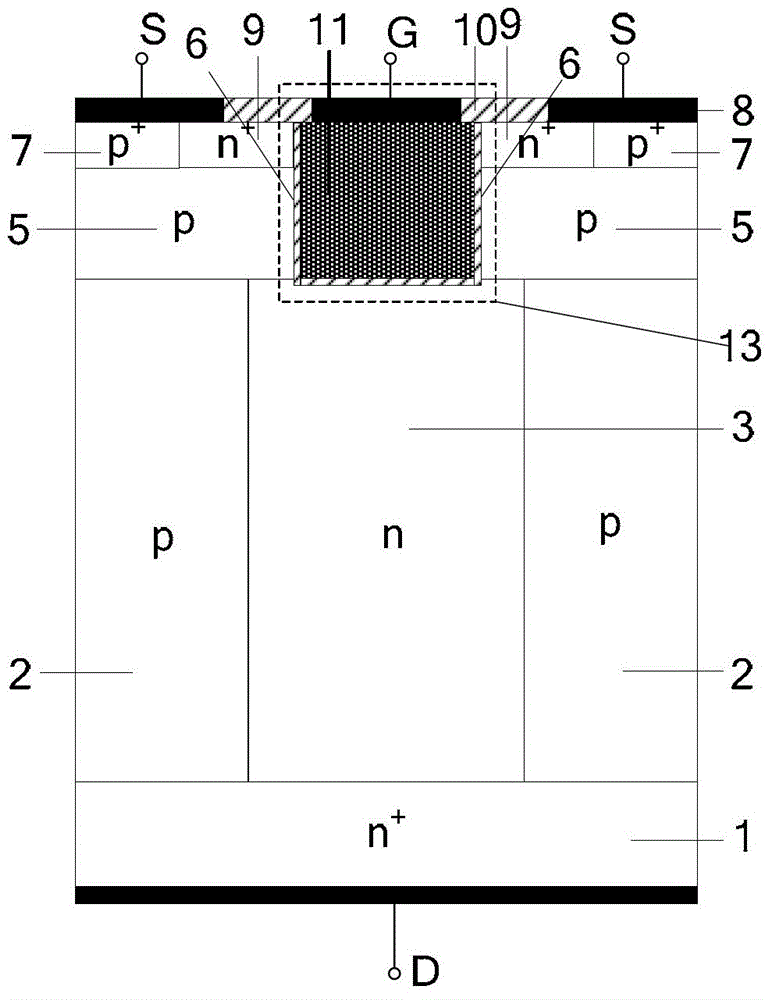

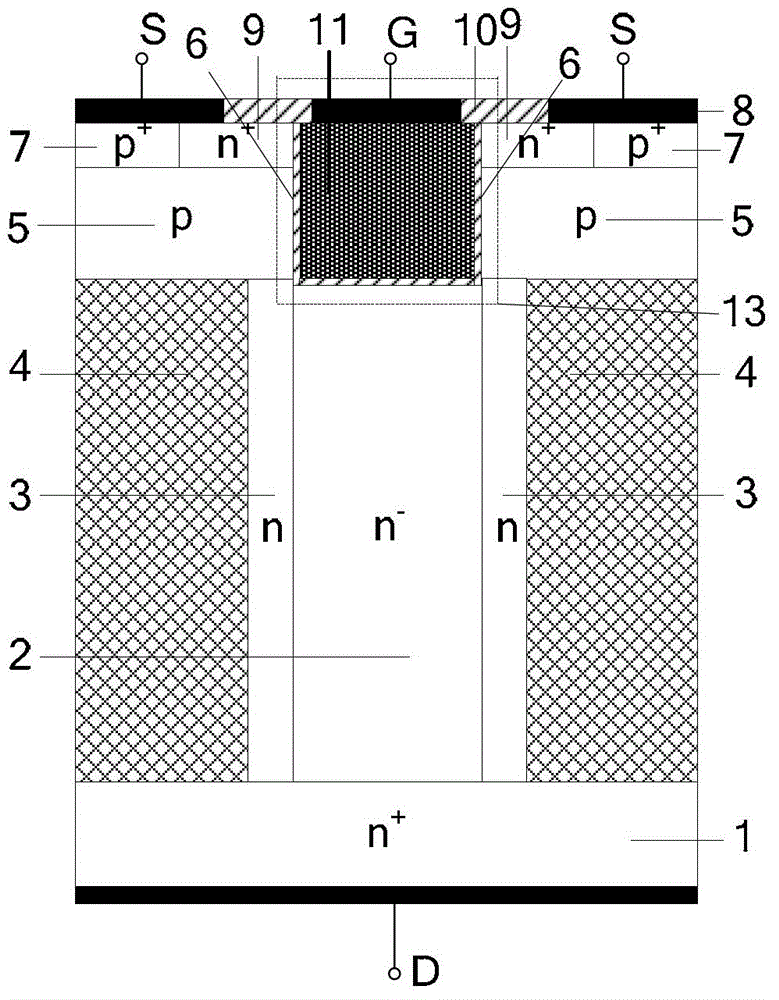

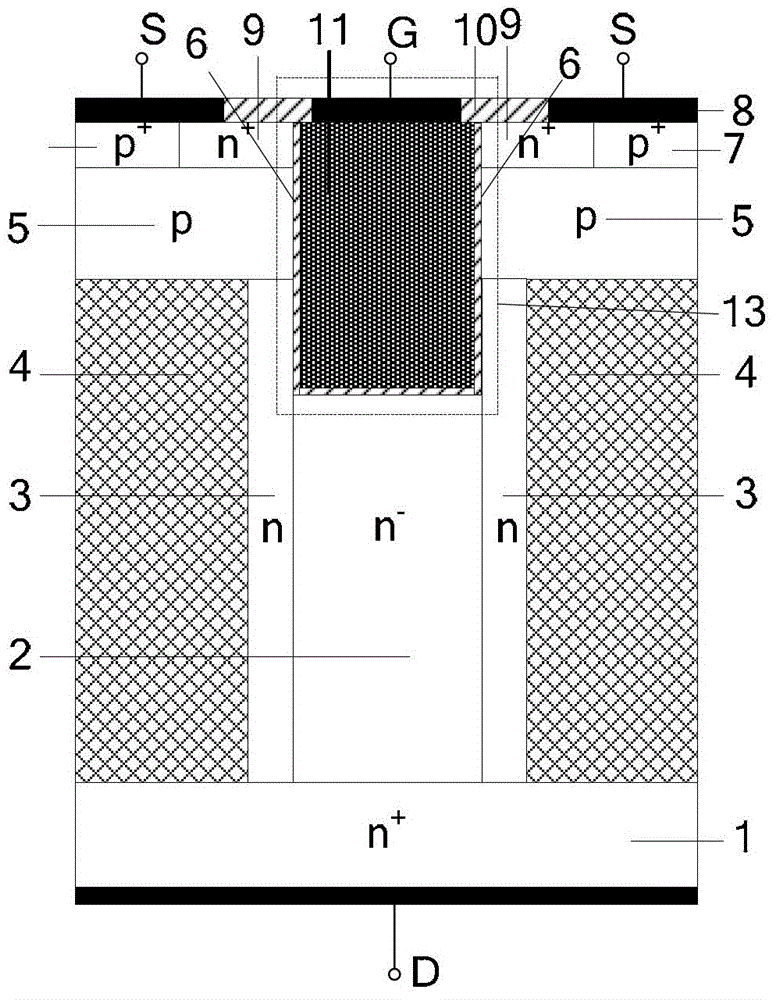

[0032] In this example, an N-channel trench-gate VDMOS device with a low-resistance current channel is taken as an example. The cross-sectional view is as follows figure 2 . In the case of N-channel VDMOS devices the semiconductor substrate is n + Type doping (that is, n-type dielectric with doping concentration greater than n-type doping concentration).

[0033] The slot-gate semiconductor power device in this example includes n + Type-doped semiconductor substrate 1, trench gate structure 13, active region, semiconductor drift region and two high-K dielectric regions 4, the semiconductor drift region includes a first semiconductor region 2 and two second semiconductor regions 3, the first The semiconductor region 2 is arranged above the semiconductor substrate 1, the two second semiconductor regions 3 are arranged above the semiconductor substrate 1, the high-K dielectric region 4 is arranged above the semiconductor substrate 1, and the two sides of the first semiconducto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More