High-voltage three-dimensional depletion super-junction LDMOS device and manufacturing method thereof

A manufacturing method and three-dimensional technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effect of increasing doping concentration and ensuring device withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

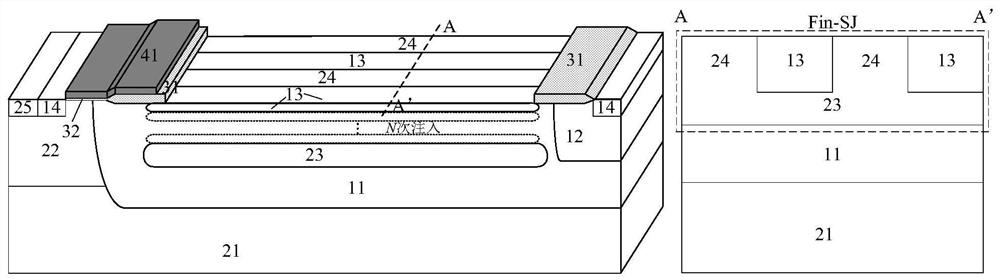

[0040] Such as figure 1 Shown is a schematic structural diagram and a cross-sectional view of a high-voltage three-dimensional depleted superjunction LDMOS device according to Embodiment 1 of the present invention, specifically including: a substrate 21 of a second conductivity type, a drift region 11 of a first conductivity type, and a well region 12 of a first conductivity type and the second conductivity type well region 22, the first dielectric oxide layer 31, the second dielectric oxide layer 32, the second conductivity type buried layer 23, the first conductivity type regions 13 and the second conductivity type regions 24 arranged periodically, and Doping the first conductivity type region 14 and heavily doping the second conductivity type region 25, control gate polysilicon 41;

[0041] Wherein, the well region 12 of the first conductivity type is located on the right side of the drift region 11 of the first conductivity type, the well region 22 of the second conductivi...

Embodiment 1

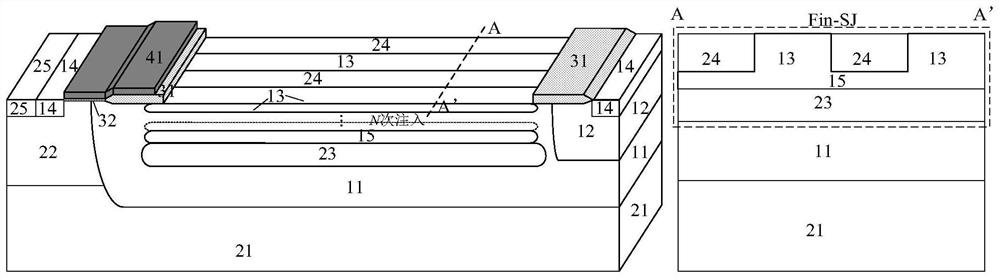

[0060] Such as figure 2 Shown is a schematic structural diagram and a cross-sectional view of the high-voltage three-dimensional depleted superjunction LDMOS device in Example 2 of the present invention, which is implanted into the buried layer of the first conductive type after the implantation of the buried layer 23 of the second conductive type in the manufacturing step 4 of the implementation example 1 15, and at the same time push the junction to form, the subsequent first conductivity type region 13 and the second conductivity type region 24 are implanted and connected to the first conductivity type buried layer 15, the dose and times of super junction implantation required in this embodiment are reduced, and the subsequent The process steps remain the same. The buried layer 15 of the first conductivity type and the region 13 of the first conductivity type surround the region 23 of the second conductivity type in three directions, forming a three-dimensional depleted su...

Embodiment 3

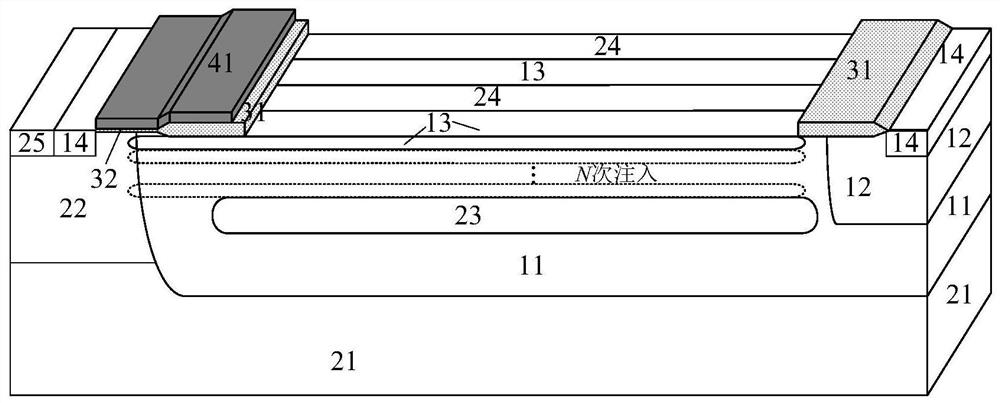

[0062] Figure 3(a) is a schematic structural diagram of a high-voltage three-dimensional depleted superjunction LDMOS device in Example 3 of the present invention. In this example, the superjunction source is implanted into the second conductivity type well region 22 on the basis of Example 1. In this process, the grounding of the second conductivity type region 24 is realized to improve the dynamic characteristics of the device. As shown in FIG. 3( b ), it is a schematic diagram of another modified structure of Embodiment 3 of the present invention. The superjunction second conductivity type region 24 is introduced into the source end heavily doped first conductivity type region 14 and heavily doped second conductivity type region 25 along the first conductivity type drift region 11 and the second conductivity type well region 22 , the super-junction first conductivity type region 13 remains unchanged to realize super-junction grounding, and the rest of the working principles ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More