Grooved gate MOS having buried layer structure

A technology of layer structure and groove gate, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve problems such as the increase of current flow path, the increase of device on-resistance, and the increase of channel resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

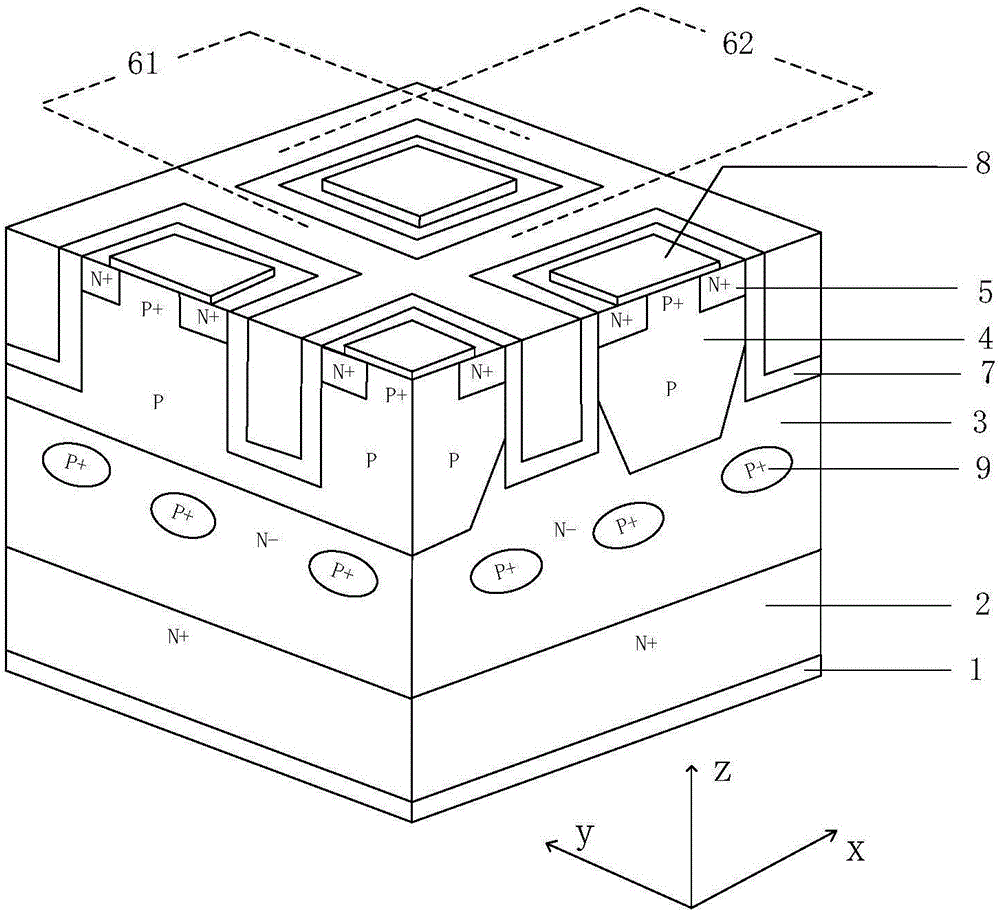

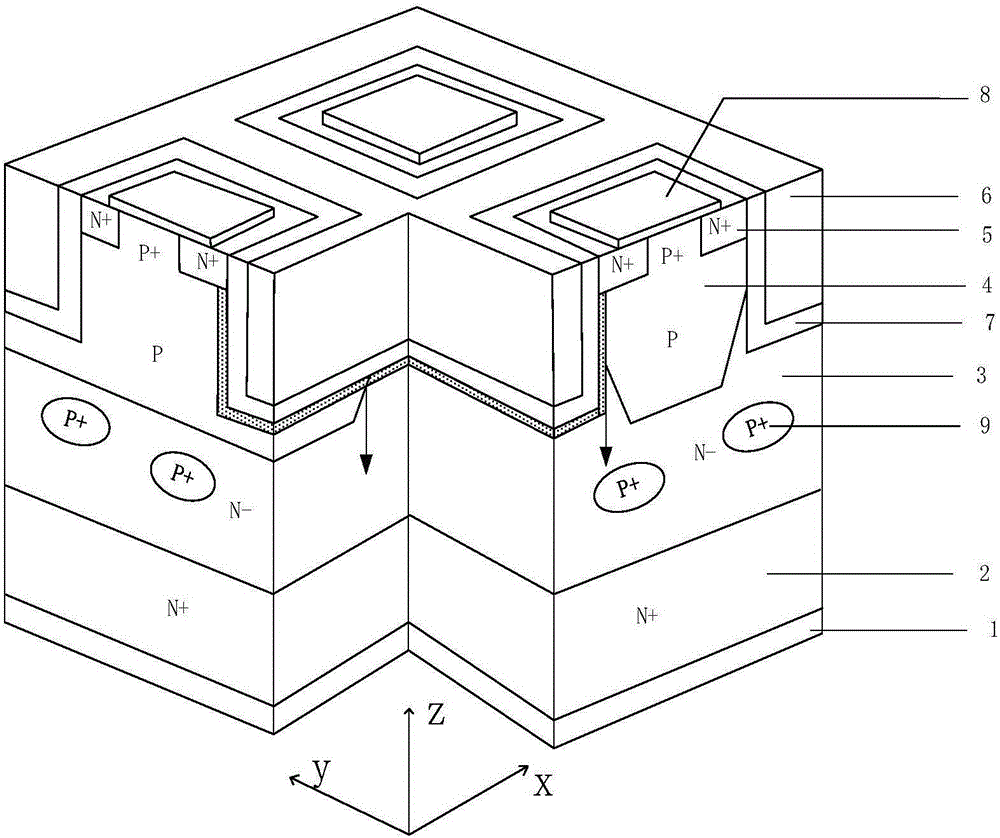

[0019] The present invention is described in detail below in conjunction with accompanying drawing

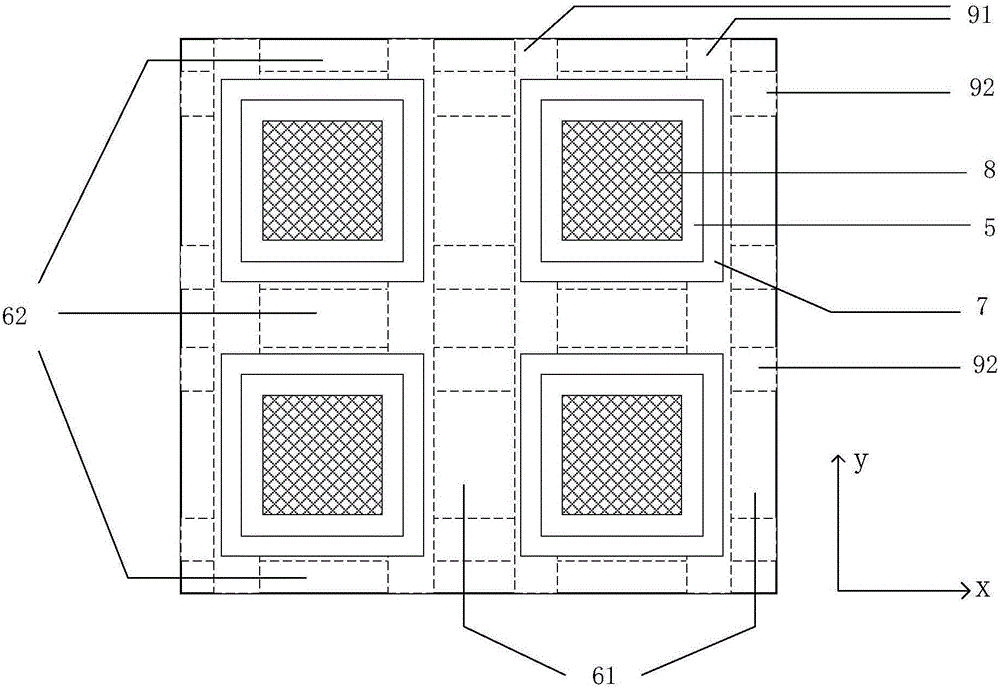

[0020] It should be noted that, like the coordinate axes in the drawings, the description corresponding to the coordinate axes in the present invention is that the lateral direction of the device corresponds to the x-axis direction, the longitudinal direction of the device corresponds to the y-direction, and the vertical direction of the device corresponds to the z-direction.

[0021] like figure 1 As shown, a trench gate MOS with a buried layer structure of the present invention includes a drain electrode 1, an N-type heavily doped single crystal silicon substrate 2 and an N- epitaxial layer 3 that are stacked sequentially from bottom to top; The upper layer of the N- epitaxial layer 3 has a first grooved gate structure 61, a second grooved gate structure 62 and a P-type body region 4; along the lateral direction of the device, both sides of the P-type body region 4 are the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More