Trench gate power MOSFET (metal oxide semiconductor filed-effect transistor) device

A device and power technology, applied in the field of trench-gate power MOSFET devices, can solve the problems of difficult process and achieve the effects of increasing doping concentration, reducing power consumption, and increasing channel density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

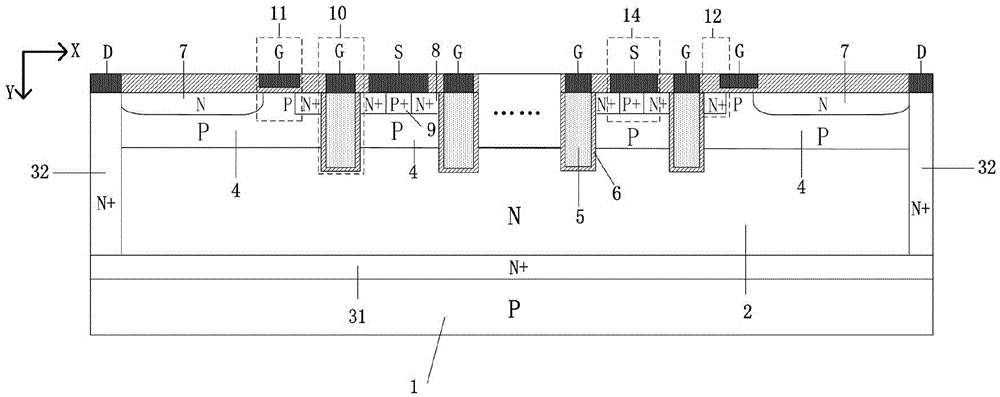

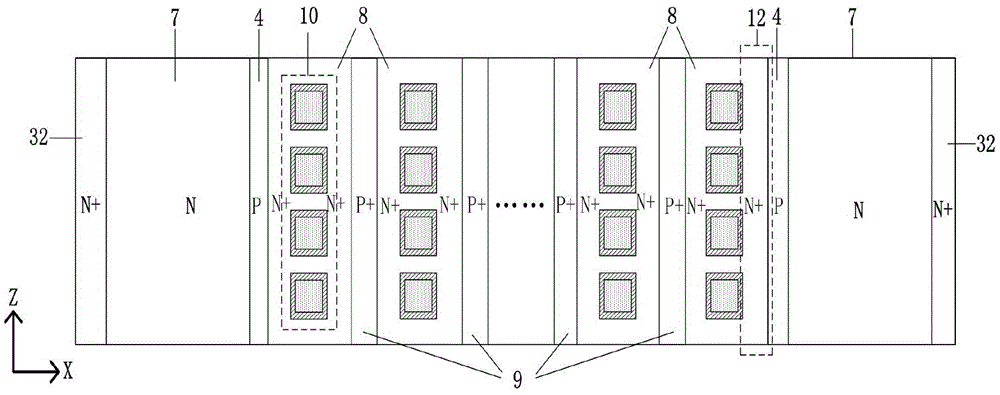

[0028] Such as figure 1 As mentioned above, it is a schematic diagram of the structure of the trench gate power MOSFET in Embodiment 1. This example includes the semiconductor substrate 1 of the second conductivity type and the heavily doped semiconductor drain region 31 of the first conductivity type above it; the heavily doped semiconductor of the first conductivity type Above the hetero-semiconductor drain region 31 is the semiconductor active layer 2 of the first conductivity type; the semiconductor body region 4 of the second conductivity type is arranged on the surface of the semiconductor active layer 2 of the first conductivity type. figure 2 It is a top view of the structure of this example. Depend on figure 1 and figure 2It can be seen from the figure that multiple columns of parallel trench gate structures 10 extend from the surface of the semiconductor body region 4 of the second conductivity type to the active layer 2 of the semiconductor of the first conducti...

Embodiment 2

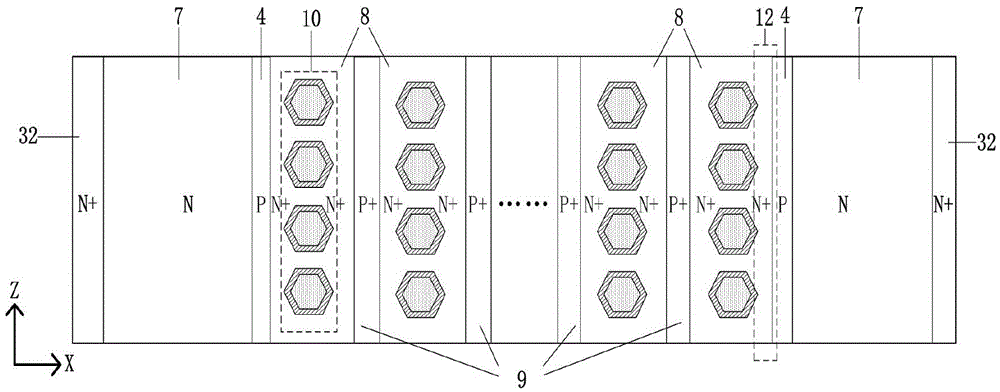

[0031] Such as image 3 As shown, the difference between this example and Example 1 is that the trench gate structure 10 is polygonal or circular in shape in a top view. The polygonal or circular trench gate can increase the current flow area and improve the current capacity.

Embodiment 3

[0033] Such as Figure 4 As shown, the difference between the structure of this example and that of Example 1 is that the trench gate source structure 14 is longitudinally composed of segmented heavily doped semiconductor source regions 8 of the first conductivity type and the second conductivity type A heavily doped semiconductor body contact region 9 of the second conductivity type is formed, and the heavily doped semiconductor body contact region 9 of the second conductivity type is surrounded by a heavily doped semiconductor source region 8 of the first conductivity type. Figure 5 It is a cross-sectional view along AA' (half cell) of this example. It can be seen from the figure that the size of the device is further reduced, thereby effectively reducing the specific on-resistance of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More