Patents

Literature

37results about How to "Variation in resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

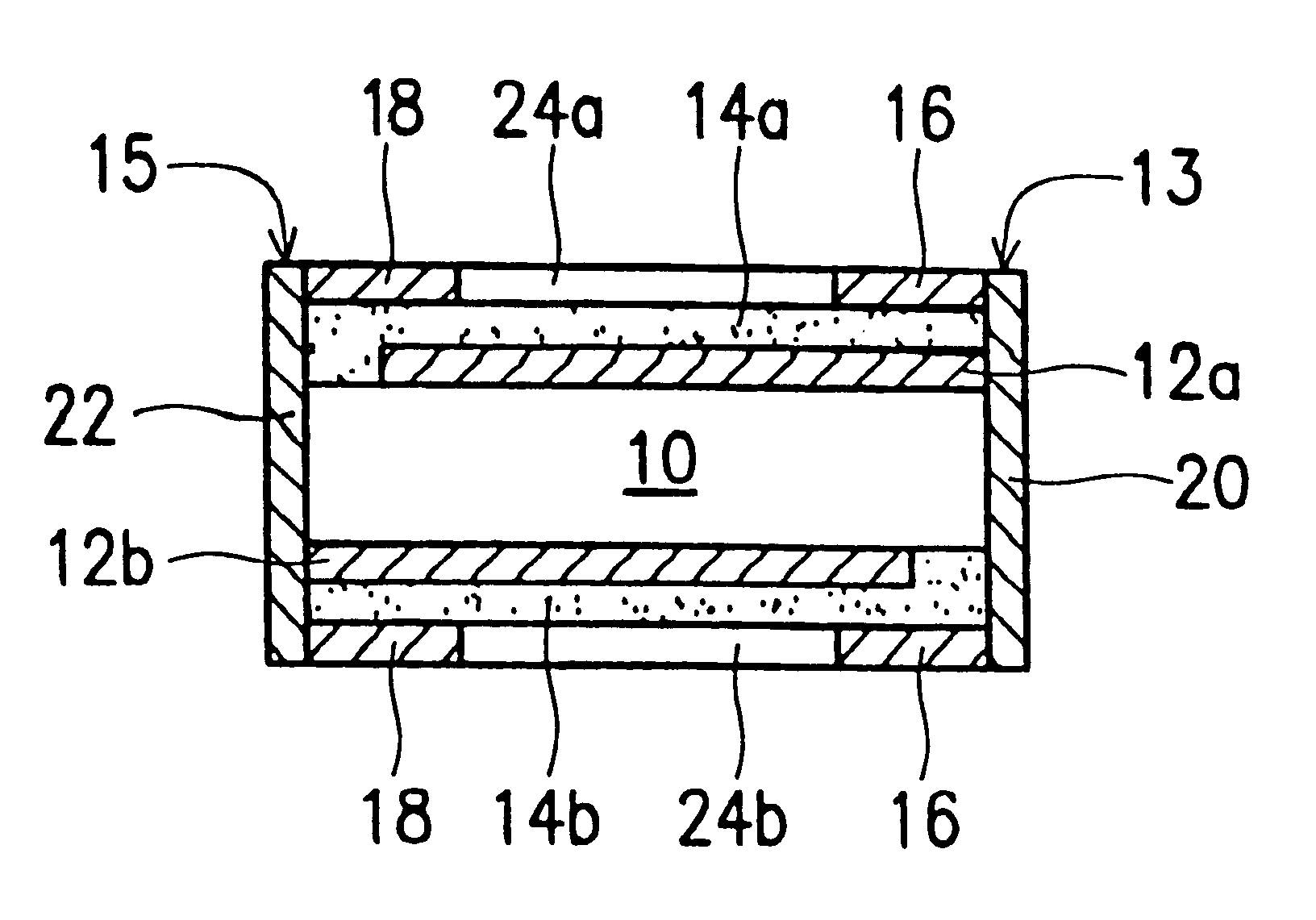

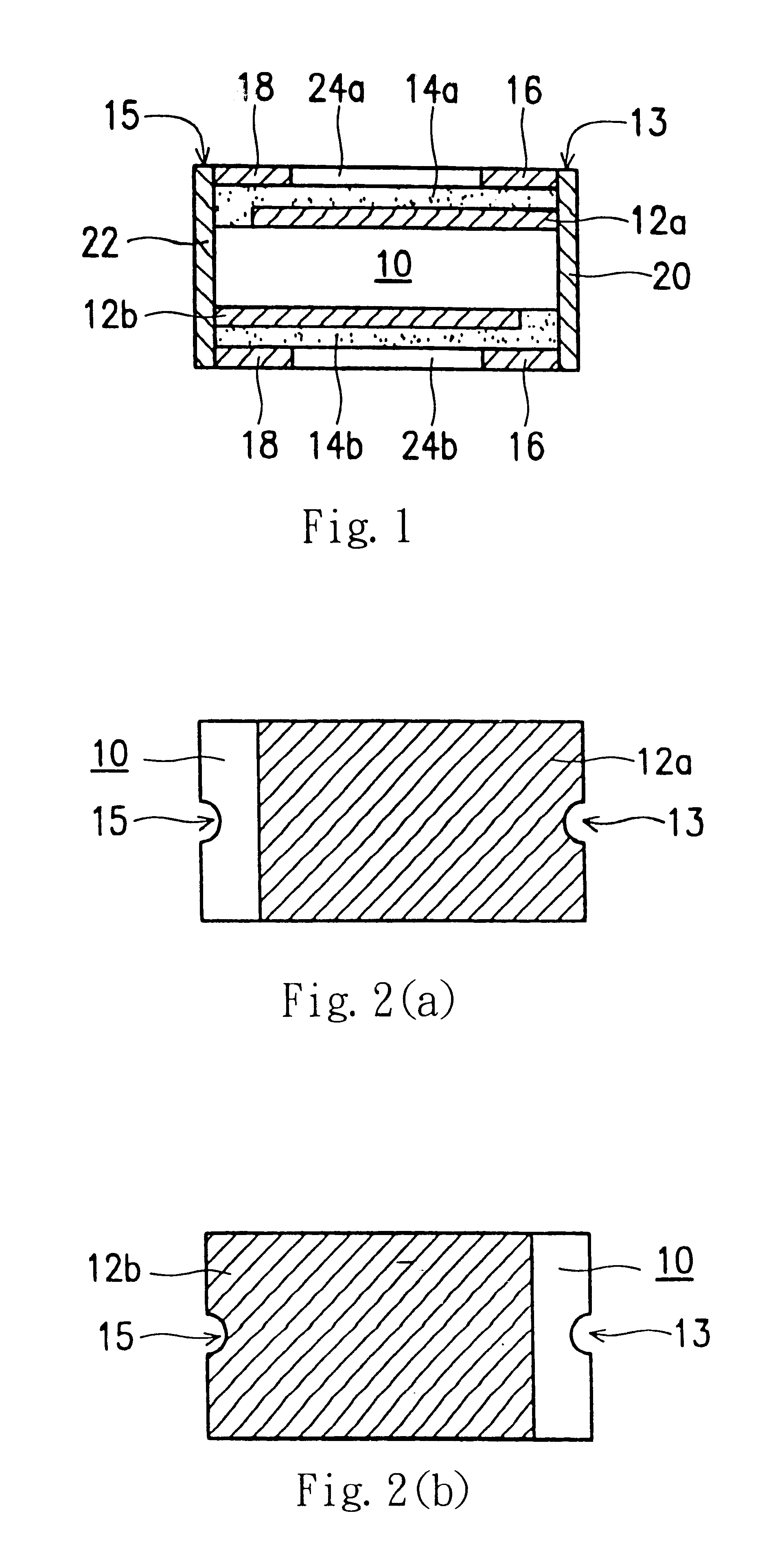

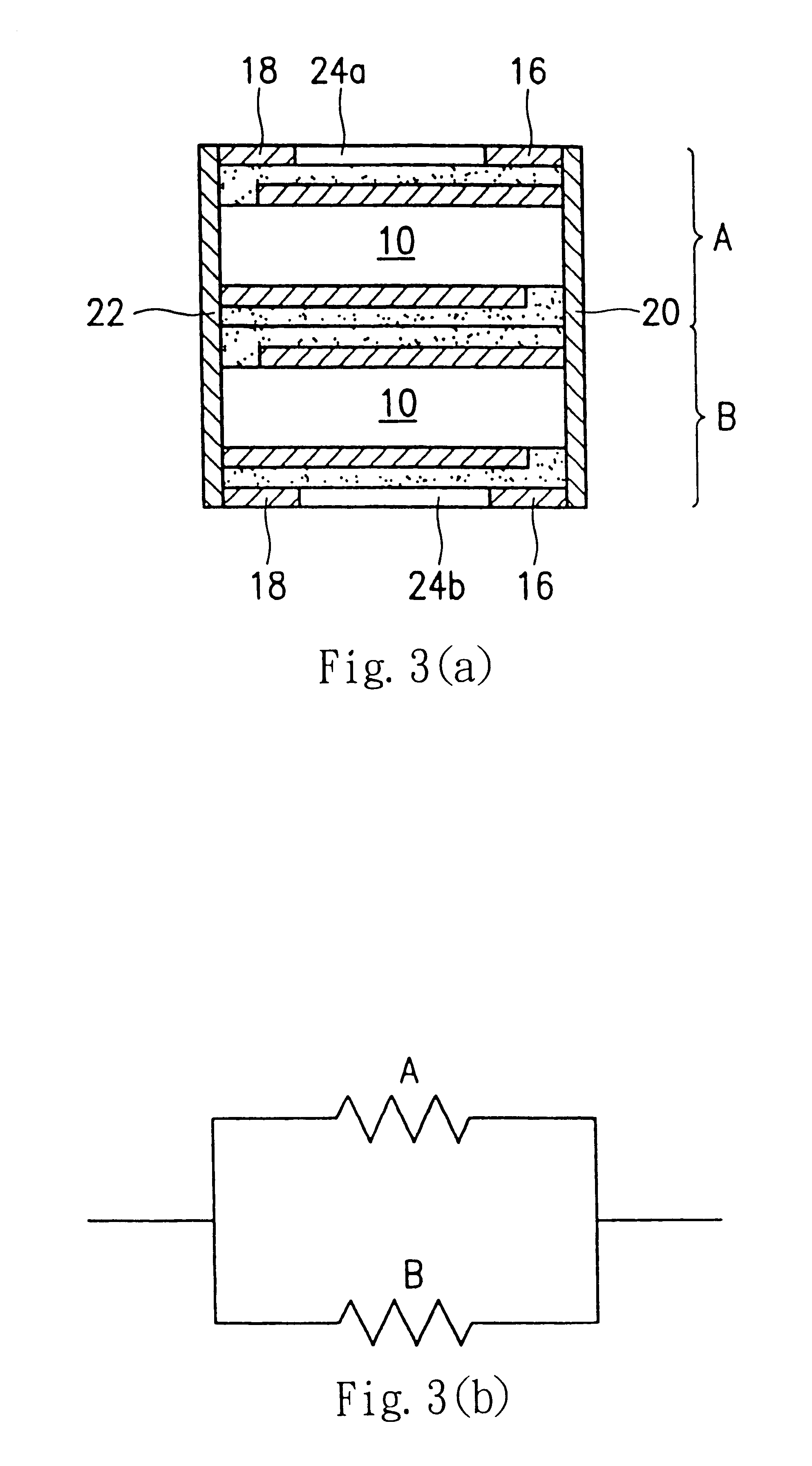

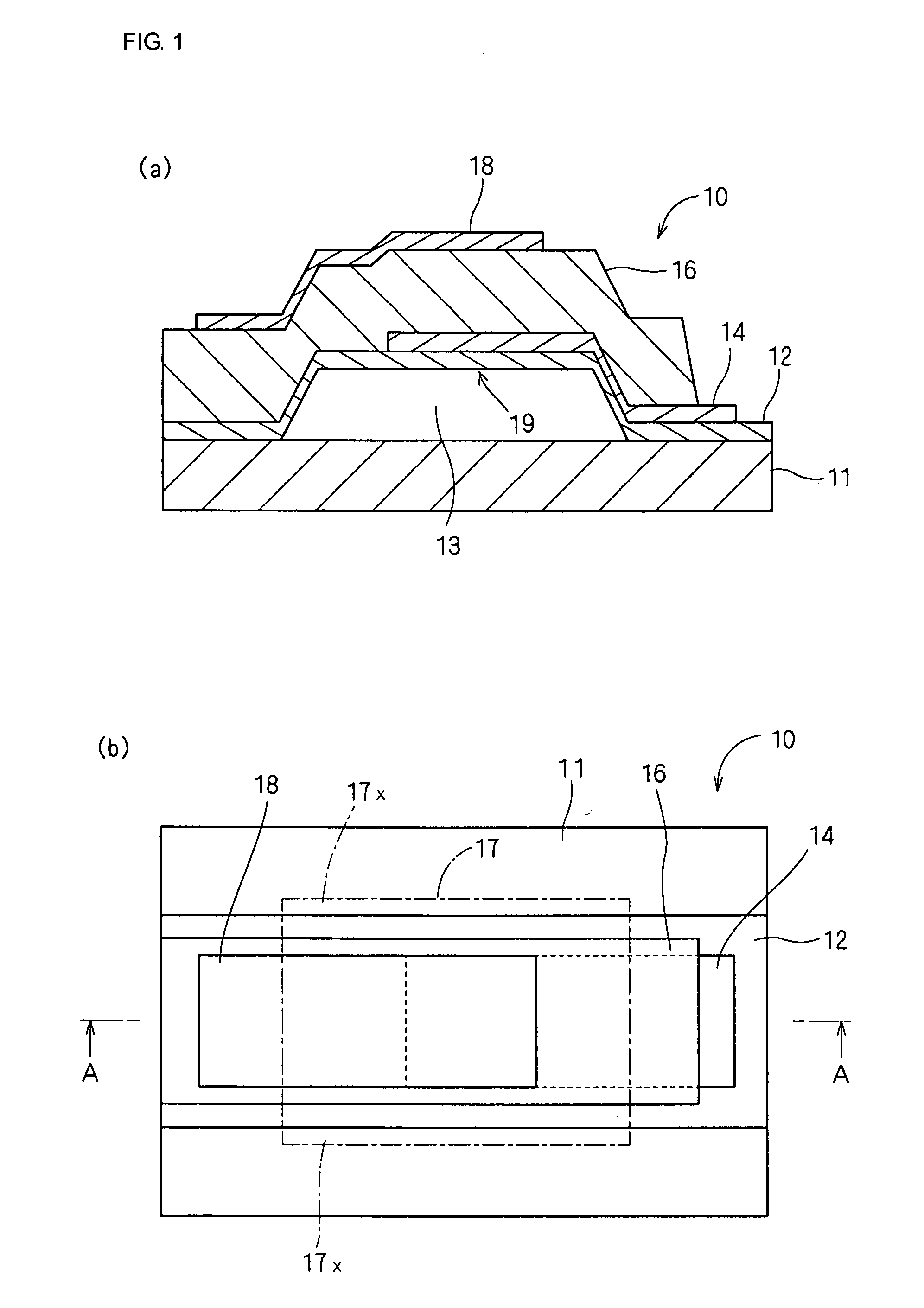

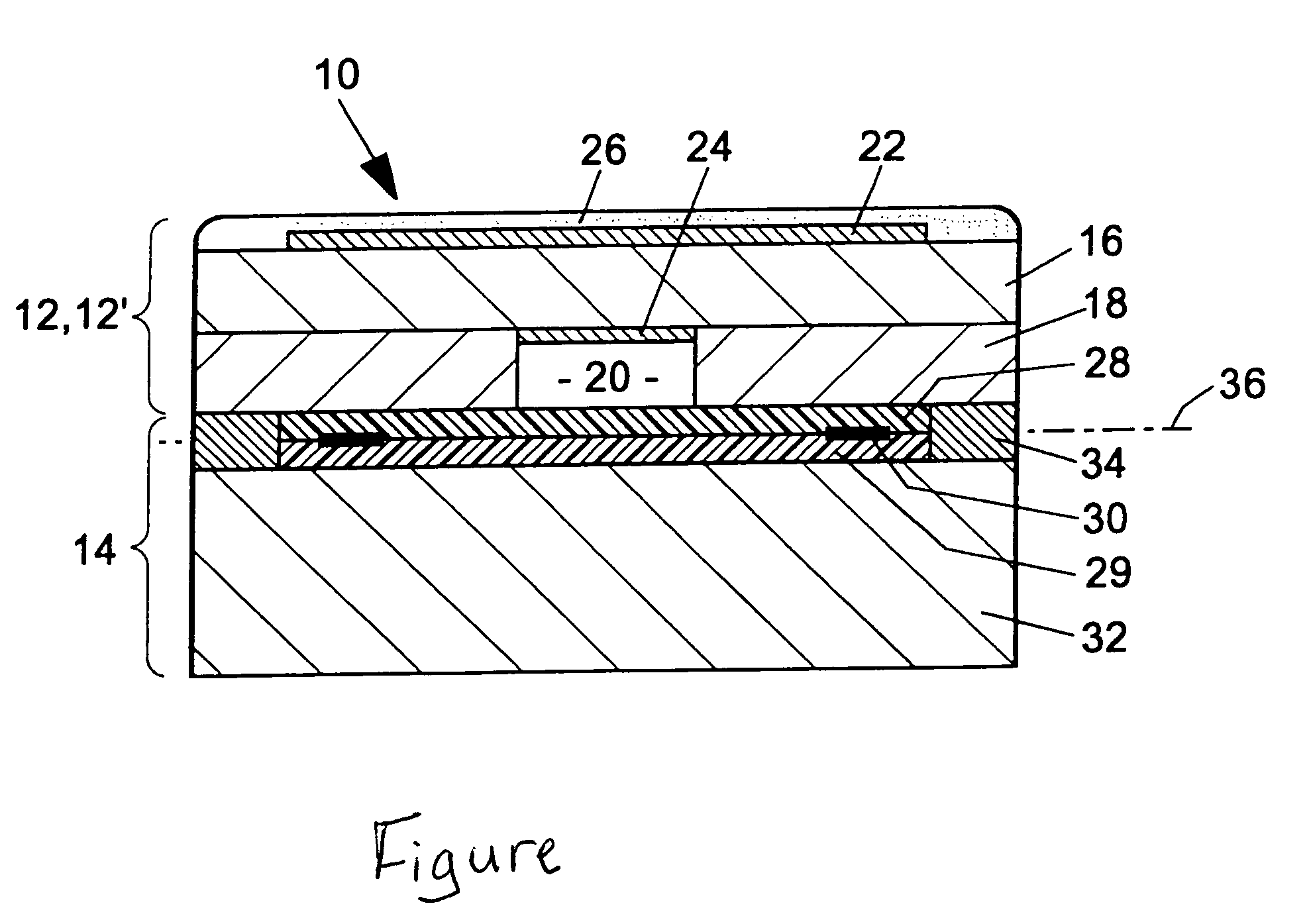

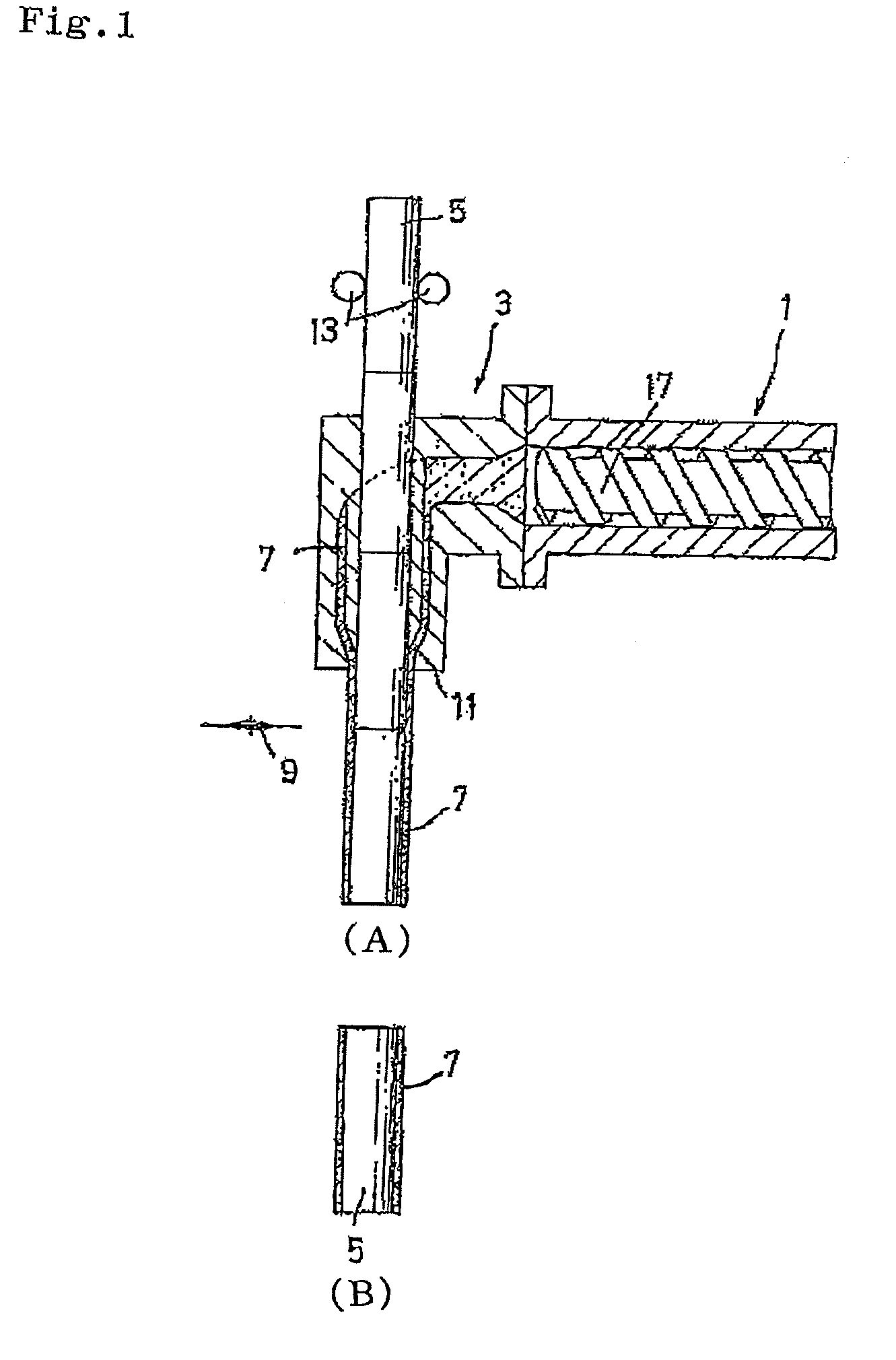

Surface mountable over-current protecting device

InactiveUS6377467B1Easy to installGood dimensional stabilityResistor terminals/electrodesNegative temperature coefficient thermistorsElectrical resistance and conductancePlanar electrode

The present invention relates to a novel thermal-sensitive resistive apparatus, such as PTC and NTC, which allocates planar electrode films on the top and bottom surfaces of a prior art thermal-sensitive resistive apparatus, such as a PTC apparatus, to laminate with an outer electrode layer. A plurality of interconnection vias are electroplated with conductive material to connect to any plane. It is convenient to surface mount the apparatus of the present invention on a printed circuit board. The present invention can largely increase the dimensional stability of components and overcome the disadvantage that thermal diffusion of the prior are surface mounted resistive apparatus is affected easily by line width and environments.

Owner:POLYTRONICS TECH

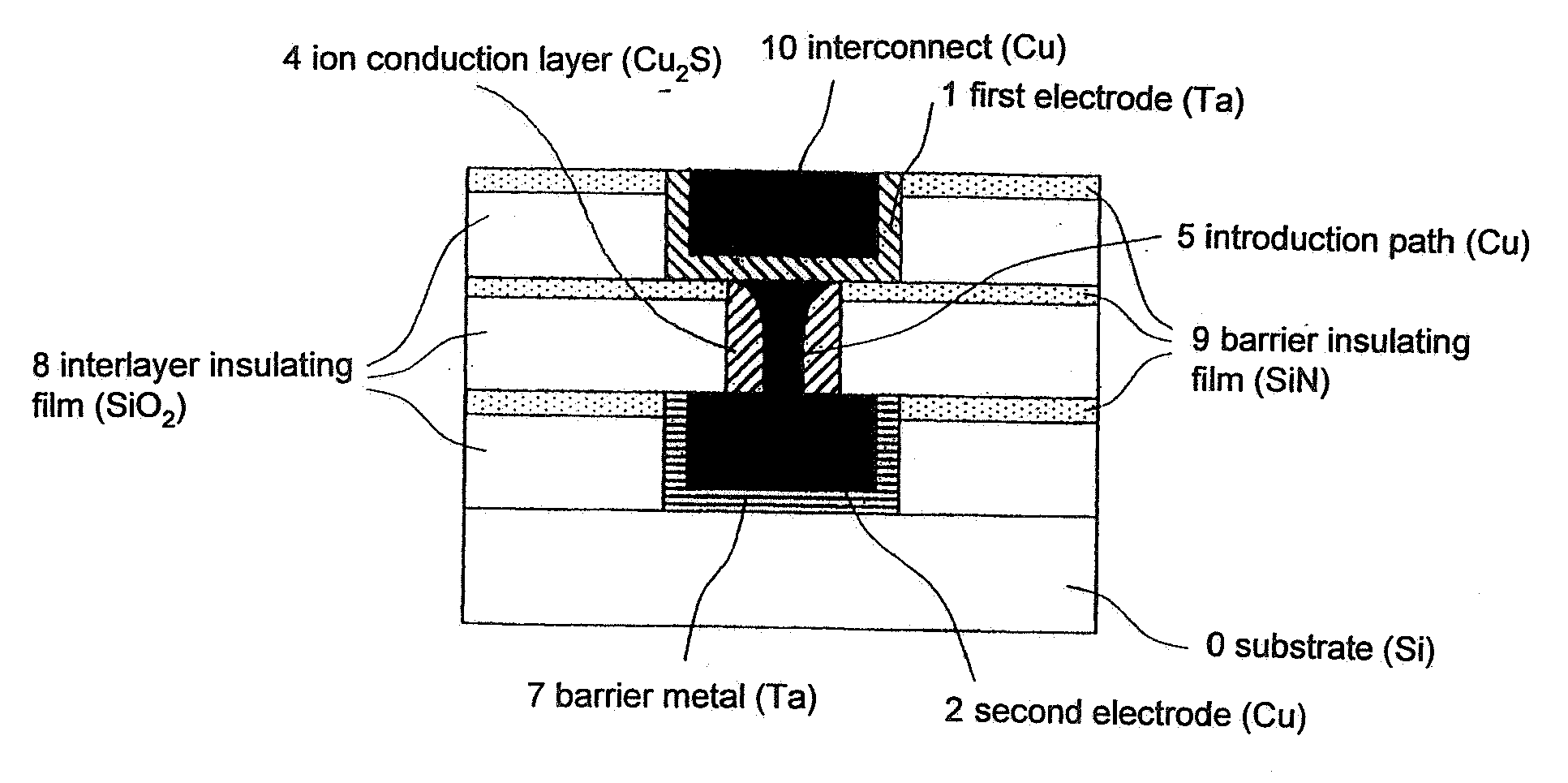

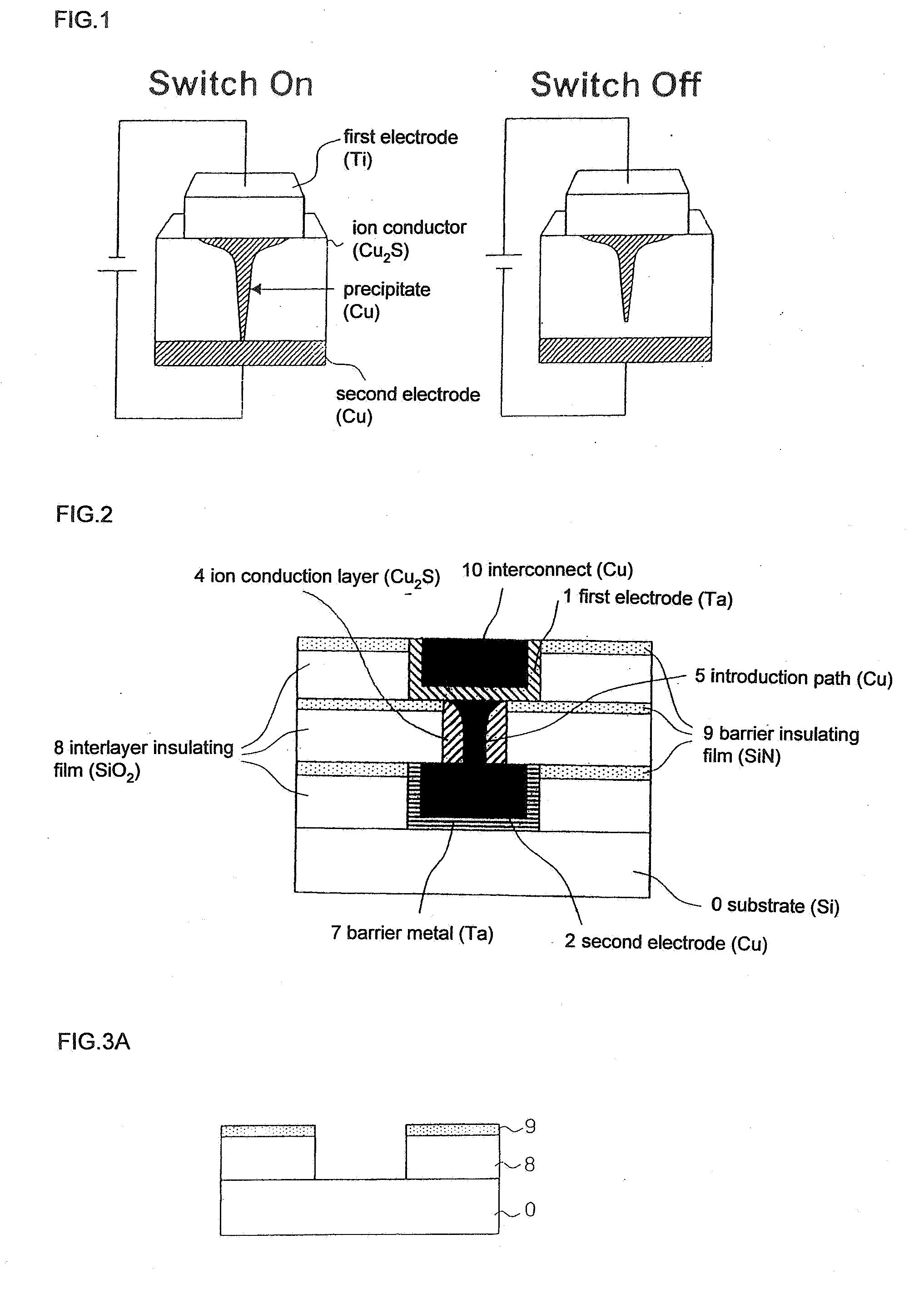

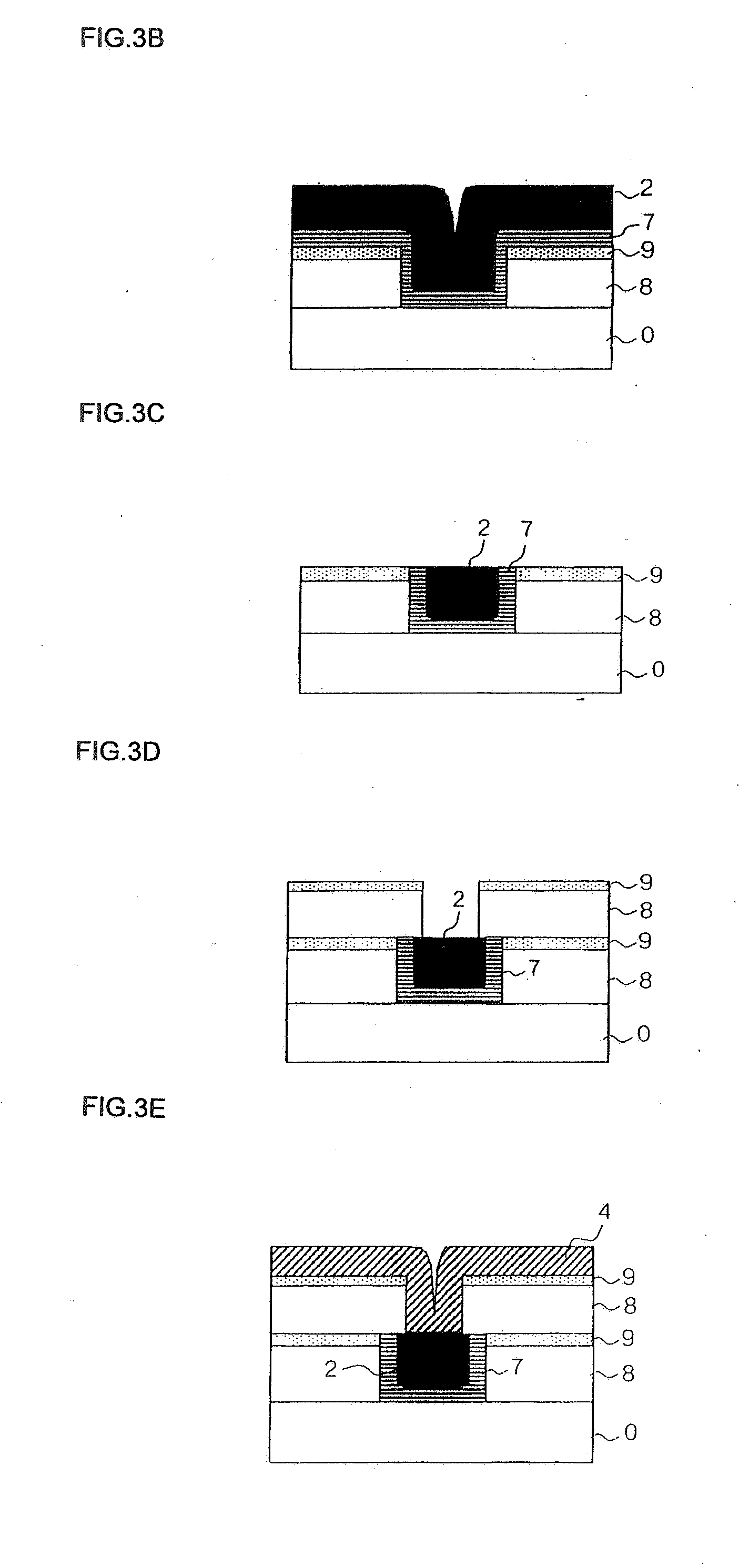

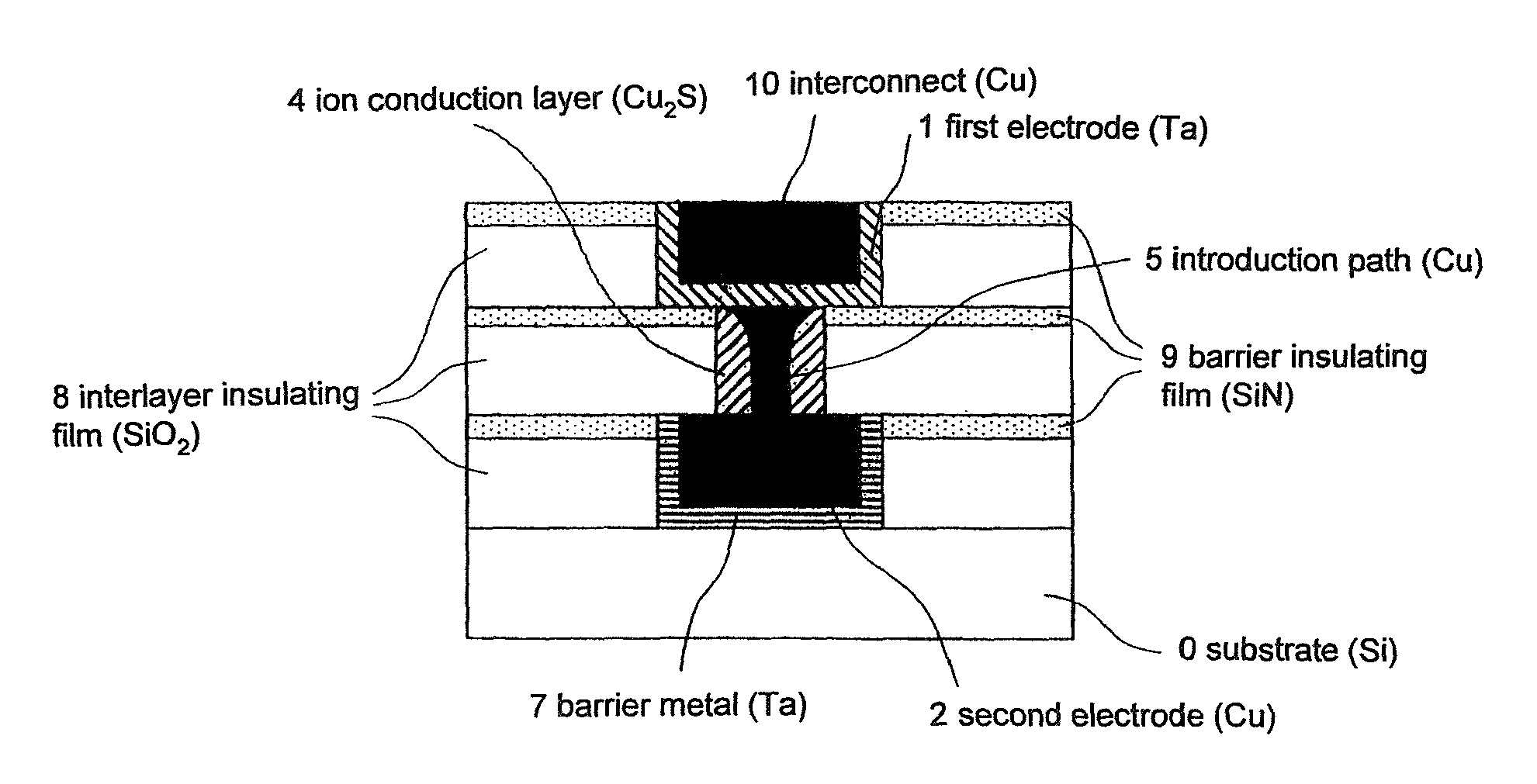

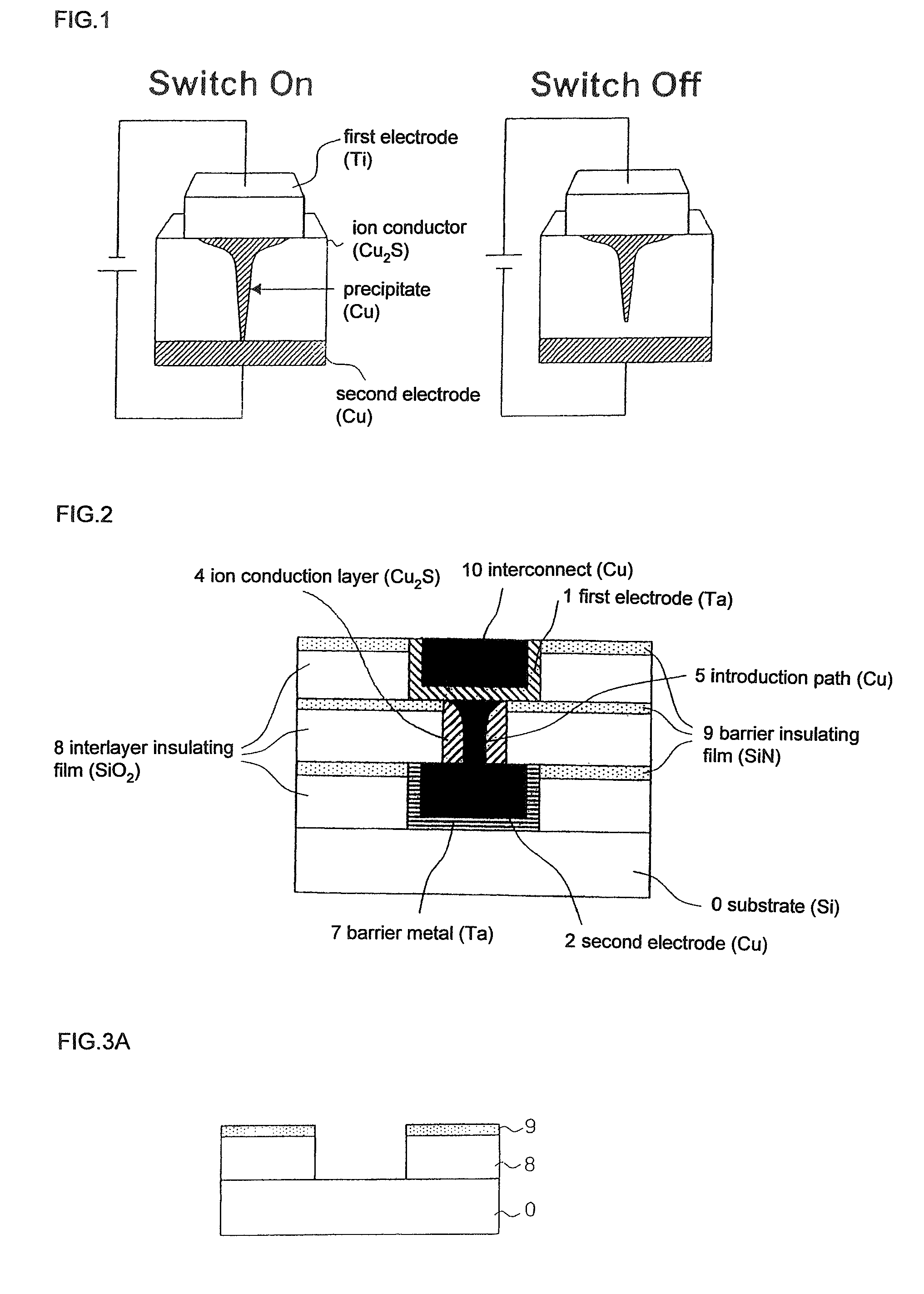

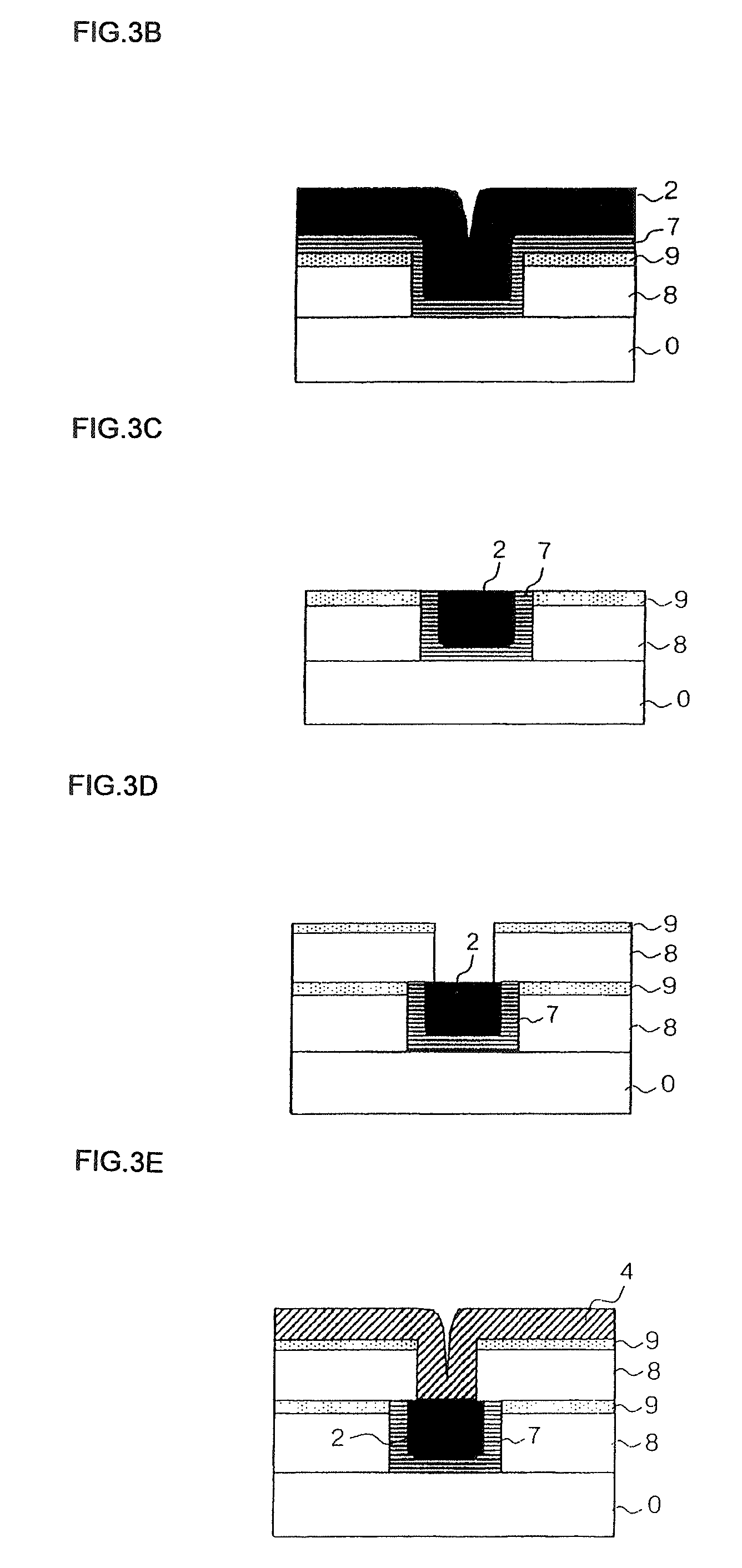

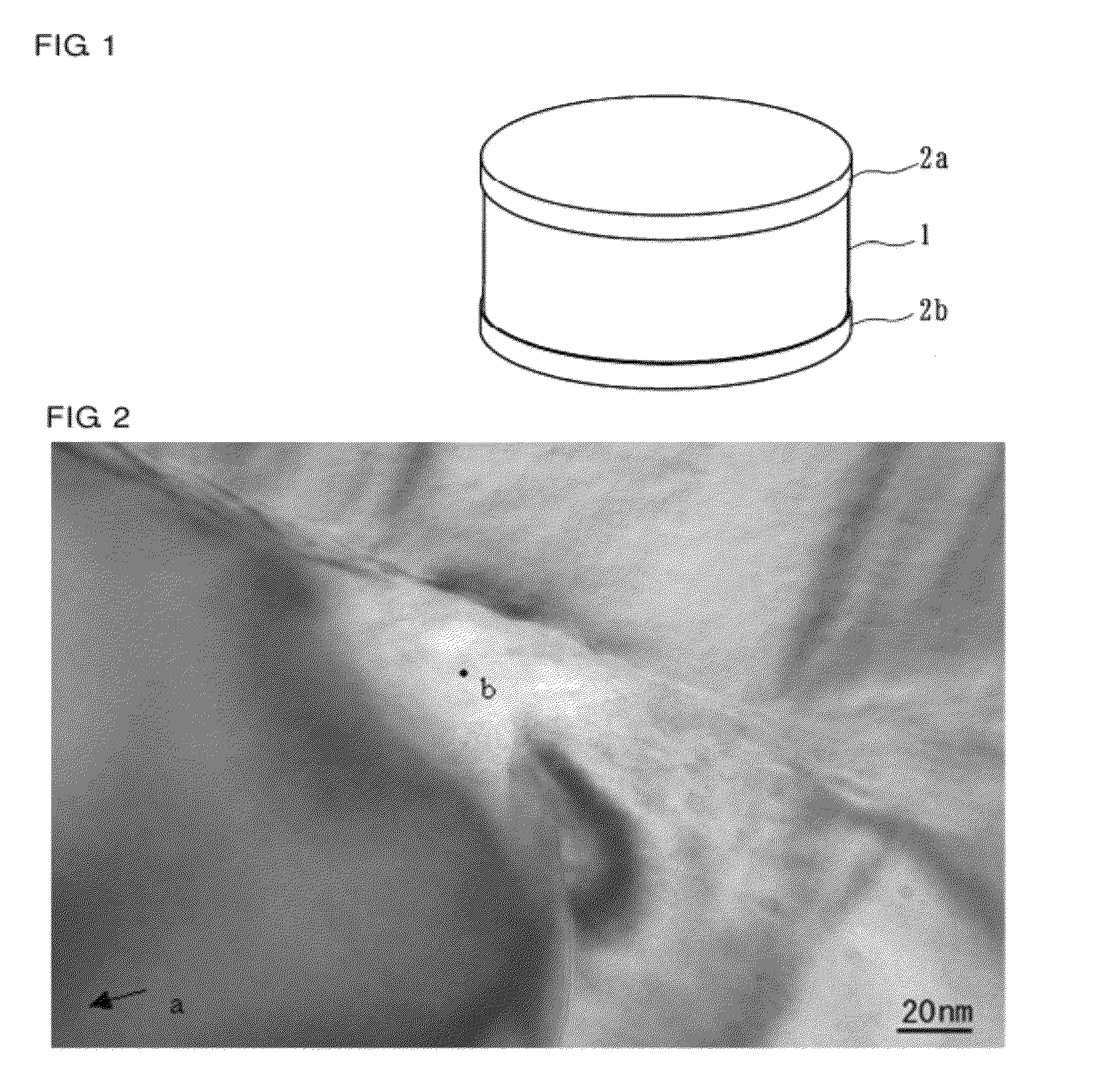

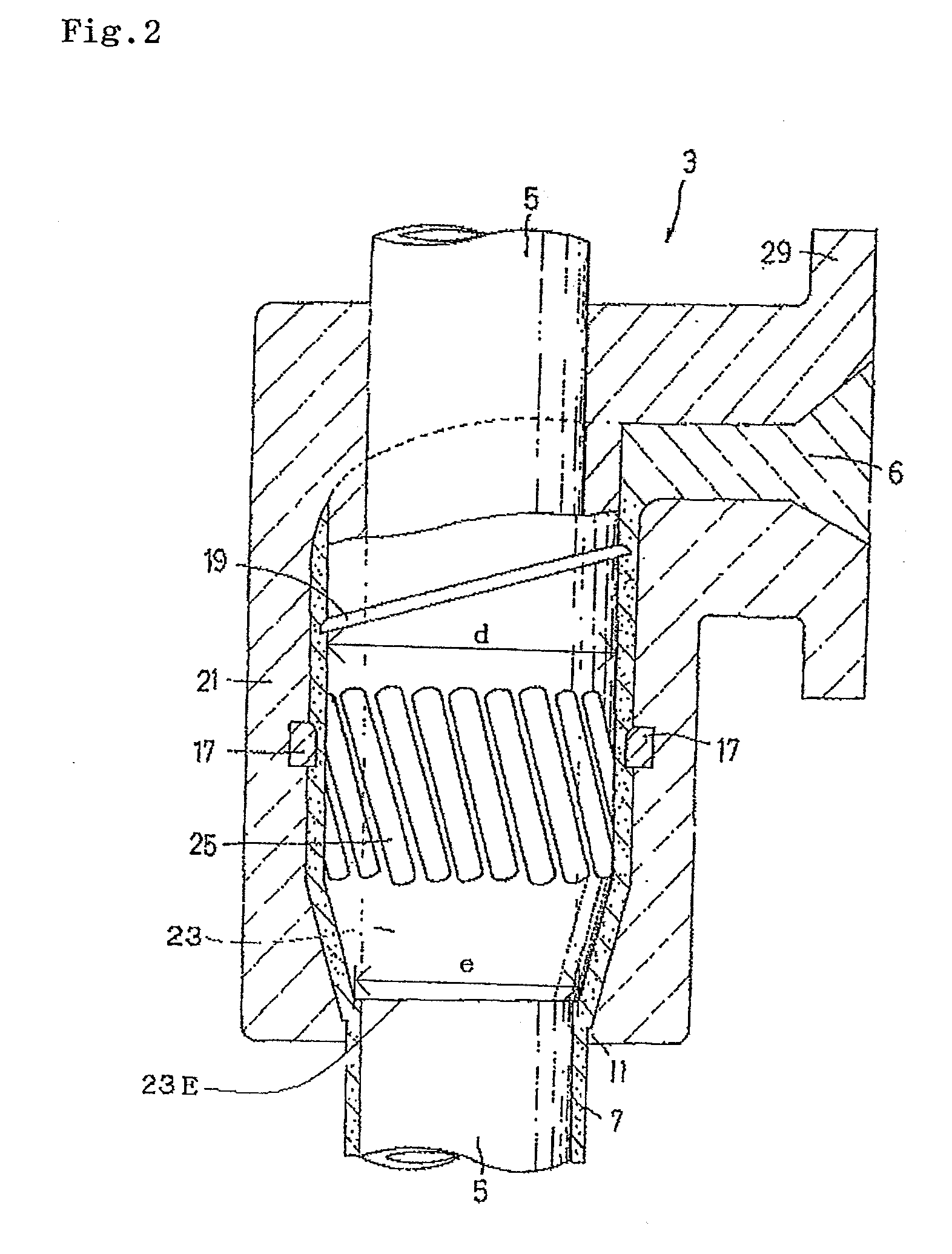

Switching Element, Switching Element Drive Method and Fabrication Method, Reconfigurable Logic Integrated Circuit, and Memory Element

ActiveUS20080036508A1Variation in resistanceIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesIonIntegrated circuit

The switching element of the present invention includes: an ion conduction layer (4) in which metal ions can move freely; a first electrode (1) that contacts the ion conduction layer (4); and a second electrode (2) that contacts the ion conduction layer (4), that is formed such that the ion conduction layer (4) is interposed between the first electrode (1) and the second electrode (2), and that supplies metal ions to the ion conduction layer (4) or that receives metal ions from the ion conduction layer (4) to cause precipitation of the metal that corresponds to the metal ions. An introduction path (5) composed of the metal and of a prescribed width is further provided on the ion conduction layer (4) for electrically connecting the first electrode (1) and the second electrode (2). The application of voltage to the first electrode (1) relative to the second electrode (2) then causes an electrochemical reaction between the introduction path (5) and the second electrode (2) whereby the electrical characteristics are switched.

Owner:NEC CORP

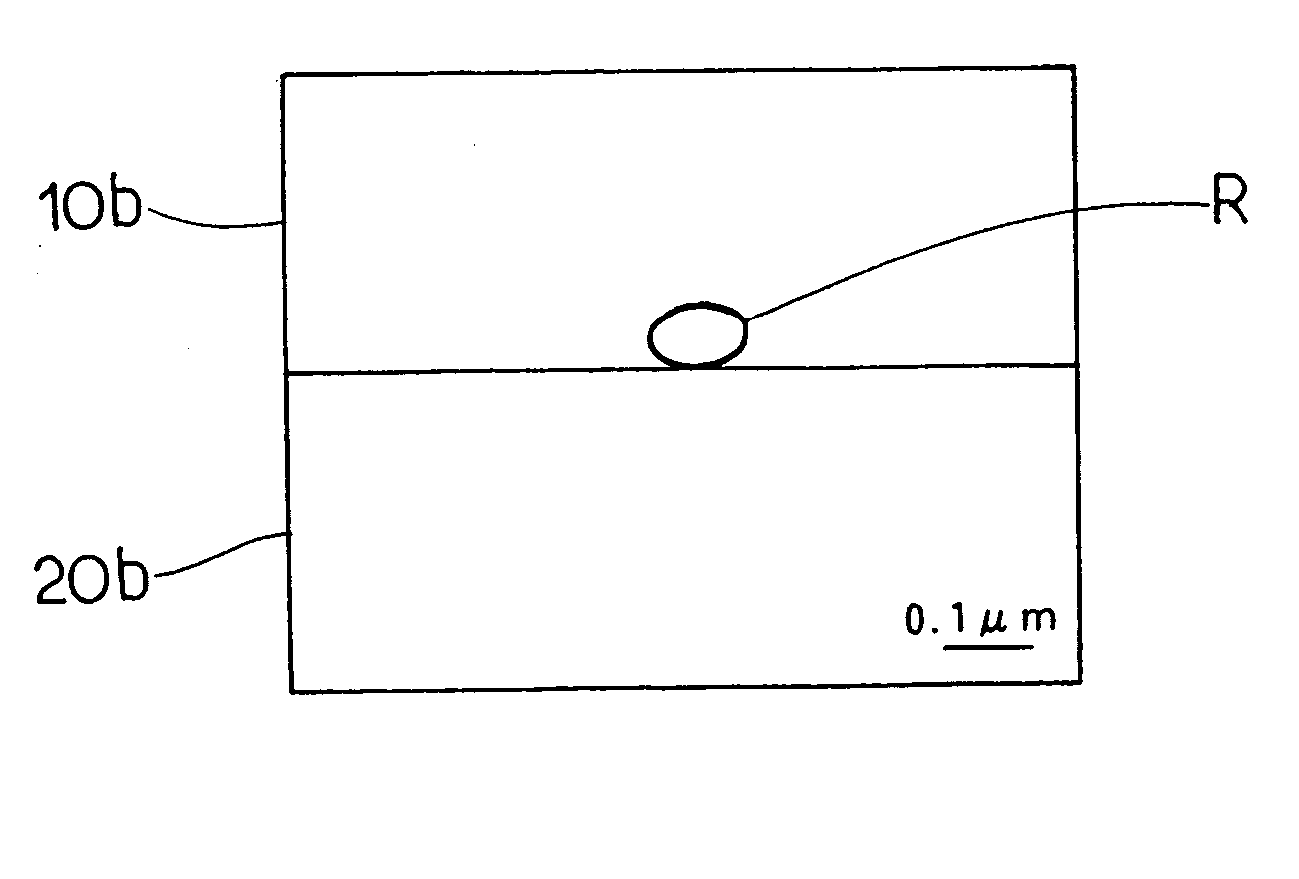

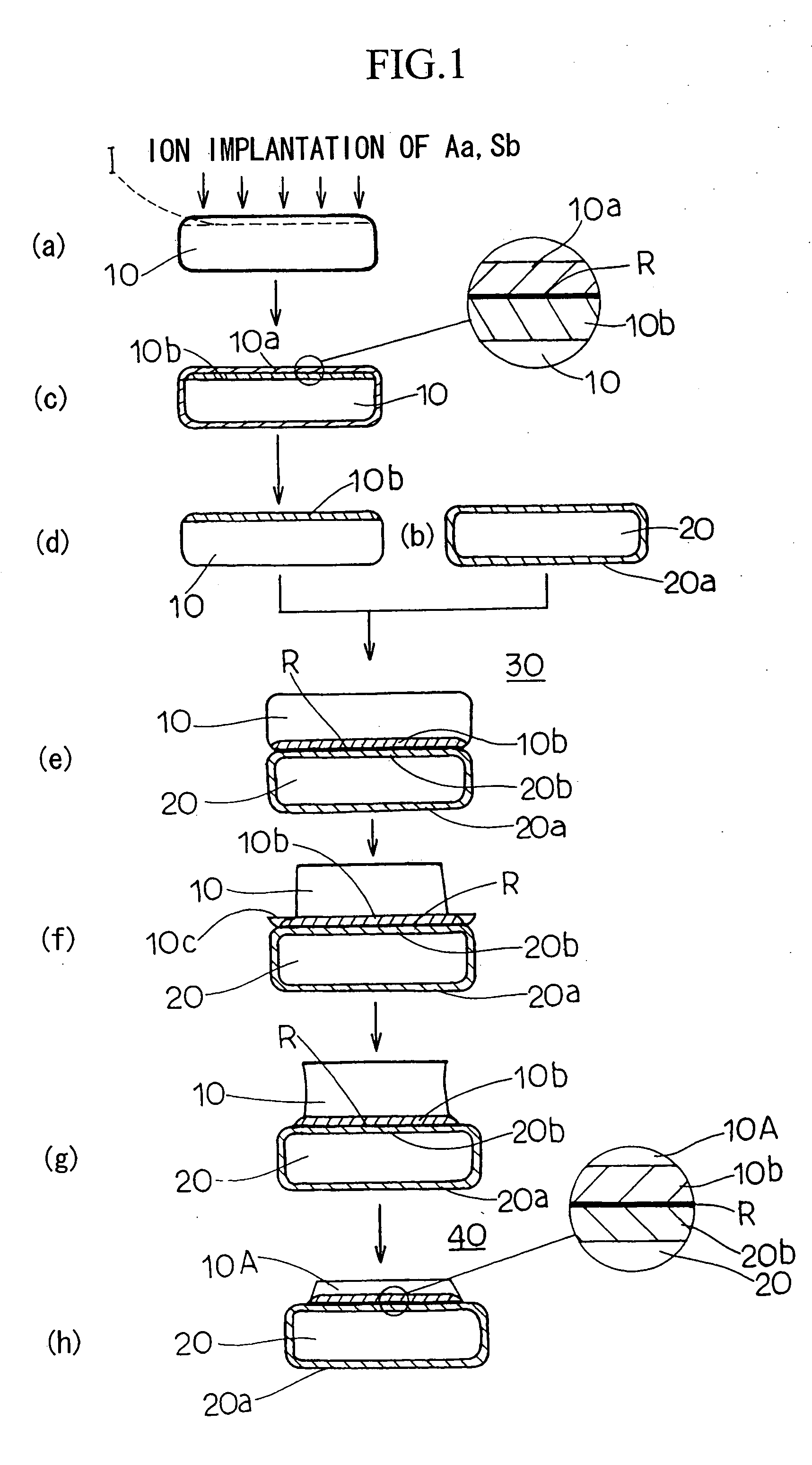

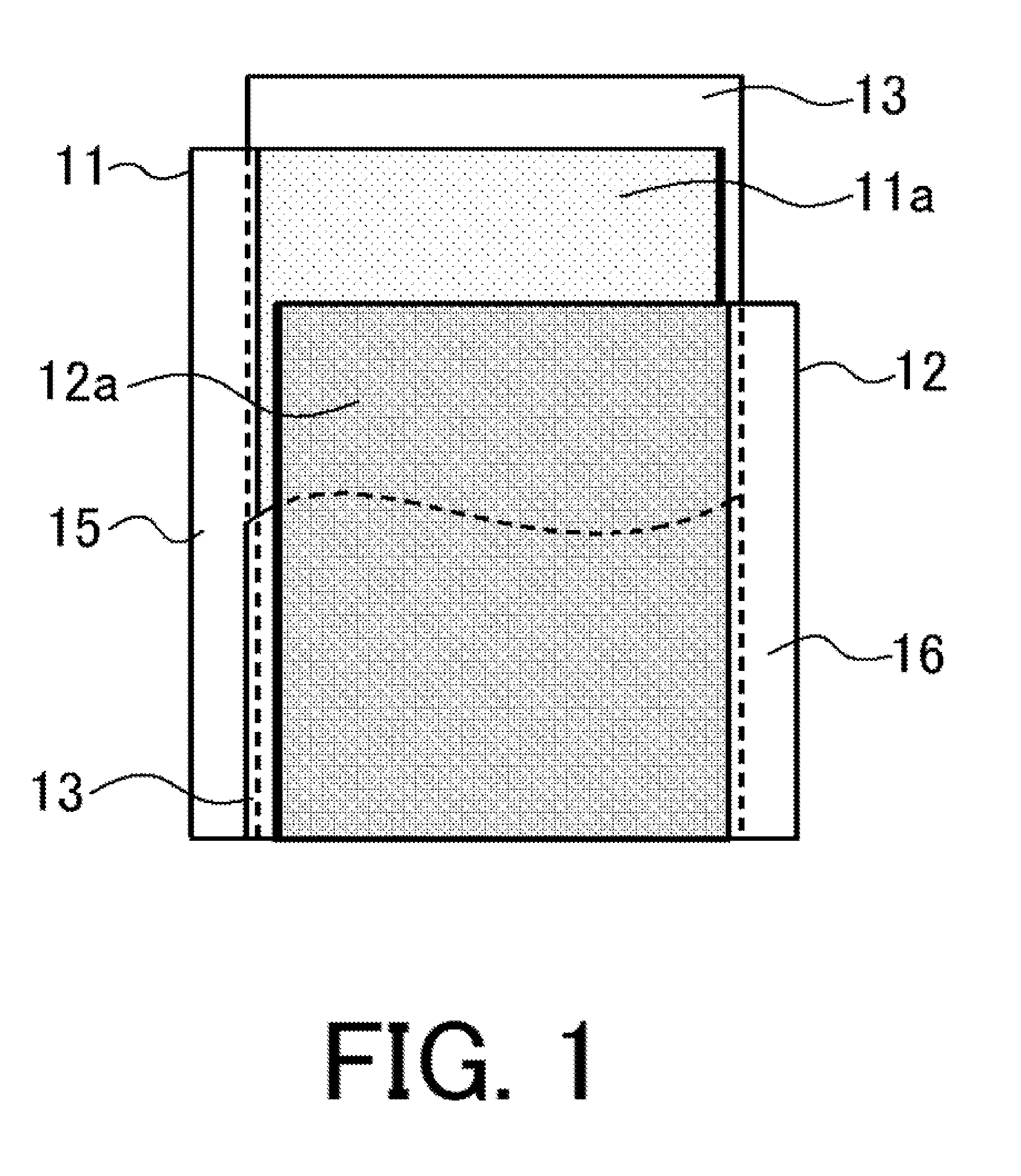

Bonded SOI substrate, and method for manufacturing the same

ActiveUS20060055003A1Avoid thickerVariation in resistanceSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsDopant

This bonded SOI substrate includes: an SOI layer having a low density impurity layer in which dopants are present at low density and a high density impurity layer in which dopants are present at high density; a wafer for a support substrate which supports said SOI layer; and a buried insulating film, wherein said SOI layer and said wafer for a support substrate are bonded with said buried insulating film therebetween, and gettering sites are formed in said high density impurity layer.

Owner:SUMCO CORP

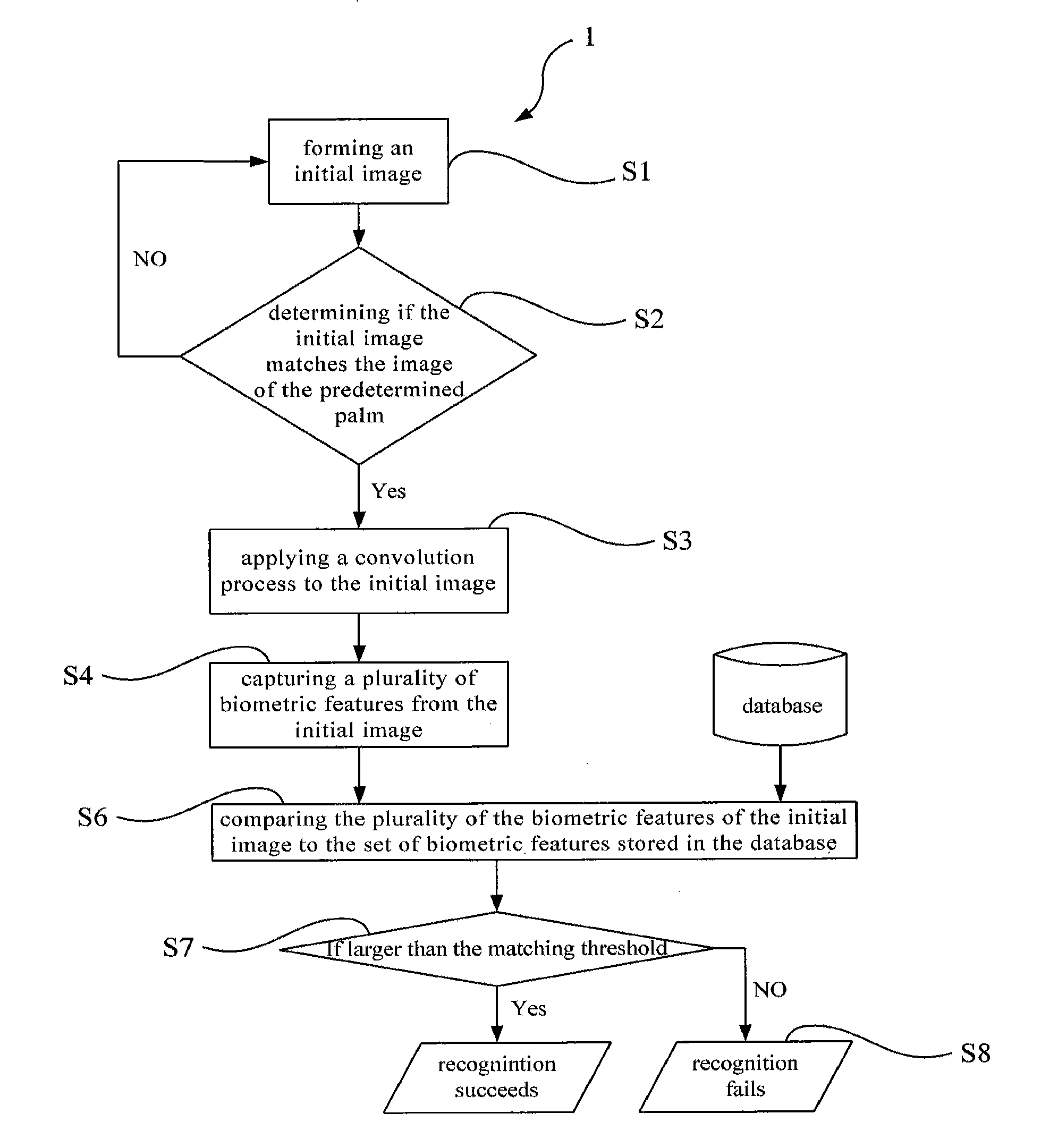

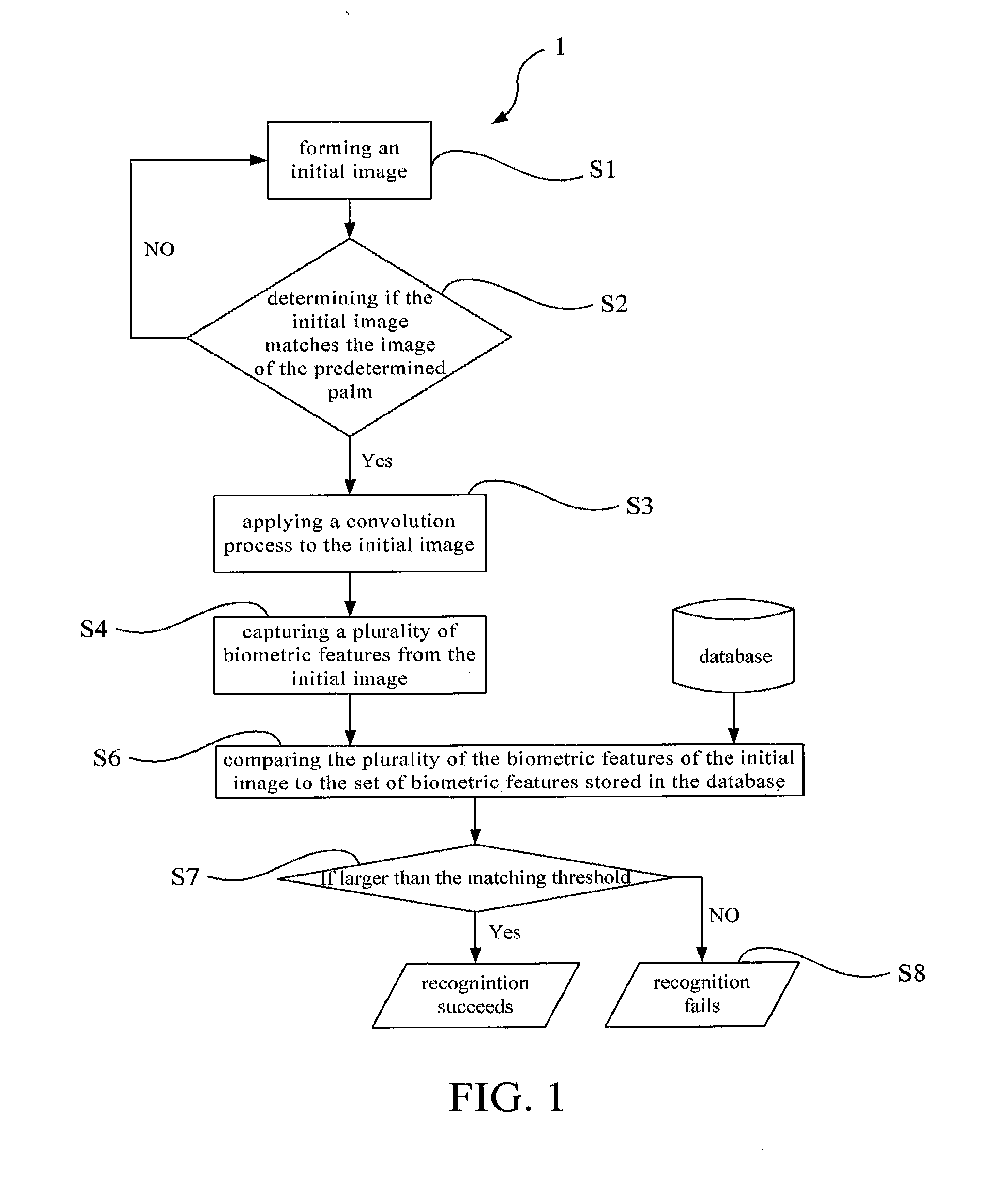

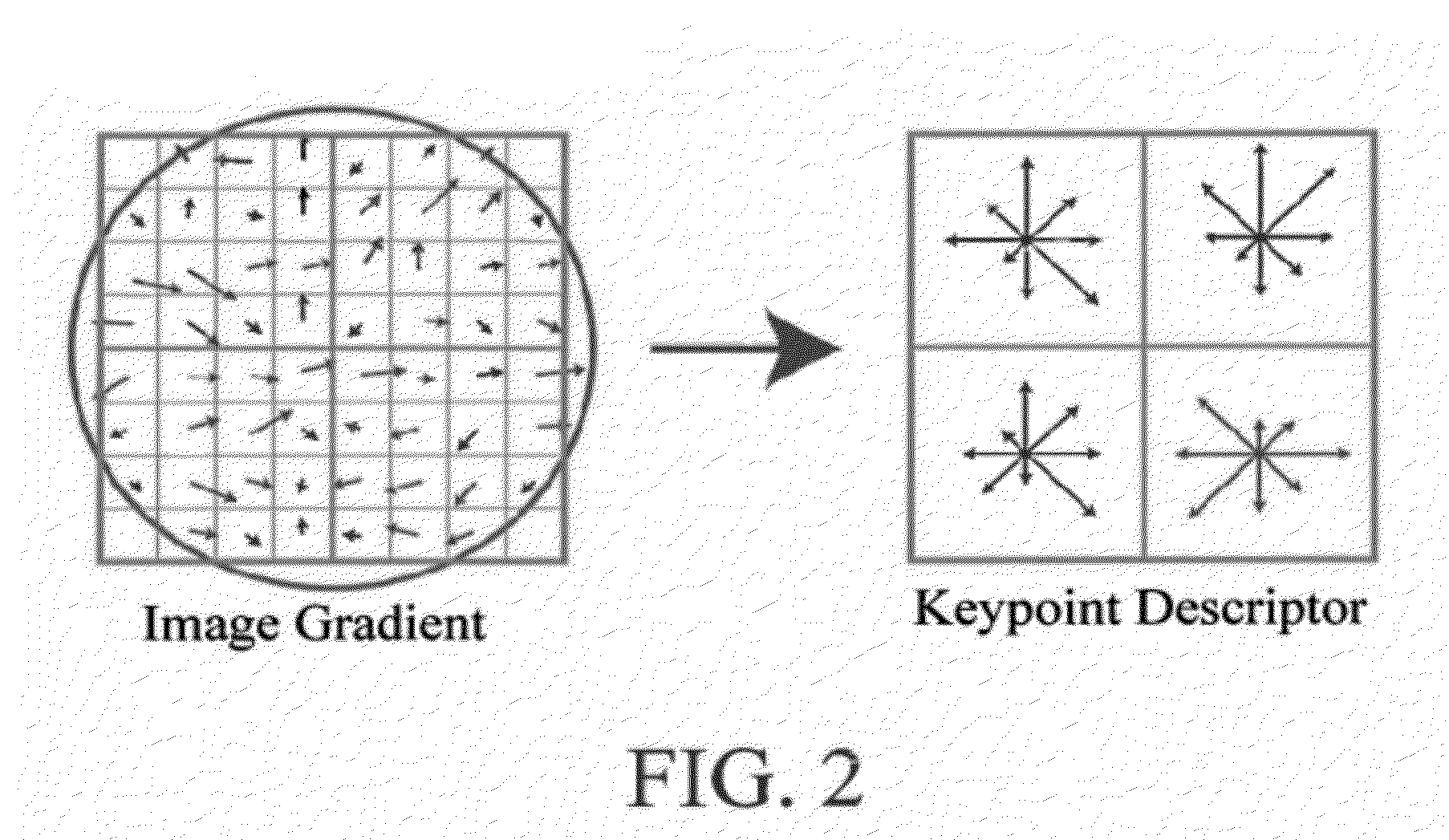

Method for recognizing the identity of user by biometrics of palm vein

InactiveUS20120057763A1Improve efficiencyImprove accuracySubcutaneous biometric featuresBlood vessel patternsPattern recognitionIdentity recognition

The present invention discloses an identity recognition method for recognizing the biometric features of a predetermined palm by biometric features stored in a database. The method of the invention includes the following steps of: (S1) forming an initial image; (S2) determining if the initial image matches the image of the palm, if yes, process step (S3); (S3) applying a convolution process to the initial image; (S4) capturing a plurality of biometric features by Scale Invariant Feature Transformation (SIFT); and (S6) comparing the plurality of the biometric features of the initial image to the biometric features stored in the database.

Owner:NAT TAIWAN UNIV OF SCI & TECH

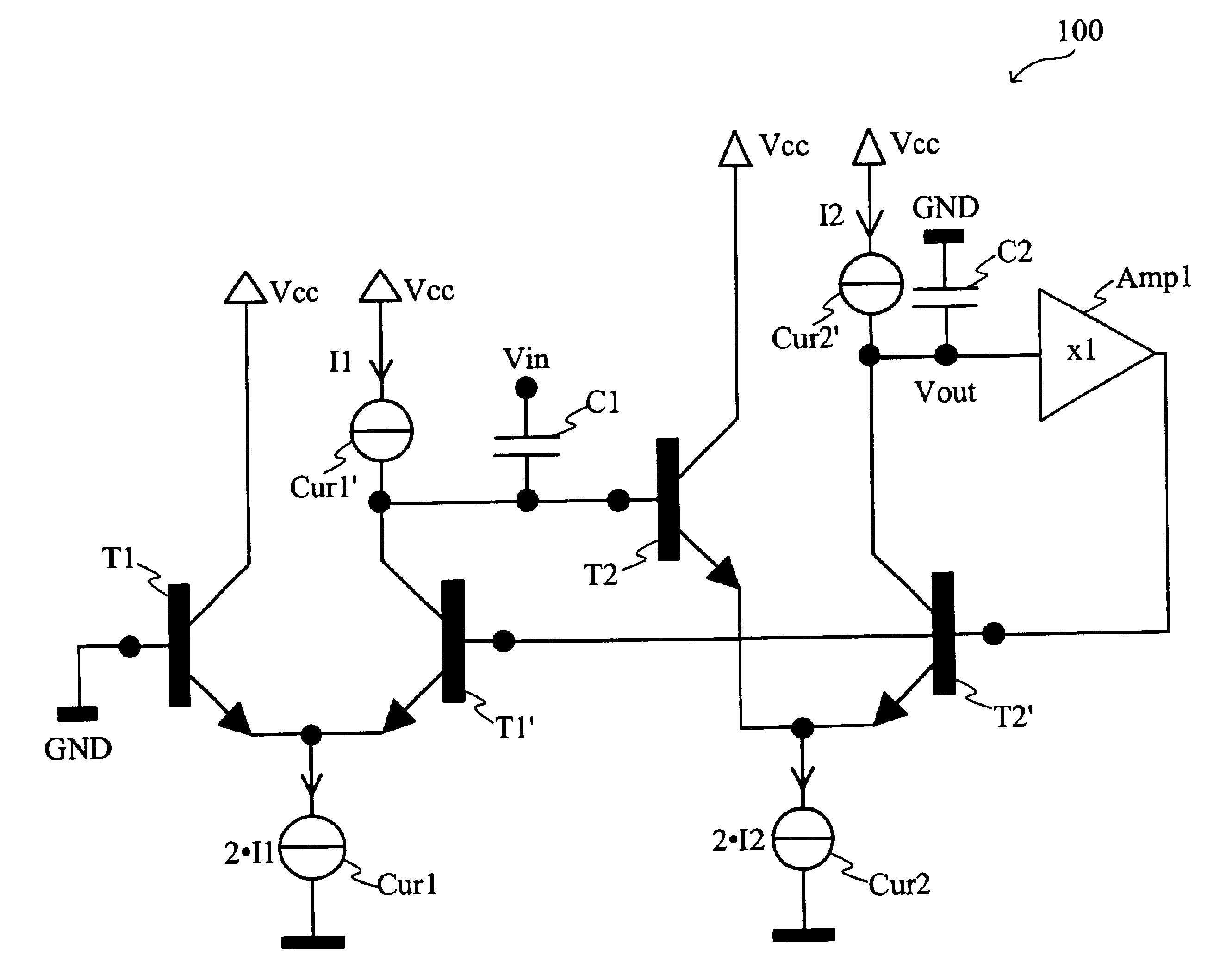

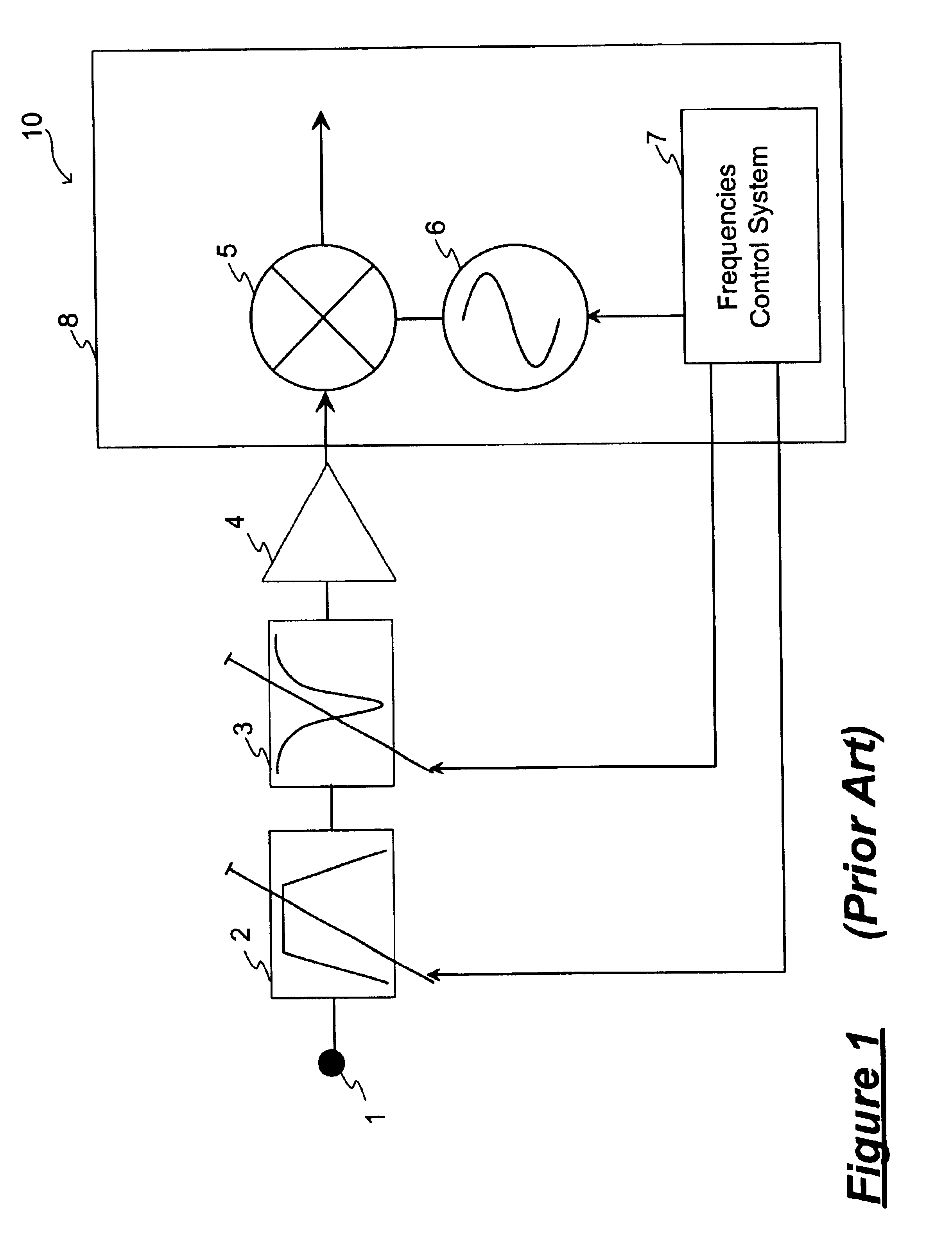

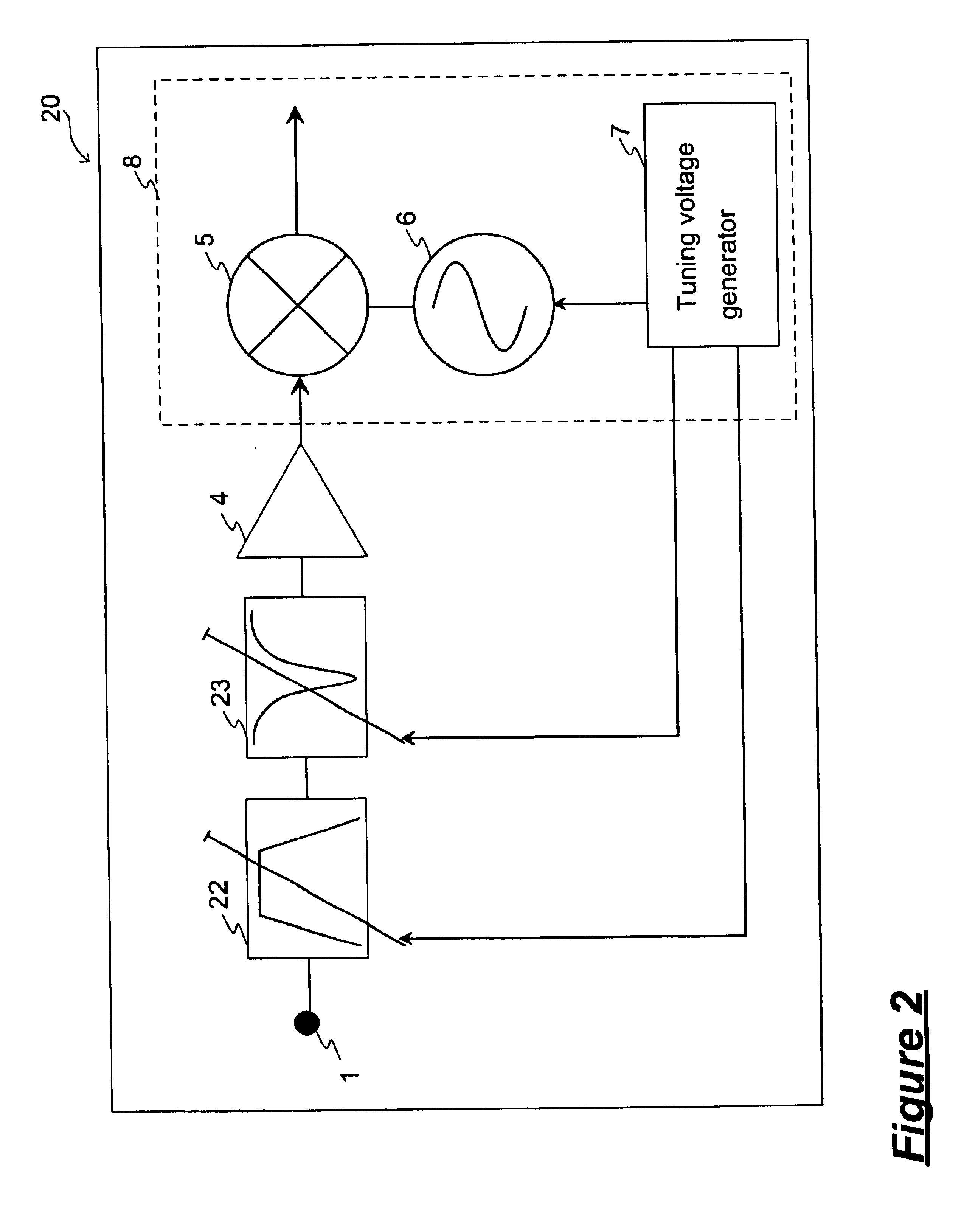

Integrated tunable filter for broadband tuner

ActiveUS6915121B2Precise changeVariation in resistanceContinuous tuning detailsRadio transmissionBandpass filteringEngineering

A tunable filter circuit includes a first differential pair biased by a first current, a second differential pair biased by a second current, a first capacitor and a second capacitor. The tunable filter circuit of the present invention can be configured as a bandpass filter or a bandstop filter by connecting the input voltage signal to different input nodes of the tunable filter circuit. The tunable filter circuit can be tuned by adjusting the values of the first current and the second current. In an alternate embodiment, frequency tuning is achieved either by switching capacitive loads or changing resistive impedances introduced at the emitter of the differential pairs, which also extends the input voltage range of the filter. This emitter resistance is implemented using MOS switches whose on-resistance can be controlled for a precise tuning within a large frequency range.

Owner:CF CRESPE LLC

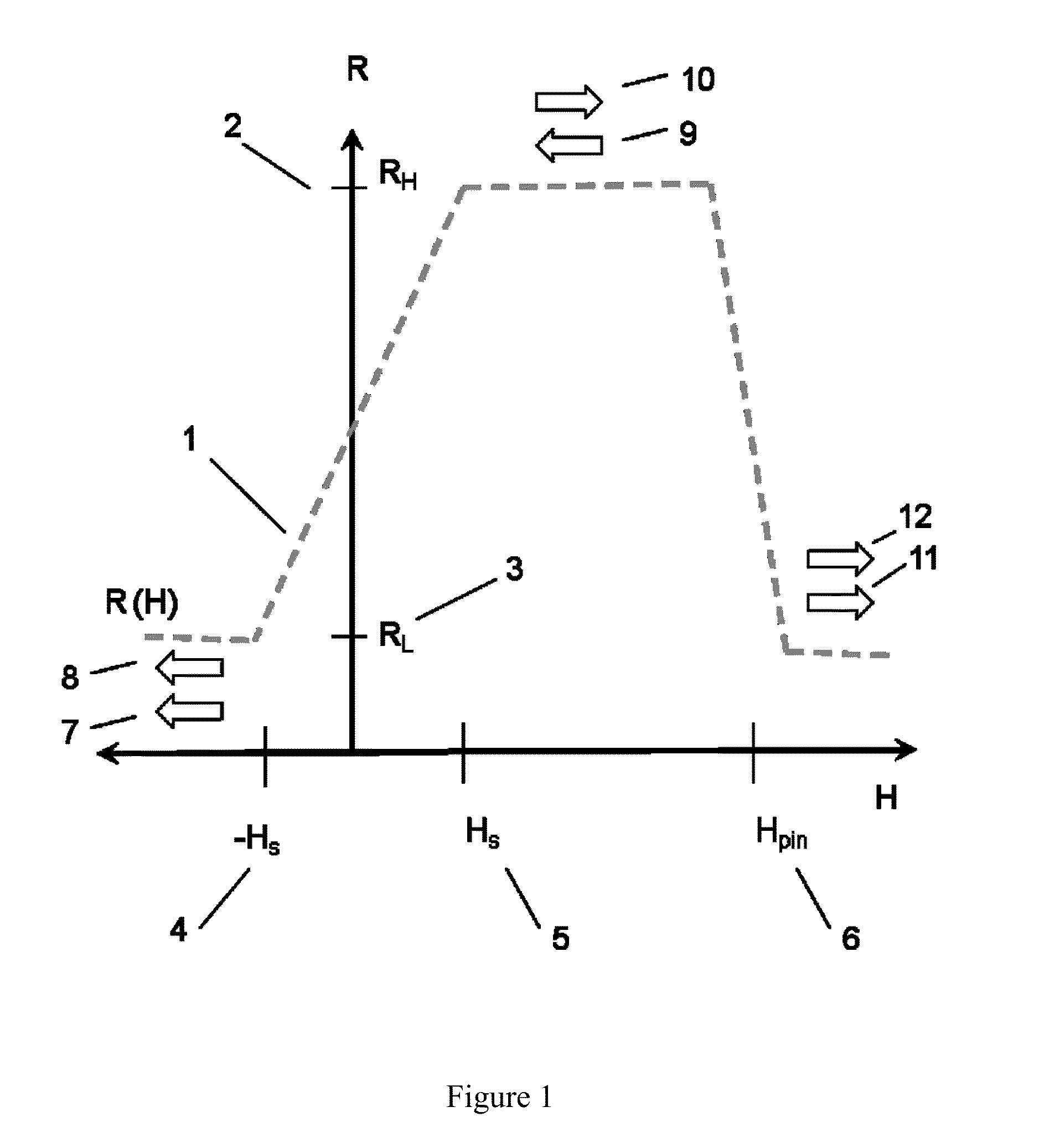

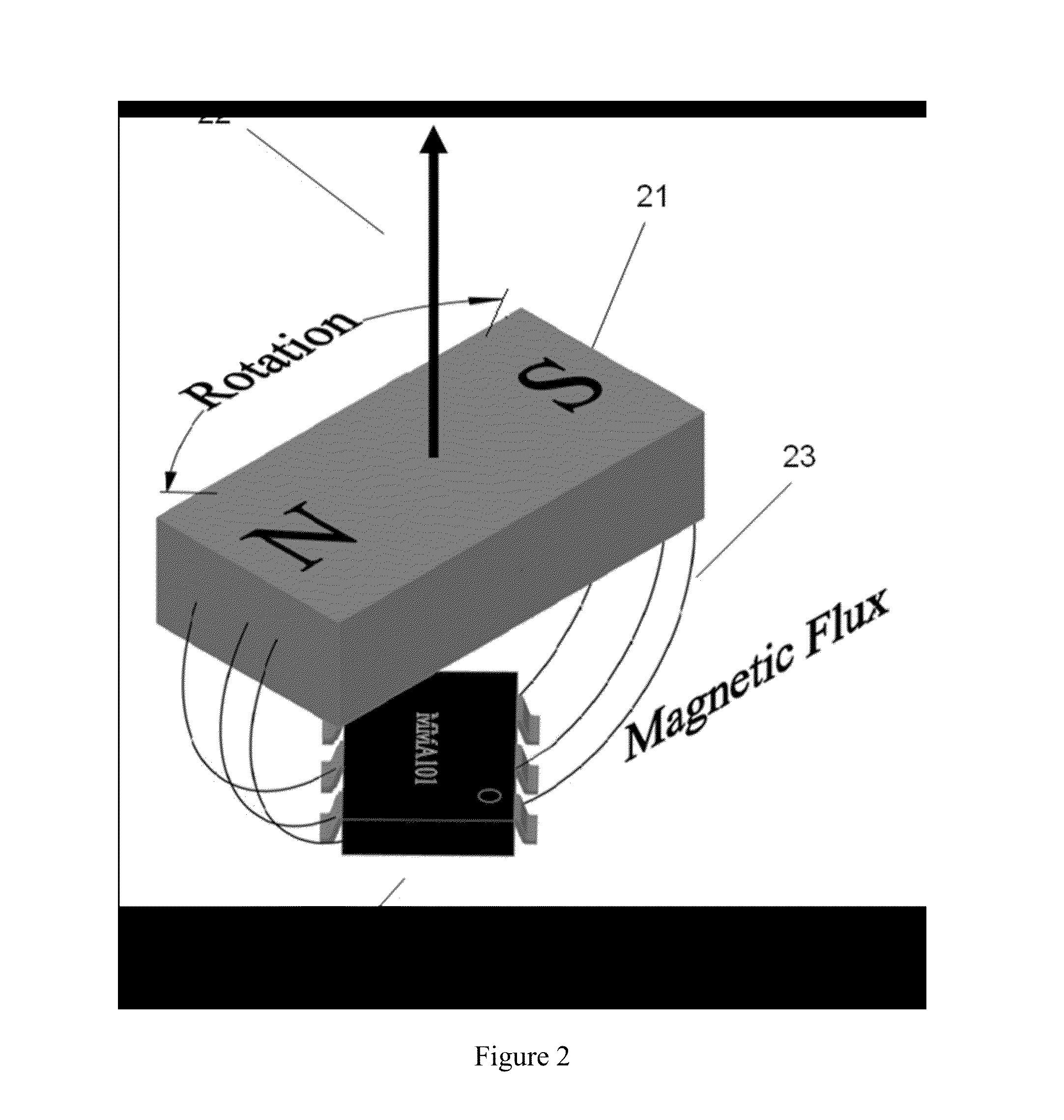

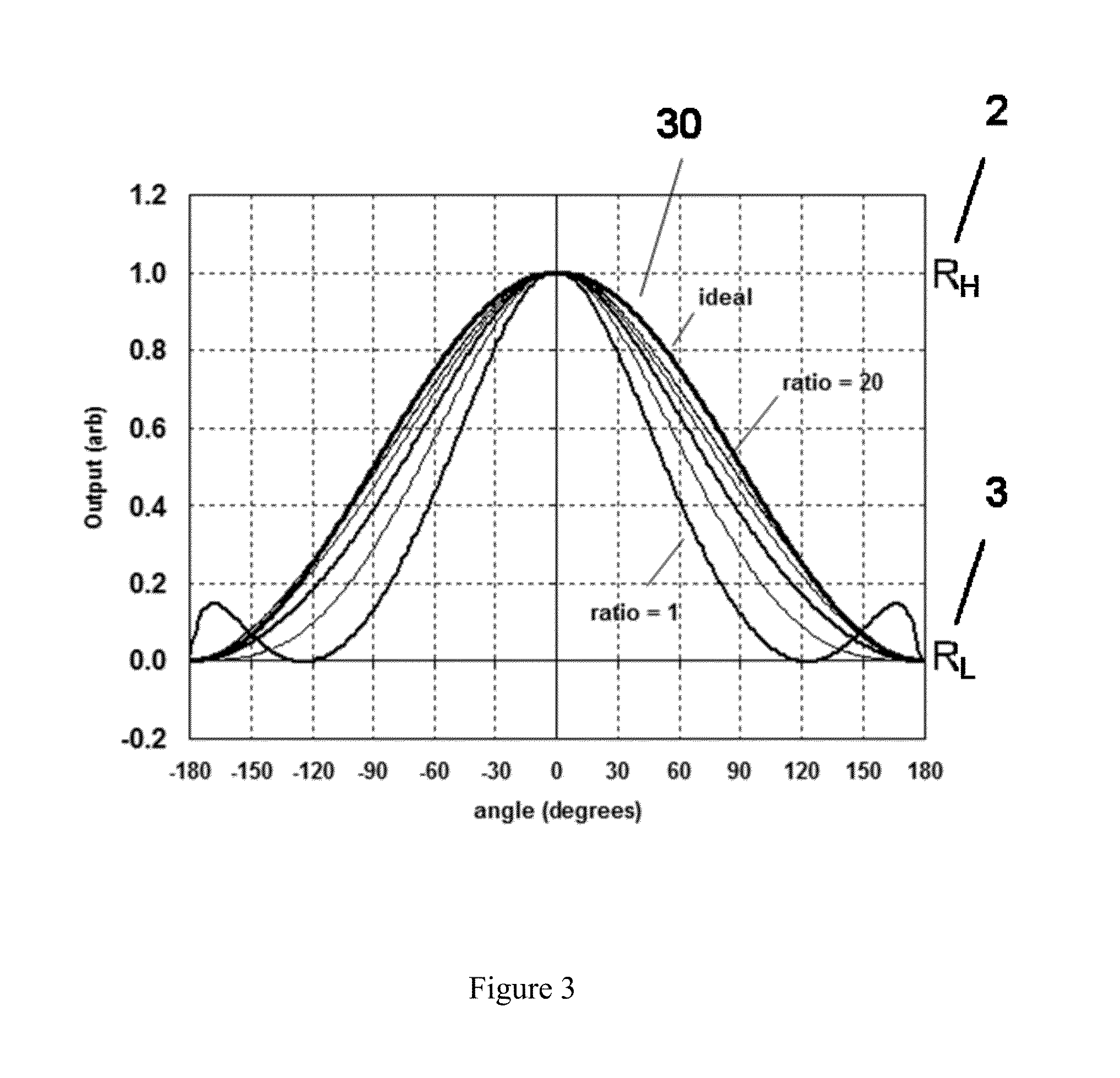

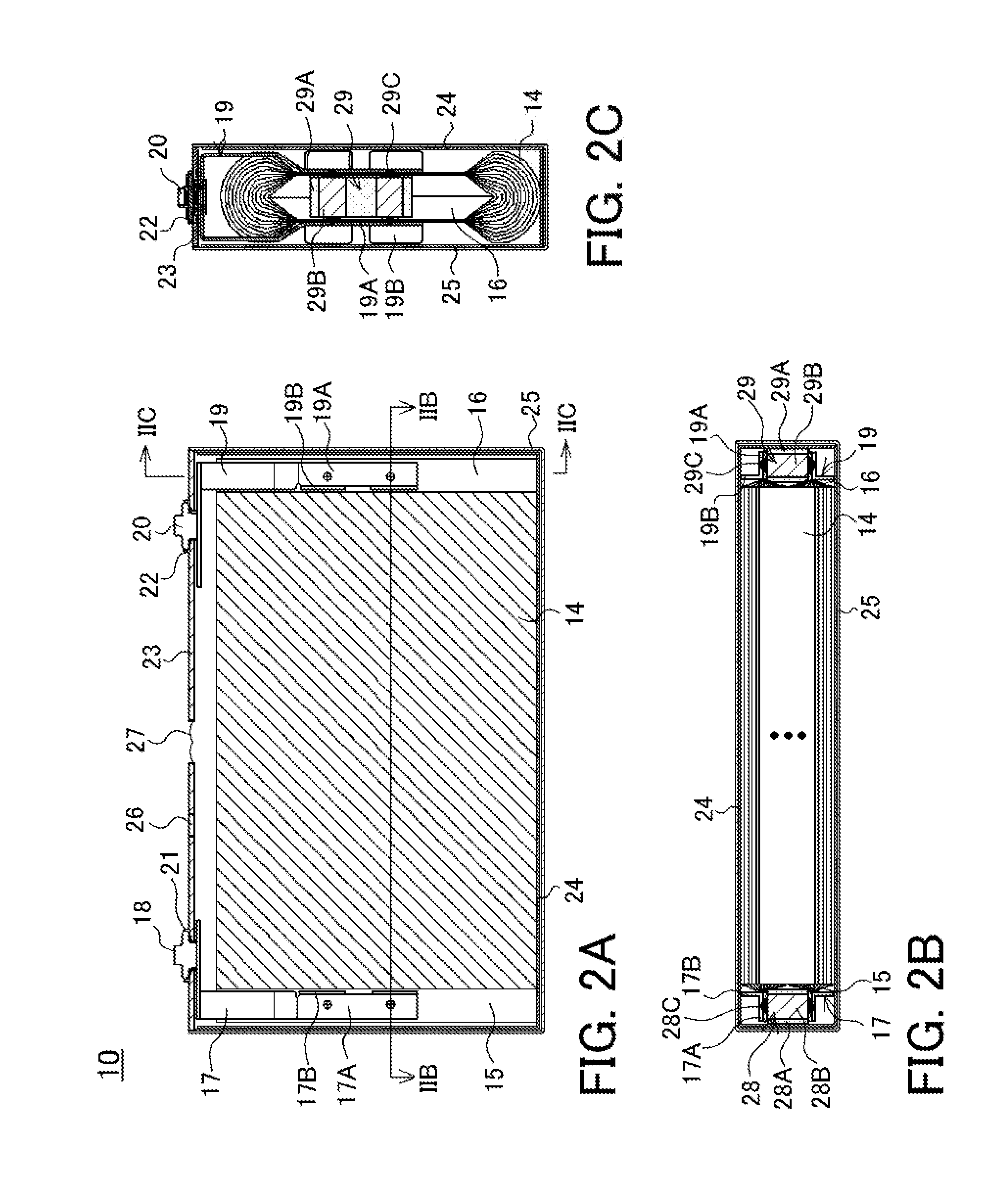

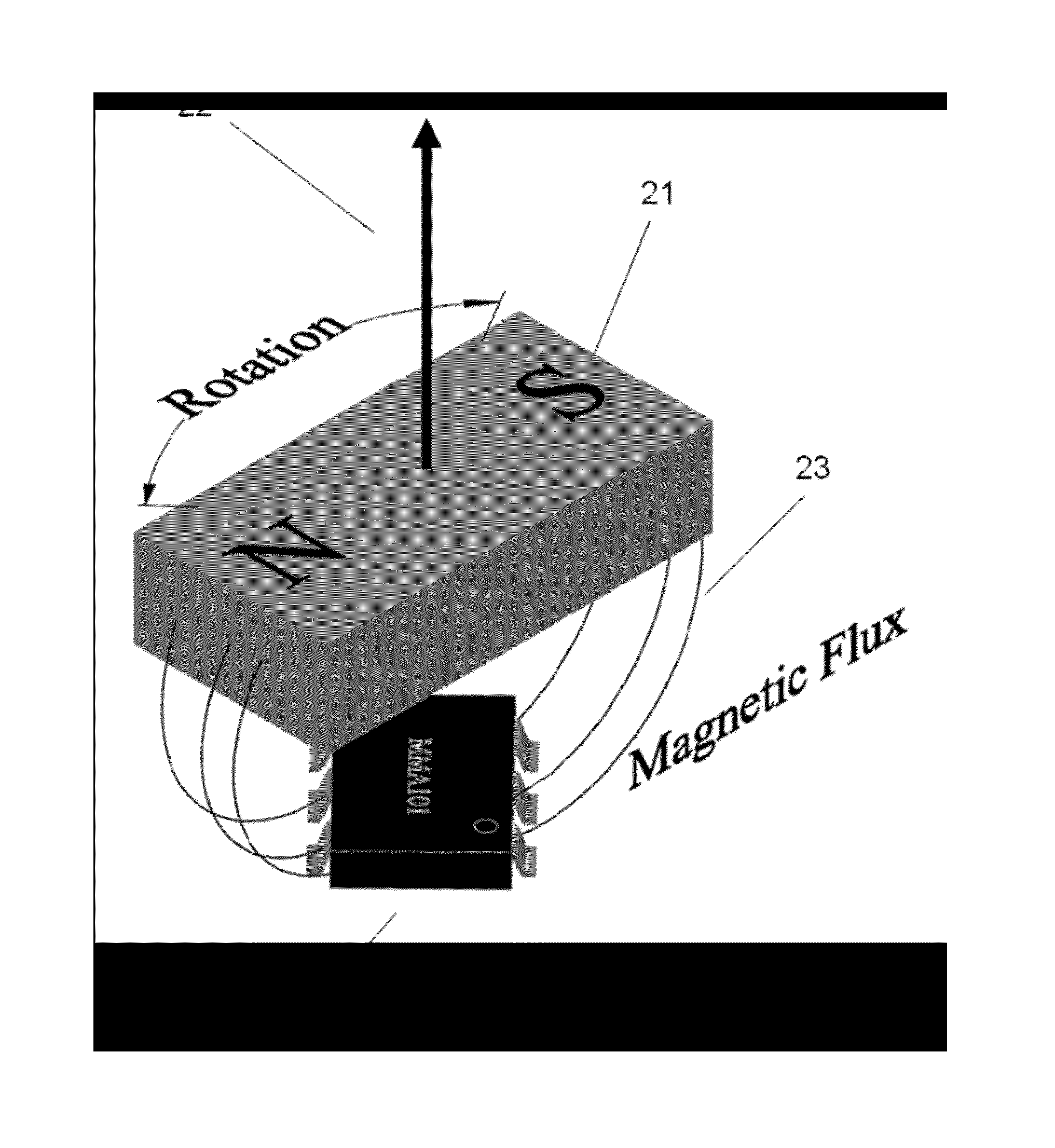

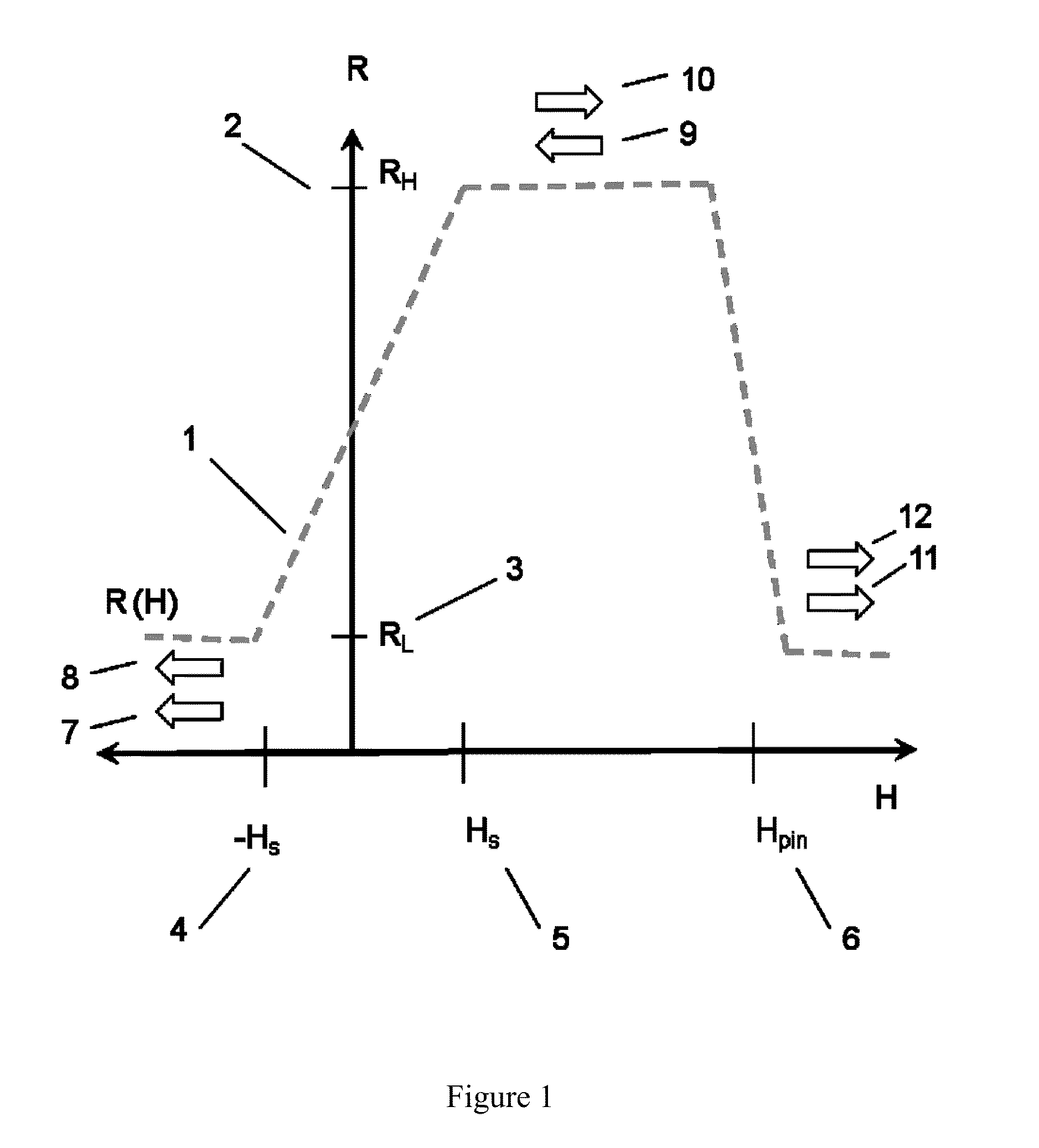

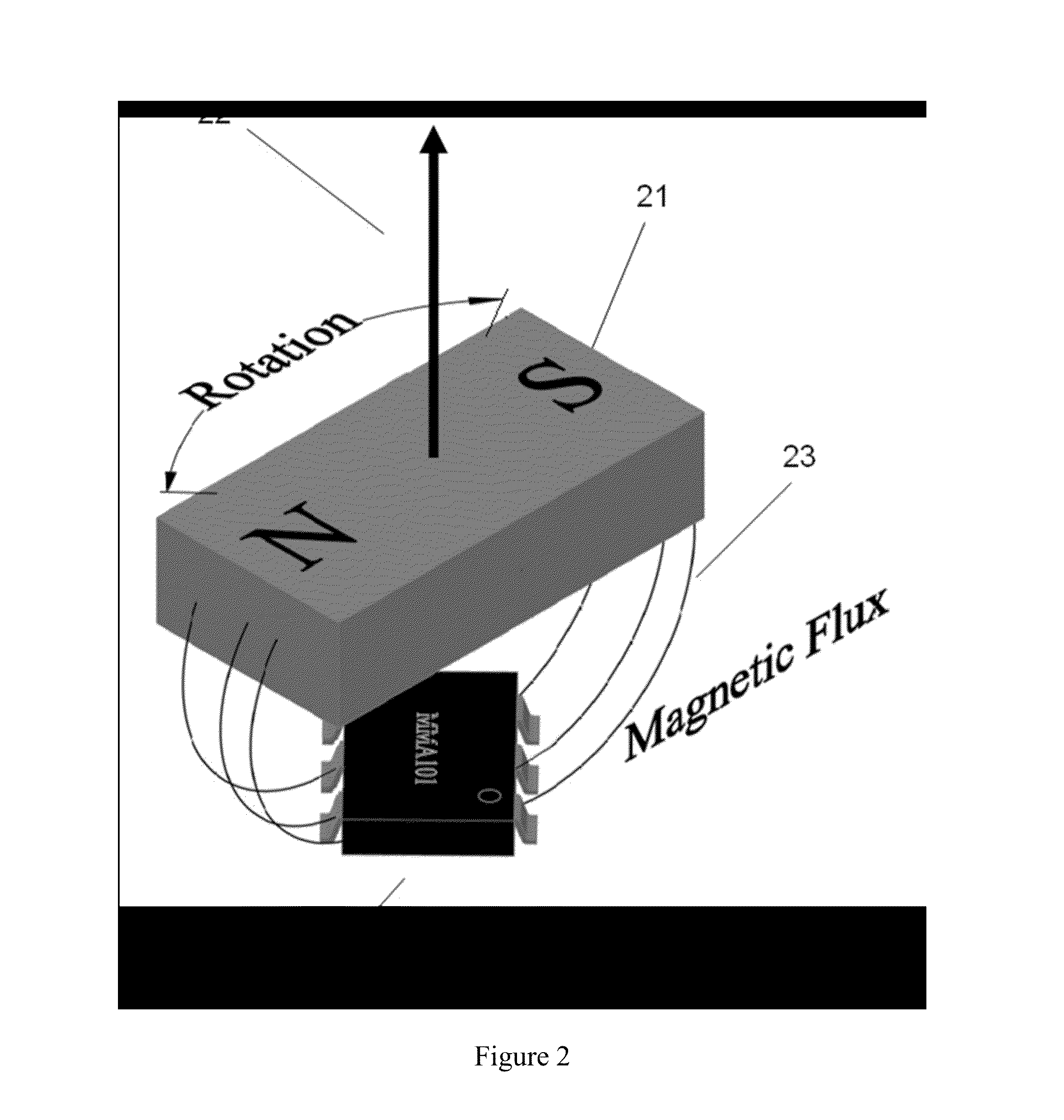

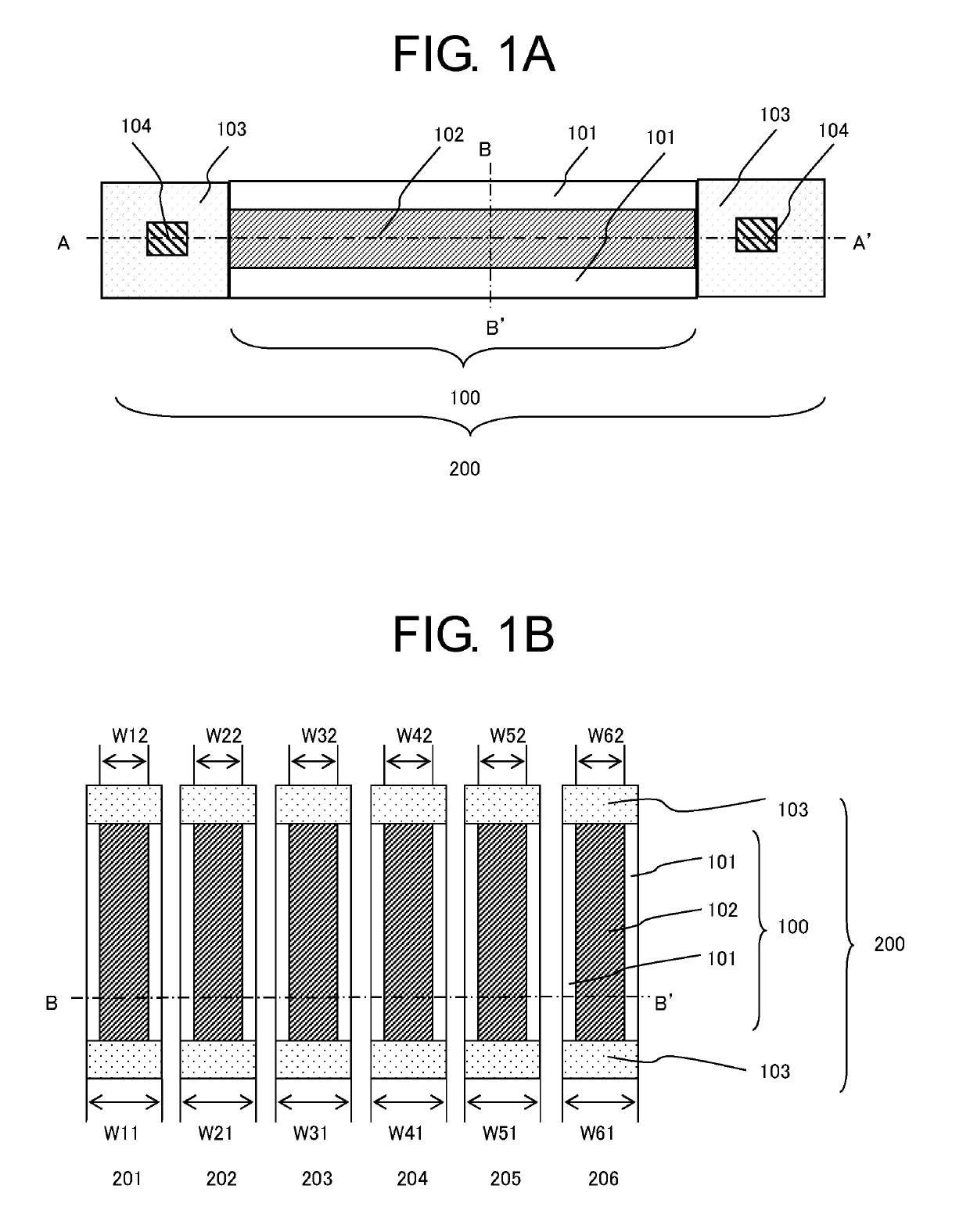

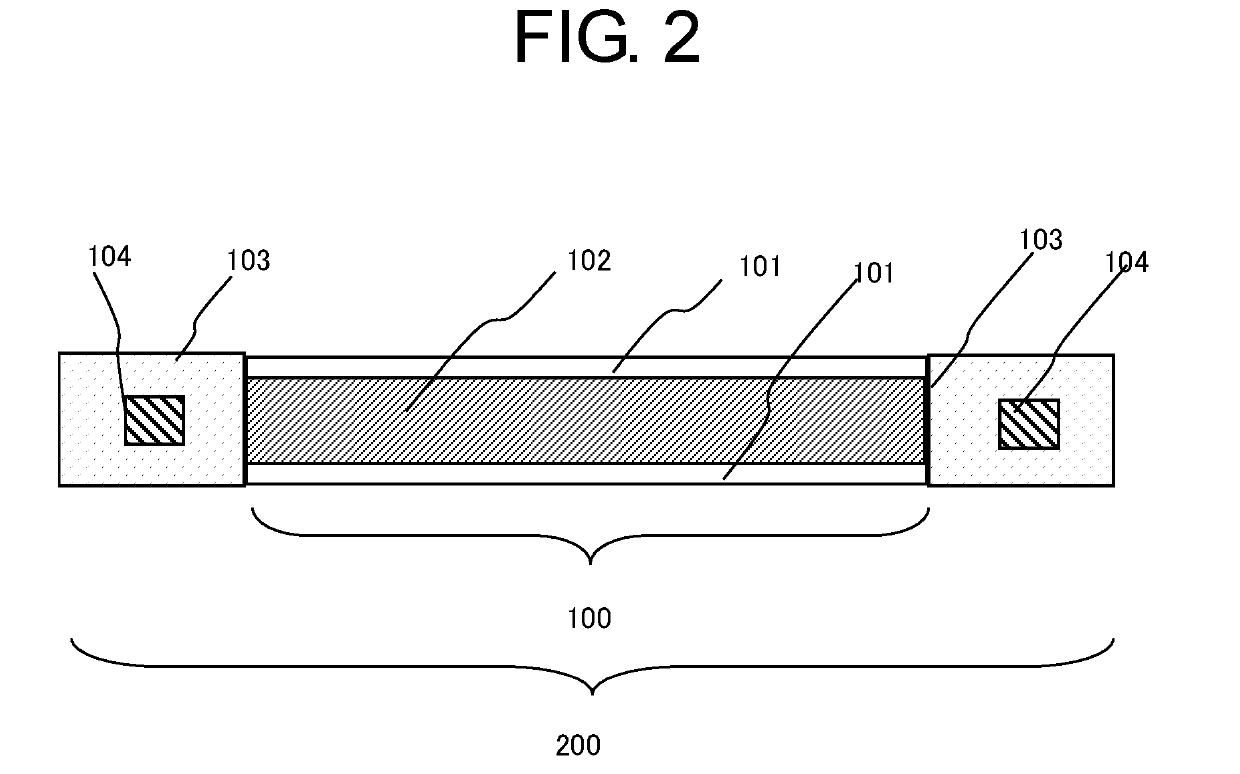

Full-Bridge Magnetoresistive Rotation Sensors and Mass Fabrication Method

ActiveUS20130335073A1Large possible output signalLow costNanomagnetismMagnetic-field-controlled resistorsFull bridgeMagnetic reluctance

A single package magnetoresistive angle sensor for use in measuring rotation angle of a magnet is disclosed. The magnetoresistive angle sensor comprises a pair of magnetoresistive sensor chips, wherein one of the chips is rotated by 180-degree rotation relative to the other. The magnetoresistive sensor chips are attached to a standard semiconductor package lead frame to form a single-axis push-pull full-bridge sensor. Each of the magnetoresistive sensor chips comprises a pair of magnetoresistance sensor arms. Each magnetoresistive sensor arm comprises one or more GMR or MTJ sensor elements. The GMR of MTR sensor elements utilize a pined layer. The element blocks of the magnetoresistive sensor electrically are interconnected and connected to the package leads by wirebonding. The magnetoresistive angle sensor can be packaged into various standard semiconductor package designs. Also, provided is a dual-axis push-pull full-bridge magnetoresistive angle sensor comprised of two pairs of magnetoresistive sensor chips.

Owner:MULTIDIMENSION TECH CO LTD

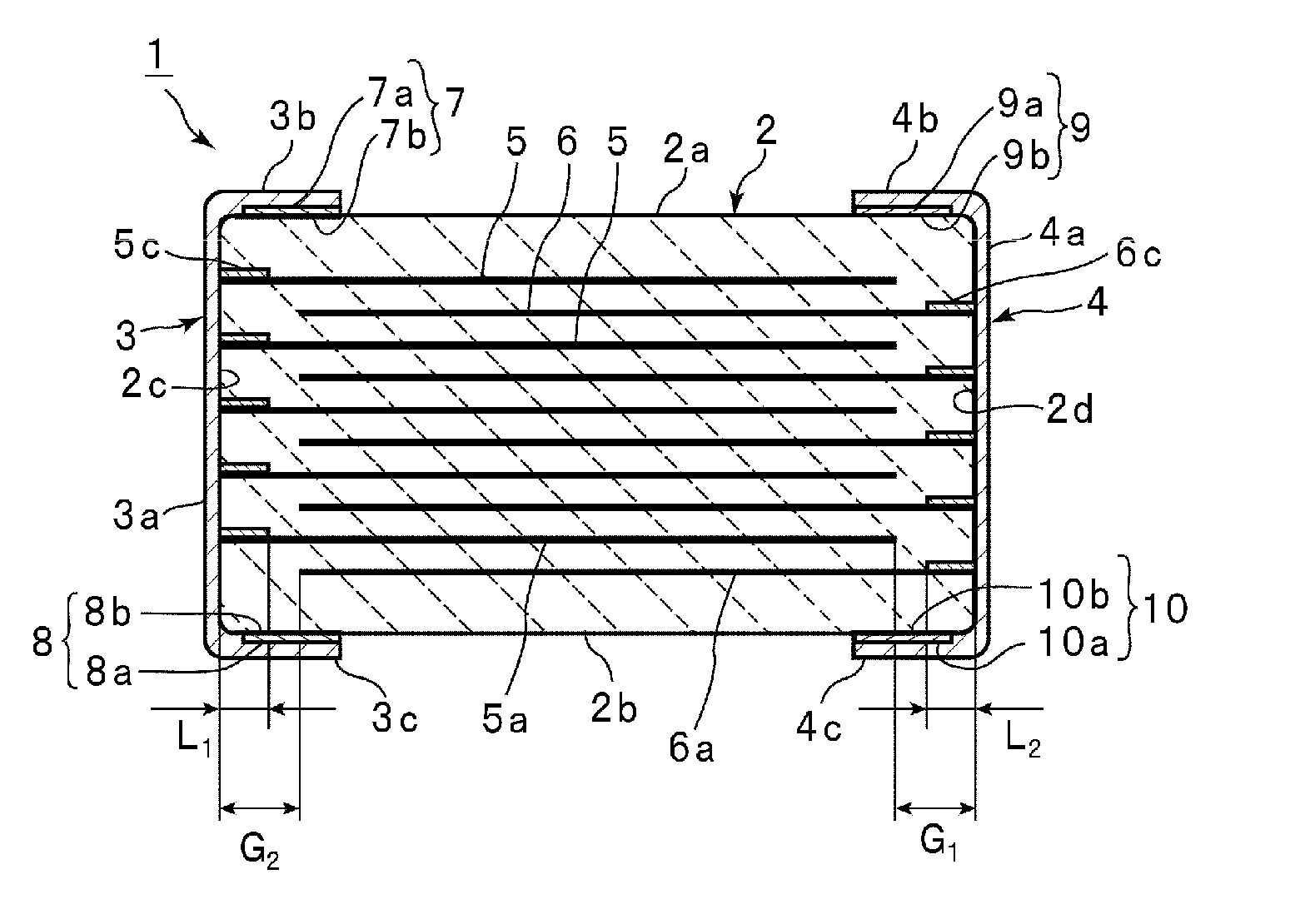

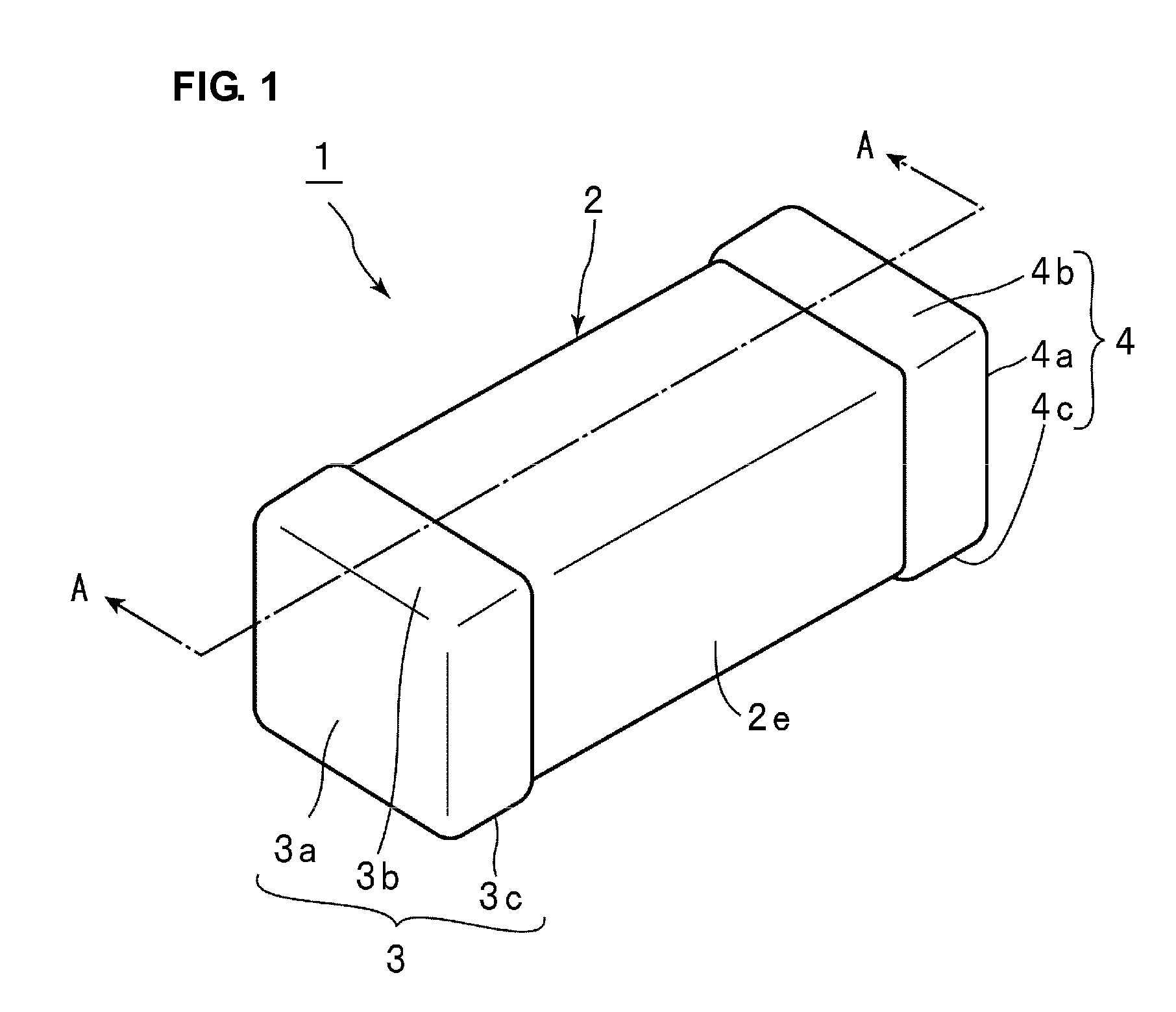

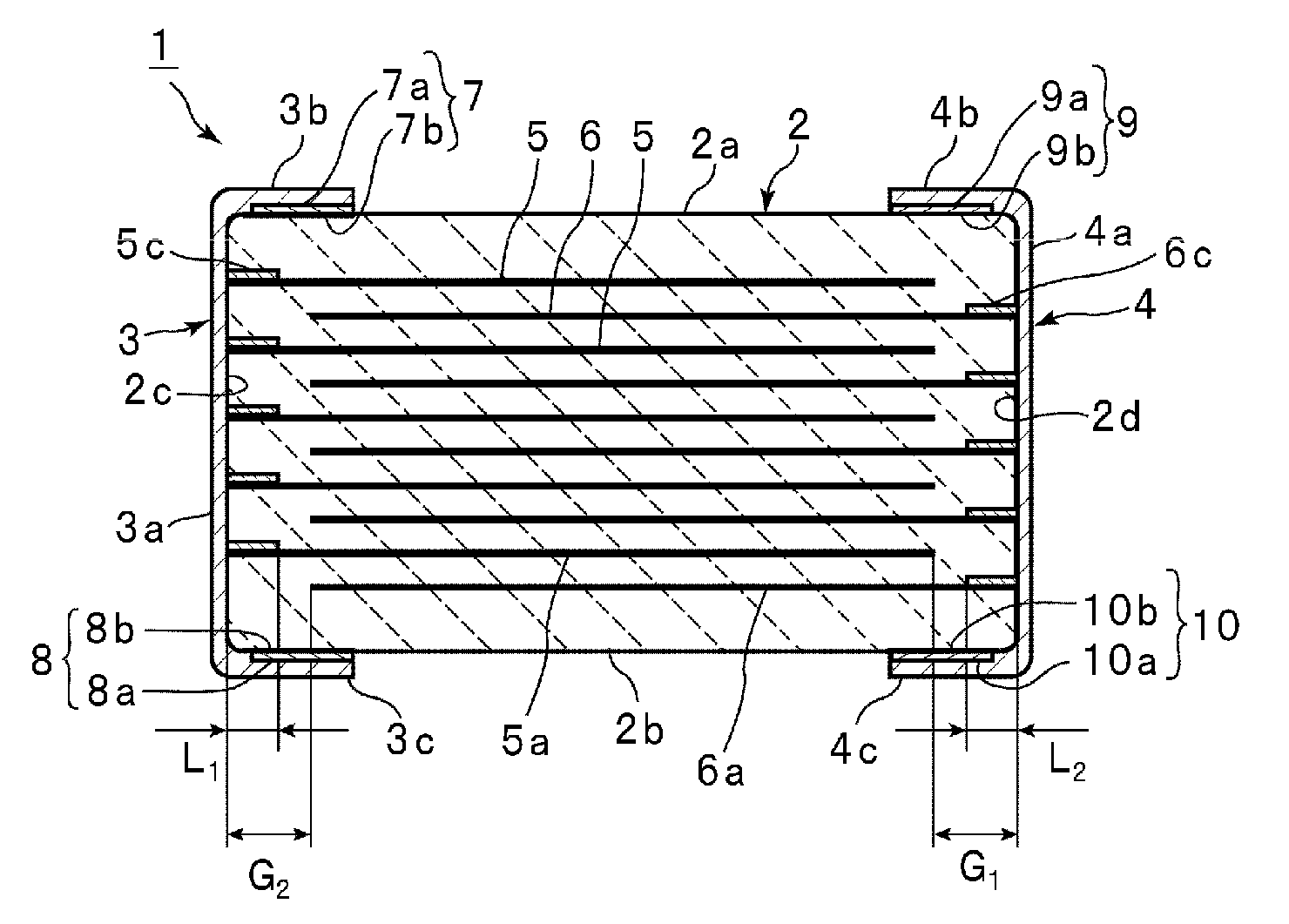

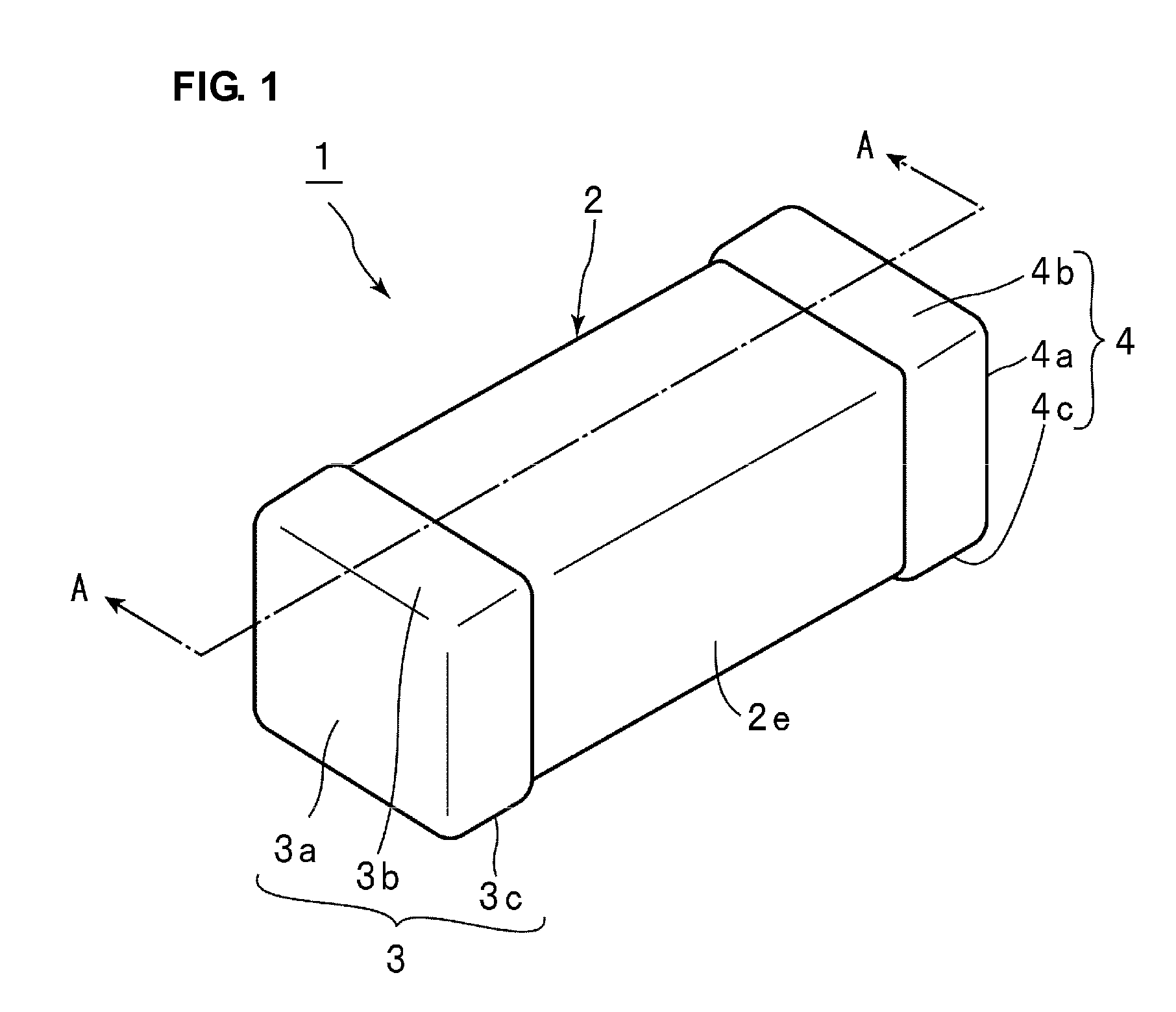

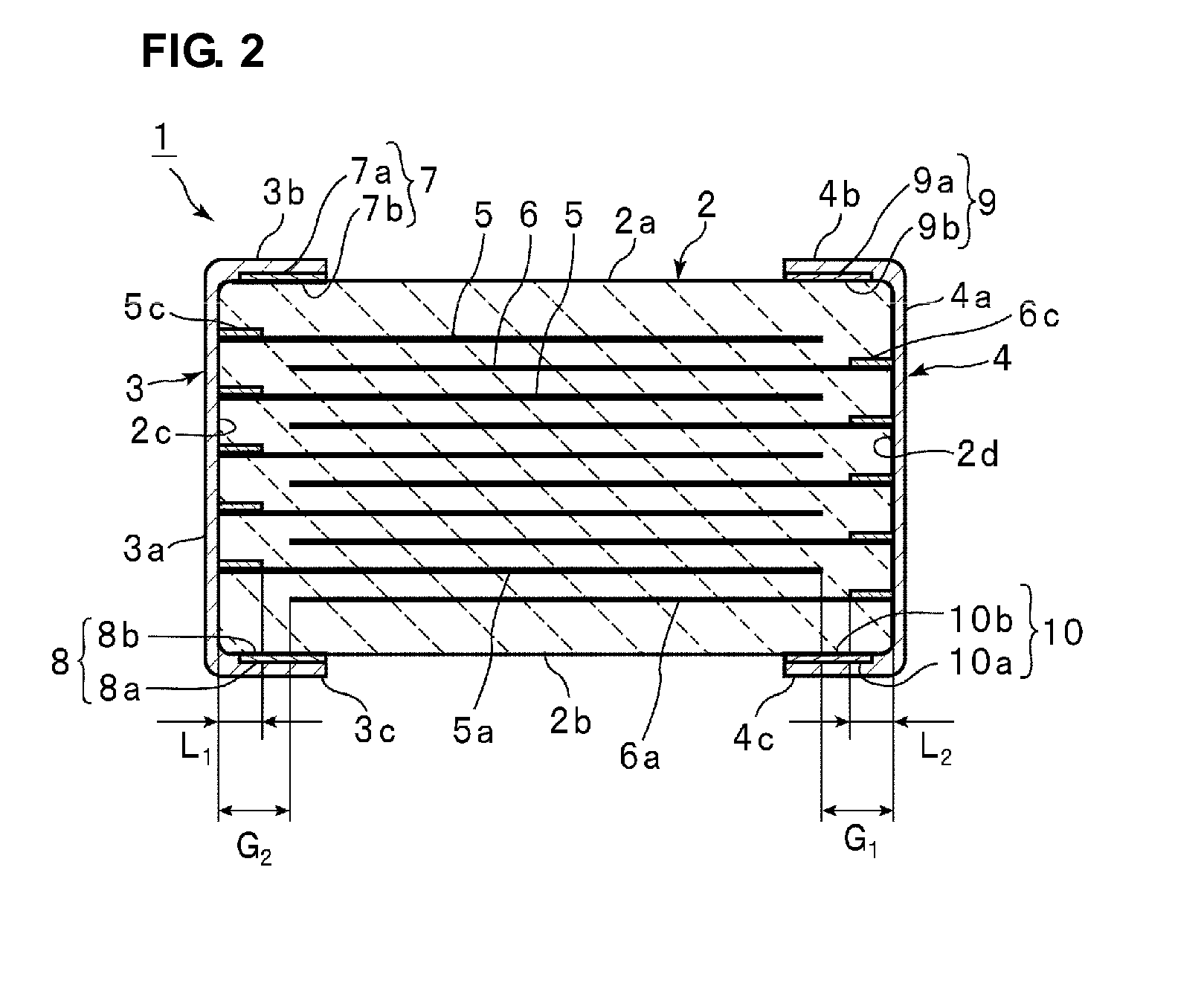

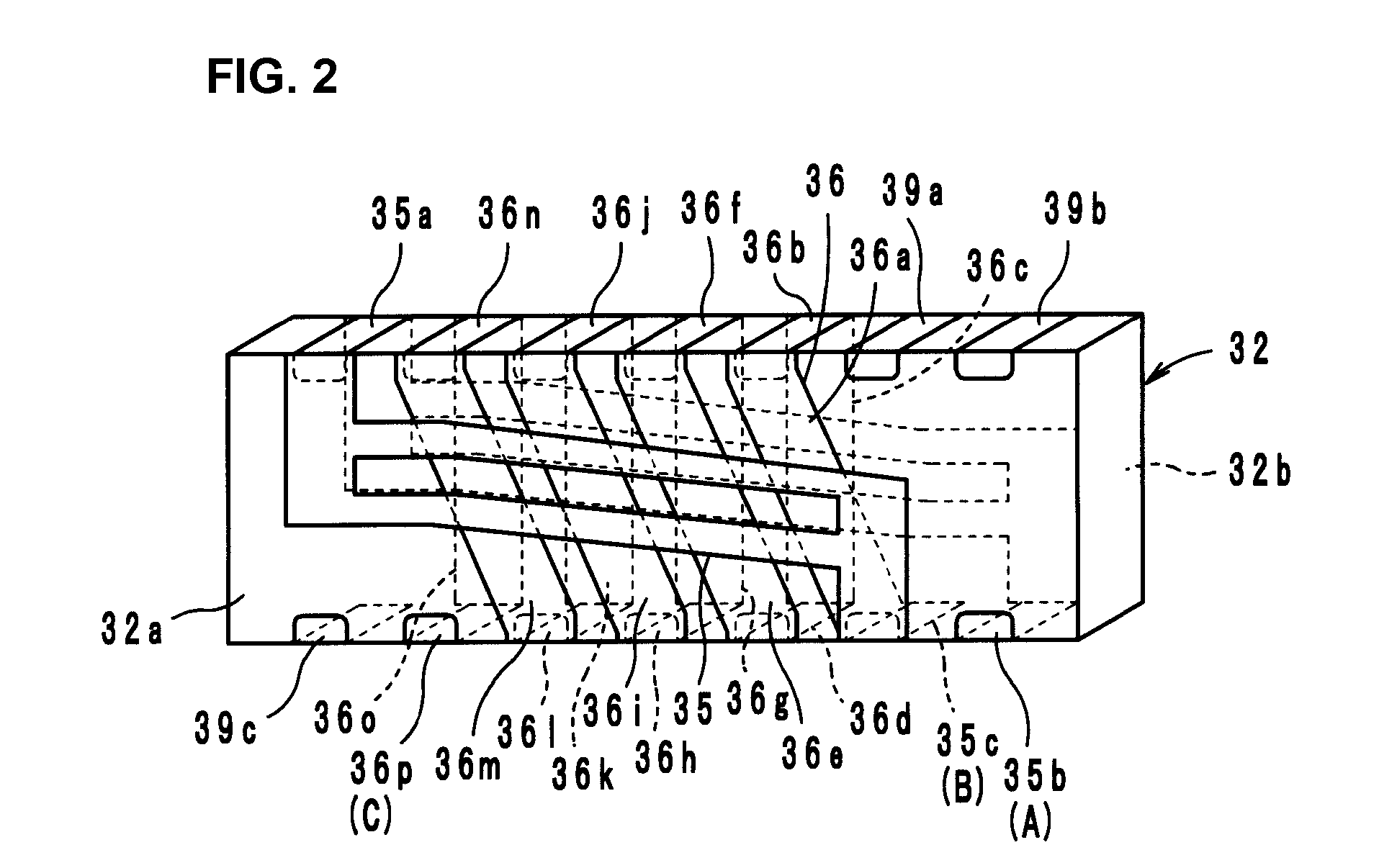

Laminated ceramic electronic component

ActiveUS20100008017A1Variation in propertyVariation in resistanceFixed capacitor electrodesStacked capacitorsMaterials scienceElectronic component

A laminated ceramic electronic component includes first internal electrodes and second internal electrodes that overlap each other through ceramic layers, each of the first and second internal electrodes having first and second effective portions, first and second connecting portions, and first and second extended portions whose film thickness is greater than that of the first and second connecting portions and which are exposed at the outer surface of a ceramic element assembly. When distances from side surfaces of the ceramic assembly on which first and second external electrodes are provided to the inner edges of the first and second extended portions are defined as L1 and L2, respectively, and a distance between side surfaces and the end of the second internal electrode or the end of the first internal electrode is defined as G2 or G1, G2>L1 and G1>L2 are satisfied.

Owner:MURATA MFG CO LTD

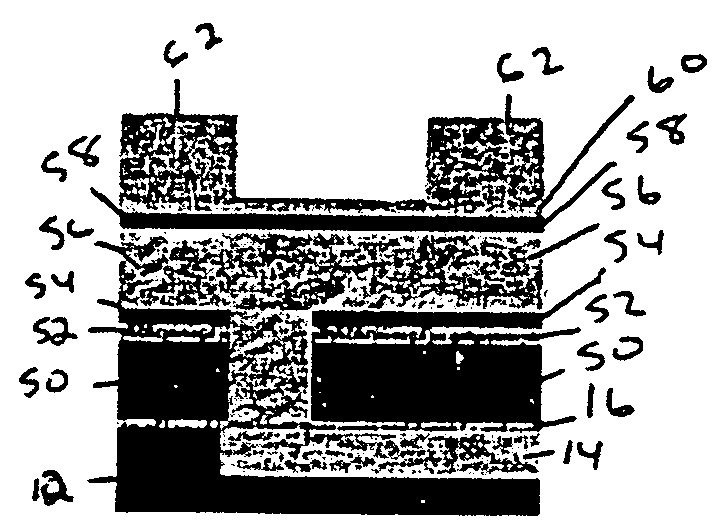

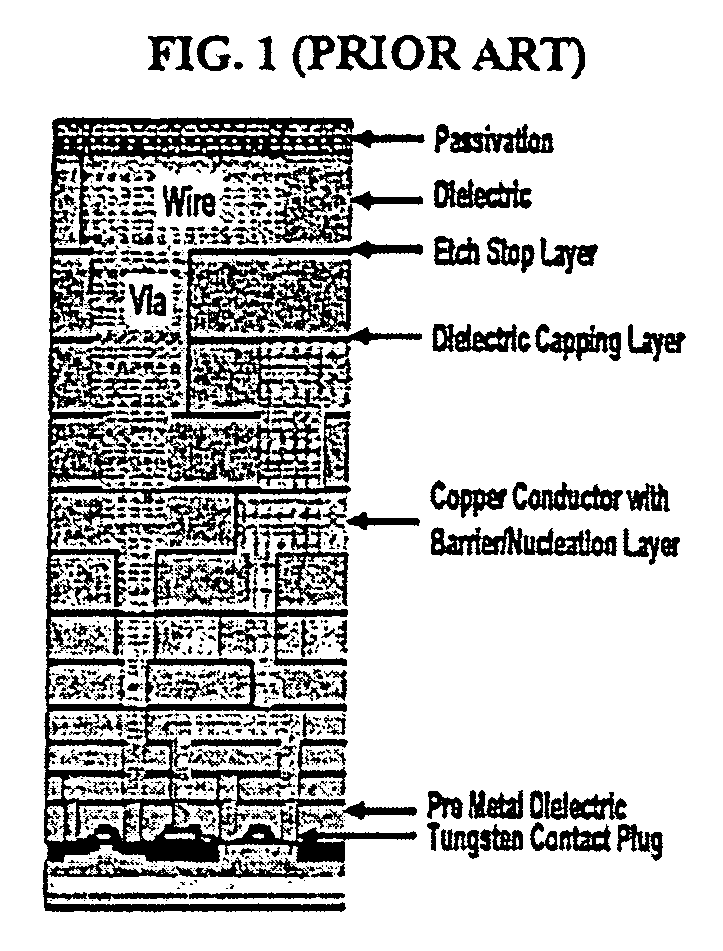

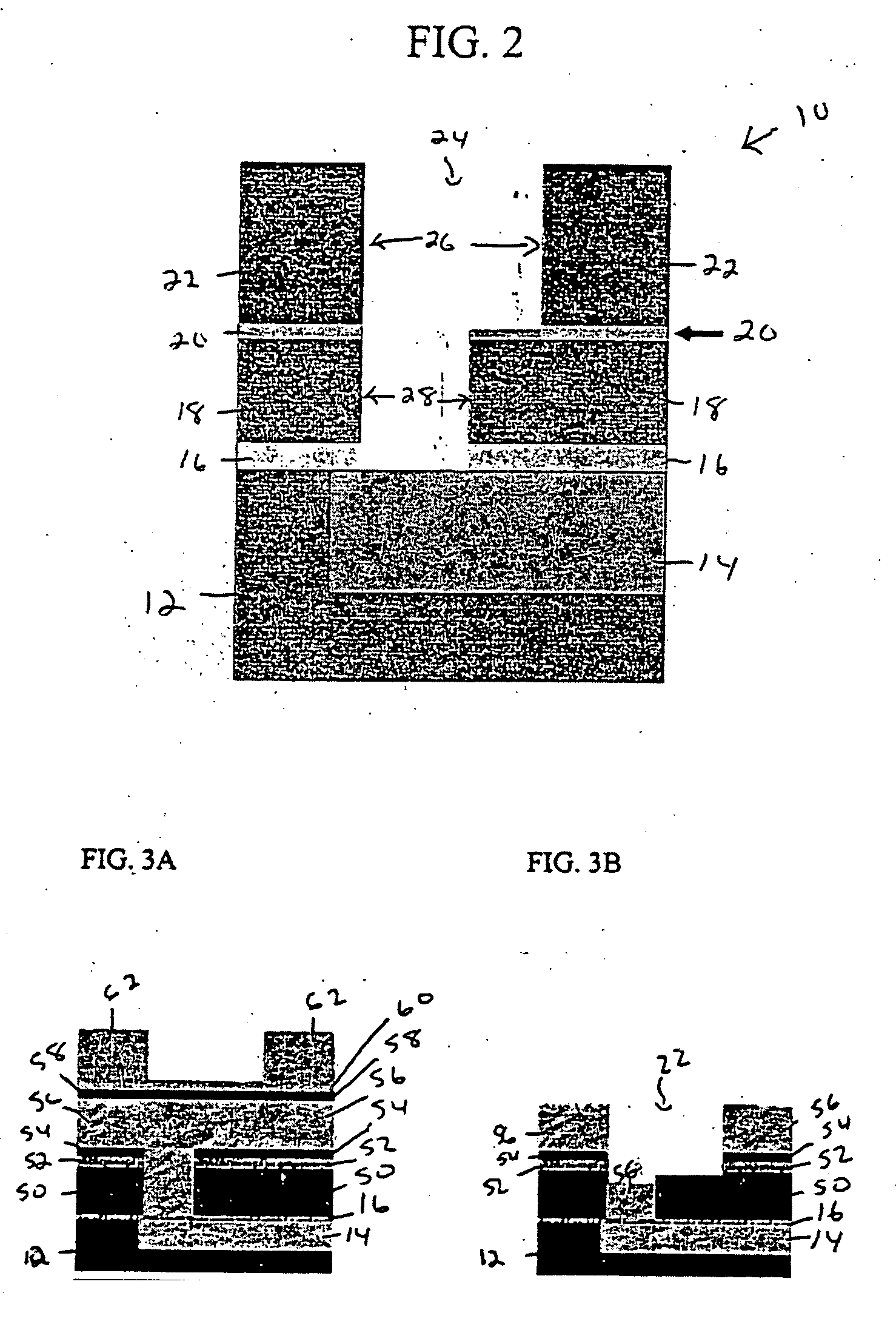

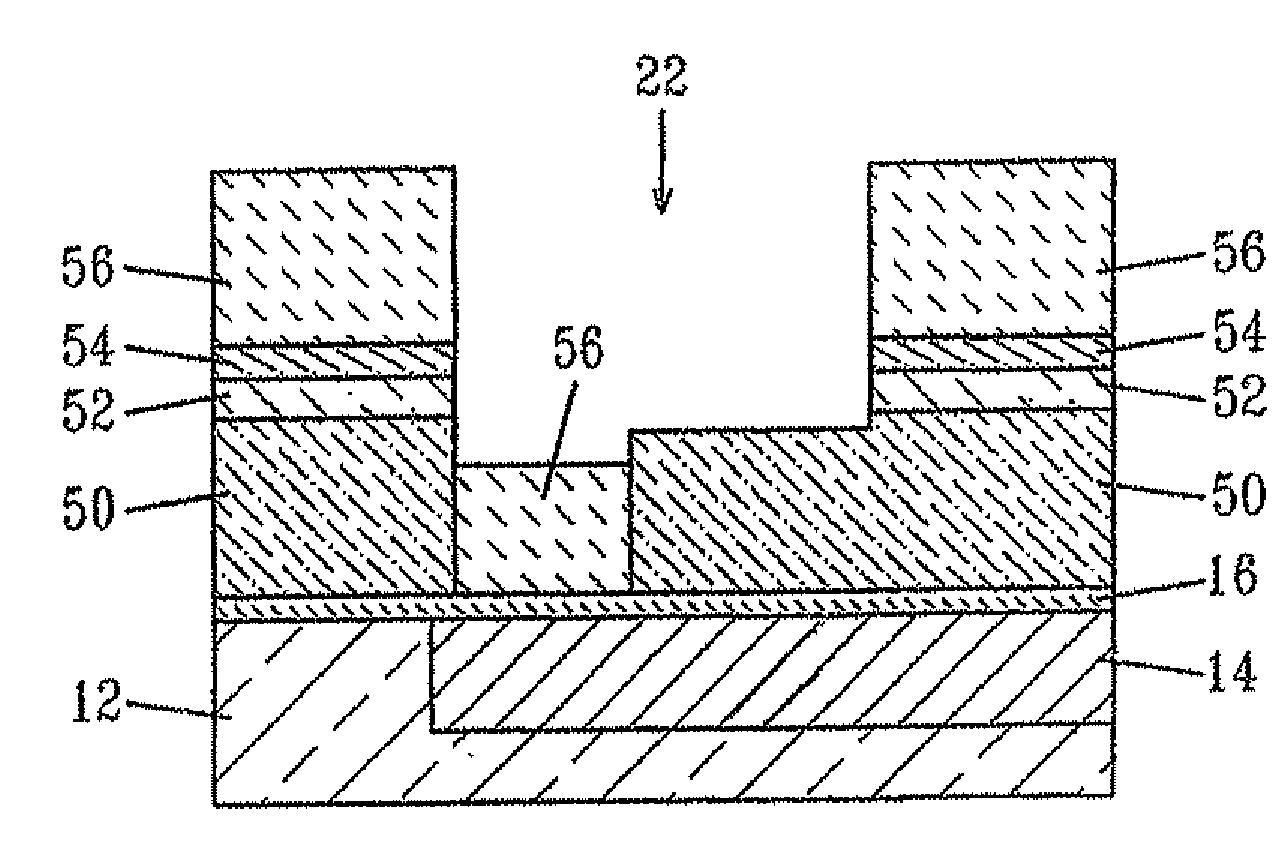

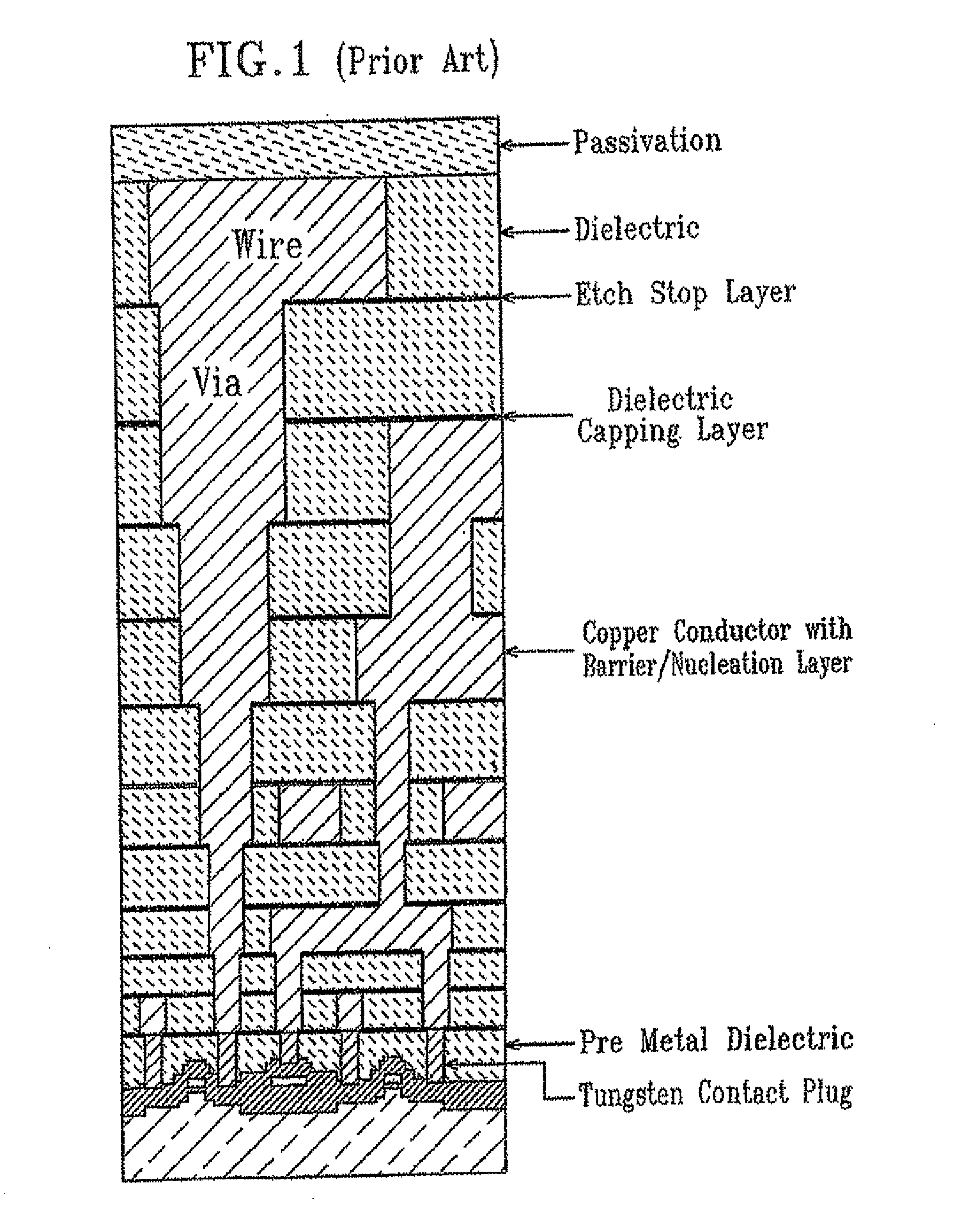

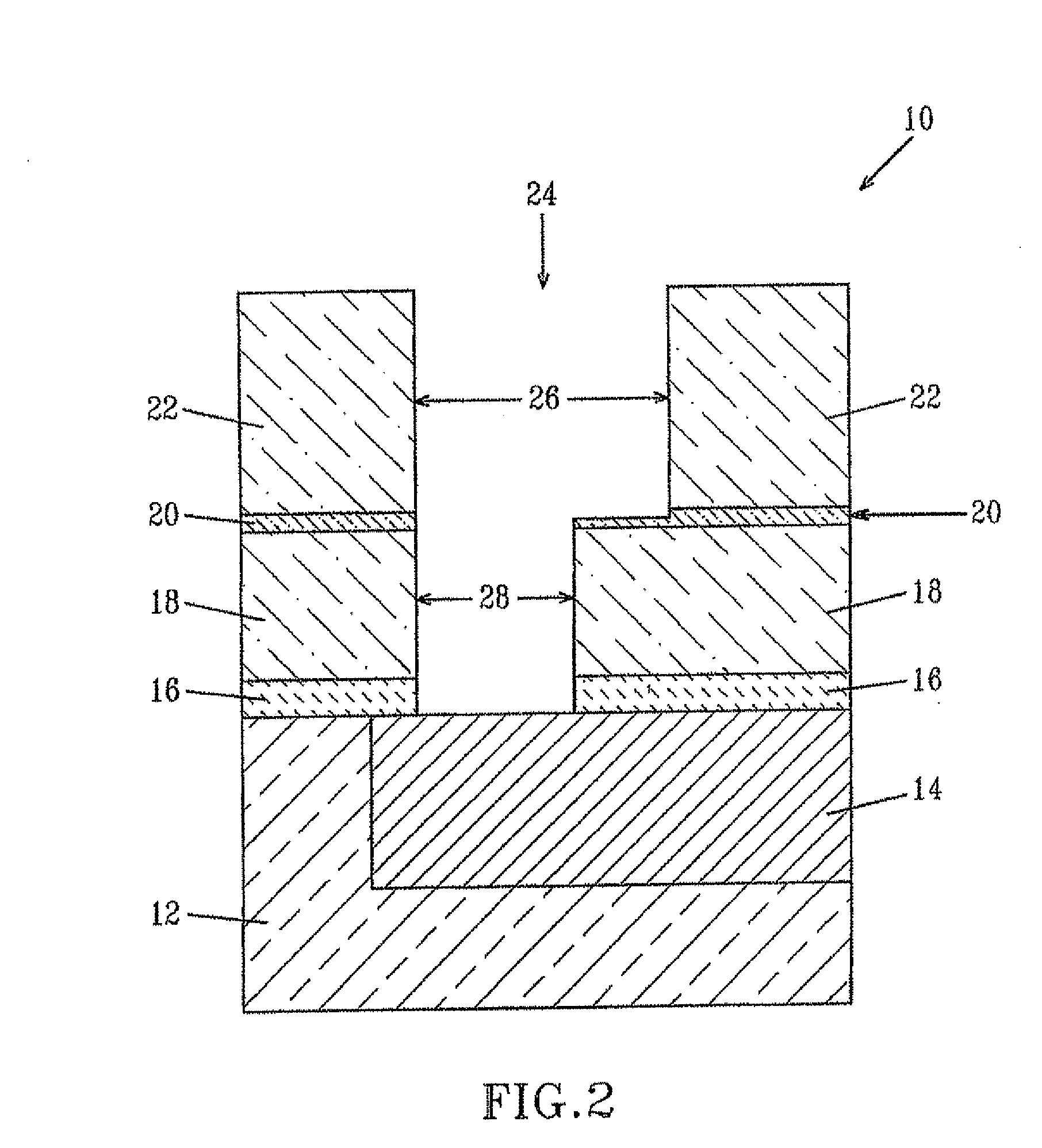

Use of a porous dielectric material as an etch stop layer for non-porous dielectric films

ActiveUS20050258542A1Minimized line height variationMinimal line resistance variationSemiconductor/solid-state device detailsSolid-state devicesEtchingGas phase

Interconnect structures possessing a non-porous (dense) low-k organosilicate glass (OSG) film utilizing a porous low-k OSG film as an etch stop layer or a porous low-k OSG film using a non-porous OSG film as a hardmask for use in semiconductor devices are provided herein. The novel interconnect structures are capable of delivering improved device performance, functionality and reliability owing to the reduced effective dielectric constant of the stack compared with that of those conventionally employed and also because of the relatively uniform line heights made feasible by these unique and seemingly counterintuitive features. The present invention also provides a fluorocarbon-based dual damascene etch process that achieves selective etching of a dense low-k OSG films relative to that of a porous low-k OSG film owing to the tunability of the gas-phase fluorine:carbon ratio (gas dissociation) and ion current below a critical threshold and given the larger carbon content of the porous film relative to that of the dense film.

Owner:TAIWAN SEMICON MFG CO LTD

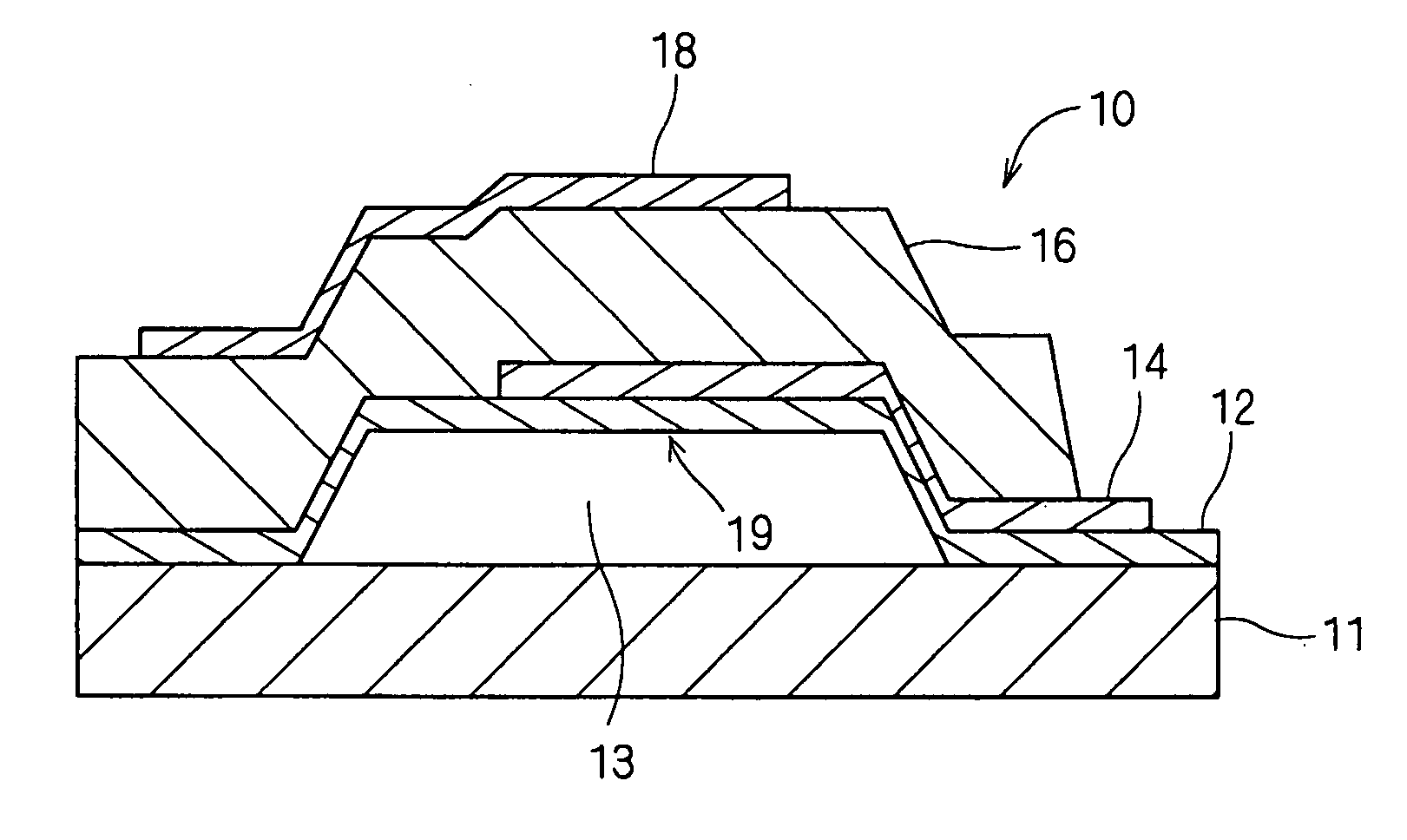

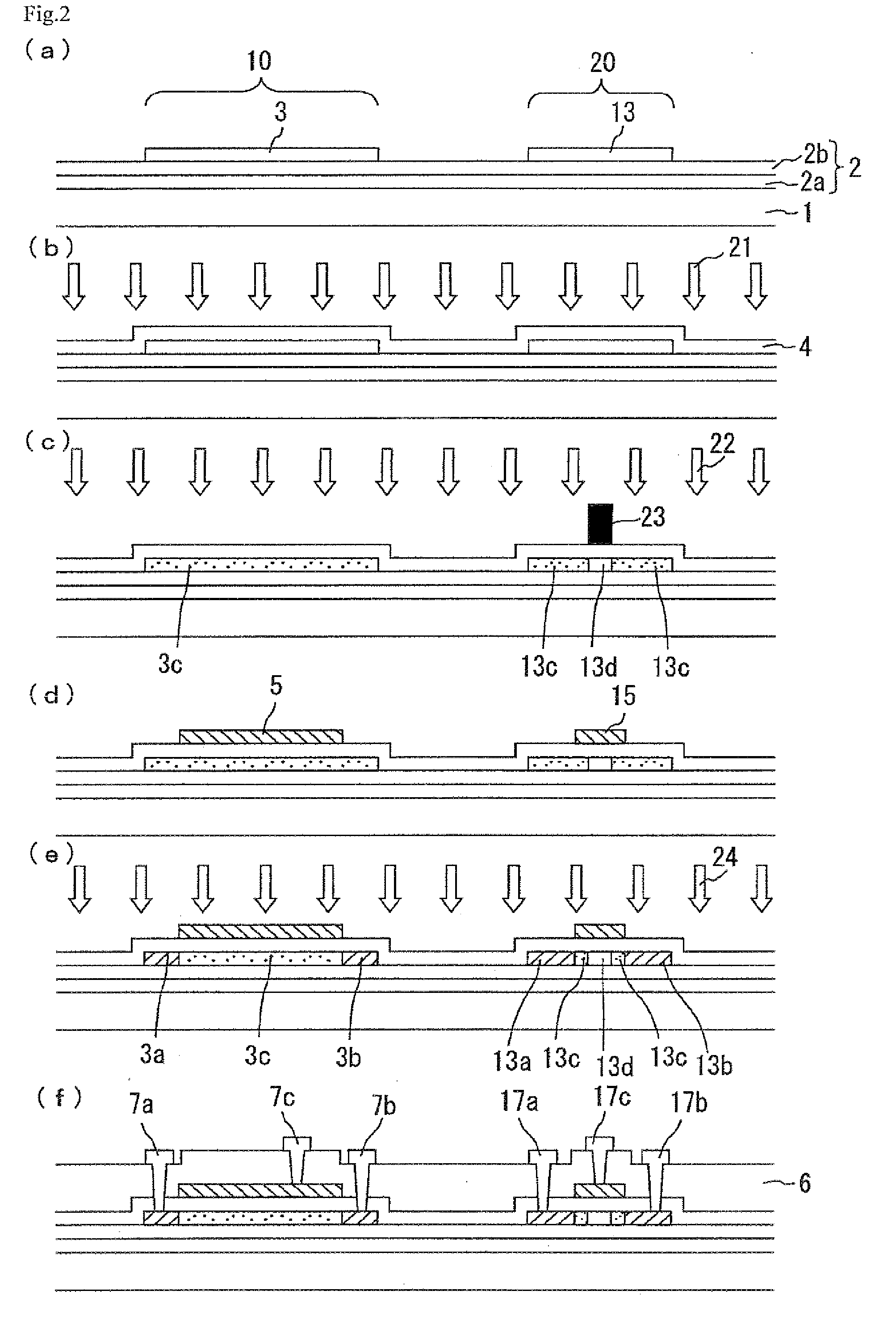

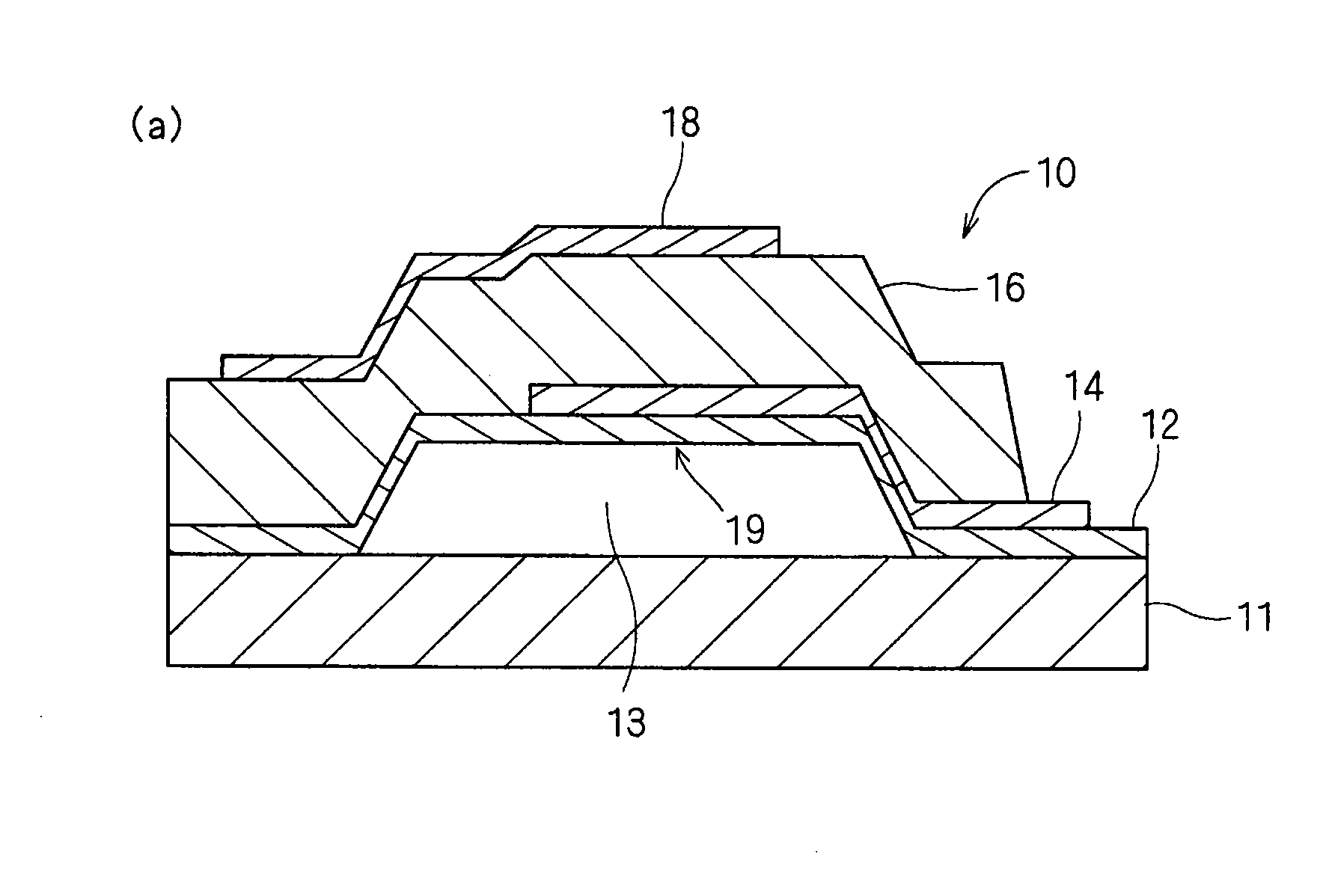

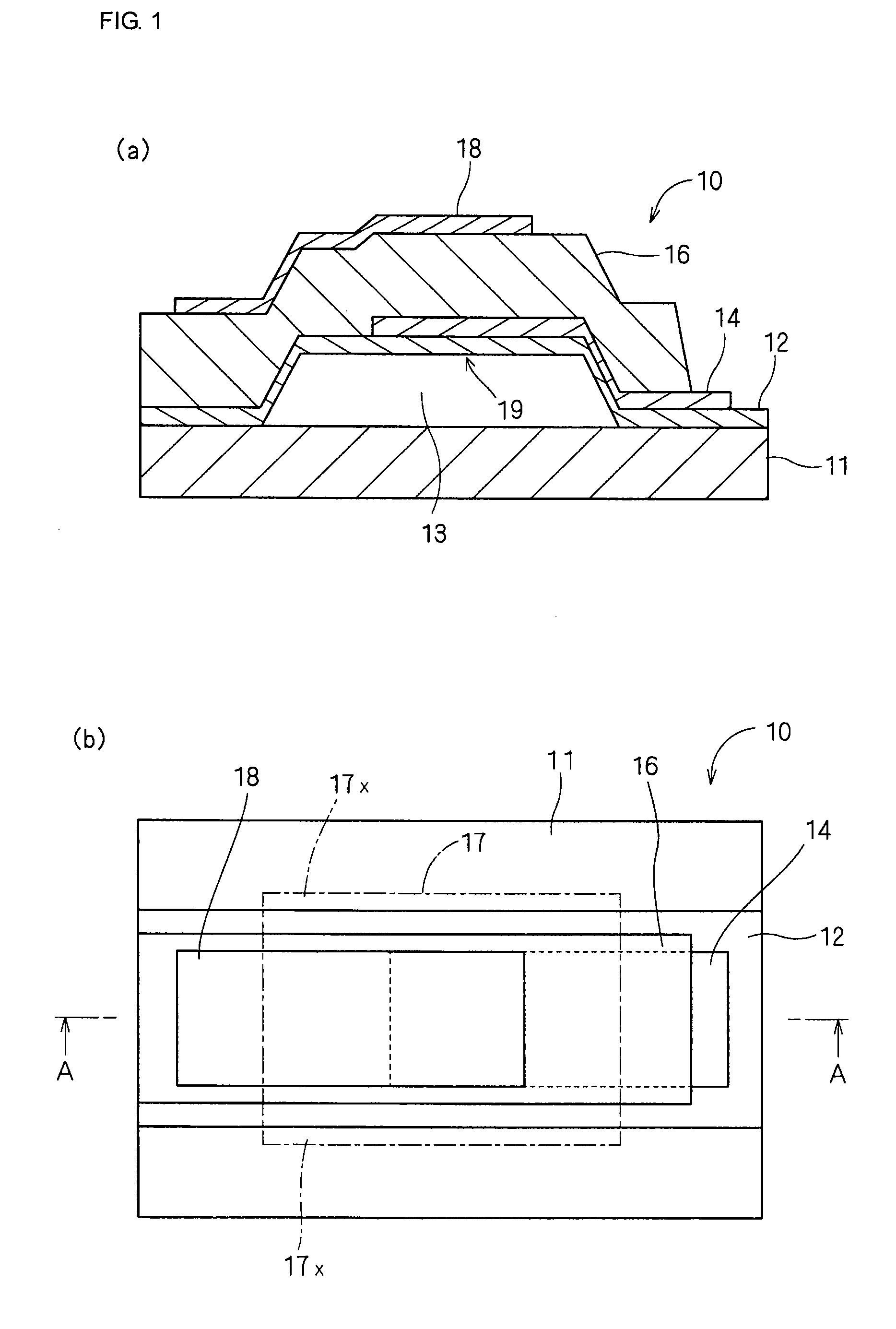

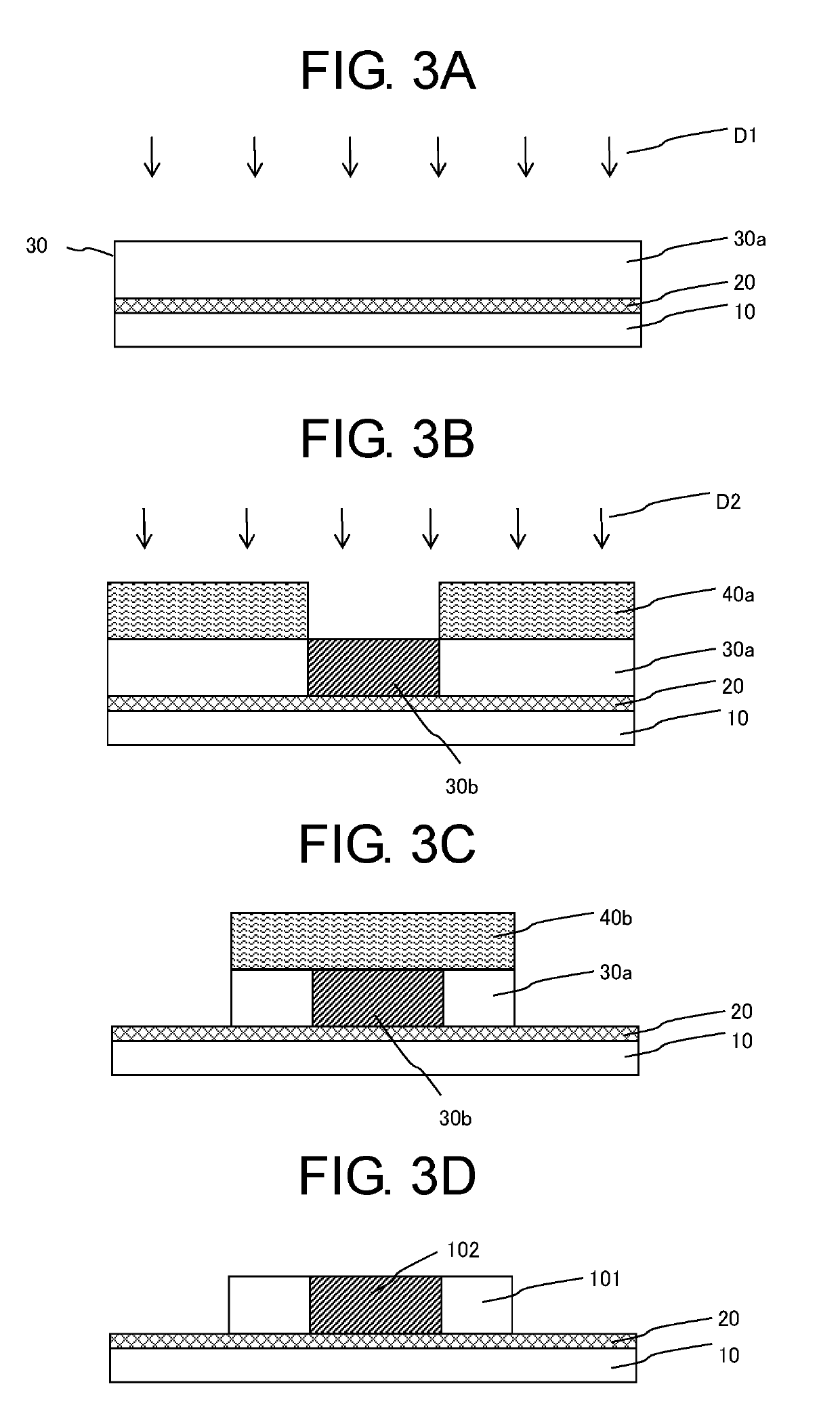

Piezoelectric thin film resonator and manufacturing method thereof

InactiveUS20070152540A1Improve resonance characteristicsSuperior resistance against electric powerPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksPiezoelectric thin filmsResonator

A piezoelectric thin film resonator which can reduce variations in resonant frequency and resonant resistance by uniformly planarizing a structural film, and a method of manufacturing the piezoelectric thin film resonator. The piezoelectric thin film resonator has a substrate having at least one flat major surface; a dielectric film having two support portions supported by the major surface of the substrate and a floating portion which is connected to the support portions and which is disposed over the major surface of the substrate with an airspace layer provided therebetween; and a vibration portion which is formed of a pair of electrodes and a piezoelectric thin film provided therebetween and which is provided on the floating portion of the dielectric film at a side opposite to the airspace layer. A surface of the dielectric film at a side opposite to the substrate is planarized by a plasma treatment using an inert gas or a gas containing an element forming a dielectric film.

Owner:MURATA MFG CO LTD

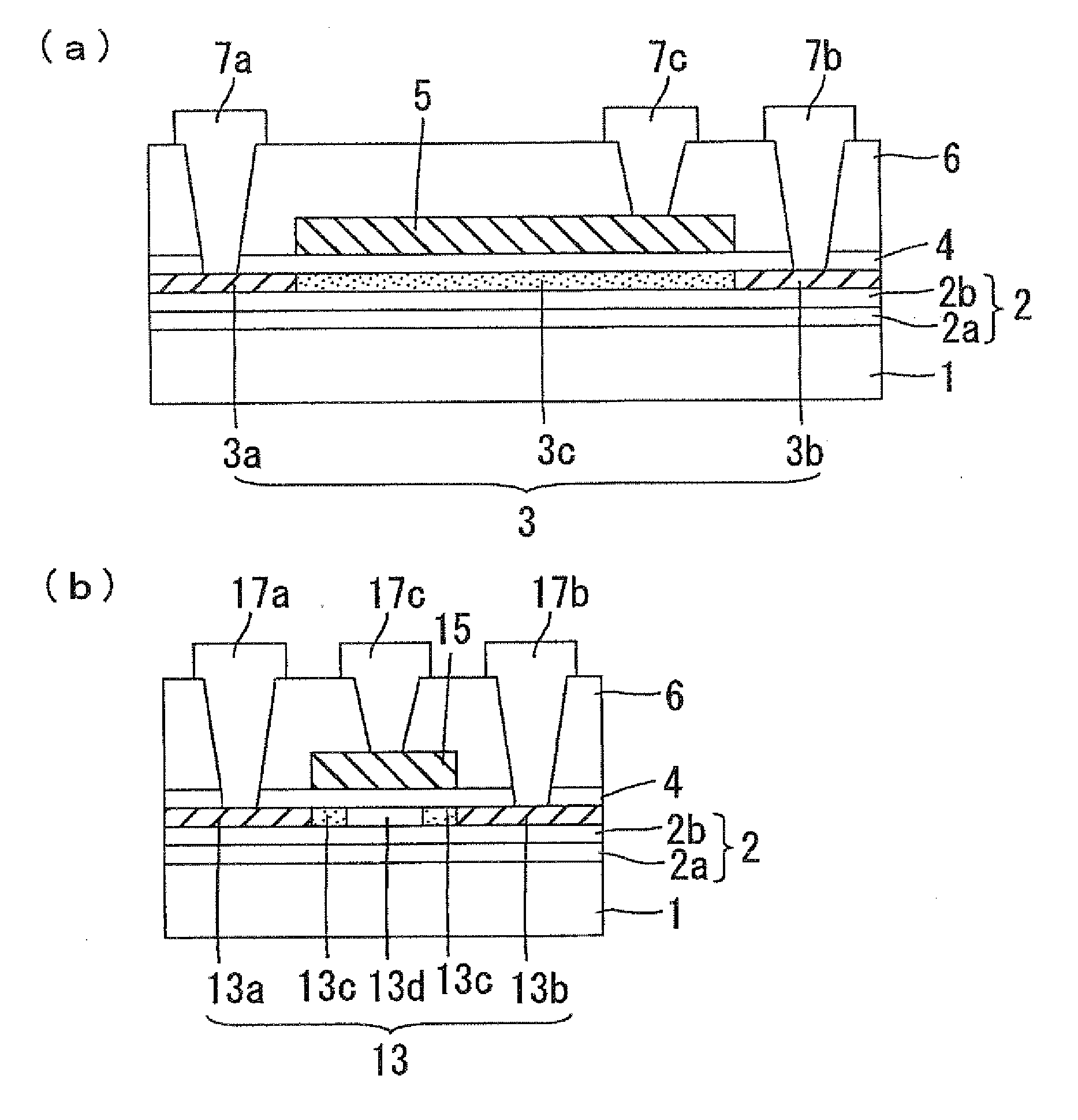

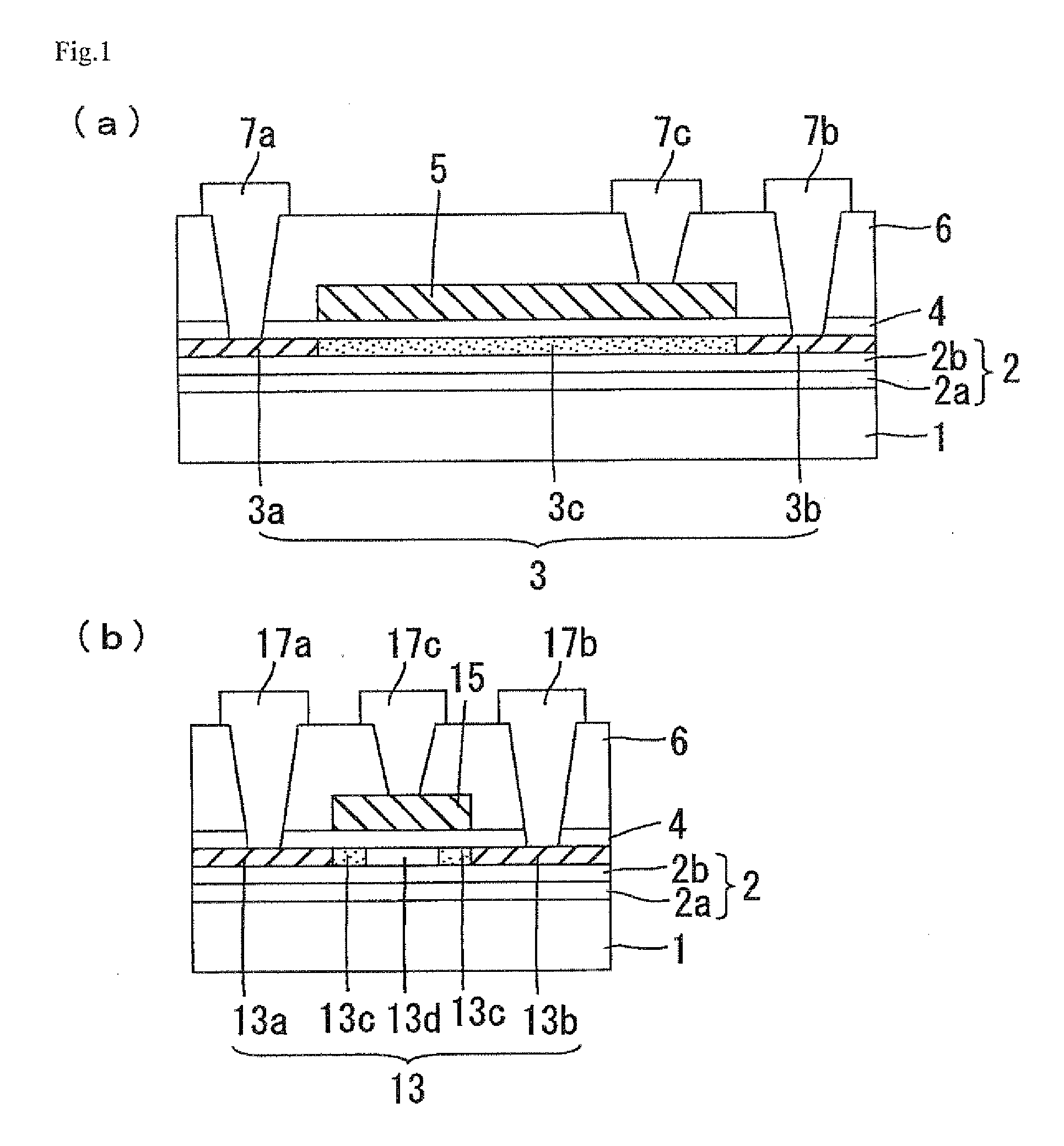

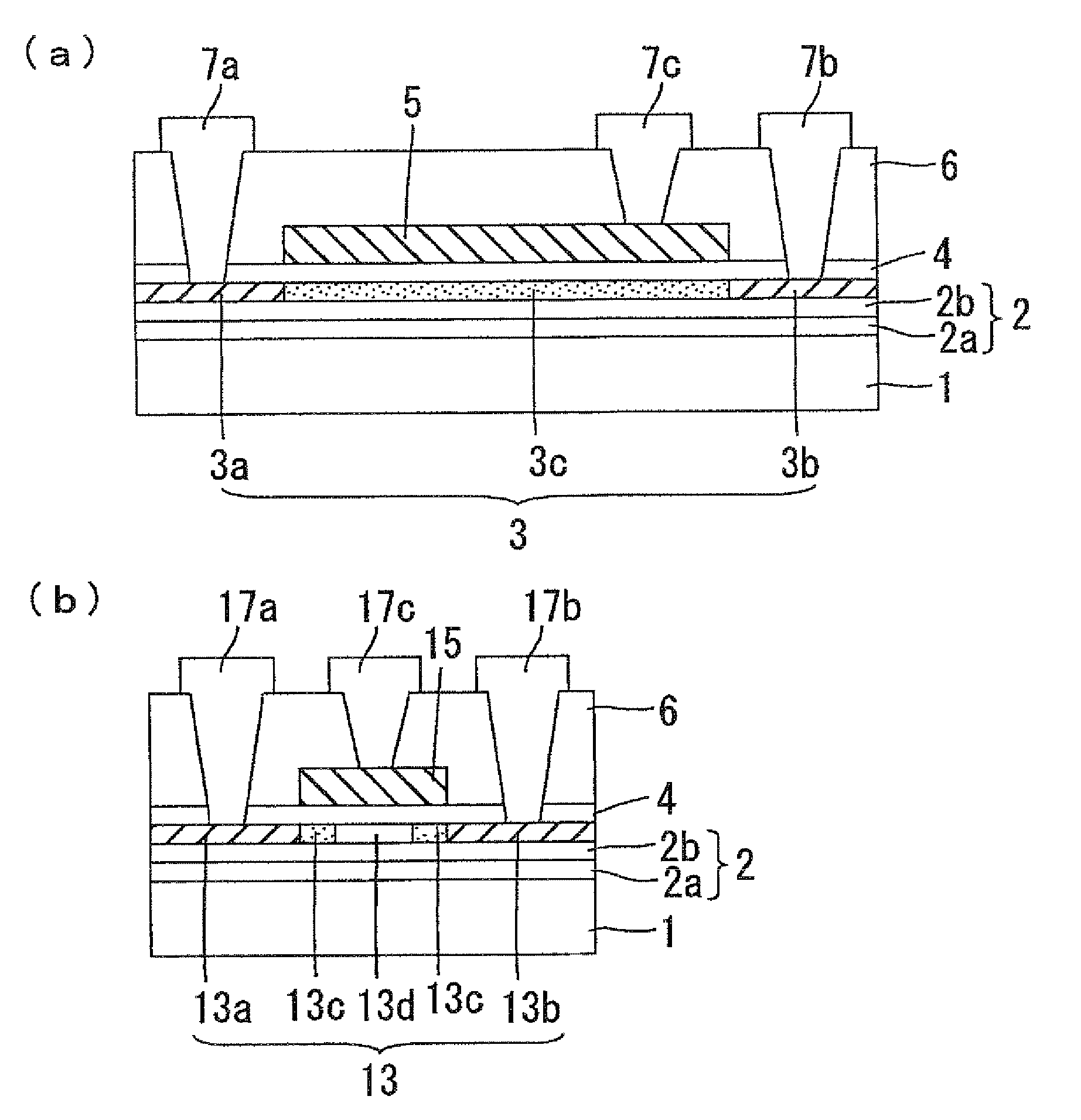

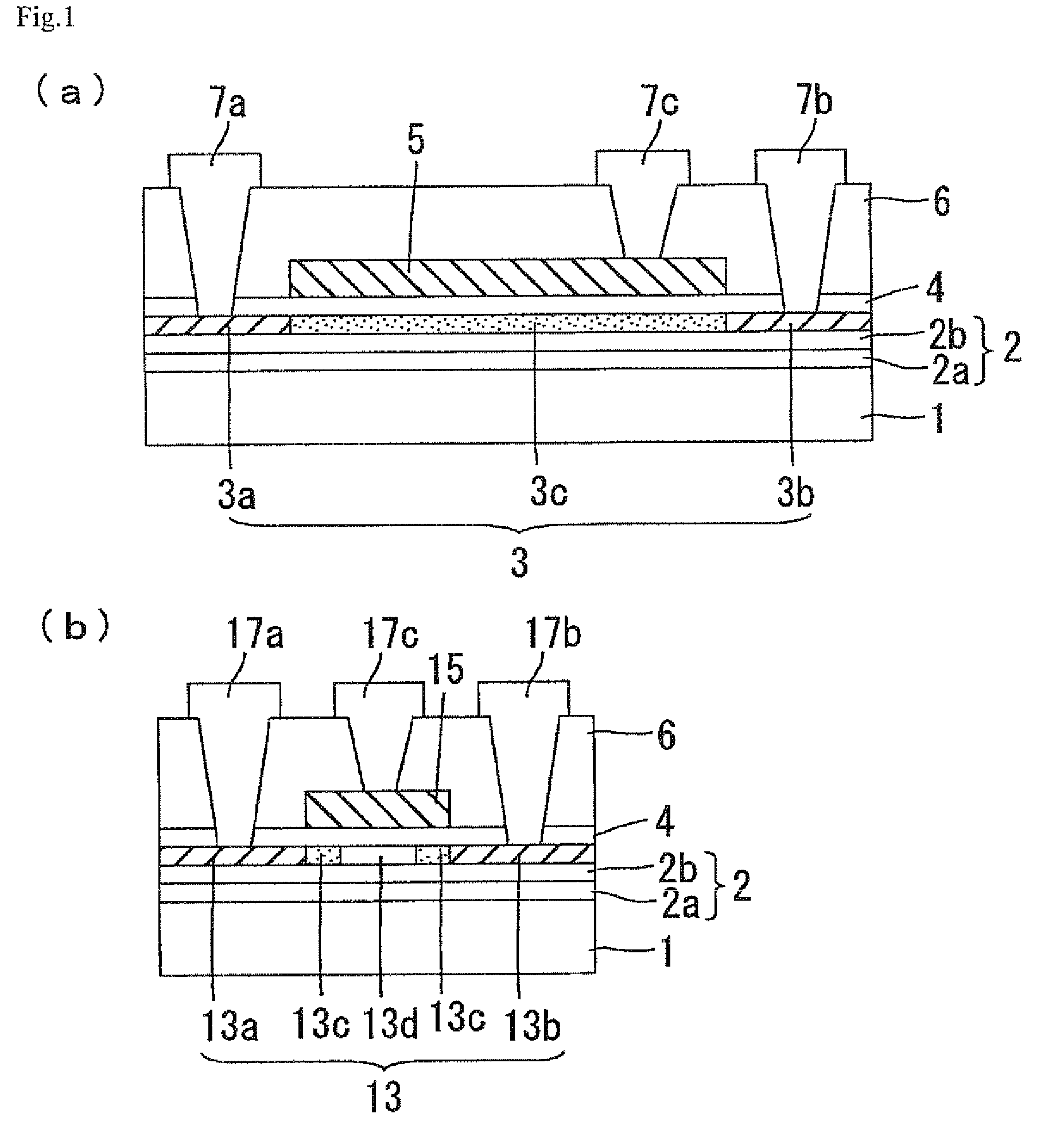

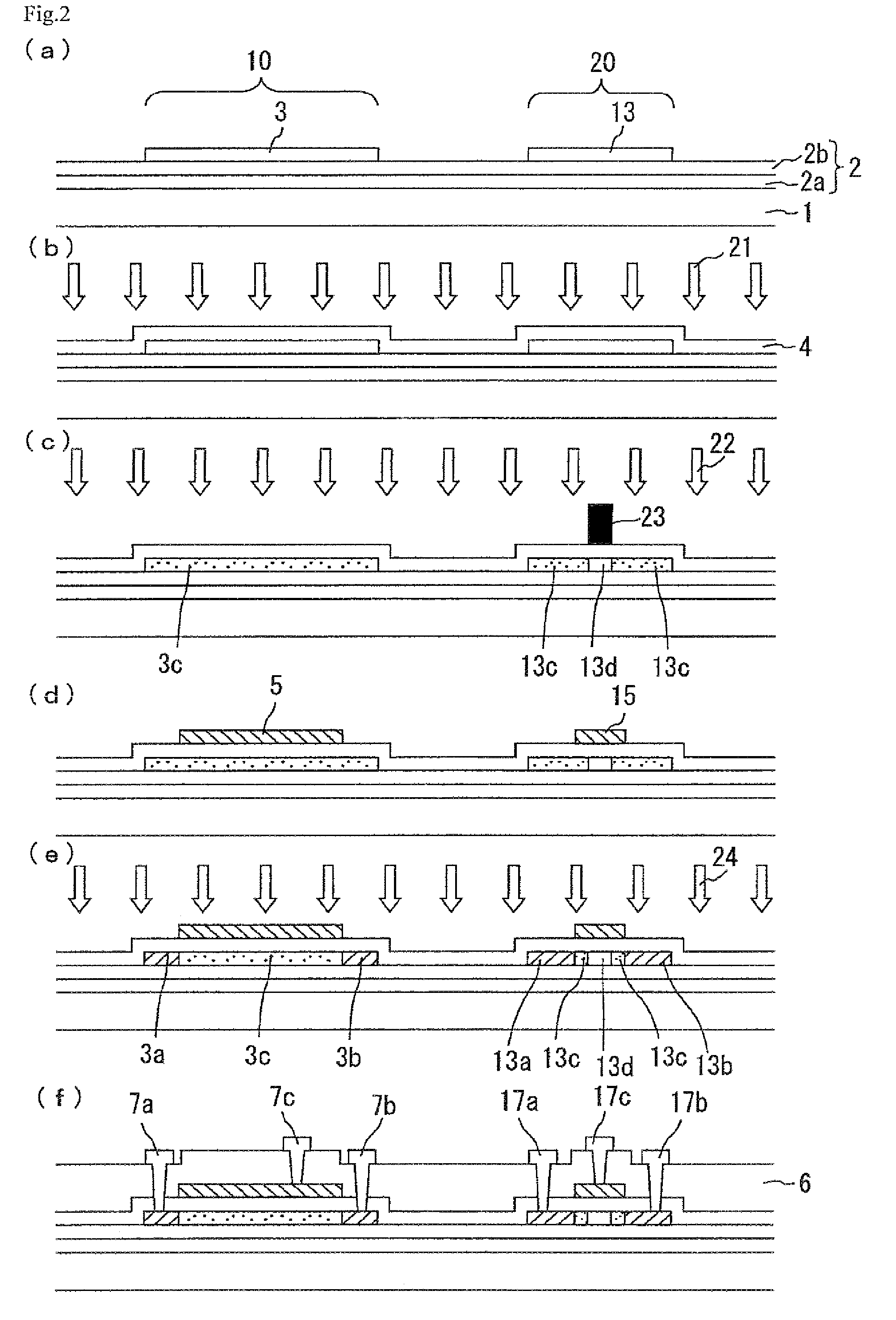

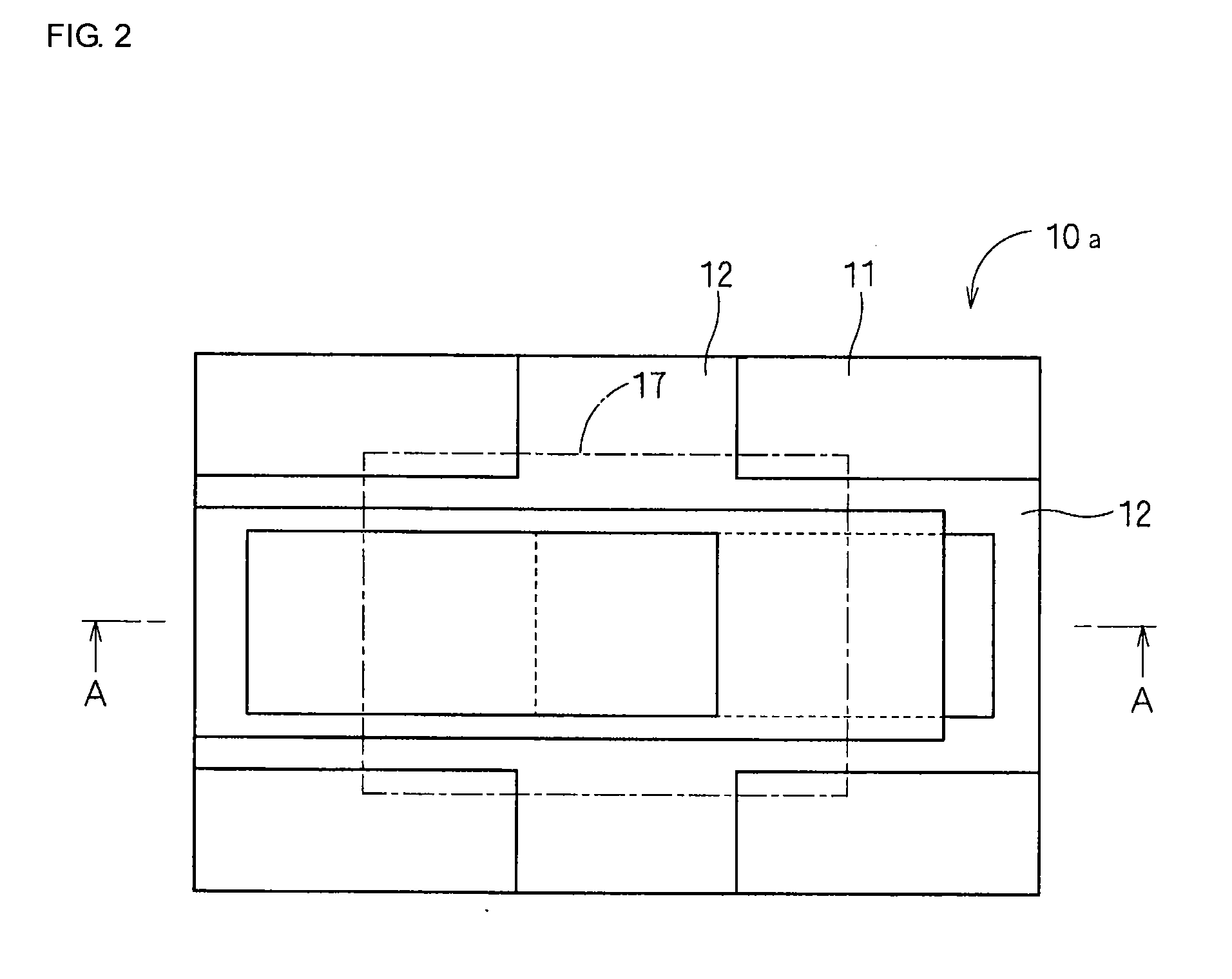

Semiconductor device, production method thereof, and electronic device

ActiveUS20100001273A1Increase the areaVariation in resistance among the TFTs can be easily suppressedTransistorSolid-state devicesHigh concentrationSemiconductor package

The present invention provides a semiconductor device which includes a thin film transistor as a resistance element, wherein a variation in resistance of the thin film transistor is suppressed without increasing an area of the resistance element and the resistance element can be produced through simplified production steps. The semiconductor device of the present invention is a semiconductor device including a first thin film transistor and a second thin film transistor on a substrate, the first thin film transistor being used as a resistance element, the second thin film transistor including a semiconductor layer having a low concentration drain region and a high concentration drain region, the low concentration drain region and the high concentration drain region being different in impurity concentration, wherein an impurity concentration of a channel region of a semiconductor layer in the first thin film transistor is the same as an impurity concentration of the low concentration drain region of the semiconductor layer in the second thin film transistor.

Owner:SHARP KK

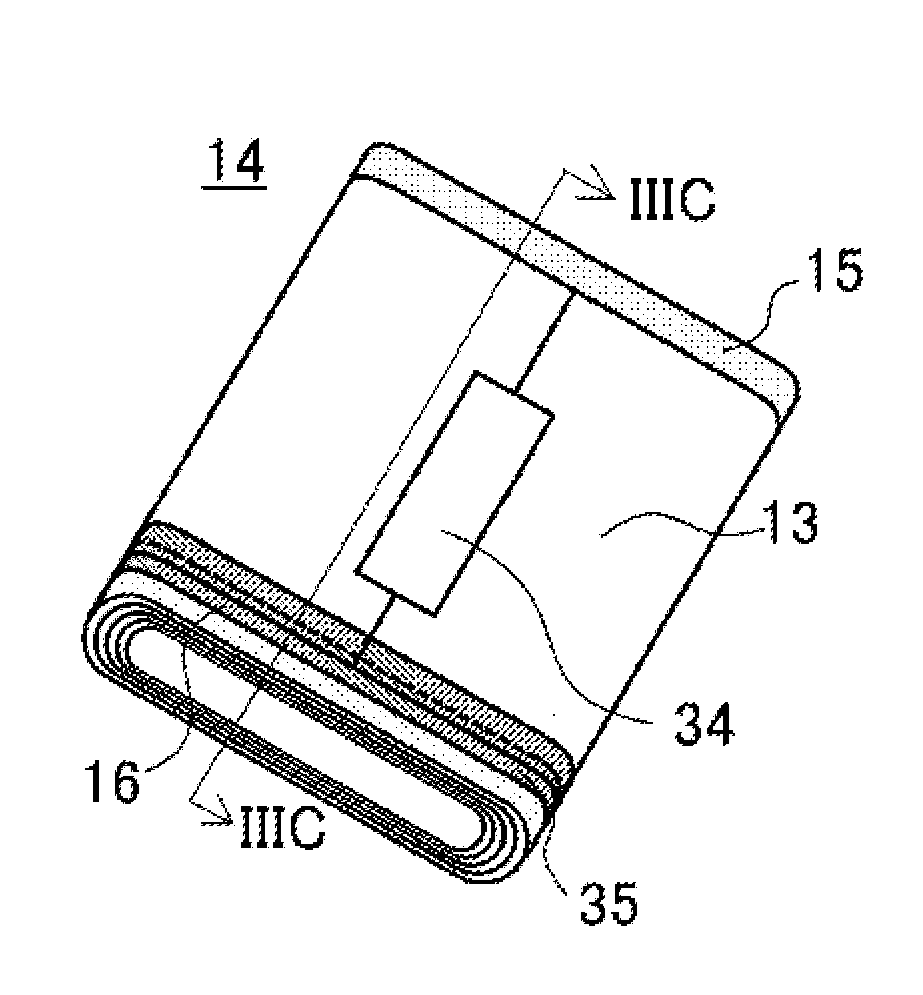

Secondary battery

InactiveUS20130084479A1Improve reliabilityRelieve pressureFinal product manufactureElectrode carriers/collectorsEngineeringCentral Site

A secondary battery with a flat wound electrode assembly includes a positive and negative electrode substrate exposed portions formed on the first and second end thereof, respectively. An end portion of a negative electrode active material mixture layer of a negative electrode plate on the negative electrode substrate exposed portion side protrudes more than an end portion of positive electrode active material mixture layer of an adjacent positive electrode plate. The negative electrode substrate exposed portion is converged on the central site in the thickness direction of the electrode assembly. A separator is located at the outermost surface of the electrode assembly, and the separator and the negative electrode substrate exposed portion of the adjacent negative electrode plate are fixed integrally with a fixing member. Thereby, semi-floating and peeling of the negative electrode active material mixture layer hardly occur at the end side of the negative electrode substrate exposed portion.

Owner:SANYO ELECTRIC CO LTD

Semiconductor device, production method thereof, and electronic device

ActiveUS8174053B2Increase the areaVariation in resistance among the TFTs can be easily suppressedSolid-state devicesSemiconductor devicesHigh concentrationPower semiconductor device

Owner:SHARP KK

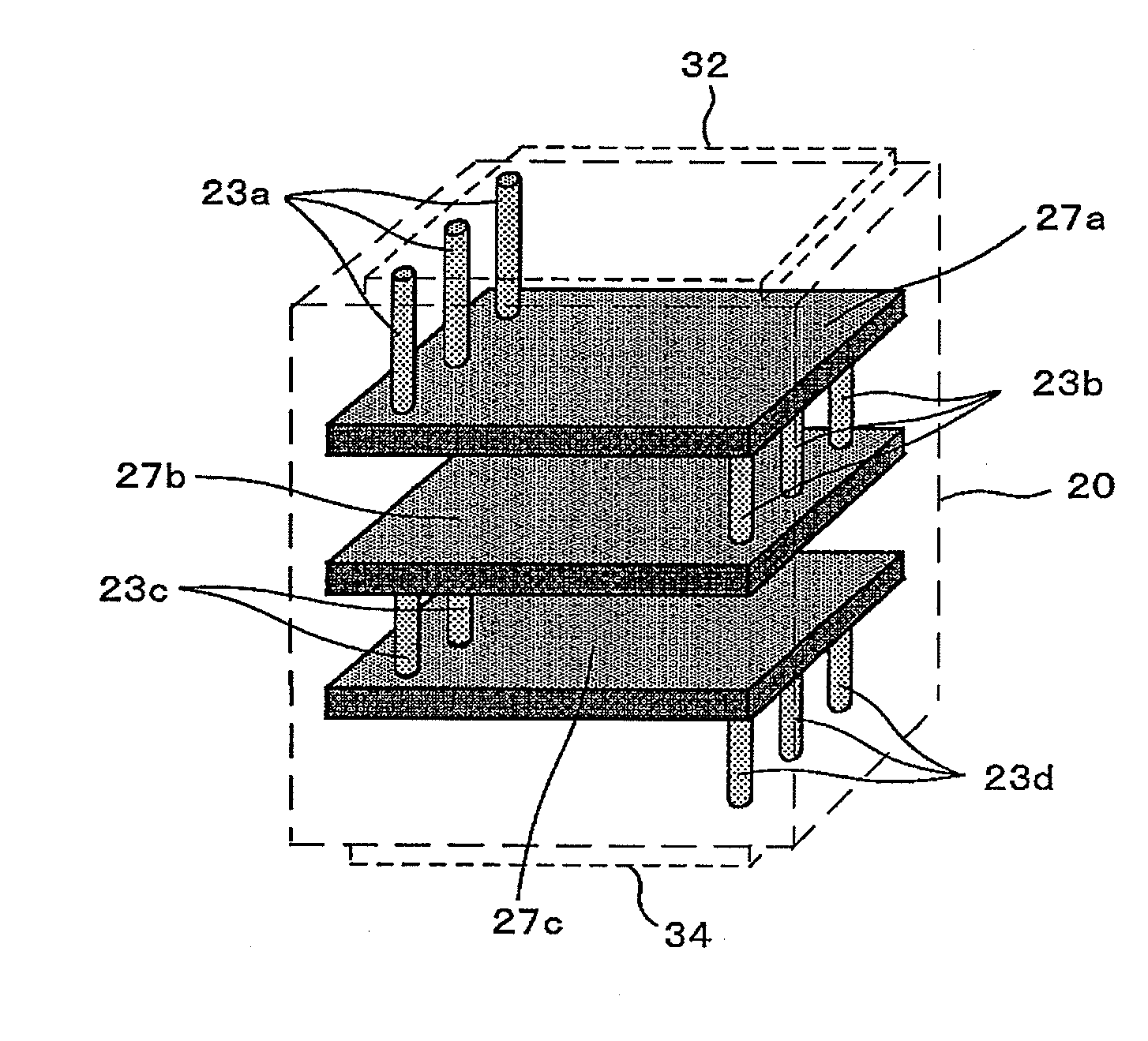

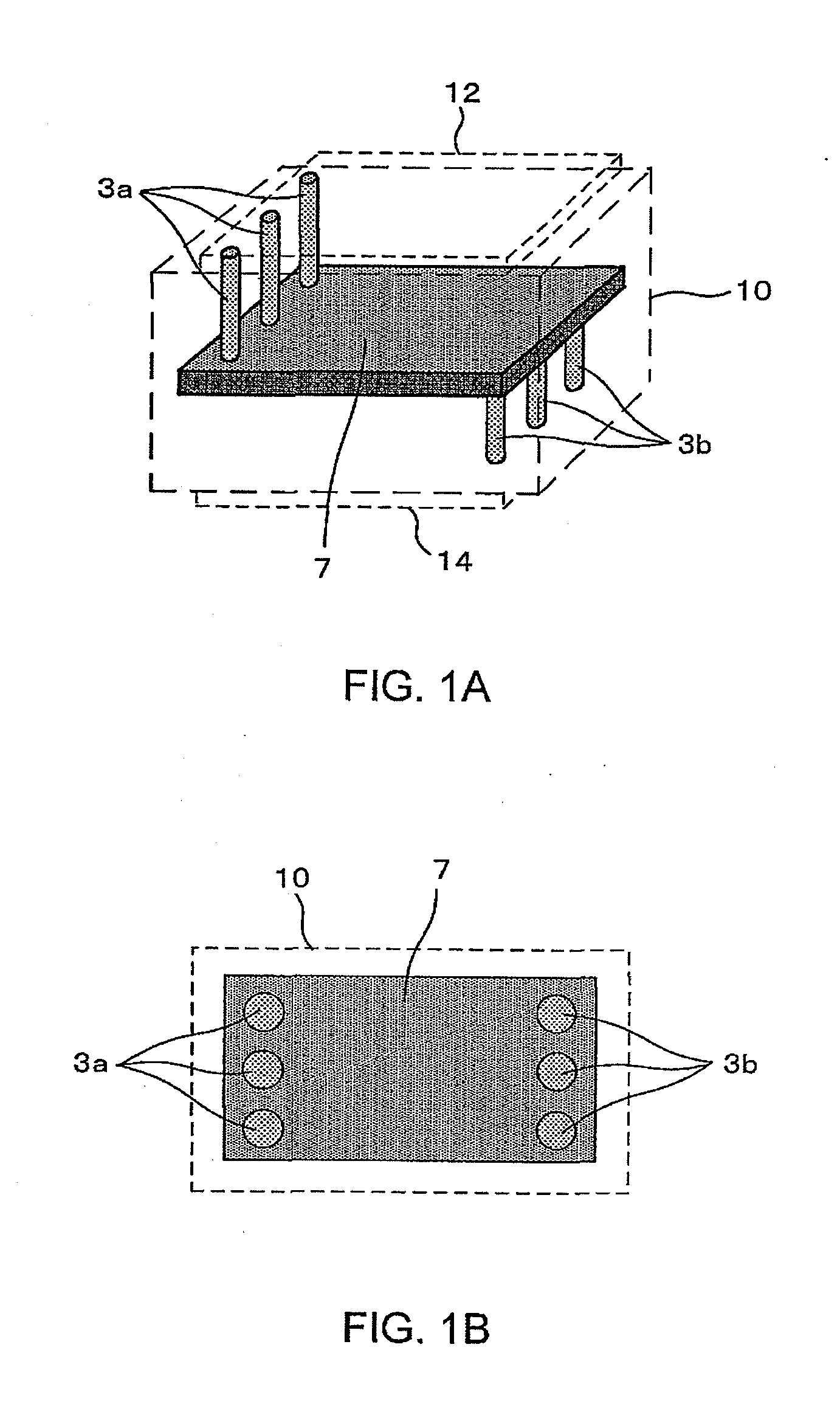

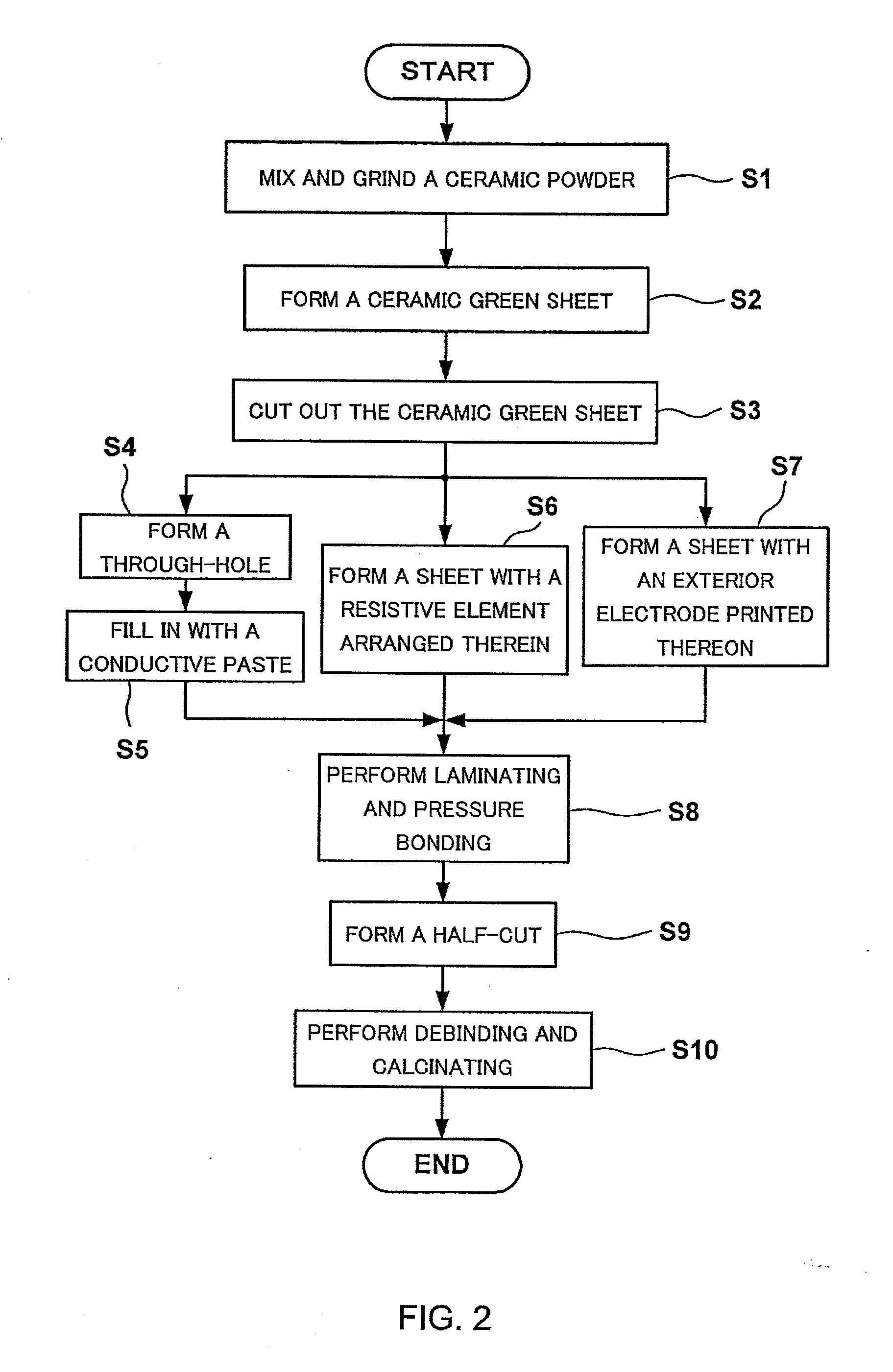

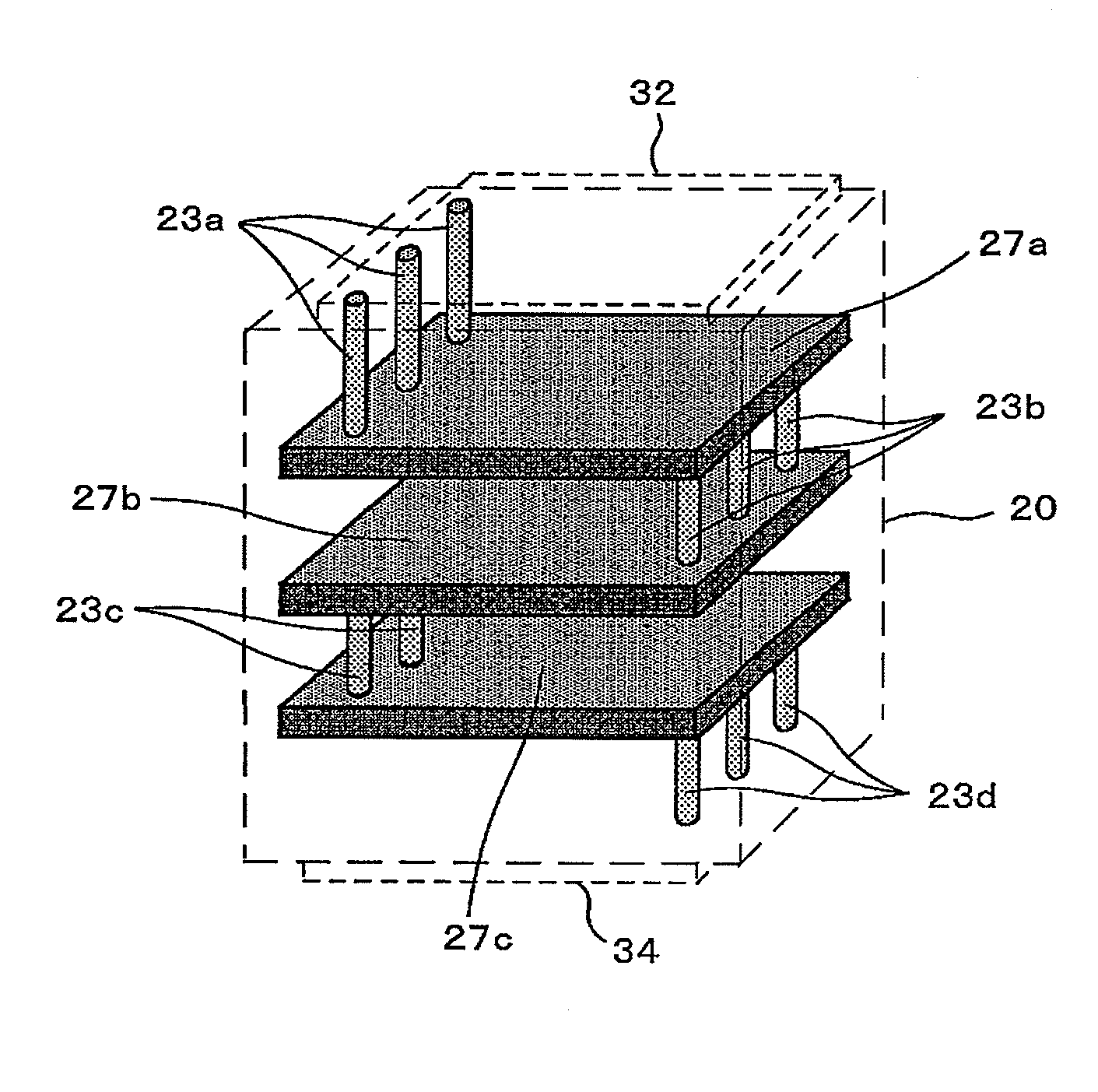

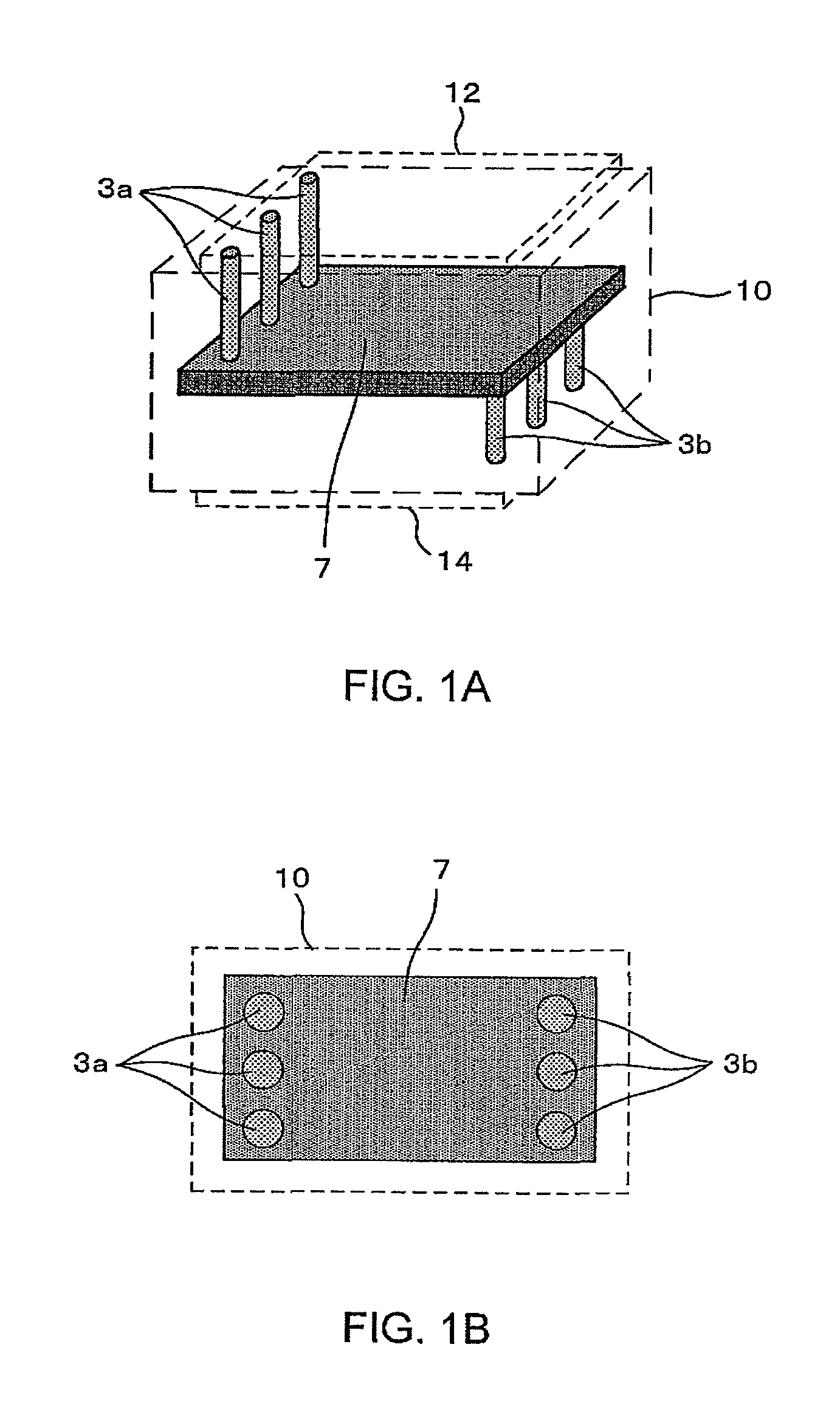

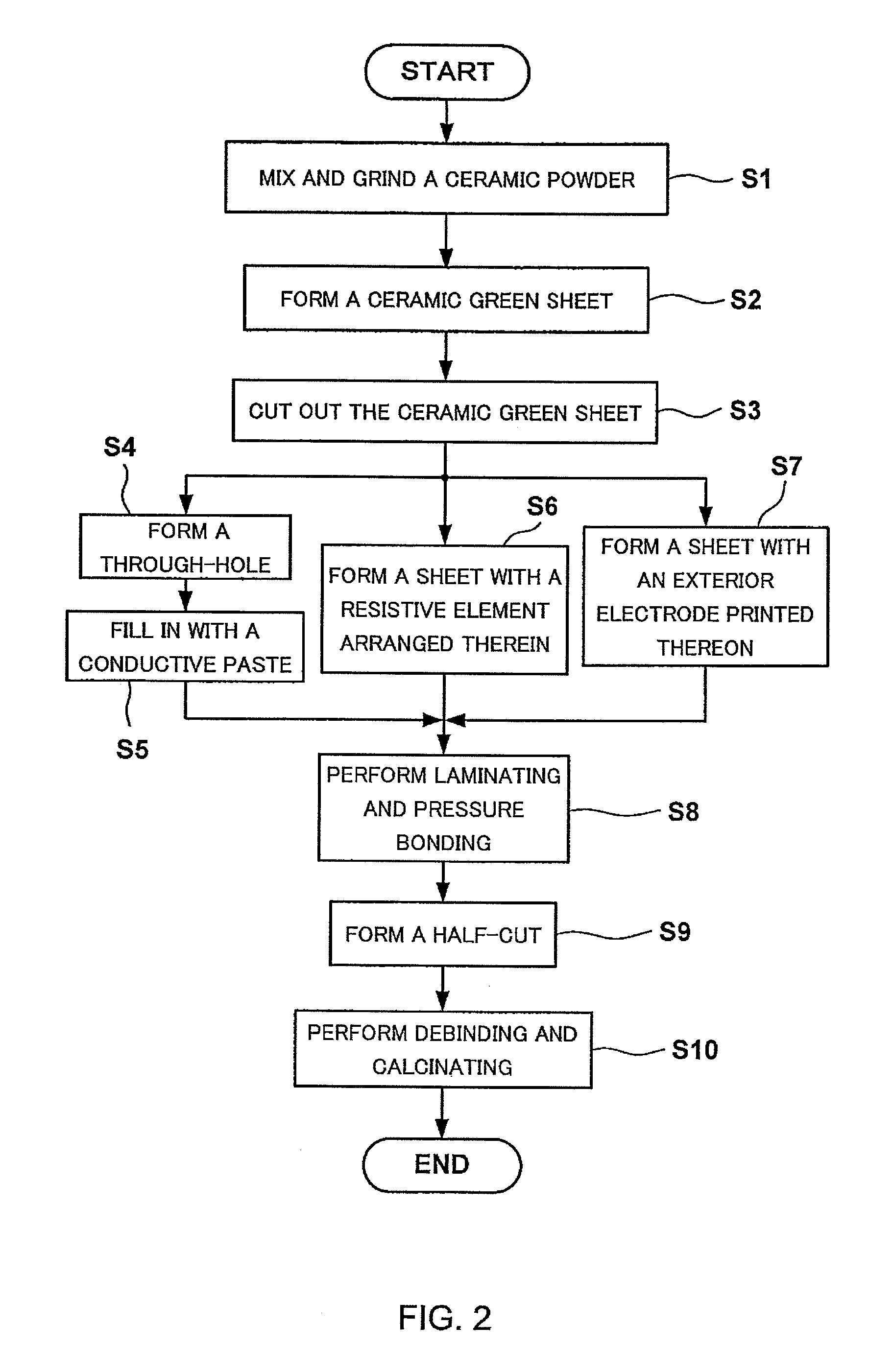

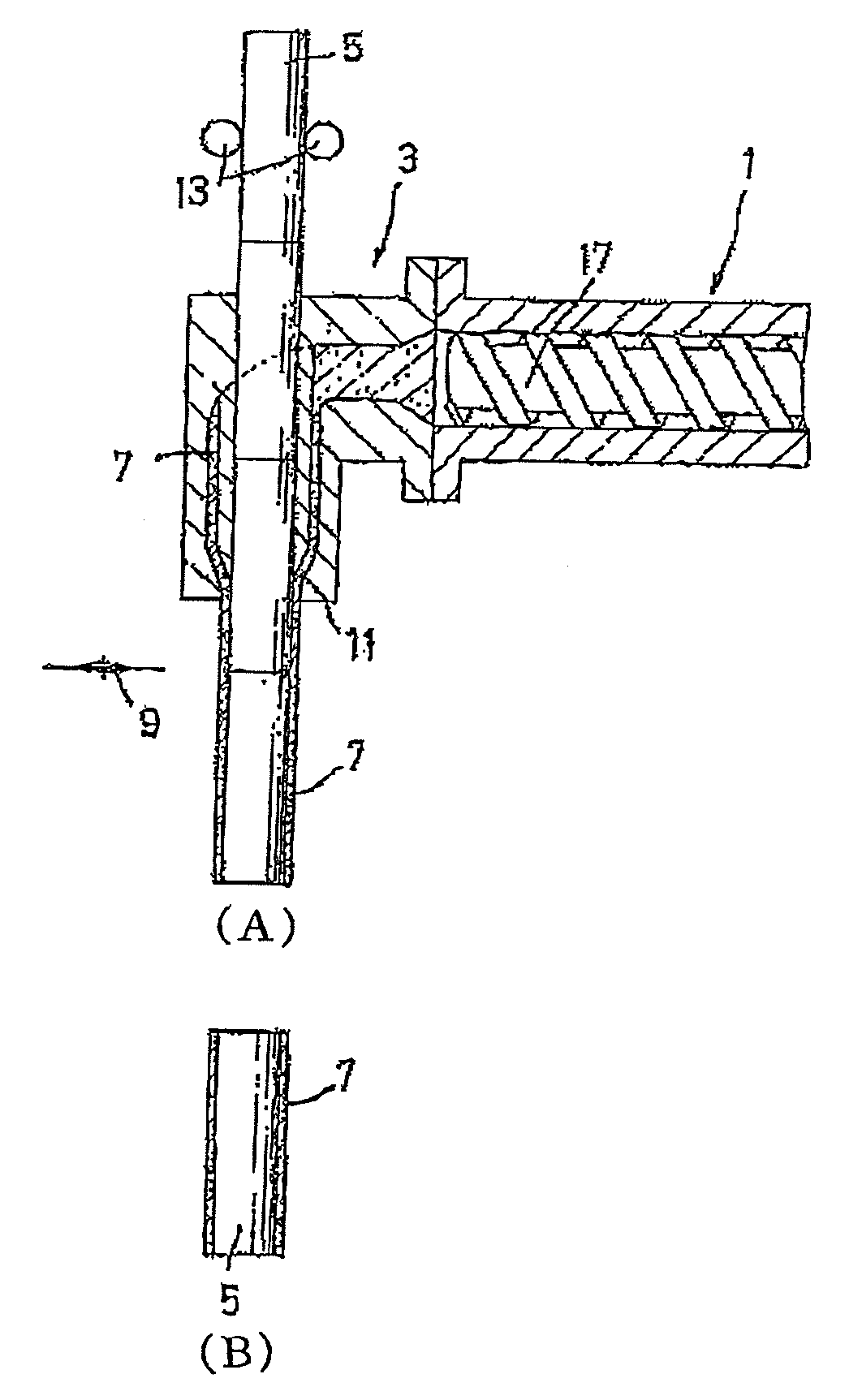

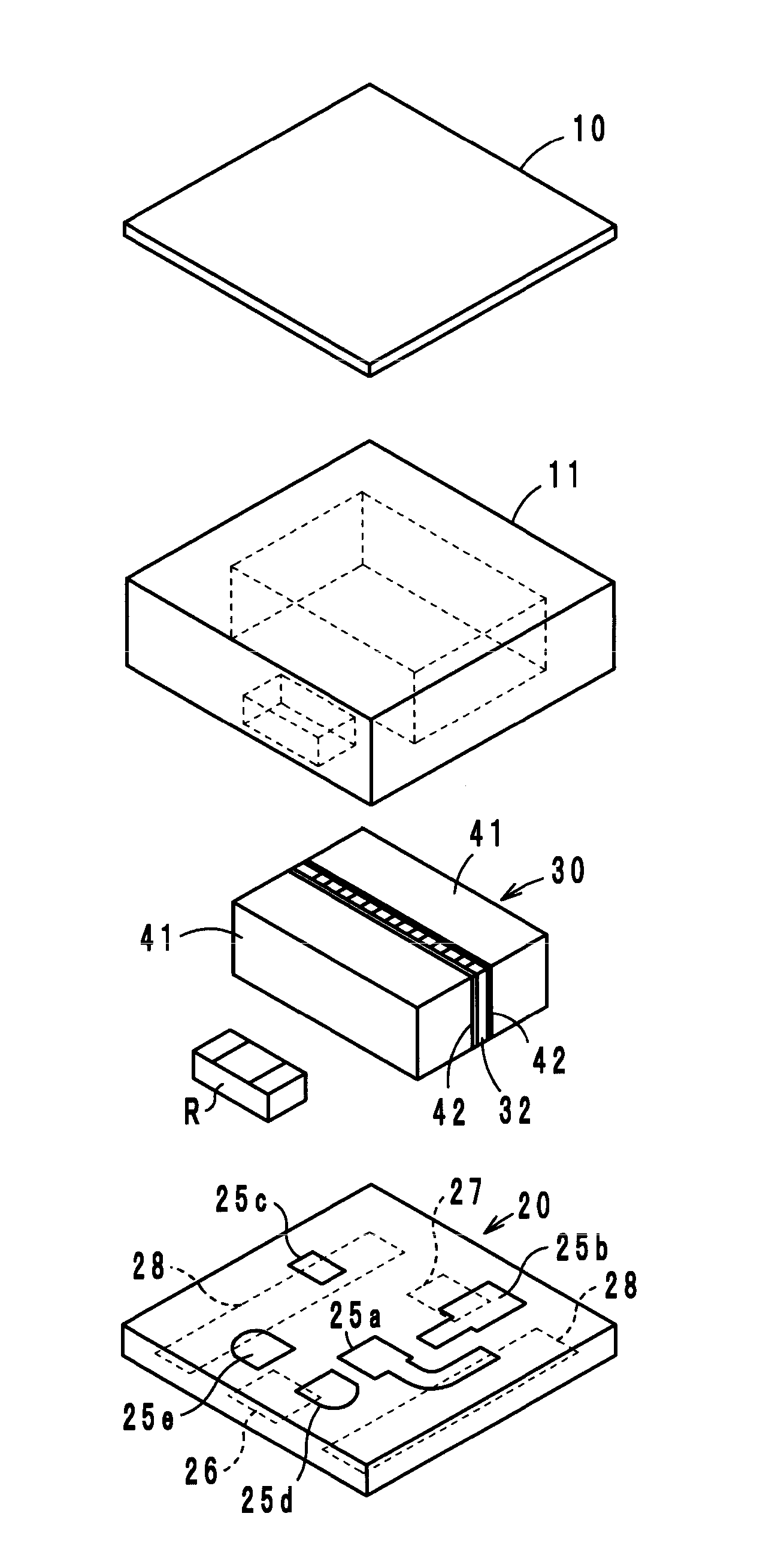

Laminated body and manufacturing method thereof

ActiveUS20100097172A1Variation in resistanceImprove connectivityResistor terminals/electrodesPrinted circuit aspectsEngineeringCeramic substrate

A laminated body and fabrication method thereof, which allow space saving and control of variation in internal layer resistance, are provided. When forming an internal-layer resistive element 7 in a multilayer ceramic substrate 10, the internal-layer resistive element 7 is connected to exterior electrodes (an upper surface electrode 32 and an undersurface electrode 34) via multiple via-electrodes 3a and 3b arranged in parallel, without a pad electrode adopted in the conventional laminated body. Moreover, in a multilayer ceramic substrate having multiple internal-layer resistive elements arranged in a multilayer structure, multiple internal-layer resistive elements are directly connected via multiple via-electrodes arranged in parallel.

Owner:KOA CORP

Switching element, switching element drive method and fabrication method, reconfigurable logic integrated circuit, and memory element

InactiveUS7960712B2Low reliabilityLow densitySemiconductor/solid-state device detailsSolid-state devicesElectricityElectrochemical response

The switching element of the present invention includes: an ion conduction layer (4) in which metal ions can move freely; a first electrode (1) that contacts the ion conduction layer (4); and a second electrode (2) that contacts the ion conduction layer (4), that is formed such that the ion conduction layer (4) is interposed between the first electrode (1) and the second electrode (2), and that supplies metal ions to the ion conduction layer (4) or that receives metal ions from the ion conduction layer (4) to cause precipitation of the metal that corresponds to the metal ions. An introduction path (5) composed of the metal and of a prescribed width is further provided on the ion conduction layer (4) for electrically connecting the first electrode (1) and the second electrode (2). The application of voltage to the first electrode (1) relative to the second electrode (2) then causes an electrochemical reaction between the introduction path (5) and the second electrode (2) whereby the electrical characteristics are switched.

Owner:NEC CORP

High zirconia refractory material

ActiveUS20110166008A1Improved creep propertiesVariation in resistanceGlass furnace apparatusRefractoryMaterials science

Fused and cast refractory product including on oxides basis in percent by weight and for a total of 100%: ZrO2+HfO2 complement to 100%; 3.5% to 6.0% SiO2; 0.7% to 1.5% Al2O3; 0.10% to 0.43% Na2O+K2O; 0.05% to 0.80% B2O3; less than 0.4% CaO+SrO+MgO+ZnO; less than 0.05% P2O5; less than 0.55% Fe2O3+TiO2; less than 1.5% other species. The ratio of percentages by weight of Al2O3 / (Na2O+K2O) being greater than or equal to 3.5 and the ratio of percentages by weight of B2O3 / (Na2O+K2O) being between 0.3 and 2.5.

Owner:SAINT GOBAIN CENT DE RES & DEVS & DETUD EUROEN

Piezoelectric thin film resonator and manufacturing method thereof

InactiveUS20080178444A1Superior resistance against electric powerVariation in propertyPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksResonatorPiezoelectric thin films

A piezoelectric thin film resonator which can reduce variations in resonant frequency and resonant resistance by uniformly planarizing a structural film, and a method of manufacturing the piezoelectric thin film resonator. The piezoelectric thin film resonator has a substrate having at least one flat major surface; a dielectric film having two support portions supported by the major surface of the substrate and a floating portion which is connected to the support portions and which is disposed over the major surface of the substrate with an airspace layer provided therebetween; and a vibration portion which is formed of a pair of electrodes and a piezoelectric thin film provided therebetween and which is provided on the floating portion of the dielectric film at a side opposite to the airspace layer. A surface of the dielectric film at a side opposite to the substrate is planarized by a plasma treatment using an inert gas or a gas containing an element forming a dielectric film.

Owner:MURATA MFG CO LTD

Planar sensor element

InactiveUS6964733B1Variation in resistanceImprove heating efficiencyMaterial electrochemical variablesElectrical conductorEngineering

A planar sensor element for determining gas components, which includes a layer structure with a heating element integrated therein with a layer-shaped heating conductor. The heating conductor is arranged in a layer plane of the layer structure so that an at least approximately homogeneous distribution of the heating power of the heating element over the cross-section of the layer structure is obtained.

Owner:ROBERT BOSCH GMBH

Use of a porous dielectric material as an etch stop layer for non-porous dielectric films

InactiveUS20080146037A1Minimized line height variationImproved device functionality and performanceSemiconductor/solid-state device detailsSolid-state devicesEtchingIon current

Interconnect structures possessing a non-porous (dense) low-k organosilicate glass (OSG) film utilizing a porous low-k OSG film as an etch stop layer or a porous low-k OSG film using a non-porous OSG film as a hardmask for use in semiconductor devices are provided herein. The novel interconnect structures are capable of delivering improved device performance, functionality and reliability owing to the reduced effective dielectric constant of the stack compared with that of those conventionally employed and also because of the relatively uniform line heights made feasible by these unique and seemingly counterintuitive features. The present invention also provides a fluorocarbon-based dual damascene etch process that achieves selective etching of a dense low-k OSG films relative to that of a porous low-k OSG film owing to the tunability of the gas-phase fluorine:carbon ratio (gas dissociation) and ion current below a critical threshold and given the larger carbon content of the porous film relative to that of the dense film.

Owner:ALSEPHINA INNOVATIONS INC

Laminated ceramic electronic component

ActiveUS8305729B2Variation in propertyVariation in resistanceFixed capacitor electrodesStacked capacitorsElectronic componentMaterials science

A laminated ceramic electronic component includes first internal electrodes and second internal electrodes that overlap each other through ceramic layers, each of the first and second internal electrodes having first and second effective portions, first and second connecting portions, and first and second extended portions whose film thickness is greater than that of the first and second connecting portions and which are exposed at the outer surface of a ceramic element assembly. When distances from side surfaces of the ceramic assembly on which first and second external electrodes are provided to the inner edges of the first and second extended portions are defined as L1 and L2, respectively, and a distance between side surfaces and the end of the second internal electrode or the end of the first internal electrode is defined as G2 or G1, G2>L1 and G1>L2 are satisfied.

Owner:MURATA MFG CO LTD

Semiconductor ceramic and positive temperature coefficient thermistor

ActiveUS8289125B2Desired PTC characteristicImprove reliabilityNon-metal conductorsLayered productsRare-earth elementThermistor

A semiconductor ceramic includes a BamTiO3-based composition, as a main component, having a perovskite structure represented by general formula AmBO3. The molar ratio m between the A site and the B site satisfies 1.001≦m≦1.01. Part of Ba constituting the A site is replaced with Bi, Ca, a rare-earth element, and Na. The molar content of the Ca when the total number of moles of the elements constituting the A site is 1 mole is 0.05 to 0.20 (preferably 0.125 to 0.175). A PTC thermistor includes a component body formed of the semiconductor ceramic. Accordingly, there is provided a lead-free semiconductor ceramic that substantially does not contain lead and that has desired PTC characteristics and high reliability.

Owner:MURATA MFG CO LTD

Laminated body and manufacturing method thereof

ActiveUS8193898B2High assemblyHighly miniaturizedResistor terminals/electrodesPrinted circuit aspectsCeramic substrateResistive element

Owner:KOA CORP

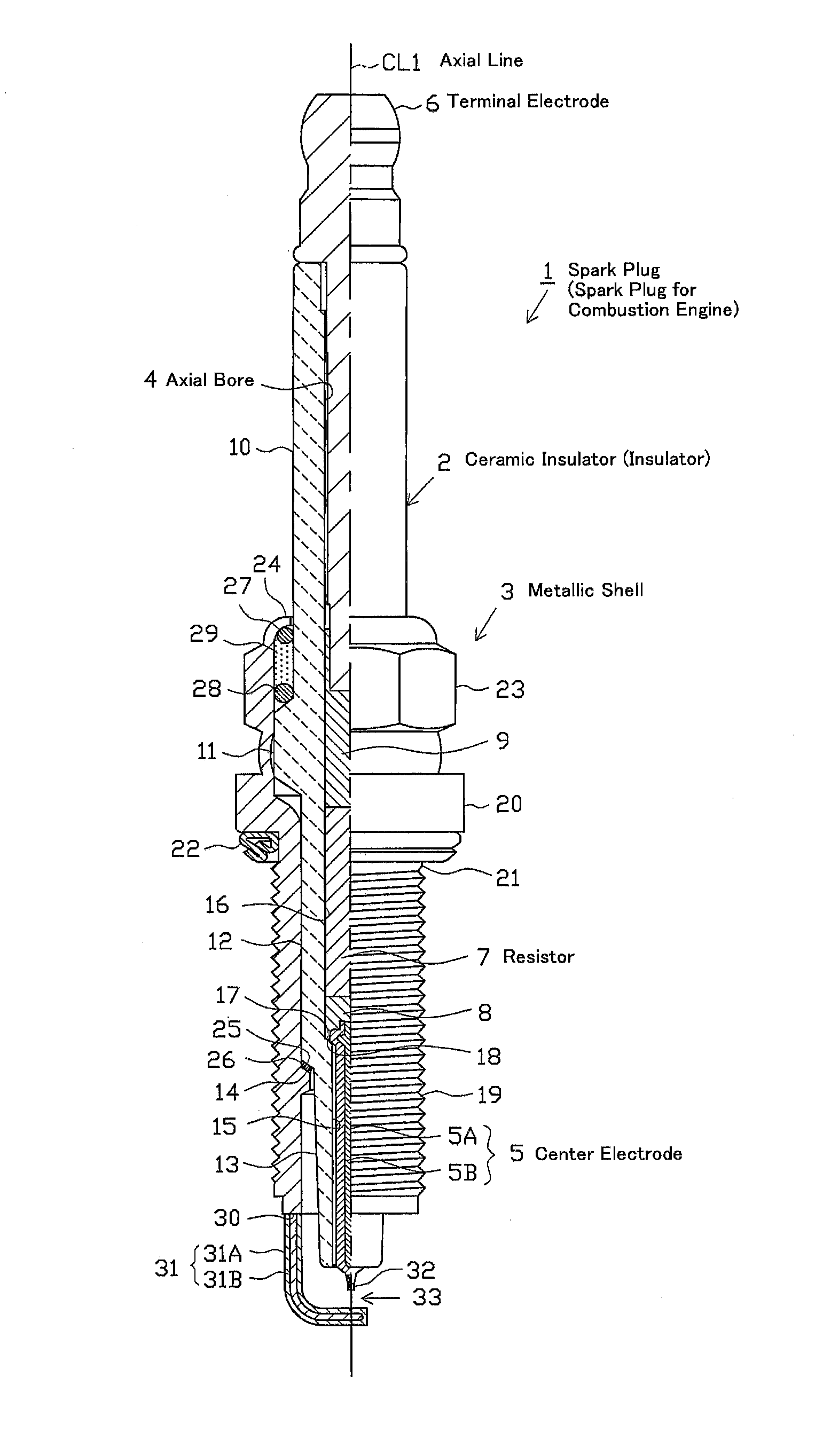

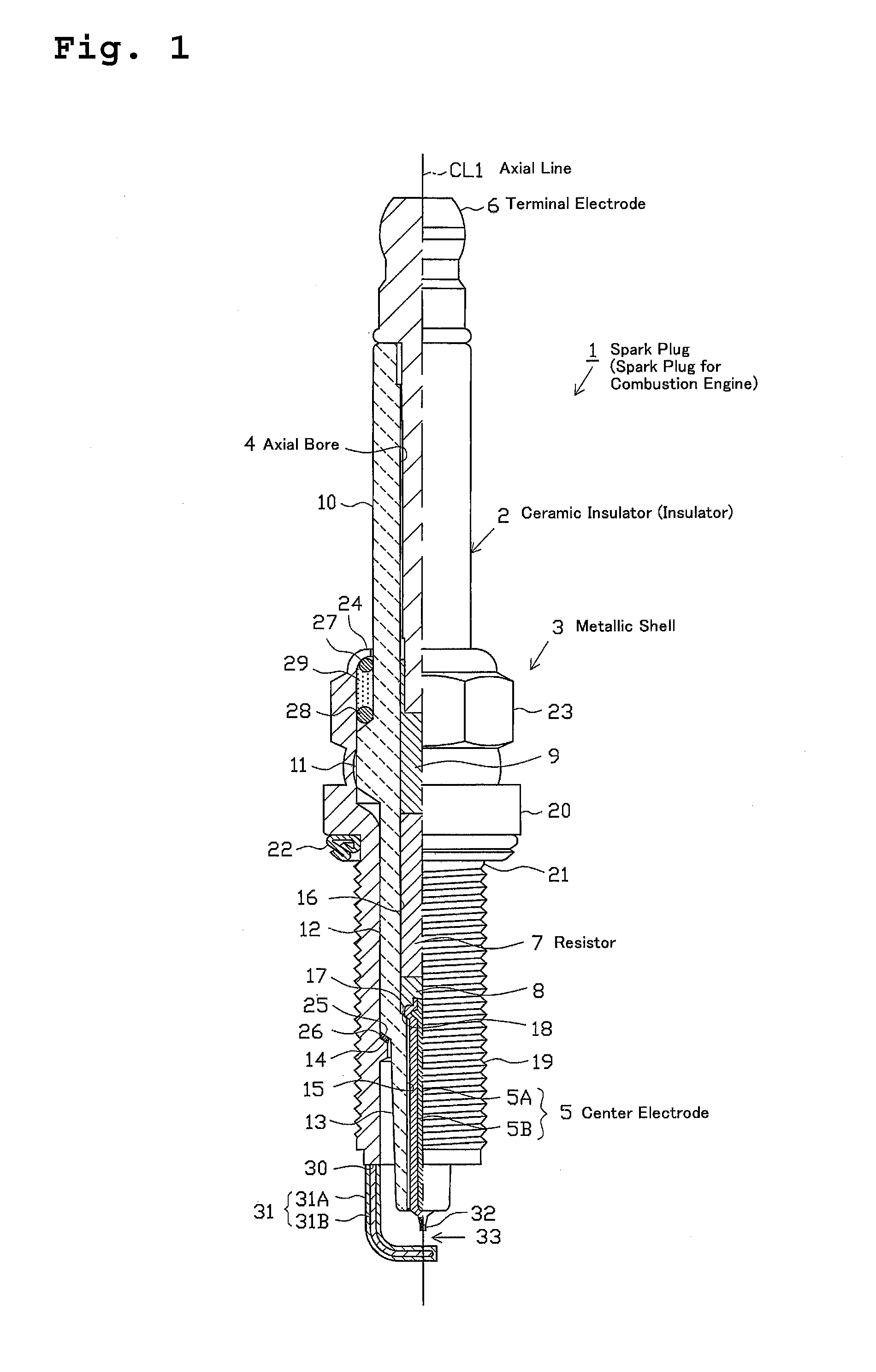

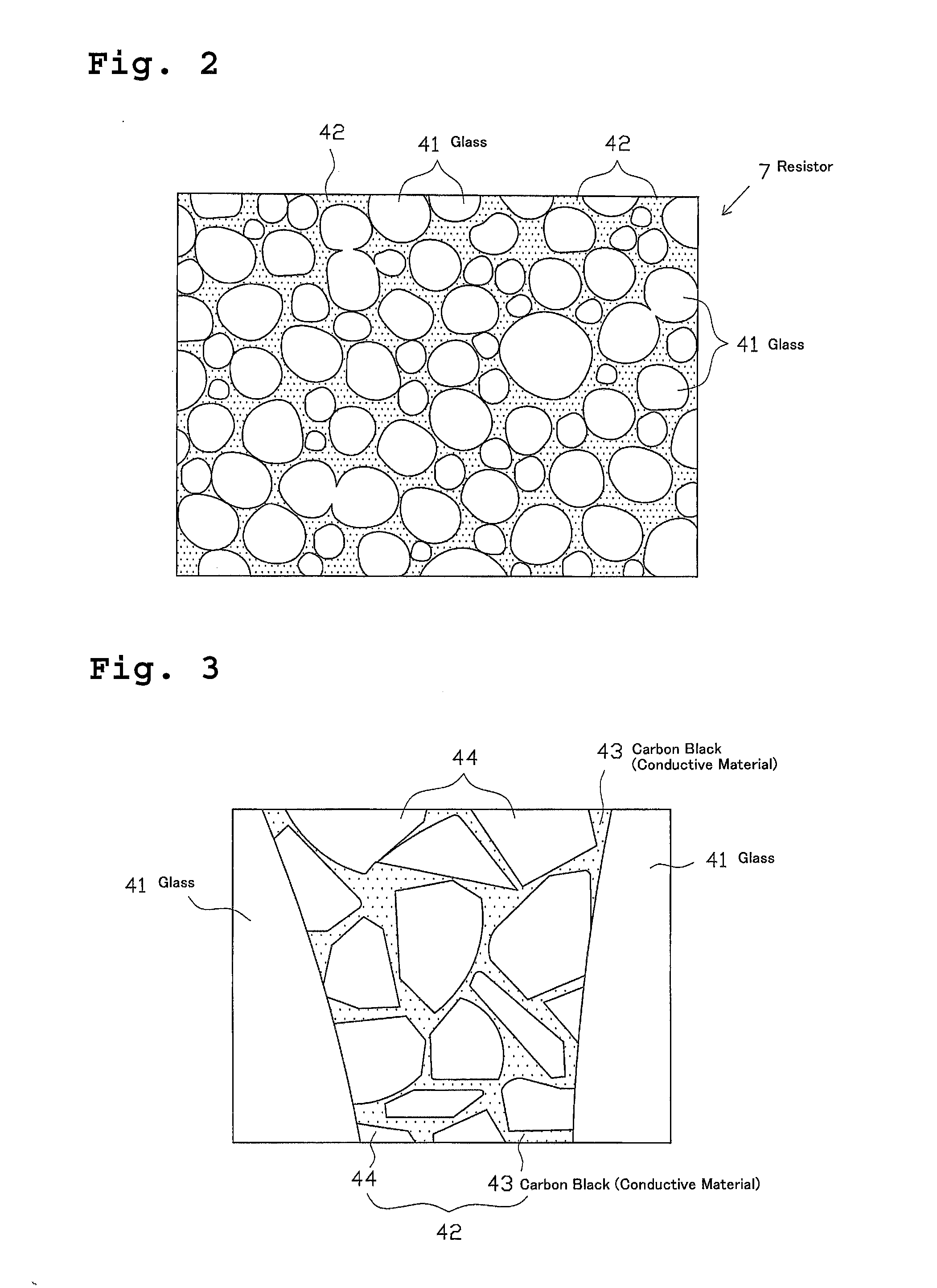

Spark plug for internal-combustion engine

ActiveUS20120176021A1Improved load life performanceVariation in resistanceSparking plugsMachines/enginesMetallurgyInternal combustion engine

A spark plug that prevents a sharp increase in resistance of a resistor and materializes an excellent load life performance. The spark plug has a resistor formed by heat-sealing of a resistor composition that contains, at least, a conductive material and glass powder. The glass powder contains between 35.0 mol % and 69.8 mol % SiO2, between 15.0 mol % and 49.8 mol % B2O3, between 5.0 mol % and 20.0 mol % Li2O, and at least one additive selected from MgO, CaO, SrO, BaO, Na2O, K2O, ZnO, and ZrO2 in a total of between 2.6 mol % and 25.0 mol %. Further, the total content of Li2O and the additive(s) in the glass powder is between 15.2 mol % and 45.0 mol %, and the ratio of the Li2O content to the total content of the additive(s) is between 1.3 and 5.0.

Owner:NGK SPARK PLUG CO LTD

High zirconia refractory material

ActiveUS8309482B2Improved creep propertiesVariation in resistanceGlass furnace apparatusRefractoryMaterials science

Fused and cast refractory product including on oxides basis in percent by weight and for a total of 100%: ZrO2+HfO2 complement to 100%; 3.5% to 6.0% SiO2; 0.7% to 1.5% Al2O3; 0.10% to 0.43% Na2O+K2O; 0.05% to 0.80% B2O3; less than 0.4% CaO+SrO+MgO+ZnO; less than 0.05% P2O5; less than 0.55% Fe2O3+TiO2; less than 1.5% other species. The ratio of percentages by weight of Al2O3 / (Na2O+K2O) being greater than or equal to 3.5 and the ratio of percentages by weight of B2O3 / (Na2O+K2O) being between 0.3 and 2.5.

Owner:SAINT GOBAIN CENT DE RES & DEVS & DETUD EUROEN

Semiconductive rubber belt, and process for producing the same

ActiveUS20100230640A1Variation in resistanceUnevenness in the molecular orientation degree is decreasedConductive materialOrganic conductorsElectrical resistance and conductanceEngineering

Owner:NITTA CHEM IND PROD CO LTD

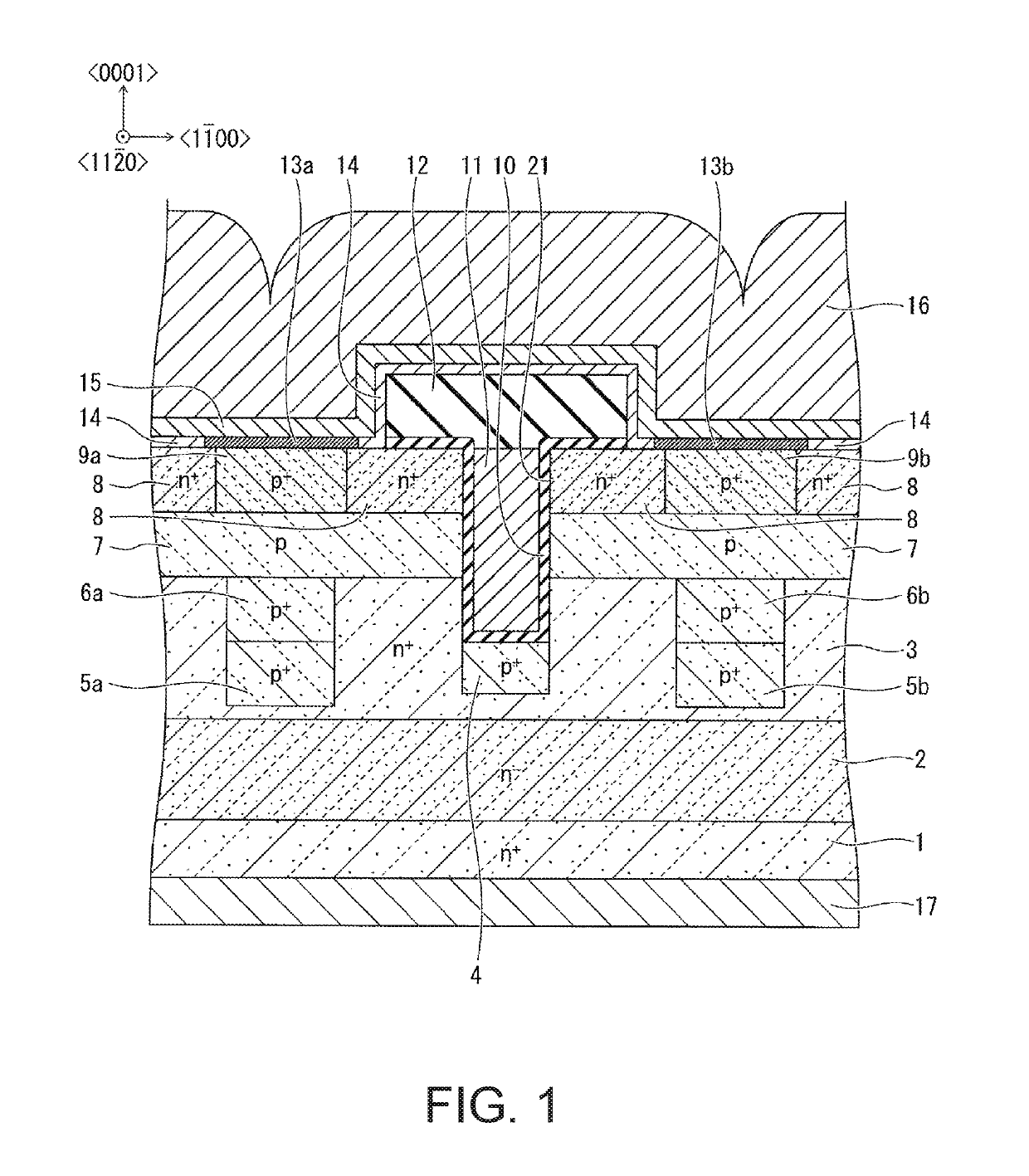

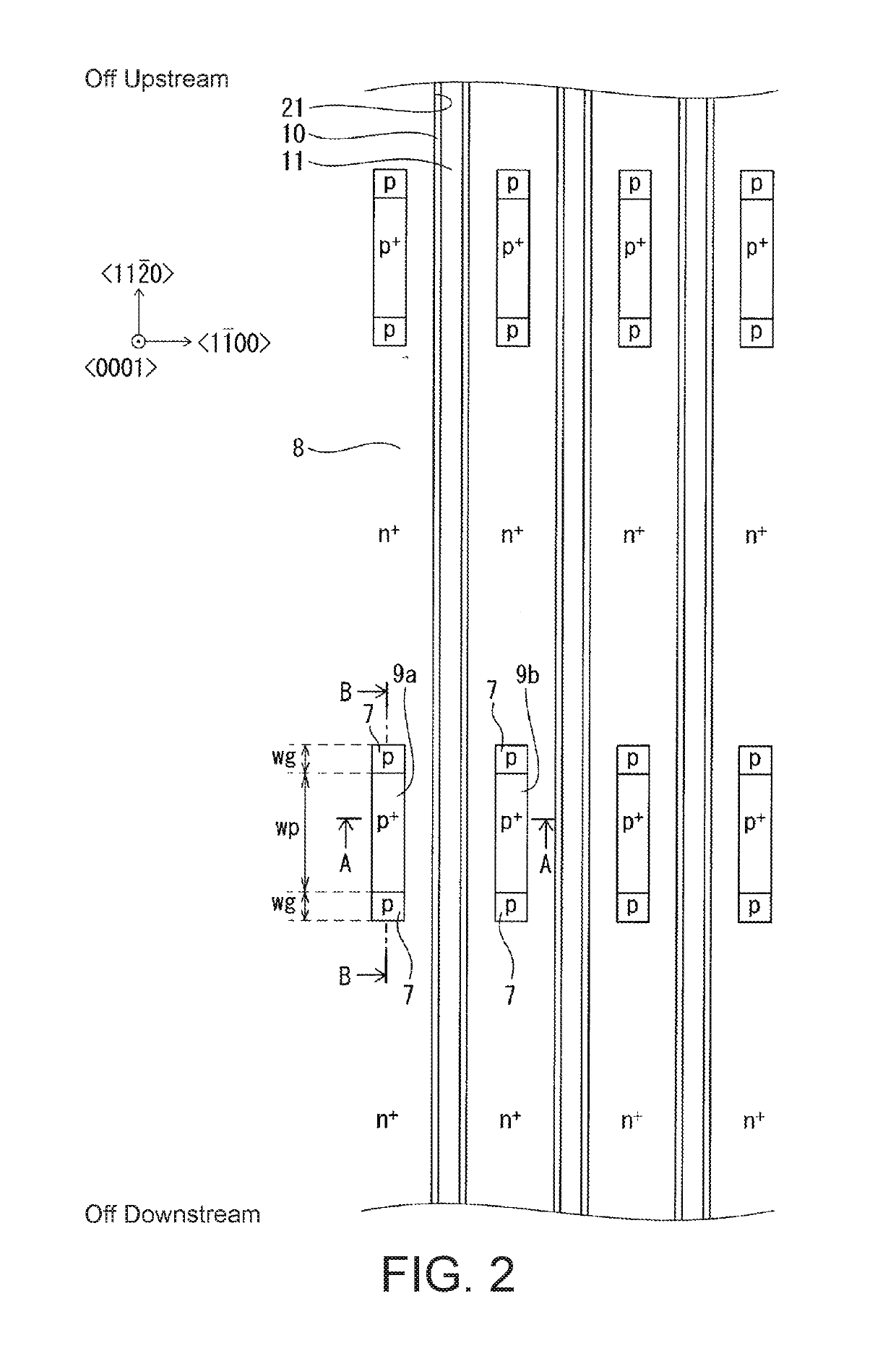

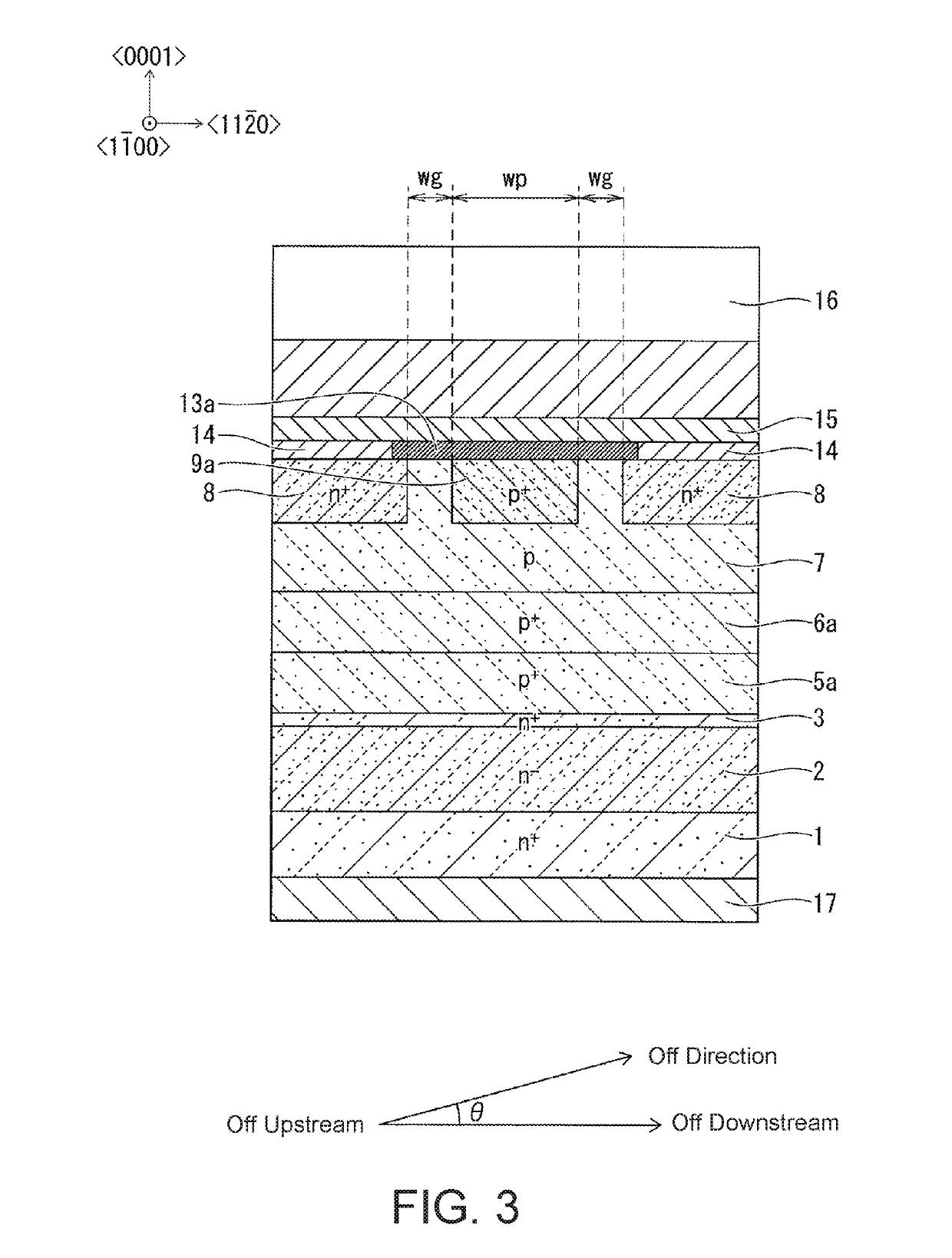

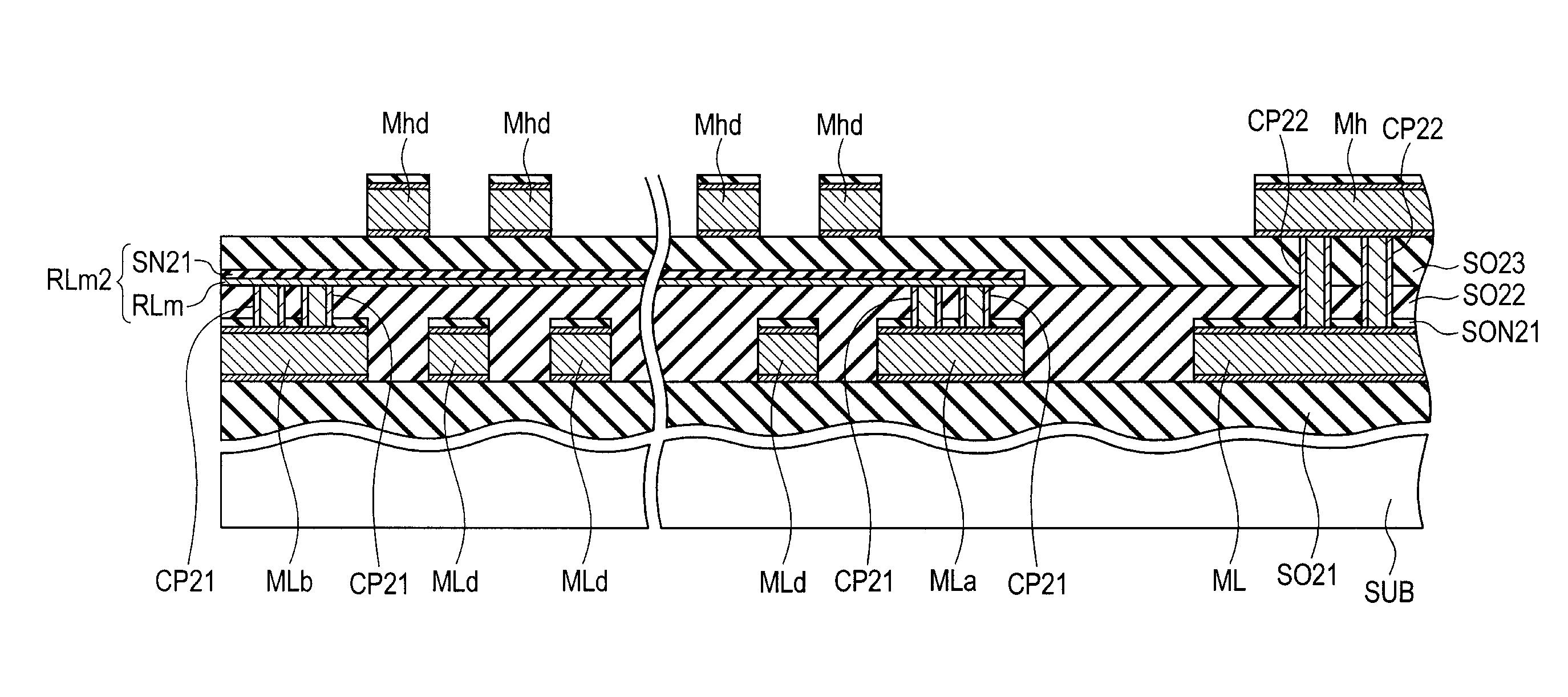

Semiconductor device and method of manufacturing same

ActiveUS20190140093A1Variation in resistanceVariation in voltageSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

This semiconductor device includes: an n-type SiC drift layer; a p-type base region; an n-type source region selectively embedded in the top part of the base region; p-type base contact regions selectively embedded in the top part of the base region so as to form a first gap with the source region along the <11-20> direction; a gate electrode provided via a gate insulating film; and an n-type drain region. The top surface of the drain region has an off-angle relative to the <11-20> direction towards the <0001> direction, and an alignment mark for positioning is formed on the top surface. The drift layer and the base region are epitaxially grown films, and a width wg of the first gap is set in accordance with a positional deviation width of the alignment mark caused by the off-angle and epitaxial growth.

Owner:FUJI ELECTRIC CO LTD

Full-bridge magnetoresistive rotation sensors and mass fabrication method

ActiveUS9116199B2Low costLarge output signalNanomagnetismMagnetic-field-controlled resistorsFull bridgePush pull

Owner:MULTIDIMENSION TECH CO LTD

Semiconductor device and method of manufacturing the same

InactiveUS20190305075A1Reduce variationAccurate voltage division ratioTransistorSemiconductor/solid-state device detailsPower semiconductor deviceEngineering

A thin film resistor includes a high-resistance region and low-resistance regions which are formed at both ends of the high-resistance region. The high-resistance region includes first high-resistance regions and a second high-resistance region, and the first high-resistance regions are formed to be in contact with both ends of the second high-resistance region formed in a rectangular shape in a transverse direction (first direction) of the second high-resistance region. In a longitudinal direction (second direction) orthogonal to the transverse direction, the first high-resistance regions have the same length as that of the second high-resistance region, and both end surfaces of the first high-resistance regions in the longitudinal direction are flush with both end surfaces of the second high-resistance region in the longitudinal direction to form flat planes.

Owner:ABLIC INC

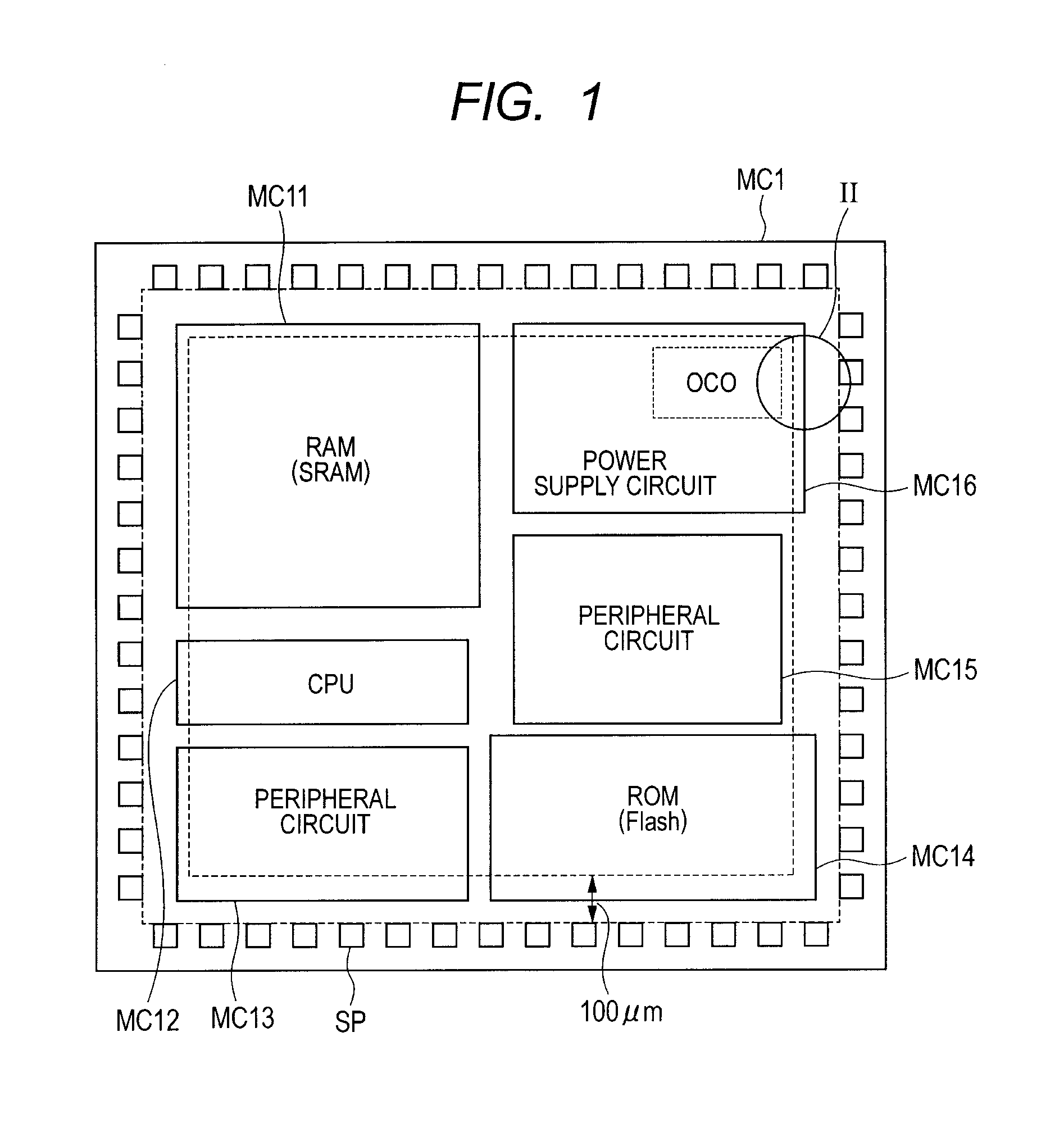

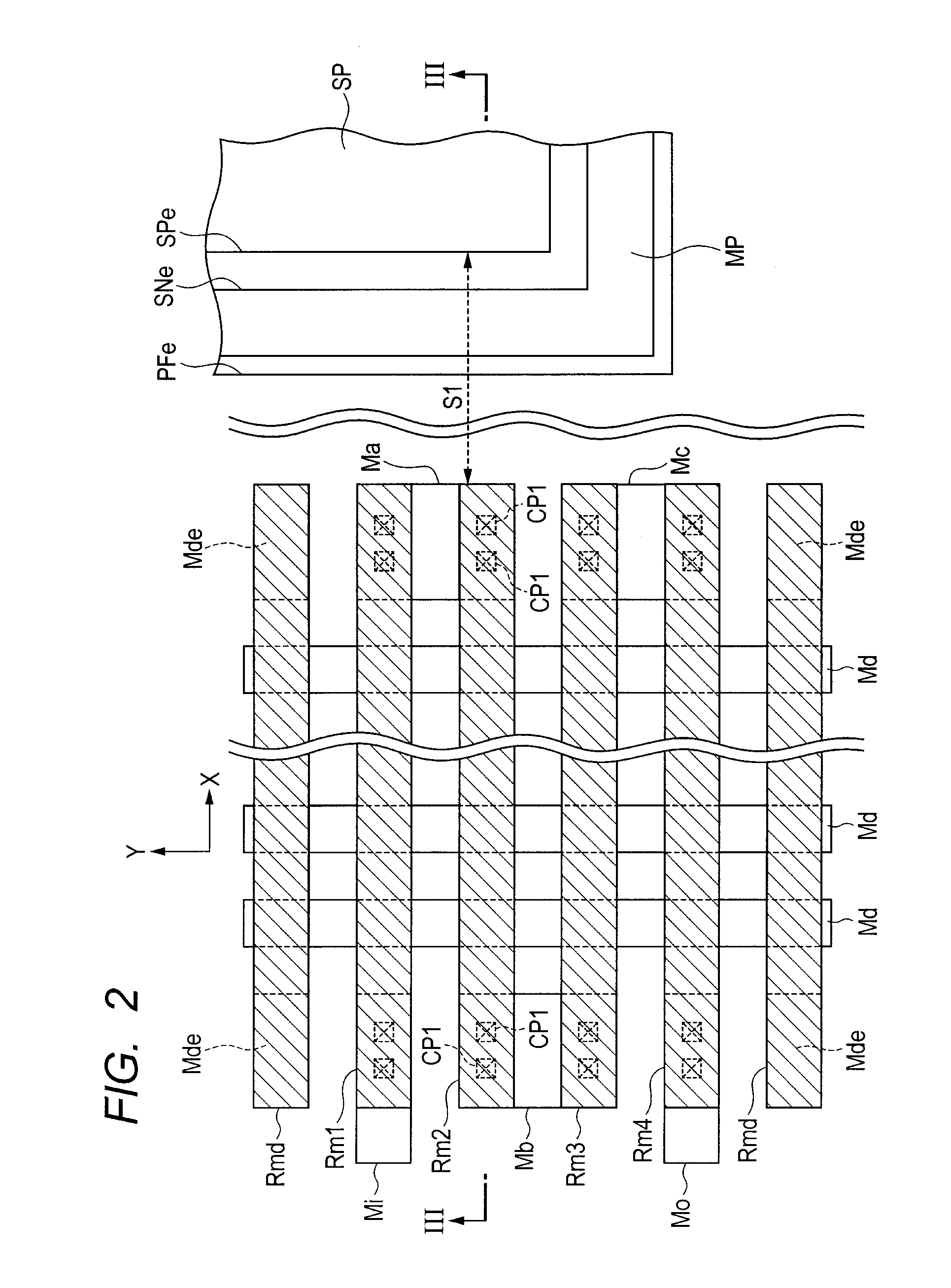

Semiconductor device and manufacturing method thereof

ActiveUS8659122B2Variation in resistanceSemiconductor/solid-state device detailsSolid-state devicesLevel aluminumEngineering

To provide a semiconductor device having a structure free from variations in resistance even when a stress is applied thereto; and a manufacturing method of the device. The semiconductor device has a metal resistor layer in a region between a passivation film and an uppermost level aluminum interconnect. This makes it possible to realize a high-precision resistor having few variations in resistance due to a mold stress that occurs in a packaging step or thereafter and therefore, makes it possible to form a high-precision analog circuit.

Owner:RENESAS ELECTRONICS CORP

Non-reciprocal circuit device

A non-reciprocal circuit device includes a ferrite arranged to receive a direct-current magnetic field from a permanent magnet, a first central electrode and a second central electrode arranged on the ferrite. The non-reciprocal circuit device further includes matching capacitors and a terminating resistor. When high frequency signals flow in a reverse direction, power consumption at the first central electrode is increased by decreasing an equivalent parallel resistance Rp of the first central electrode, in relation to power consumption at the terminating resistor.

Owner:MURATA MFG CO LTD

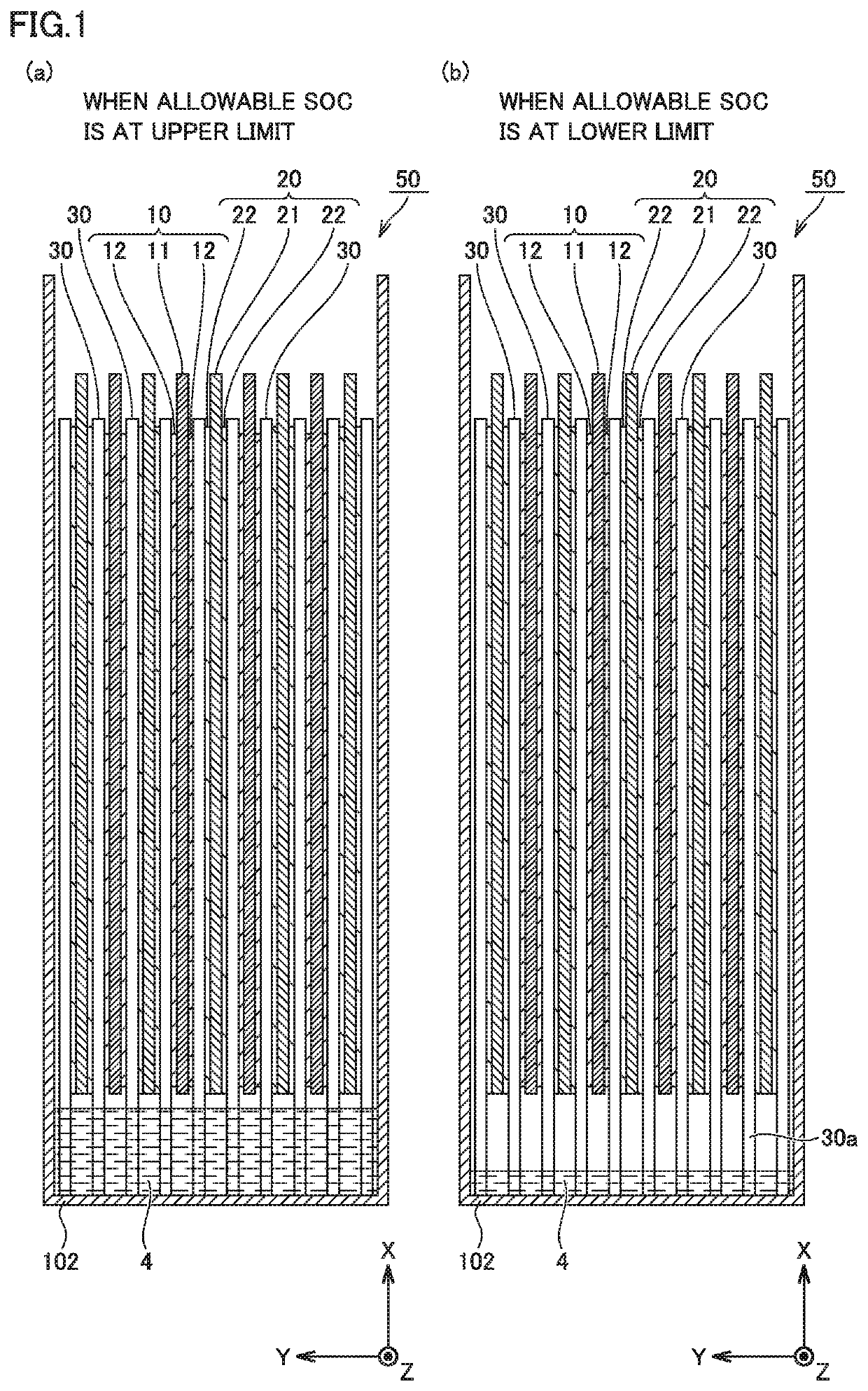

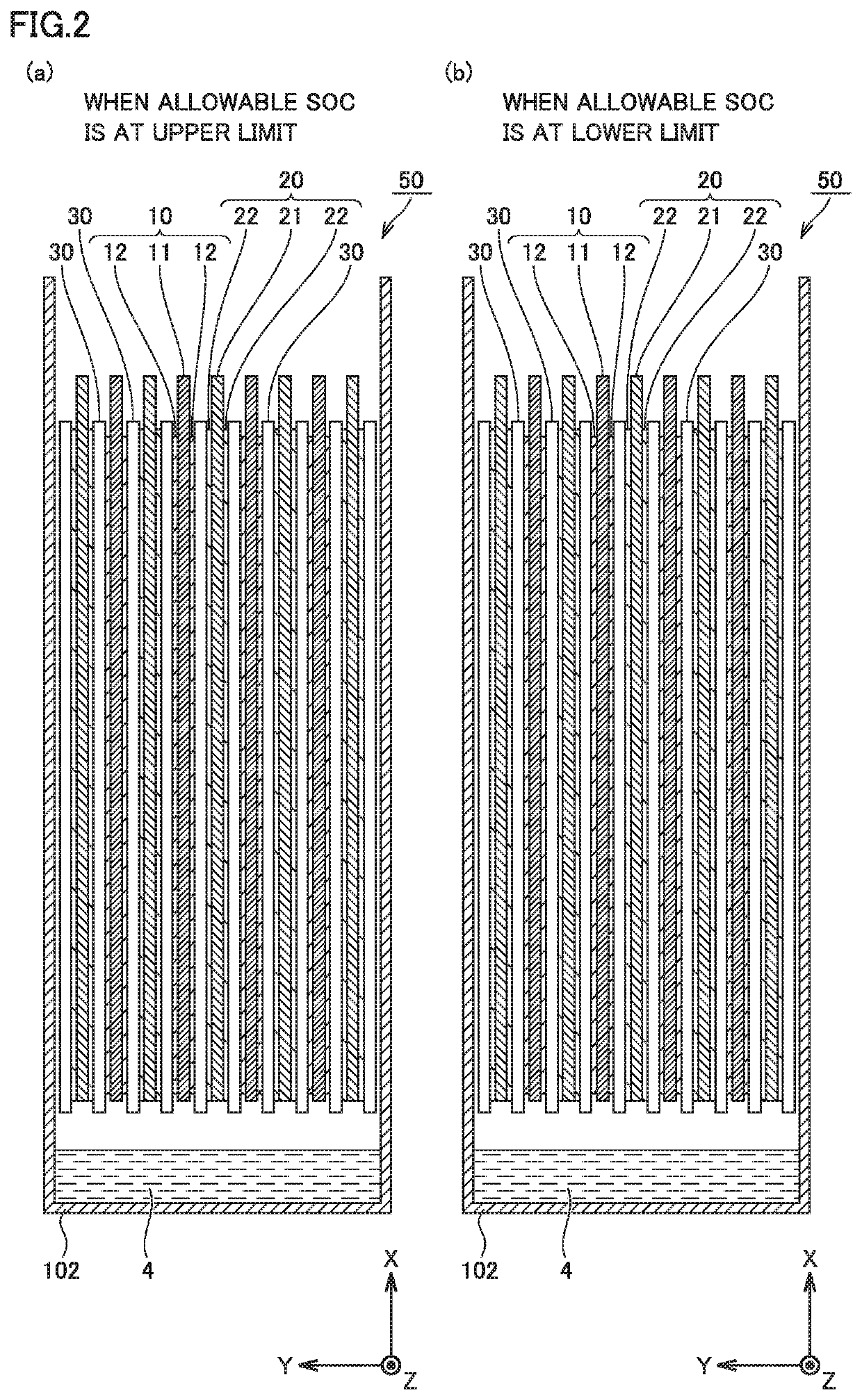

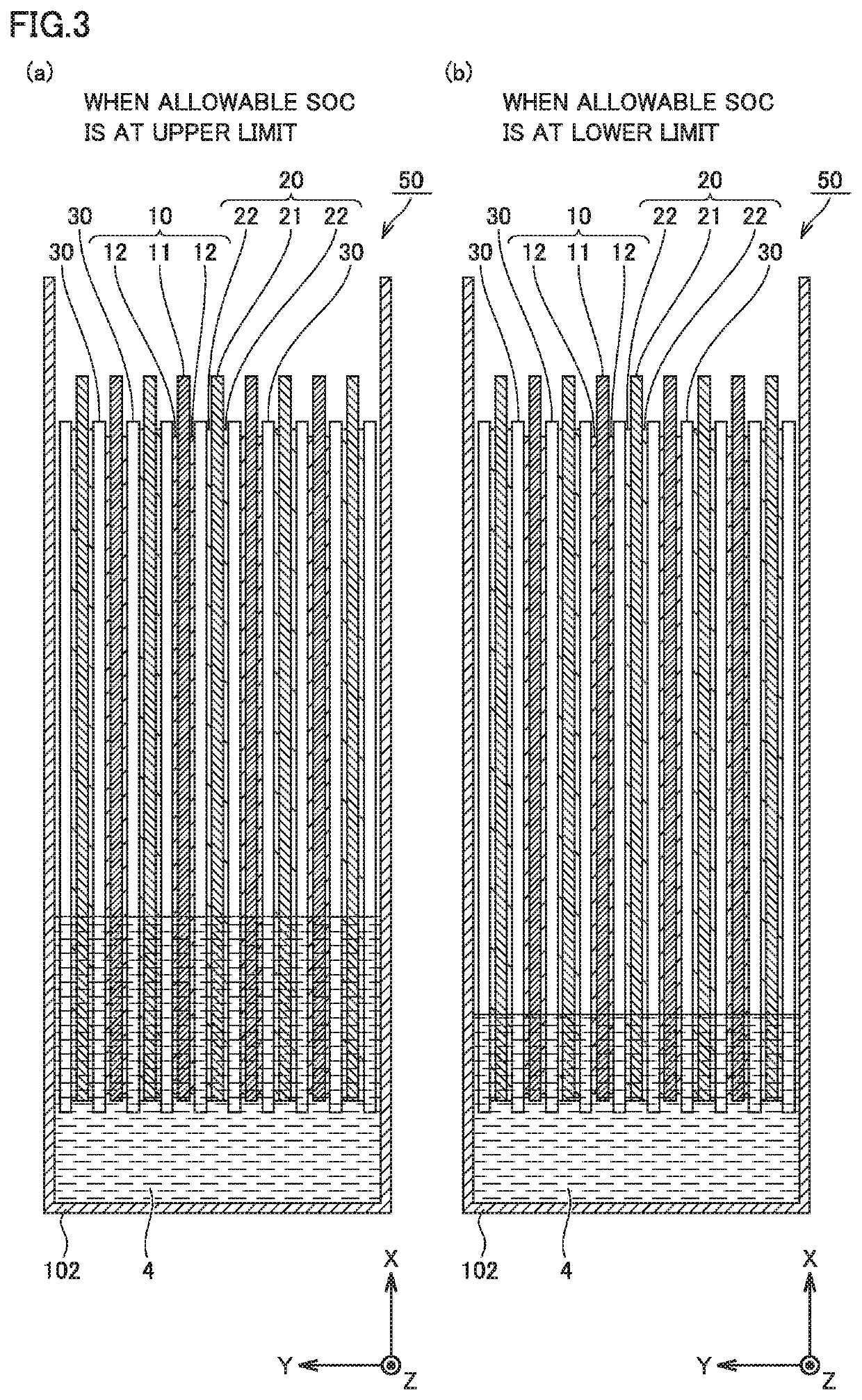

Non-aqueous electrolyte secondary battery

ActiveUS10797355B2Increase resistanceSuppression of variation in resistance of an electrodeLarge-sized flat cells/batteriesFinal product manufactureState of chargeEngineering

A non-aqueous electrolyte secondary battery includes a housing, a stack-type electrode array accommodated in the housing, and an electrolyte solution. The electrolyte solution includes an infiltrated portion infiltrated into the stack-type electrode array and an excess portion other than the infiltrated portion. In a set-up state that the non-aqueous electrolyte secondary battery is arranged such that a direction of stack of the stack-type electrode array is orthogonal to a vertical direction, a lower end of the separator projects below lower ends of the positive electrode and the negative electrode. In the set-up state, within a range of an operating state of charge, a projecting portion of any of the plurality separators is always in contact with the excess portion and the plurality of positive electrodes and the plurality of negative electrodes are not in contact with the excess portion at any time.

Owner:TOYOTA JIDOSHA KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com