Patents

Literature

114results about How to "Prevent electromigration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

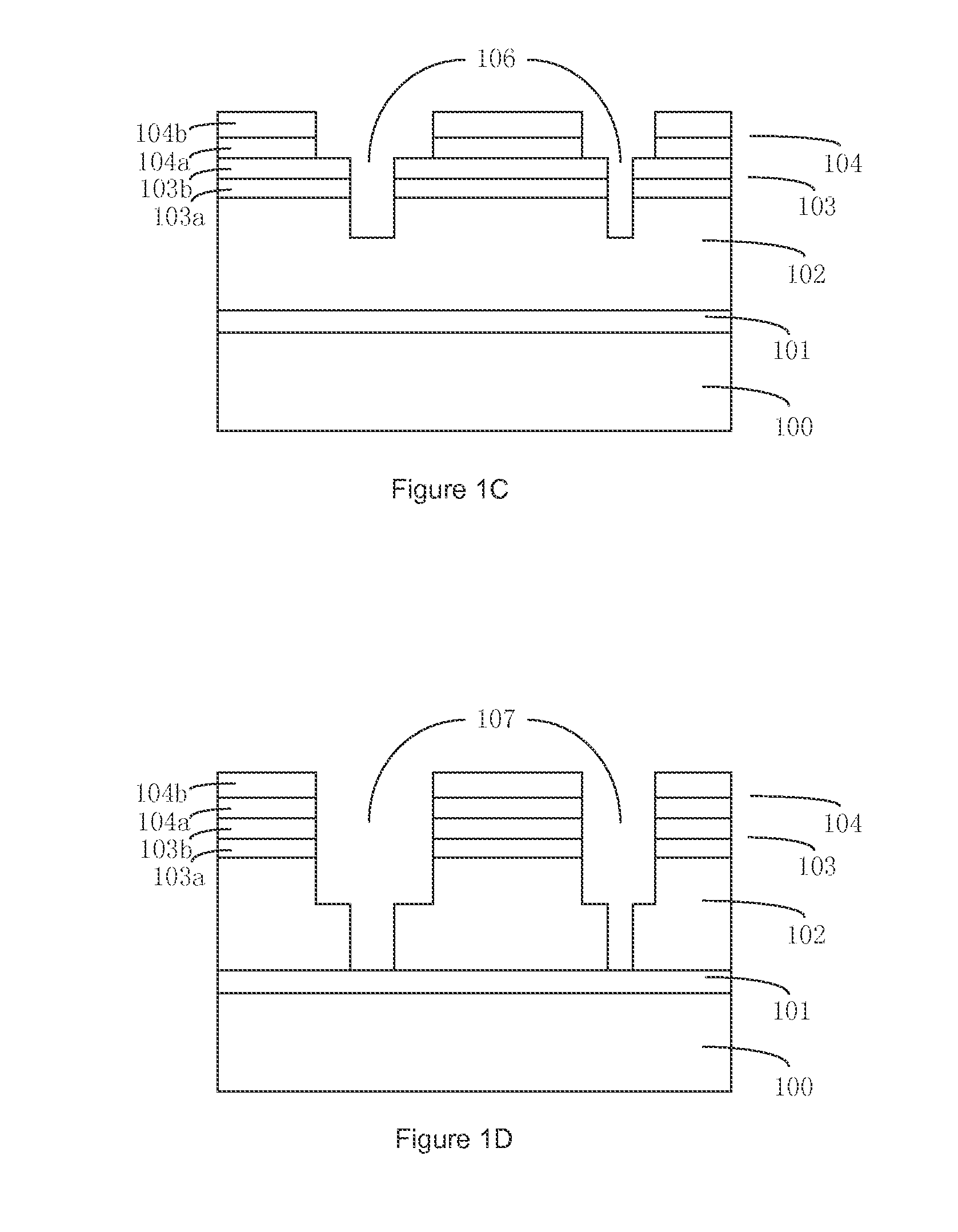

Light-emitting semiconductor device

ActiveUS7291865B2Inhibit interface reactionReduce the driving voltageSolid-state devicesSemiconductor/solid-state device manufacturingContact layerLight emitting device

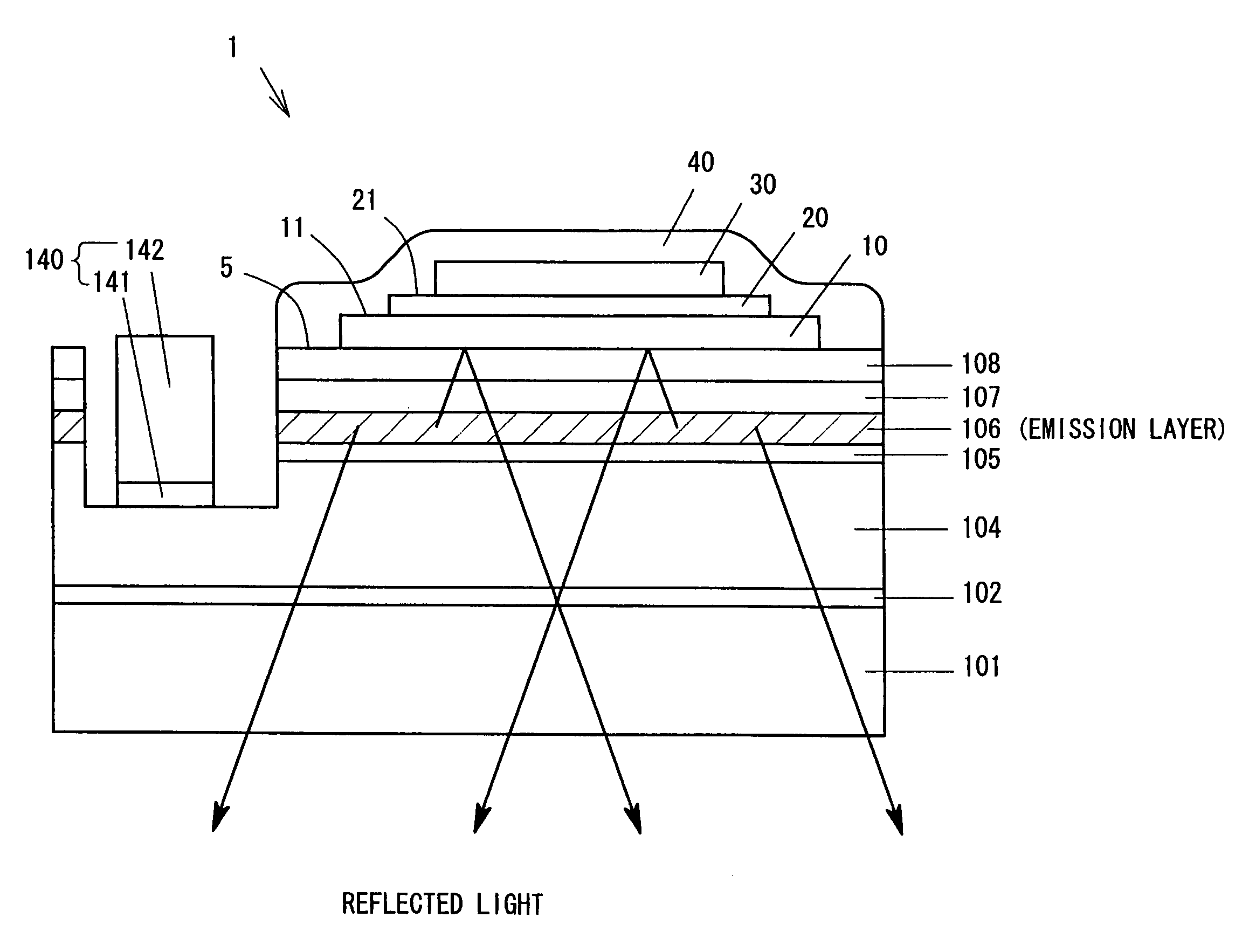

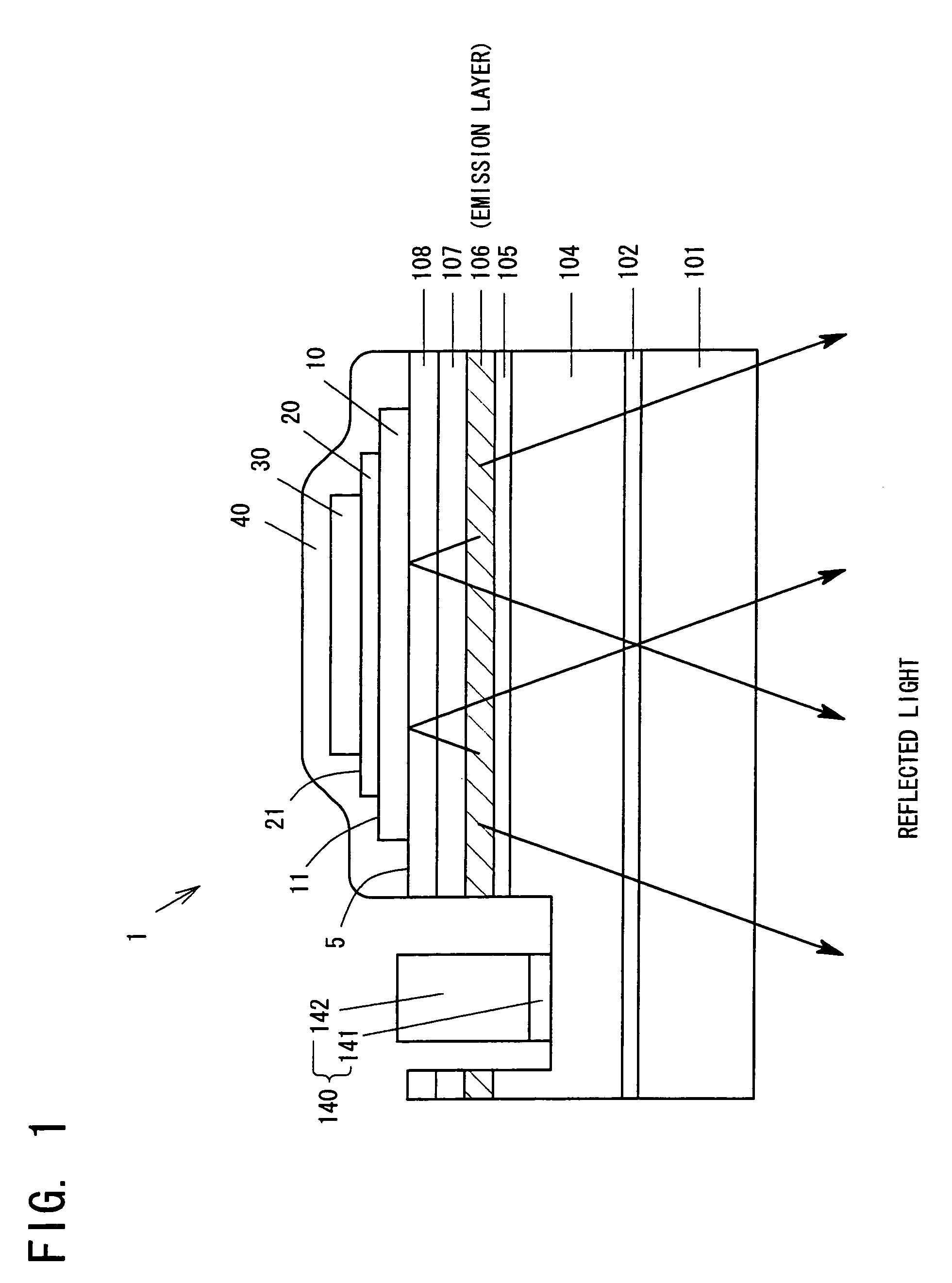

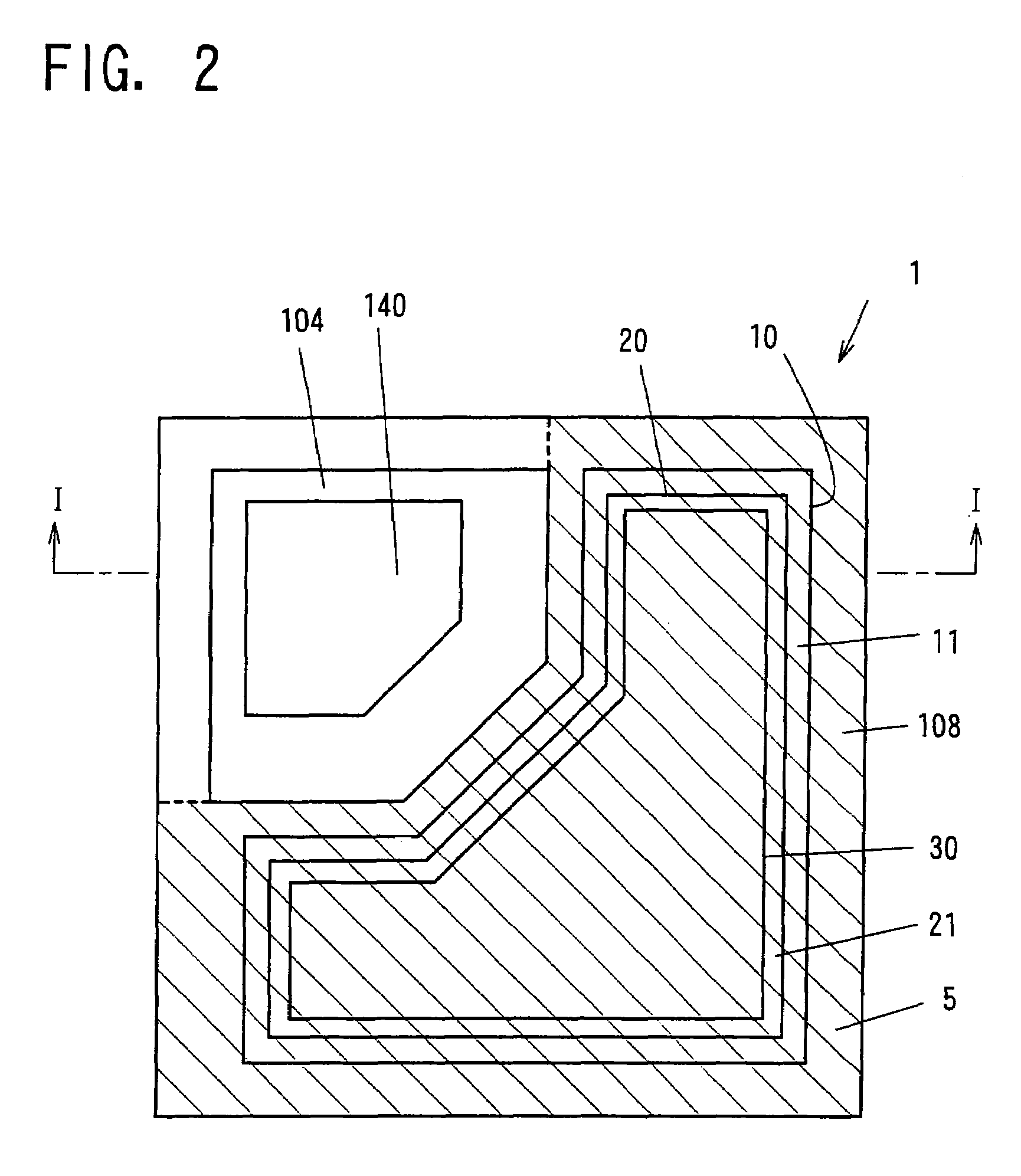

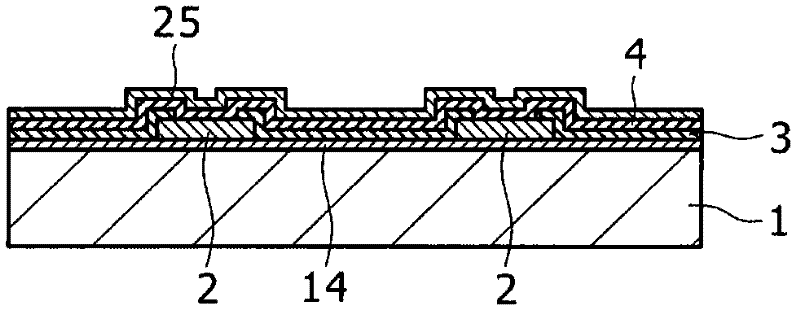

A flip-chip type of Group III nitride based compound semiconductor light-emitting device comprises a transparent conductive film 10 made of ITO on a p-type contact layer. On the transparent conductive film, an insulation protection film 20, a reflection film 30 which is made of silver (Ag) and aluminum (Al) and reflects light to a sapphire substrate side, and a metal layer 40 made of gold (Au) are deposited in sequence. Because the insulation protection film 20 exists between the transparent conductive film 10 and the reflection film 30, metal atoms comprised in the reflection film 30 can be prevented from diffusing in the transparent conductive film 10. That enables the transparent conductive film 10 to maintain high transmissivity. As a result, a light-emitting device having high external quantum efficienty can be provided.

Owner:TOYODA GOSEI CO LTD

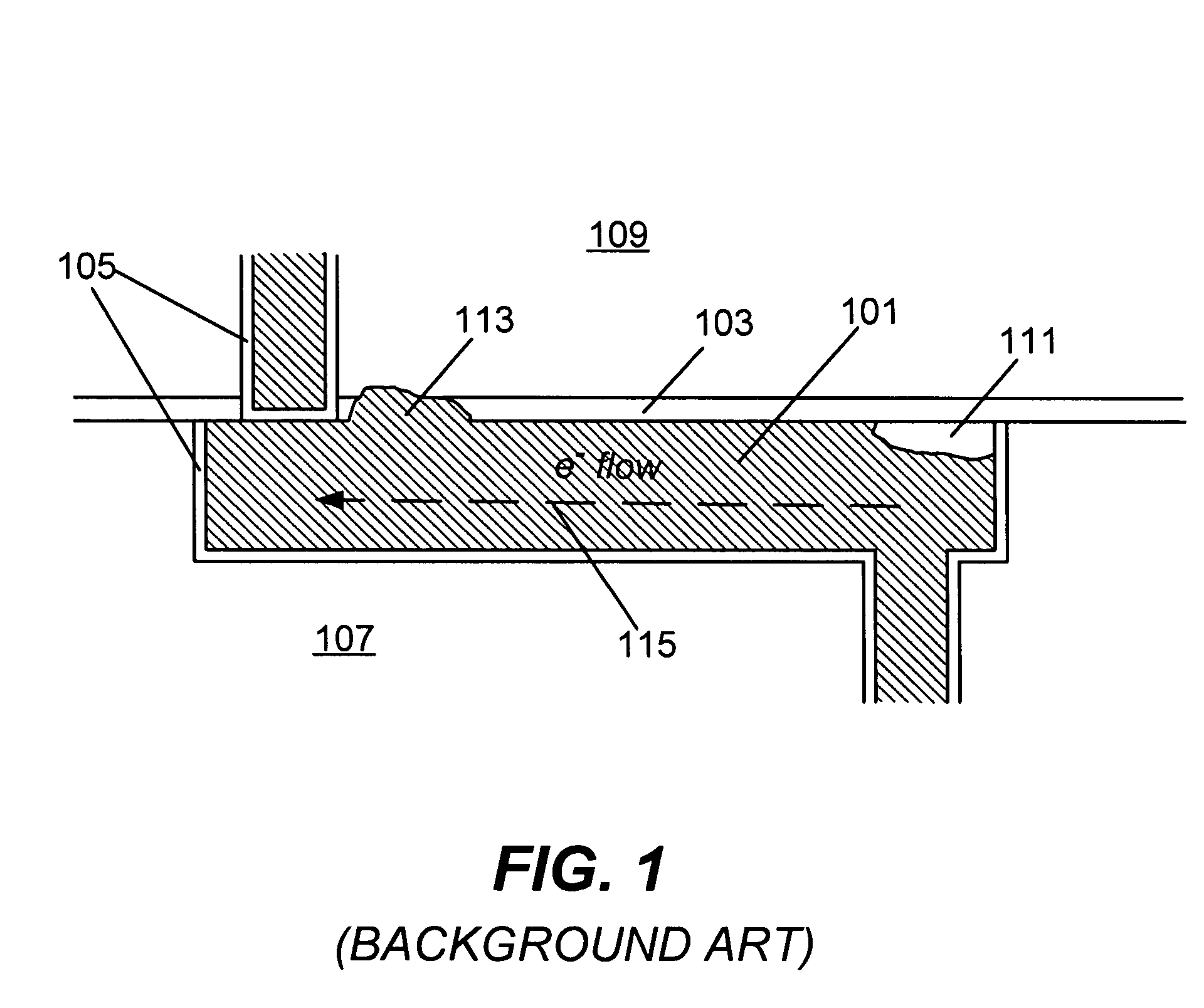

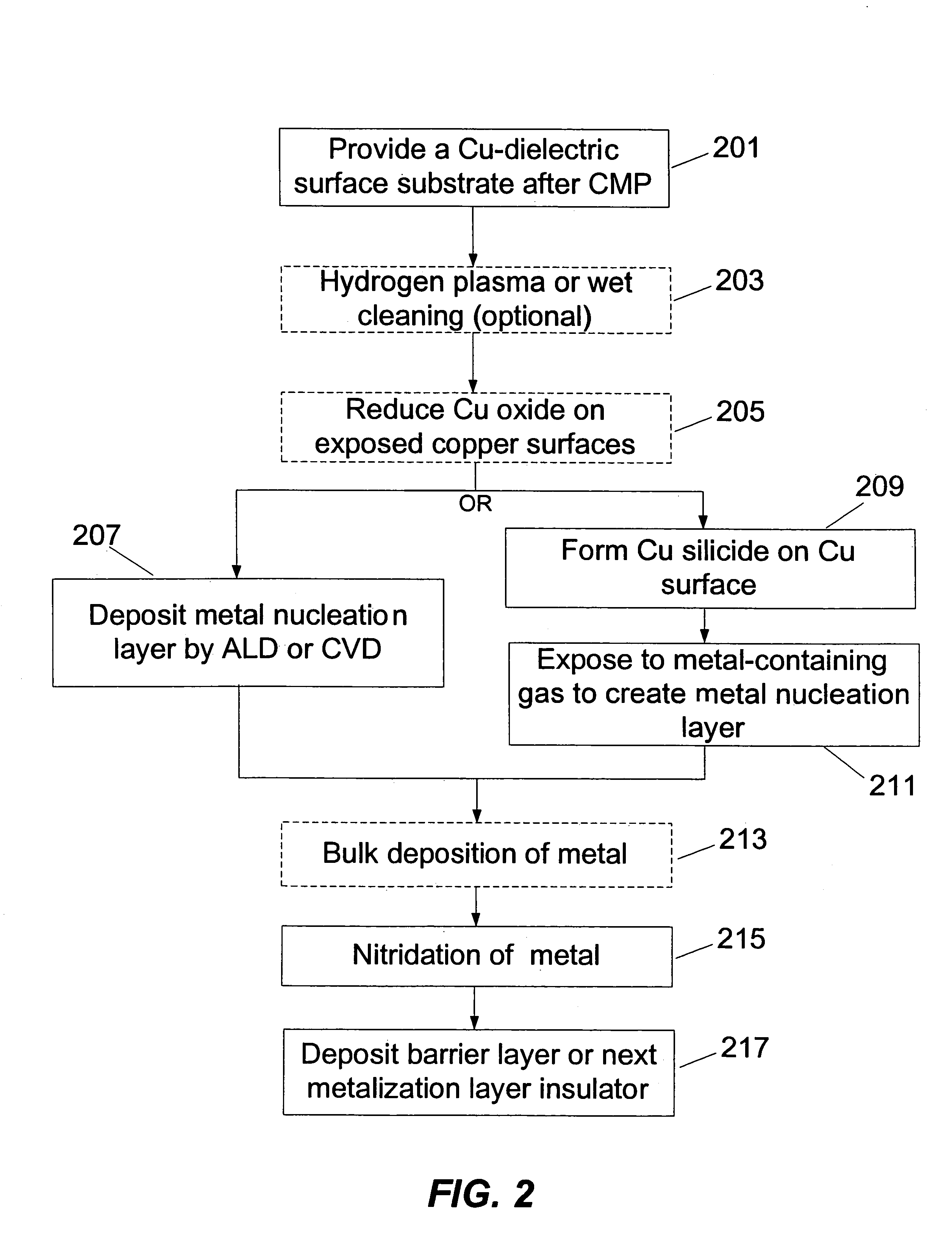

Selective refractory metal and nitride capping

InactiveUS7157798B1Inhibited DiffusionPrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesNucleationCopper

A method for creating a refractory metal and refractory metal nitride cap effective for reducing copper electromigration and copper diffusion is described. The method includes depositing a refractory metal nucleation layer and nitriding at least the upper portion of the refractory metal layer to form a refractory metal nitride. Methods to reduce and clean the copper lines before refractory metal deposition are also described. Methods to form a thicker refractory metal layer using bulk deposition are also described.

Owner:NOVELLUS SYSTEMS

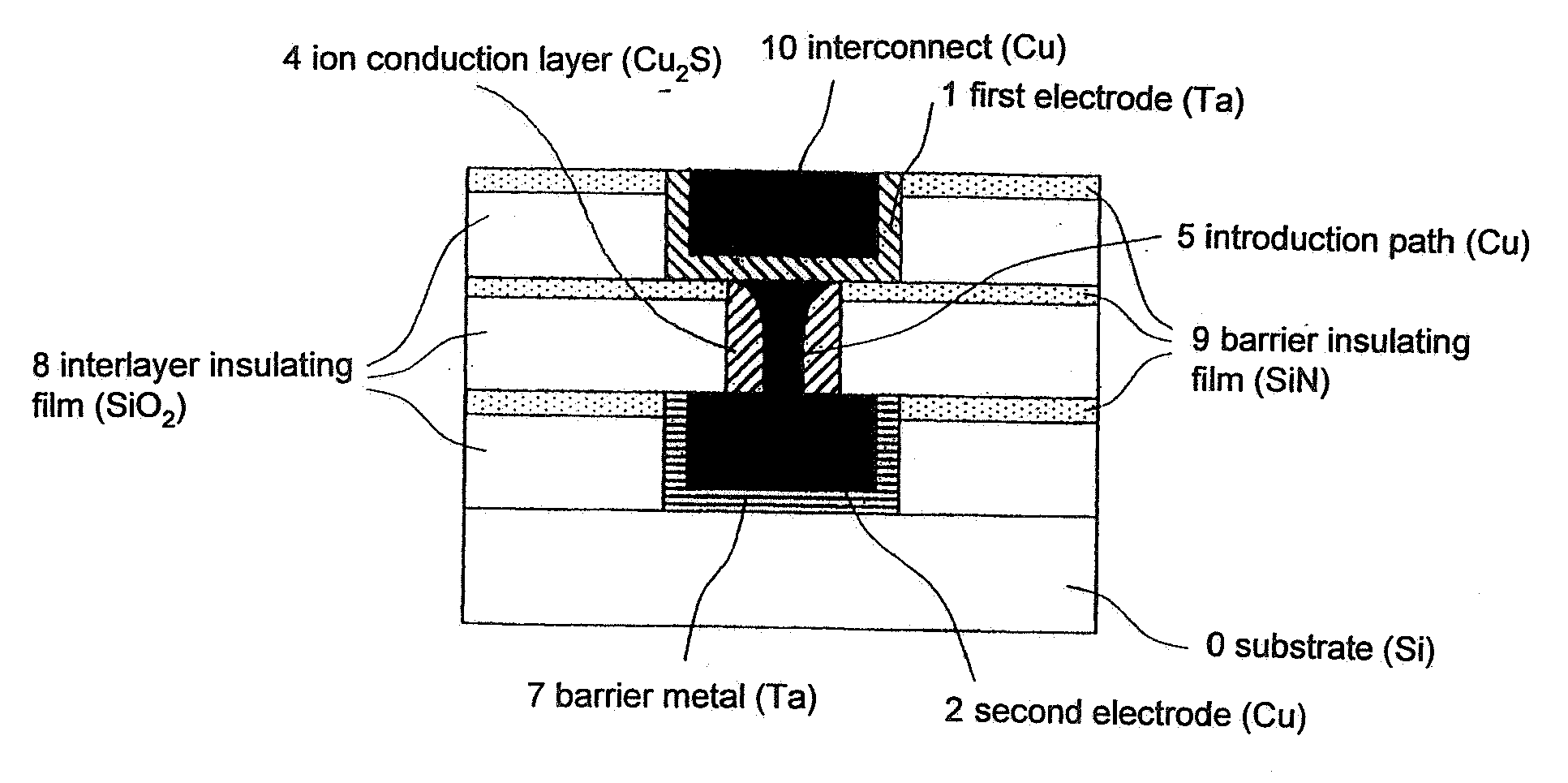

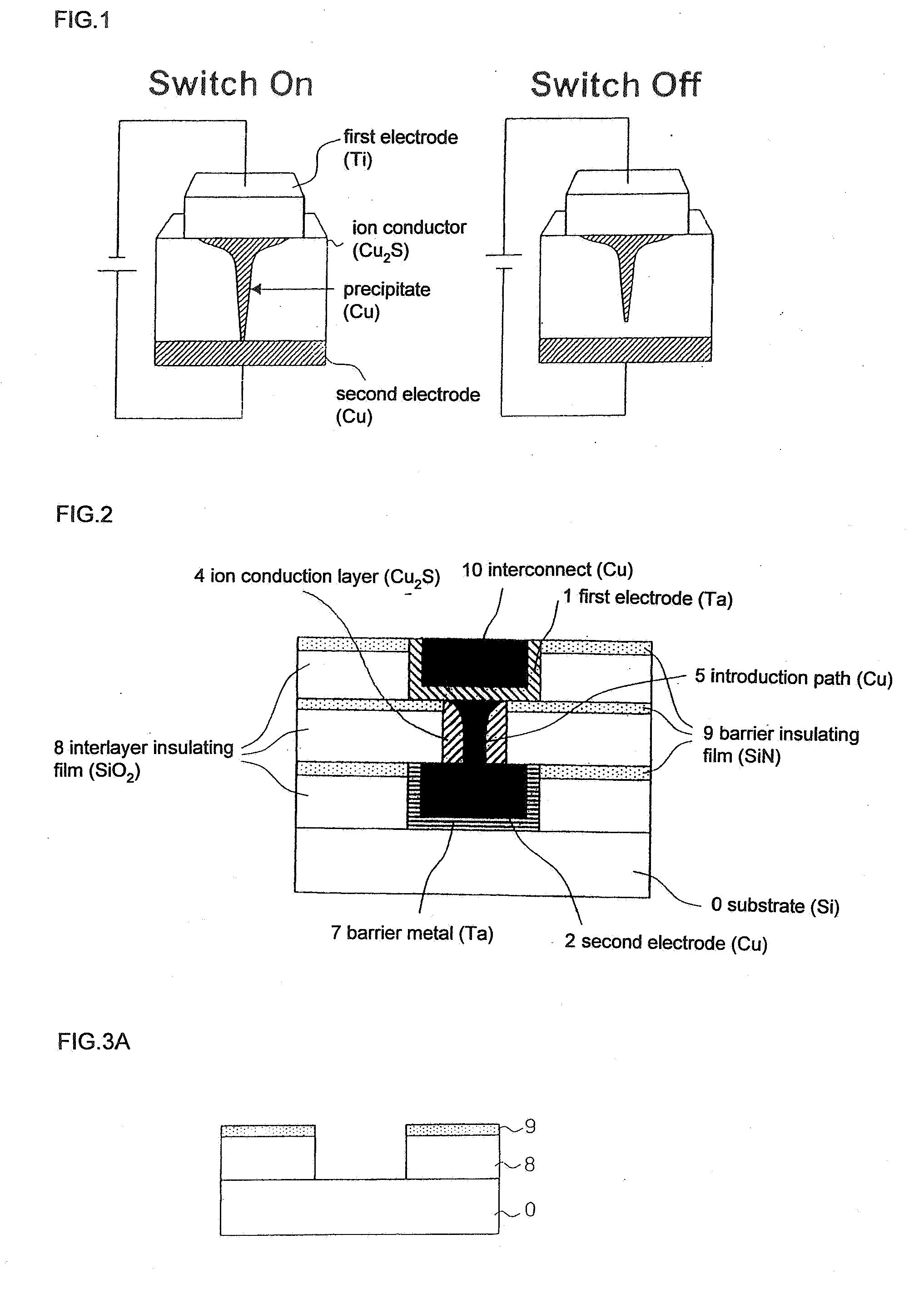

Switching Element, Switching Element Drive Method and Fabrication Method, Reconfigurable Logic Integrated Circuit, and Memory Element

ActiveUS20080036508A1Variation in resistanceIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesIonIntegrated circuit

The switching element of the present invention includes: an ion conduction layer (4) in which metal ions can move freely; a first electrode (1) that contacts the ion conduction layer (4); and a second electrode (2) that contacts the ion conduction layer (4), that is formed such that the ion conduction layer (4) is interposed between the first electrode (1) and the second electrode (2), and that supplies metal ions to the ion conduction layer (4) or that receives metal ions from the ion conduction layer (4) to cause precipitation of the metal that corresponds to the metal ions. An introduction path (5) composed of the metal and of a prescribed width is further provided on the ion conduction layer (4) for electrically connecting the first electrode (1) and the second electrode (2). The application of voltage to the first electrode (1) relative to the second electrode (2) then causes an electrochemical reaction between the introduction path (5) and the second electrode (2) whereby the electrical characteristics are switched.

Owner:NEC CORP

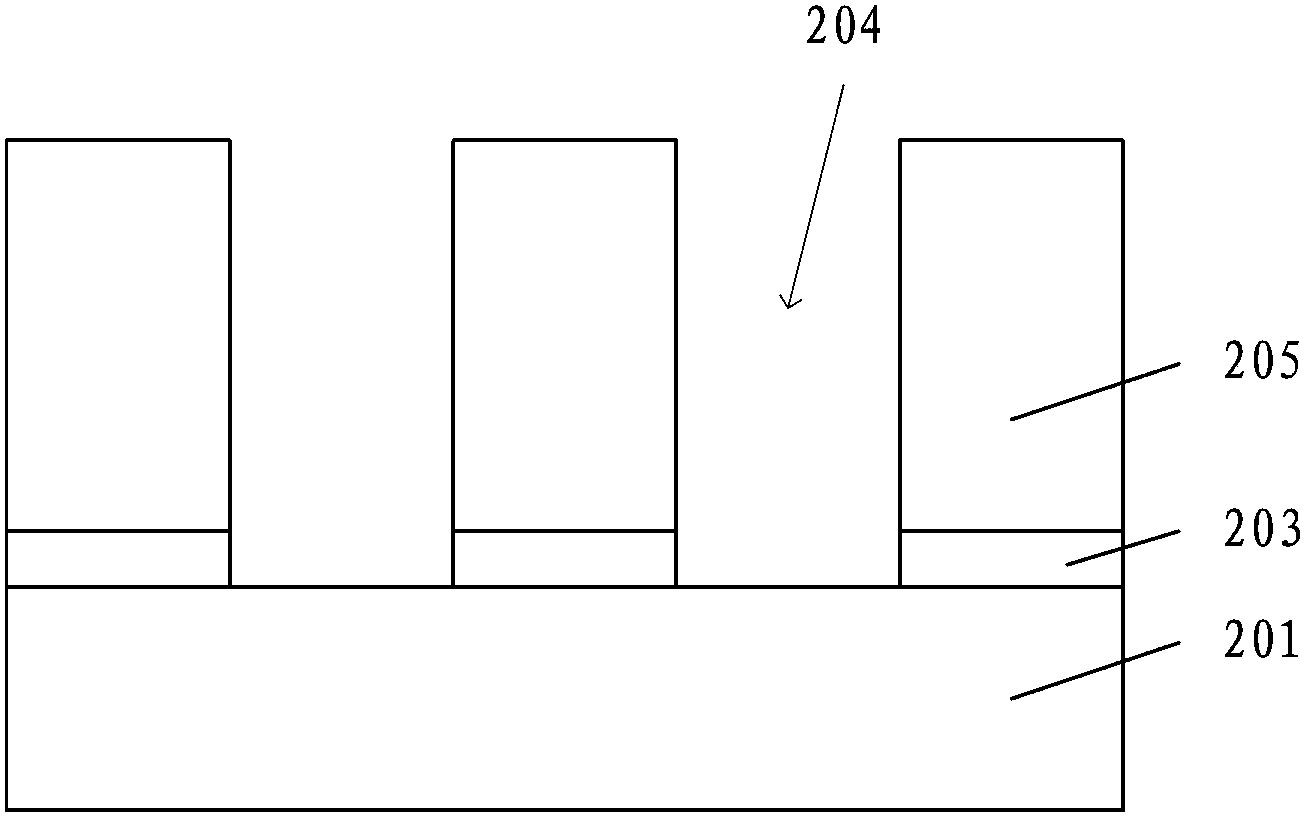

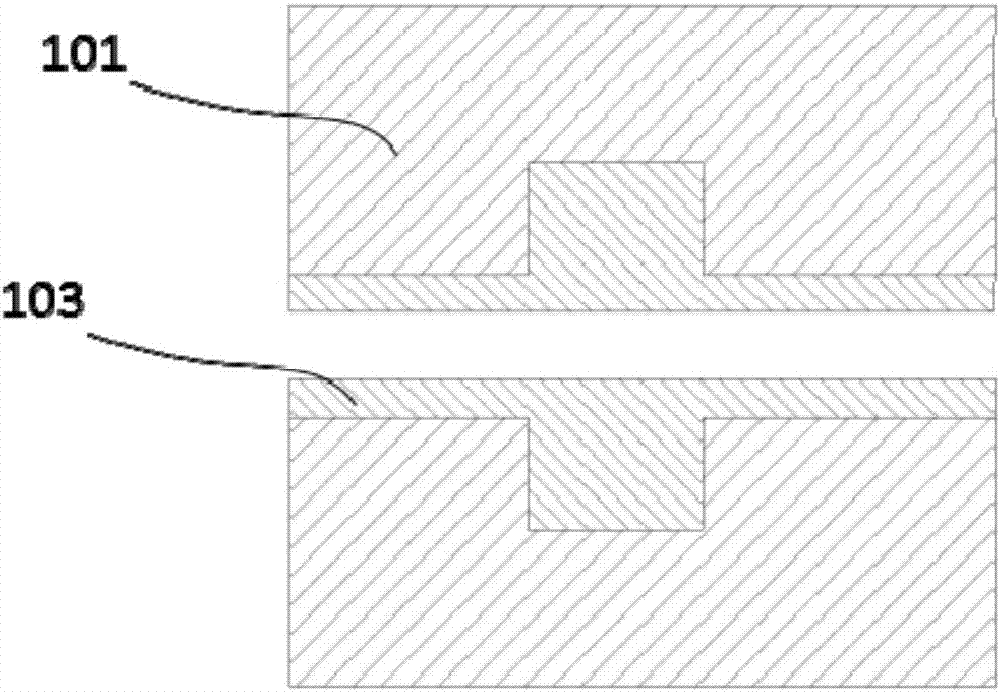

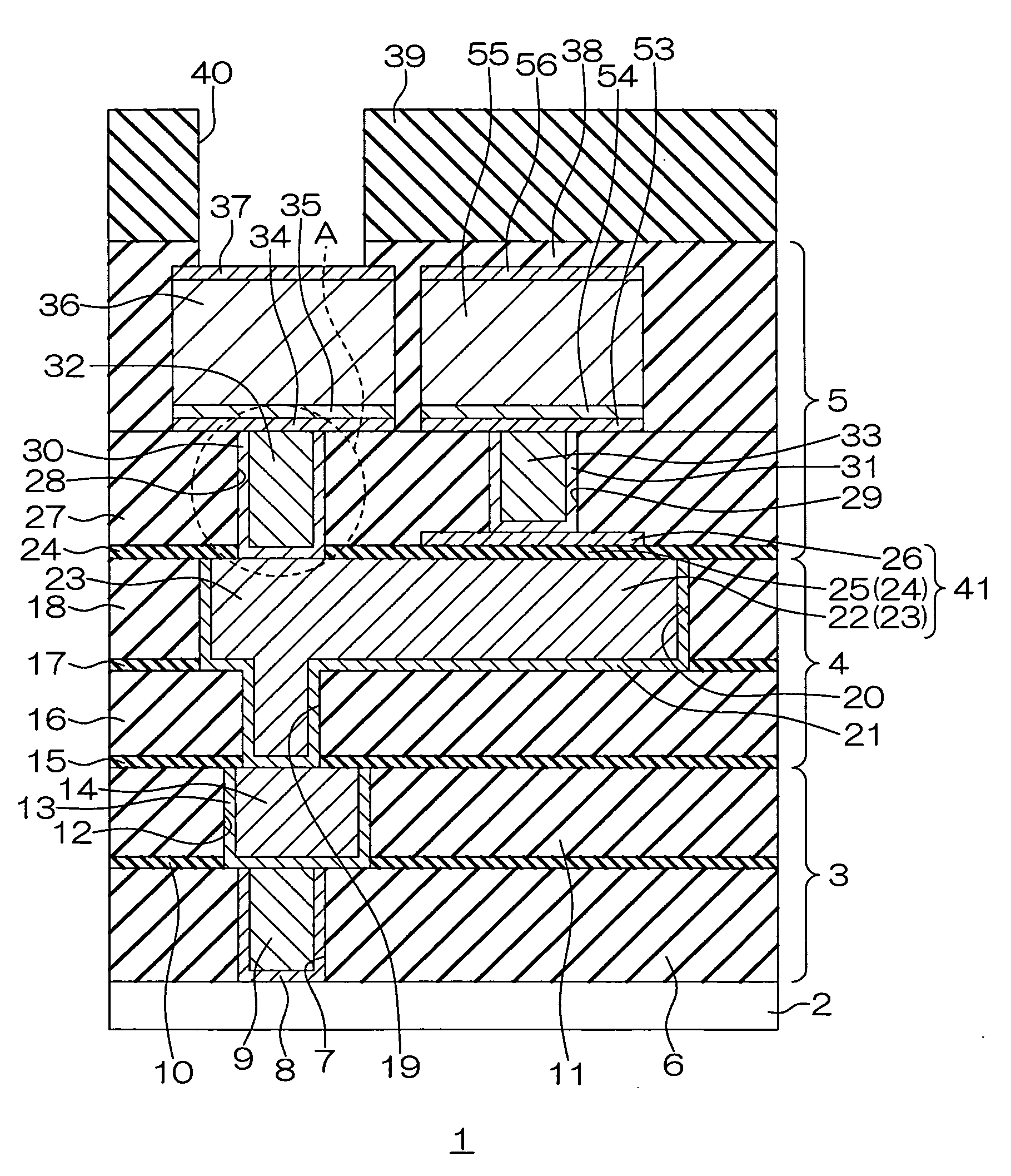

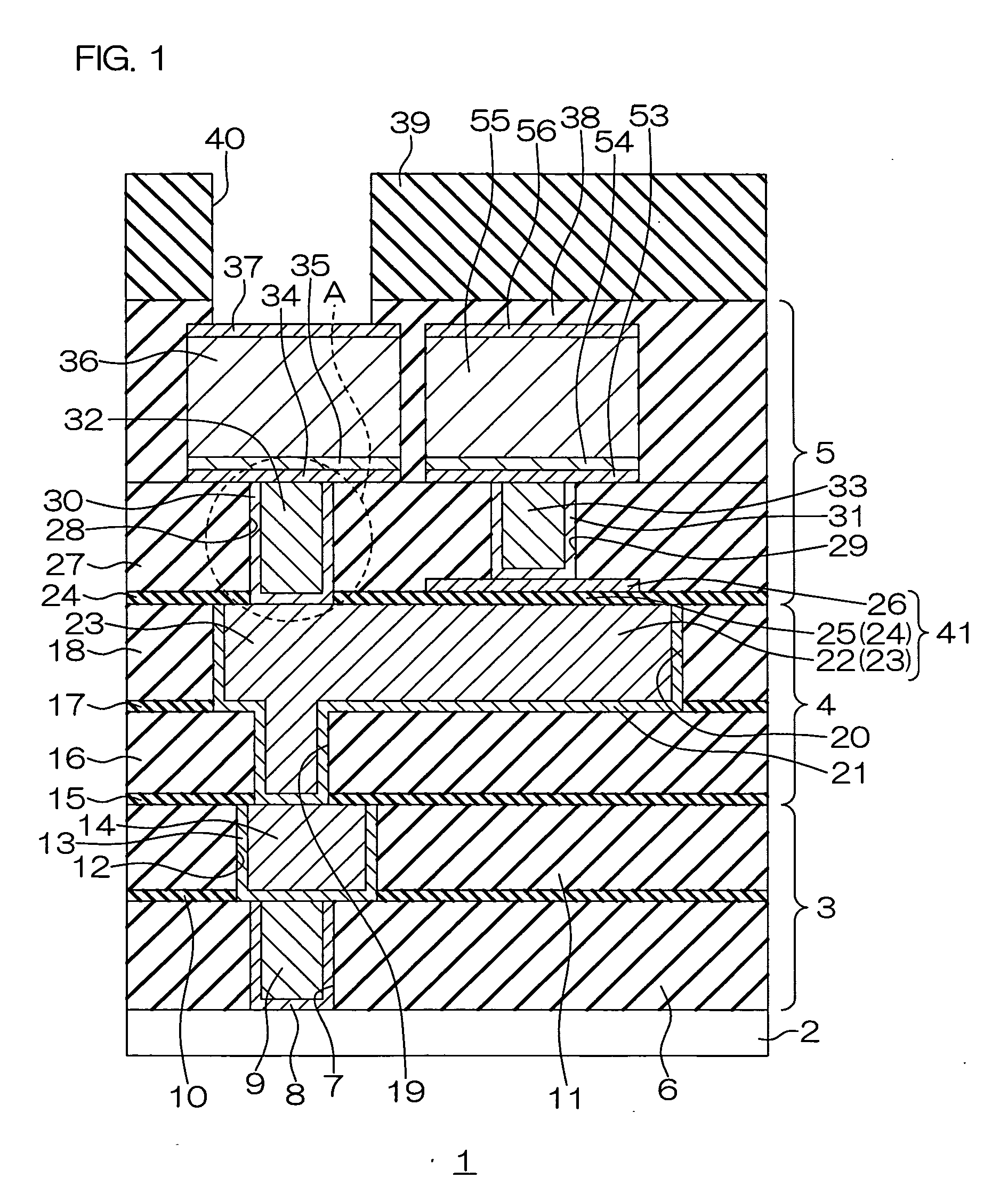

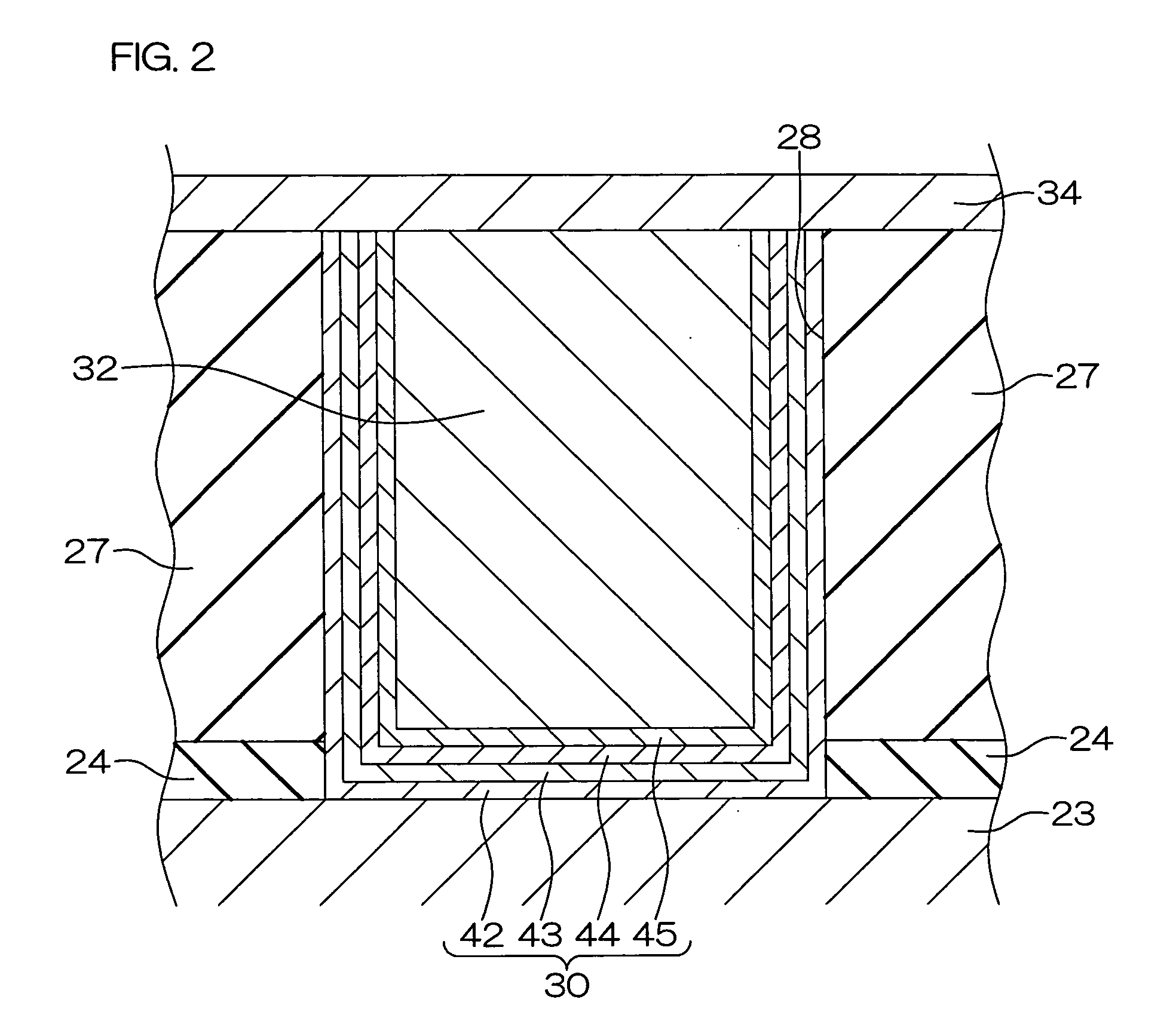

Semiconductor device having a leading wiring layer

InactiveUS7091616B2High reliabilityPrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

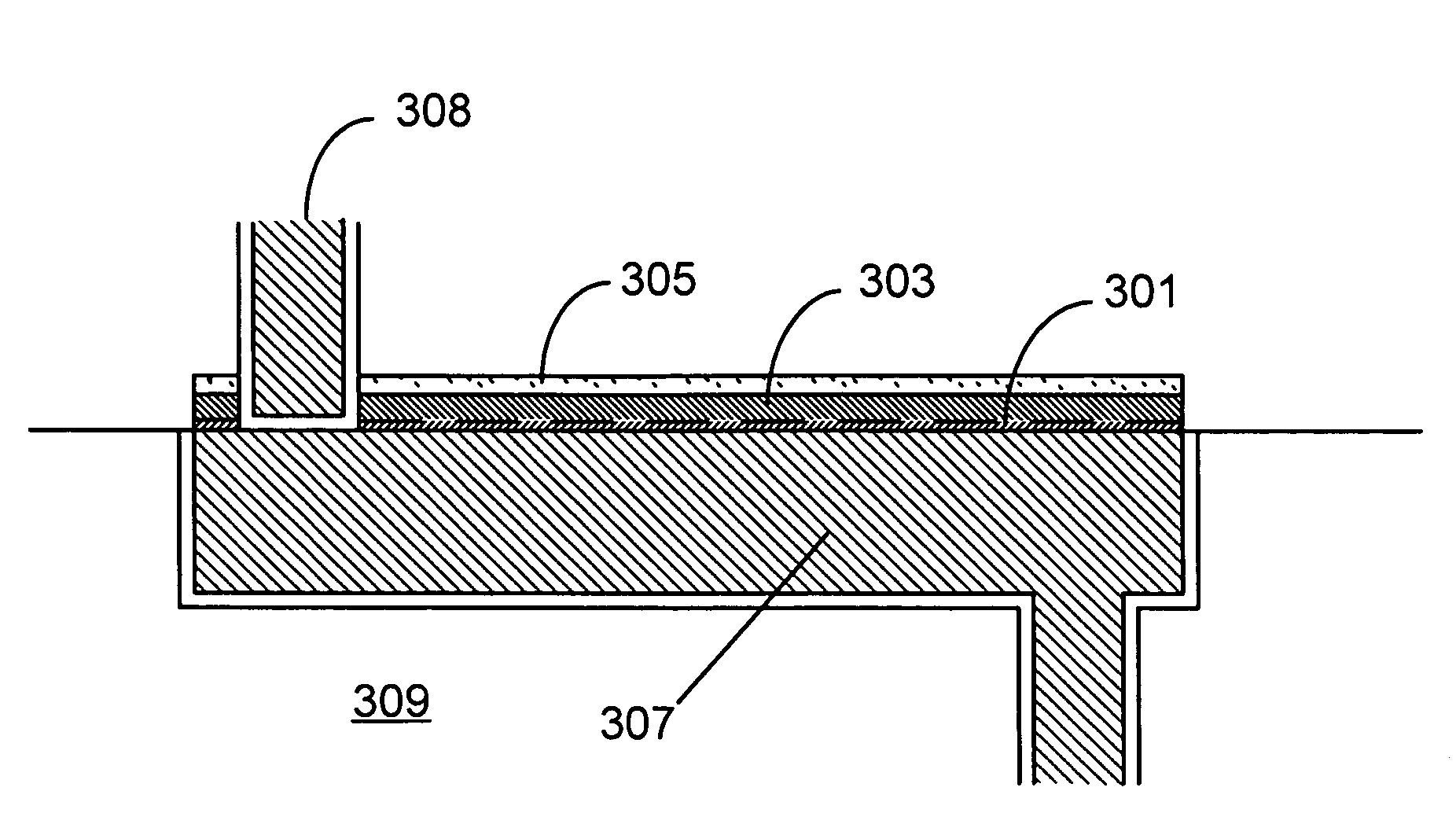

A leading wiring layer is provided with a main conductor layer, a first barrier metal layer for covering bottom and side surfaces of the main conductor layer, and a second barrier metal layer for covering a top surface of the main conductor layer. This ensures the respective barrier metal layers to cover entire surroundings including the side, bottom and top surfaces of the main conductor layer.

Owner:SHARP KK

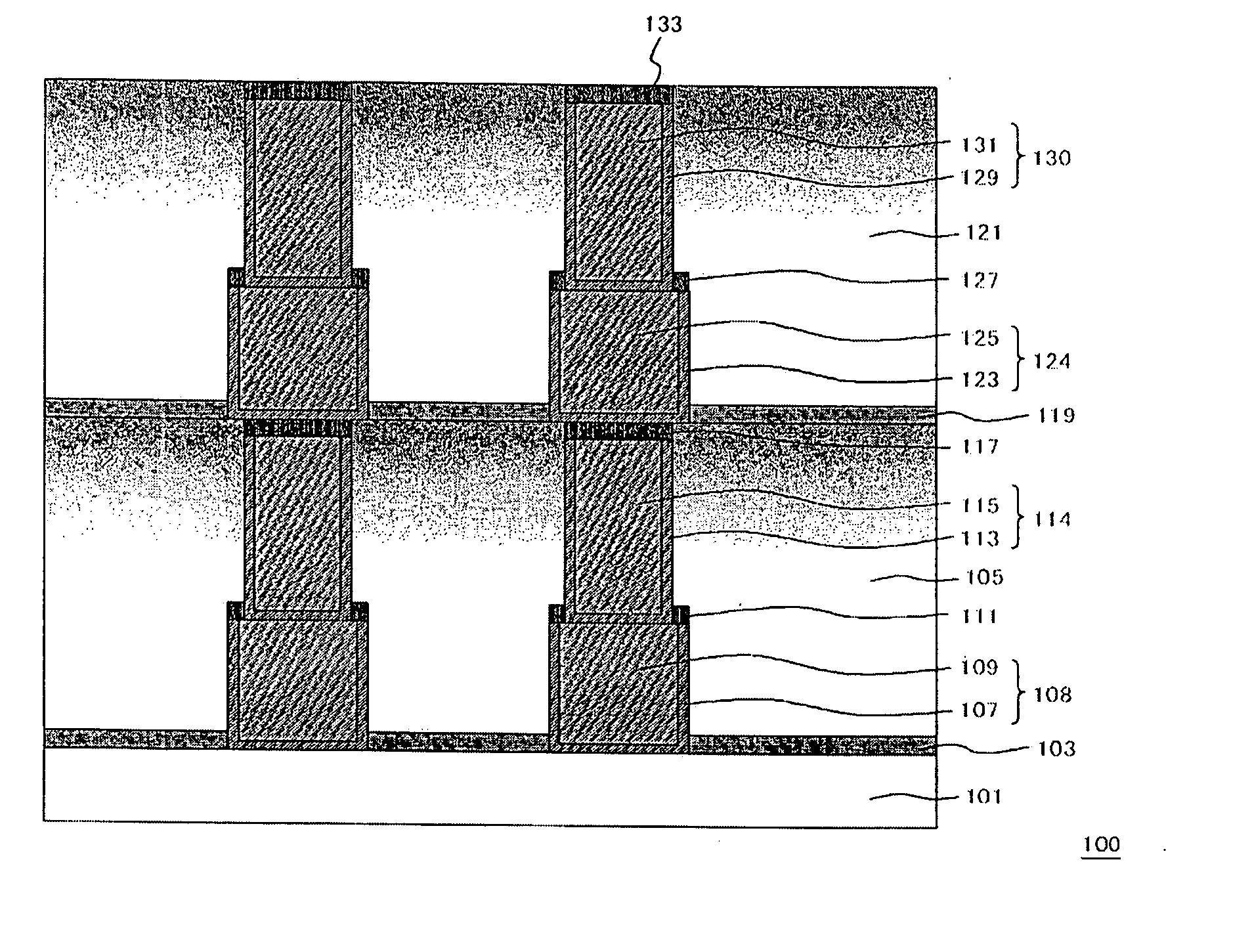

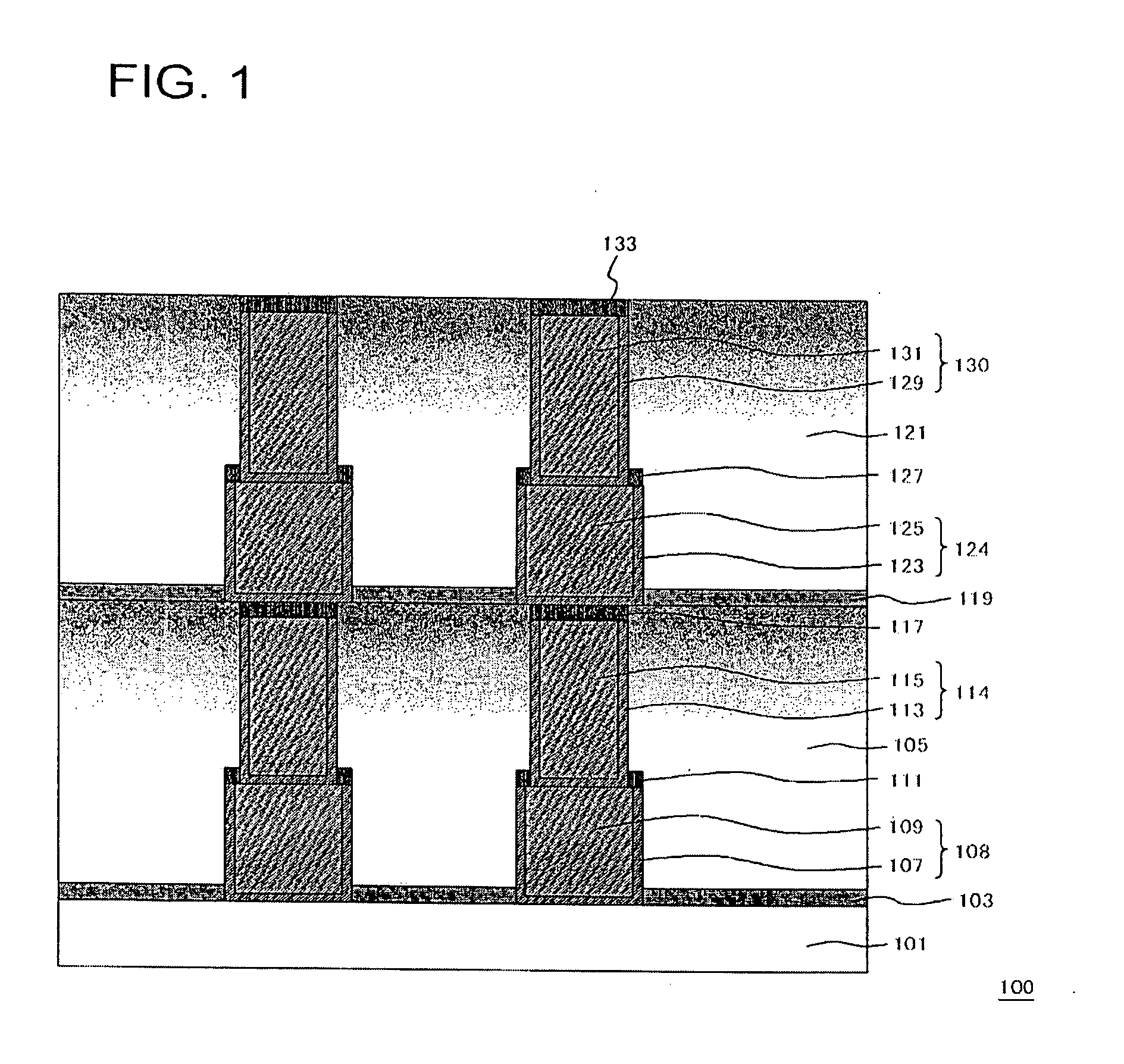

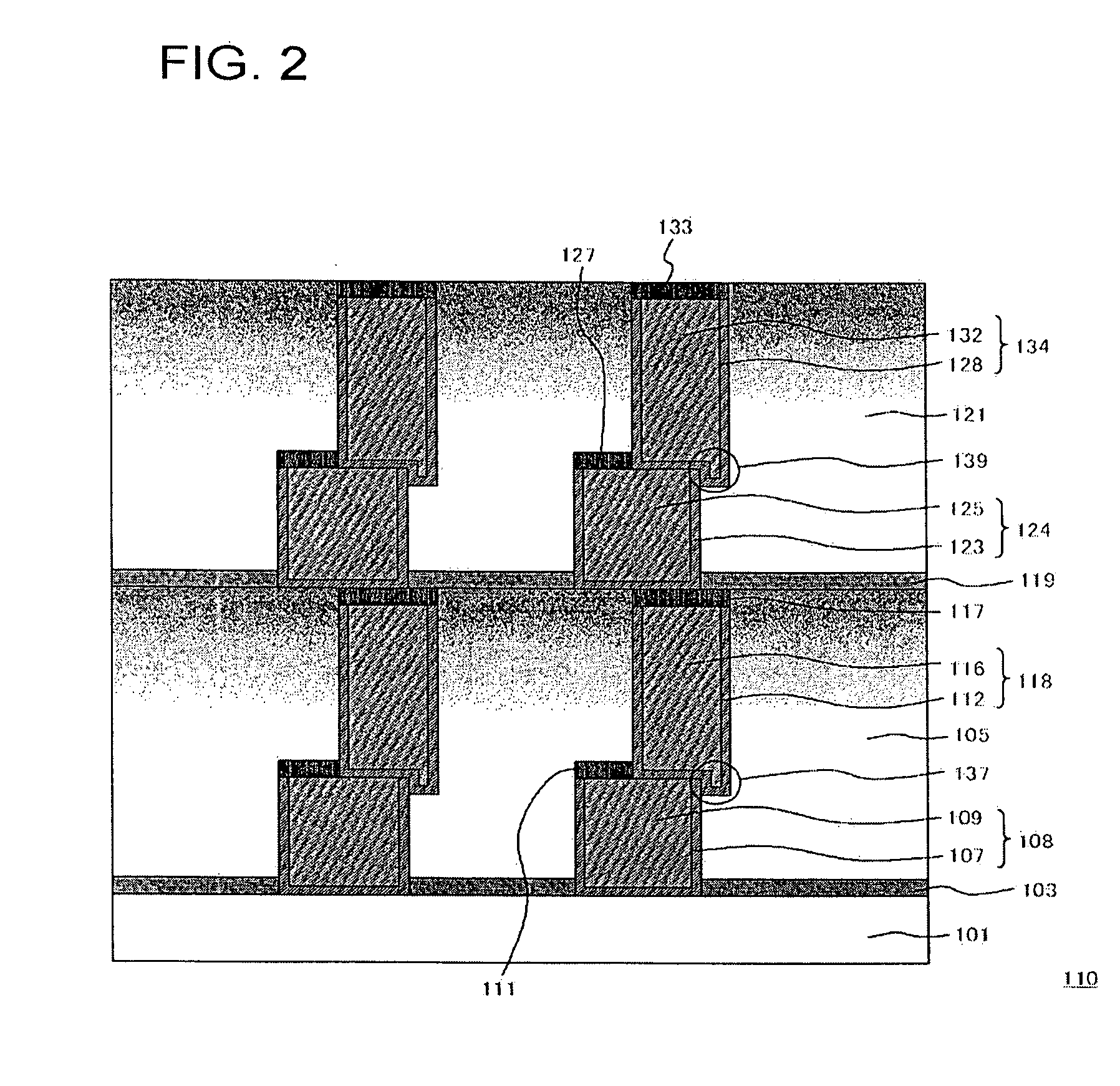

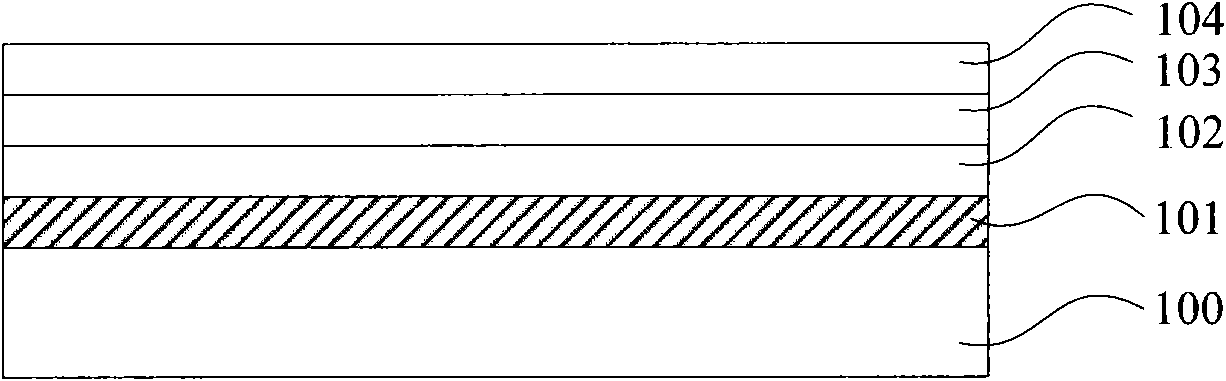

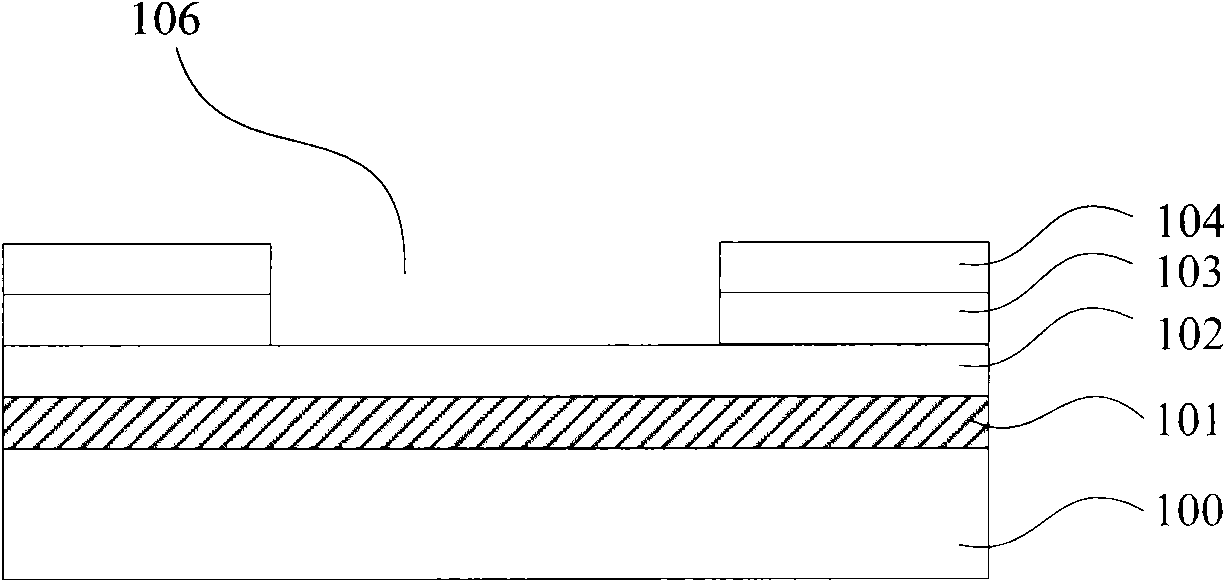

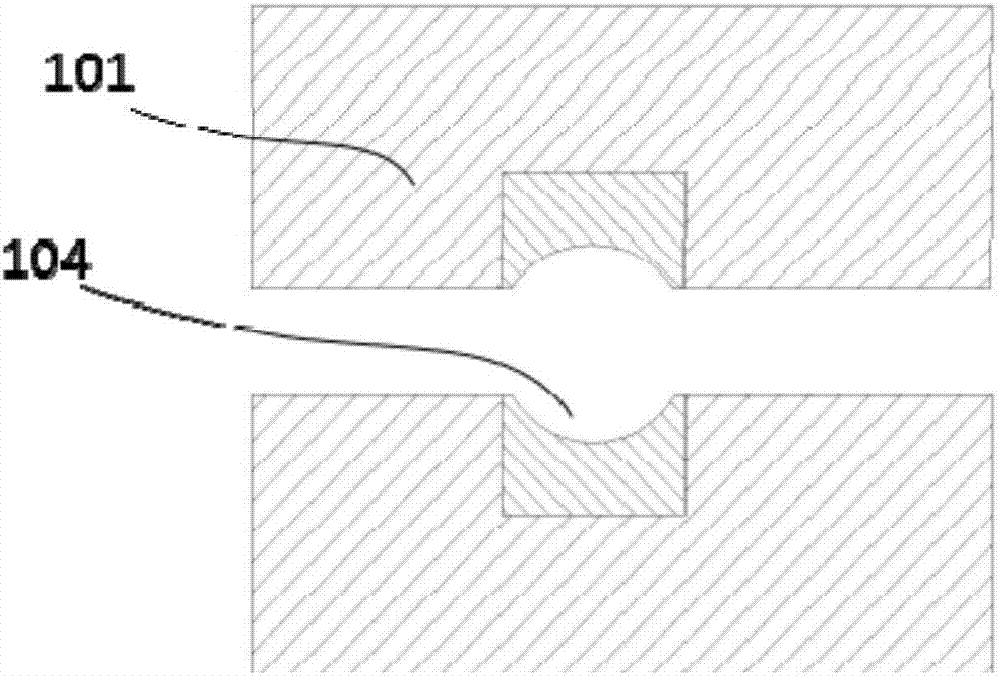

Semiconductor device and manufacturing process therefor

ActiveUS20060211235A1Low dielectric constantContact resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringCopper

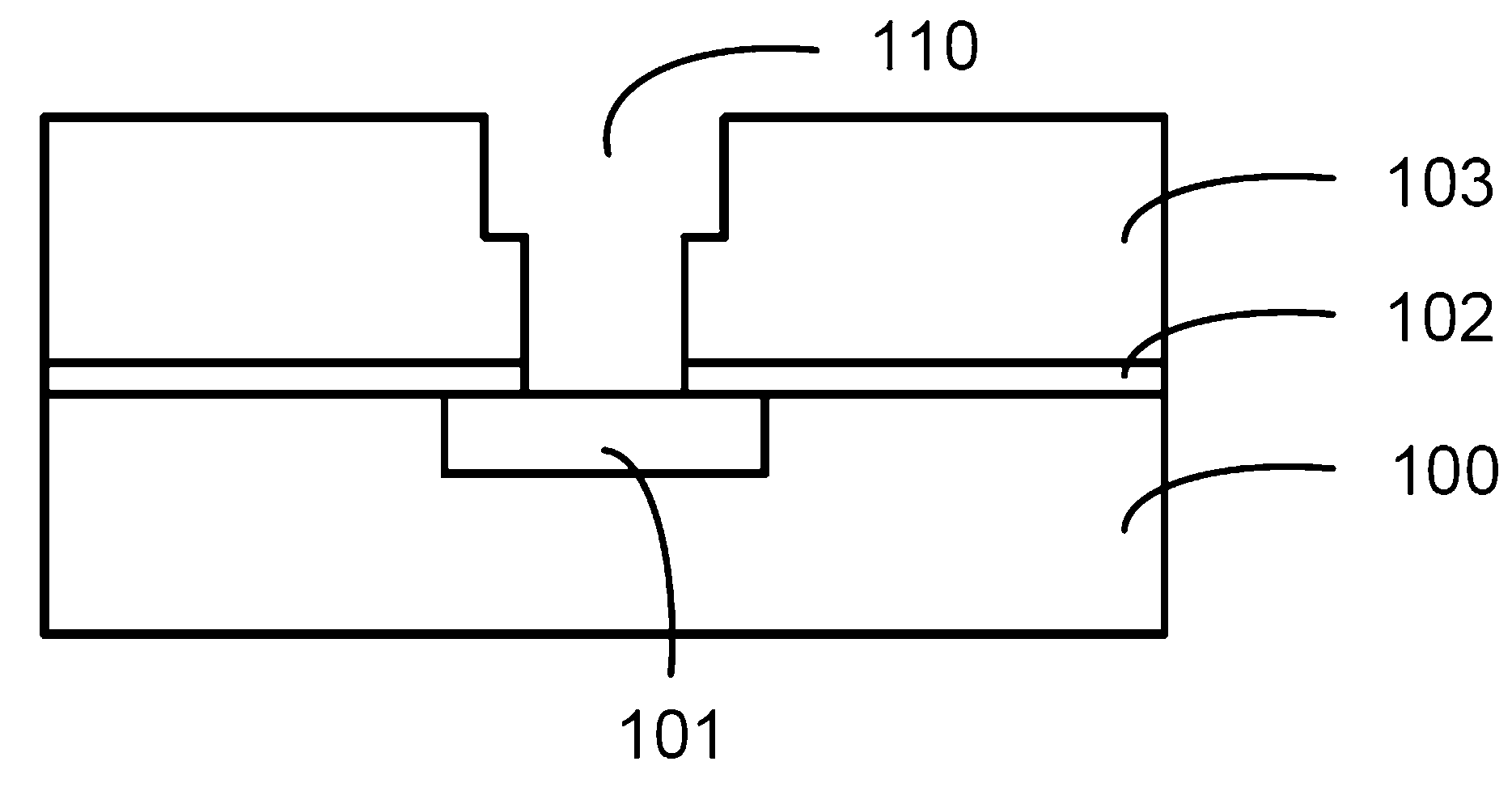

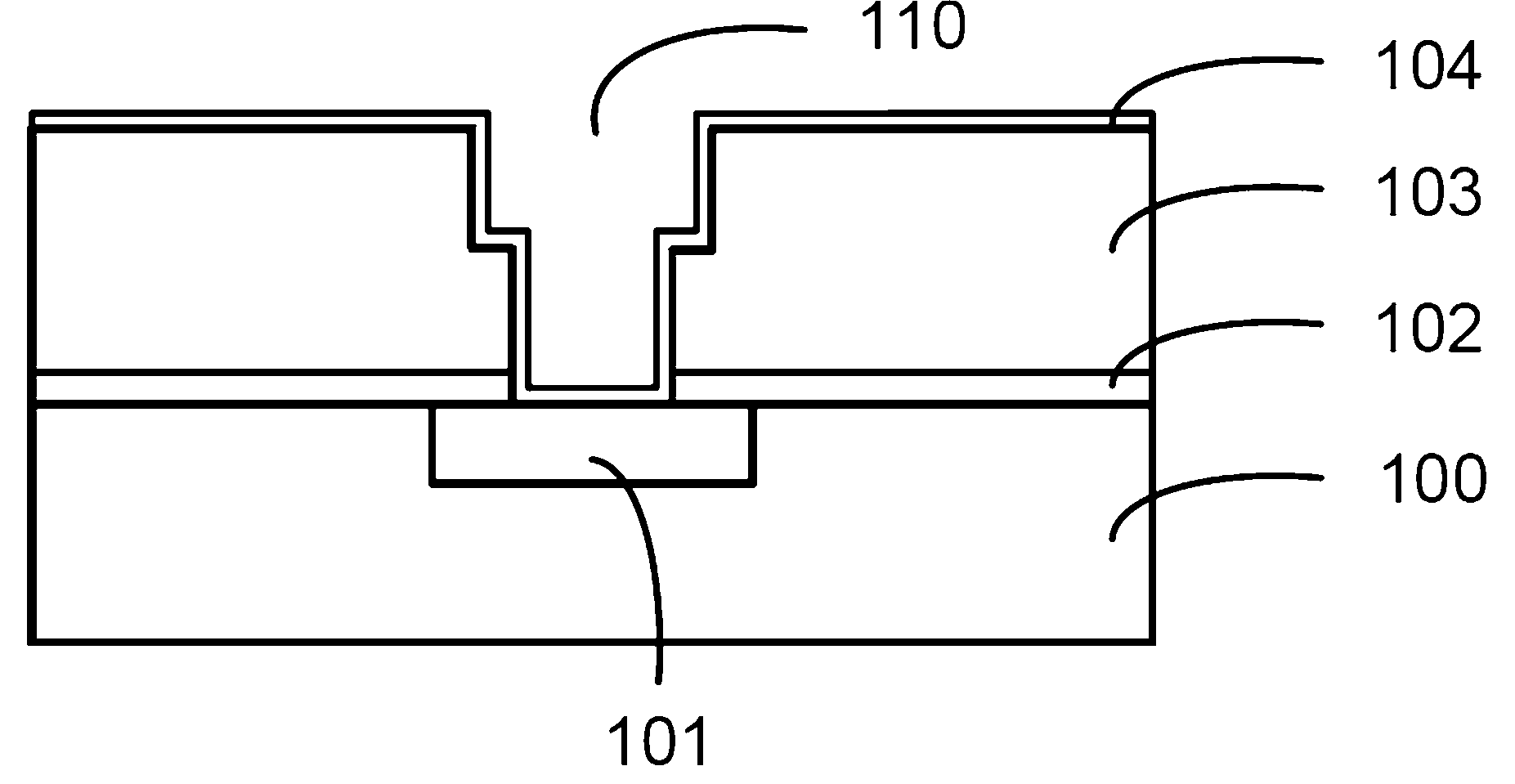

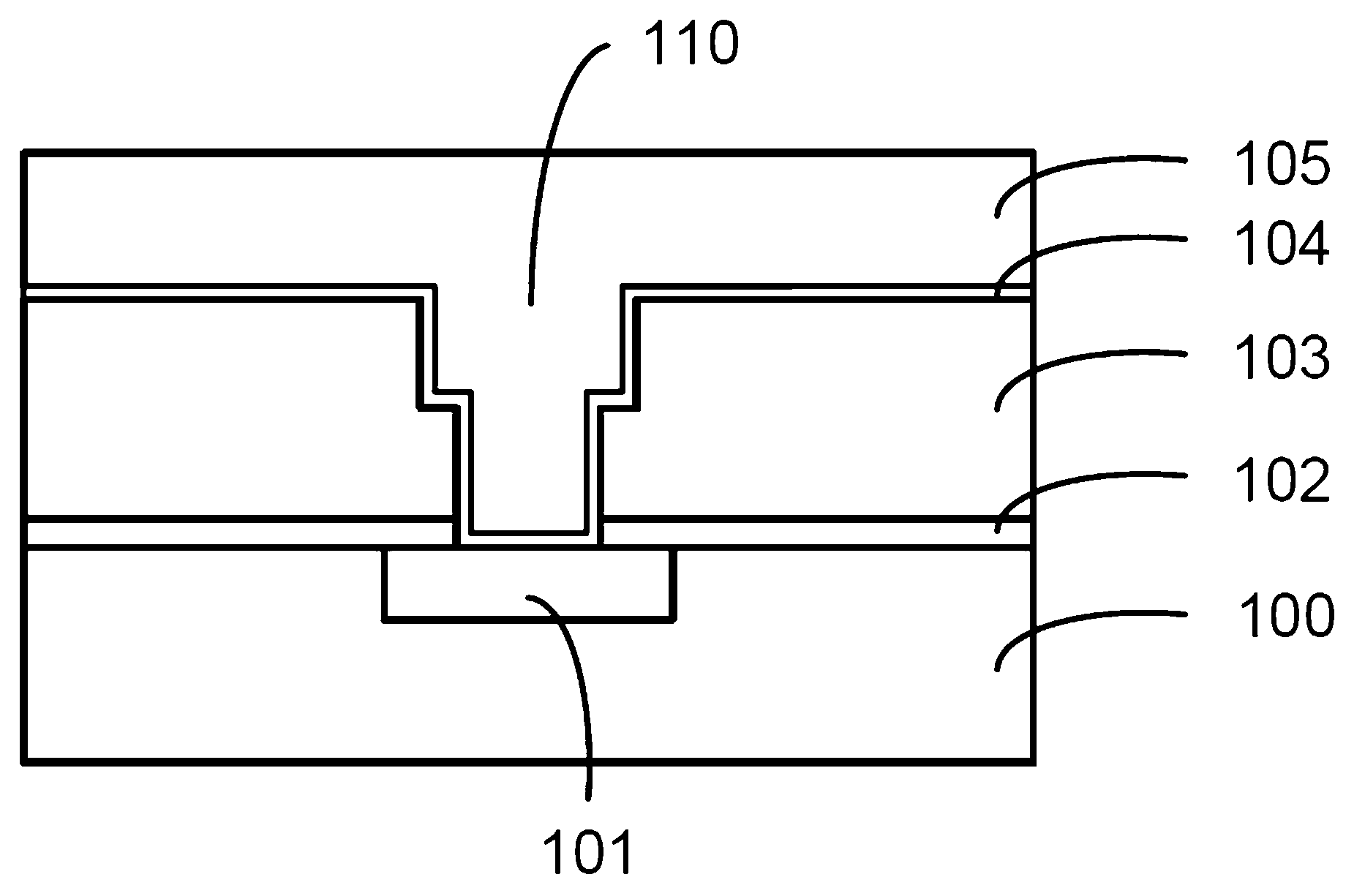

An object of this invention is to effectively reduce a connection resistance between a plug and an interconnect, and a dielectric constant of an insulating film. A semiconductor device 100 has a semiconductor substrate (not shown); a first interconnect 108 made of a copper-containing metal which is formed over the semiconductor substrate; a conductive first plug 114 formed over the first interconnect 108 and connected to the first interconnect 108; a Cu silicide layer 111 over the first interconnect 108 in an area other than the area where the first plug 114 is formed; a Cu silicide layer 117 over the first plug 114; and a first porous MSQ film 105 formed over an area from the side surface of the first interconnect 108 to the side surface of the first plug 114 and covering the side surface of the first interconnect 108, the upper portion of the first interconnect 108 and the side surface of the first plug 114.

Owner:RENESAS ELECTRONICS CORP

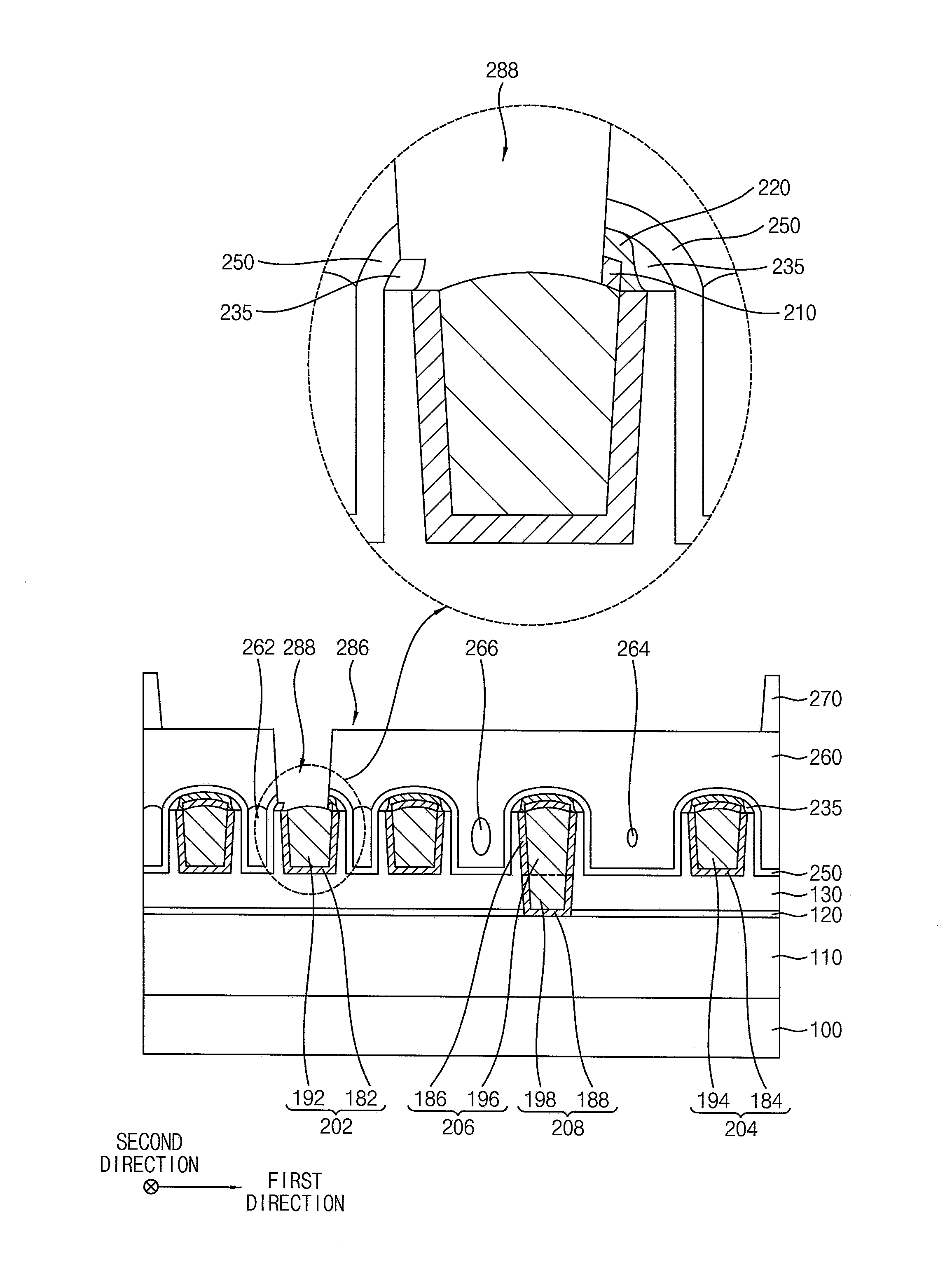

Semiconductor devices

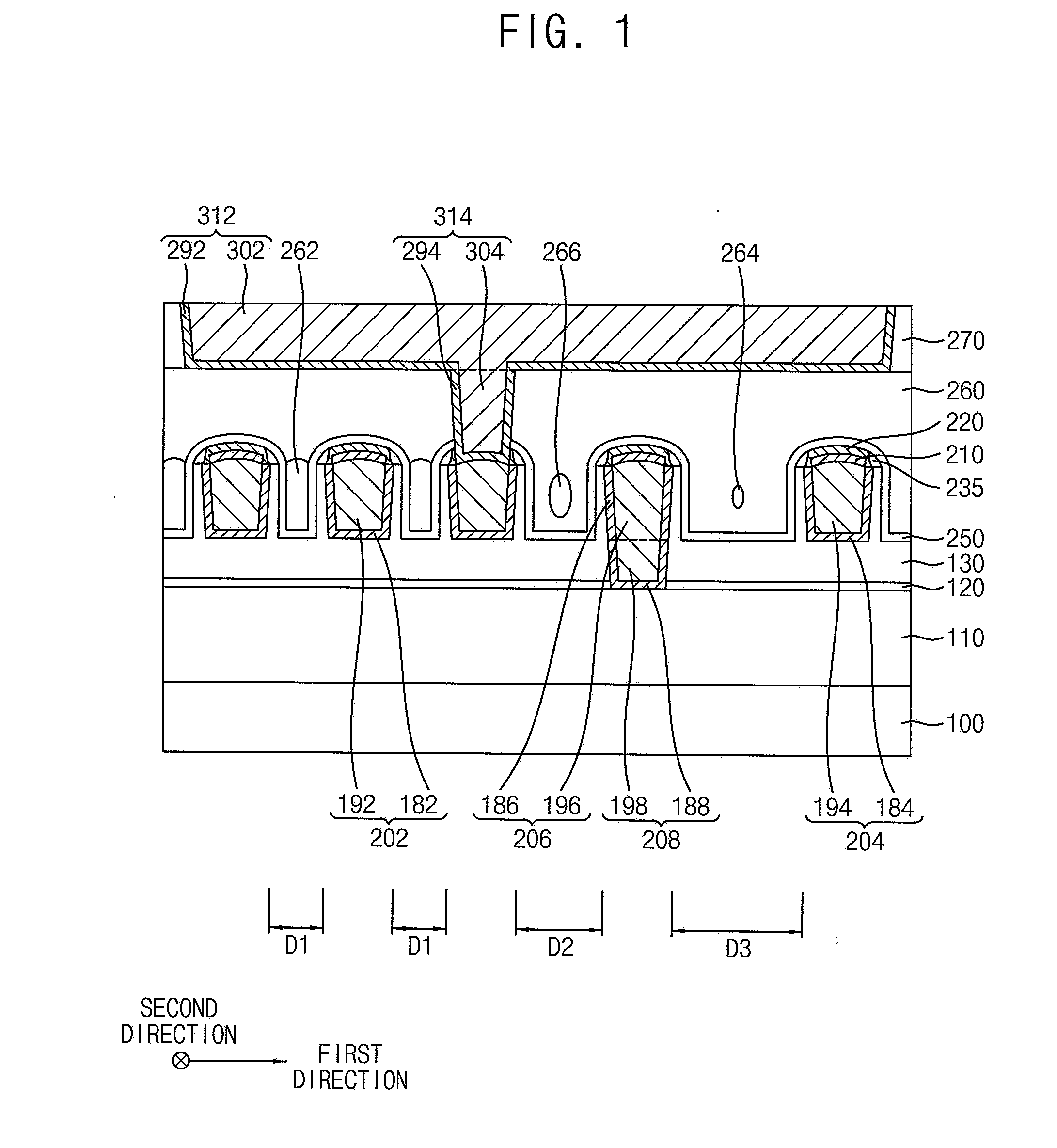

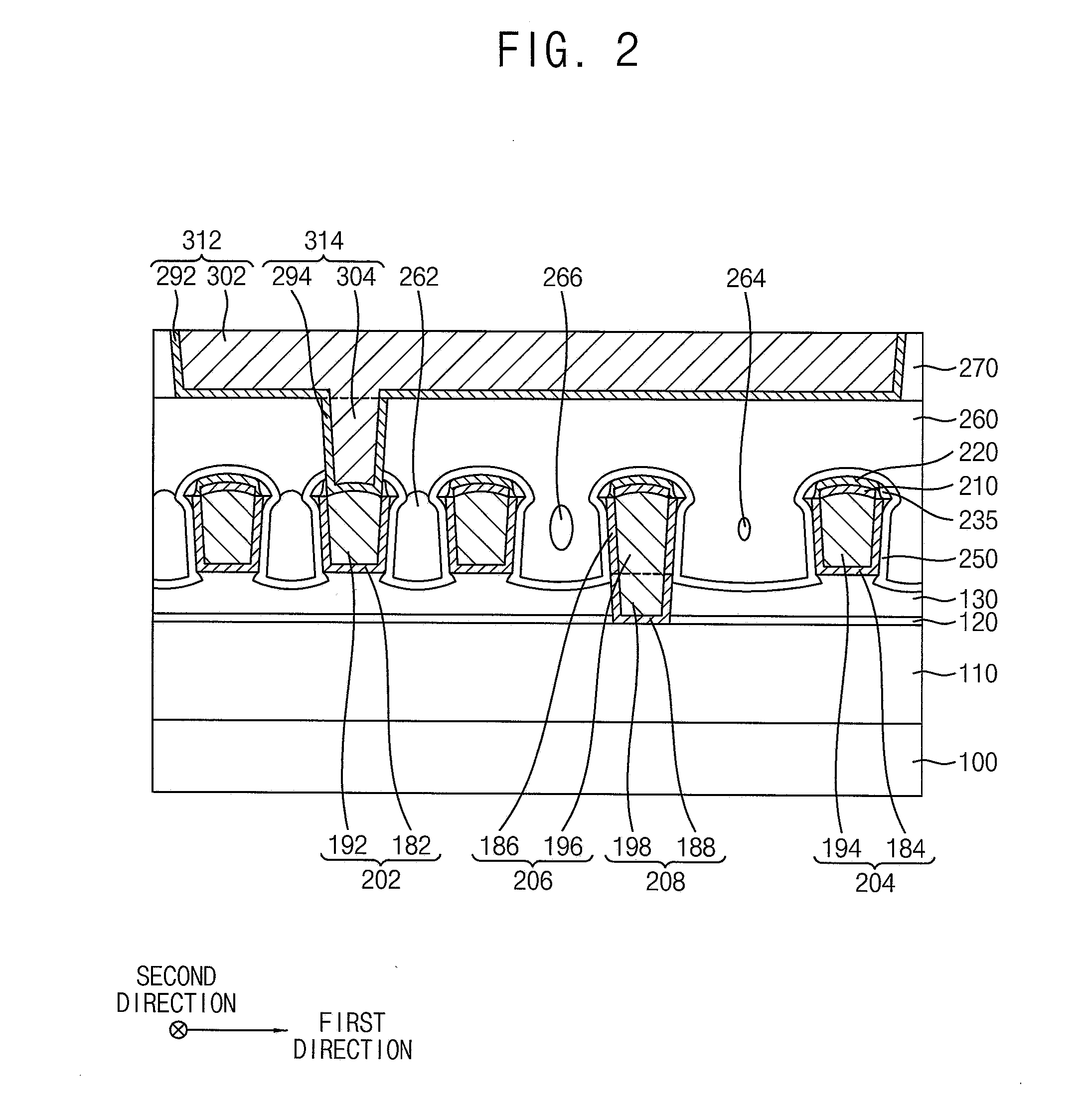

ActiveUS20160372415A1Avoid delayImprove reliabilityTransistorSemiconductor/solid-state device detailsEngineeringNitride

A semiconductor device may include a plurality of wiring structures spaced apart from each other, a protection pattern including a metal nitride on each of the wiring structures, a spacer on a sidewall of the protection pattern, and an insulating interlayer structure containing the wiring structures and having an air gap between the wiring structures.

Owner:SAMSUNG ELECTRONICS CO LTD

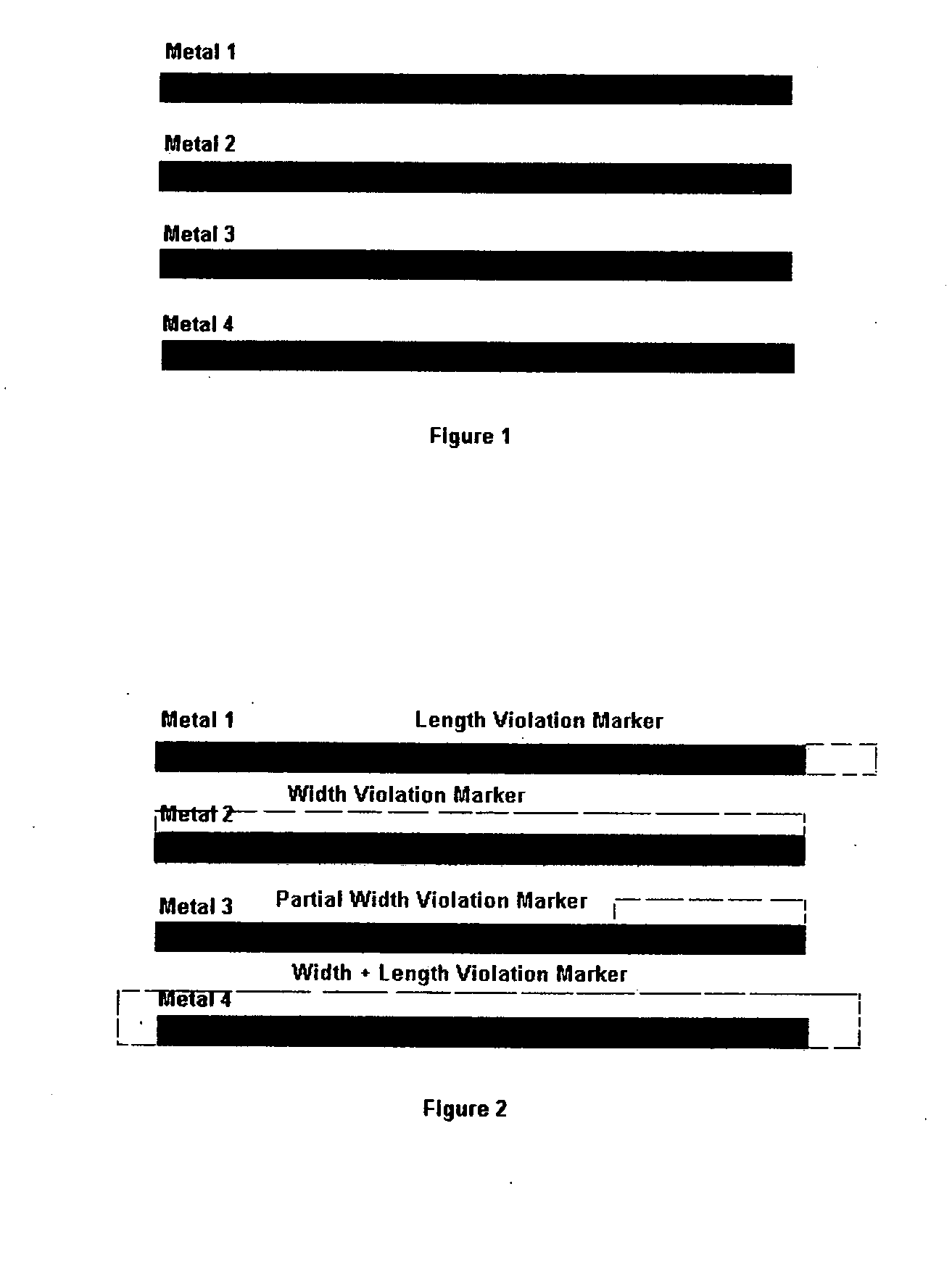

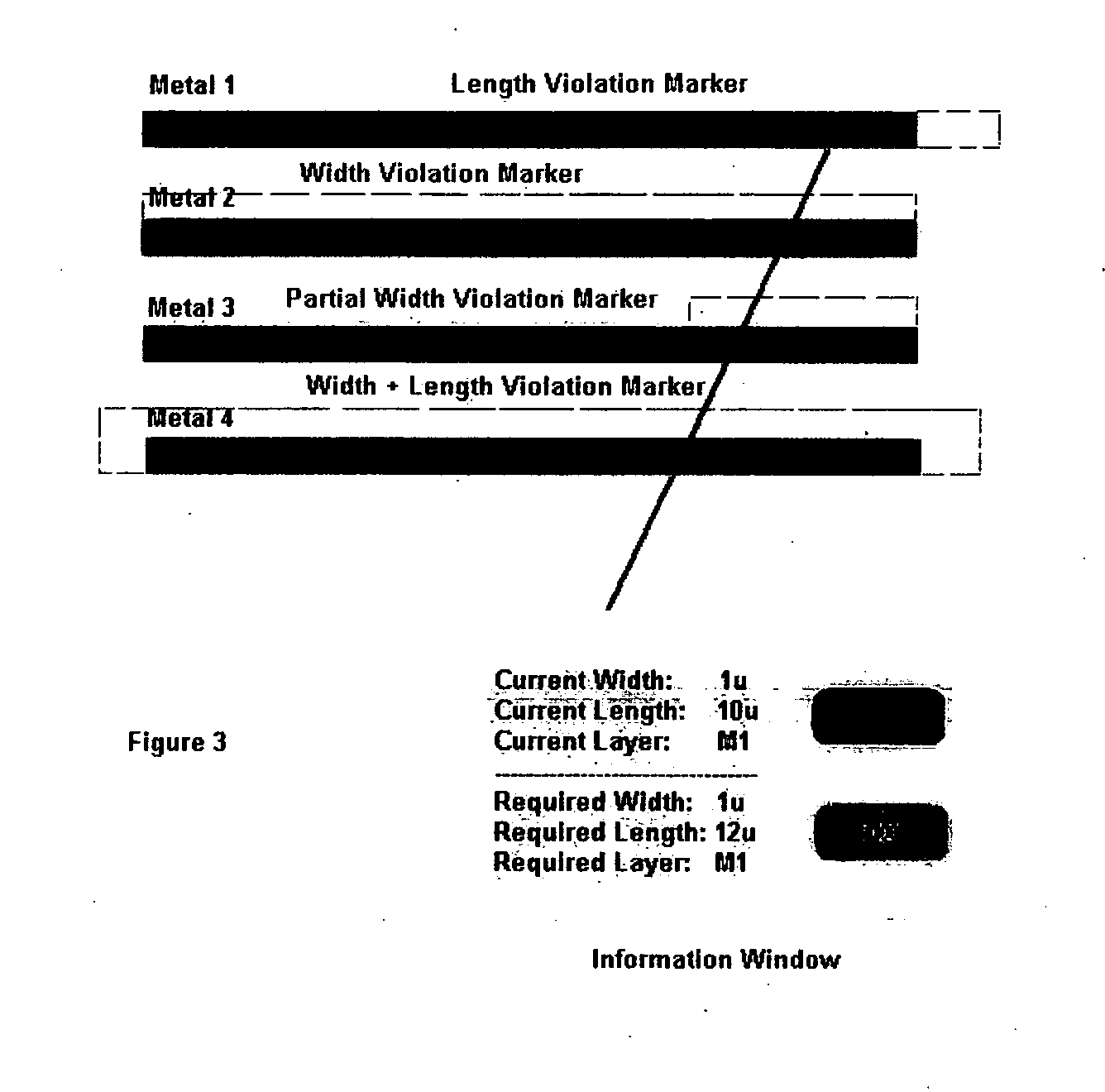

System and method for automatic elimination of electromigration and self heat violations during construction of a mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness

InactiveUS20080086709A1Prevent electromigrationEliminate electromigrationComputer aided designSpecial data processing applicationsGraphicsPosition dependent

A system and method for automatic elimination of electromigration (EM) and self heat (SH) violations during construction of a mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness, are disclosed. The method includes analyzing a selected polygon for space, width and length, in a mask layout block and obtaining one or more electromigration and / or self heat rules associated with the polygon from a technology and an external constraints file. The method also includes analyzing contacts and VIA's for amount and location in order to comply with electromigration and self heat rules. The method provides a violation marker associated with the selected position for the polygon that graphically represents a width, space, length and other polygon's physical characteristics within the mask layout block where the selected polygon complies with the electromigration and / or self heat violation. The method and system also provides an option to automatically correct the electromigration (EM) and self heat violation of the mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness.

Owner:MICROLOGIC DESIGN AUTOMATION

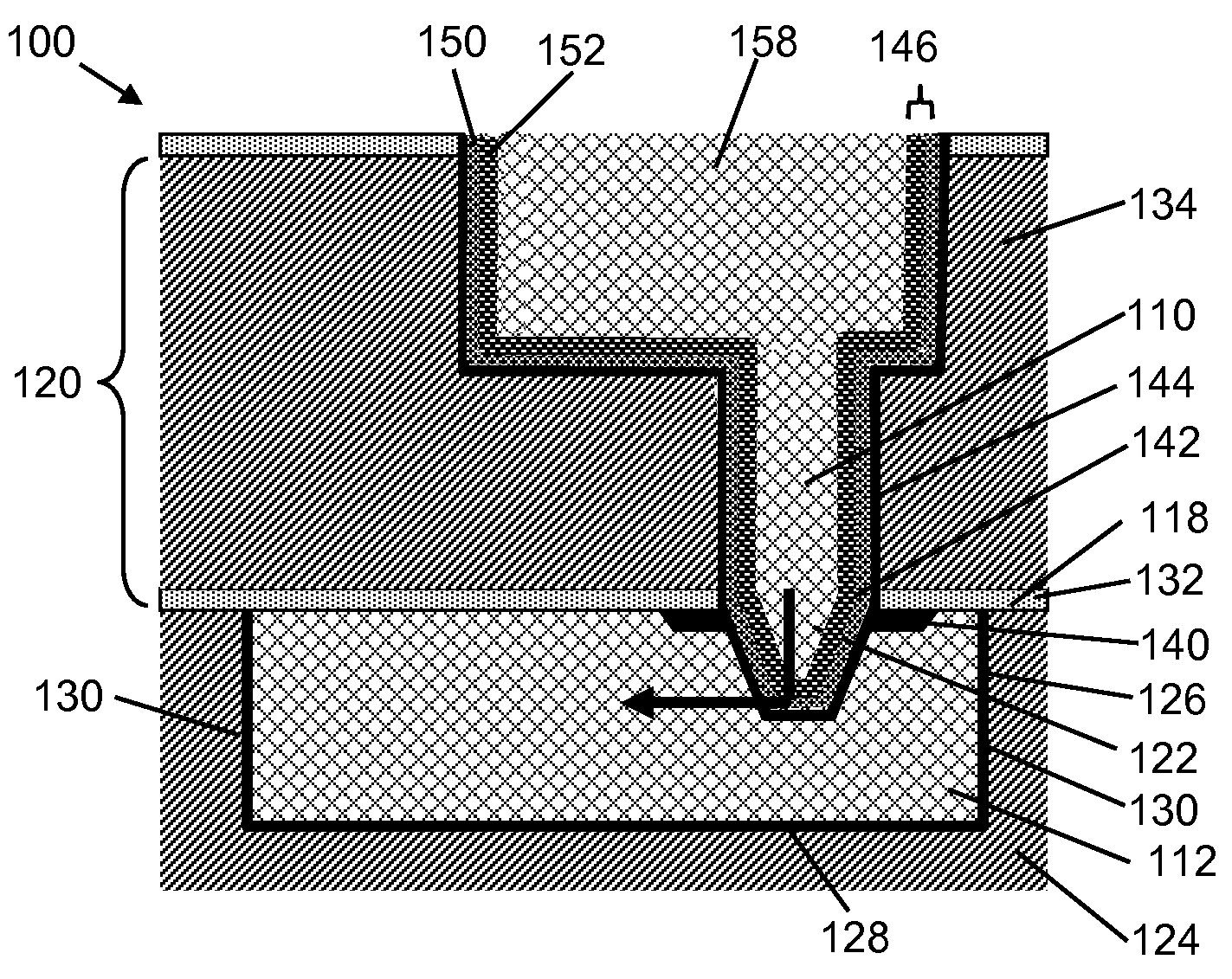

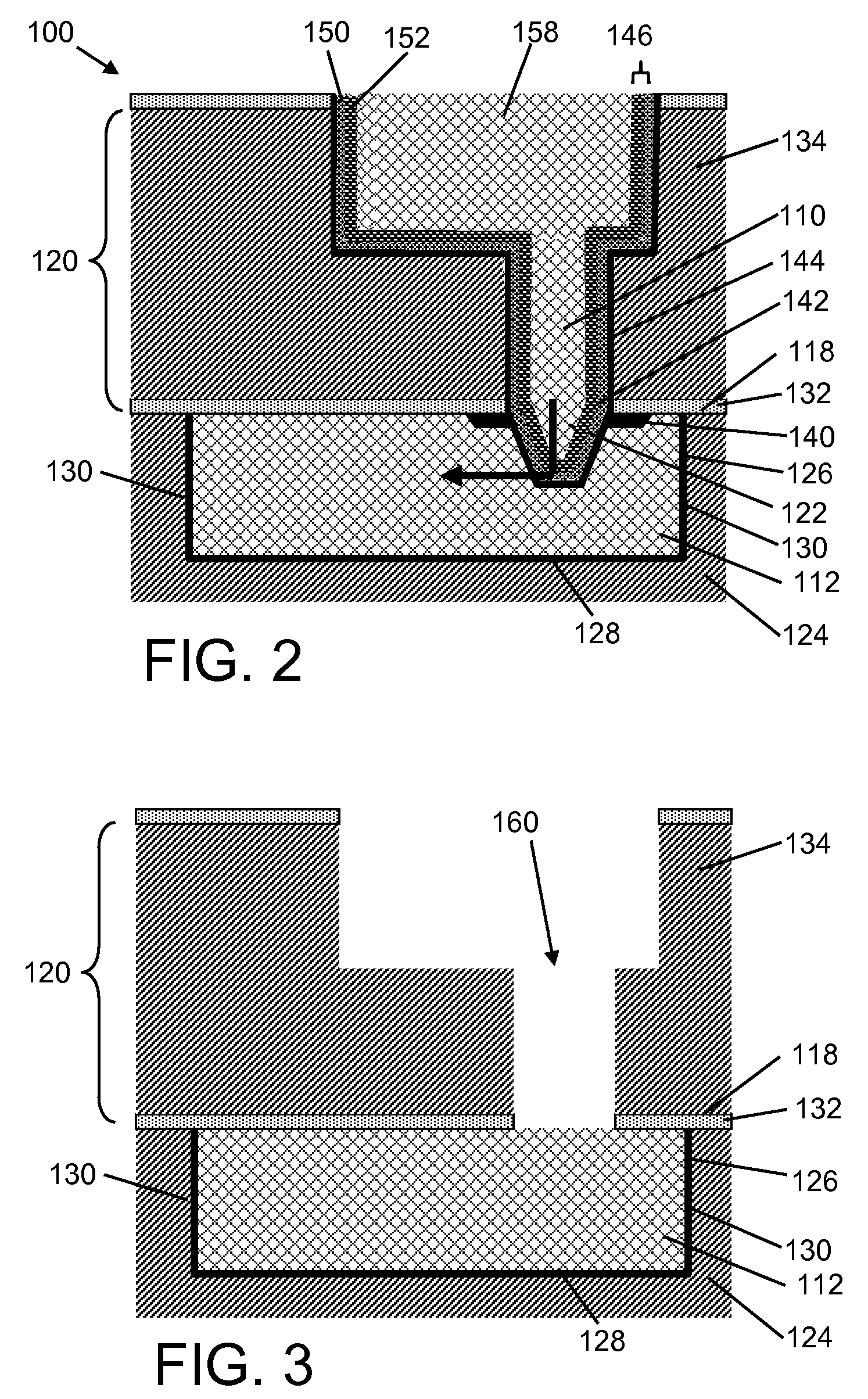

Structure including via having refractory metal collar at copper wire and dielectric layer liner-less interface and related method

InactiveUS20080203570A1Simple interfacePrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesCopper wireDielectric layer

Structures including a refractory metal collar at a copper wire and dielectric layer liner-less interface, and a related method, are disclosed. In one embodiment, a structure includes a copper wire having a liner-less interface with a dielectric layer thereabove; a via extending upwardly from the copper wire through the dielectric layer; and a refractory metal collar extending from a side of the via and partially along the liner-less interface. Refractory metal collar prevents electromigration induced slit voiding by improving the interface around the via, and prevents void nucleation from occurring near the via. Also, the refractory metal collar provides electrical redundancy in the presence of voids around the via and dielectric layer liner-less interface.

Owner:TAIWAN SEMICON MFG CO LTD

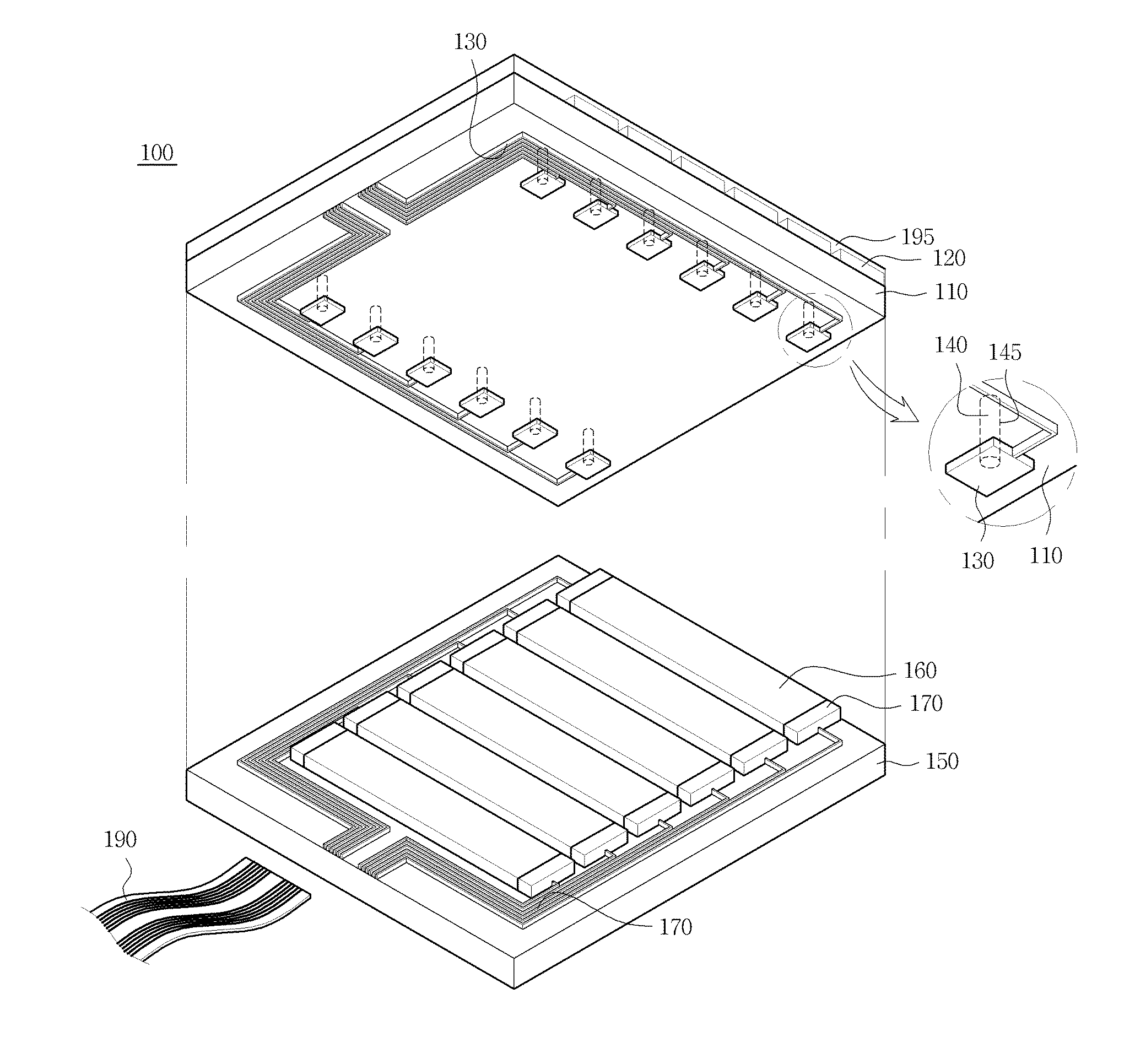

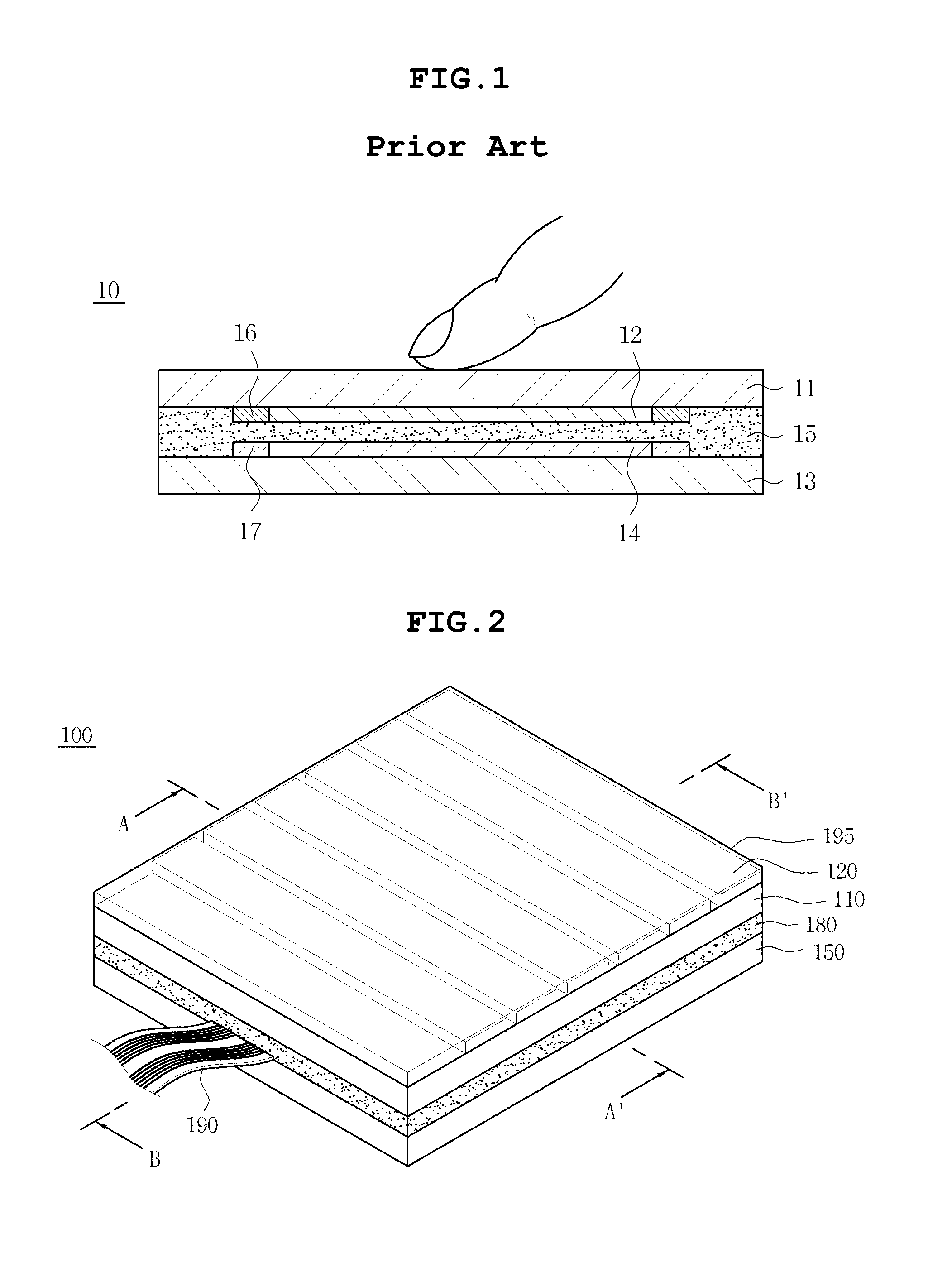

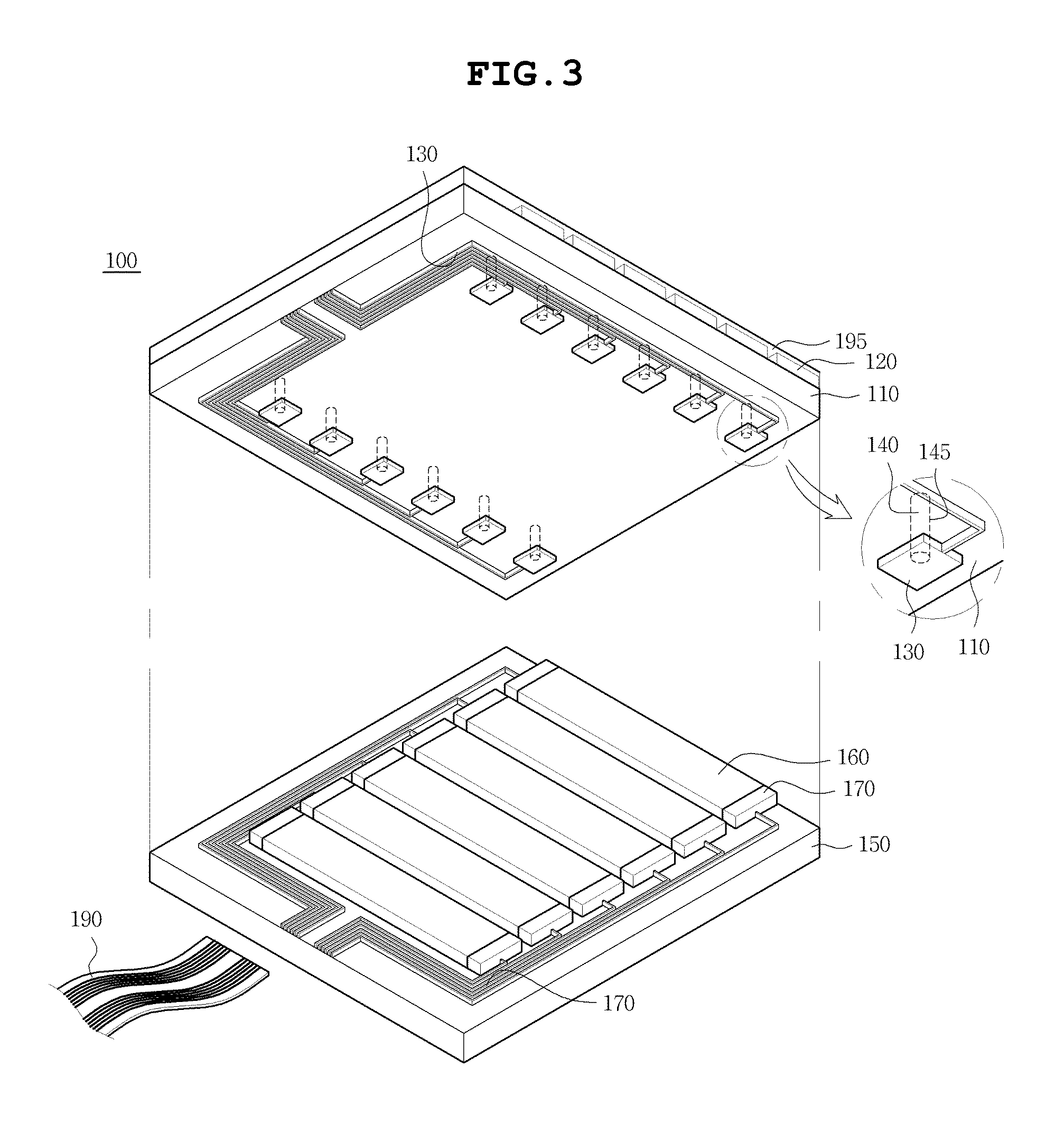

Capacitive touch panel

InactiveUS20110298747A1Prevent electromigrationHigh sensitivityInput/output processes for data processingEngineeringTouch panel

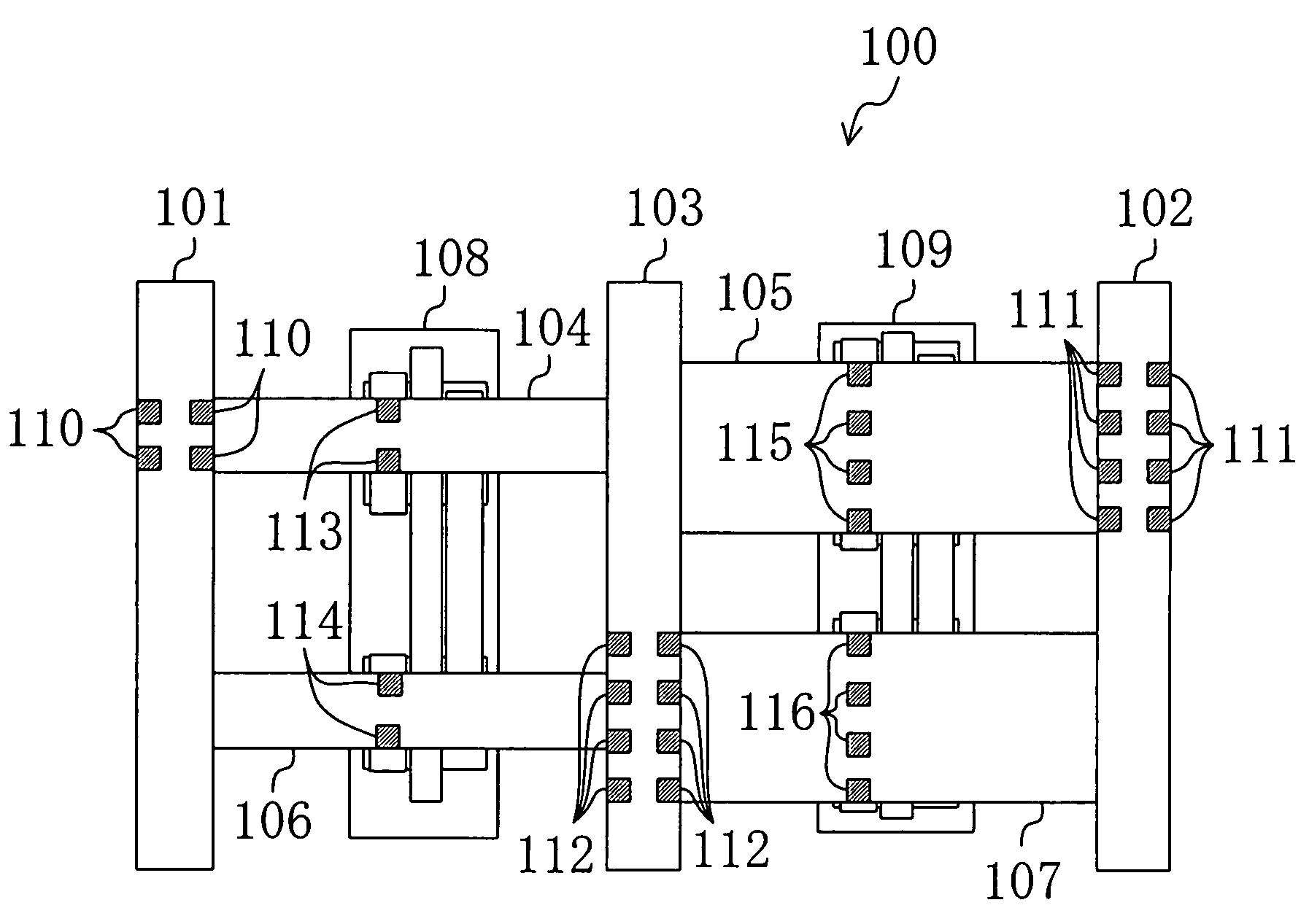

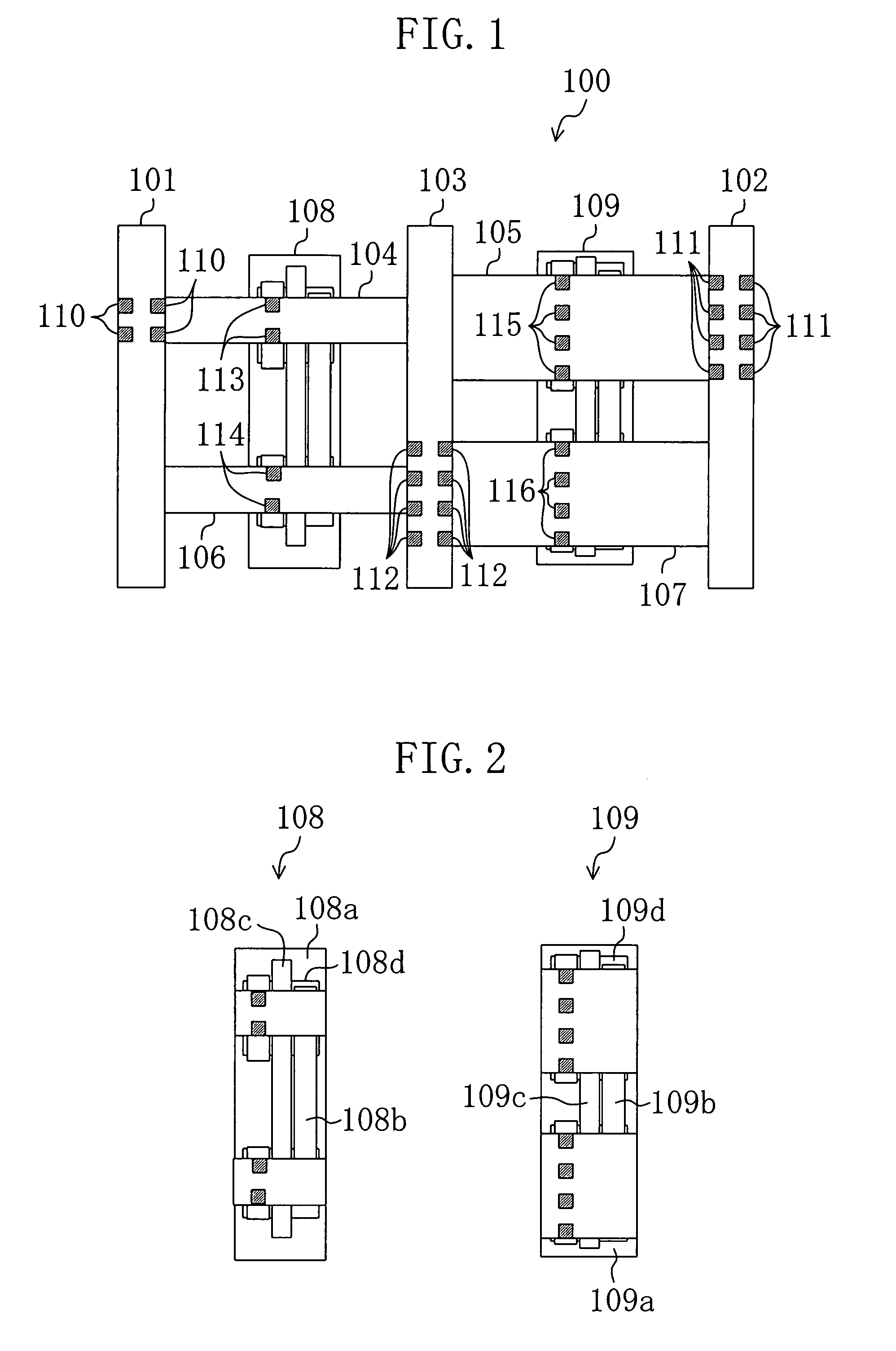

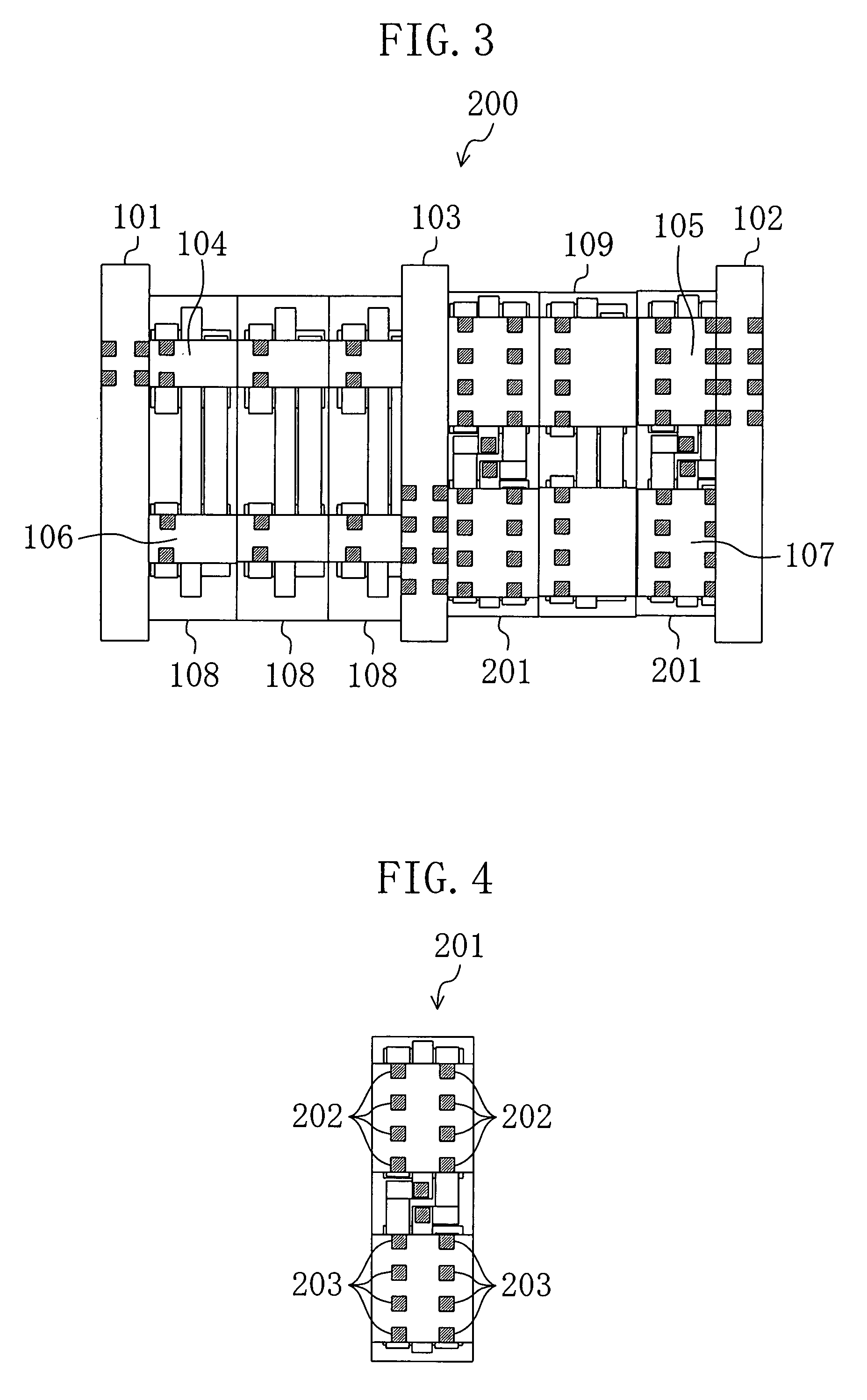

Disclosed herein is a capacitive touch panel 100 including a first transparent electrode 120 formed on one surface of a first transparent substrate 110, a first electrode wiring 130 formed on the other surface of the first transparent substrate 110, a conductive via 140 penetrating through the first transparent substrate 110 to connect the first transparent electrode 120 to the first electrode wiring 130, a second transparent electrode 160 formed on one surface of a second transparent substrate 150, a second electrode wiring 170 connected to the second transparent electrode 160, and an adhesive layer 180 formed between the other surface of the first transparent substrate 110 and the second transparent electrode 160 so that the other surface of the first transparent substrate 110 is opposite to the second transparent electrode 160.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

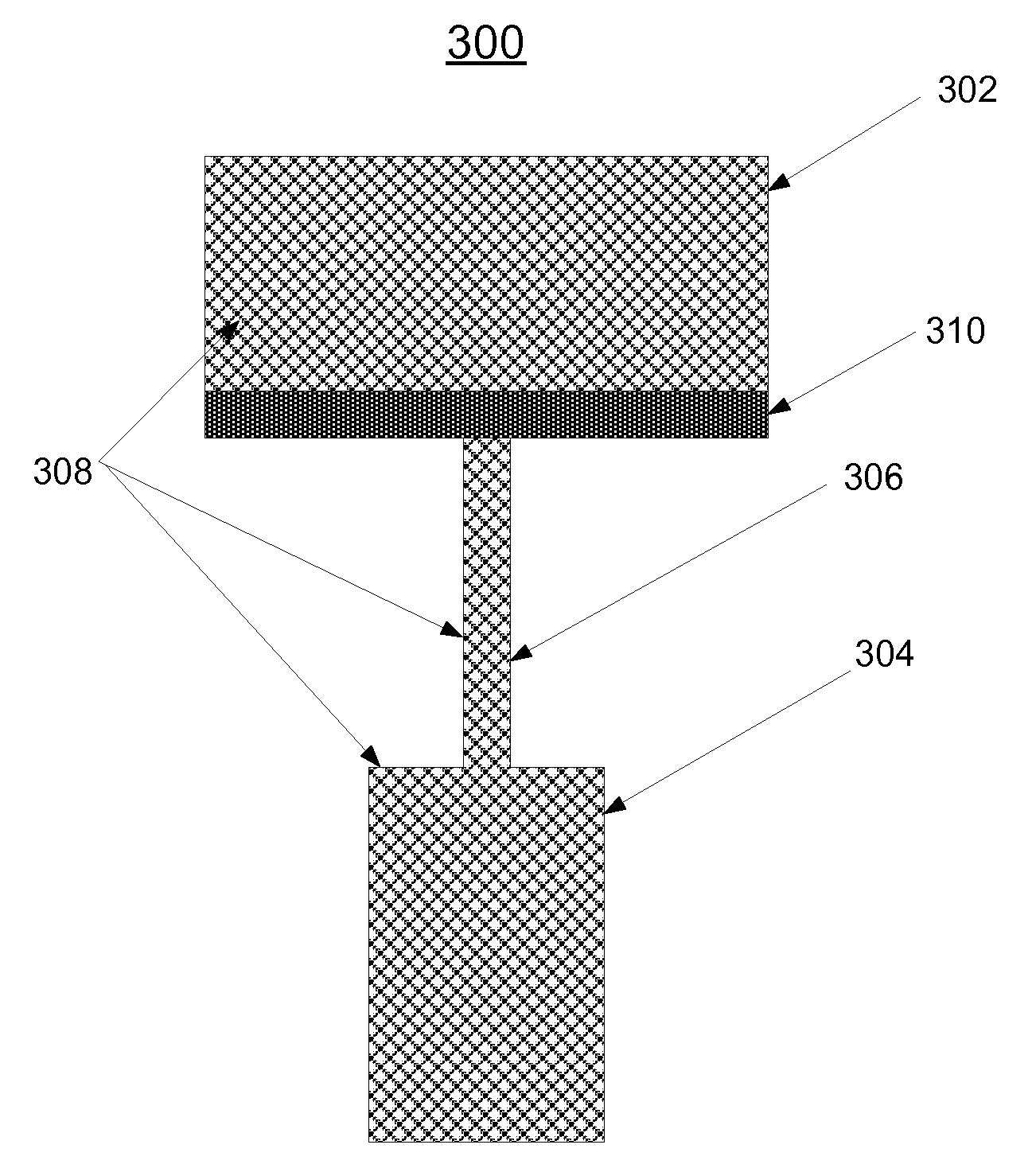

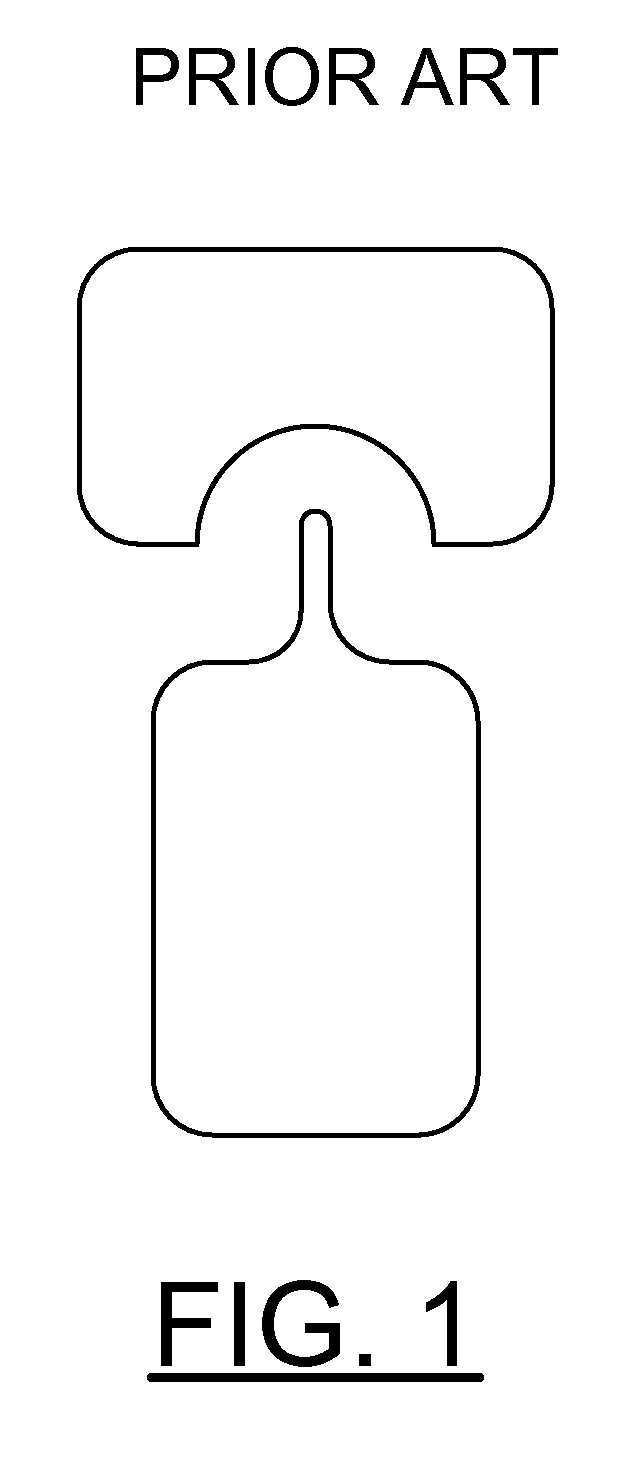

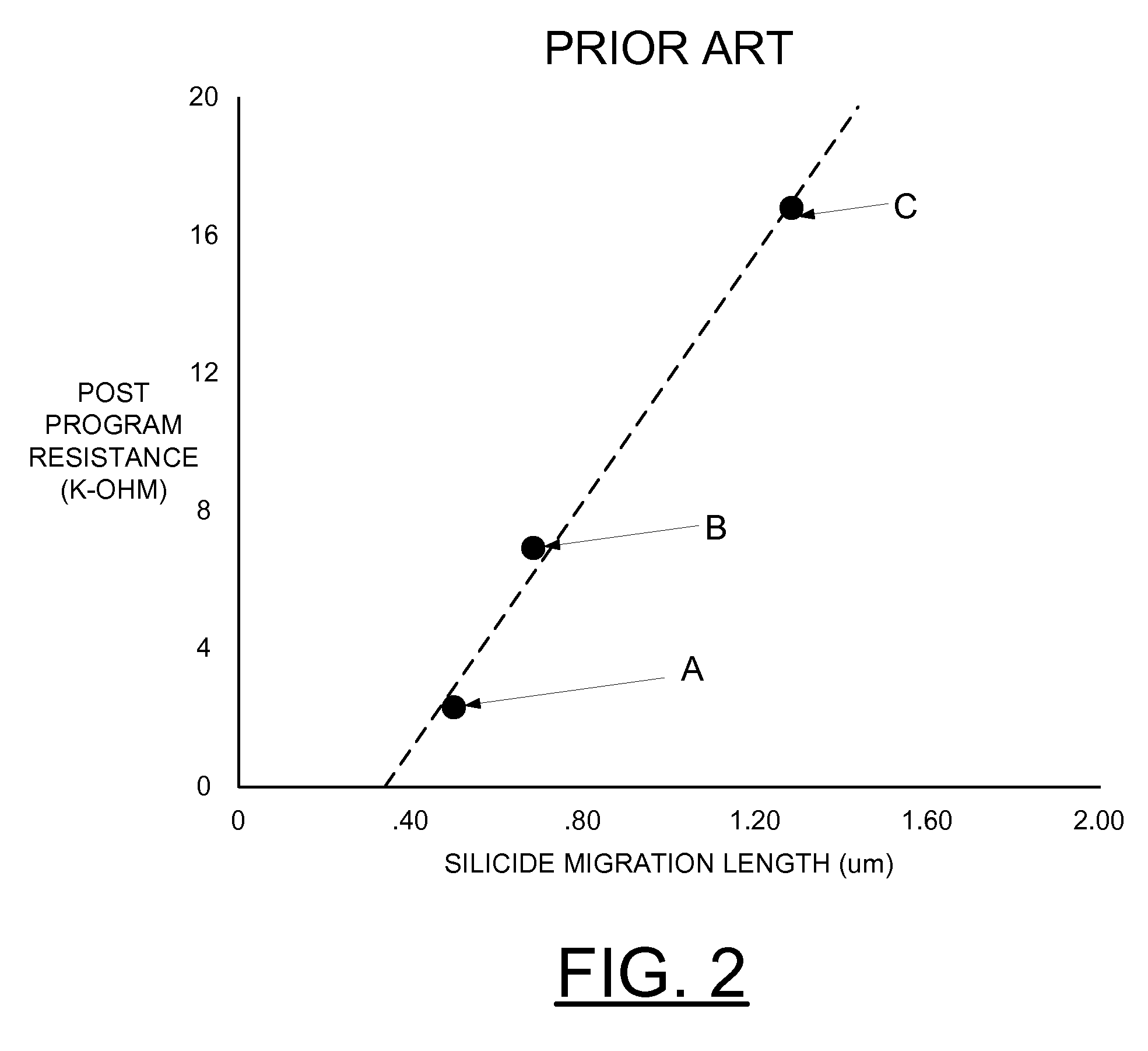

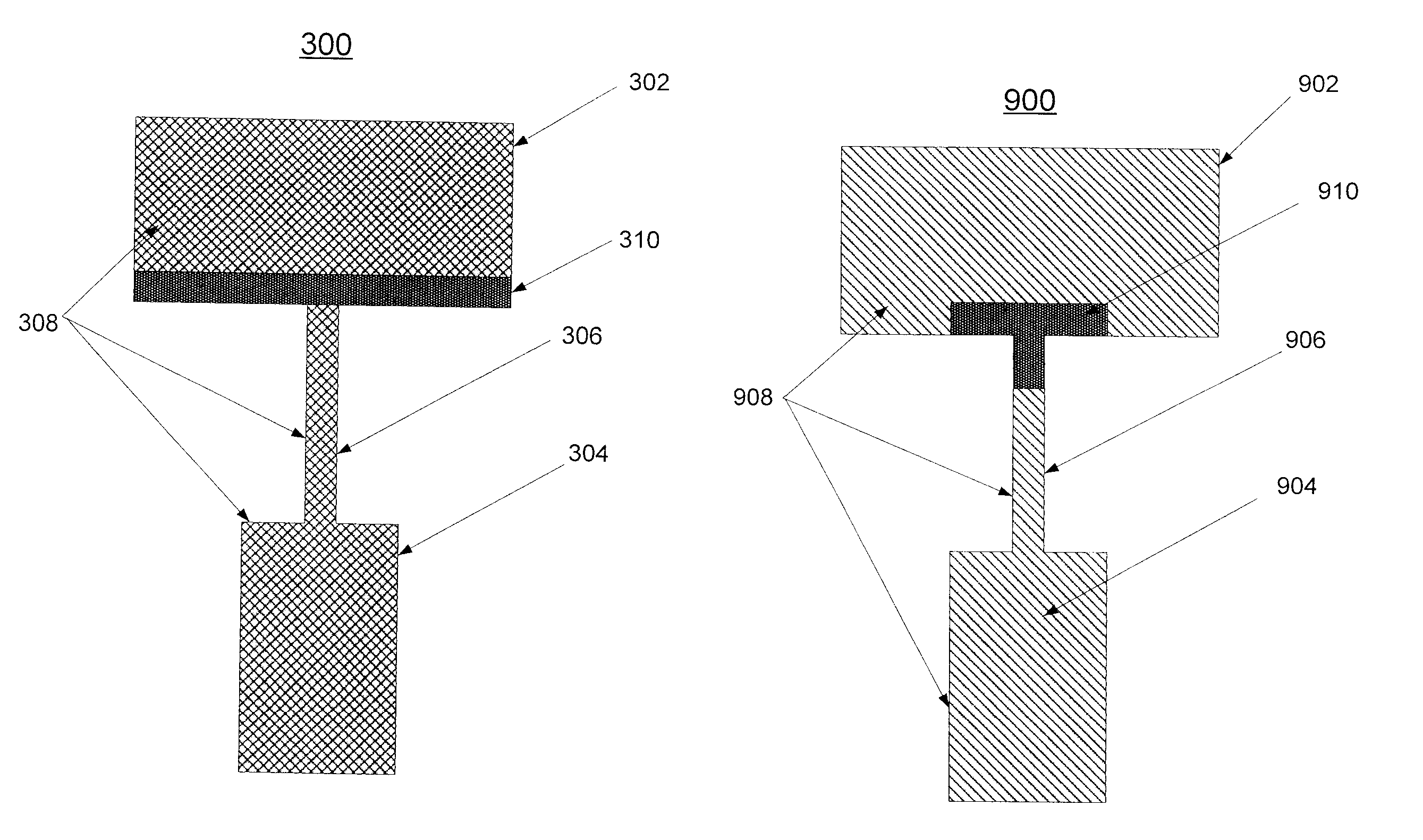

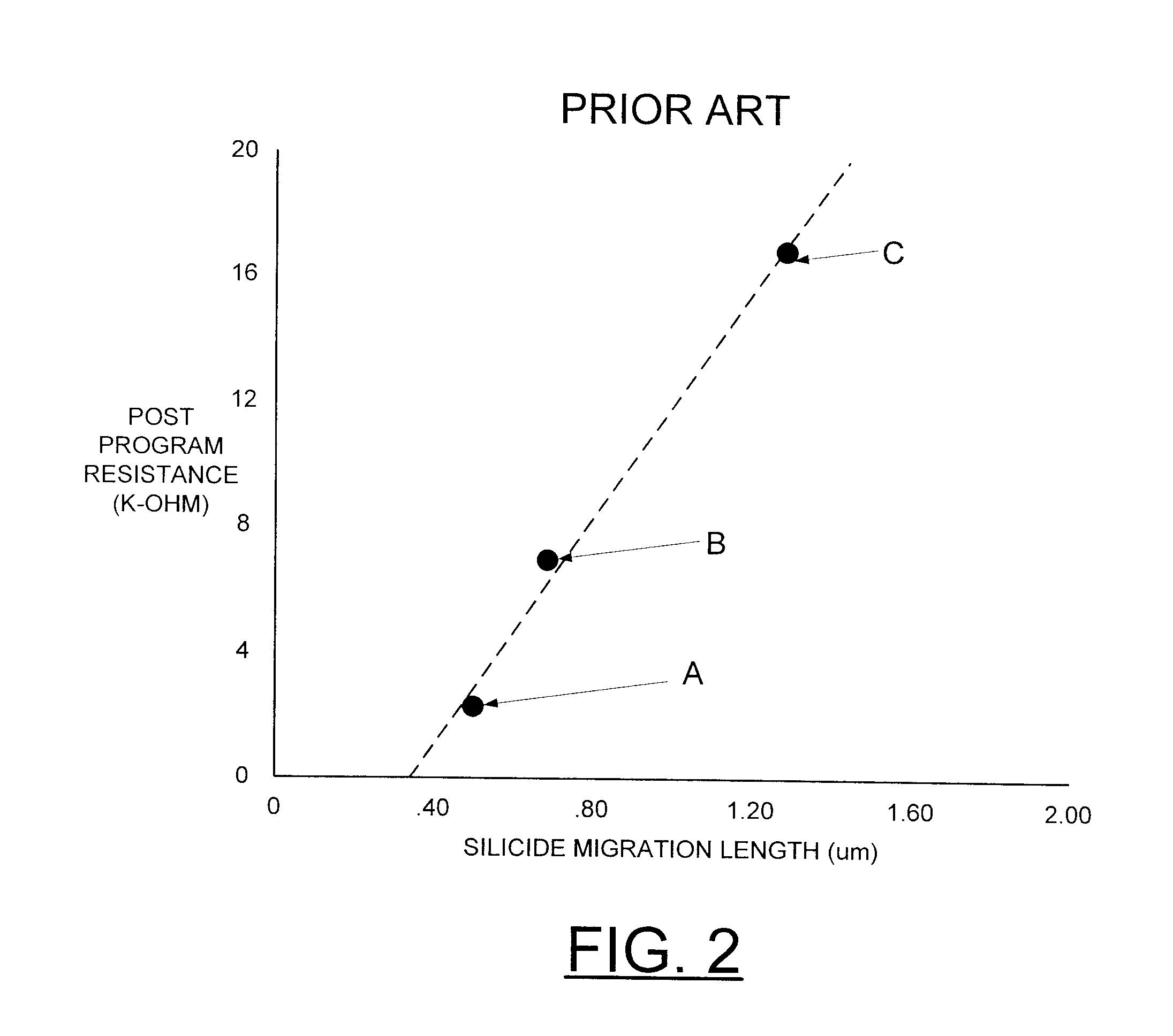

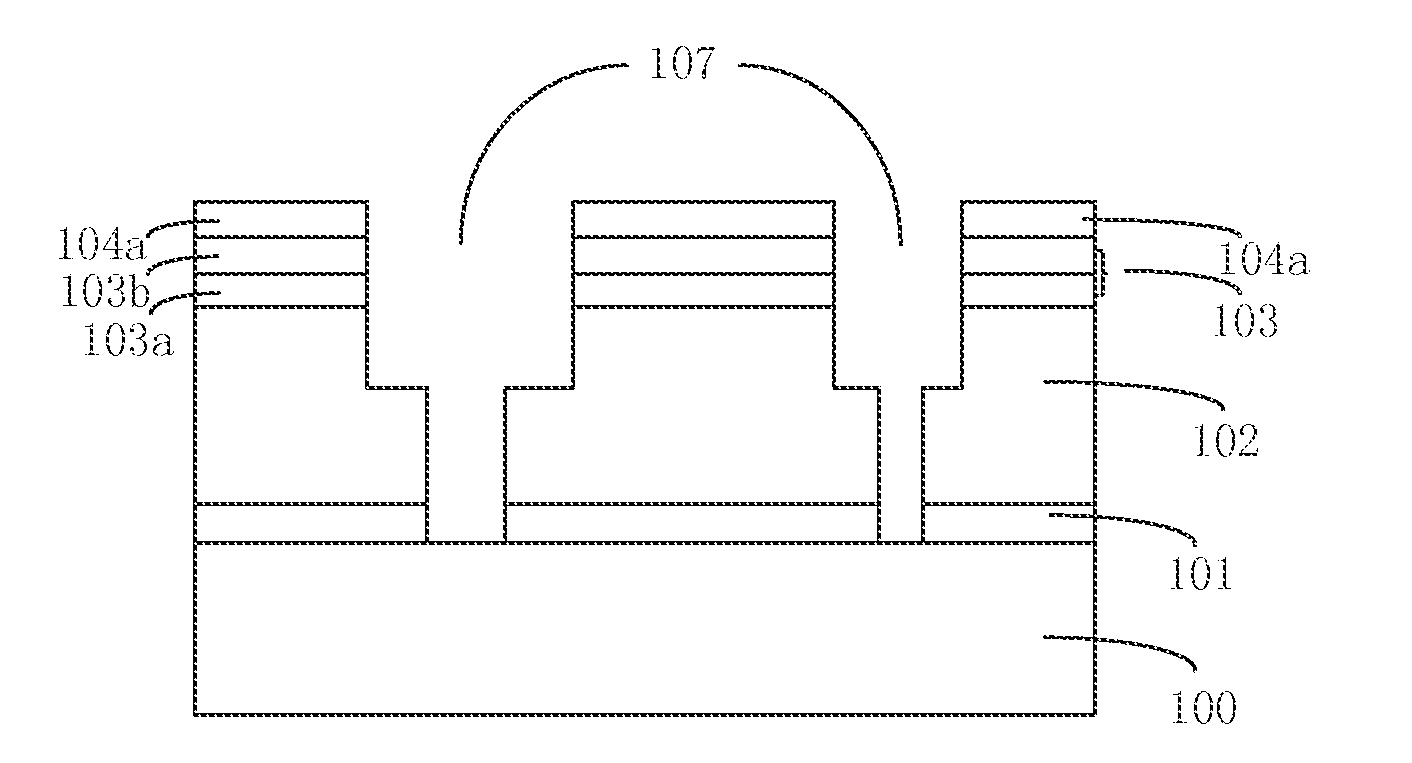

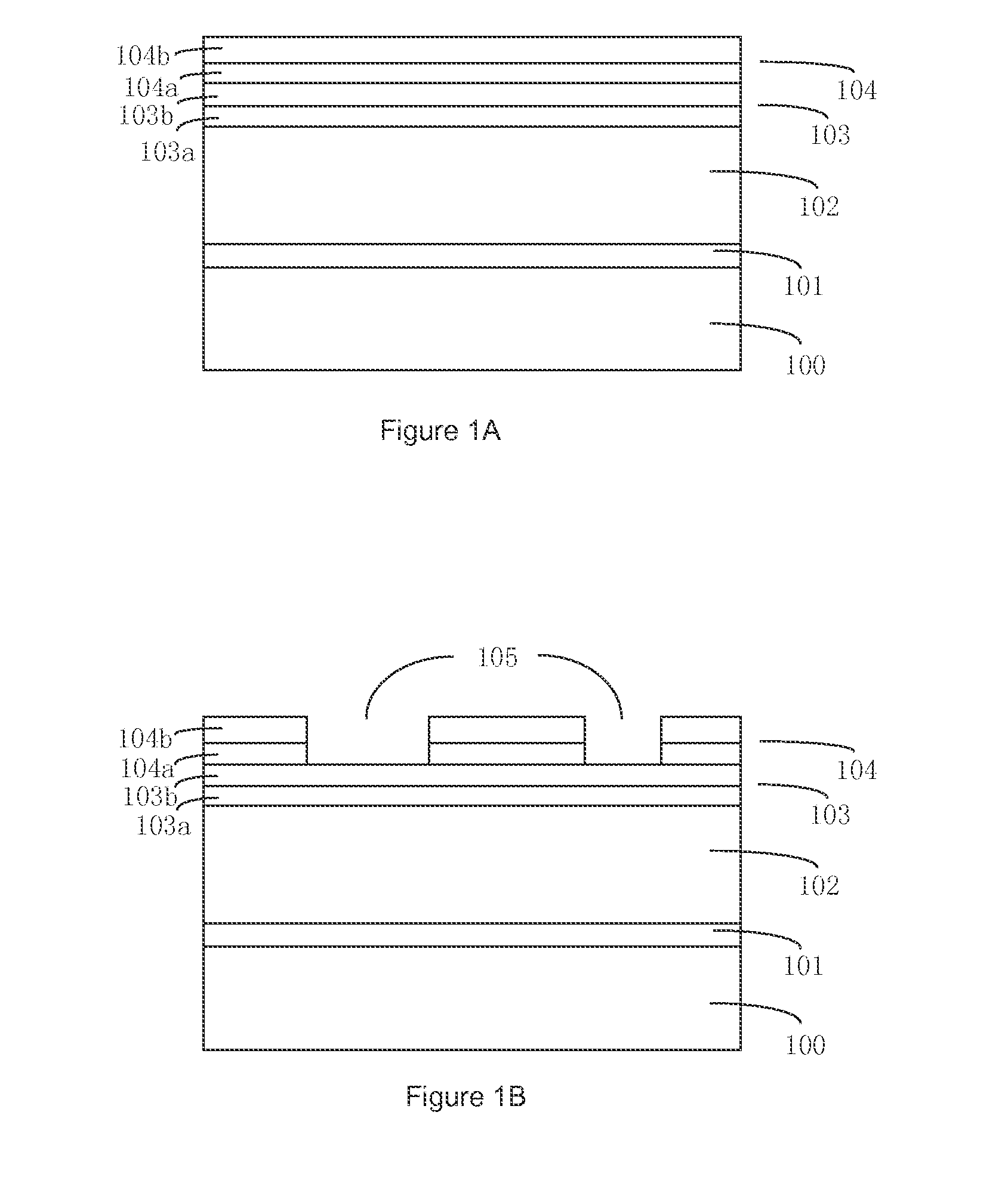

E-Fuse and Method for Fabricating E-Fuses Integrating Polysilicon Resistor Masks

InactiveUS20080029843A1Avoid flowReduced series resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectromigration

An E-fuse and a method for fabricating an E-fuse integrating polysilicon resistor masks, and a design structure on which the subject E-fuse circuit resides are provided. The E-fuse includes a polysilicon layer defining a fuse shape including a cathode, an anode, and a fuse neck connected between the cathode and the anode silicide formation. A silicide formation is formed on the polysilicon layer with an unsilicided portion extending over a portion of the cathode adjacent the fuse neck. The unsilicided portion substantially prevents current flow in the silicide formation region of the cathode, with electromigration occurring in the fuse neck during fuse programming. The unsilicided portion has a substantially lower series resistance than the series resistance of the fuse neck.

Owner:INT BUSINESS MASCH CORP

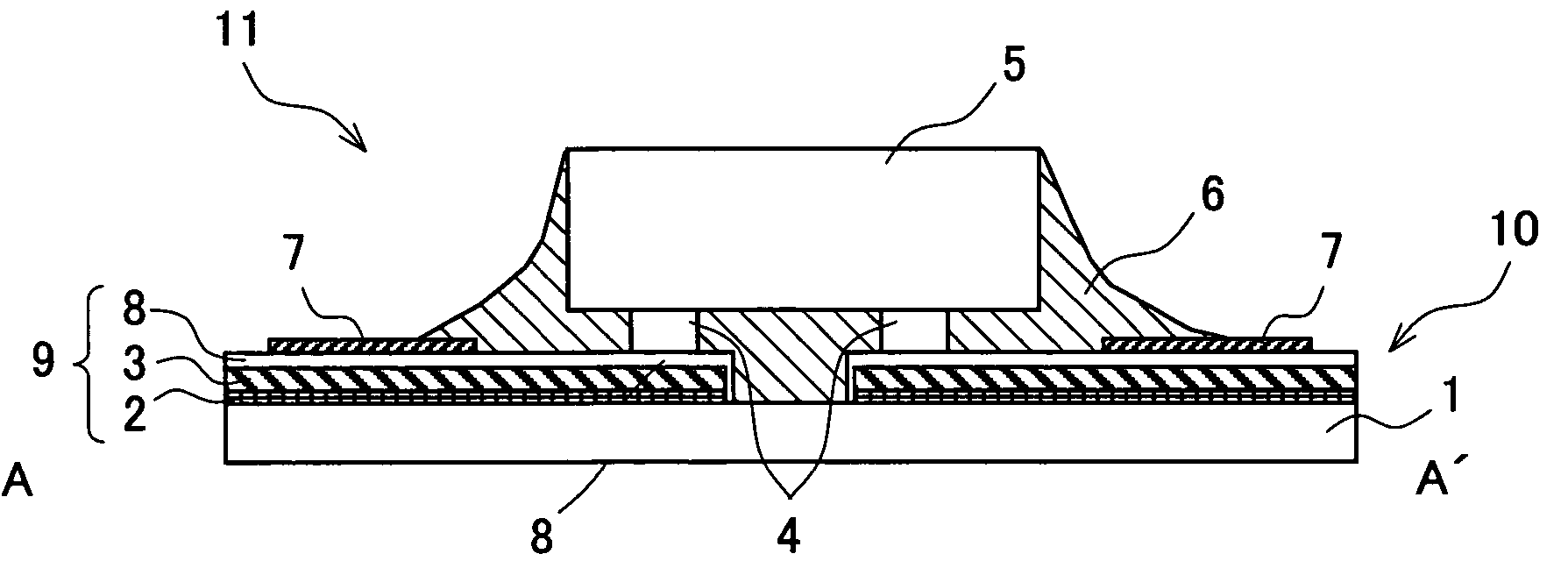

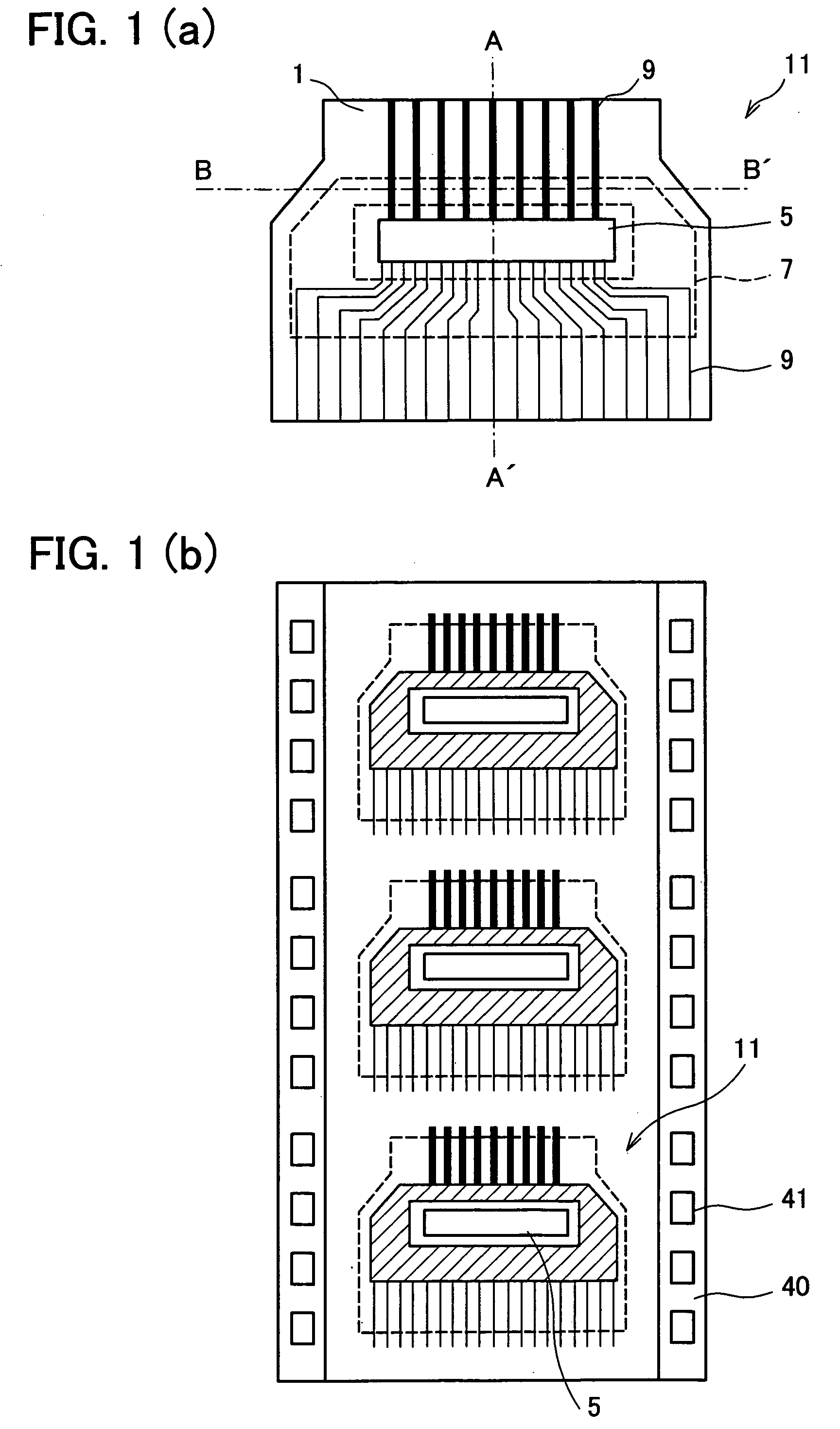

Semiconductor device

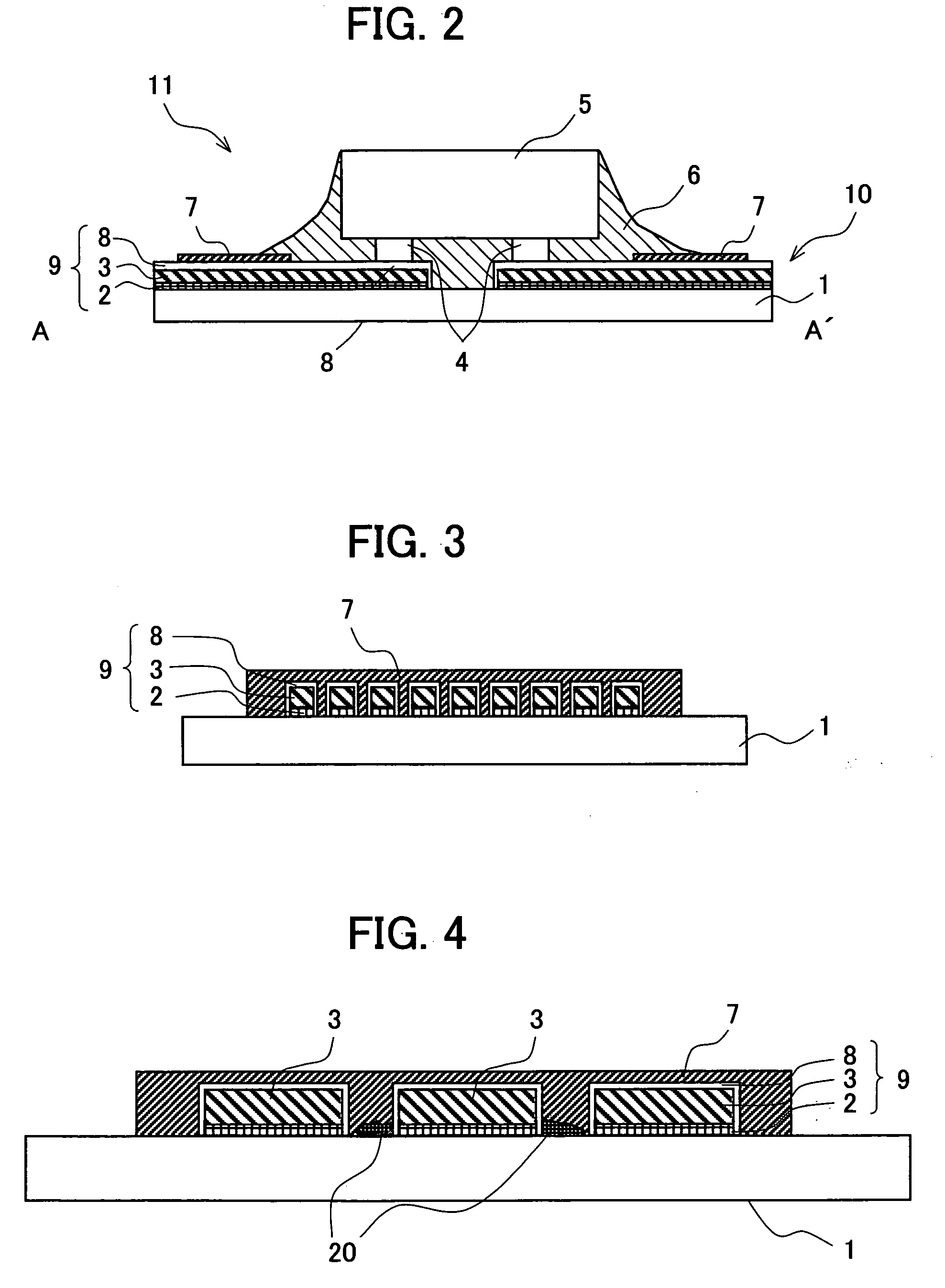

ActiveUS20050263909A1High reliable semiconductorPrevent electromigrationPrinted circuit assemblingFinal product manufactureDevice materialSemiconductor chip

A high reliability semiconductor device is provided which can prevent electromigration due to the deposition of metal ions originating from wires. The device includes: a flexible wiring board 11 including a base film 1 and multiple wires 9; a semiconductor chip 5 mounted to the flexible wiring board 11; and a sealing resin 6 disposed between the flexible wiring board 11 and the semiconductor chip 5 so as to at least partially in contact with the wires 9. The sealing resin 6 contains a metal ion binder mixed thereto.

Owner:SHENZHEN TOREY MICROELECTRONIC TECH CO LTD

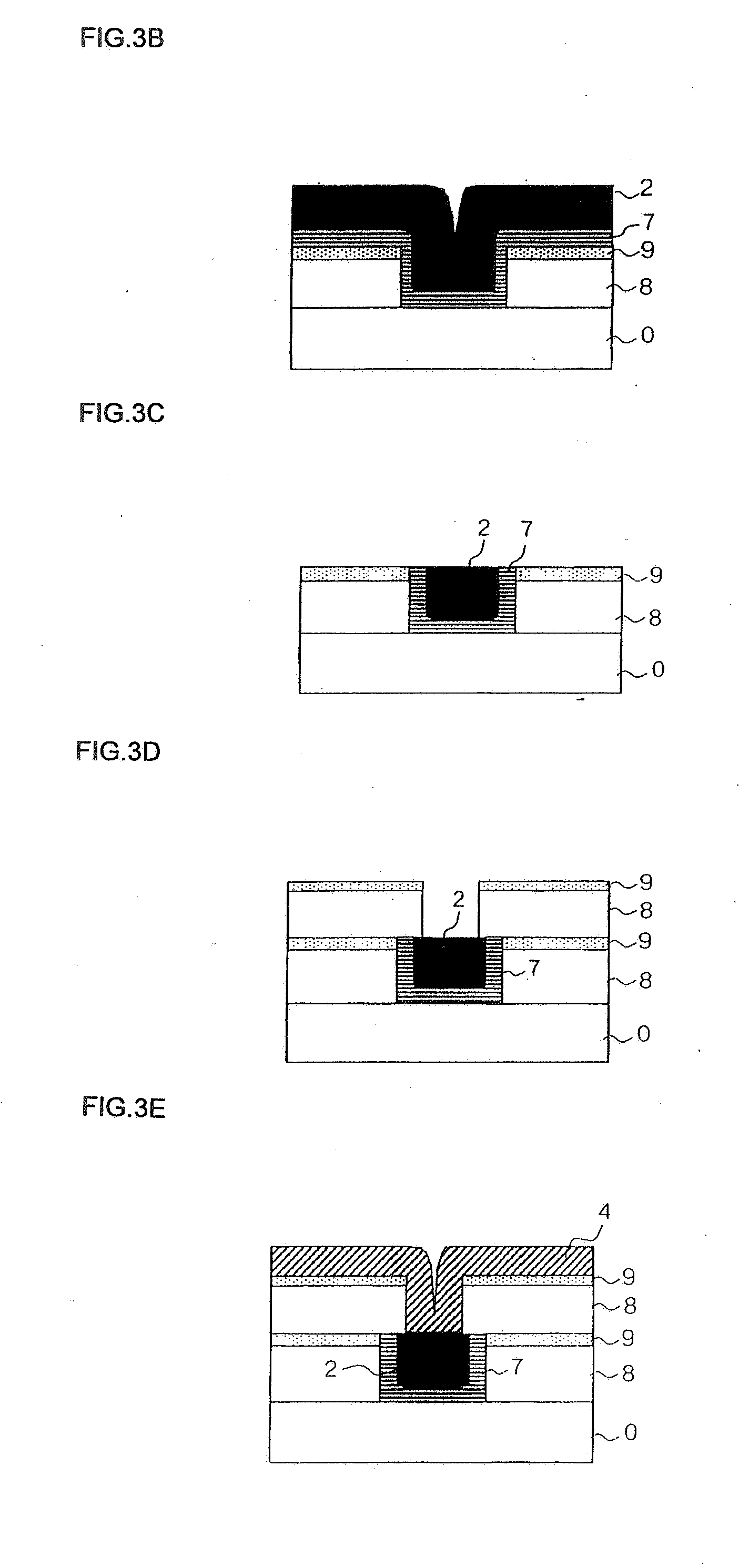

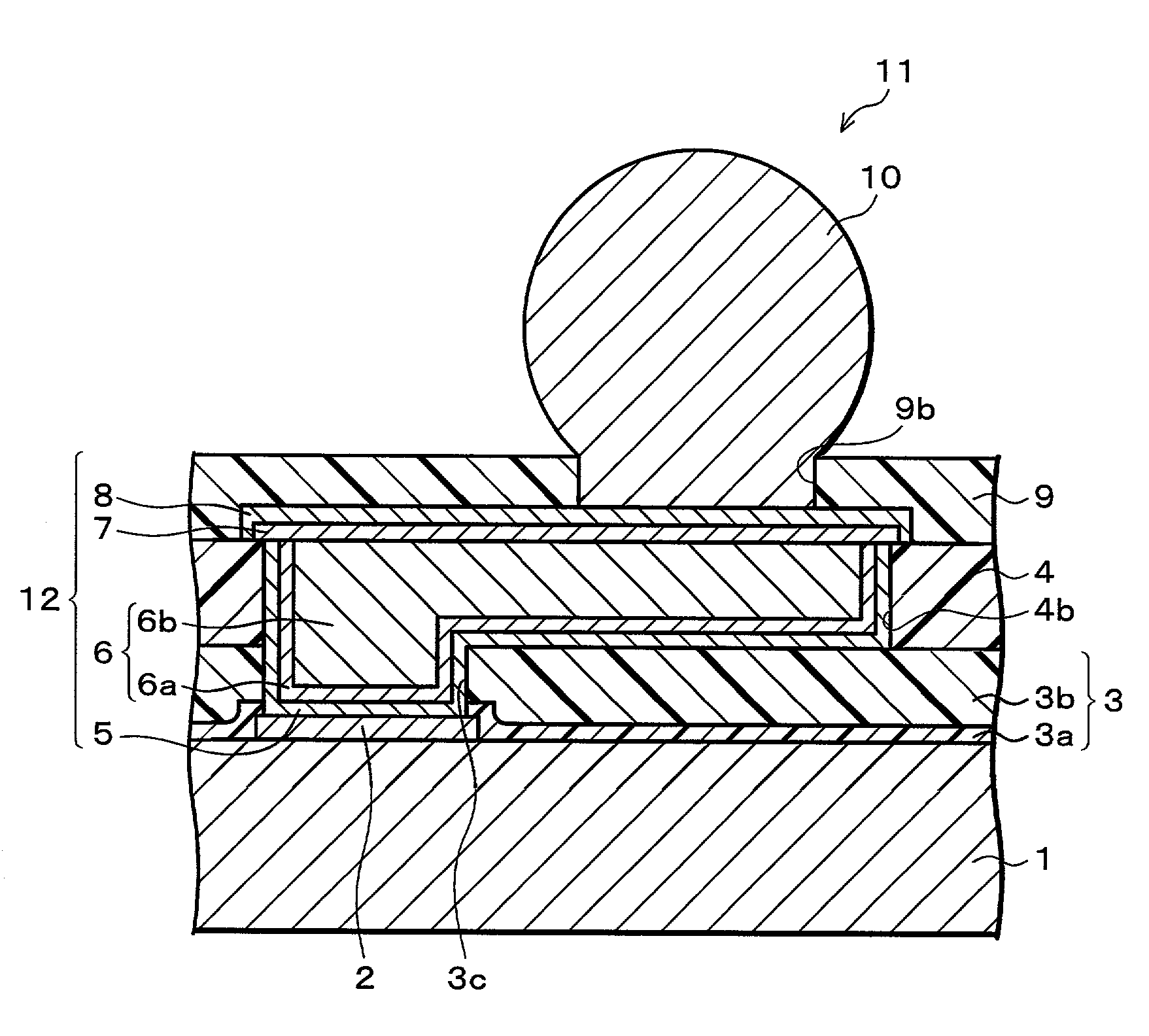

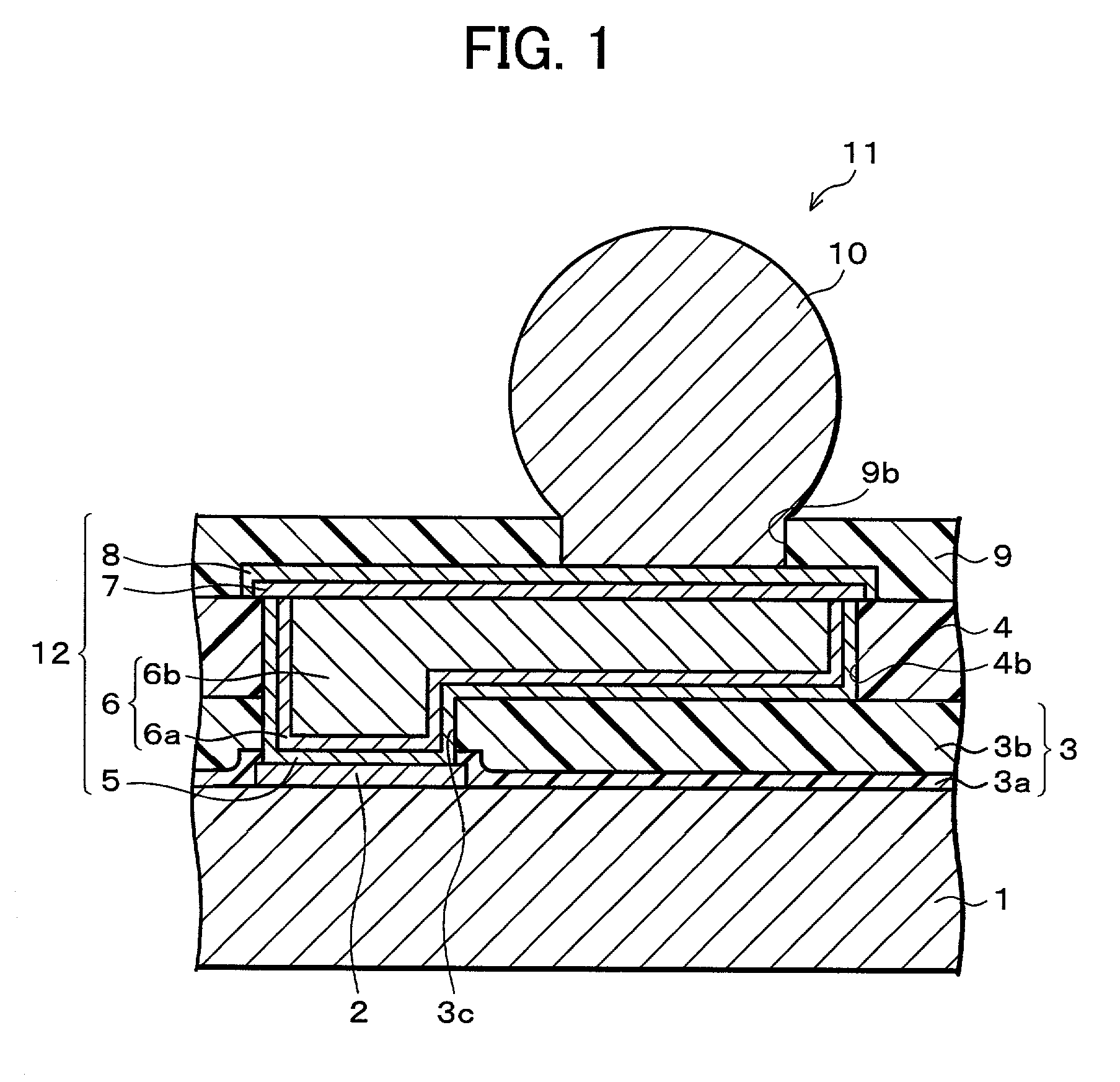

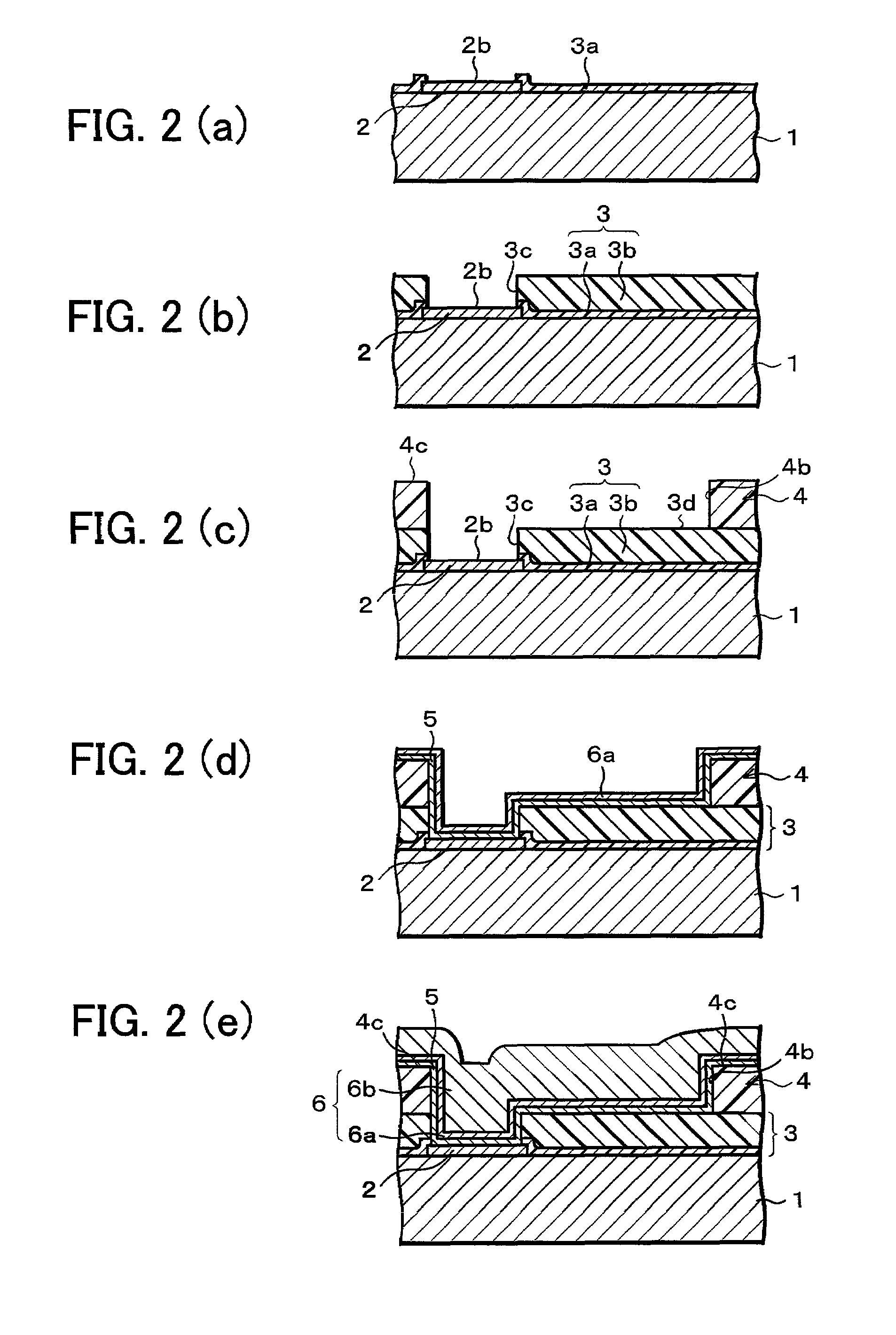

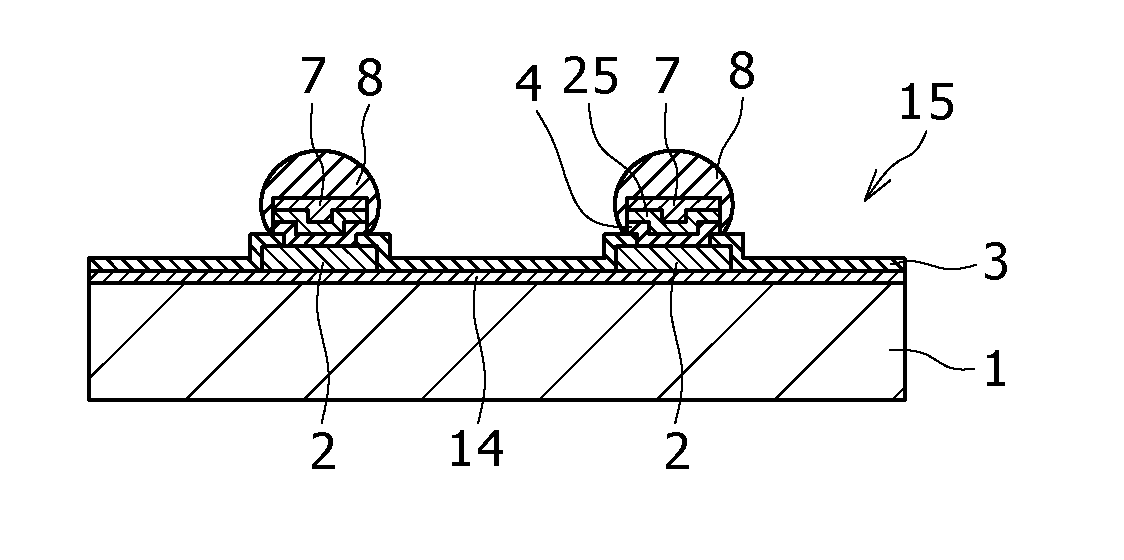

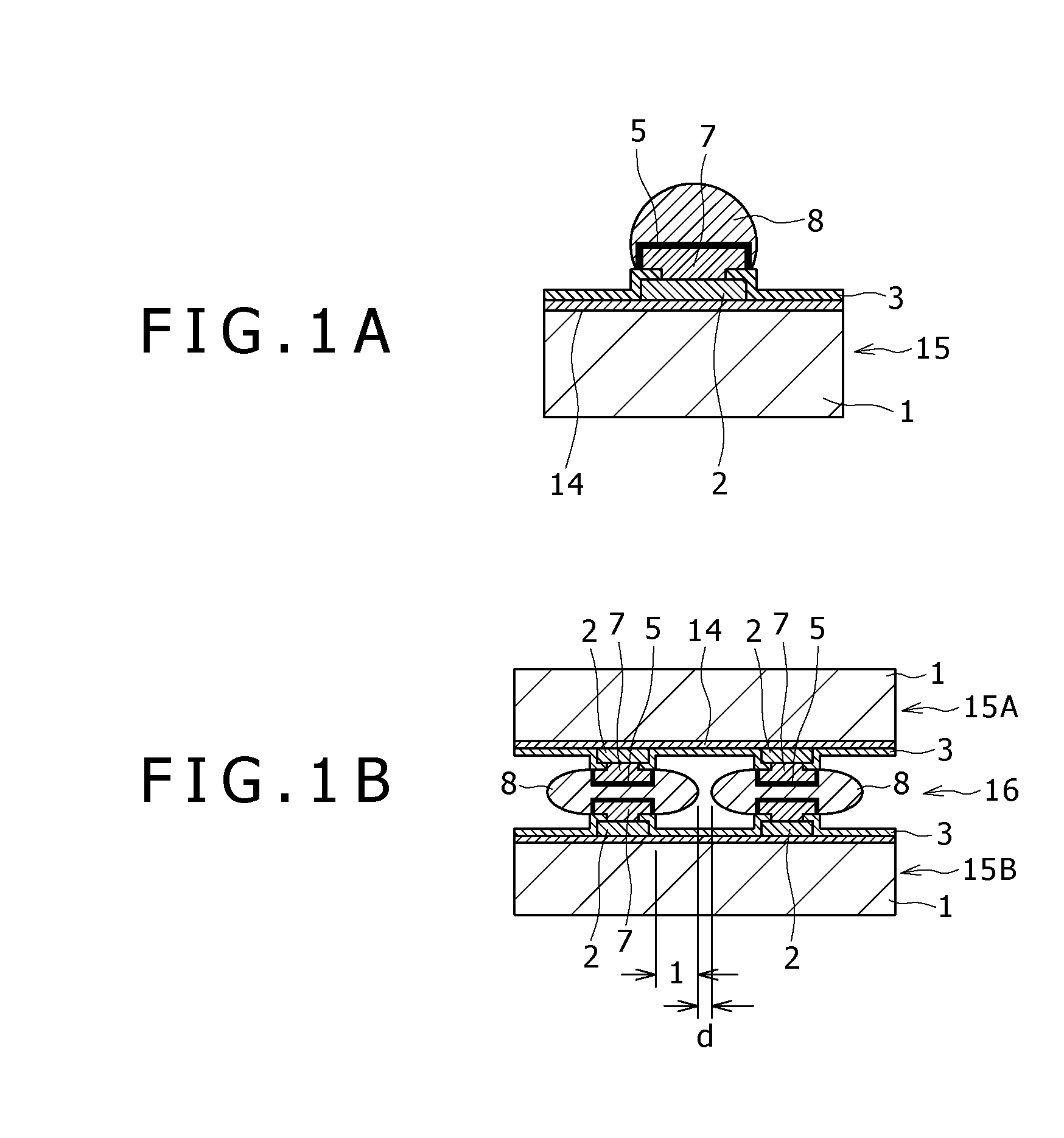

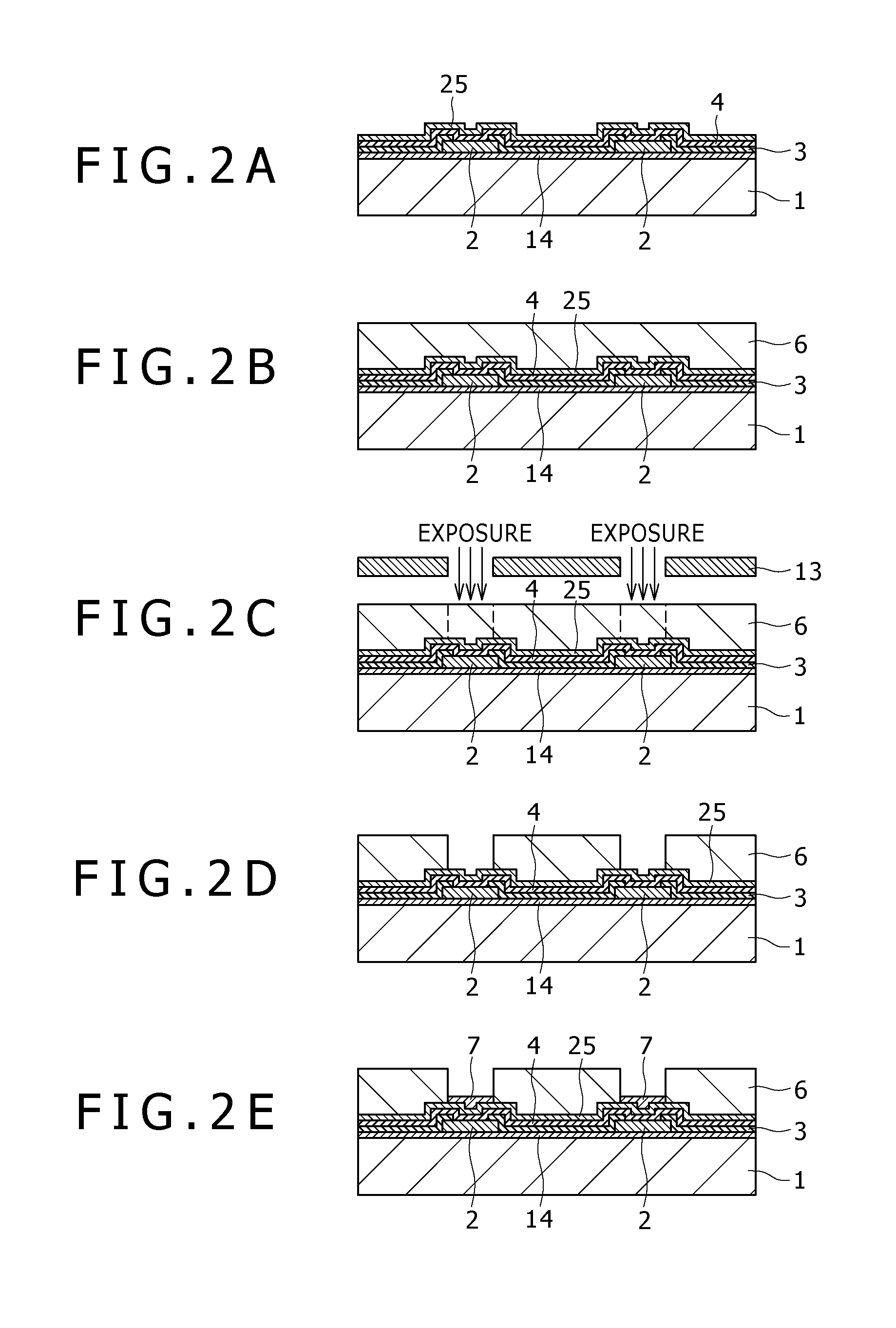

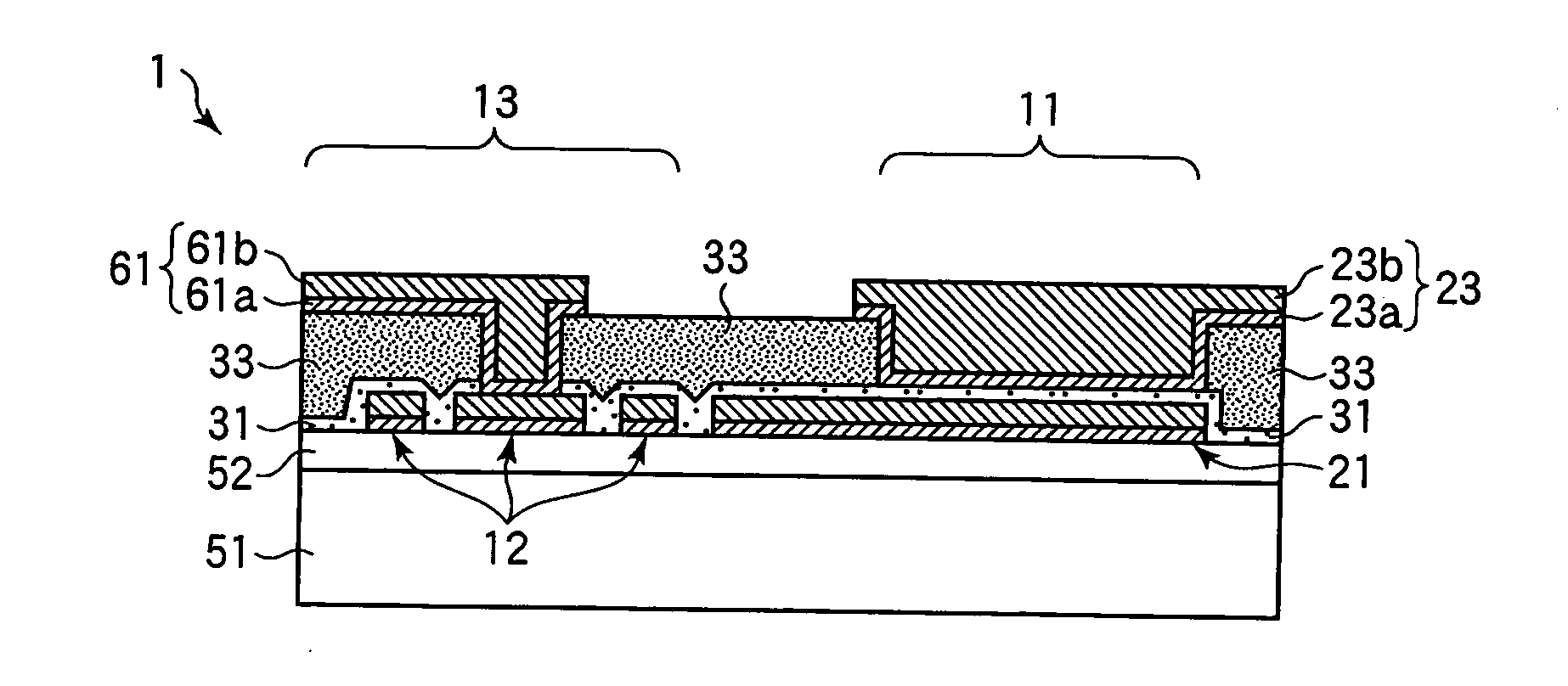

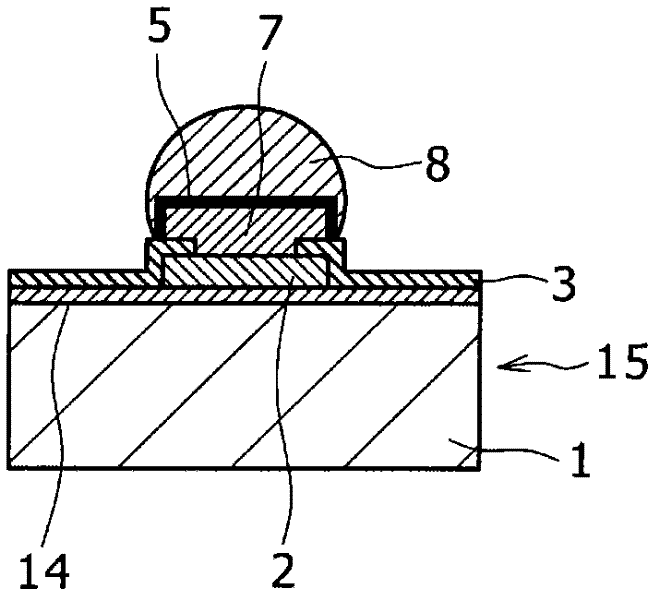

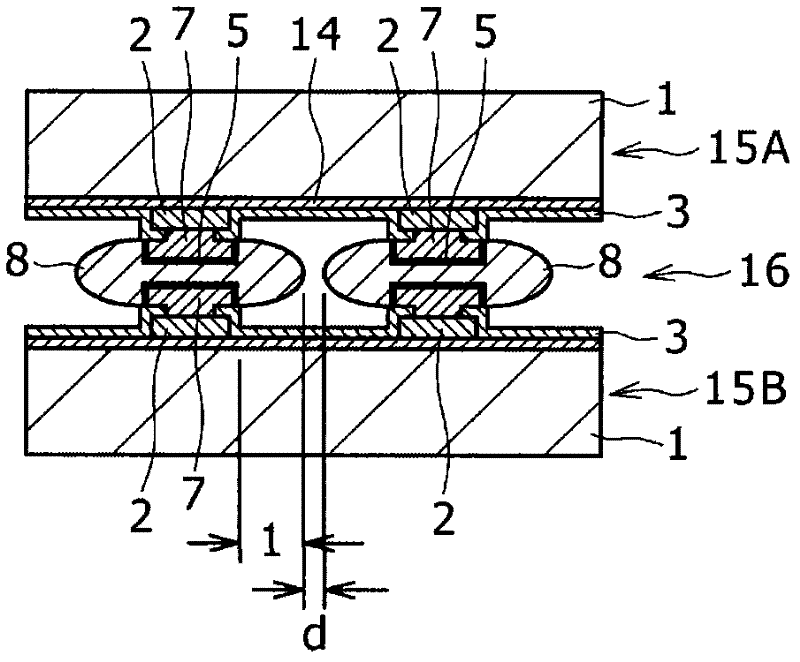

Semiconductor device, chip-on-chip mounting structure, method of manufacturing the semiconductor device, and method of forming the chip-on-chip mounting structure

InactiveUS20110193223A1Prevent short-circuitingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipSemiconductor chip

A semiconductor device includes: a semiconductor chip having a semiconductor substrate; a pad electrode formed on the semiconductor substrate; a base metal layer formed on said pad electrode; and a bump electrode formed on the base metal layer, in which an exposed surface including a side surface of the base metal layer is covered with the solder bump electrode.

Owner:SONY CORP

E-fuse and method for fabricating e-fuses integrating polysilicon resistor masks

InactiveUS20070262413A1Overcome disadvantagesAvoid flowSemiconductor/solid-state device detailsSolid-state devicesElectromigrationResistor

An E-fuse and a method for fabricating an E-fuse are provided integrating polysilicon resistor masks. The E-fuse includes a polysilicon layer defining a fuse shape including a cathode, an anode, and a fuse neck connected between the cathode and the anode silicide formation. A silicide formation is formed on the polysilicon layer with an unsilicided portion extending over a portion of the cathode adjacent the fuse neck. The unsilicided portion substantially prevents current flow in the silicide formation region of the cathode, with electromigration occurring in the fuse neck during fuse programming. The unsilicided portion has a substantially lower series resistance than the series resistance of the fuse neck.

Owner:IBM CORP

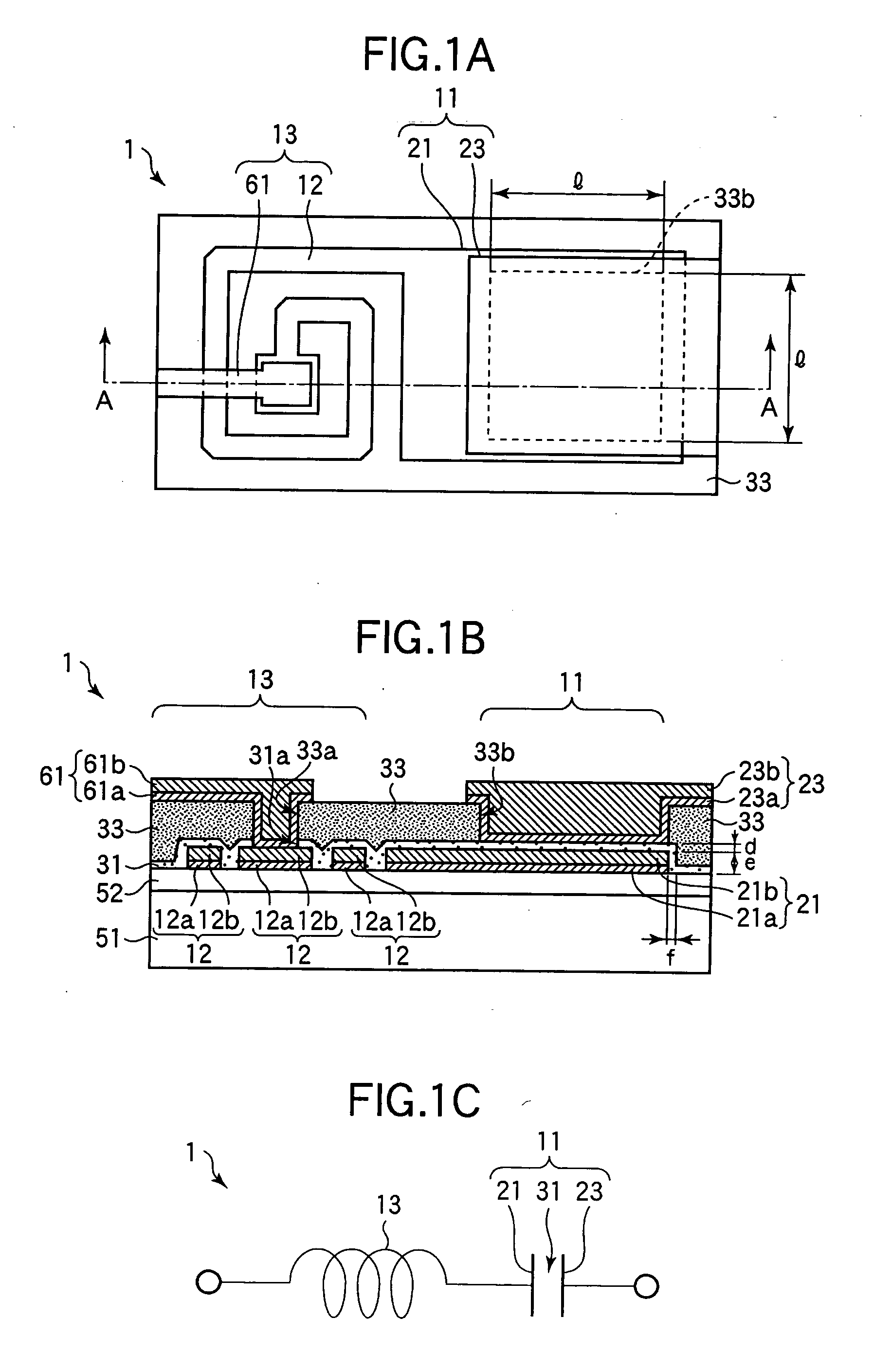

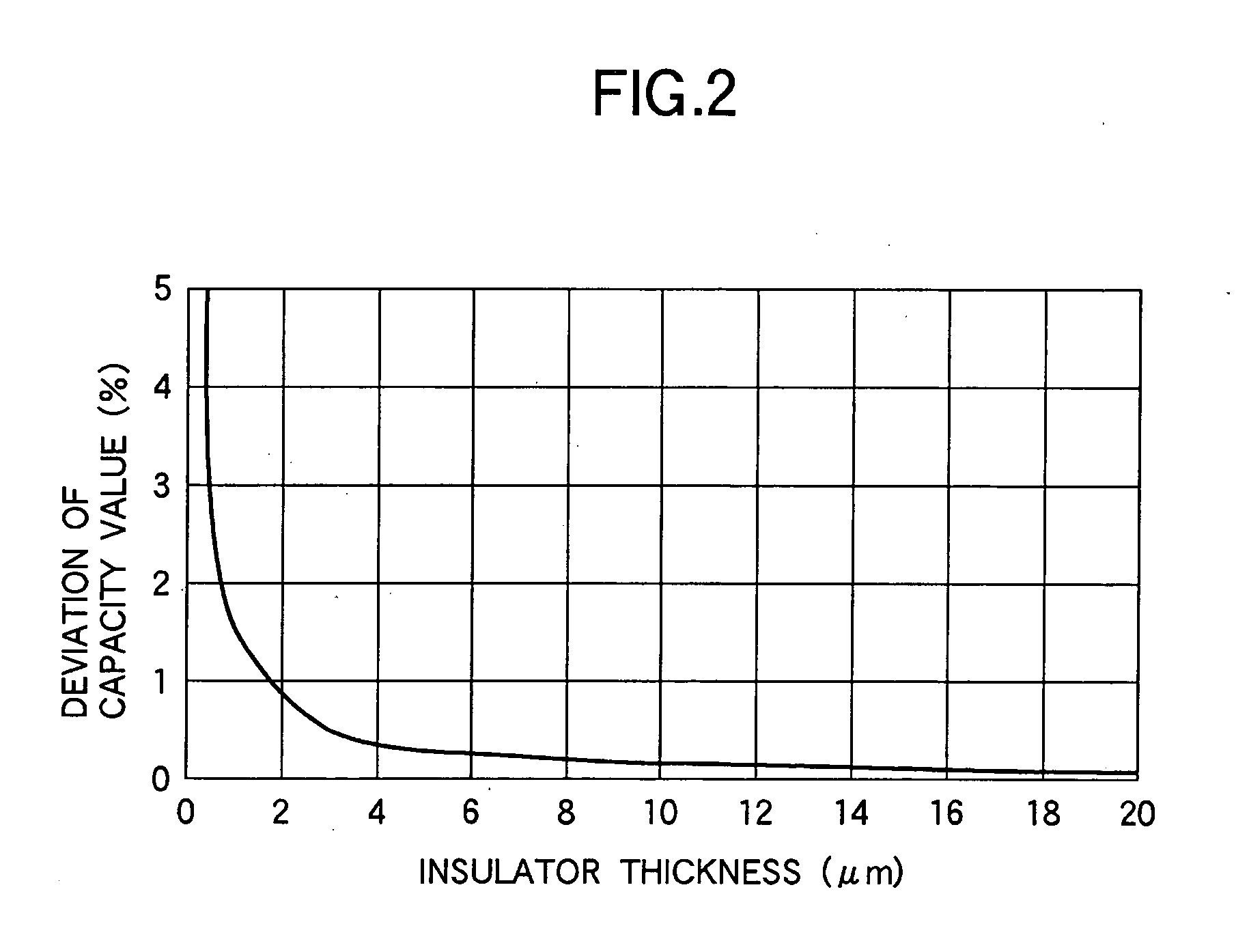

Electronic component

ActiveUS20070109719A1Accurate valuePrevent electromigrationThin/thick film capacitorFixed capacitor electrodesElectrical conductorCapacity value

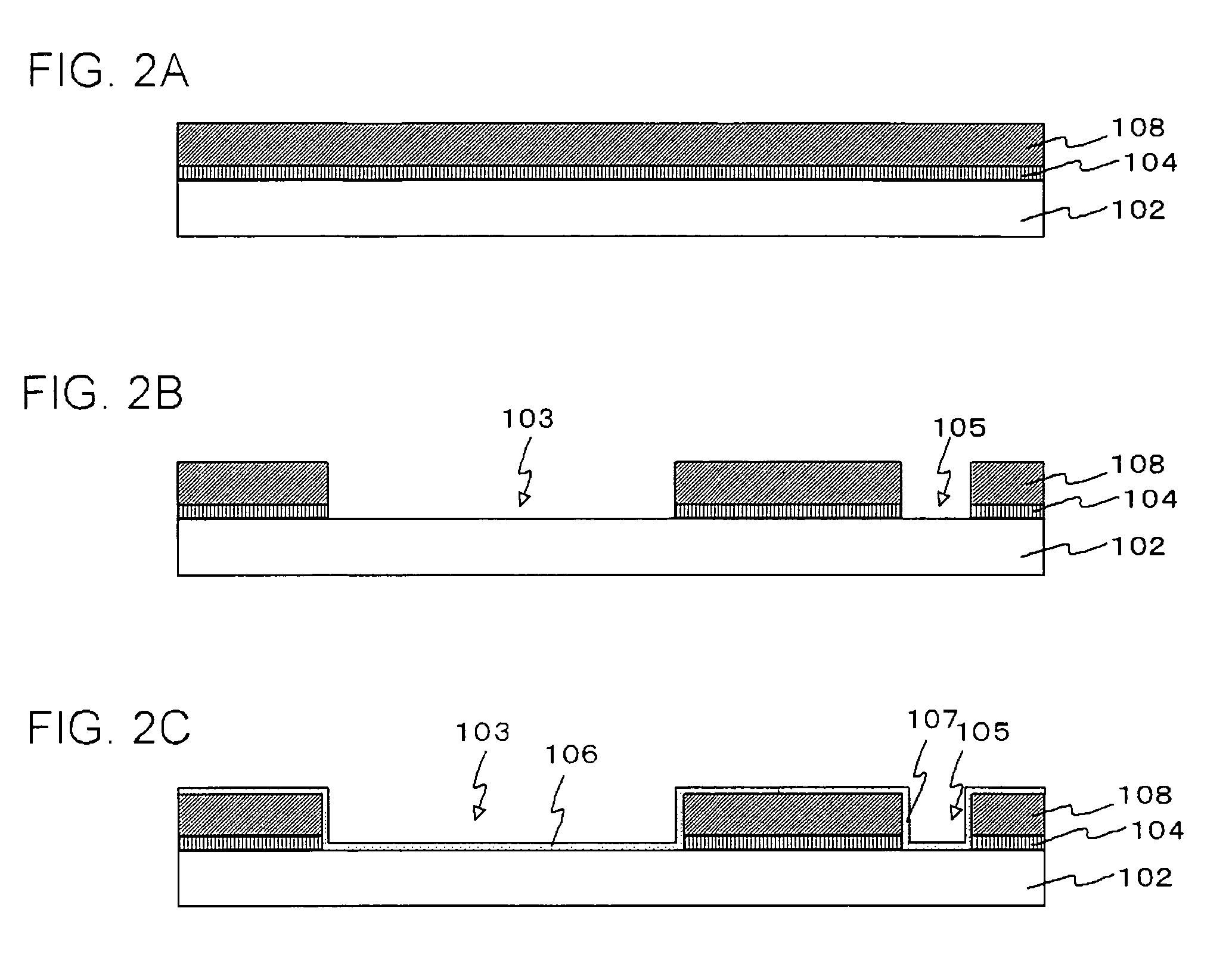

The invention relates to an electronic component including a capacitor and provides an electronic component in which electromigration can be prevented and whose capacitor element has an accurate capacity value. The electronic component includes a bottom conductor formed on a substrate, a dielectric film formed to cover the bottom conductor, an organic insulation film formed on the dielectric film, and a top conductor formed in an opening provided in the organic insulation film over the bottom conductor, the top conductor forming a capacitor element in combination with the bottom conductor and the dielectric film.

Owner:TDK CORPARATION

Novel method for electromigration and adhesion using two selective deposition

ActiveUS20150028483A1Prevent electromigrationImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDevice material

A method of manufacturing a semiconductor device includes providing a semiconductor substrate, sequentially forming an etch stop layer and an interlayer dielectric layer on the semiconductor substrate, forming a copper metal interconnect structure in the interlayer dielectric layer, forming a copper layer in the copper metal interconnect structure, forming a cobalt layer on the copper layer, and forming an aluminum nitride layer on the cobalt layer. The stack of cobalt layer and copper layer effectively suppresses electromigration caused by diffusion of the copper layer into the interlayer dielectric layer, improves the adhesion between the copper layer and the etch stop layer, and prevents delamination.

Owner:SEMICON MFG INT (SHANGHAI) CORP

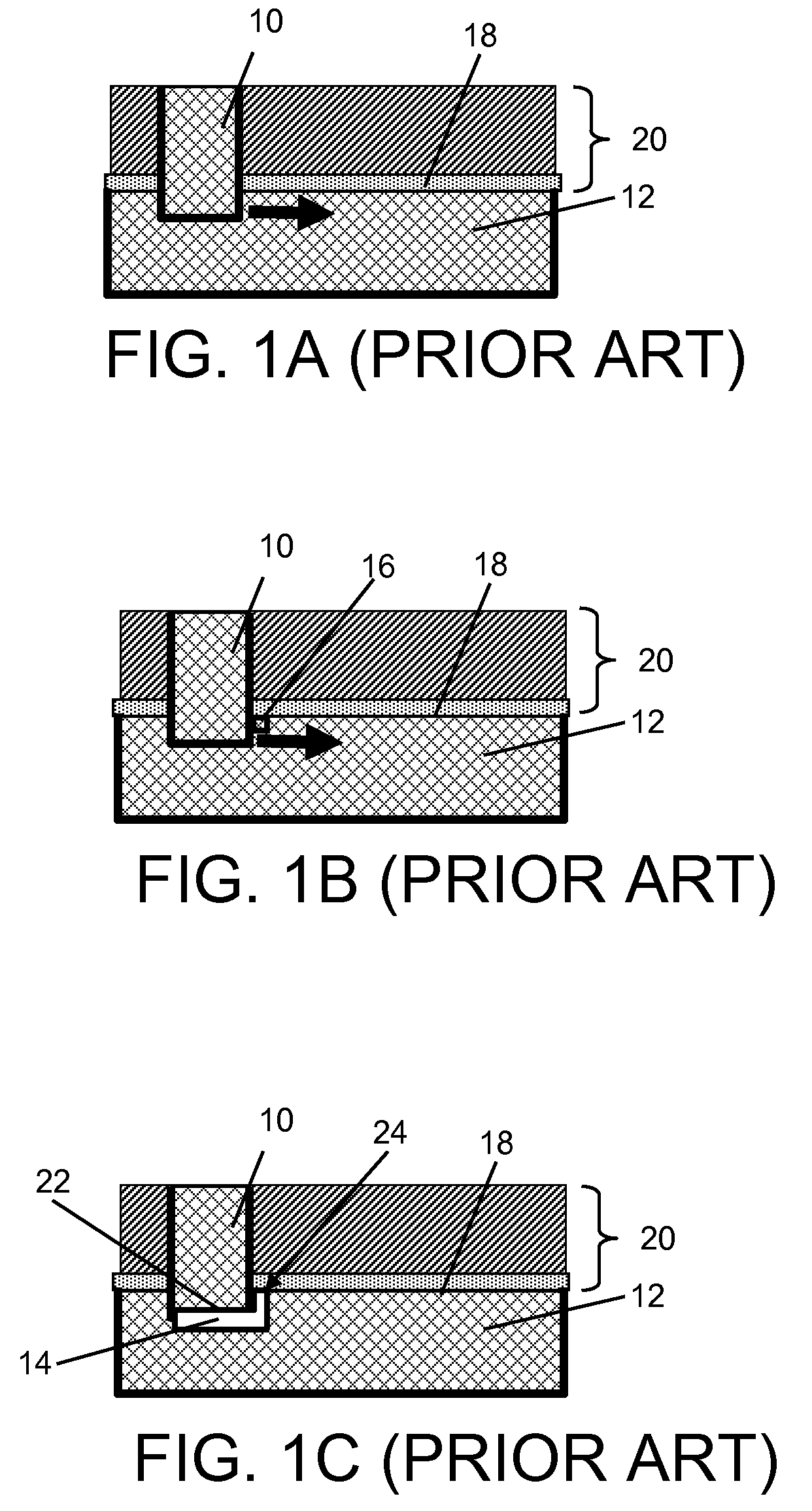

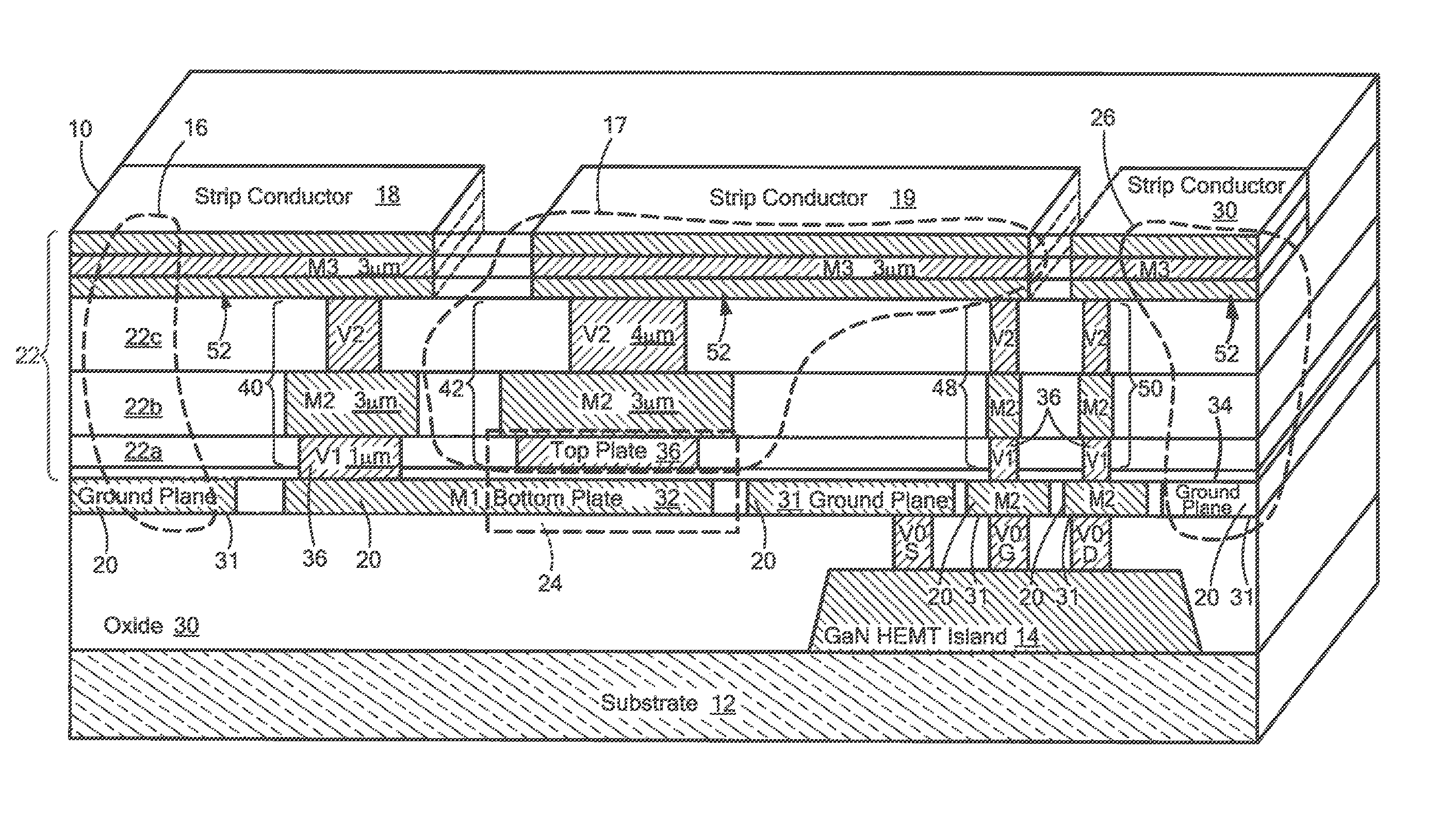

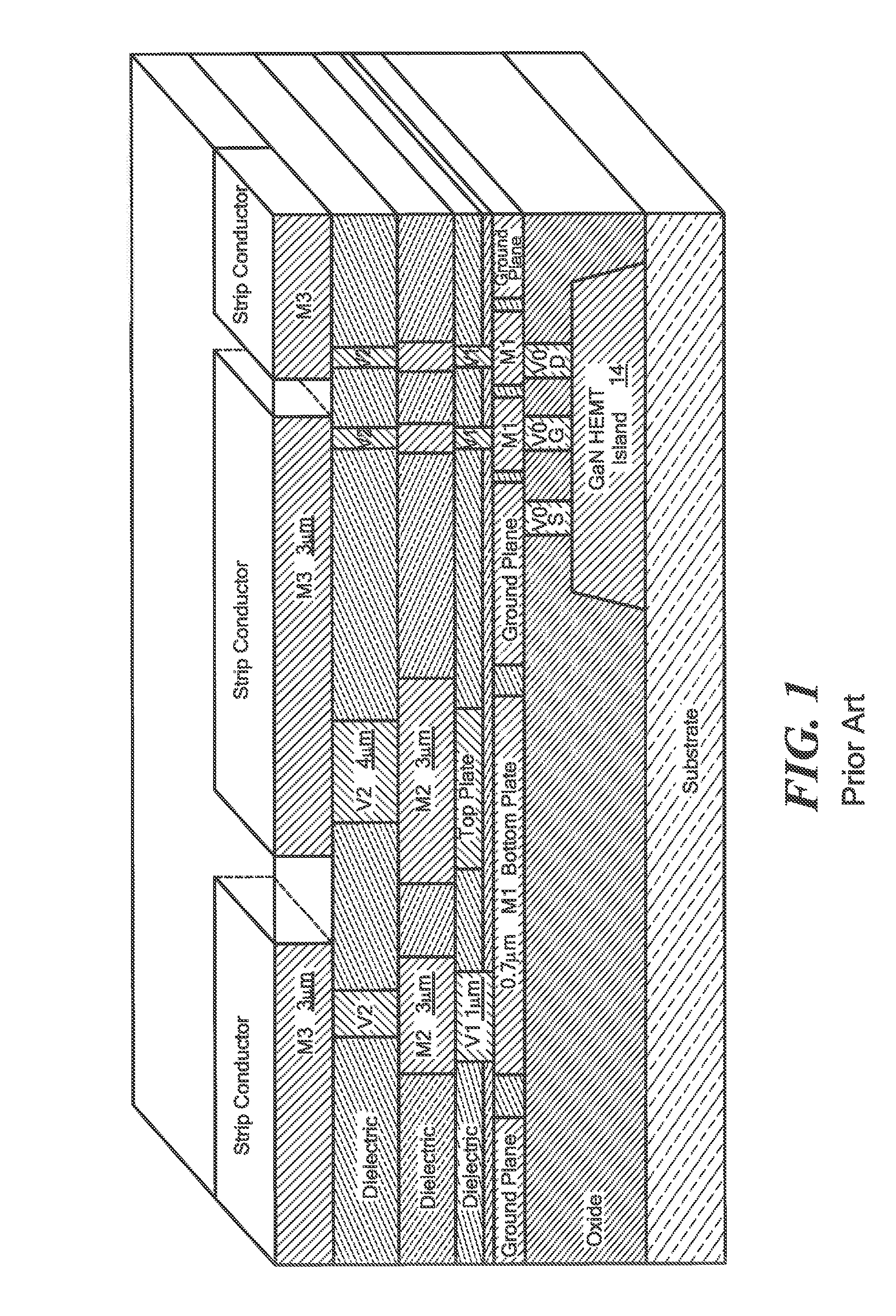

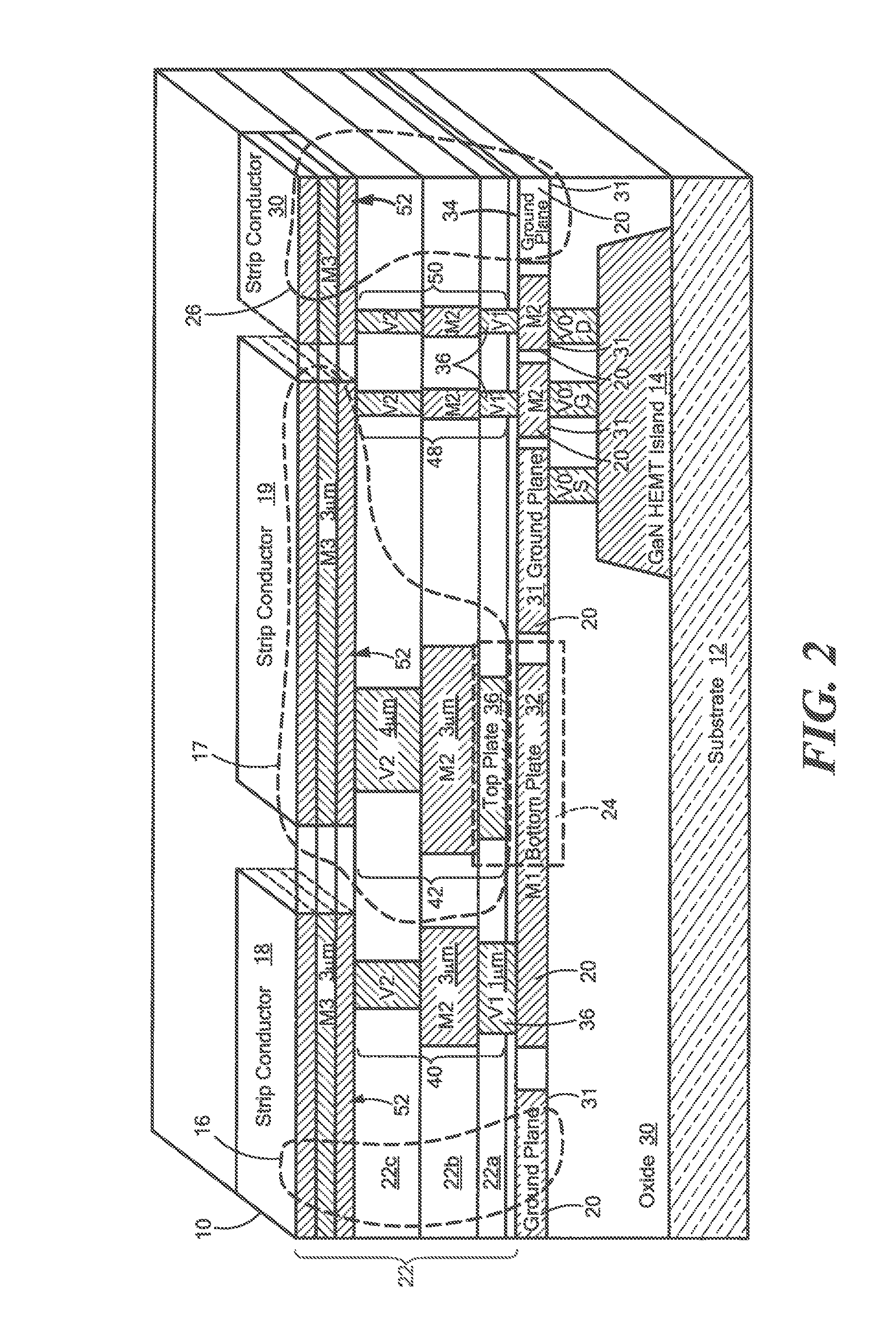

Microwave integrated circuit (MMIC) damascene electrical interconnect for microwave energy transmission

ActiveUS9478508B1Microwave transmission line loss can be lowerIncrease powerSemiconductor/solid-state device detailsSolid-state devicesMicrowaveSemiconductor structure

A semiconductor structure having a semiconductor layer having an active device therein. A dielectric structure is disposed over the semiconductor layer, such dielectric structure having open ended trench therein. An electrical interconnect level is disposed in the trench and electrically connected to the active device. A plurality of stacked metal layers is disposed in the trench. The stacked metal layers have disposed on bottom and sidewalls thereof conductive barrier metal layers.

Owner:RAYTHEON CO

Ceramic powder for electronic component packaging material and production method for ceramic powder

The invention belongs to ceramic powder for producing an electronic component packaging material and a production method for the ceramic powder. The ceramic powder comprises 35 to 85 weight percent of composite oxides containing part of BaO, B2O3, SiO2, Al2O3, MgO, CaO, SrO, ZnO, ZrO2, and TiO2, and 15 to 65 weight percent of quartz powder and colorant; and the production method comprises the following steps of preparing the composite oxides, preparing the raw materials of the ceramic powder, performing ball-milling, mixing and drying. According to the method, the composite oxides, quartz or composite oxides, quartz, and colorant are adopted, the composite oxides are sintered, and the sintered composite oxides and the quartz powder are mixed so as to obtain the ceramic powder for the packaging material, so that the method has the characteristics of simple process, high efficiency, low energy consumption and production cost and the like, and can be used for industrial large-scale production. The ceramic powder which is prepared by the method can be sintered at the temperature of between 800 and 1,000 DEG C by the conventional method to form the electronic component packaging material and a base plate for a chip, wherein the thermal expansion coefficient of the electronic component packaging material and the base plate is 10<-20> to 10<-6> / DEG C, and the electronic component packaging material and the base plate are high and reliable in comprehensive performance.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

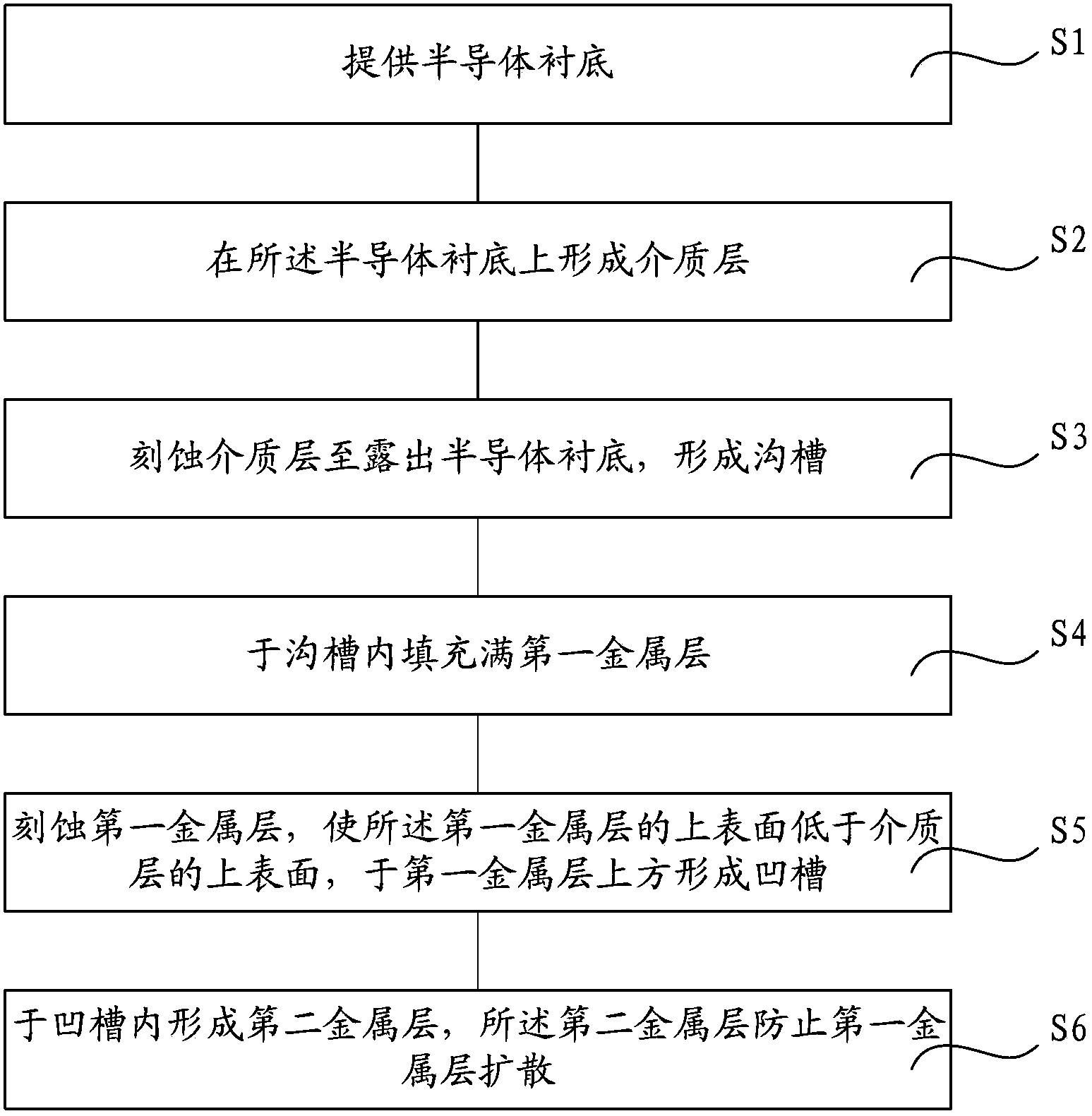

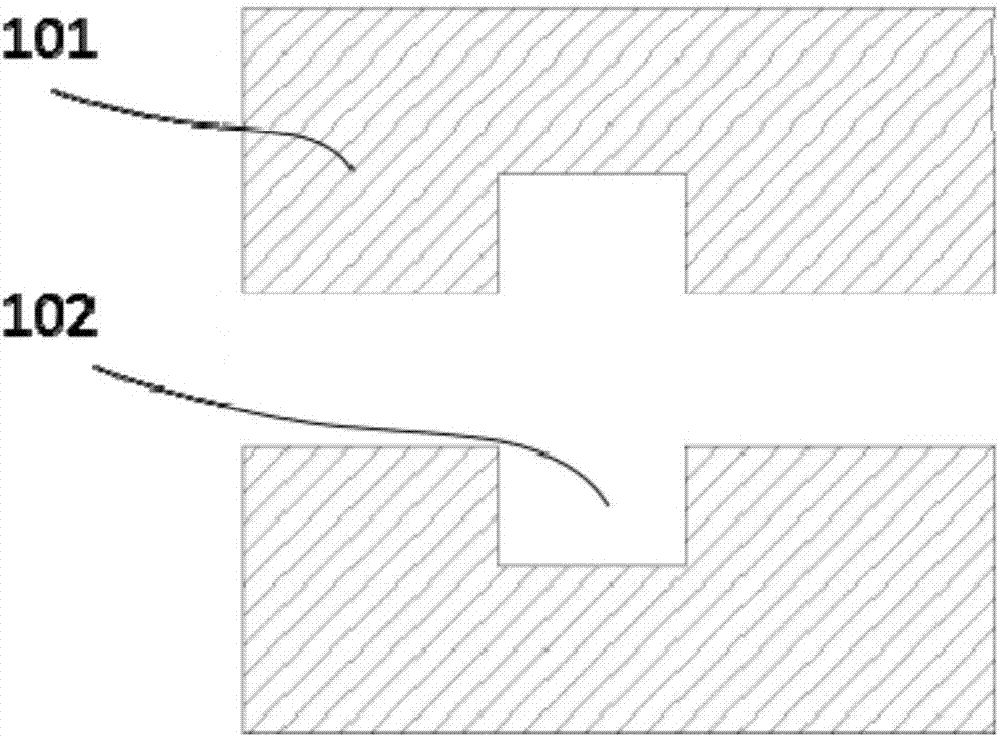

Interconnection structure and its formation method

ActiveCN103474416APrevent electromigrationPrevent degradationSemiconductor/solid-state device detailsSolid-state devicesInterconnectionFailure causes

An interconnection structure and its formation method are disclosed. The interconnection structure comprises a semiconductor substrate, a dielectric layer positioned on the semiconductor substrate, a first metal layer positioned on the semiconductor substrate and a second metal layer positioned, wherein the first metal layer is positioned in the dielectric layer, the upper surface of the first metal layer is lower than the upper surface of the dielectric layer, and a groove is arranged above the first metal layer. The interconnection structure also comprises a second metal layer which is positioned in the groove and is used for preventing diffusion of the first metal layer. According to the interconnection structure and its formation method, the second metal layer is deposited on the surface of the first metal layer positioned in the dielectric layer so as to prevent electromigration of atoms in the first metal layer. And then, the interconnection structure performance degradation or failure caused by electromigration of atoms in the first metal layer is avoided, and electrical properties of the formed interconnection structure are raised.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device, chip-on-chip mounting structure, method of manufacturing the semiconductor device, and method of forming the chip-on-chip mounting structure

InactiveCN102163578AIncrease intervalIncreasing the thicknessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

The invention provides a semiconductor device, a chip-on-chip mounting structure, a method of manufacturing the semiconductor device and a method of forming the chip-on-chip mounting structure. The semiconductor device includes: a semiconductor chip having a semiconductor substrate; a pad electrode formed on the semiconductor substrate; a base metal layer formed on said pad electrode; and a bump electrode formed on the base metal layer, in which an exposed surface including a side surface of the base metal layer is covered with the solder bump electrode. As a result, even when the interval between the adjacent solder bump electrodes is reduced, the yield and reliability of the bonding are enhanced.

Owner:SONY CORP

Manufacturing method of copper interconnection structure

ActiveCN102881633APrevent proliferationImprove reliabilitySemiconductor/solid-state device manufacturingManganeseInterconnection

The invention discloses a manufacturing method of a copper interconnection structure, which comprises the steps as follows: a) providing a semiconductor substrate, forming an oxygen-containing dielectric layer on the upper surface of the semiconductor substrate, and forming a groove for forming the copper interconnection structure in the oxygen-containing dielectric layer, b) forming a tantalum metal layer on the oxygen-containing layer and in the groove, c) forming a copper-manganese seed crystal layer on the tantalum metal layer, and d) forming the copper interconnection structure on the copper-manganese seed crystal layer in the groove and performing an annealing process. According to the manufacturing method, the tantalum metal layer is formed between the oxygen-containing dielectric layer and the copper-manganese seed crystal layer, the annealing process is performed to form a thinner anti-diffusion barrier layer by reactions of oxygen in the oxygen-containing dielectric layer and manganese in the copper-manganese seed crystal layer with the tantalum metal layer, cooper is effectively prevented from diffusing to the oxygen-containing dielectric layer, and the electric resistance of the copper interconnection structure is not affected.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Radio frequency micro-strip structure for Ti/Ni/Ag material system

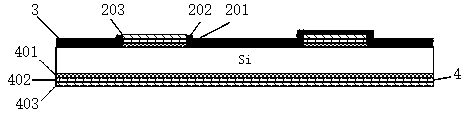

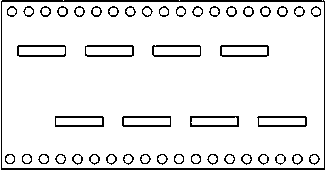

PendingCN108448217AImprove performanceLow costSemiconductor/solid-state device detailsSolid-state devicesHigh resistancePunching

The invention discloses a radio frequency micro-strip structure for the punching and non-punching structures of a Ti / Ni / Ag material system, and a manufacturing method thereof. According to the invention, a punching structure is composed of a through hole, a W covering layer, a passivation layer, a front surface Ti / Ni / Ag metal laminated layer, a Si substrate and a back metal laminated layer. A non-punching structure is composed of a passivation layer, a front surface Ti / Ni / Ag metal laminated layer, a Si substrate and a back metal laminated layer. The front surface Ti / Ni / Ag metal laminated layeris provided with patterns. The Si substrate is made of the high-resistance Si material. According to the invention, the pollution problem of the front metal on IC process lines when the front metal is Au can be avoided. Meanwhile, the complex problem of the technological process caused by the front metal of Cu can also be avoided. The process compatibility of the manufacturing process and the ICprocess is met. At the same time, Ag, lower in resistivity than Au and Cu, is introduced into the material system, so that the radio frequency micro-strip structure is smaller in transmission loss. Inaddition, the passivation layer can be added, so that the electromigration of Ag can be effectively prevented. Finally, during the punching process, the punching structure does not completely penetrate the substrate. The adsorption leakage of the substrate during the subsequent IC process is avoided.

Owner:SOUTHWEAT UNIV OF SCI & TECH

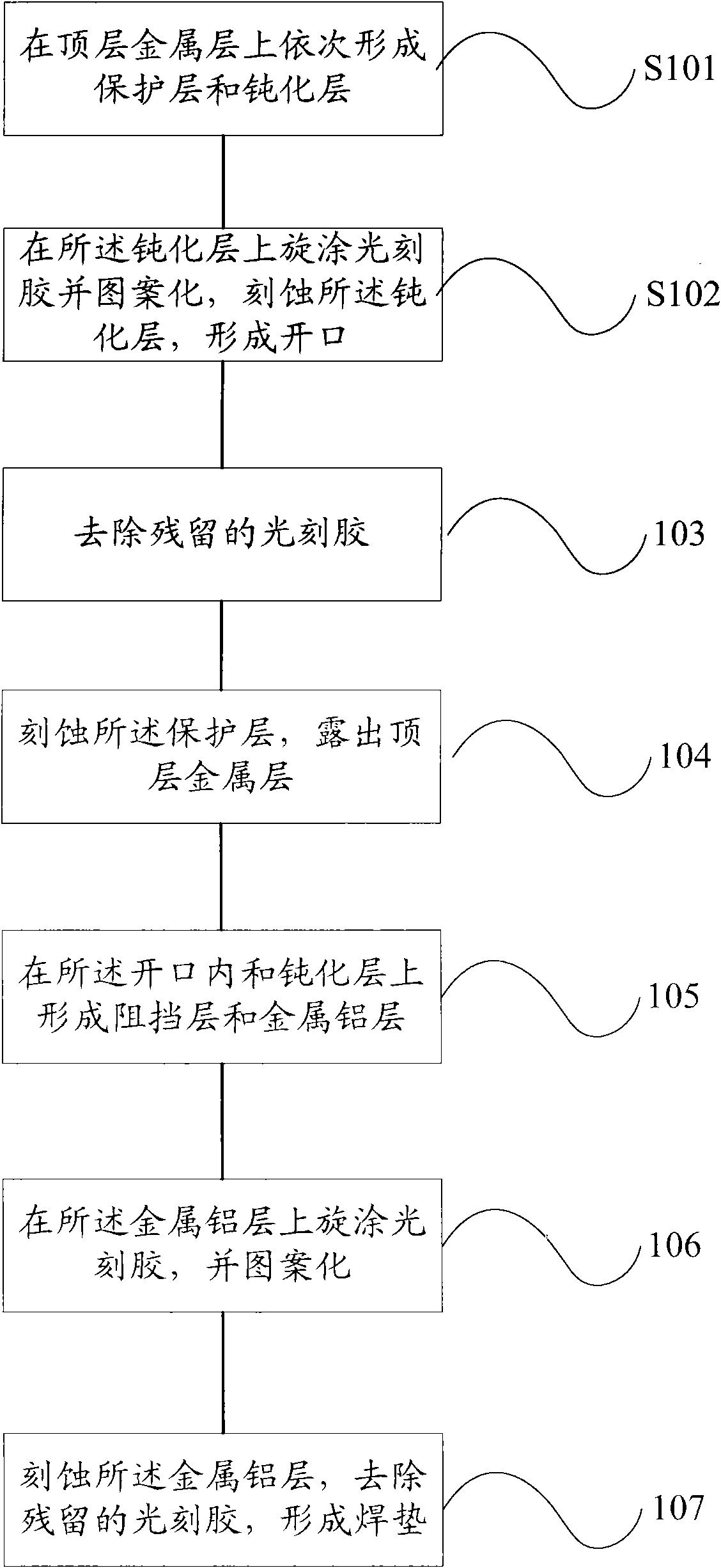

Method for manufacturing semiconductor device

InactiveCN102024720AImprove reliabilityPrevent oxidationSemiconductor/solid-state device manufacturingOxygenPhotoresist

The invention discloses a method for manufacturing a semiconductor device, which comprises: providing a substrate, wherein a top metal layer is formed on the surface of the substrate; forming a protective layer on the top metal layer; annealing the protective layer; forming a passivated layer on the protective layer; photoetching and etching the passivated layer to form a solder pad opening; forming a barrier layer and a metal aluminum layer in the solder pad opening and on the passivated layer; and photoetching and etching the metal aluminum layer to form a solder pad. In the invention, residual needle holes in the protective layer are eliminated or reduced, oxidization of the top metal layer by oxygen passing through the needle holes during ashing photoresist removal is prevented, and electromigration problem thus caused is avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

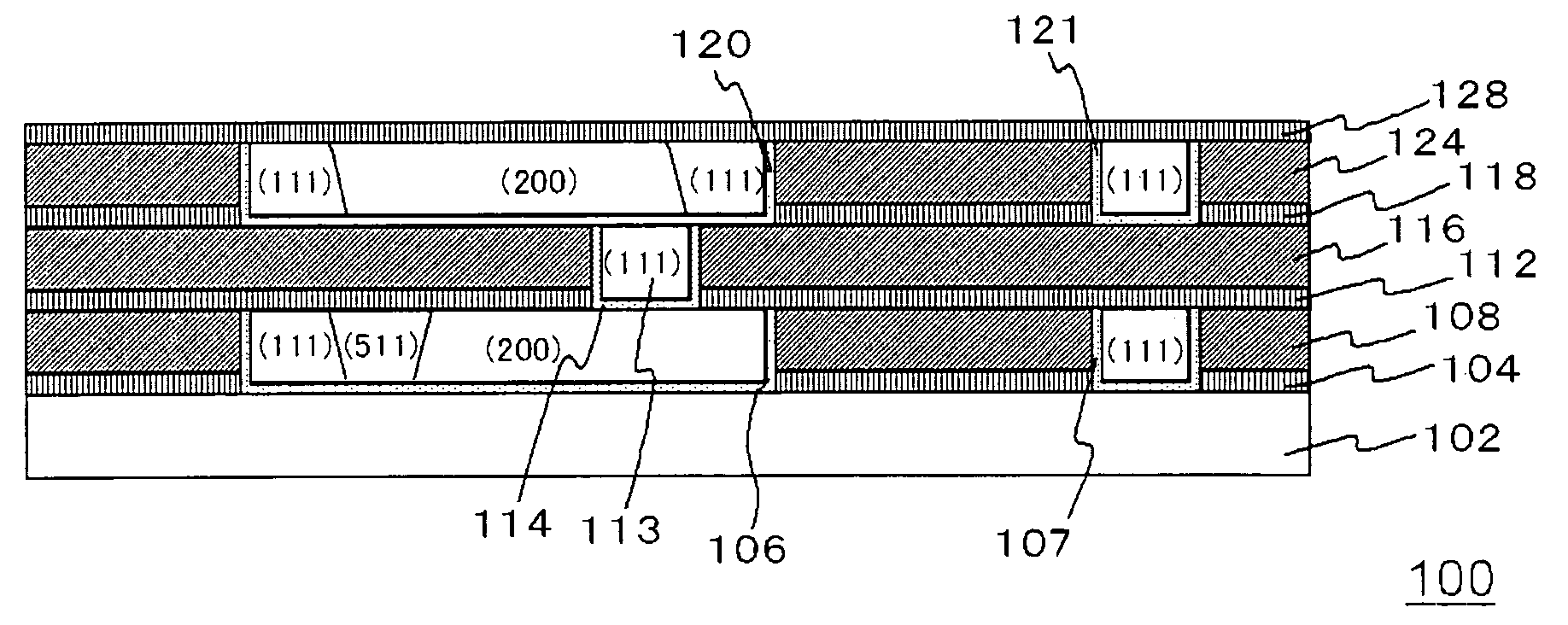

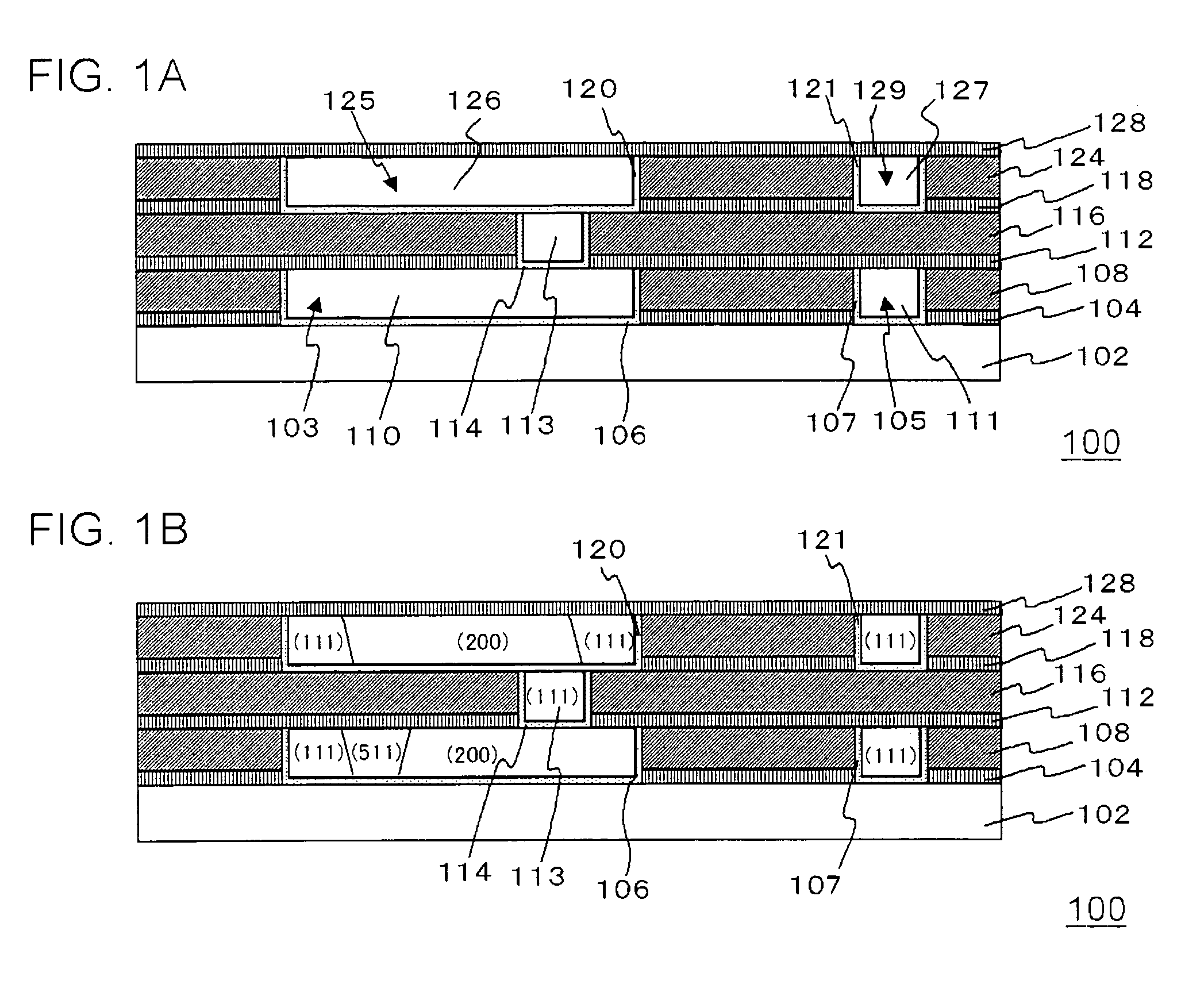

Narrow and wide copper interconnections composed of (111), (200) and (511) surfaces

ActiveUS7728432B2Suppress generationPrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

A semiconductor device includes: a semiconductor substrate; an insulating film provided on the semiconductor substrate; a plurality of copper interconnections provided on the same level in the insulating film. The copper interconnection includes: a first copper interconnection having a relatively narrow width; and a second copper interconnection having a relatively wide width. The first copper interconnection has the top surface thereof principally composed of copper, and the second copper interconnection has the top surface thereof principally composed of copper.

Owner:RENESAS ELECTRONICS CORP

Semiconductor integrated circuit device and power source wiring method therefor

InactiveUS7786513B2Large regionPrevent electromigrationSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorElectric potential

In a semiconductor integrated circuit device, from a first power source strap supplying a potential to a first standard cell receiving a supply of the potential, the potential is supplied via a first cell power source line having a constant width. The width of the first cell power source line is determined in accordance with power consumed by the first standard cell and with the number of standard cells that can be placed between the first power source strap and a third power source strap.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

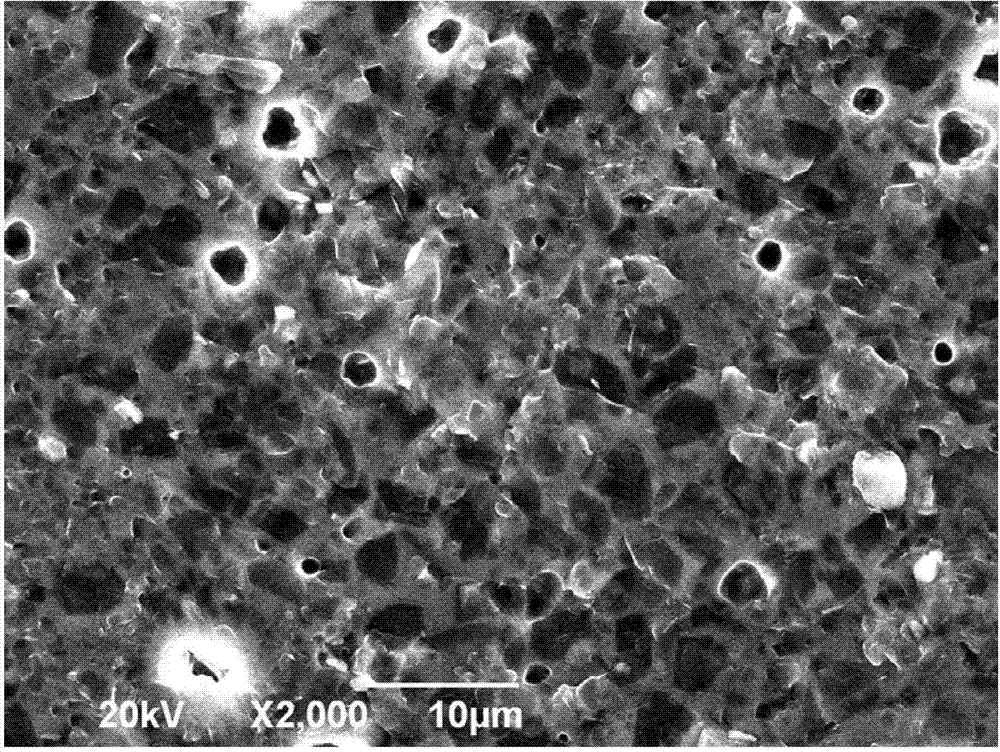

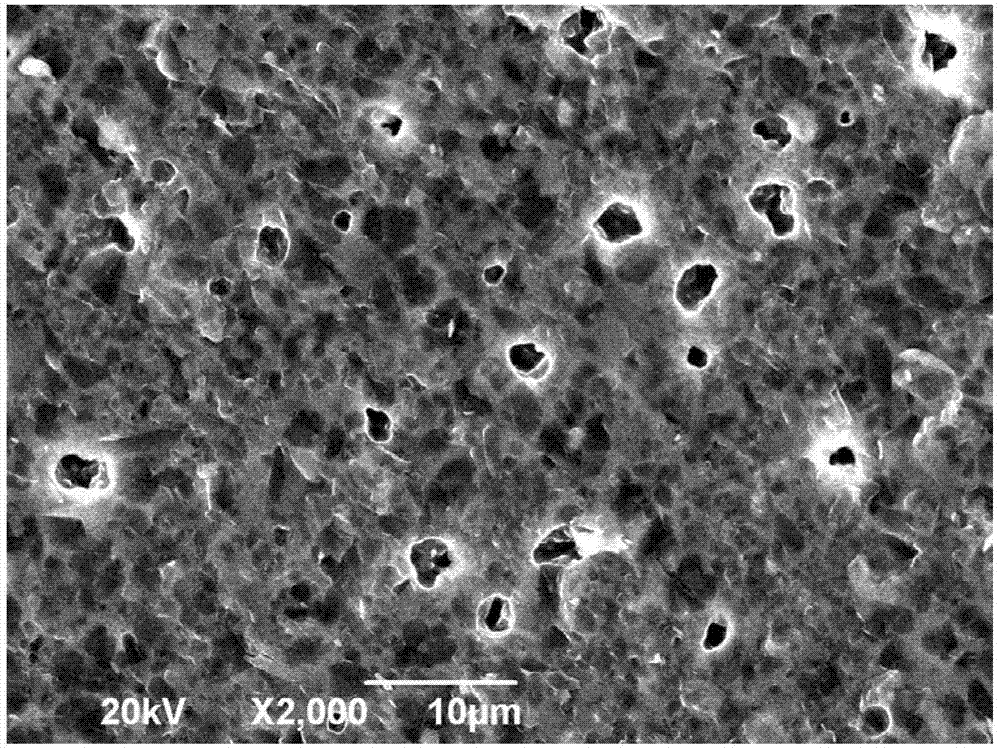

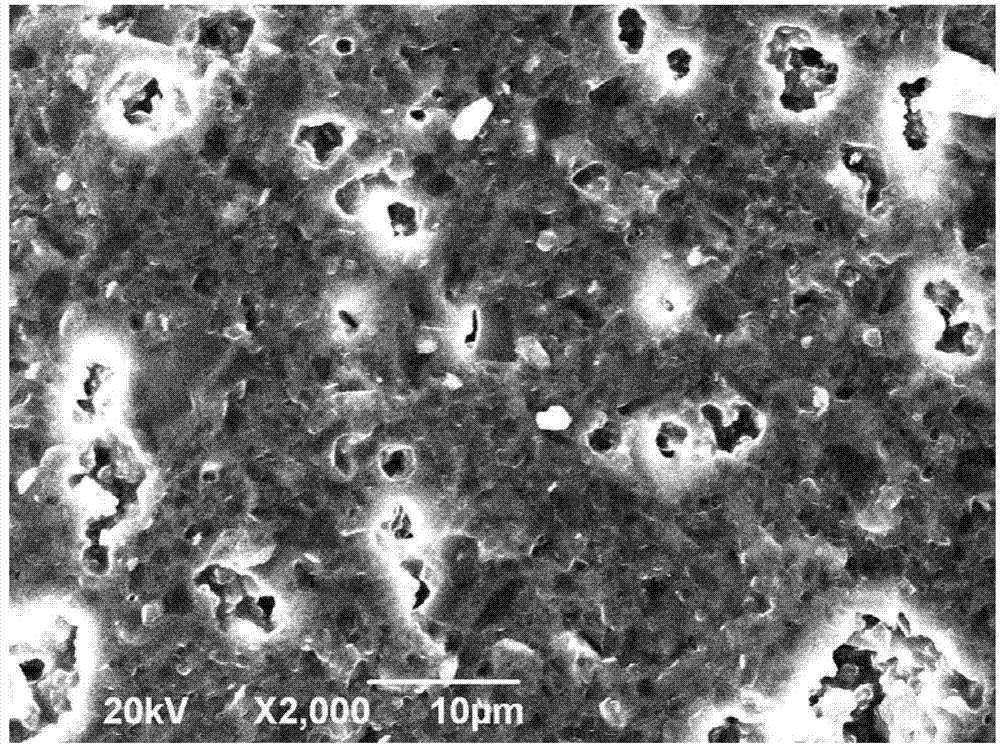

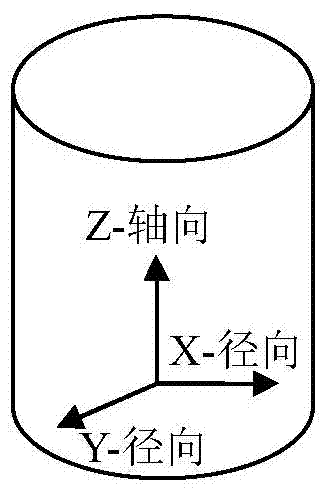

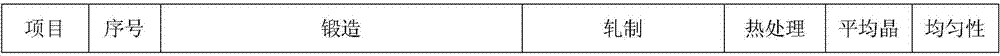

Processing method of copper alloy target material

ActiveCN104746020AImprove stabilityImprove uniformityVacuum evaporation coatingSputtering coatingManufacturing technologyThermal insulation

The invention discloses a processing method of a copper alloy target material and belongs to the field of a sputtering target material manufacturing technology. The method mainly comprises the following steps: uniformly heating a high-purity copper alloy ingot to 350-600 DGE C by a heating furnace and carrying out thermal insulation for 1-3 h; carrying out hot forging on the ingot respectively in the X / Y / Z three directions by forging equipment; carrying out multi-pass reciprocating cold-rolling on the forged billet by a two-roll mill with the pass deformation being 8-20% and the total deformation being 70-90%; and treating the rolled billet by a thermal treatment furnace at 250-450 DEG C and carrying out thermal insulation for 2-4 h so as to obtain a high-purity copper alloy sputtering target billet which meets requirements. Average grain size of the copper alloy target material obtained by the above method is below 30 microns, and texture is distributed at random. The target material can meet the technological manufacture procedure of an integrated circuit 45nm and below.

Owner:GRIKIN ADVANCED MATERIALS

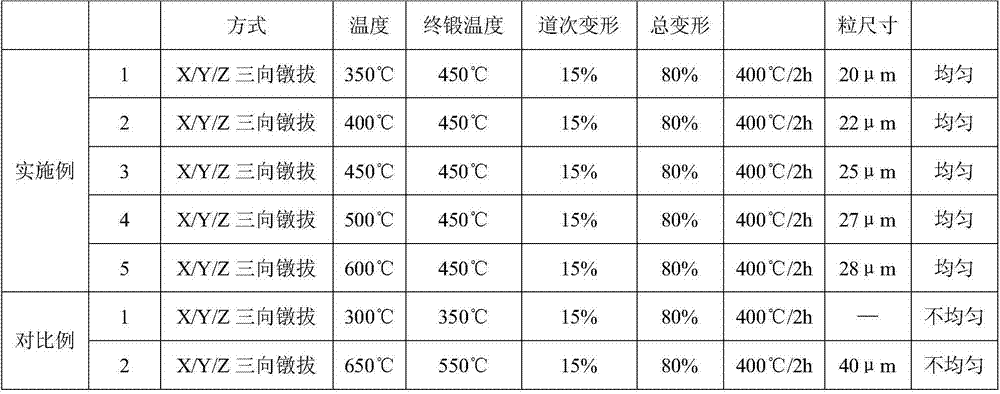

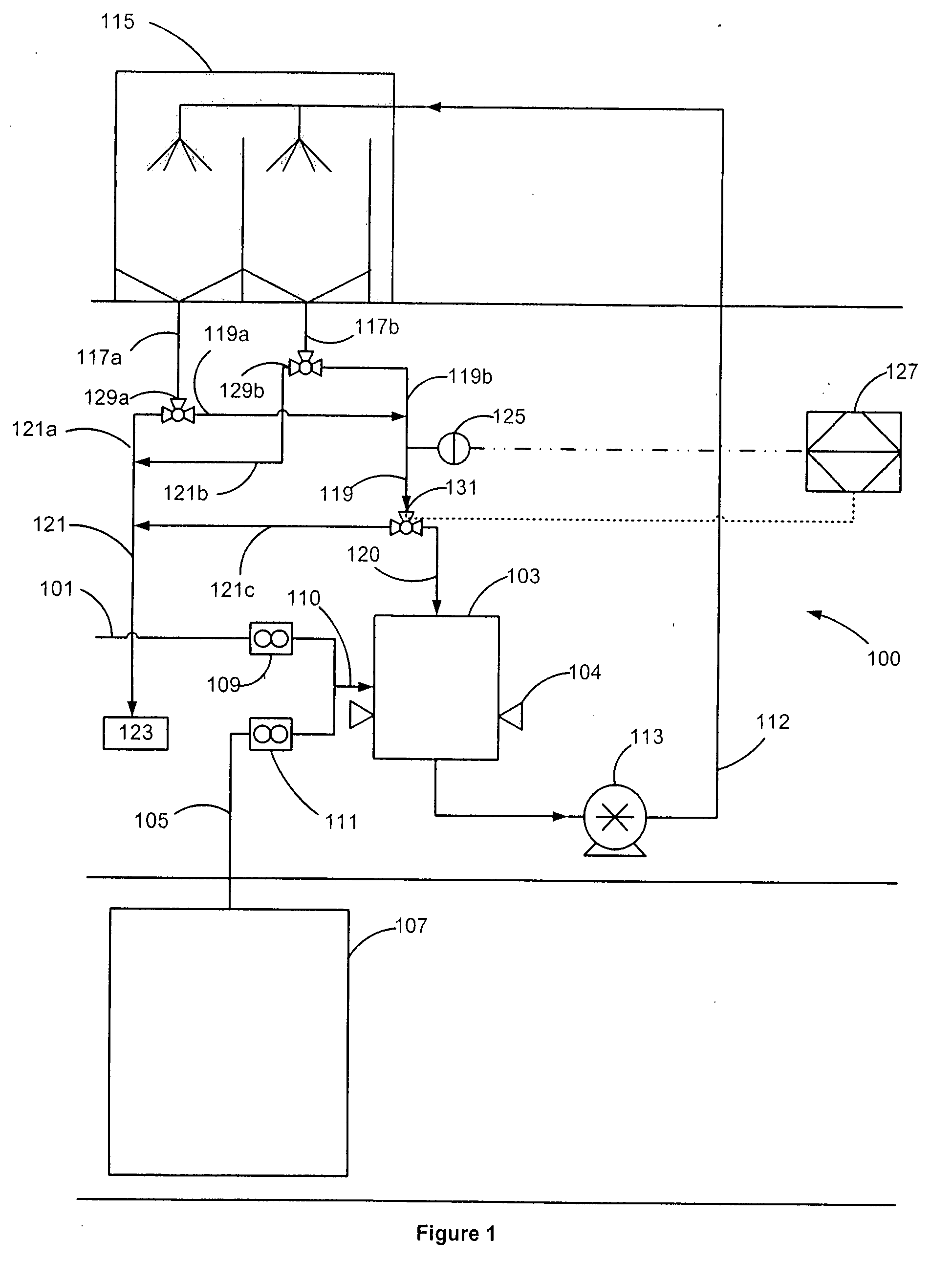

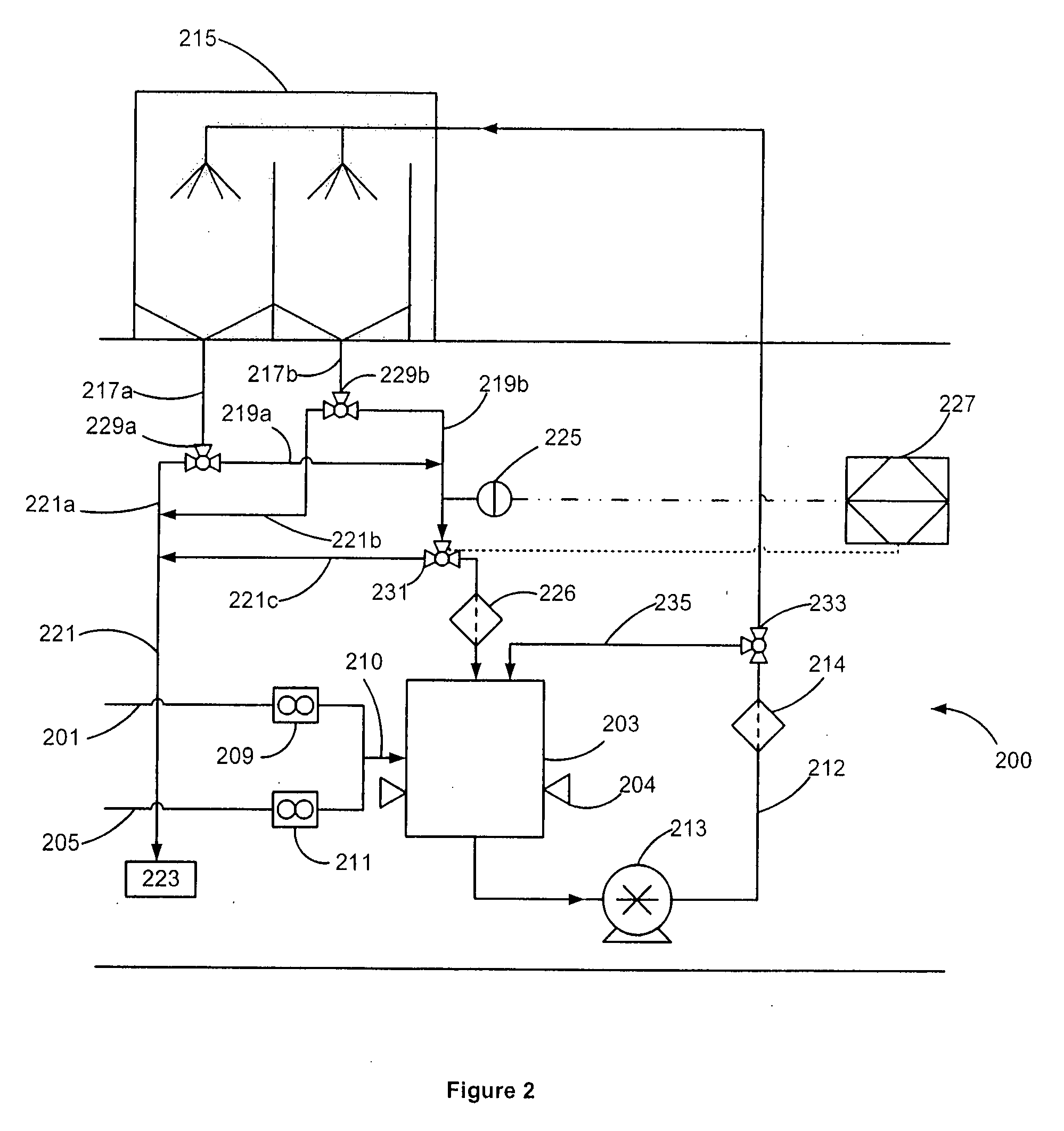

Method and apparatus for recycling process fluids

ActiveUS20070235392A1Prevent electromigrationSemiconductor/solid-state device manufacturingMixer accessoriesCopper interconnectProcess engineering

A method and apparatus for recycling a process fluid from a drain of a semiconductor process tool. The process fluid may be an acidic cobalt solution or an electroless cobalt solution used in a semiconductor process step to prevent electromigration in copper interconnects. The used process fluid is collected from the tool drain and recycled back to the tool inlet if a condition of the fluid is within a predetermined range. Otherwise, the used process fluid is drained from the system. The system may also operate in a bleed and feed mode where a portion of the used process fluid is periodically drained from the system.

Owner:AIR LIQUIDE ELECTRONICS US LP

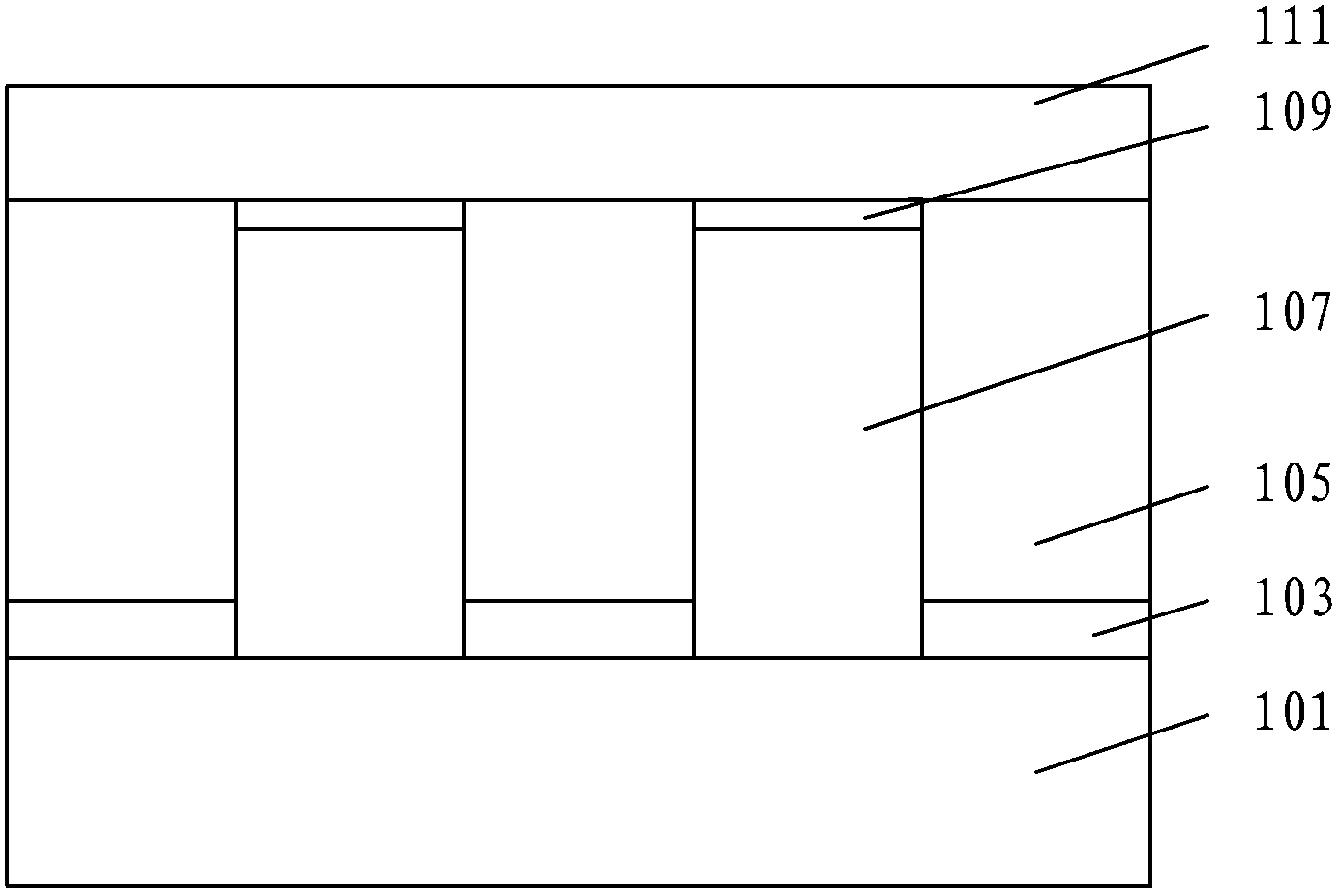

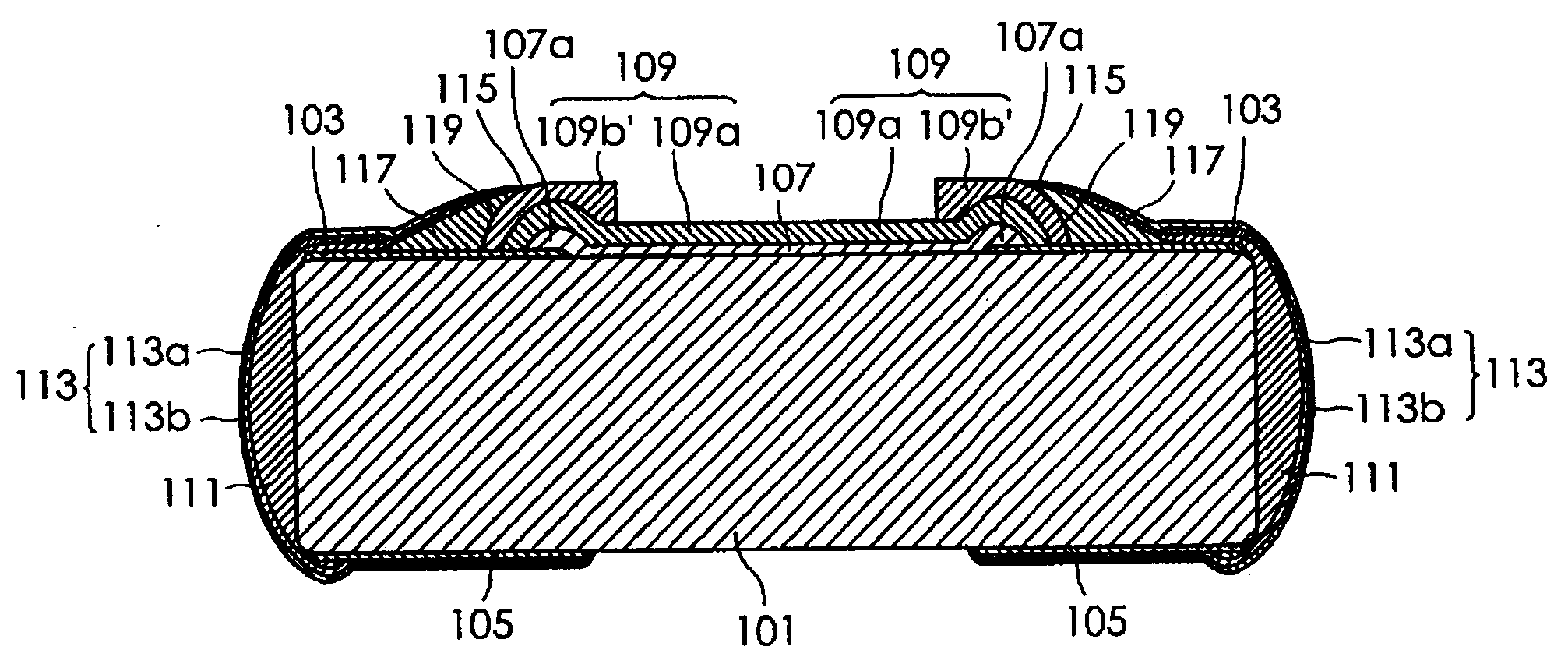

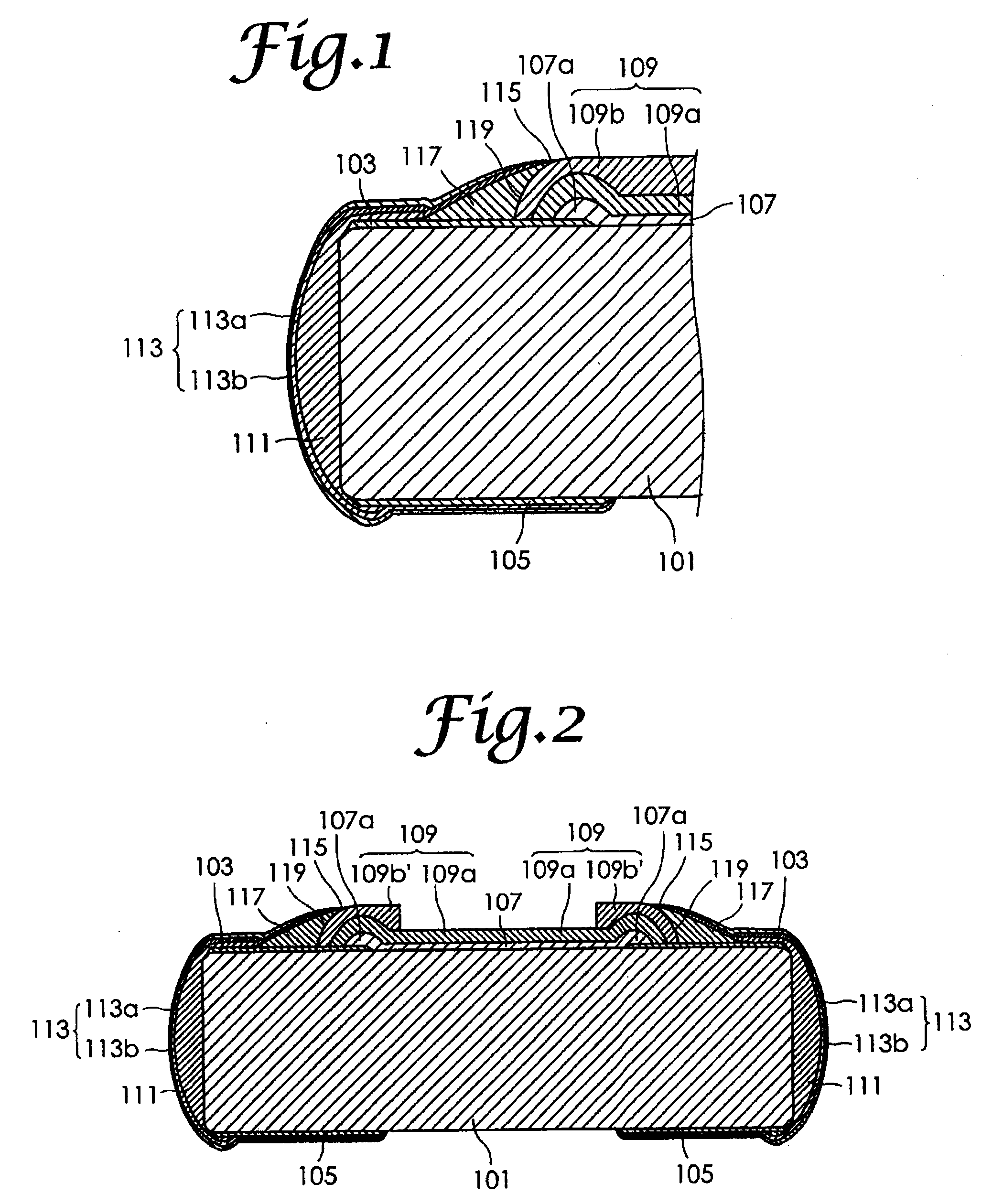

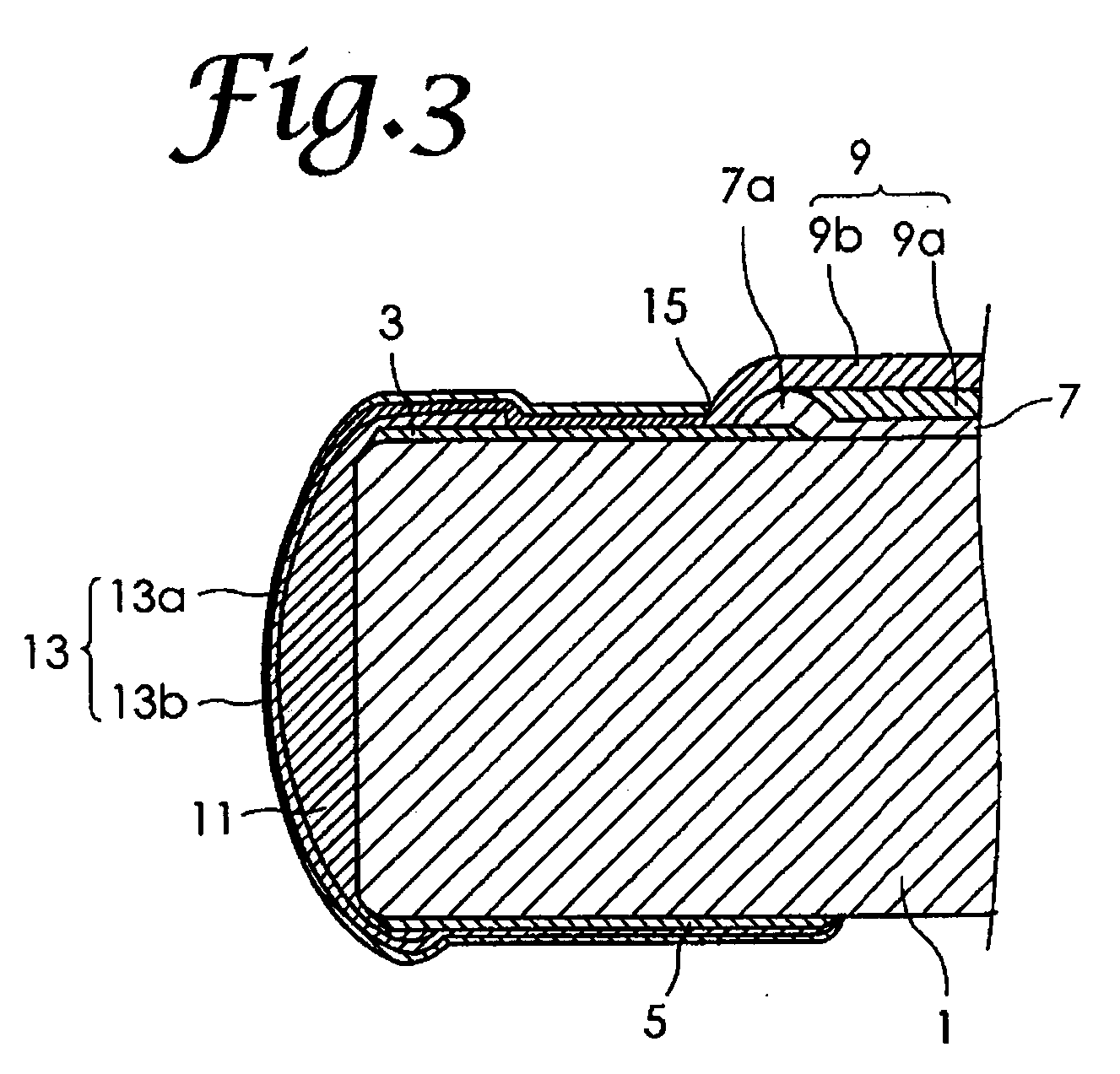

Terminal structure of chiplike electric component

InactiveUS20090231086A1Avoid enteringPrevent electromigrationResistor chip manufactureFixed capacitor dielectricEpoxyOptoelectronics

A terminal structure of a chip-like electric component capable of blocking entry of electromigration-causing factors through an insulating resin layer in the vicinity of the peak of a raised portion of an electrical element forming layer is obtained. A metal-glaze-based front electrode 103 containing silver is provided on a surface of an insulating ceramic substrate 101. A resistor layer 107 electrically connected to the front electrode 103 is provided on the substrate surface. A glass layer 109a is provided to completely cover a surface of the resistor layer 107 as well as a surface of an end portion of the resistor layer 107 and also to partially cover the front electrode 103. An insulating resin layer 109b is provided to cover a surface of the glass layer 109a as well as a surface of at least an end portion of the glass layer 109a and to partially cover the front electrode 103. A conductive layer 117 made of a resin-based conductive paint is provided to extend over the surface of the front electrode 103 and an portion of the insulating resin layer 109b in the vicinity of the peak of raised end portion of the insulating resin layer 109b. The resin-based conductive paint is made by kneading particulate conductive silver powder and scale-like conductive silver powder into an epoxy-based insulating resin paint.

Owner:HOKURIKU ELECTRIC INDS

Method for inhibiting copper electromigration in hybrid bonding of wafers

ActiveCN107993928AIncrease contact resistanceInhibit thermal expansionSemiconductor/solid-state device manufacturingSingle layer grapheneCvd graphene

The invention discloses a method for inhibiting copper electromigration in hybrid bonding of wafers. The method comprises the following steps of forming metal layers on at least two semiconductor substrates; carrying out chemico-mechanical polishing on the semiconductor substrates to form a plurality of recesses in the metal layers; plating the metal layers with the plurality of recesses with graphene; and carrying out thermal treatment on the at least two semiconductor substrates to bond the metal layers through the graphene. The recesses of specific heights are firstly formed through control, single-layer graphene is accurately transferred into each recess to form a cover coating, wafer bonding is carried out through a hybrid bonding method of the wafers, and thermal treatment is finallycarried out at certain temperature, so that copper electromigration can be inhibited.

Owner:YANGTZE MEMORY TECH CO LTD

Method for preparing anti-oxidation conductive glue

InactiveCN107760242AImprove antioxidant capacityPrice increaseNon-macromolecular adhesive additivesPolyureas/polyurethane adhesivesEpoxyDiethylenetriamine

The invention relates to the technical field of electronic product preparation and particularly relates to a method for preparing anti-oxidation conductive glue. The method comprises preparing a copper sulfate solution and a reducing solution, blending the two solutions to obtain a reaction solution, treating the reaction solution to obtain ultrafine copper powder, dispersing the ultrafine copperpowder in deionized water, blending the ultrafine copper powder and a silver ammonia solution for a reaction, treating the reaction product to obtain silver-coated copper powder, adding the silver-coated copper powder and polyurethane granules into diluted hot-melt epoxy resin, and adding diethylenetriamine and tributyl phosphate into the diluted hot-melt epoxy resin to obtain the anti-oxidation conductive glue. Silver on the copper powder surfaces has high electrical conductivity and chemical stability. The potential difference between copper ions and silver can prevent silver from falling off because of electrochemical corrosion and improve oxidation resistance of the conductive glue. Through use of polyurethane in the epoxy resin, the brittleness of the conductive glue is well improved,silver-coated copper powder precipitation under gravity is prevented and the electro-migration caused by precipitation of conductive particles in the conductive glue is prevented. The method has a wide application prospect.

Owner:CHANGZHOU LANXU CHEM CO LTD

Semiconductor device

ActiveUS20080296730A1Excellent adhesionPrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesCopper wireAluminium

A semiconductor device according to the present invention has a multilayer wiring structure laminating and disposing a plurality of with sandwiching an insulating film and includes: a copper wire having copper as a main component; an insulating film formed on the copper wire; an aluminum wire having aluminum as a main component and formed on the insulating film to be electrically connected to the copper wire via a via hole formed to penetrate through the insulating film; and a surface protective film formed on the aluminum wire; and the surface protective film formed with a pad opening exposing a portion of the aluminum wire as an electrode pad for electrical connection with an external portion.

Owner:ROHM CO LTD