Semiconductor device, chip-on-chip mounting structure, method of manufacturing the semiconductor device, and method of forming the chip-on-chip mounting structure

A chip mounting and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as short circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

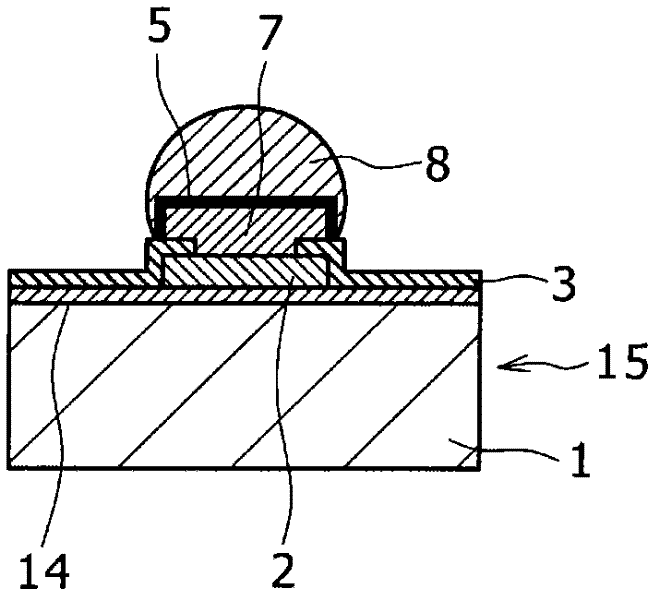

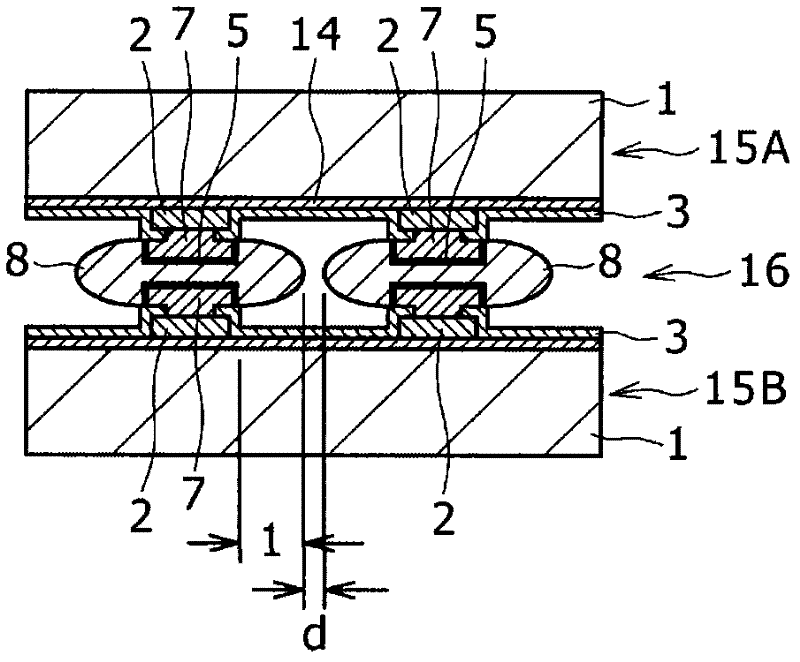

[0052] Figure 1A with 1B The structure of the semiconductor device (semiconductor chip) 15 according to the first embodiment of the present invention is schematically illustrated.

[0053] The semiconductor device 15 is composed of a semiconductor substrate 1 made of Si or the like, a pad electrode 2 made of aluminum, an insulating film 14 (corresponding to the insulating film 64 previously described in the related art), a protective film 3 (corresponding to the previous The protective film 53 ), the copper (Cu) plating layer 5 , the Ni plating layer 7 , the Sn-based solder bump electrode 8 , and the like described in the related art are constituted. Likewise, the under bump metallurgy (UBM) layer is composed of Ni plating layer 7 and Cu plating layer 5 . The size of the solder bump electrode 8, for example, its diameter may be equal to or smaller than 30 μm and its height may be equal to or smaller than 15 μm.

[0054] Such as Figure 1A As shown, it is important for the...

no. 2 approach

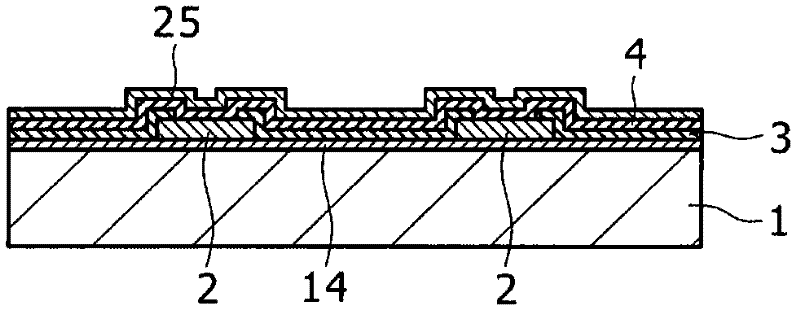

[0073] Figure 3A ~ 3I A semiconductor device according to a second embodiment of the present invention, and steps for manufacturing the semiconductor device of the second embodiment are illustrated respectively.

[0074] First, similar to the reference Figures 4A-4H In the case of the description given, the insulating film 14 , the pad electrode 2 , the protective film 3 , the Ti sputtering layer 4 , the Cu sputtering layer 25 , and the Ni plating layer 7 are sequentially formed on the semiconductor substrate 1 .

[0075] Next, if Figure 3B As shown, the Cu sputtering layer 25 except the portion of the Cu sputtering layer 25 under the Ni plating layer 7 is selectively etched away using the Ni plating layer 7 as an etching mask.

[0076] Next, if Figure 3C As shown, the Ti sputtering layer 4 except for the portion of the Ti sputtering layer 4 under the Ni plating layer 7 is selectively etched away using the Ni plating layer 7 as an etching mask.

[0077] Next, if Figure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More