Patents

Literature

85 results about "ChIP-on-chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

ChIP-on-chip (also known as ChIP-chip) is a technology that combines chromatin immunoprecipitation ('ChIP') with DNA microarray ("chip"). Like regular ChIP, ChIP-on-chip is used to investigate interactions between proteins and DNA in vivo. Specifically, it allows the identification of the cistrome, the sum of binding sites, for DNA-binding proteins on a genome-wide basis. Whole-genome analysis can be performed to determine the locations of binding sites for almost any protein of interest. As the name of the technique suggests, such proteins are generally those operating in the context of chromatin. The most prominent representatives of this class are transcription factors, replication-related proteins, like origin recognition complex protein (ORC), histones, their variants, and histone modifications.

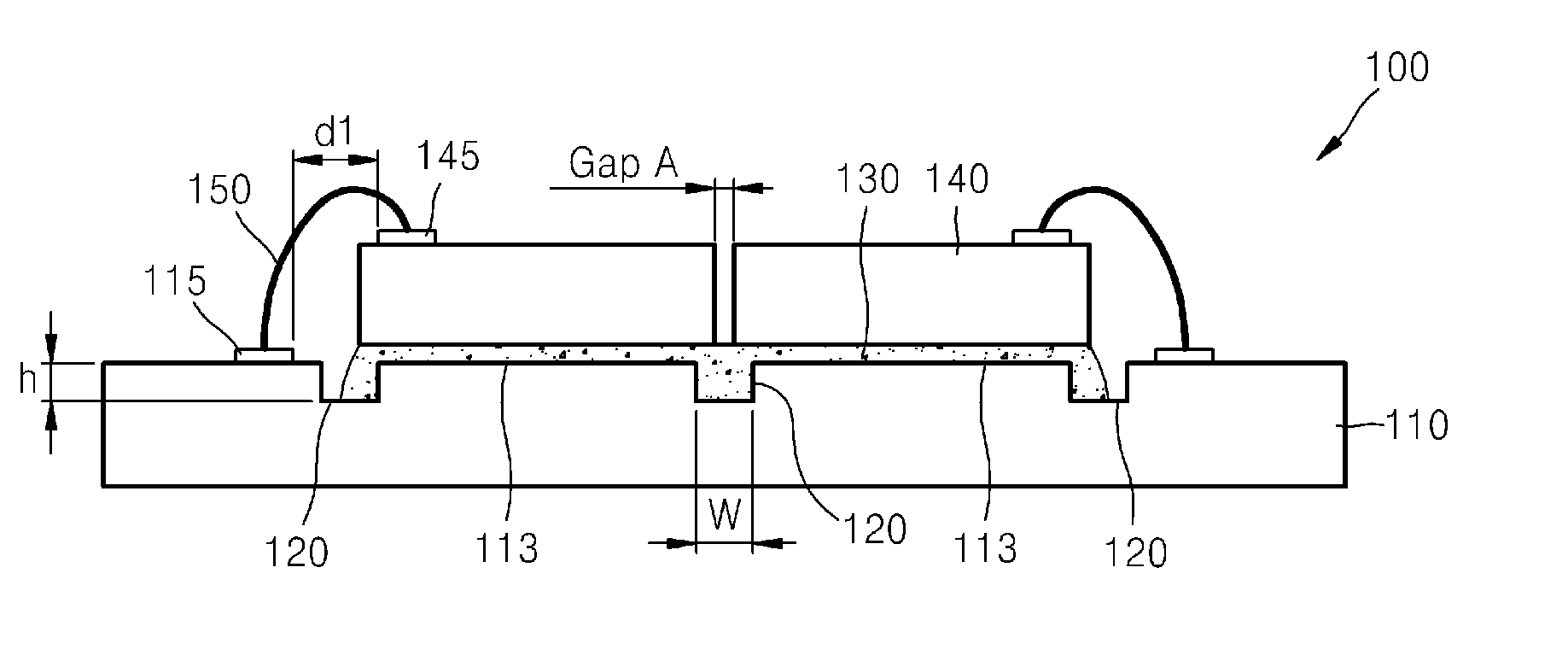

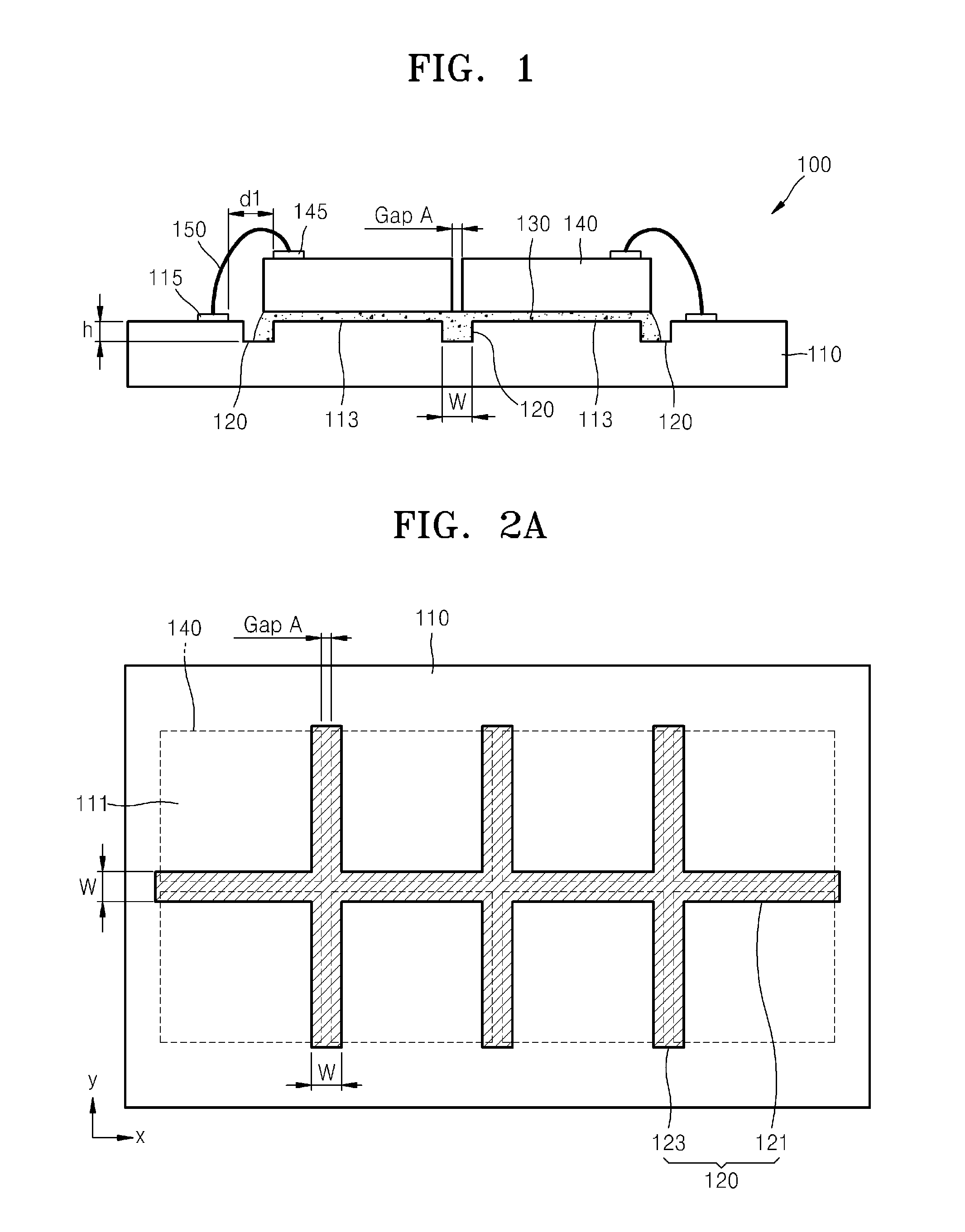

Chip package structure and method of manufacturing the same

InactiveUS20130026655A1Semiconductor/solid-state device detailsSolid-state devicesChIP-on-chipElectrical and Electronics engineering

A chip package structure includes a substrate in which a plurality of grooves are formed, an adhesive layer disposed on the substrate, and a plurality of chips attached to the adhesive layer. In addition, a method of fabricating the chip package structure includes forming a plurality of grooves in the substrate, dispensing a die attach material on a plurality of chip attaching regions between the plurality of grooves, and attaching a plurality of chips respectively on the plurality of chip attaching regions.

Owner:SAMSUNG ELECTRONICS CO LTD

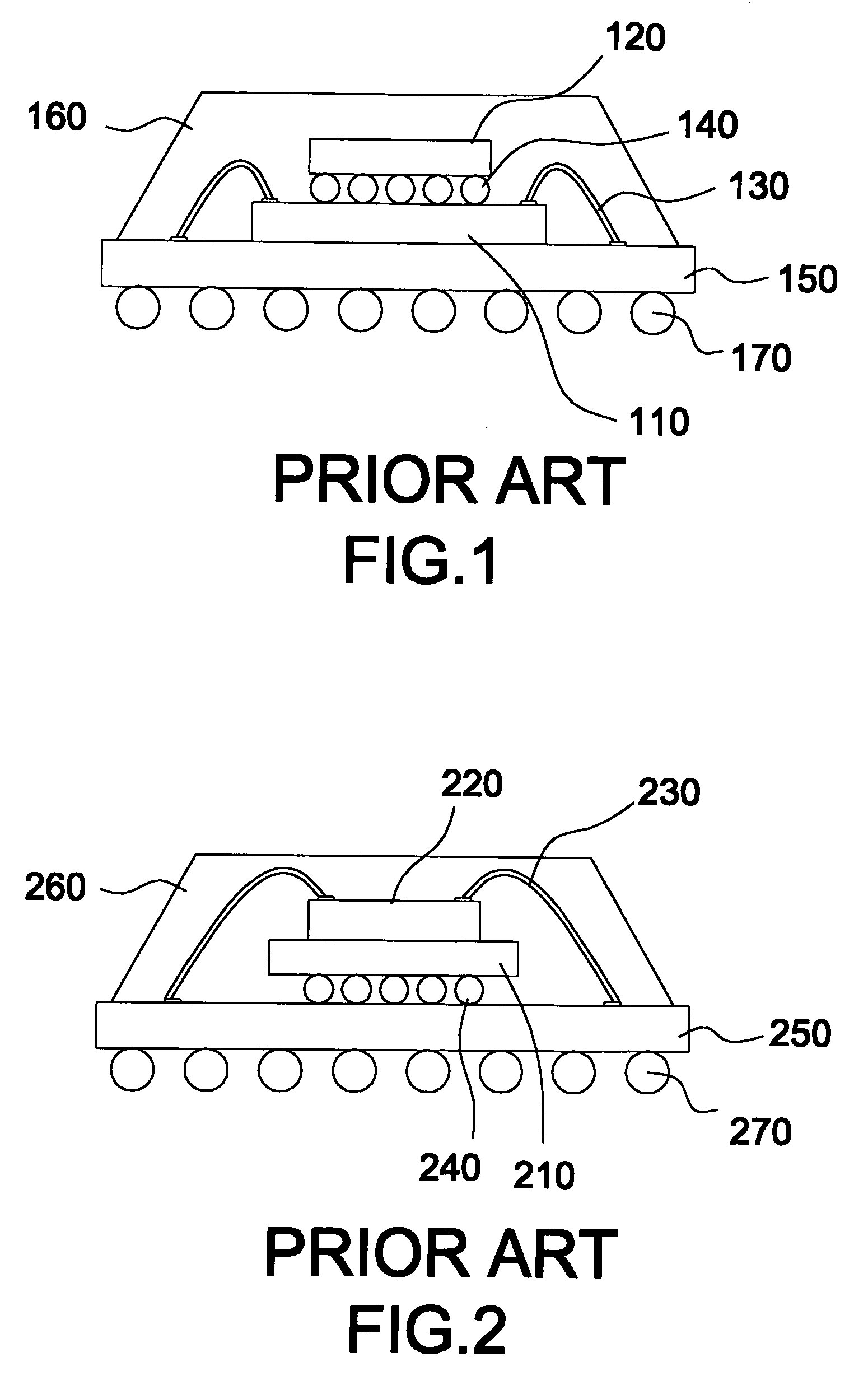

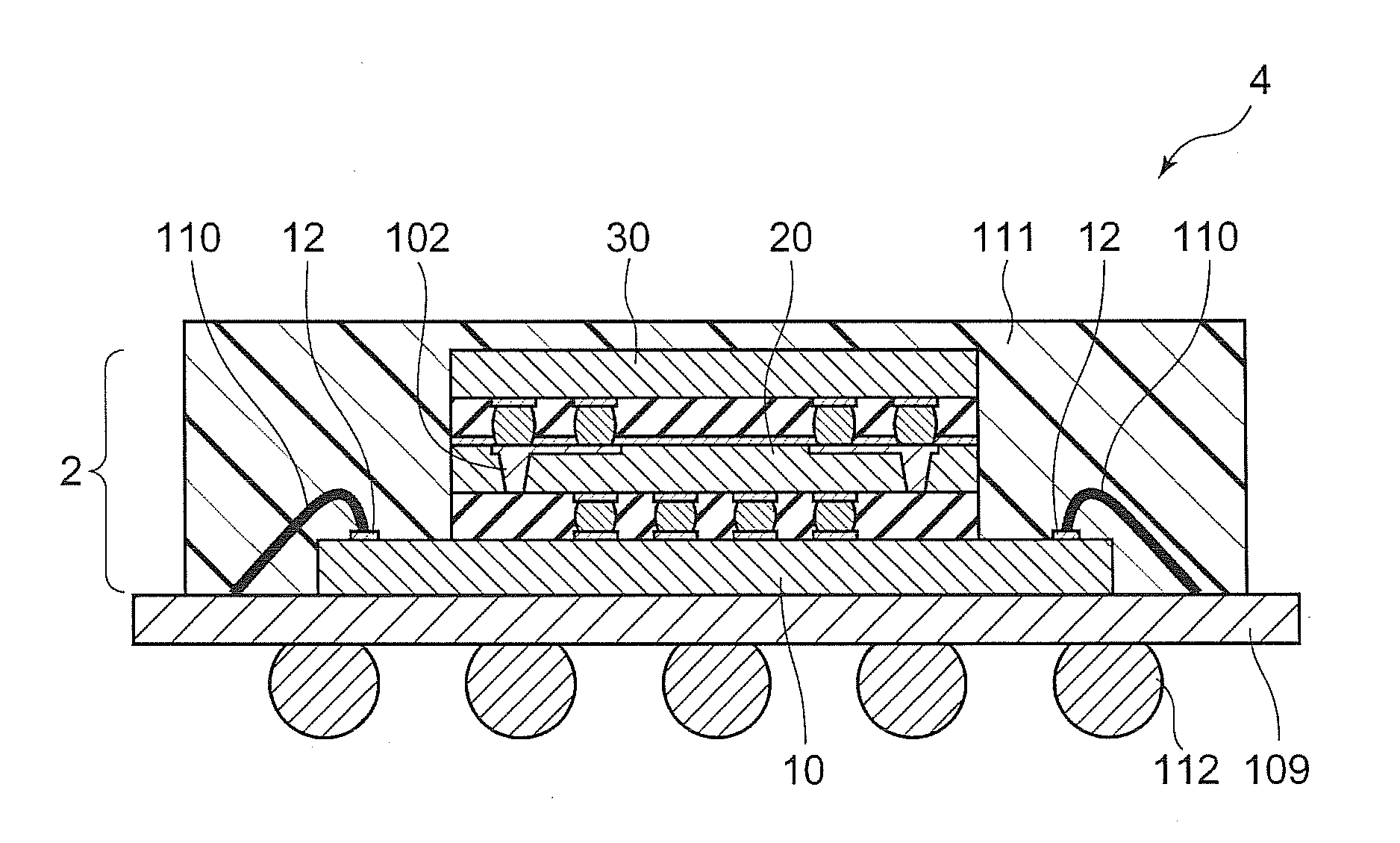

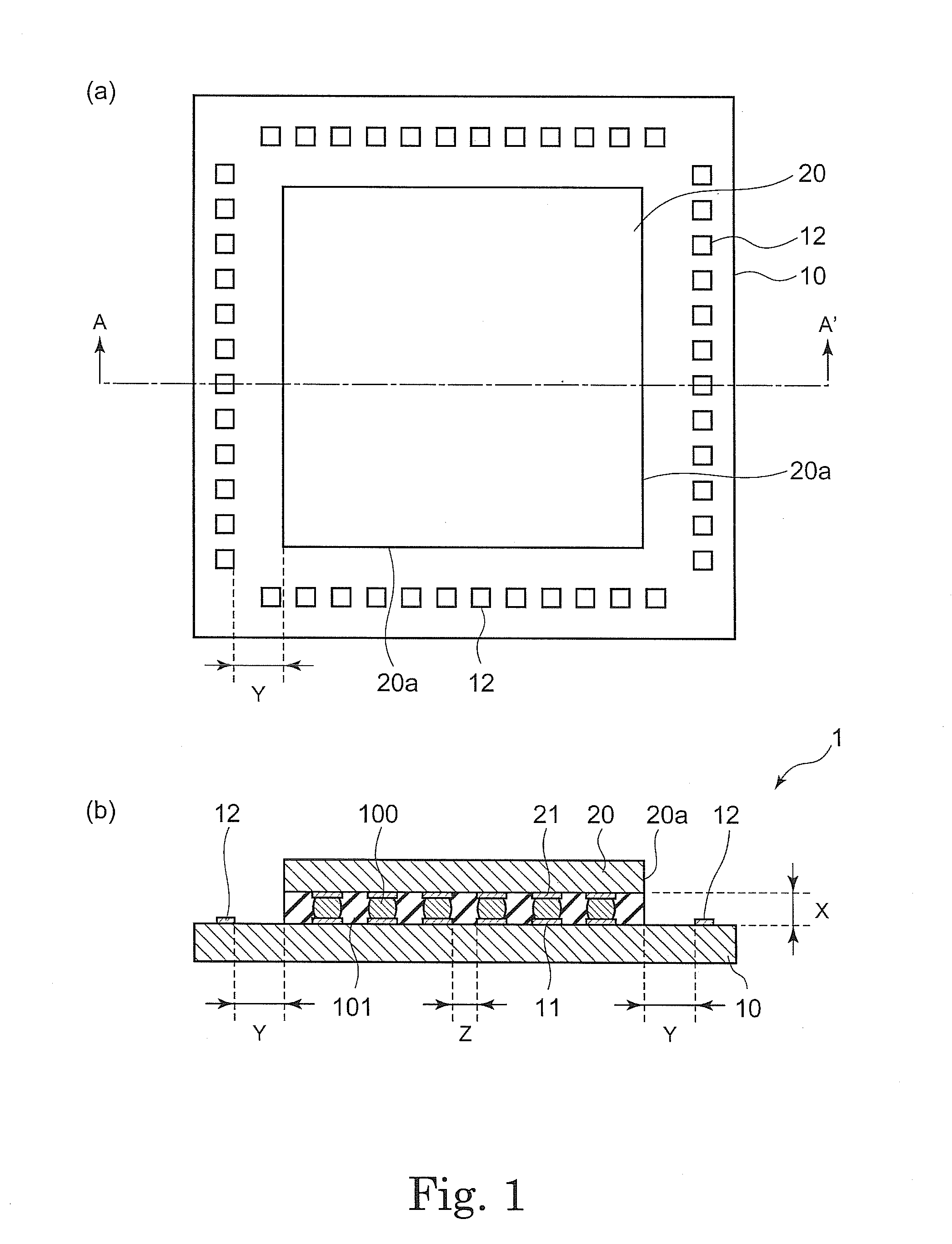

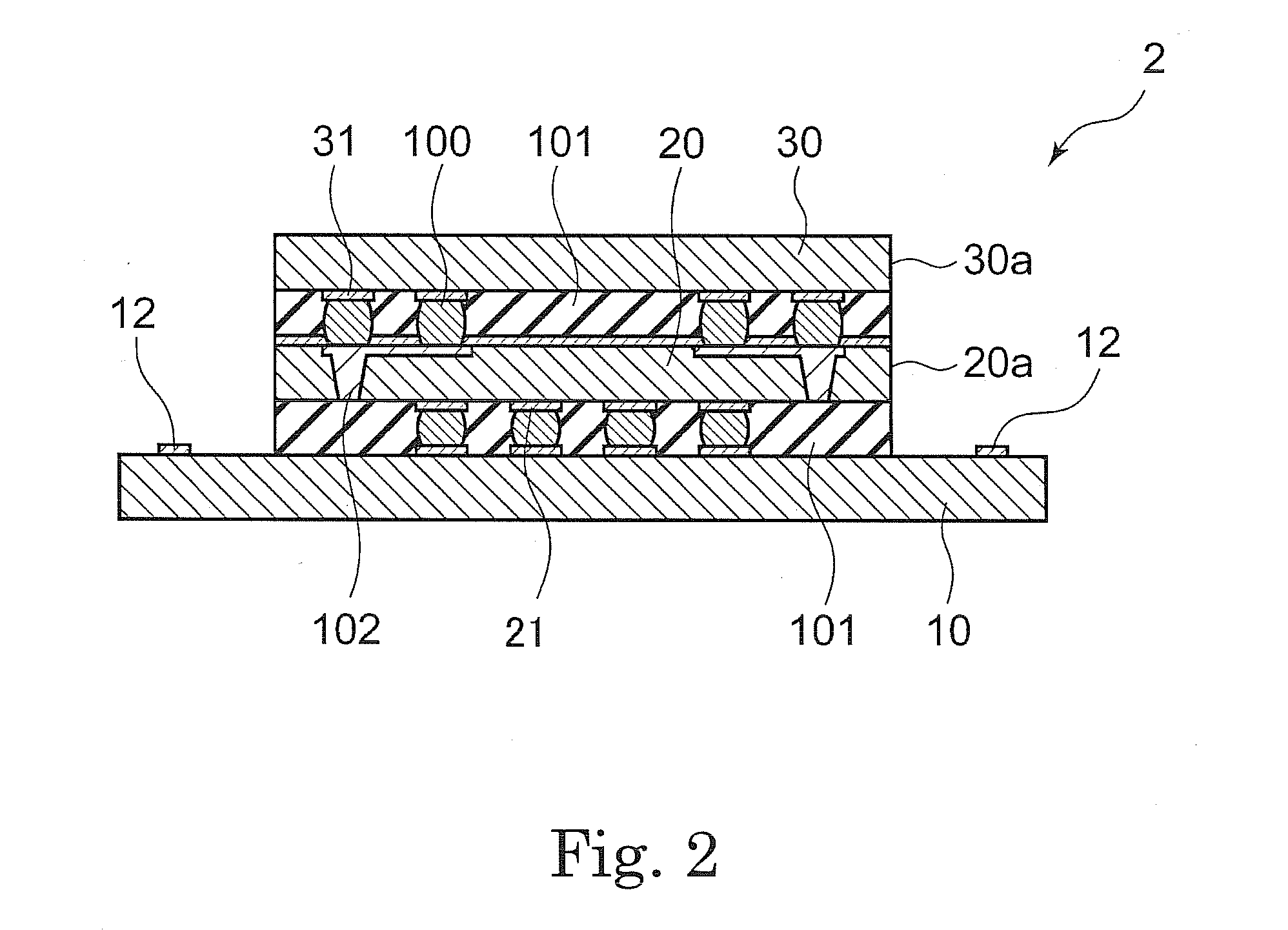

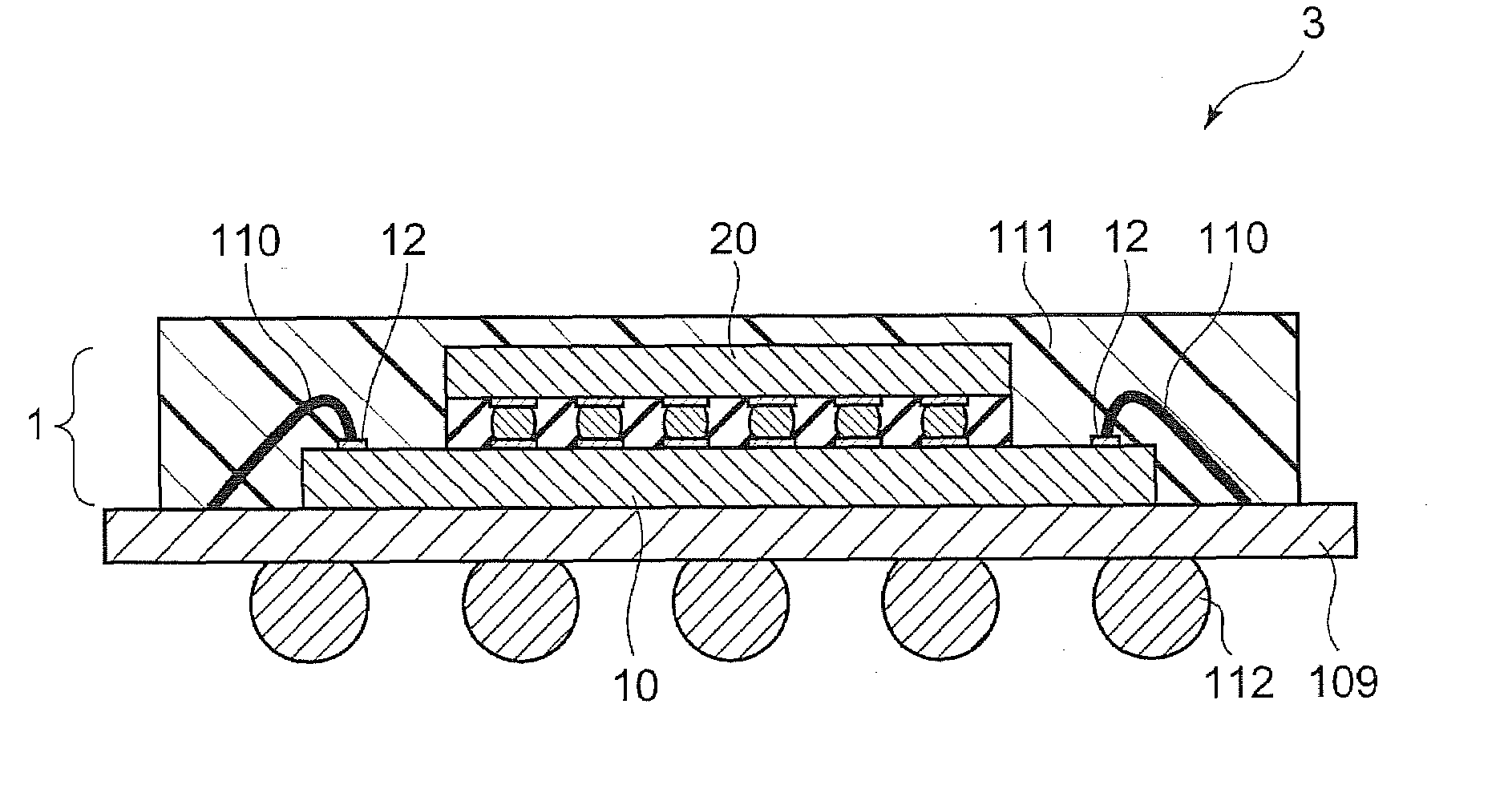

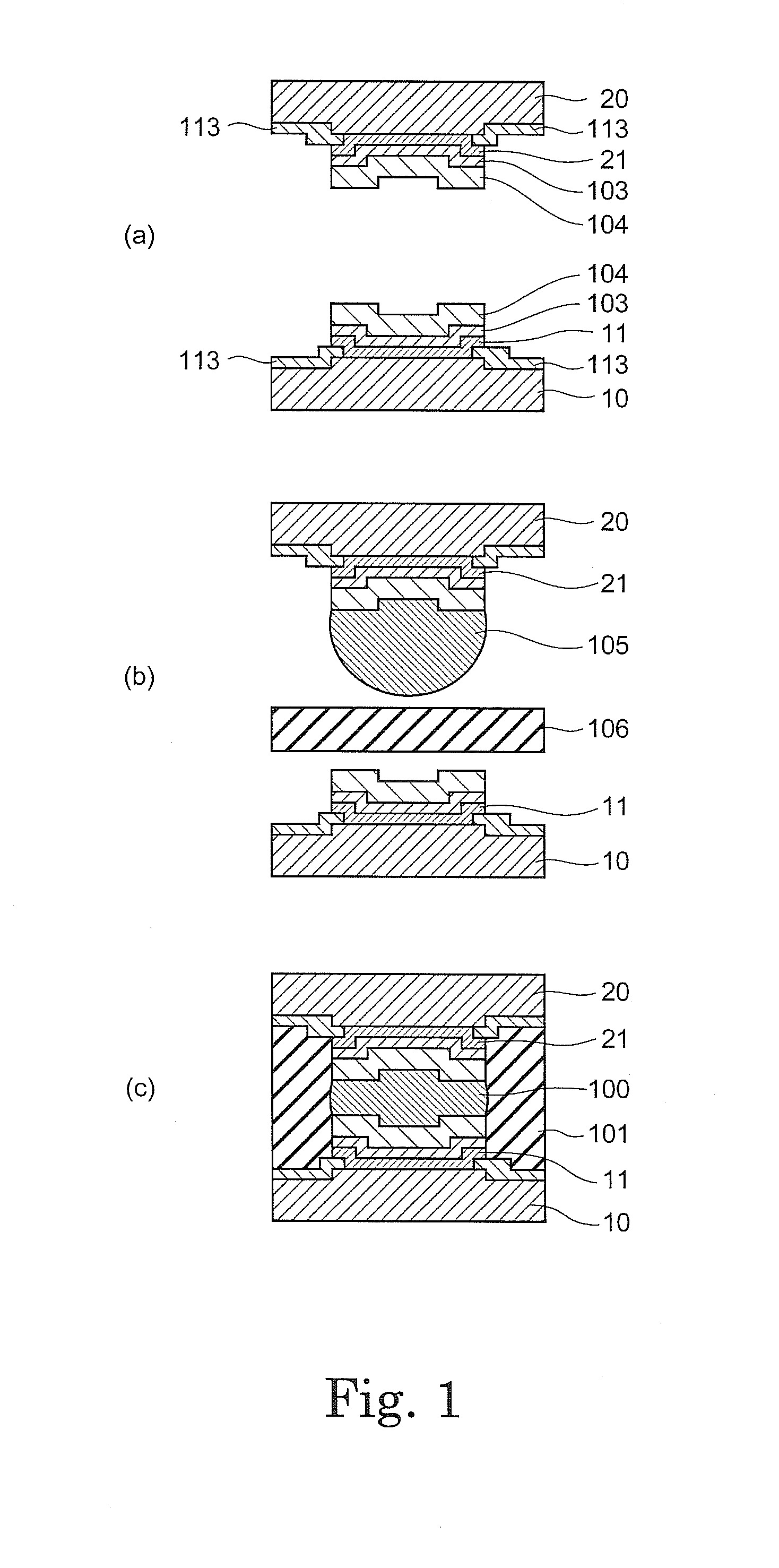

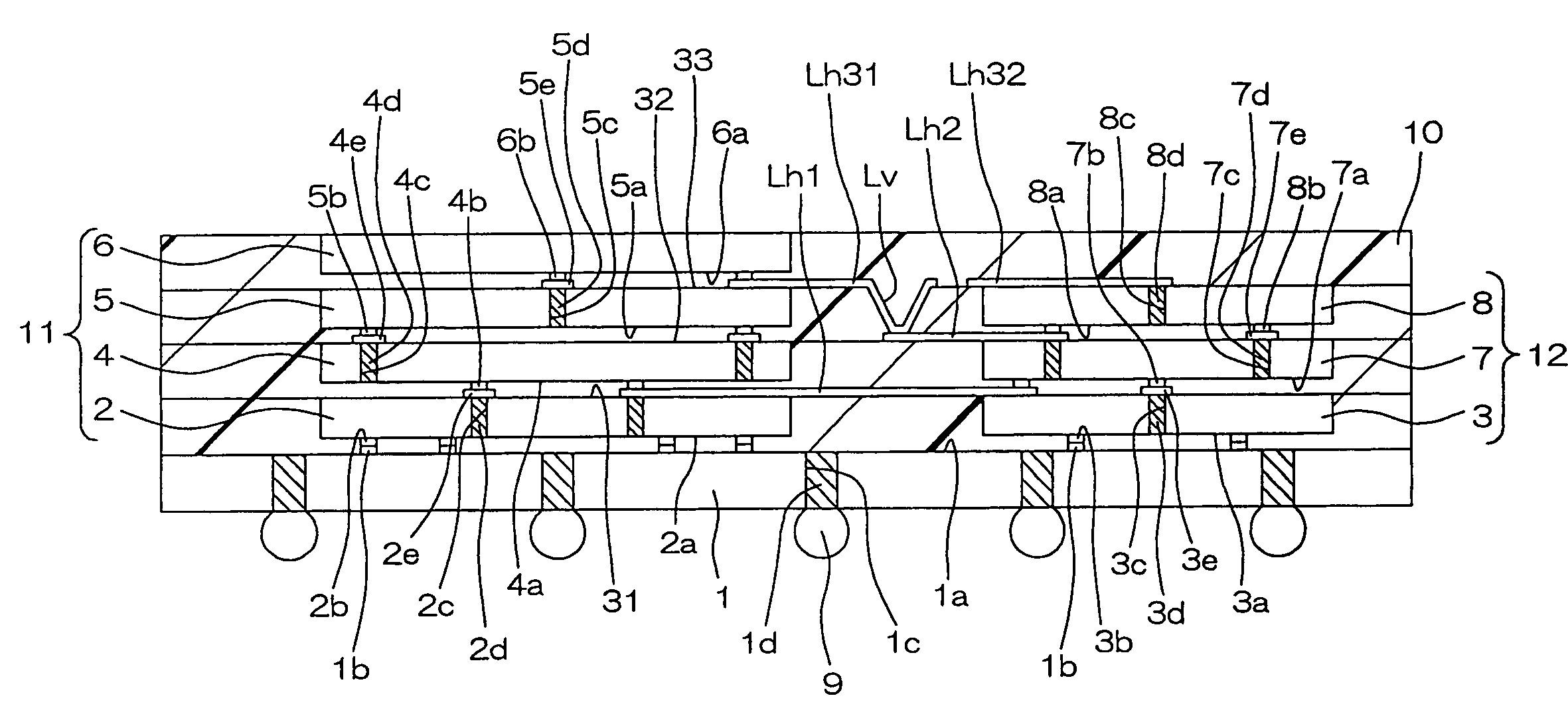

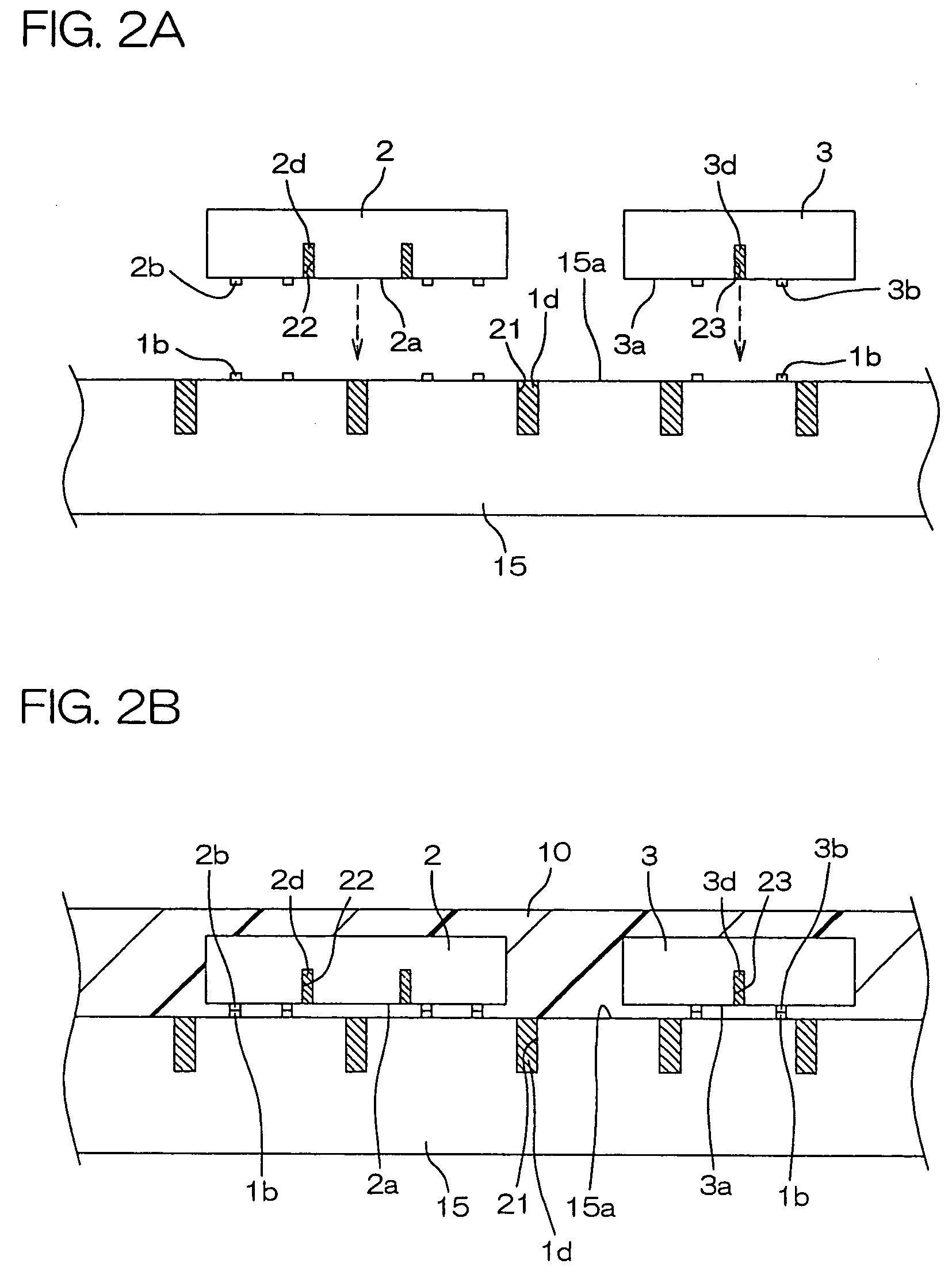

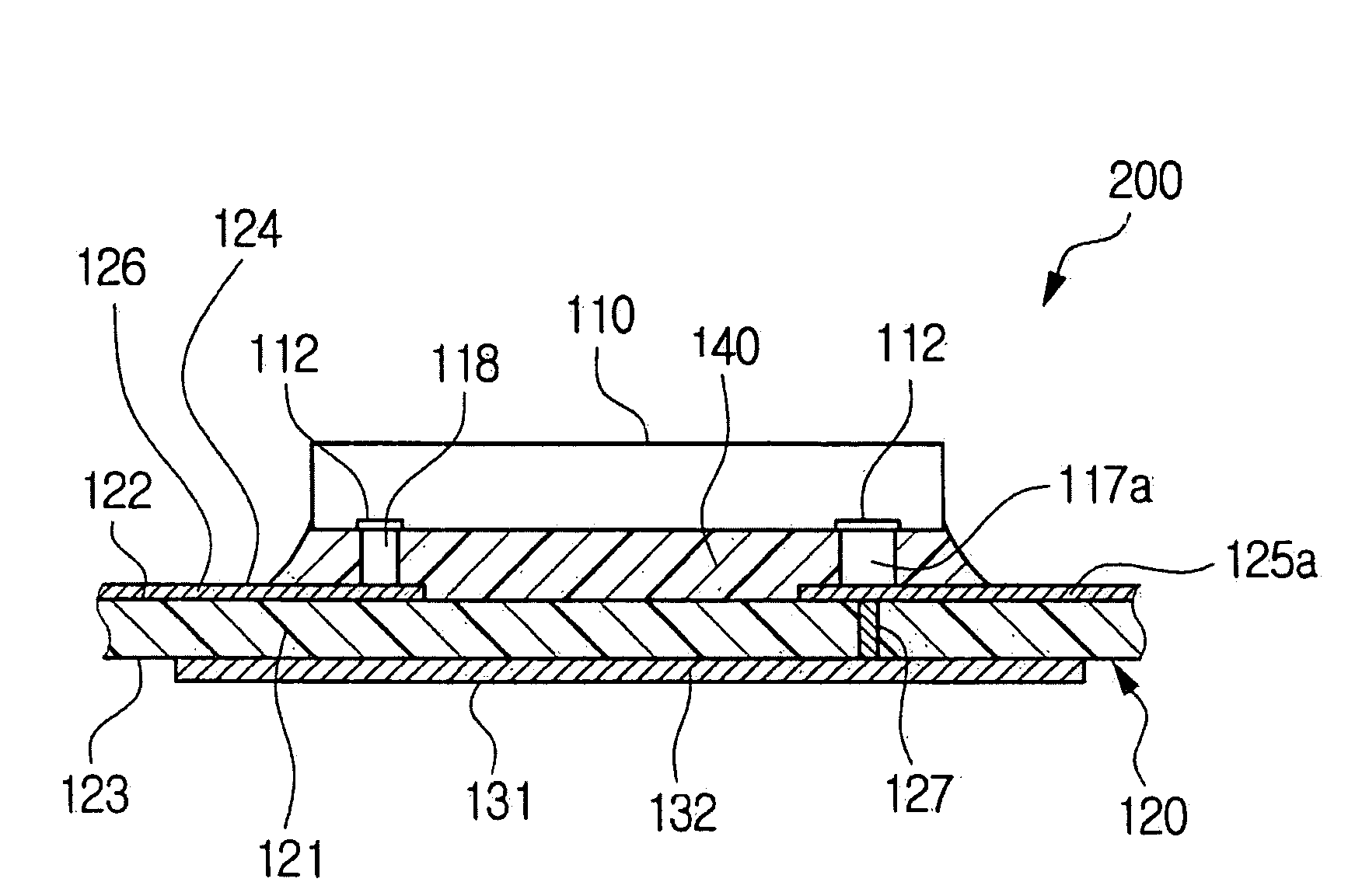

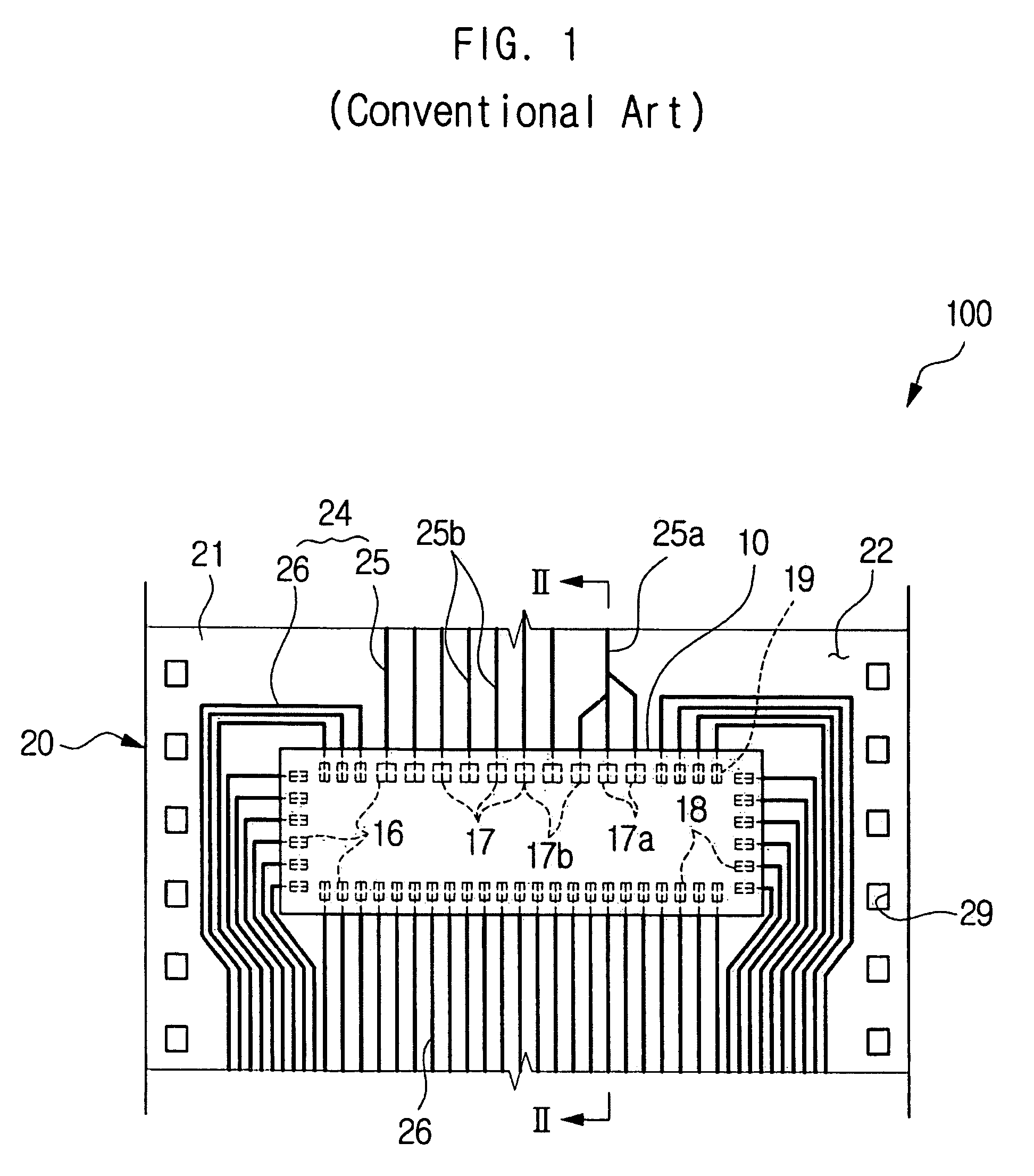

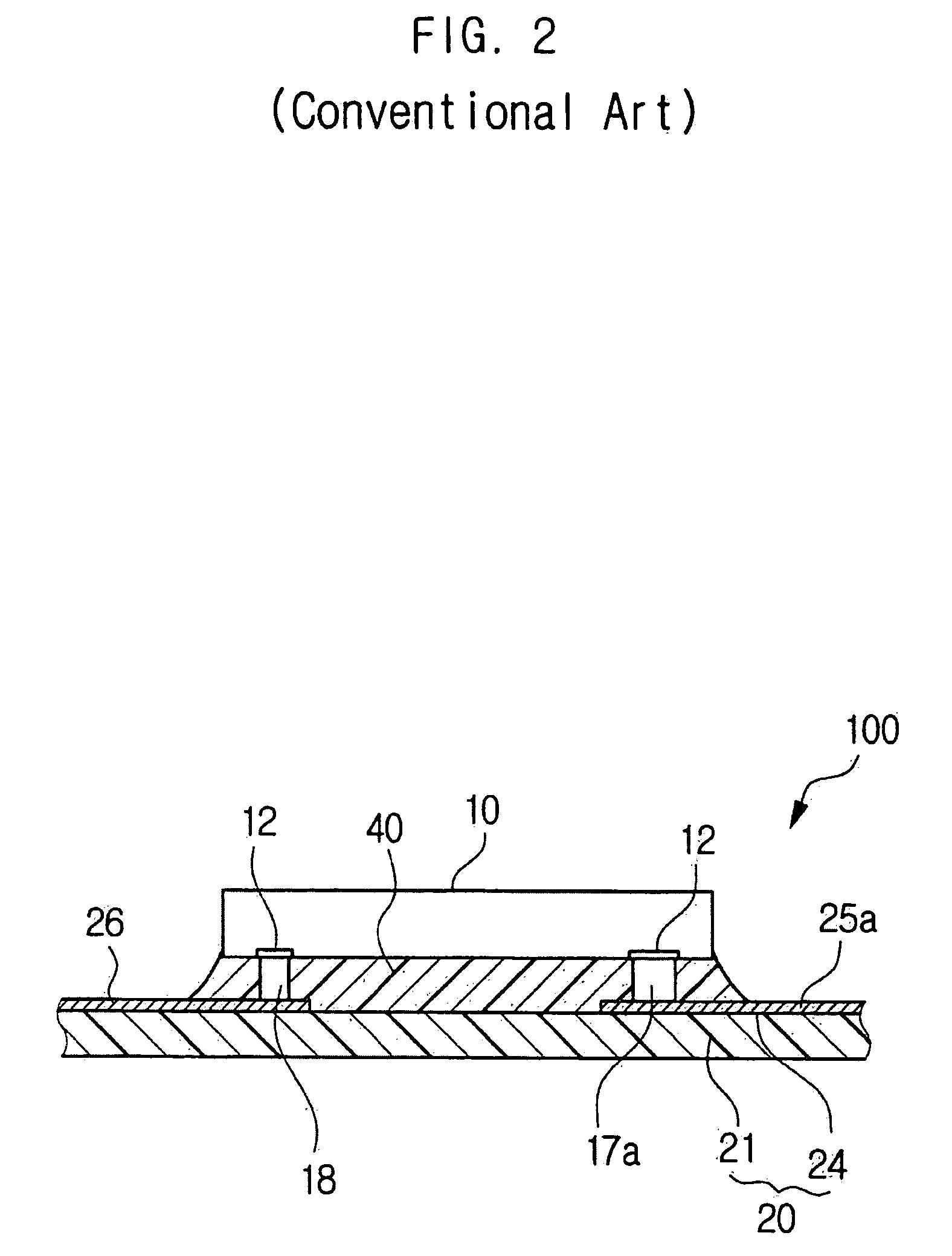

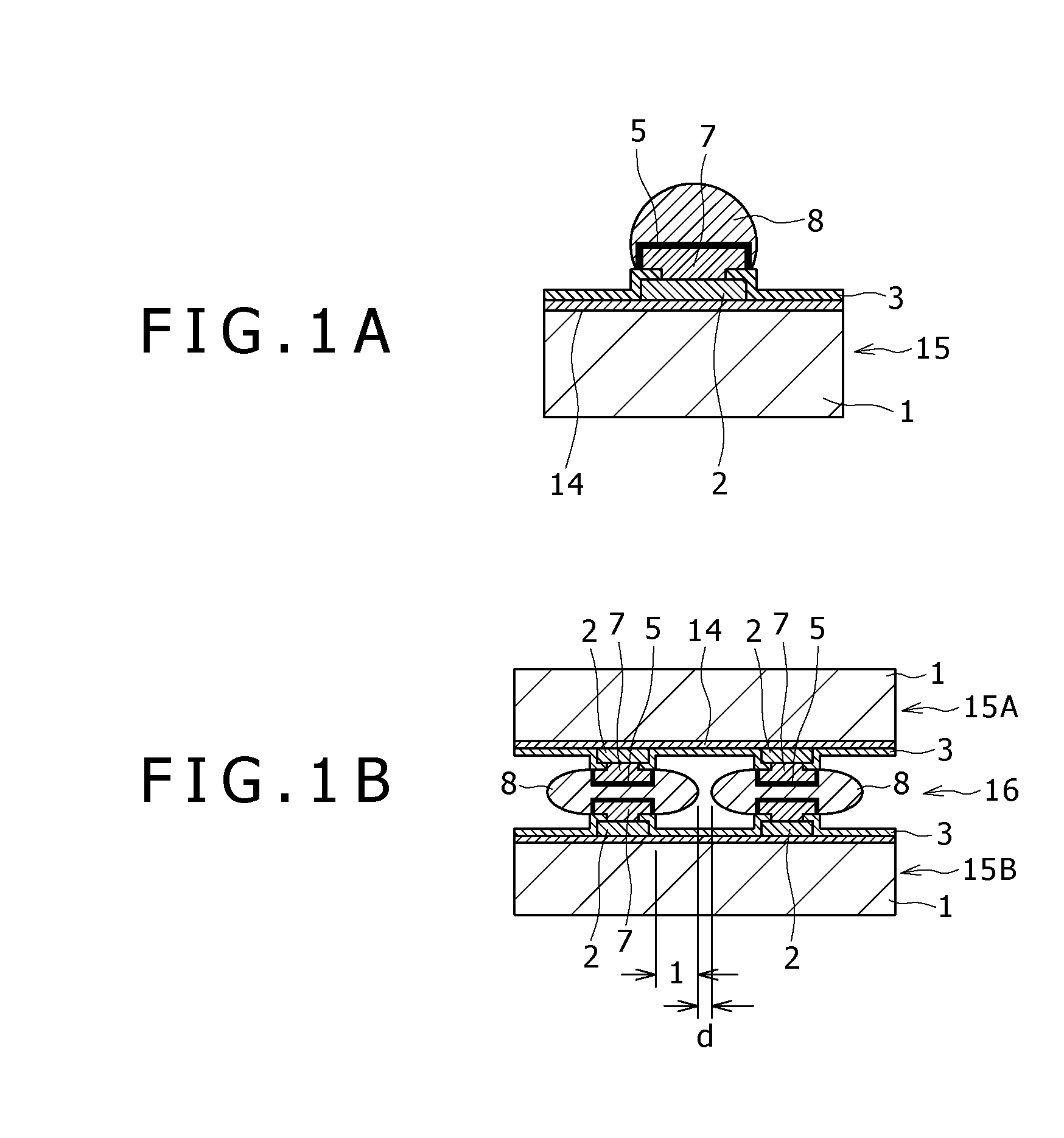

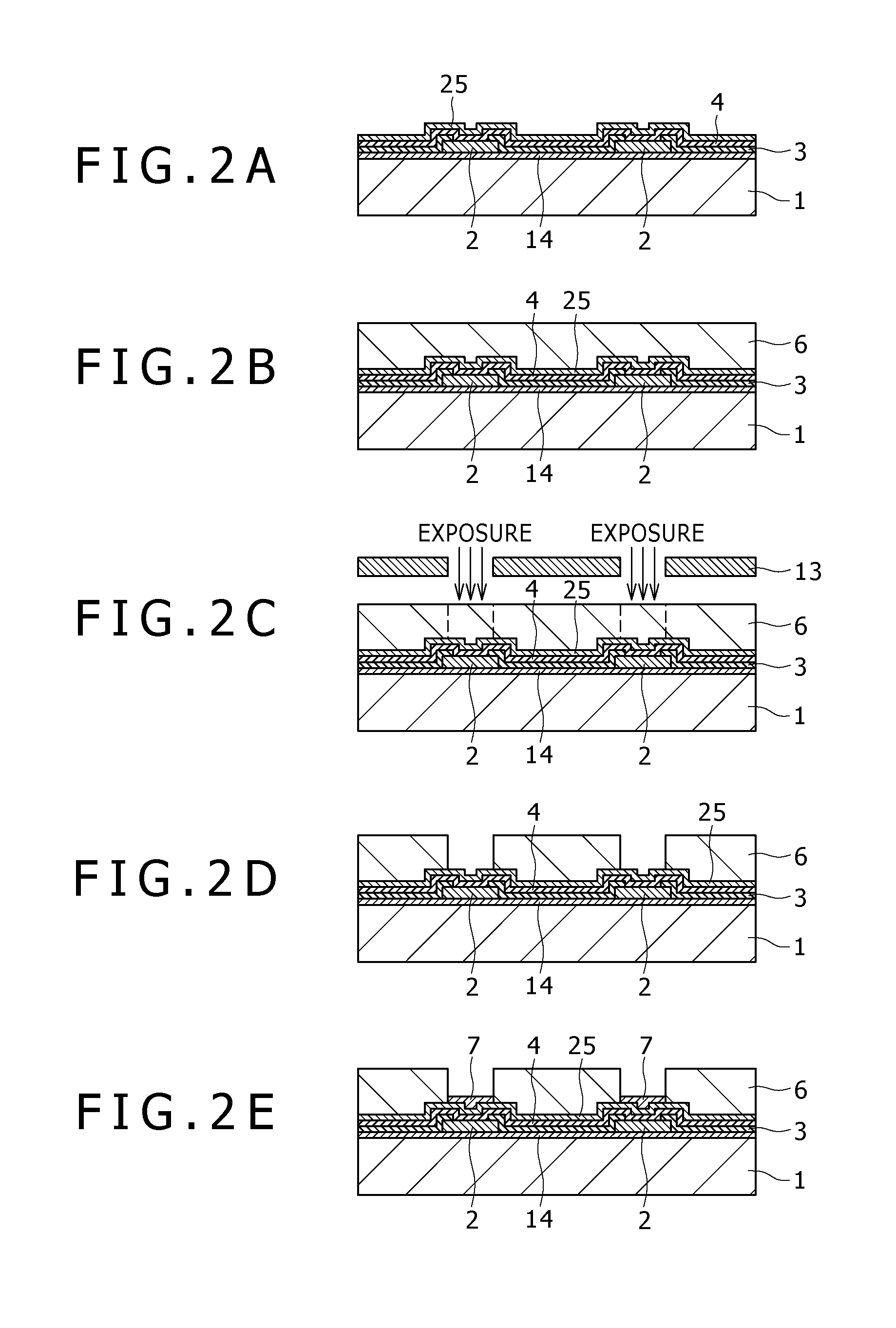

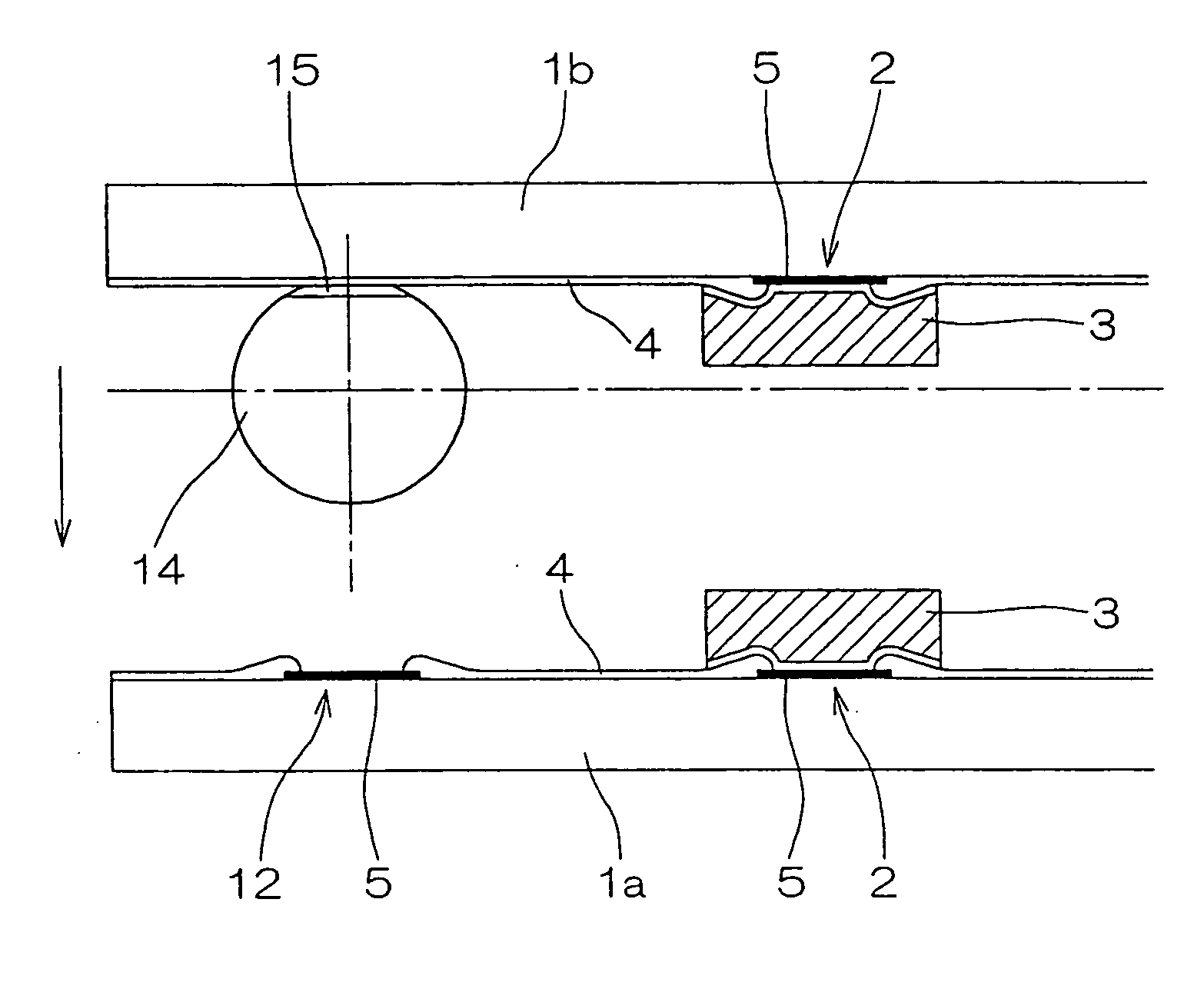

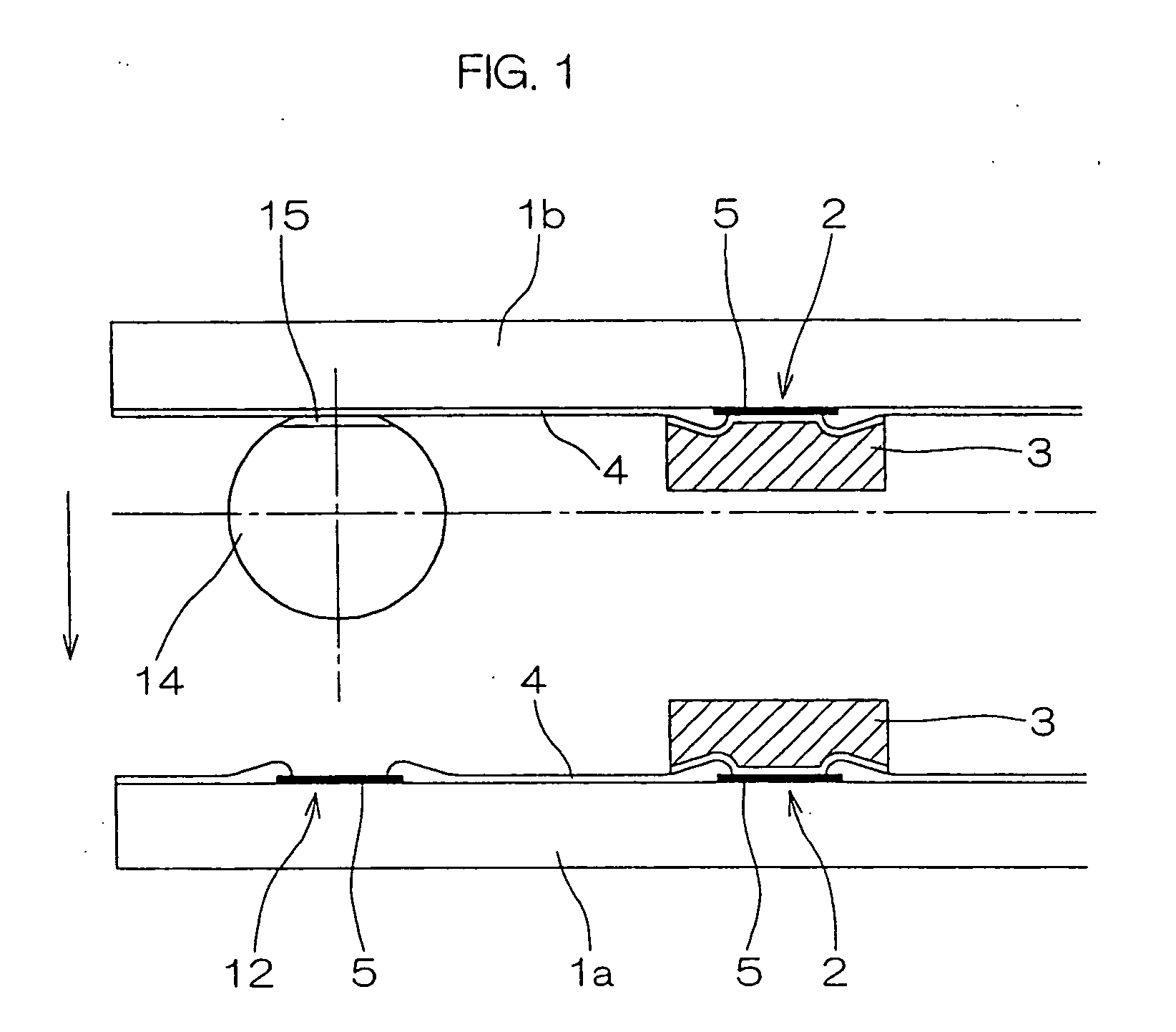

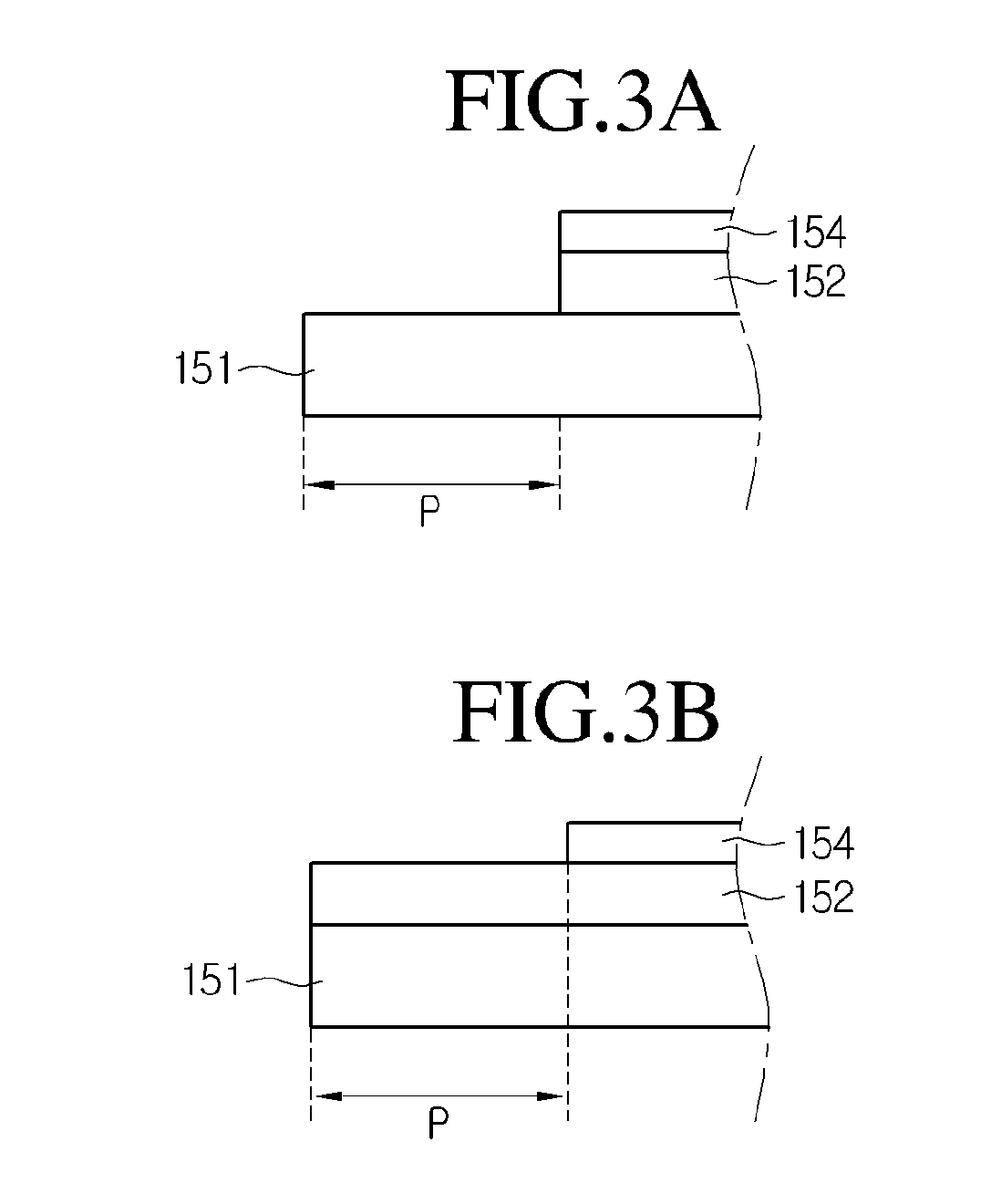

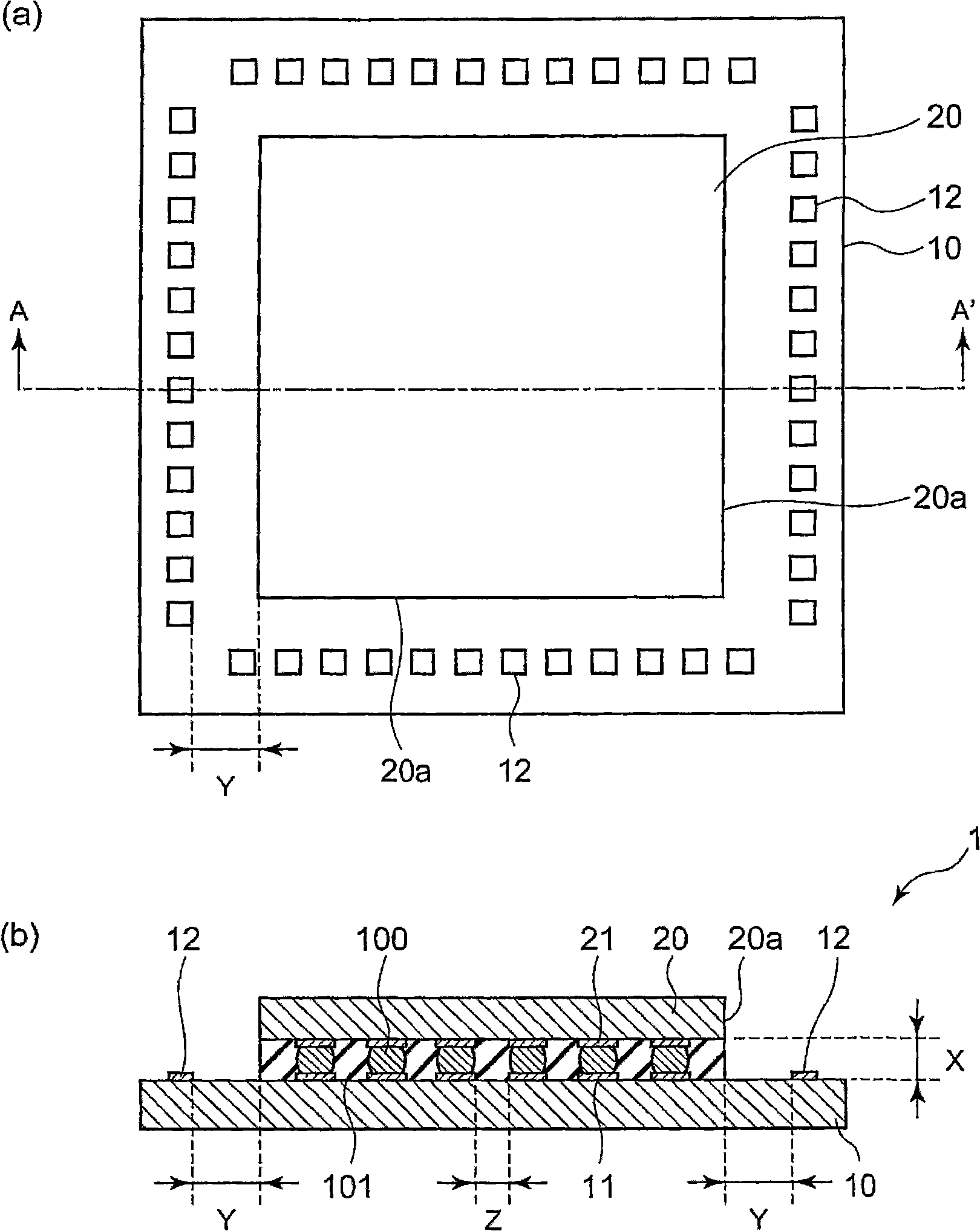

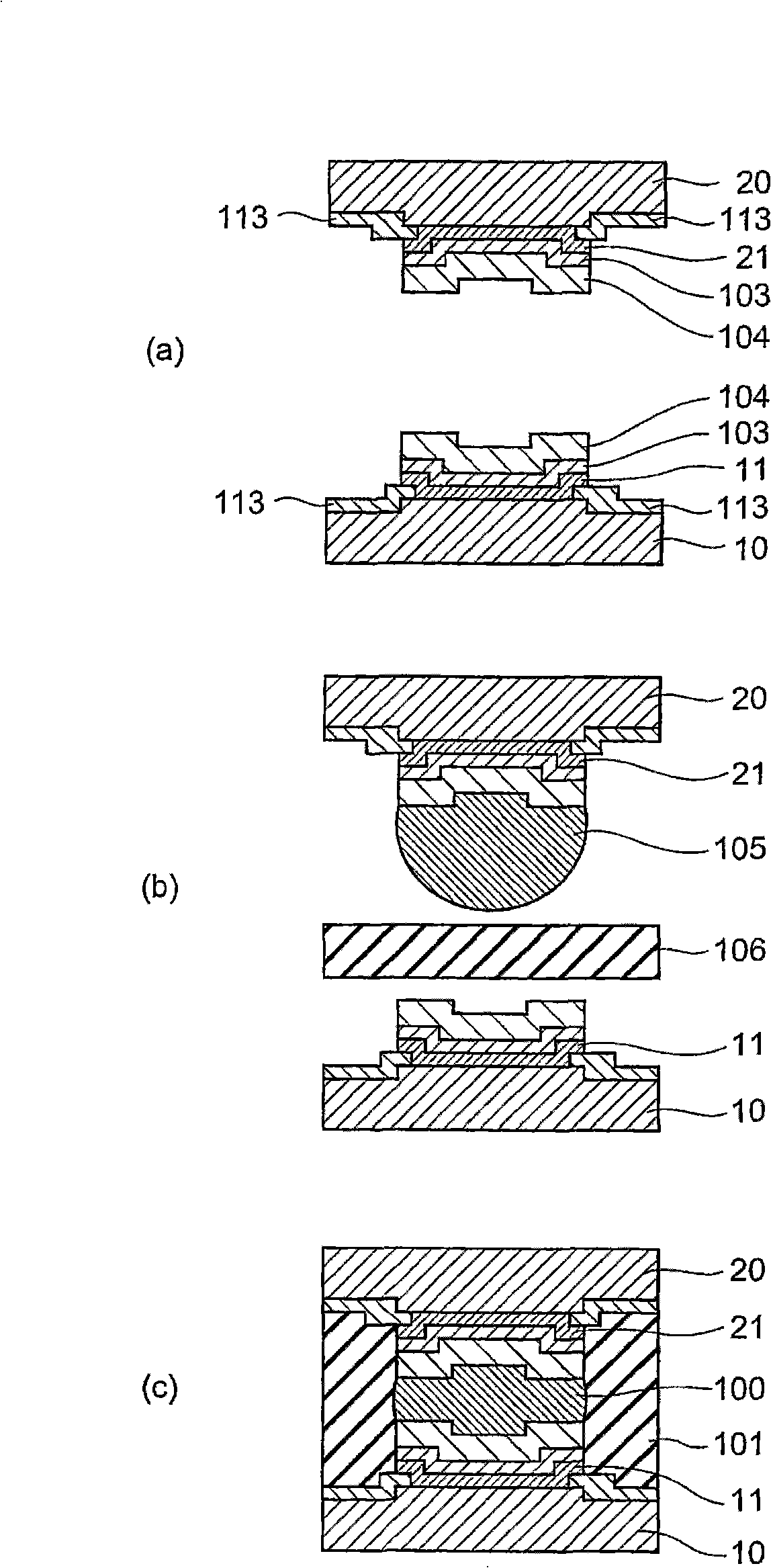

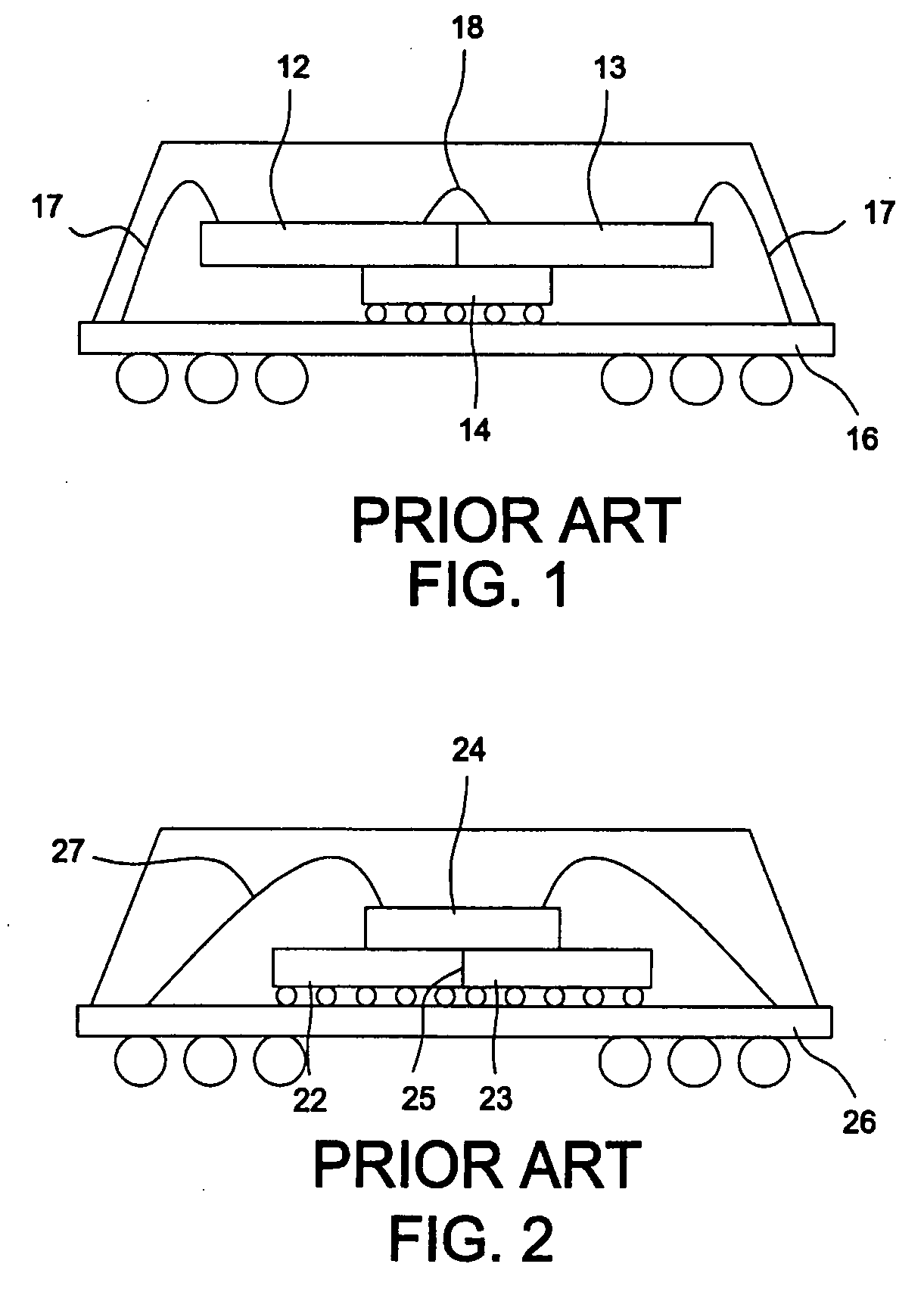

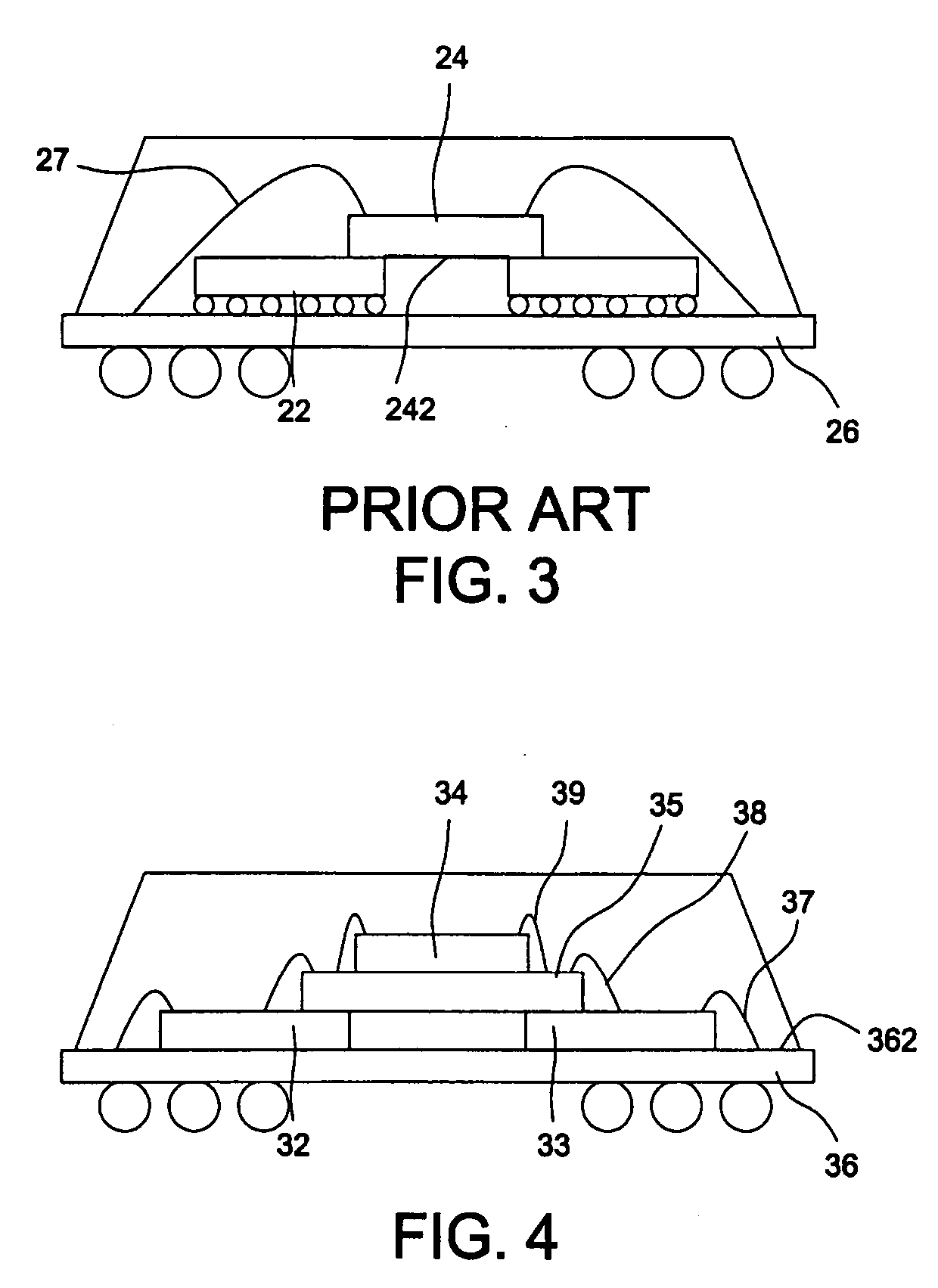

Semiconductor device of chip-on-chip structure

InactiveUS6965166B2Improve productivityEffective positioningSemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipDevice material

A semiconductor device including a first semiconductor chip, a second semiconductor chip bonded to the first semiconductor chip in a stacked relation, and a registration structure which causes the first and second semiconductor chips to be positioned with respect to each other by depression-projection engagement therebetween. The registration structure includes, for example, a registration recess provided on a surface of the first semiconductor chip, and a registration projection provided on a surface of the second semiconductor chip for engagement with the registration recess. The registration projection may be a spherical member provided on the surface of the second semiconductor chip.

Owner:ROHM CO LTD

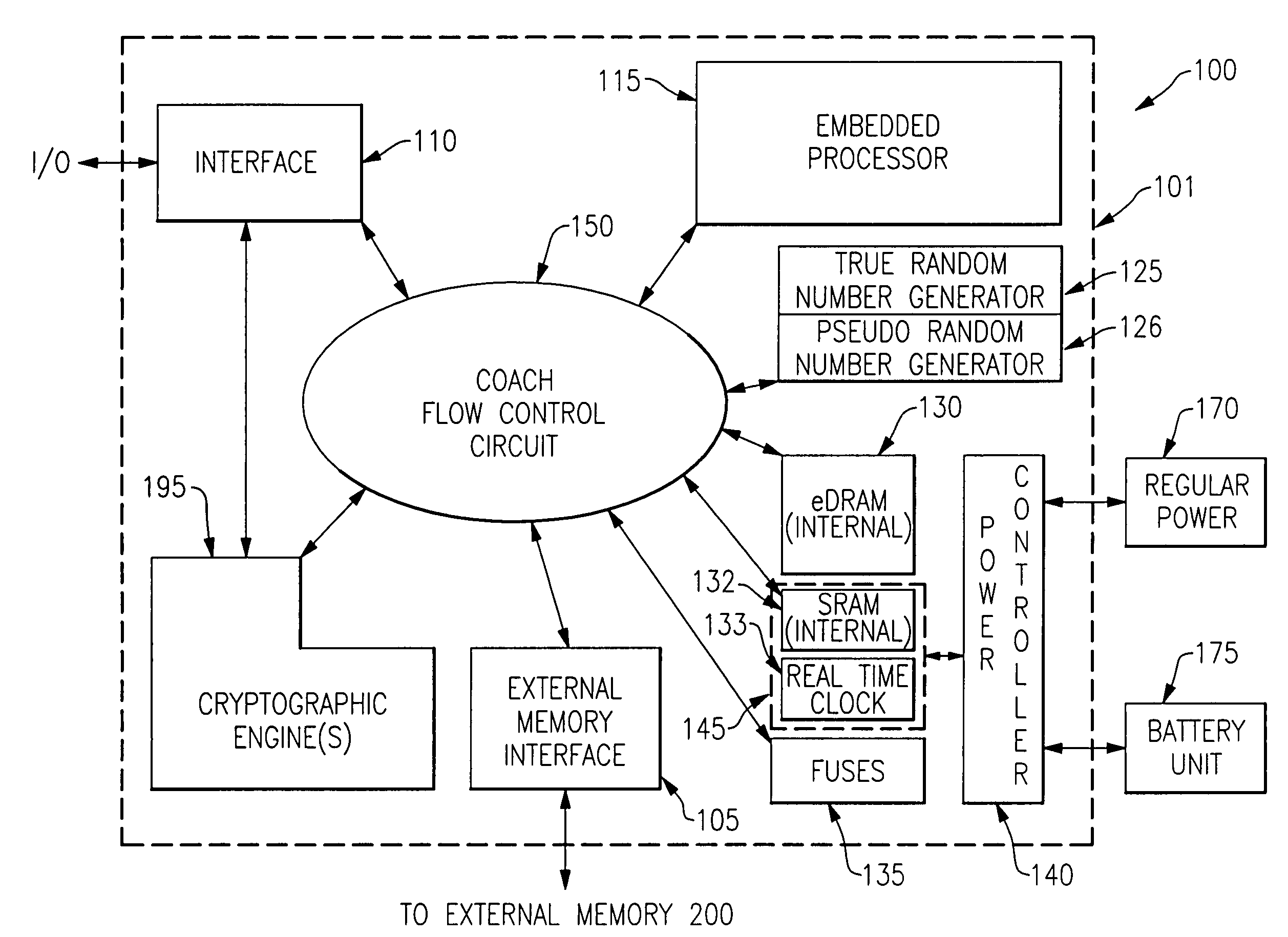

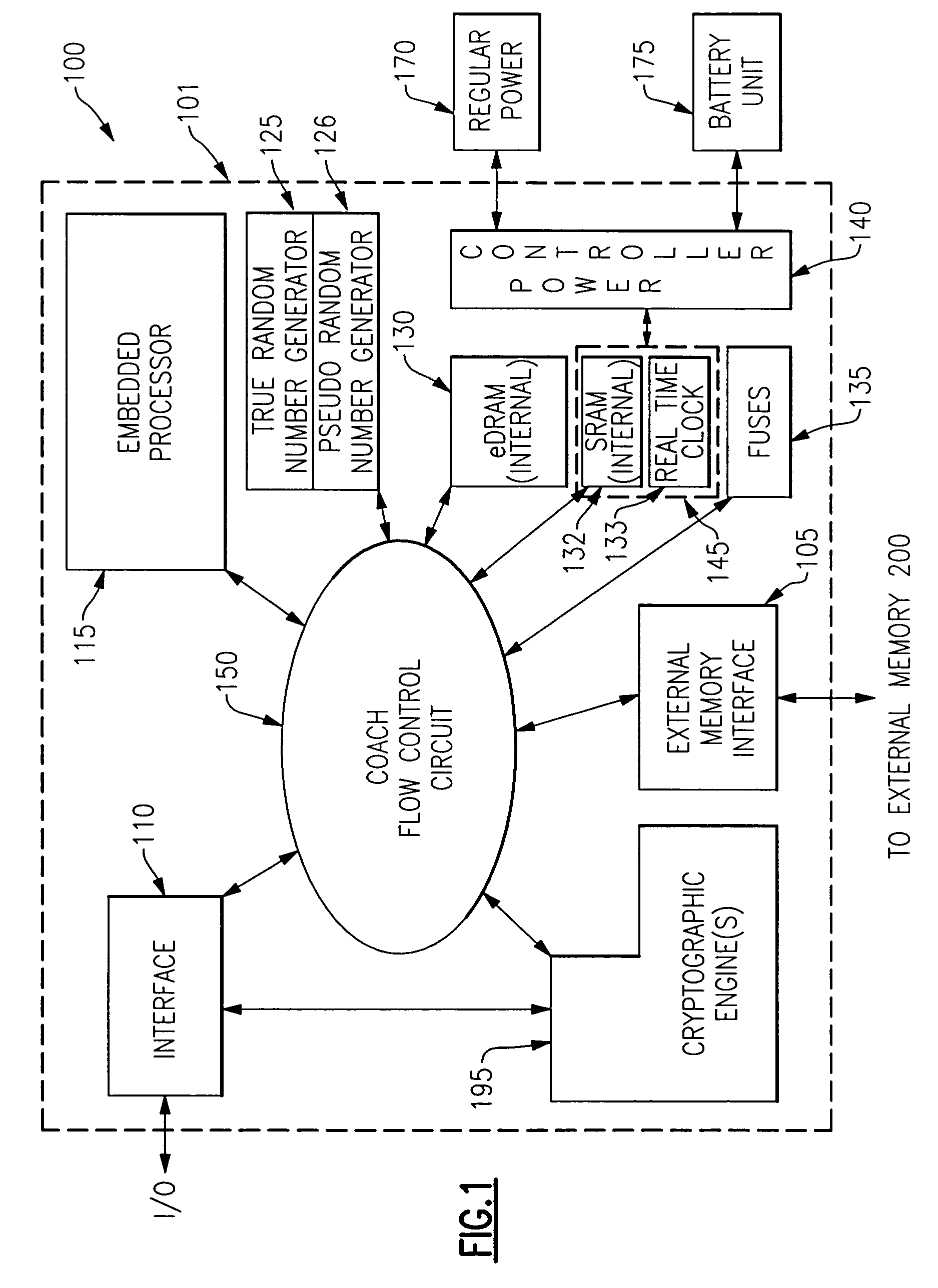

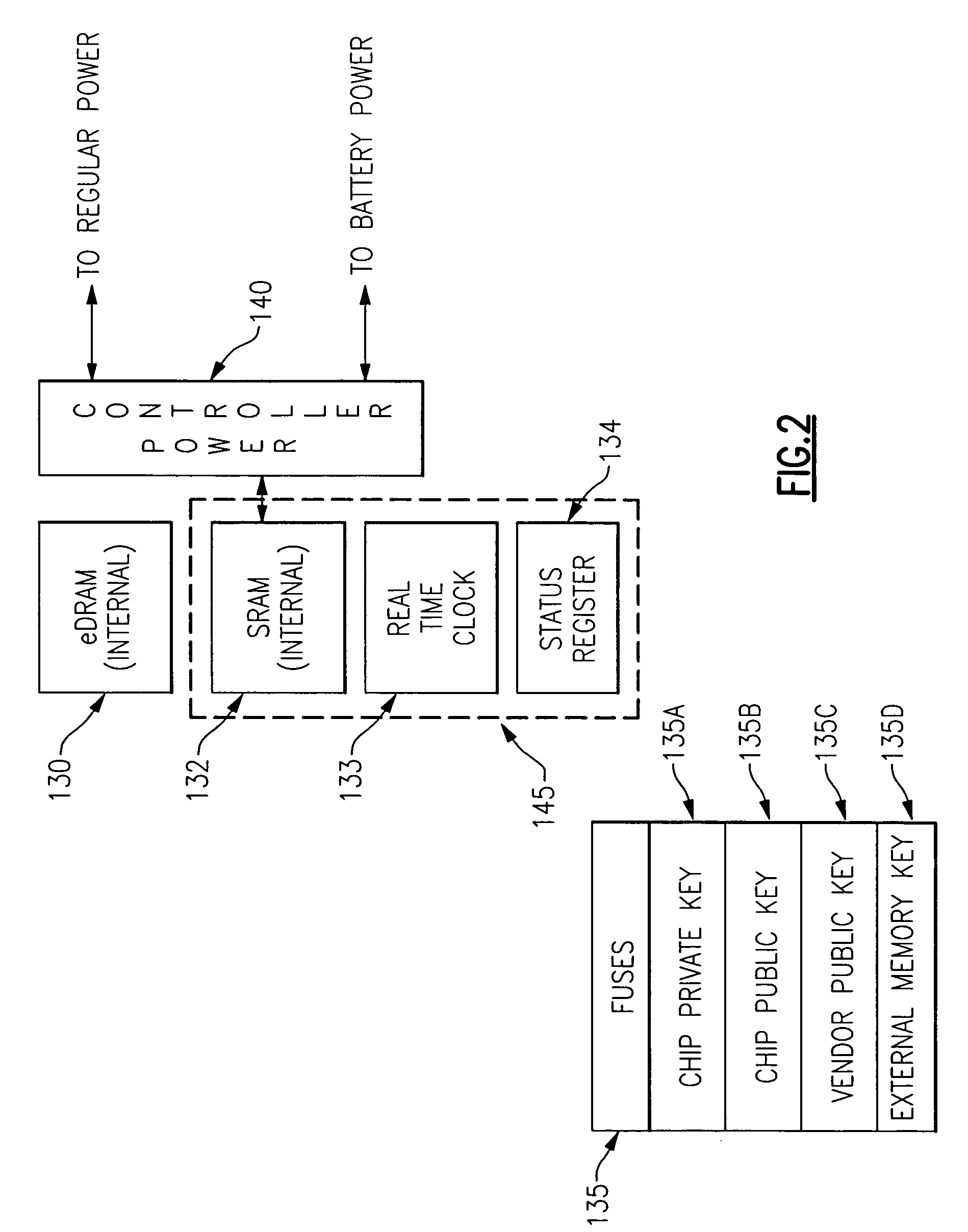

System and method for processing by distinct entities securely configurable circuit chips

InactiveUS20060059368A1Improve process capabilityInhibit involvementUser identity/authority verificationUnauthorized memory use protectionHard codingThird party

A system and method are provided in which a third party chip vendor is enabled to securely program an electronic circuit chip supplied from a chip manufacturer. The chip vendor supplies a vendor's public cryptography key to the chip manufacturer who hard codes it on the chip along with a chip private key and a chip public key. One or more cryptographic engines on the chip, which preferably has a tamper resistant / detecting boundary, are used to decrypt program instructions supplied to the chip after having been encrypted with the vendor's private key and the chip public key. The chip includes a processor and an associated memory which receives a version of the instructions decrypted with the chip private key and the vendor's public key. The chip also preferably includes programmable hardware which is also securely programmable by the downstream chip vendor. The chip, as processed by the chip vendor is shipped with a battery in place to provide power for maintaining data held in volatile memory portions of the chip.

Owner:IBM CORP

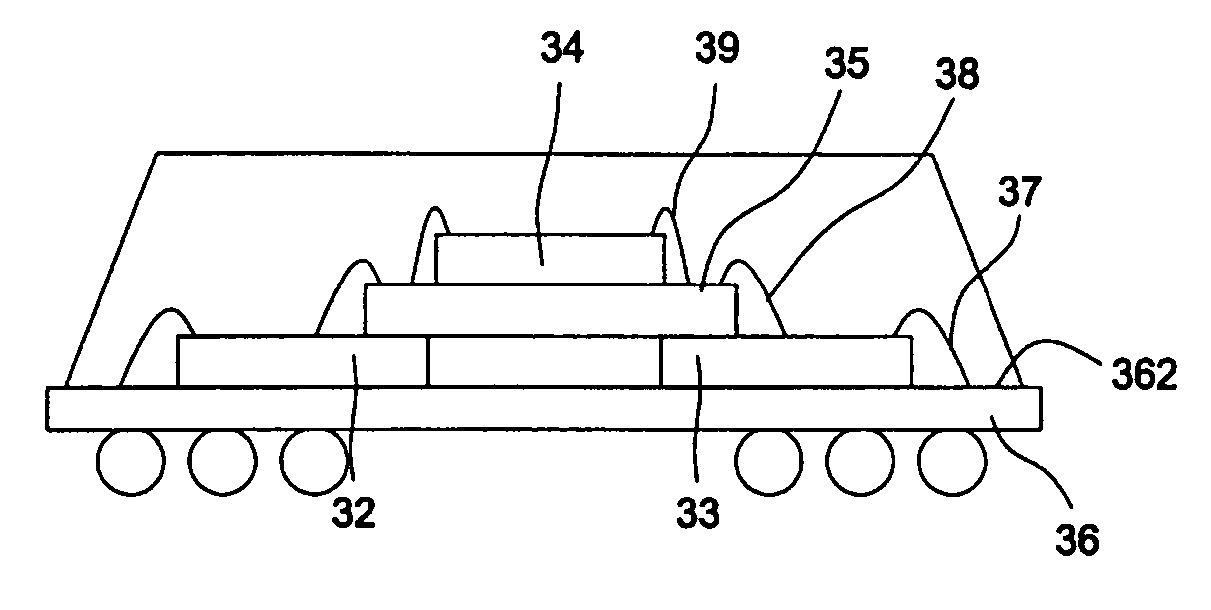

Flip chip stacked package

ActiveUS20050046040A1Improve cooling effectUpgrade thermal performanceSemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipAdhesive

A flip chip stacked package mainly comprises a carrier, a lower chip, an upper chip, a plurality of bumps, a plurality of bonding wires and a supporter. The supporter is attached to the lower surface of the carrier via an adhesive and covers the opening of the carrier. Thus, the lower chip can be disposed in the opening. In addition, the lower chip is electrically flip-chip bonded to the upper chip via the bumps and electrically connected to the carrier via the bonding wires. Accordingly, the heat generated from the lower chip can be transmitted to outside via the supporter. Furthermore, the upper chip is directly exposed to outside so that the capability of the heat dissipation will be enhanced.

Owner:ADVANCED SEMICON ENG INC

Integrated circuit packaging system with a dual board-on-chip structure and method of manufacture thereof

A method of manufacture of an integrated circuit packaging system includes: providing a first board-on-chip-structure having a first integrated circuit die mounted over a substrate and the substrate having a substrate cavity; mounting a second board-on-chip-structure over the first board-on-chip-structure, the second board-on-chip-structure having a second integrated circuit die mounted under an interposer and the interposer having an interposer cavity; connecting the first board-on-chip-structure to the second board-on-chip-structure with an internal interconnect; and encapsulating the first board-on-chip-structure, the second board-on-chip-structure, and the internal interconnect with an encapsulation.

Owner:STATS CHIPPAC LTD

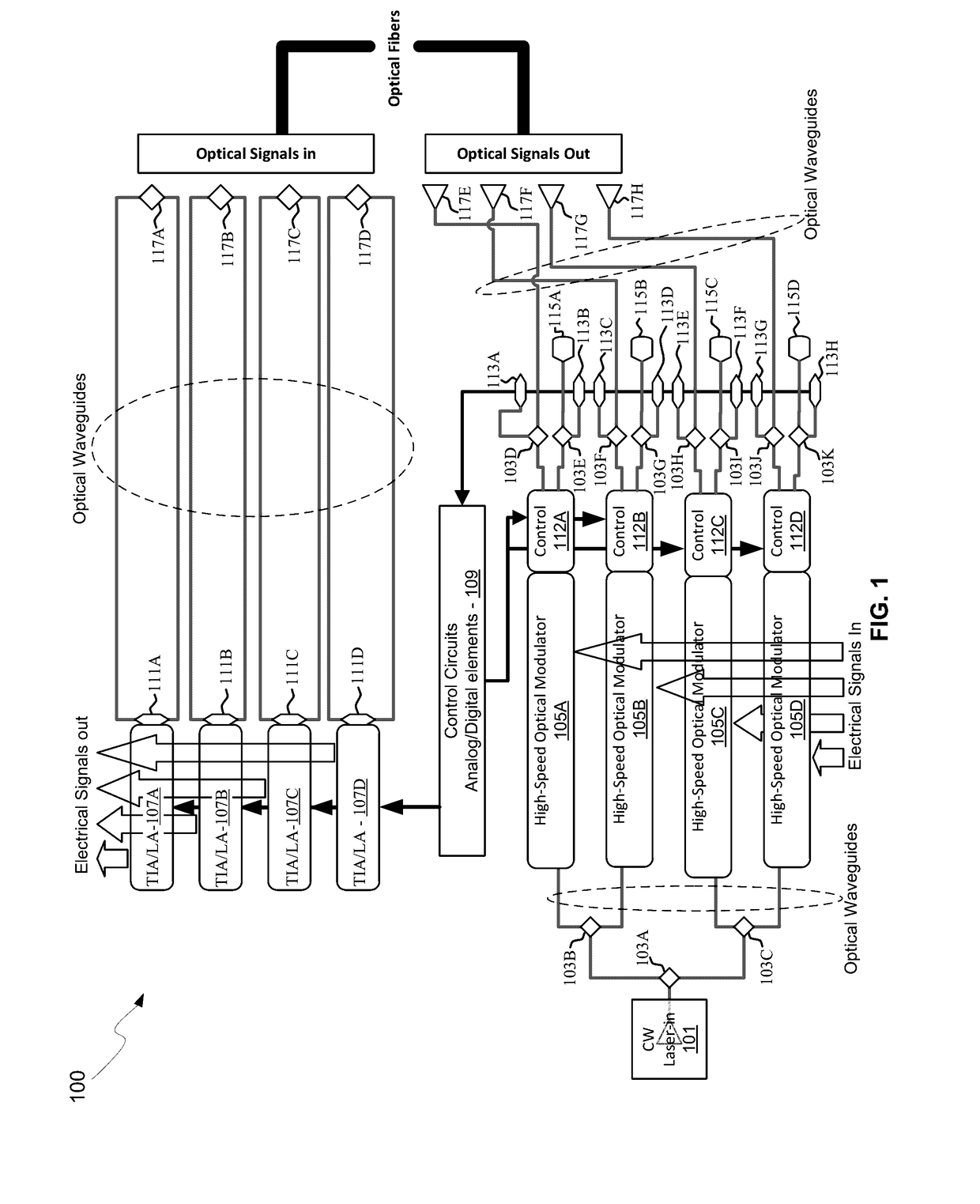

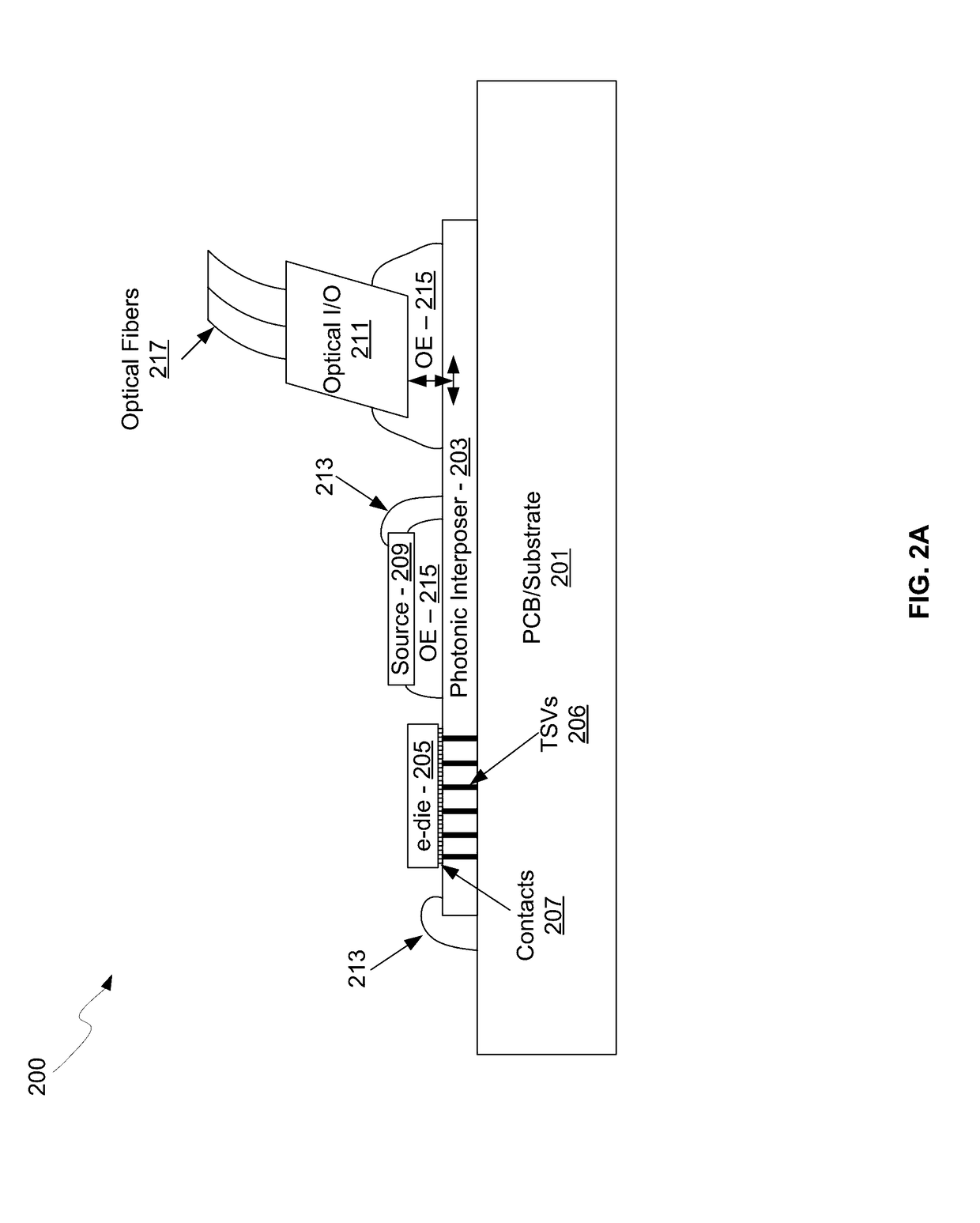

Method And System For A Chip-On-Wafer-On-Substrate Assembly

Methods and systems for a chip-on-wafer-on-substrate assembly are disclosed and may include in an integrated optical communication system comprising an electronics die and a substrate. The electronics die is bonded to a first surface of a photonic interposer and the substrate is coupled to a second surface of the photonic interposer opposite to the first surface. An optical fiber and a light source assembly are coupled to the second surface of the interposer in one or more cavities formed in the substrate. The integrated optical communication system is operable to receive a continuous wave (CW) optical signal in the photonic interposer from the light source assembly; and communicate a modulated optical signal to the optical fiber from said photonic interposer. A mold compound may be on the first surface of the interposer and in contact with the electronics die. The received CW optical signal may be coupled to an optical waveguide in the photonic interposer using a grating coupler.

Owner:CISCO TECH INC

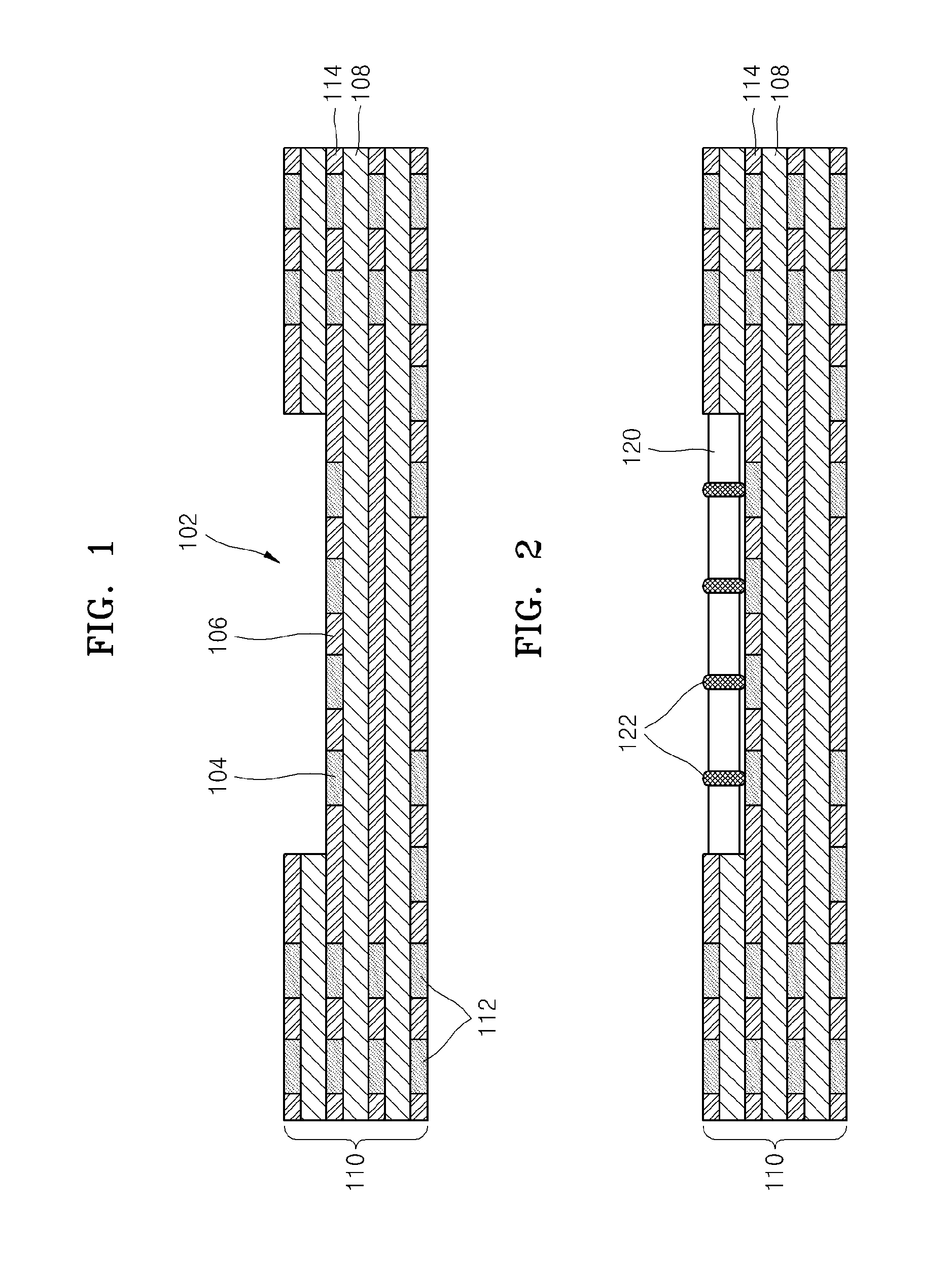

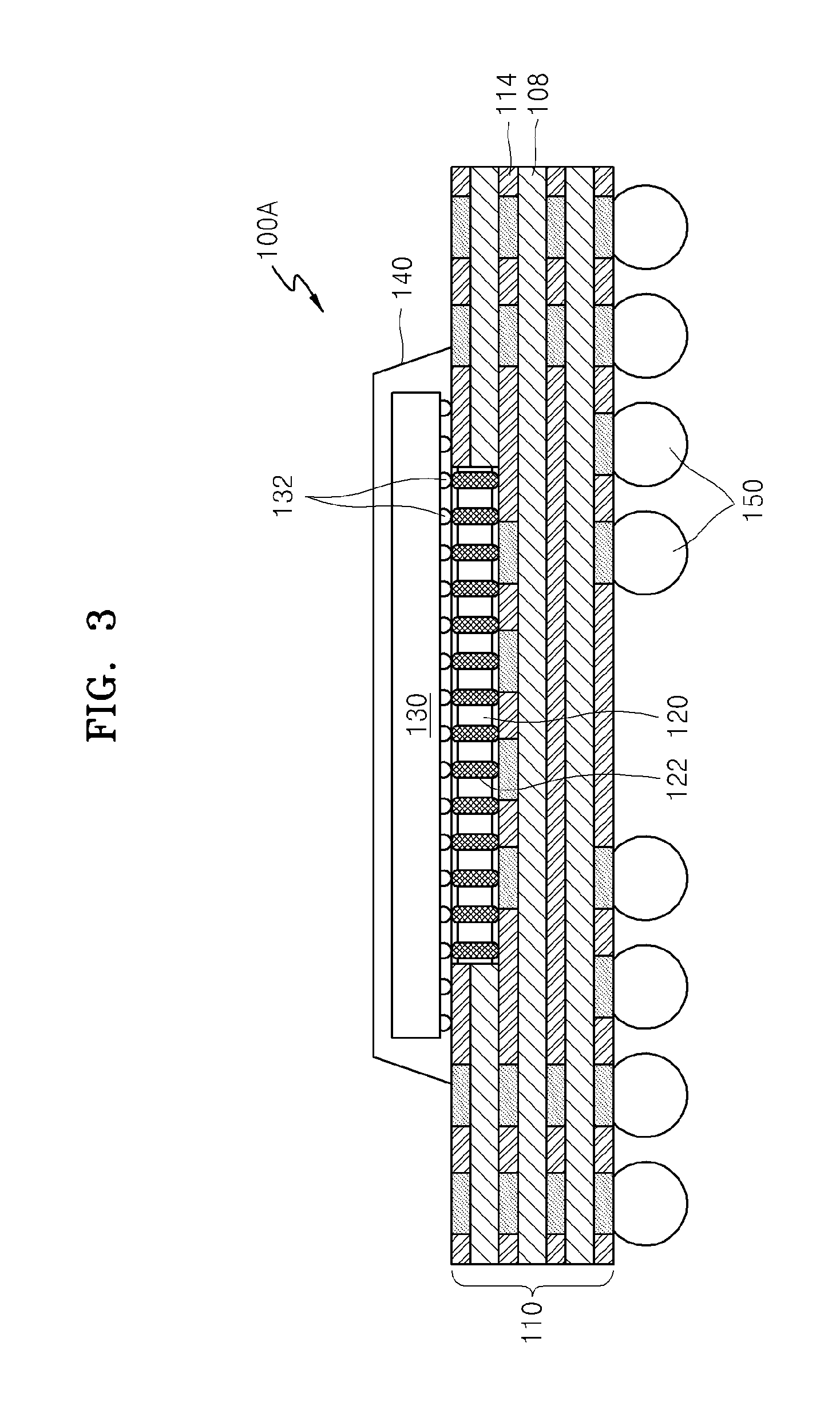

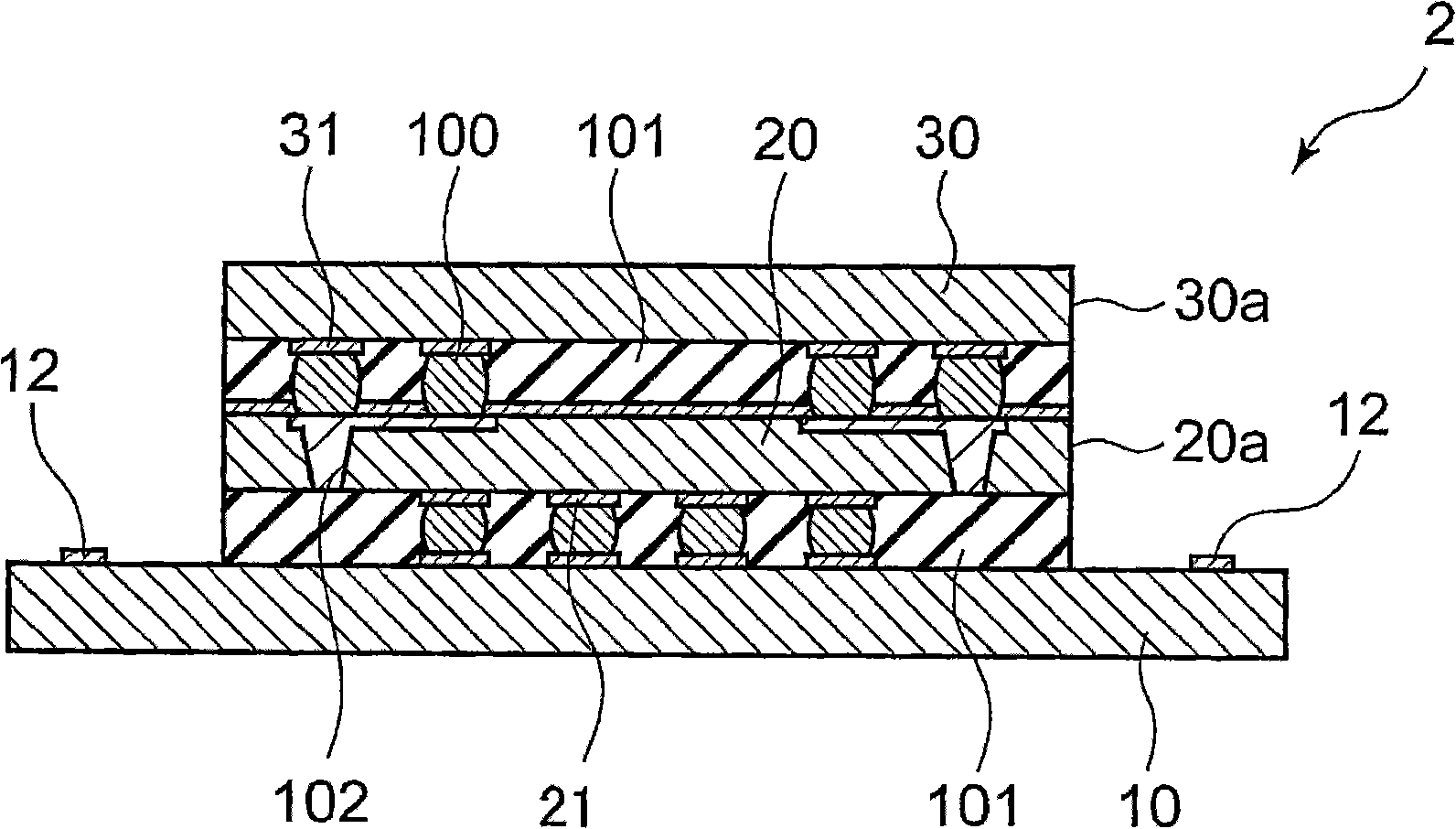

Embedded chip-on-chip package and package-on-package comprising same

ActiveUS20110317381A1Small sizeImproved internal connectionPrinted circuit aspectsSolid-state devicesChIP-on-chipSemiconductor chip

An embedded chip-on-chip package comprises a printed circuit board having a recessed semiconductor chip mounting unit, a first semiconductor chip embedded in the recessed semiconductor chip mounting unit, and a second semiconductor chip mounted on the first semiconductor chip and the printed circuit board.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor electronic component and semiconductor device using the same

InactiveUS20100102446A1Minimize bleedingMeet the requirementsSemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipShortest distance

Owner:SUMITOMO BAKELITE CO LTD

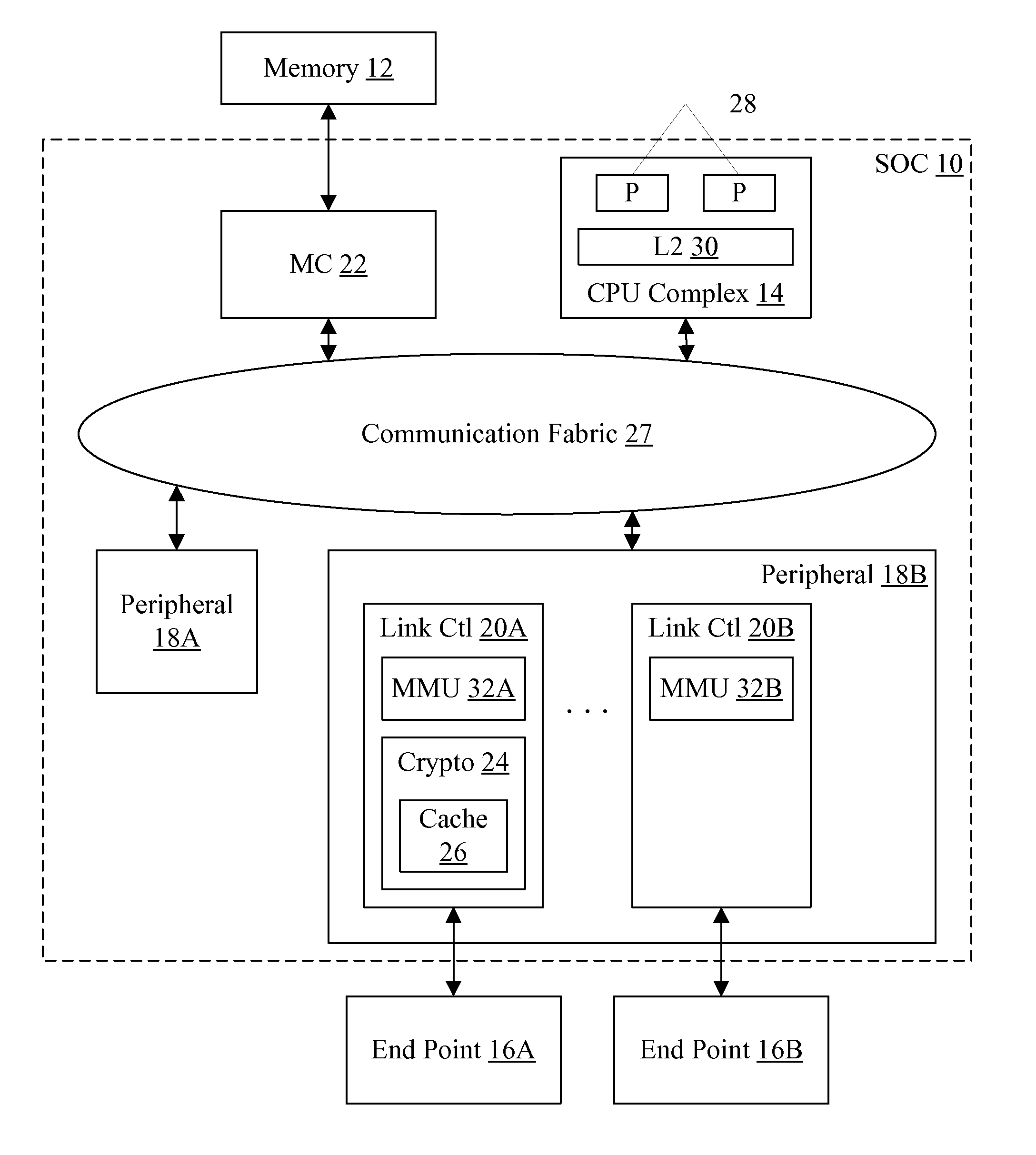

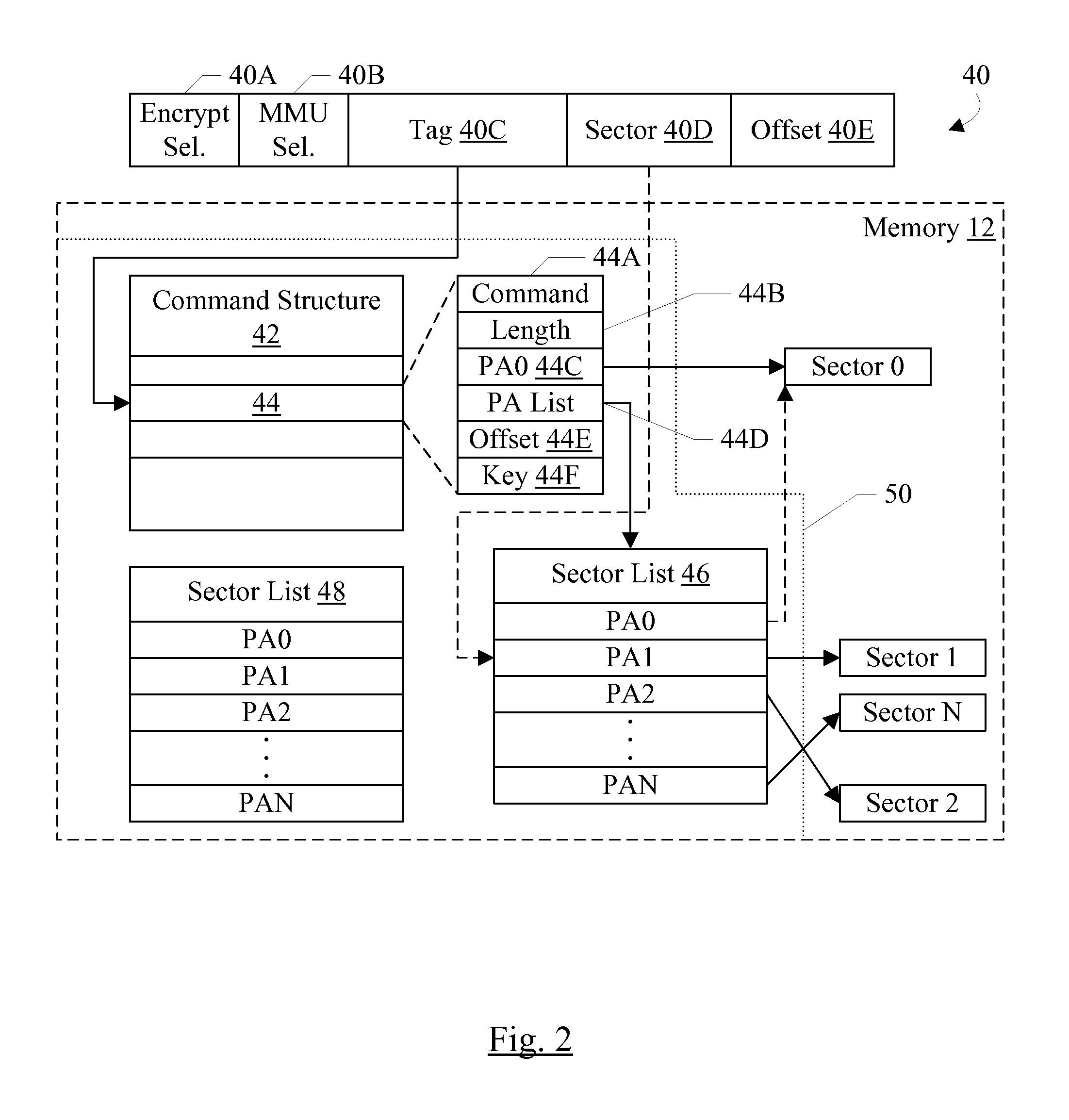

Embedded Encryption/Secure Memory Management Unit for Peripheral Interface Controller

ActiveUS20150046702A1Lower latencyReduce dataSynchronising transmission/receiving encryption devicesUnauthorized memory use protectionComputer hardwareManagement unit

In an embodiment, a peripheral interface controller may include an inline cryptographic engine which may encrypt data being sent over a peripheral interface and decrypt data received from the peripheral interface. The encryption may be transparent to the device connected to the peripheral interface that is receiving / supplying the data. In an embodiment, the peripheral interface controller is included in a system on a chip (SOC) that also includes a memory controller configured to couple to a memory. The memory may be mounted on the SOC in a chip-on-chip or package-on-package configuration. The unencrypted data may be stored in the memory for use by other parts of the SOC (e.g. processors, on-chip peripherals, etc.). The keys used for the encryption / decryption of data may remain within the SOC.

Owner:APPLE INC

Adhesive tape and semiconductor device using the same

InactiveUS20100078830A1Good ion migration resistanceGood solder wettabilitySemiconductor/solid-state device detailsSynthetic resin layered productsChIP-on-chipSemiconductor chip

The present invention relates to an adhesive tape for electrically connecting semiconductor chips in a chip-on-chip type semiconductor device. The adhesive tape comprising: (A) 10 to 50 wt % of film forming resin; (B) 30 to 80 wt % of curable resin; and (C) 1 to 20 wt % of curing agent having flux activity.

Owner:SUMITOMO BAKELITE CO LTD

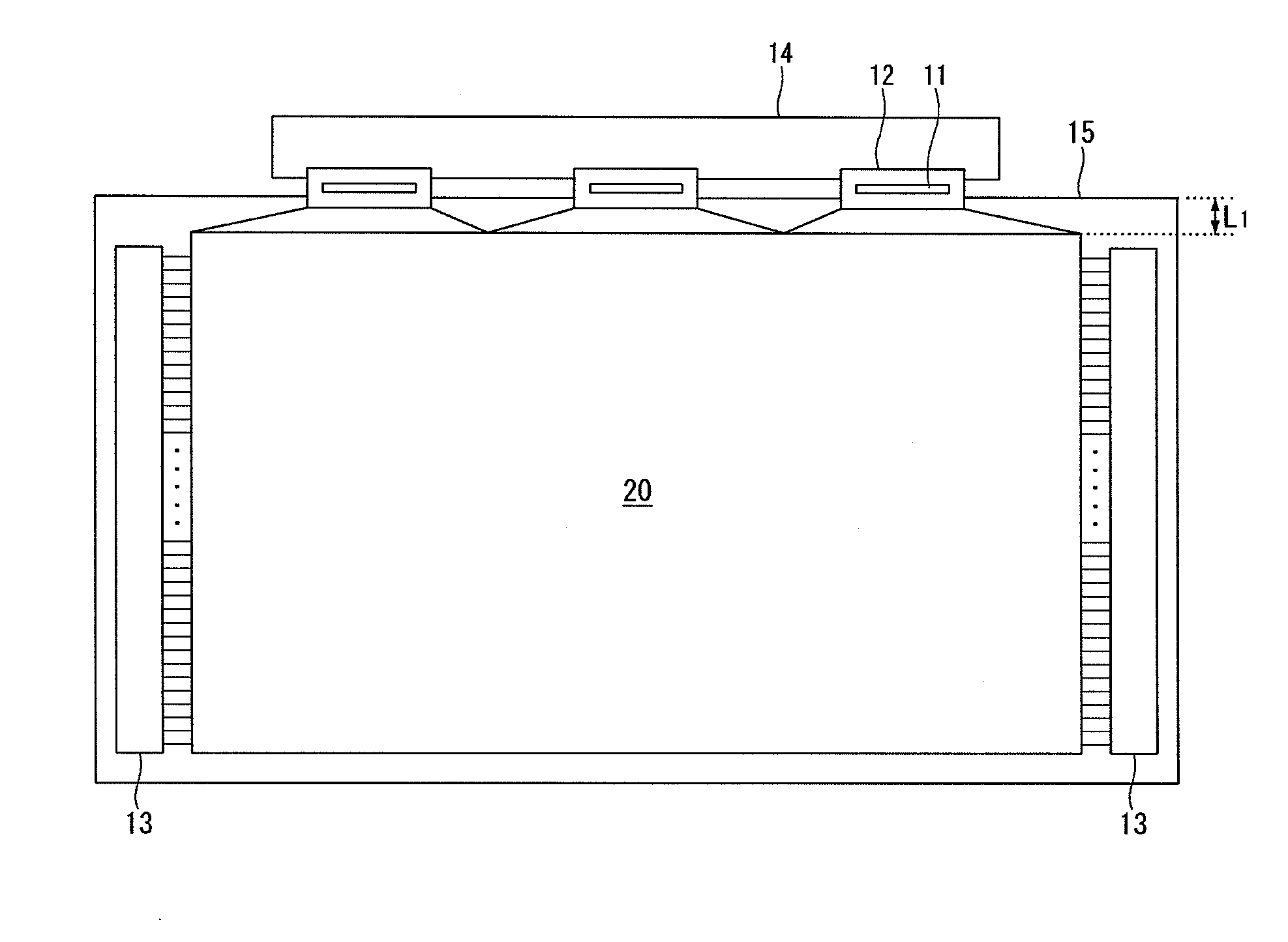

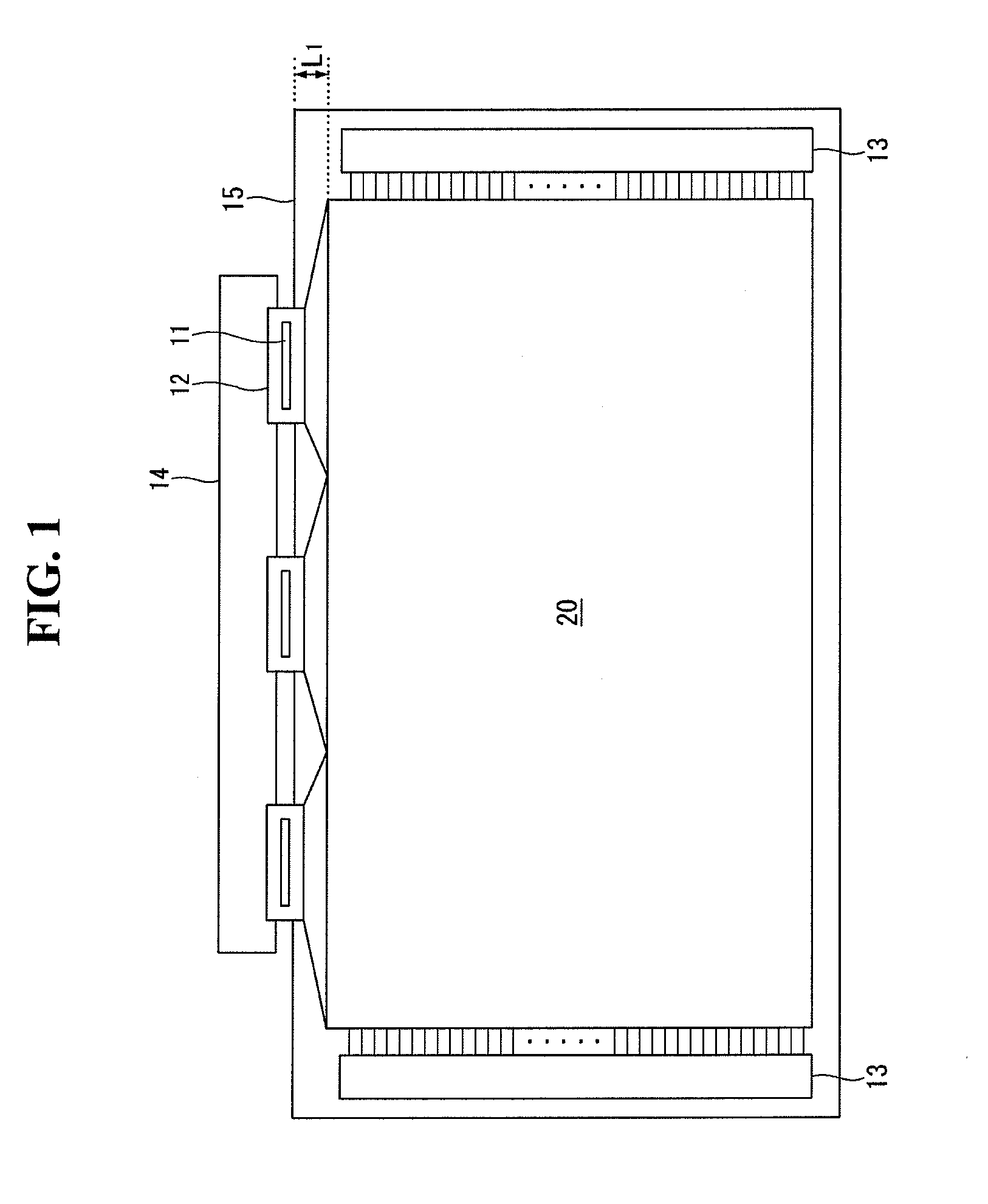

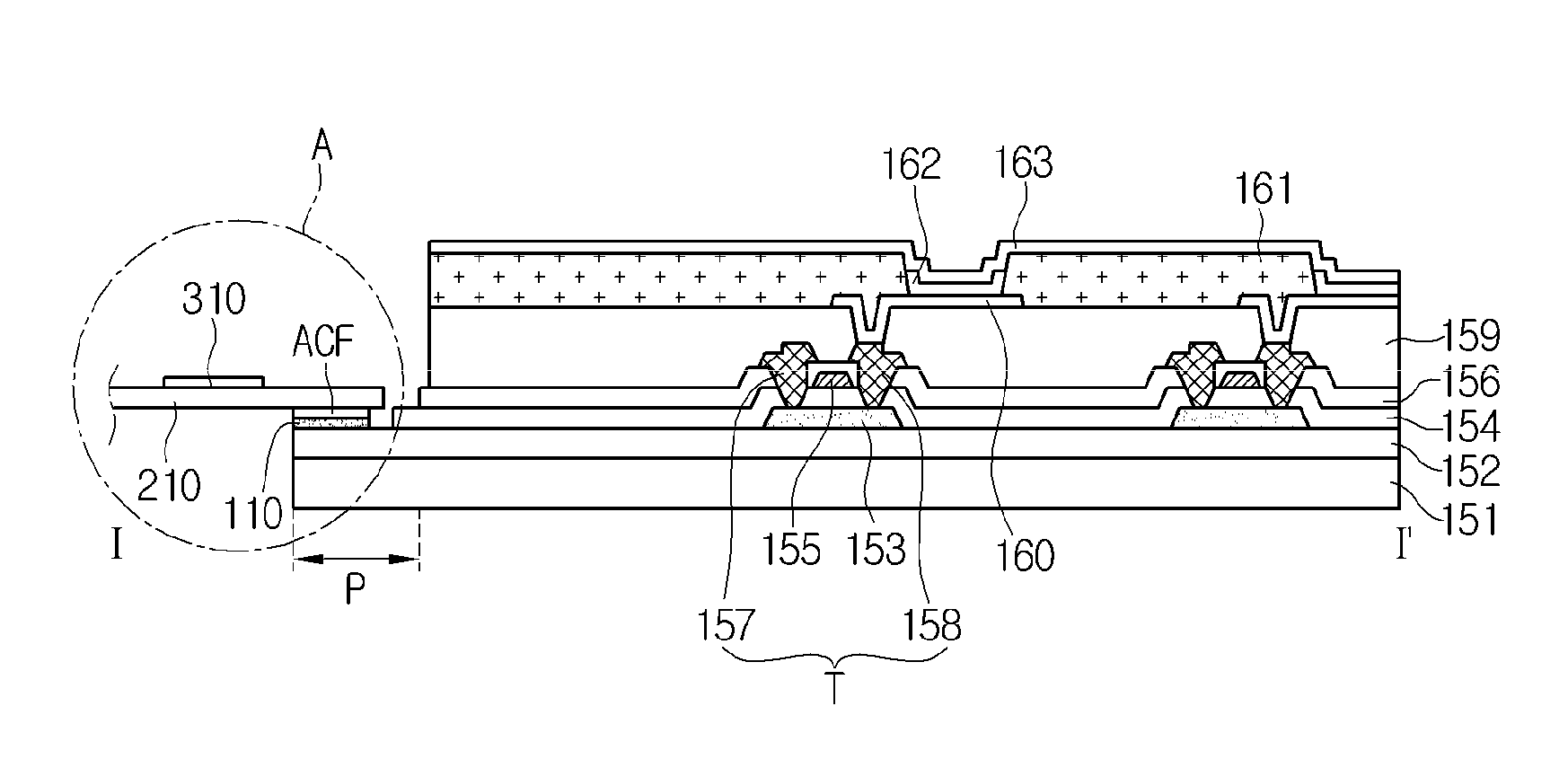

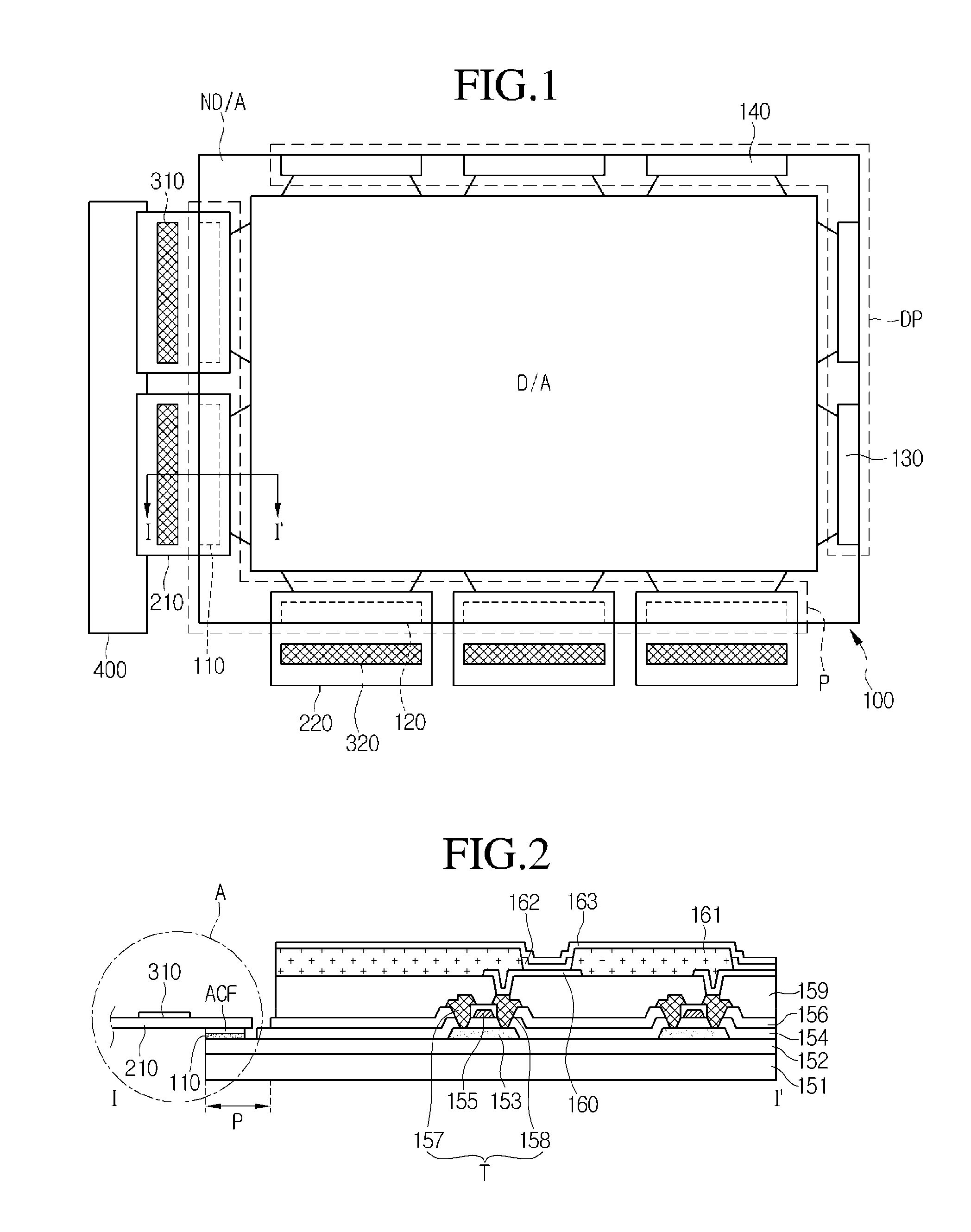

Liquid crystal display

ActiveUS20100265225A1Small sizePreventing defective orientation of liquid crystalsCathode-ray tube indicatorsNon-linear opticsChip on filmChIP-on-chip

A liquid crystal display is disclosed. The liquid crystal display includes a liquid crystal display panel including an upper substrate, a lower substrate, a liquid crystal layer between the upper substrate and the lower substrate, and m×n liquid crystal cells (where m and n are a positive integer) arranged in a matrix format according to a crossing structure of m / 2 data lines and 2n gate lines, a plurality of chip on films (COFs) on which source driver integrated circuits (ICs) supplying a data voltage to the data lines are mounted, a printed circuit board (PCB) connected to input terminals of the COFs, and a gate drive circuit directly mounted onto the lower substrate, the gate drive circuit supplying a gate pulse to the gate lines.

Owner:LG DISPLAY CO LTD

Semiconductor device and method for manufacturing same

InactiveUS7247518B2Improve signal transmission speedSemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipSemiconductor chip

There is provided a semiconductor device of a chip-on-chip structure having a support semiconductor chip, first and second chip blocks supported and connected on one surface of the support semiconductor chip and an insulator arranged between the first and second chip blocks. The first and second chip blocks each include one or a plurality of semiconductor chips having an active surface nearly parallel with the one surface of the support semiconductor chip. Within the insulator, an intralevel wiring is arranged on a wiring plane as a plane including an inactive or active surface of any of the semiconductor chips structuring the first or second chip block.

Owner:ACHLYS TECH INC

Semiconductor packages and methods of manufacturing the same

InactiveUS20090184411A1Semiconductor/solid-state device detailsSolid-state devicesChIP-on-chipSemiconductor package

Provided are semiconductor packages and methods of manufacturing the semiconductor package. The semiconductor packages may include a substrate including a chip pad, a redistributed line which is electrically connected to the chip pad and includes an opening. The semiconductor packages may also include an external terminal connection portion, and an external terminal connection pad which is disposed at an opening and electrically connected to the redistributed line. The present general inventive concept can solve the problem where an ingredient of gold included in a redistributed line may be prevented from being diffused into an adjacent bump pad to form a void or an undesired intermetallic compound. In a chip on chip structure, a plurality of bumps of a lower chip are connected to an upper chip to improve reliability, diversity and functionality of the chip on chip structure.

Owner:SAMSUNG ELECTRONICS CO LTD

Tape wiring substrate and chip-on-film package using the same

ActiveUS7420270B2Semiconductor/solid-state device detailsCross-talk/noise/interference reductionChip on filmChIP-on-chip

A chip-on-film package may include a tape wiring substrate, a semiconductor chip mounted on the tape wiring substrate, and a molding compound provided between the semiconductor chip and the tape wiring substrate. The tape wiring substrate may include a film having upper and lower surfaces. Vias may penetrate the film. An upper metal layer may be provided on the upper surface of the film and include input terminal patterns and / or output terminal patterns. The input terminal patterns may include ground terminal patterns and / or power terminal patterns. A lower metal layer may be provided on the lower surface of the film and include a ground layer and / or a power layer. The ground layer and the power layer may cover at least a chip mounting area.

Owner:SAMSUNG ELECTRONICS CO LTD

Light emitting diode

InactiveUS20070018189A1Uniform colorLight colorSolid-state devicesSemiconductor devicesChIP-on-chipColor mixing

A light emitting diode is disclosed. A light emitting diode comprises: a bracing frame; and at least two chips stacked on the bracing frame in a chip-on-chip stacking manner. The light emitting diode for uniform color mixing is completed after each of said at least two chips is electrically connected.

Owner:UNITY OPTO TECH CO LTD

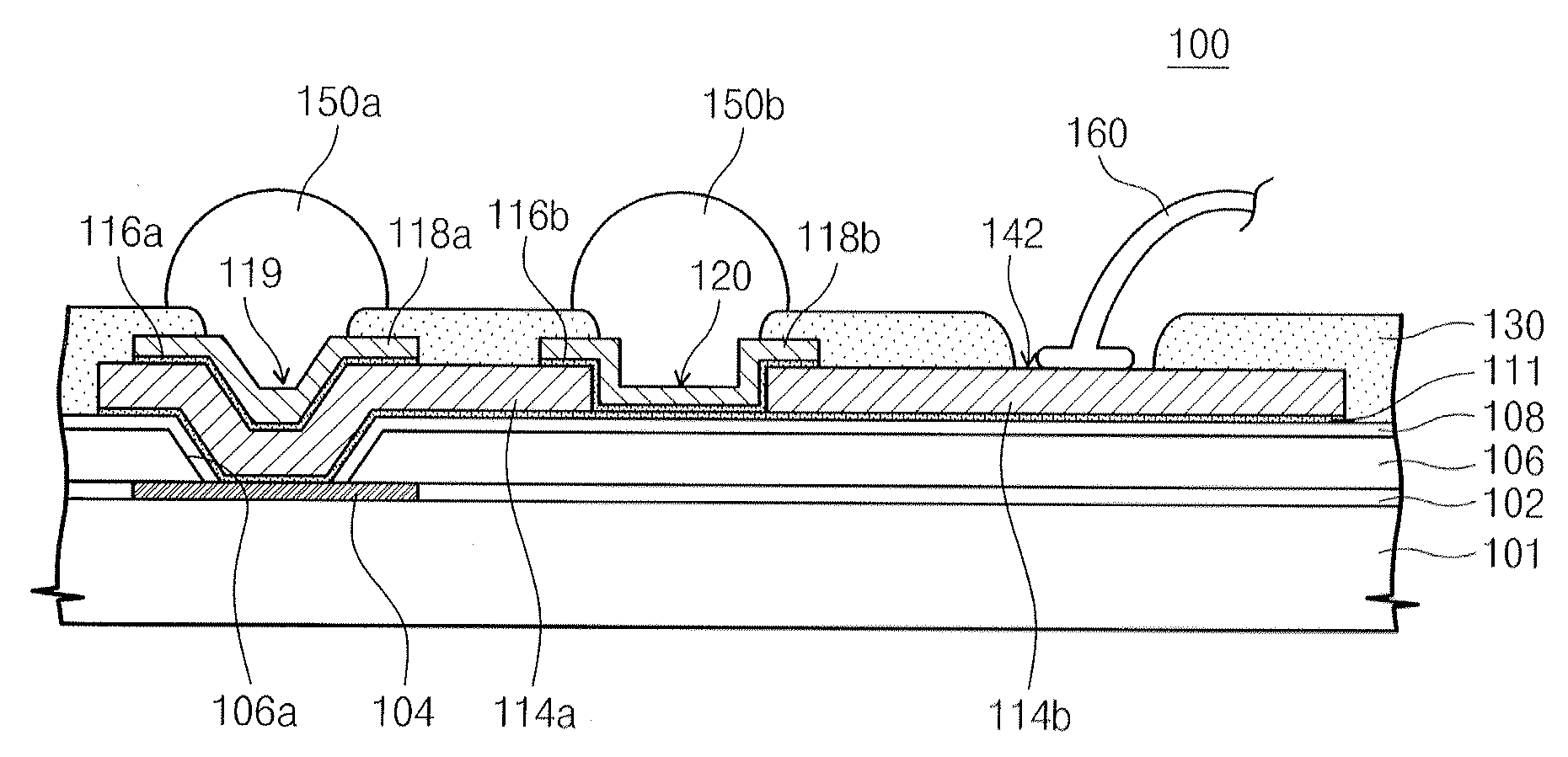

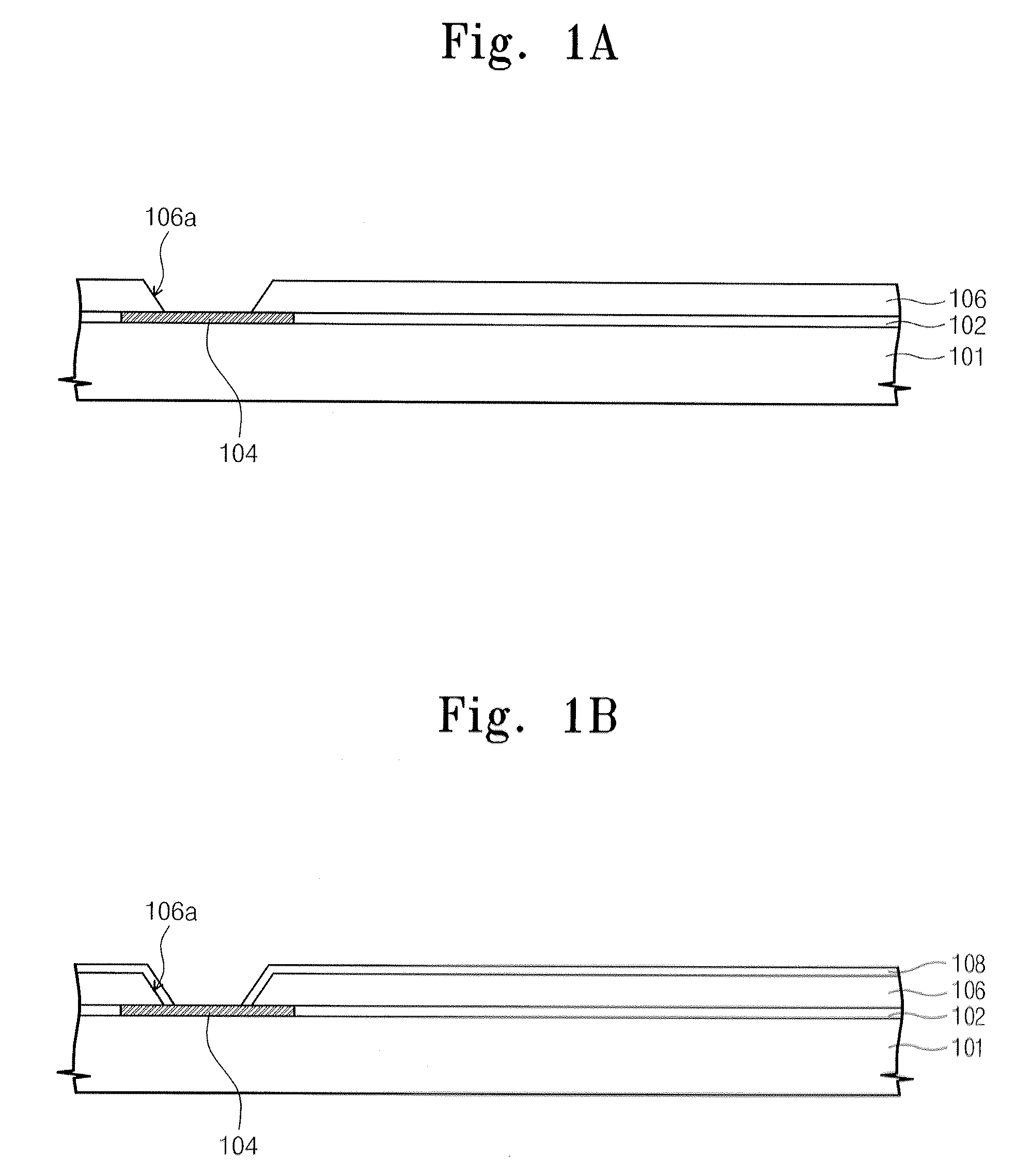

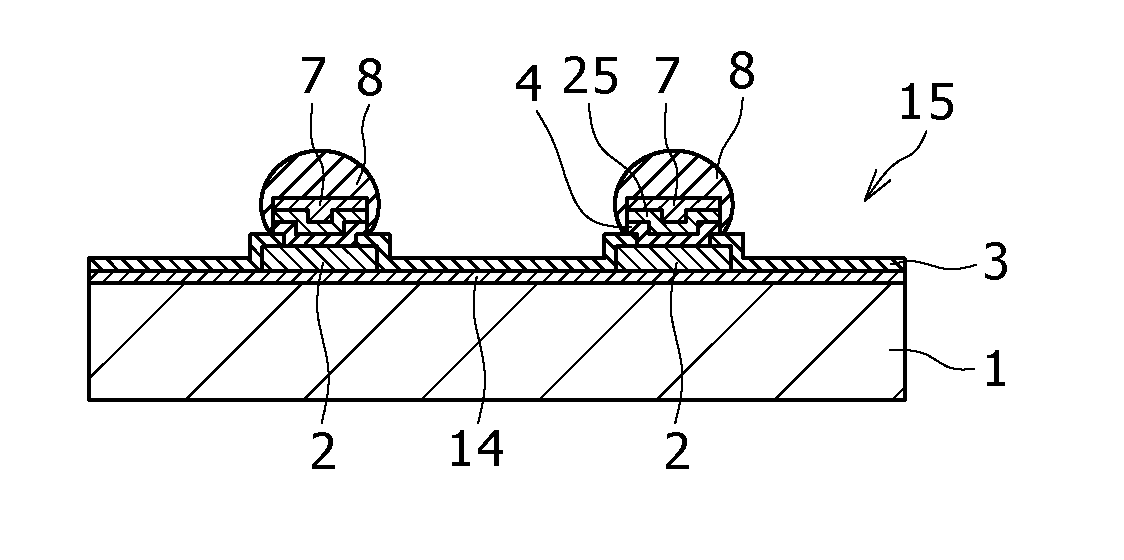

Semiconductor device, chip-on-chip mounting structure, method of manufacturing the semiconductor device, and method of forming the chip-on-chip mounting structure

InactiveUS20110193223A1Prevent short-circuitingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipSemiconductor chip

A semiconductor device includes: a semiconductor chip having a semiconductor substrate; a pad electrode formed on the semiconductor substrate; a base metal layer formed on said pad electrode; and a bump electrode formed on the base metal layer, in which an exposed surface including a side surface of the base metal layer is covered with the solder bump electrode.

Owner:SONY CORP

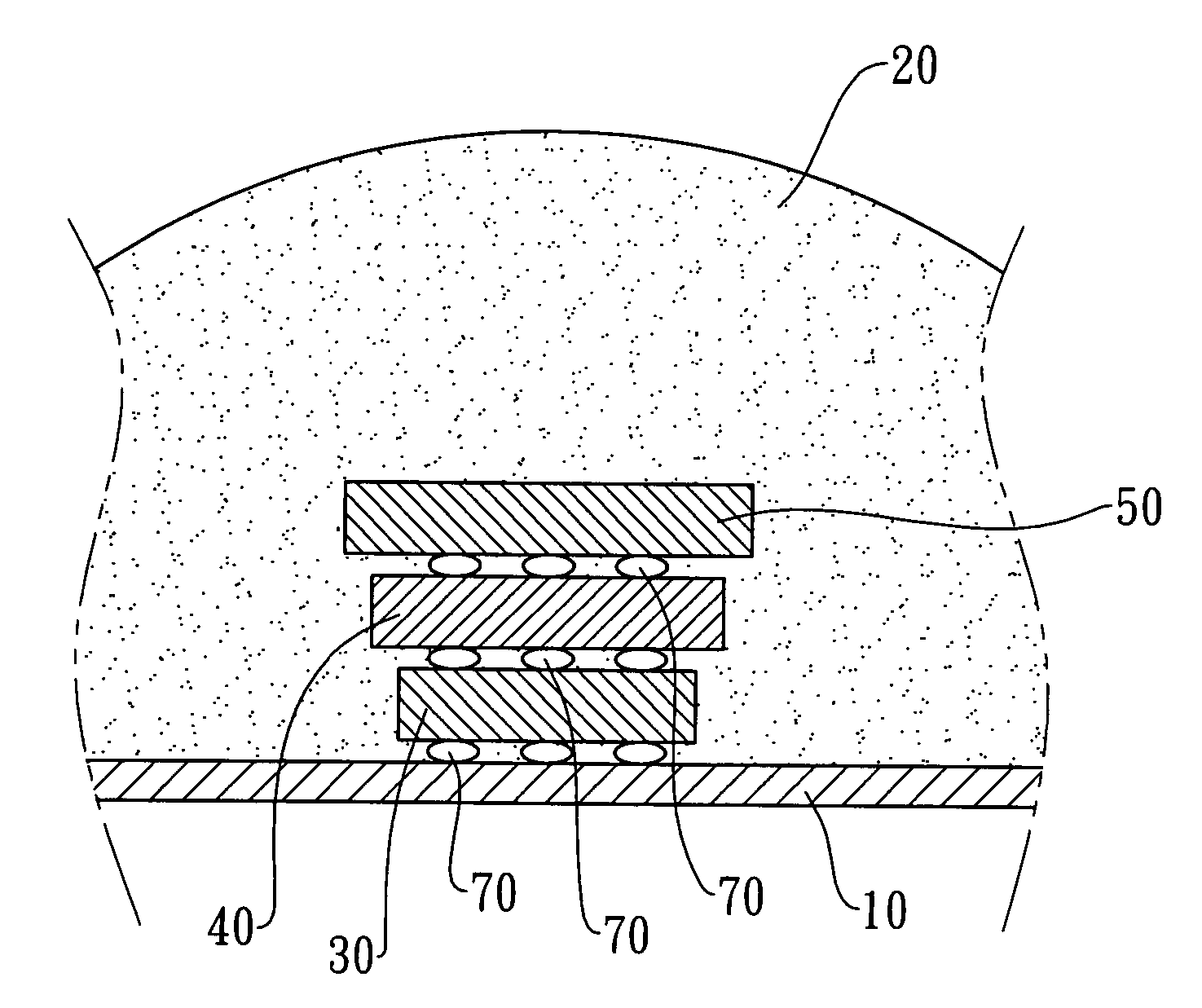

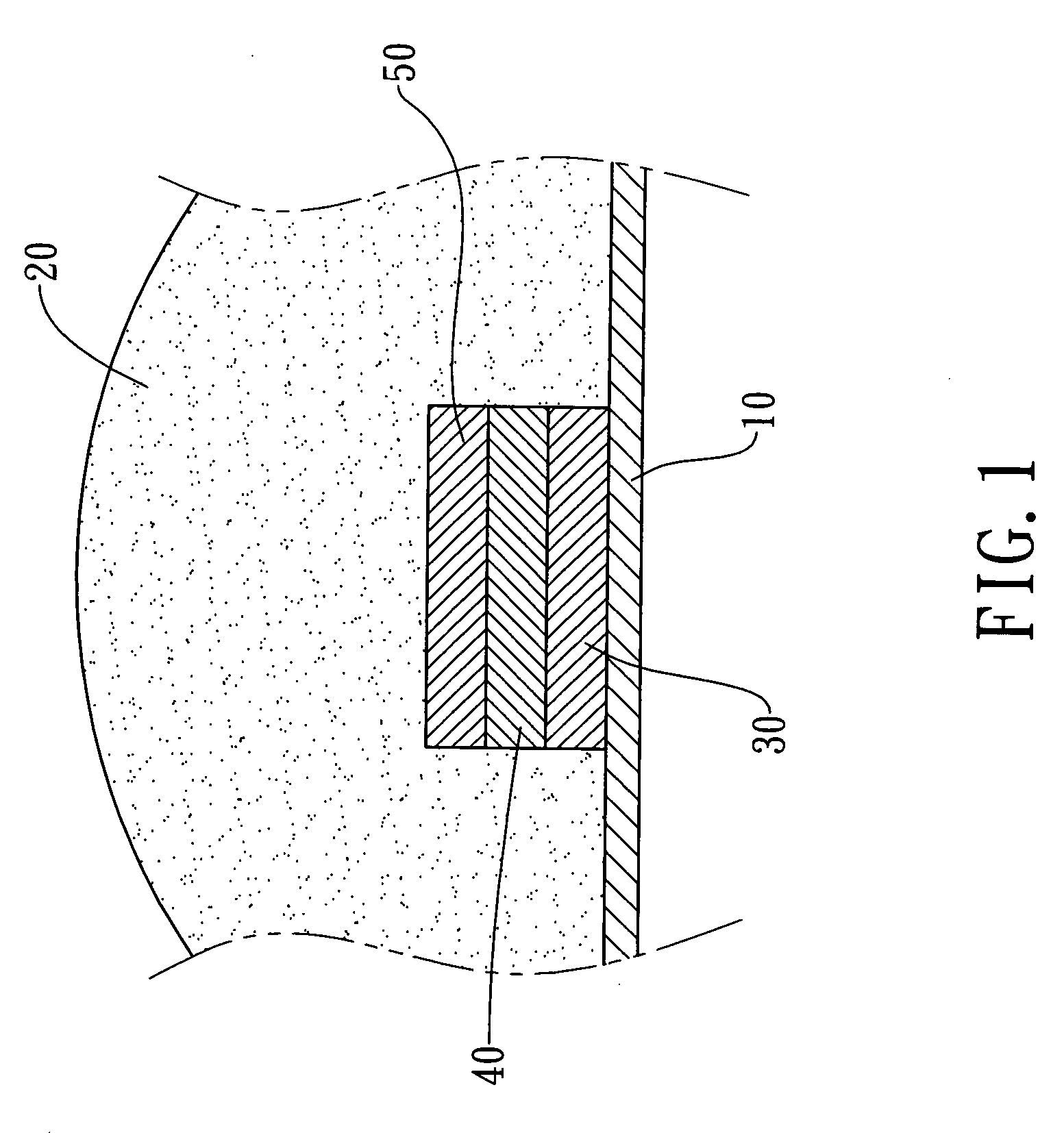

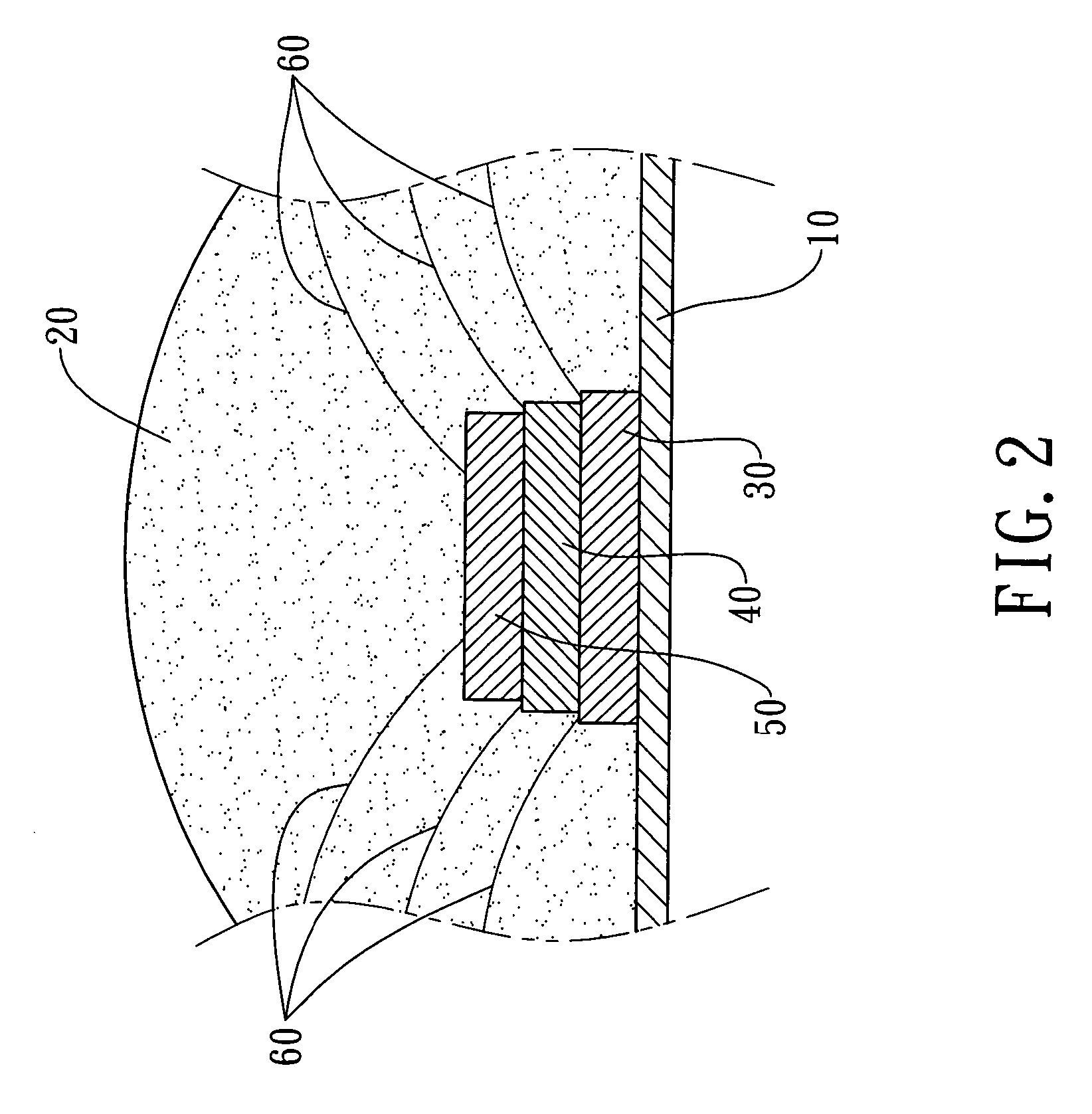

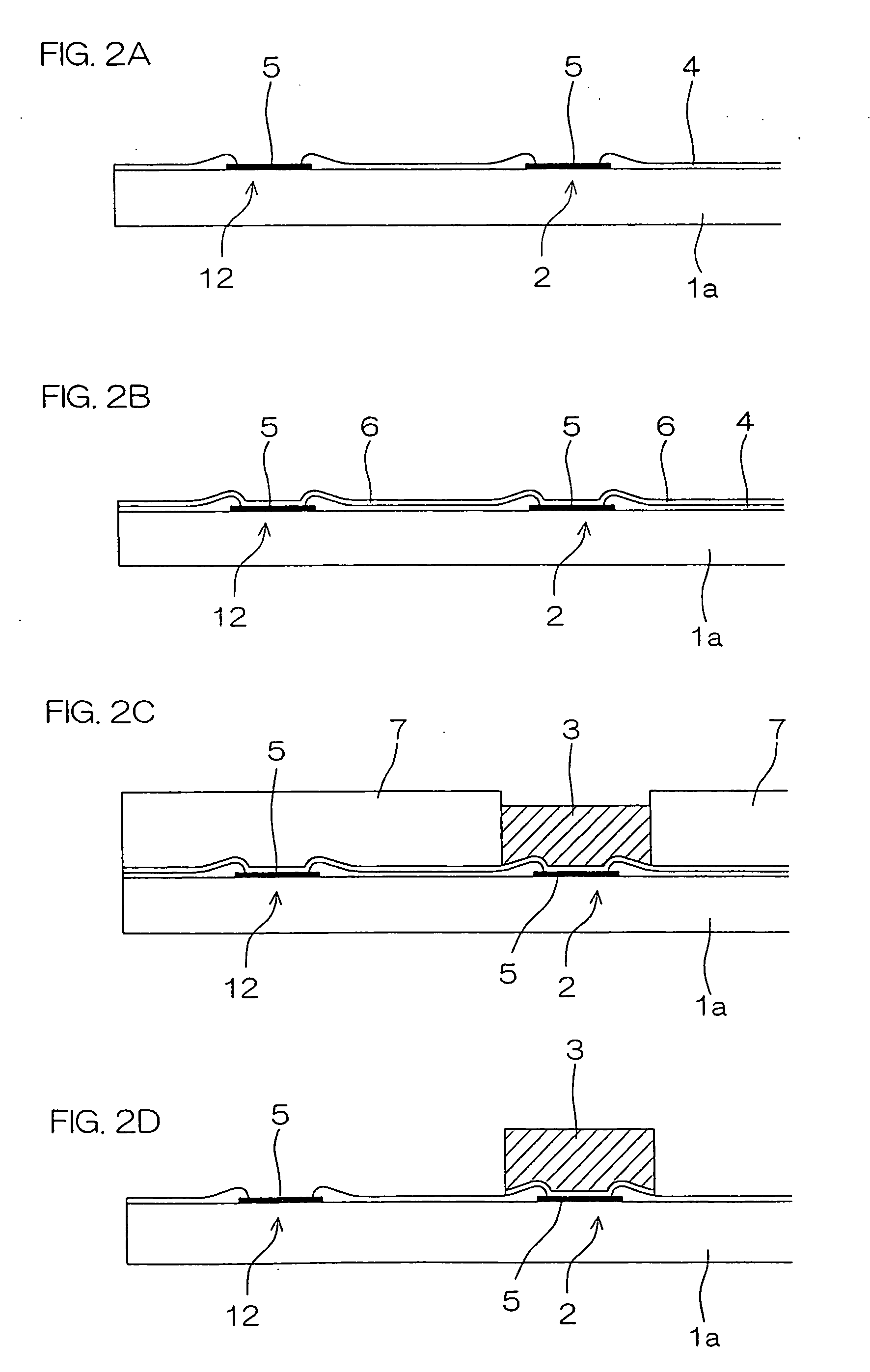

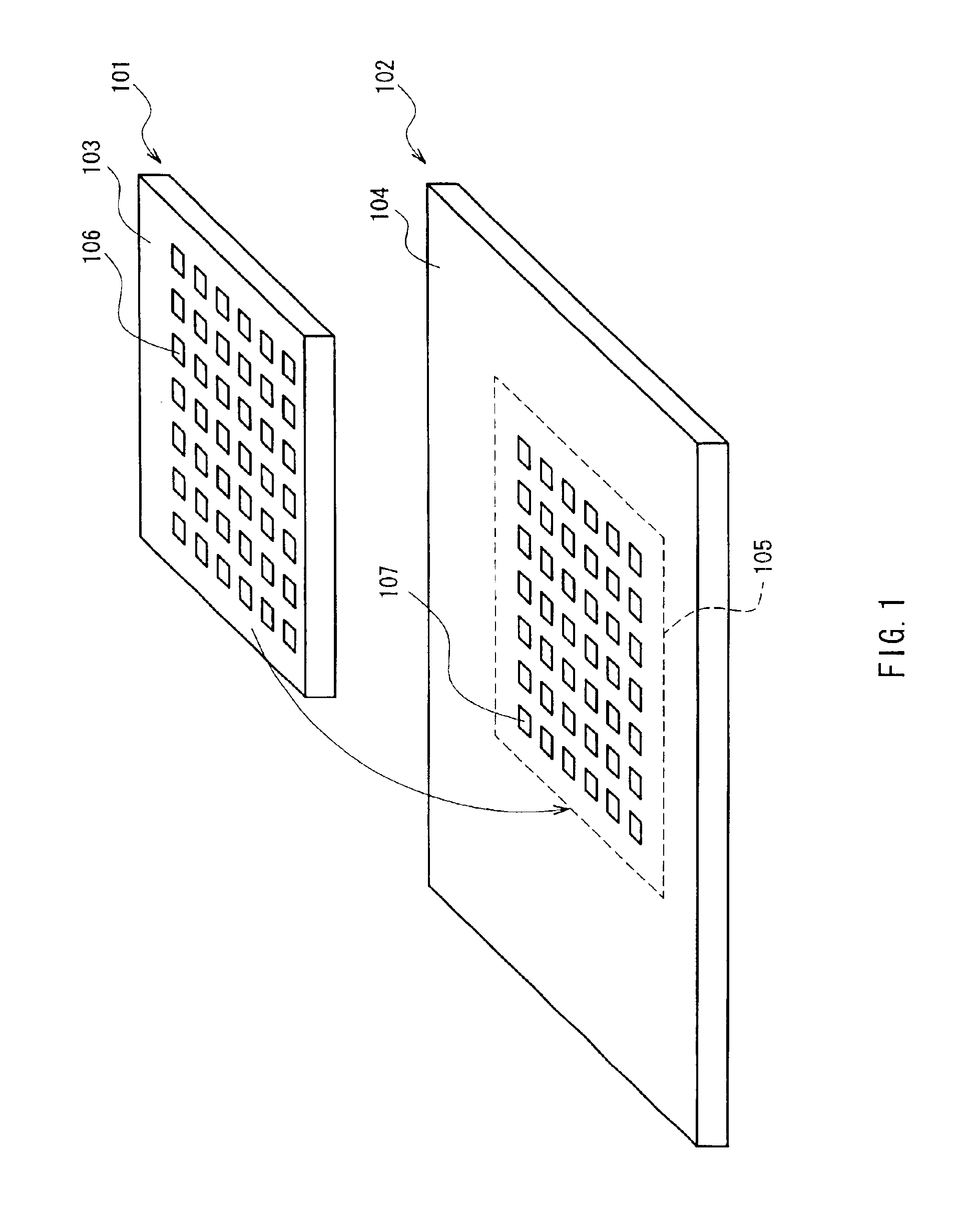

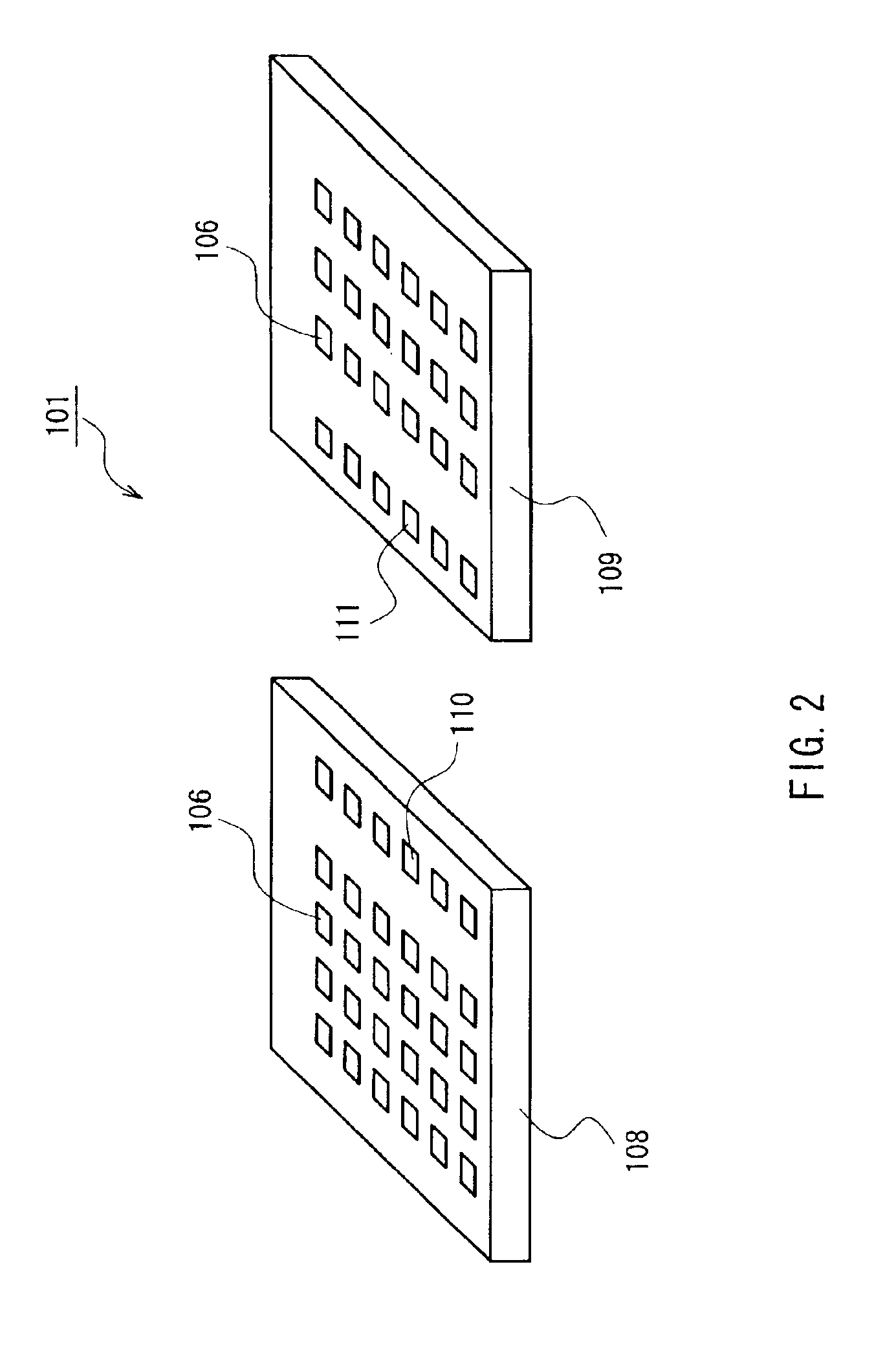

Semiconductor device of chip-on-chip structure, assembling process therefor, and semiconductor chip to be bonded to solid surface

InactiveUS20050253274A1Effective positioningImprove productivitySemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipDevice material

A semiconductor device including a first semiconductor chip, a second semiconductor chip bonded to the first semiconductor chip in a stacked relation, and a registration structure which causes the first and second semiconductor chips to be positioned with respect to each other by depression-projection engagement therebetween. The registration structure includes, for example, a registration recess provided on a surface of the first semiconductor chip, and a registration projection provided on a surface of the second semiconductor chip for engagement with the registration recess. The registration projection may be a spherical member provided on the surface of the second semiconductor chip.

Owner:ROHM CO LTD

Semiconductor device

ActiveUS20090189293A1Increase layout areaHigh capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceChIP-on-chip

A semiconductor device having a chip-on-chip structure is constituted of a first semiconductor chip and even-numbered pairs of second semiconductor chips, all of which are laminated together on the surface of an interposer. The first semiconductor chip controls each pair of the second semiconductor chips so as to activate one second semiconductor chip while inactivating another second semiconductor chip. The second semiconductor chips are paired together in such a way that through-vias and electrodes thereof are positioned opposite to each other via bumps. Since drive voltage electrodes supplied with a drive voltage (VDD) and reference potential electrodes supplied with a reference potential (VSS) are mutually connected together between the paired second semiconductor chips, it is possible to increase the overall electrostatic capacitance of each second semiconductor chip so as to substantially reduce feed noise without increasing the overall layout area of the semiconductor device.

Owner:LONGITUDE LICENSING LTD

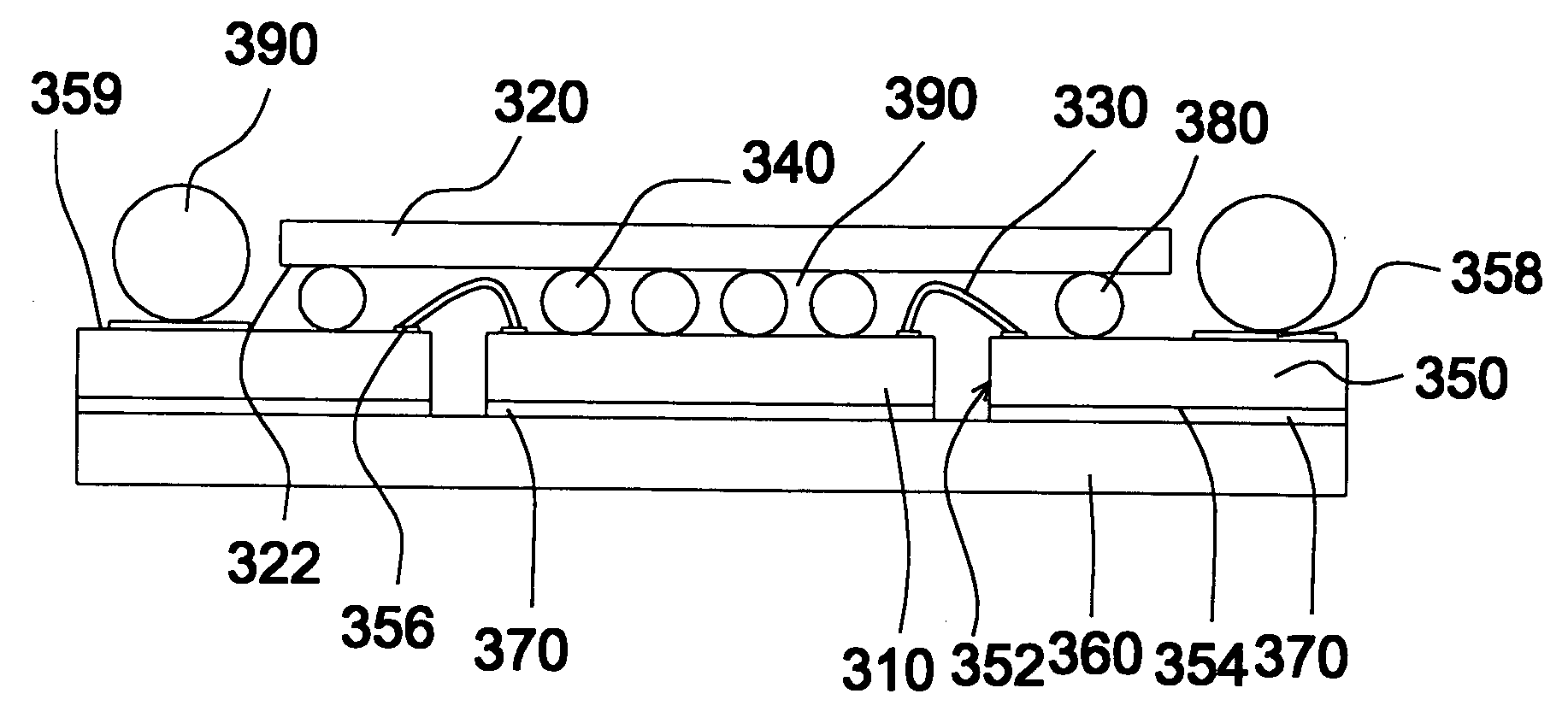

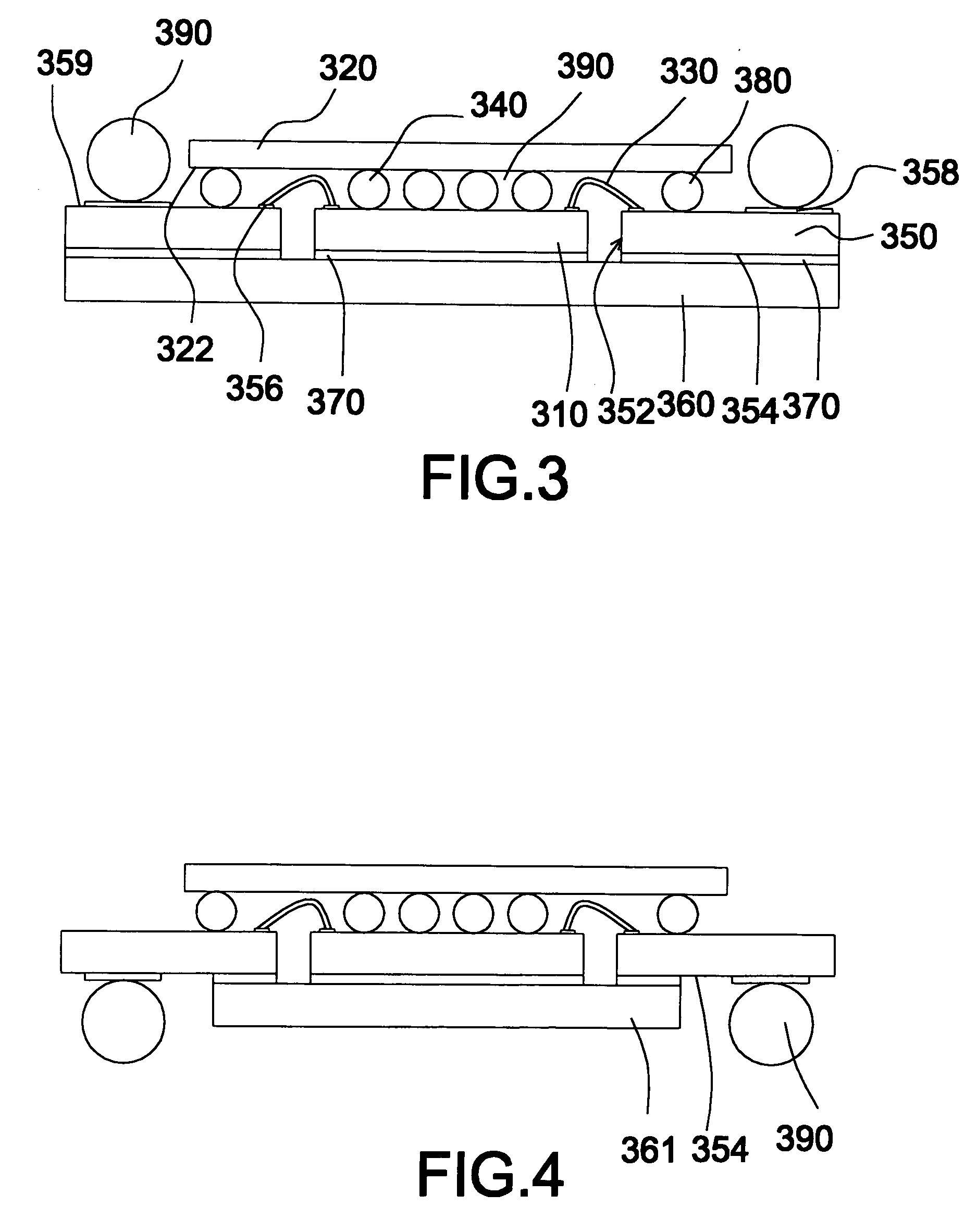

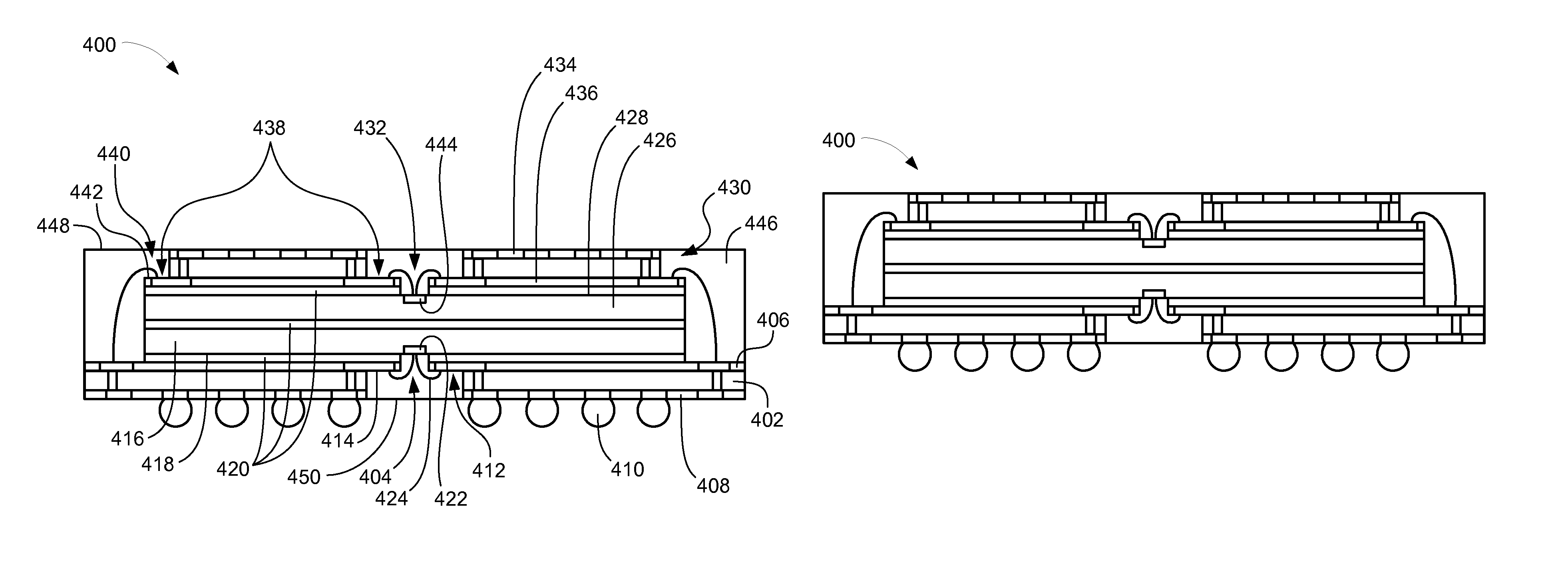

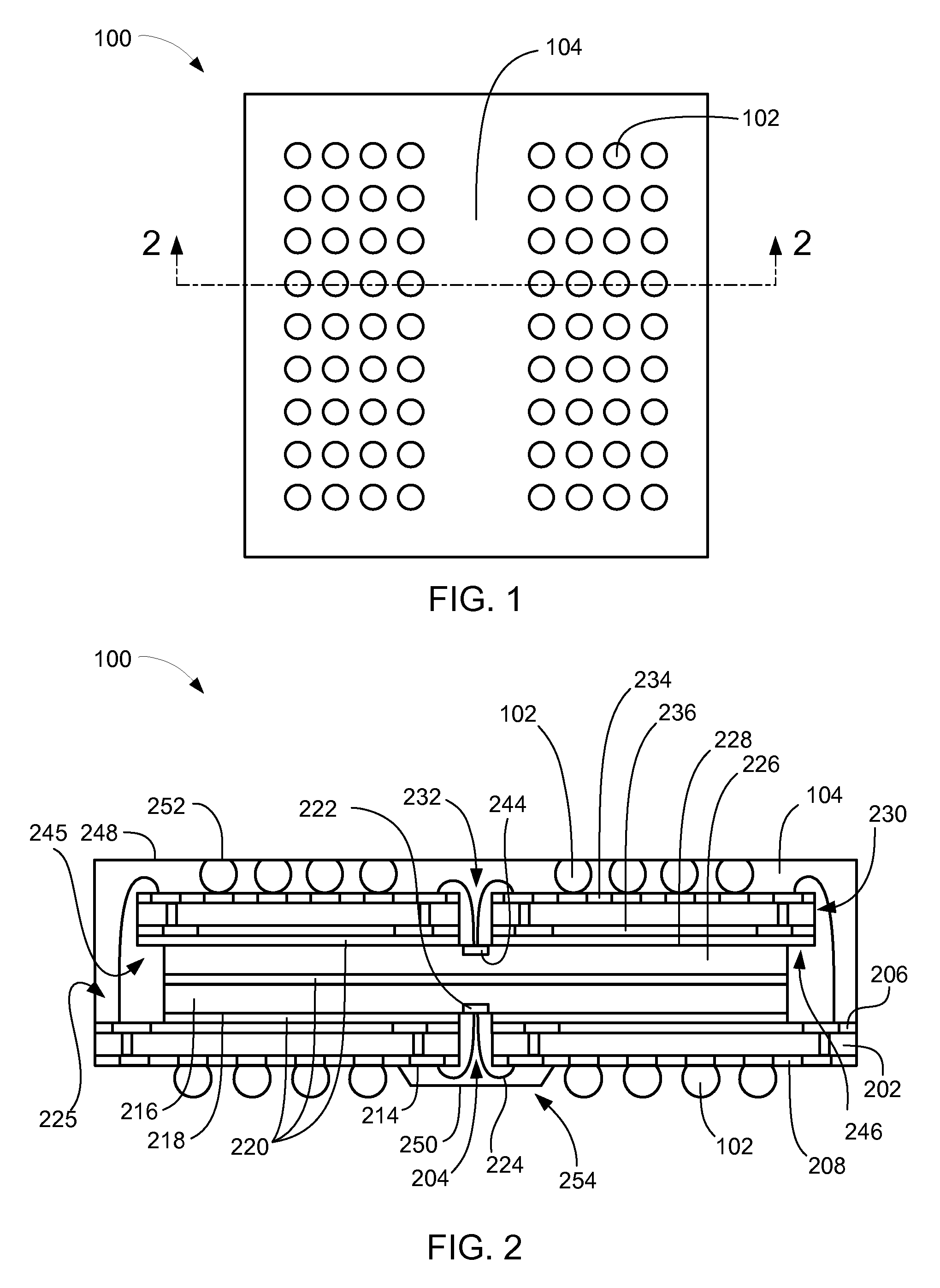

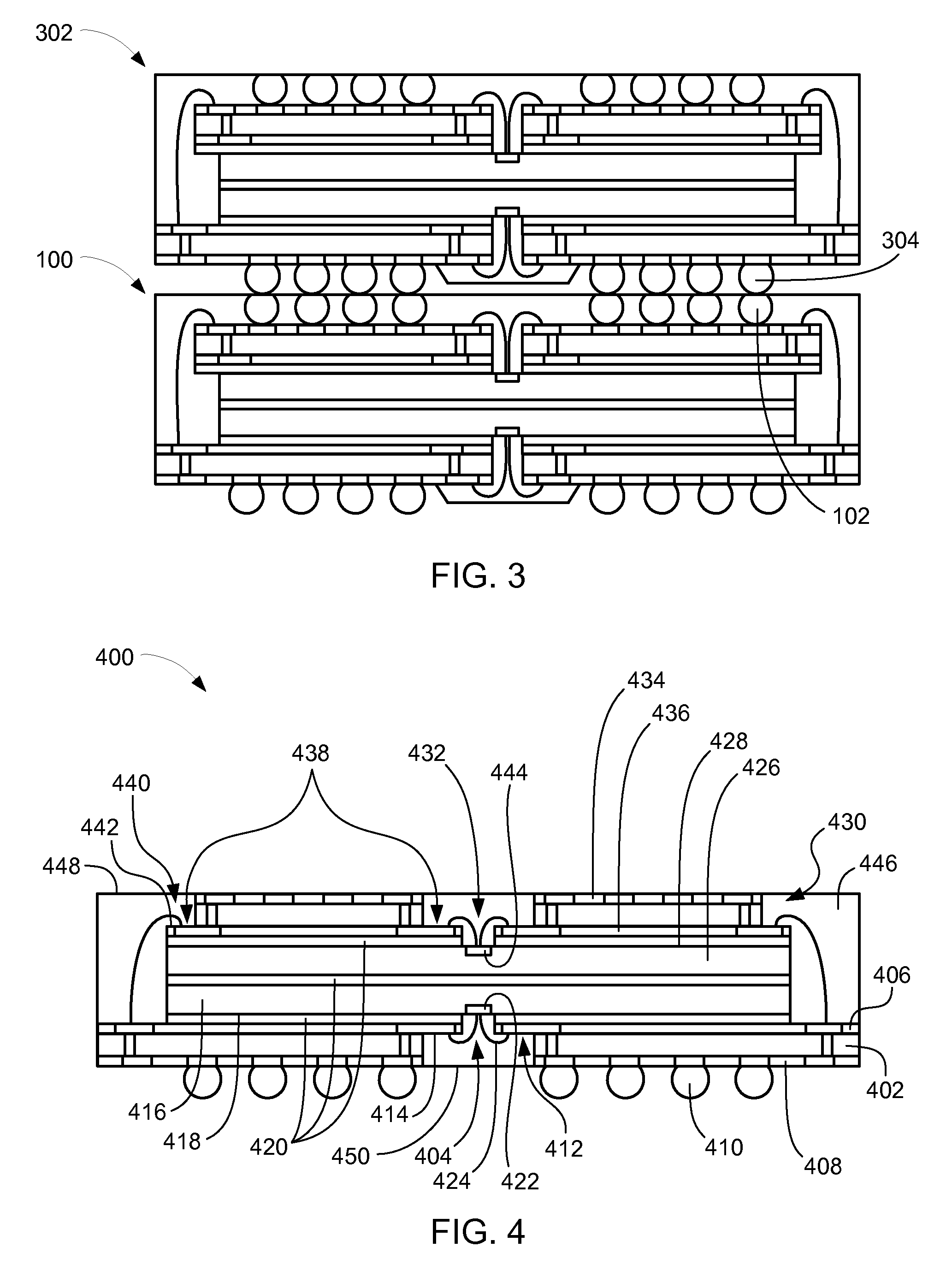

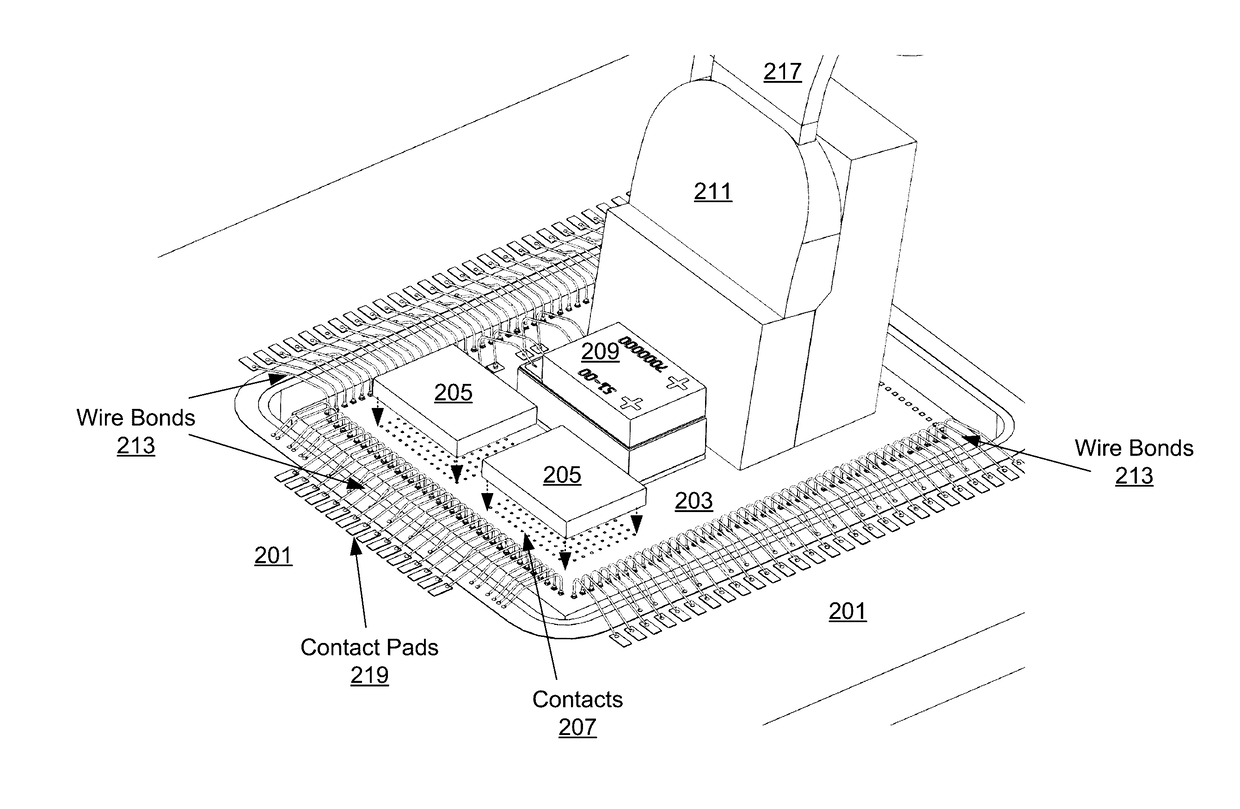

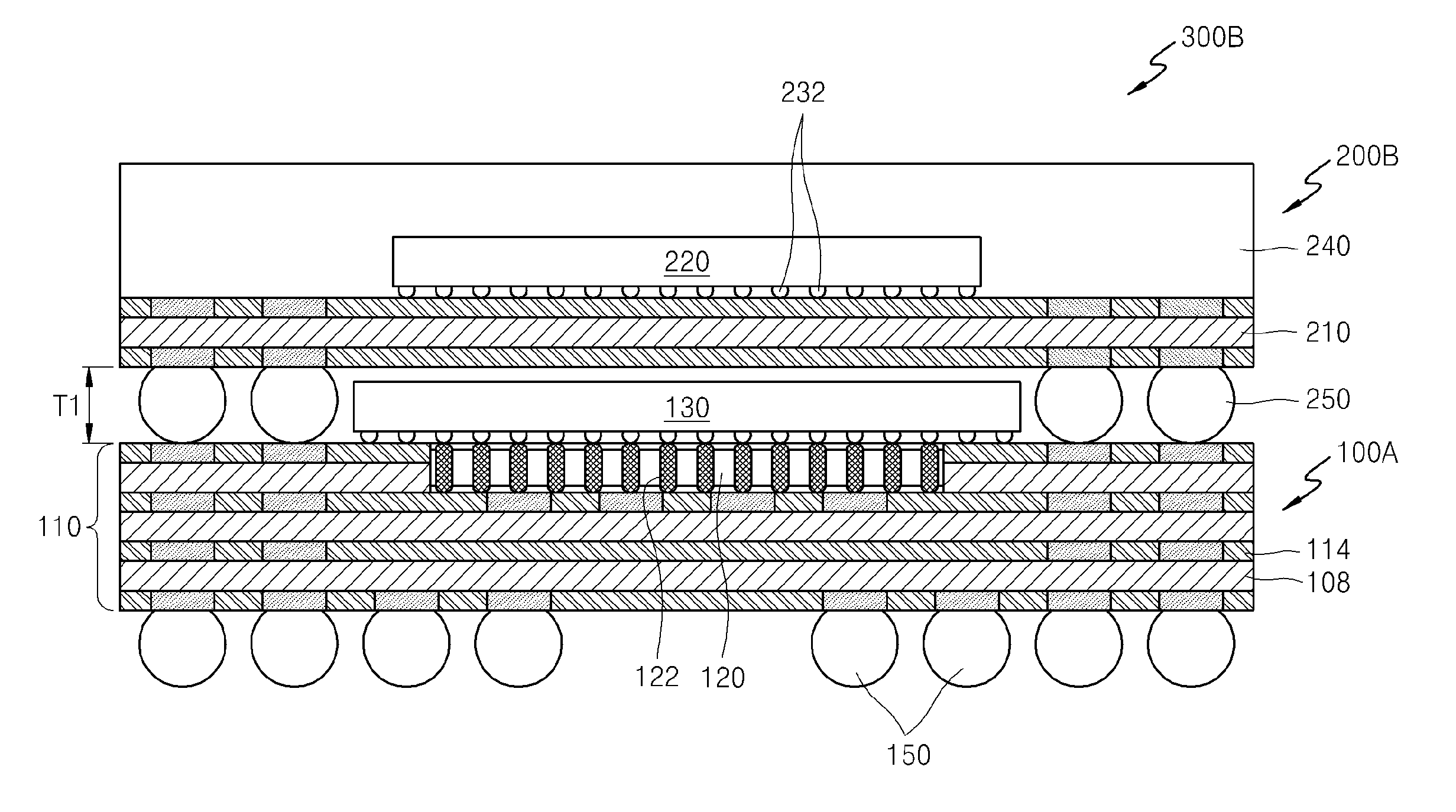

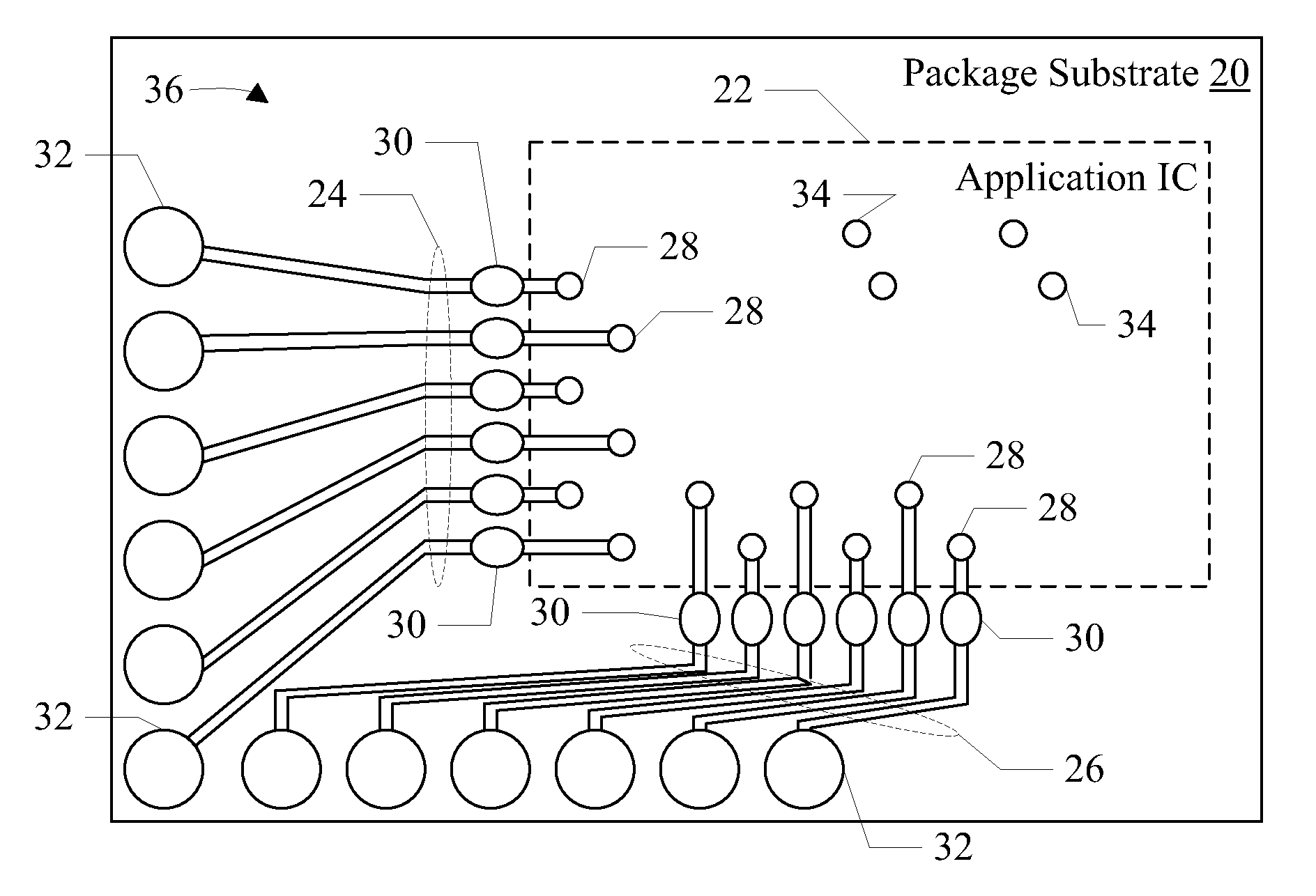

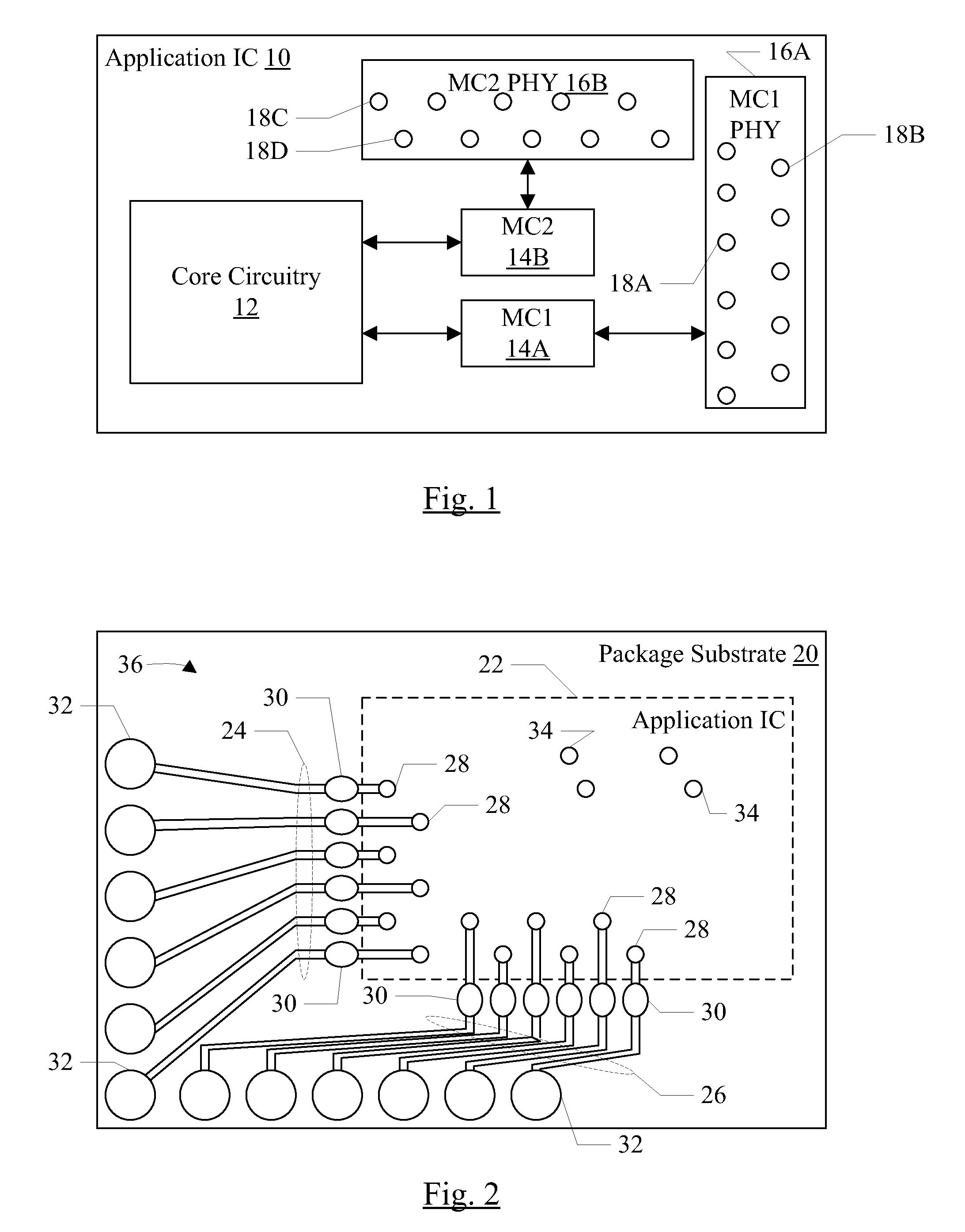

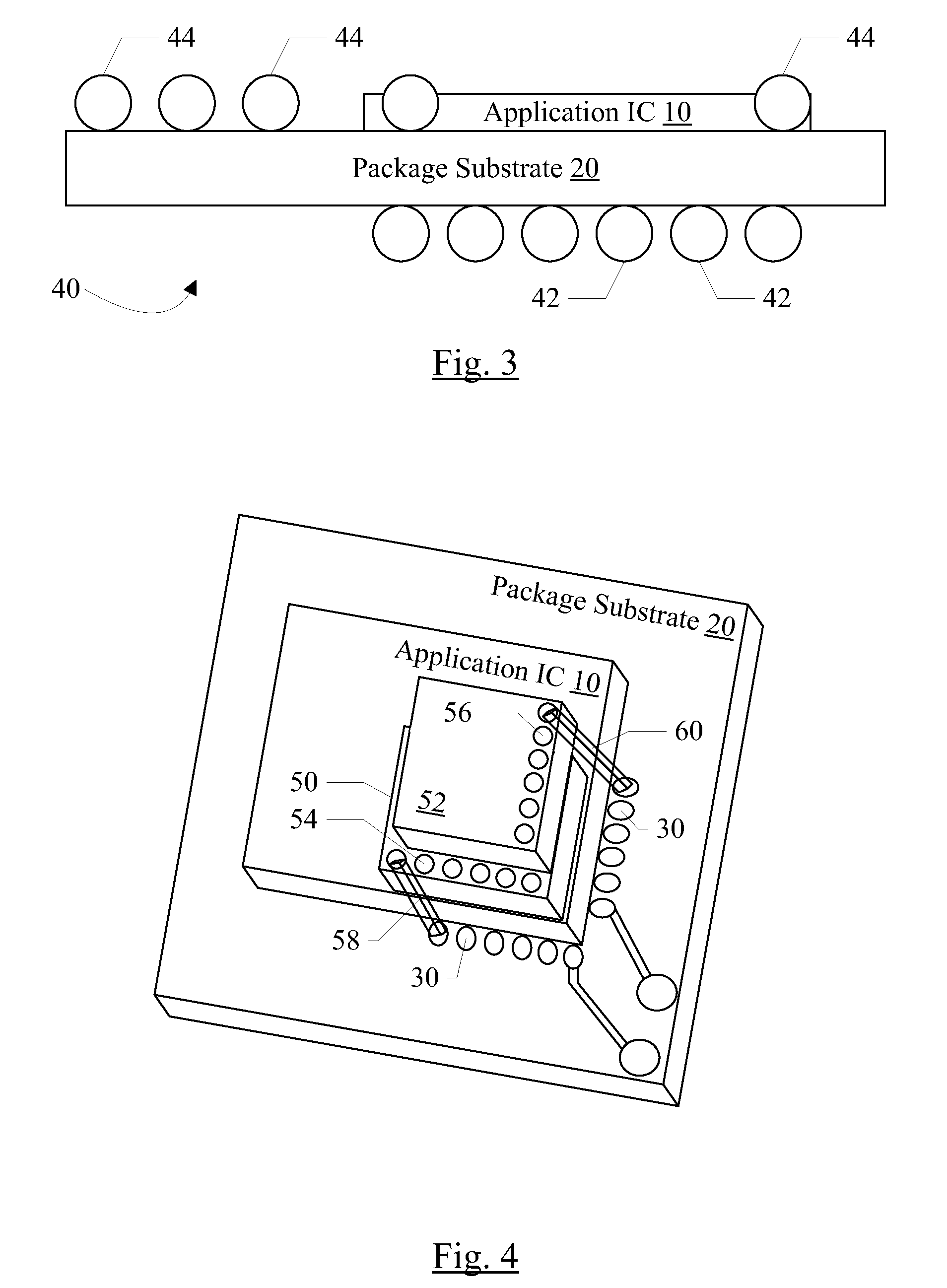

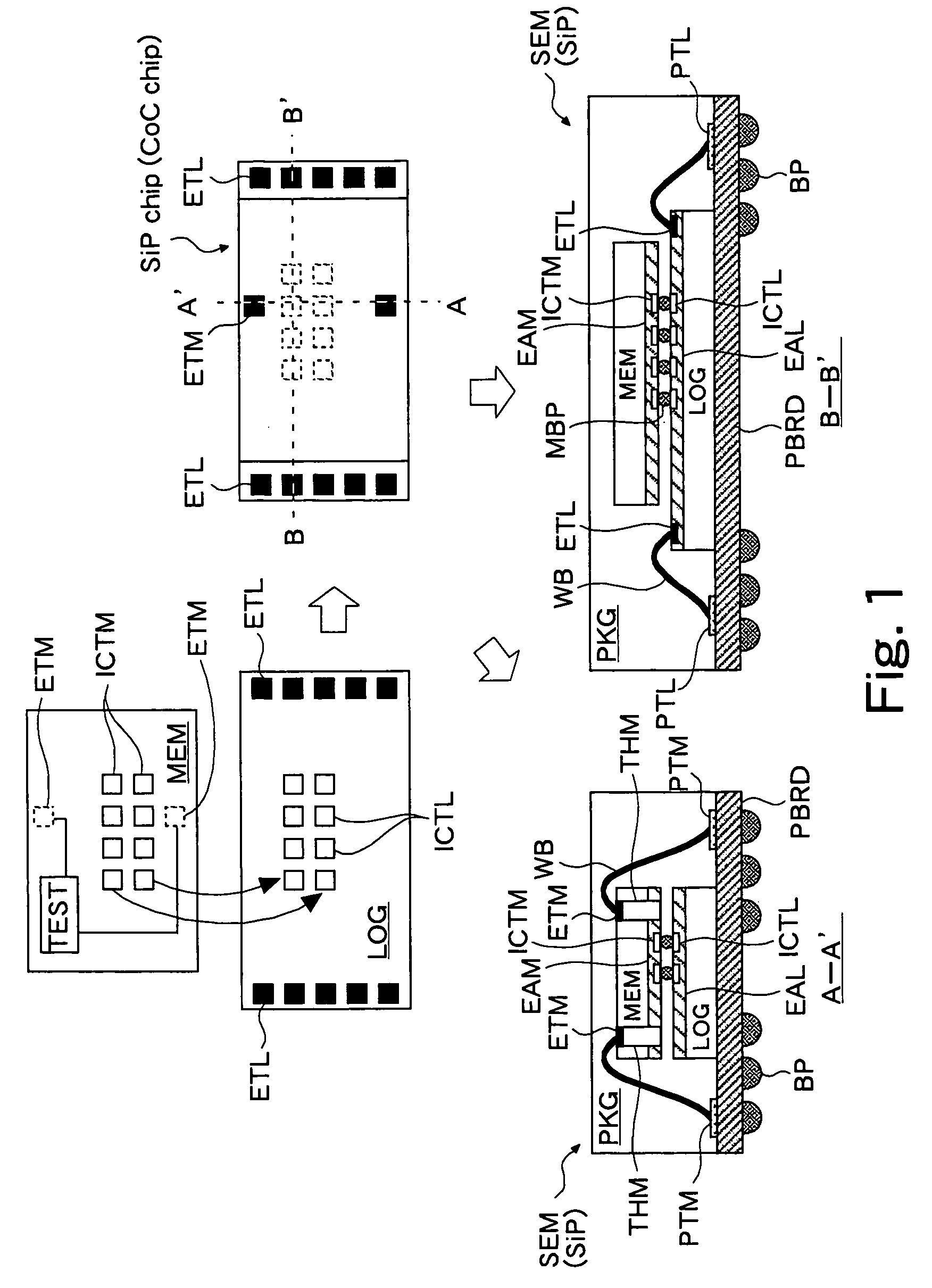

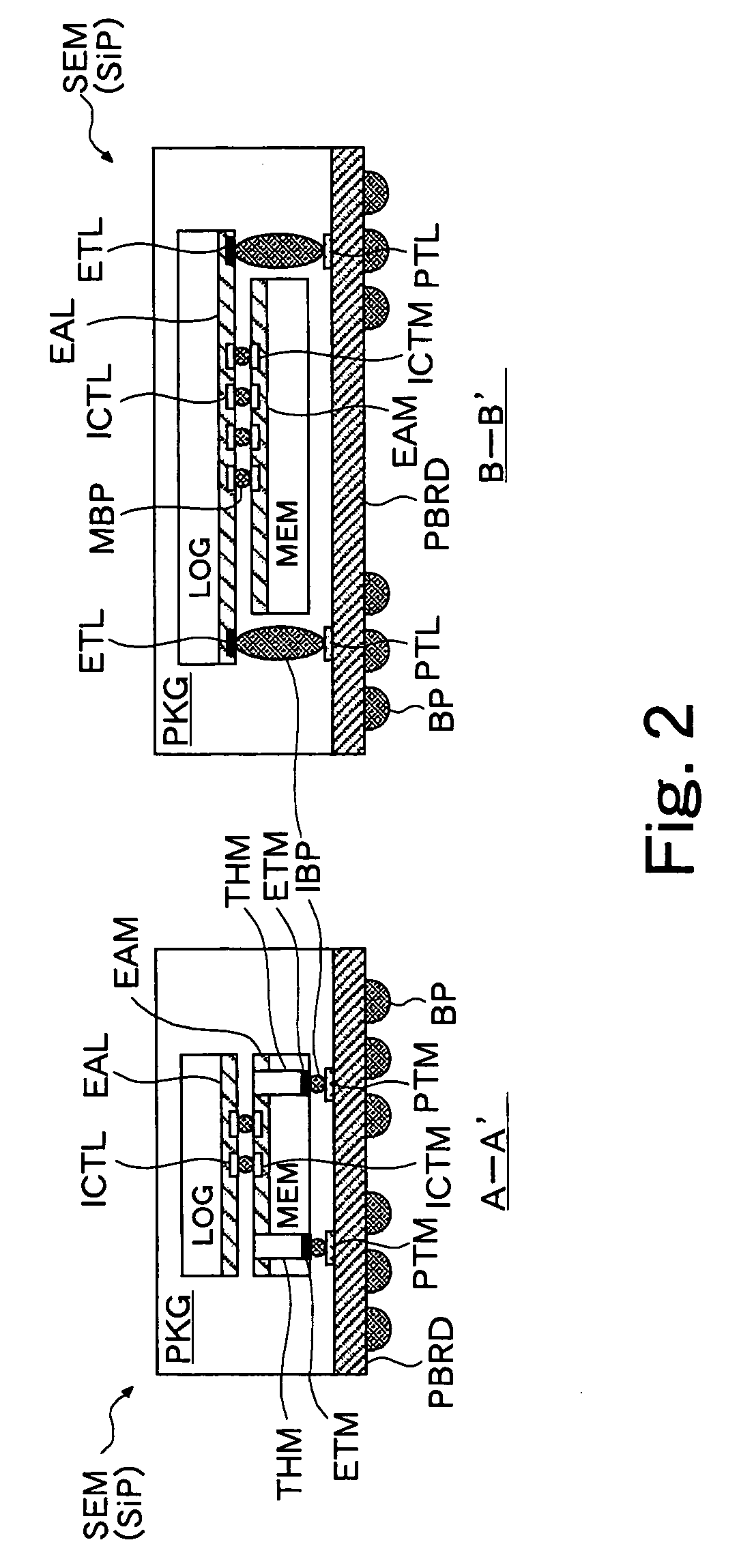

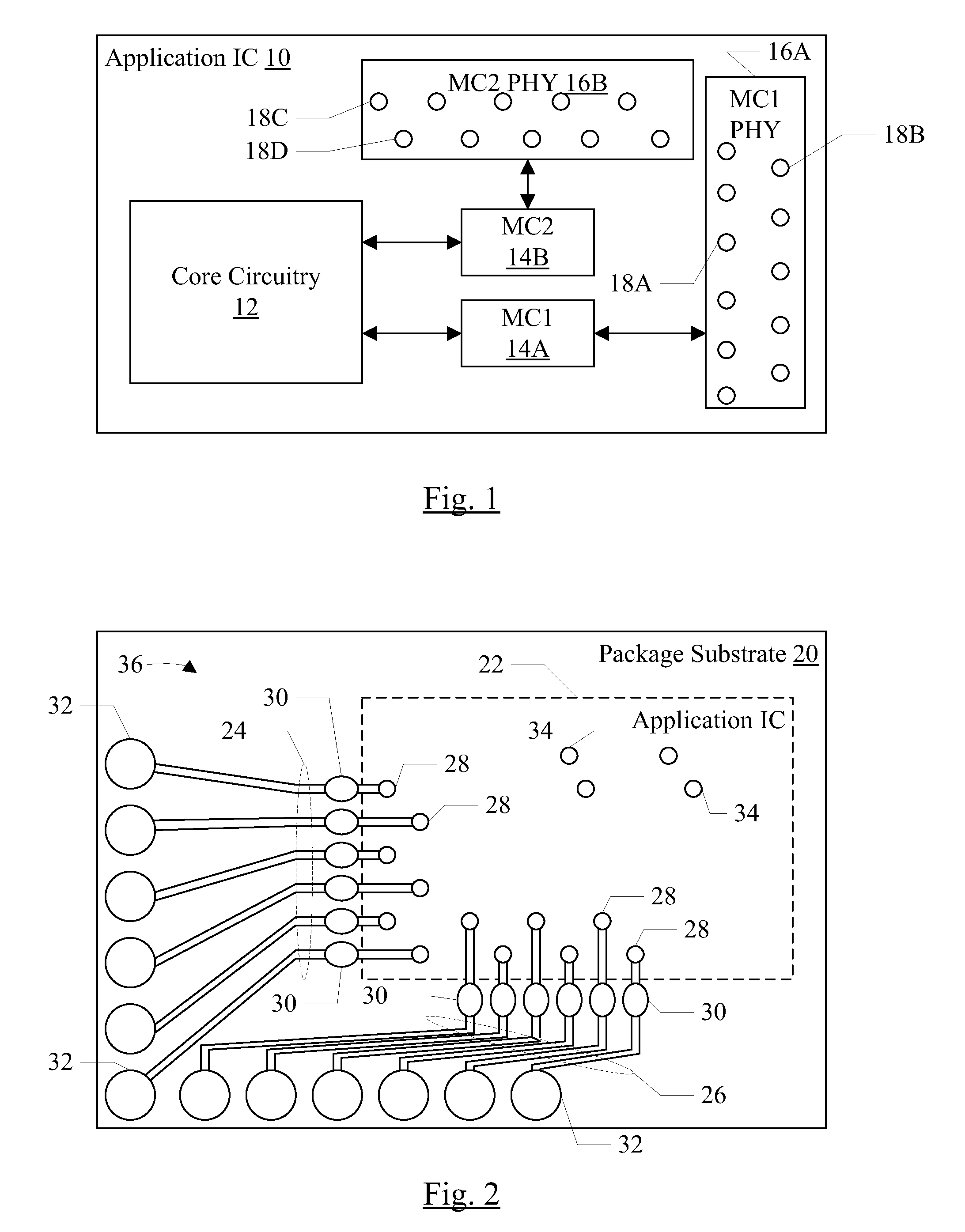

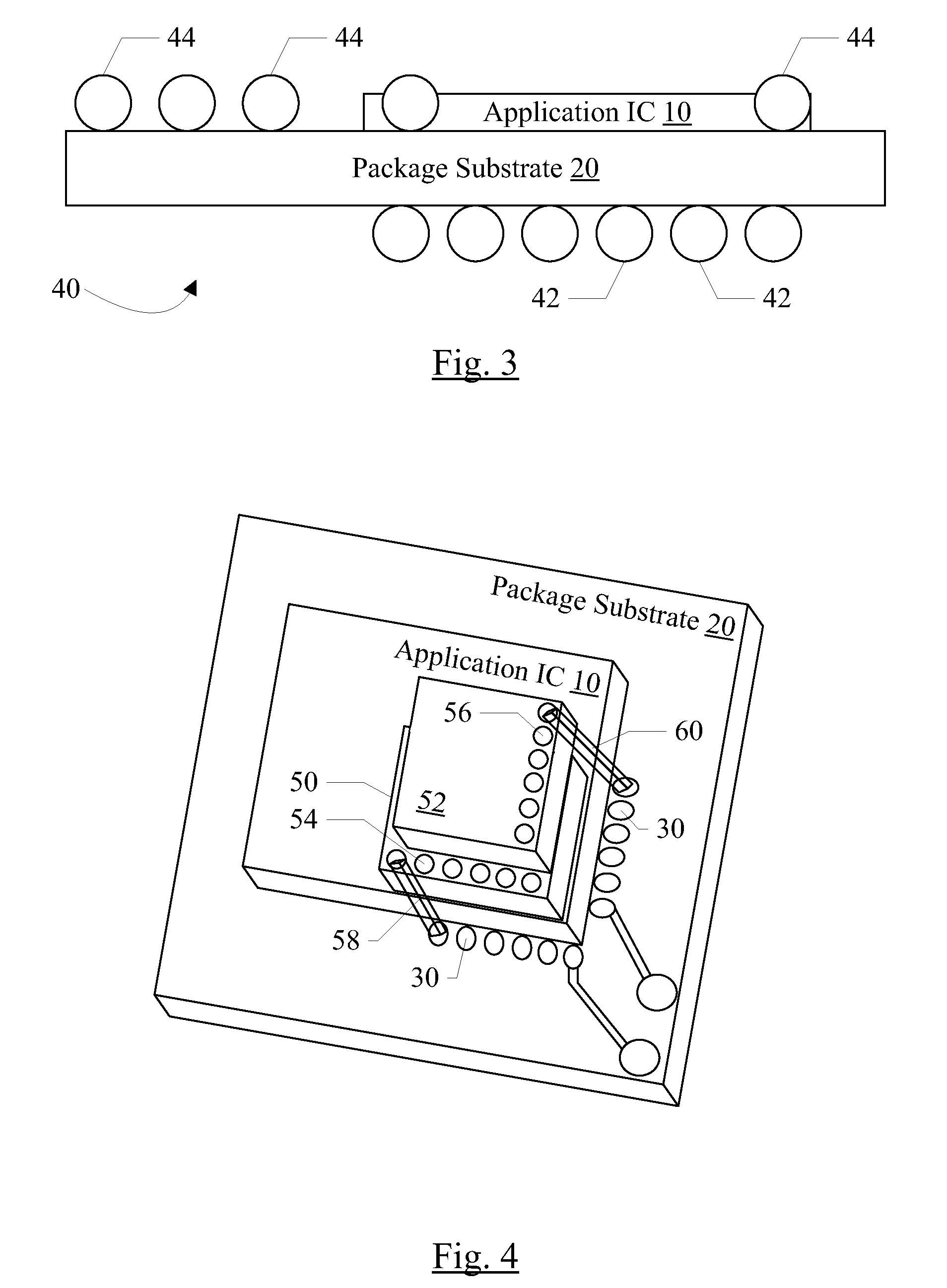

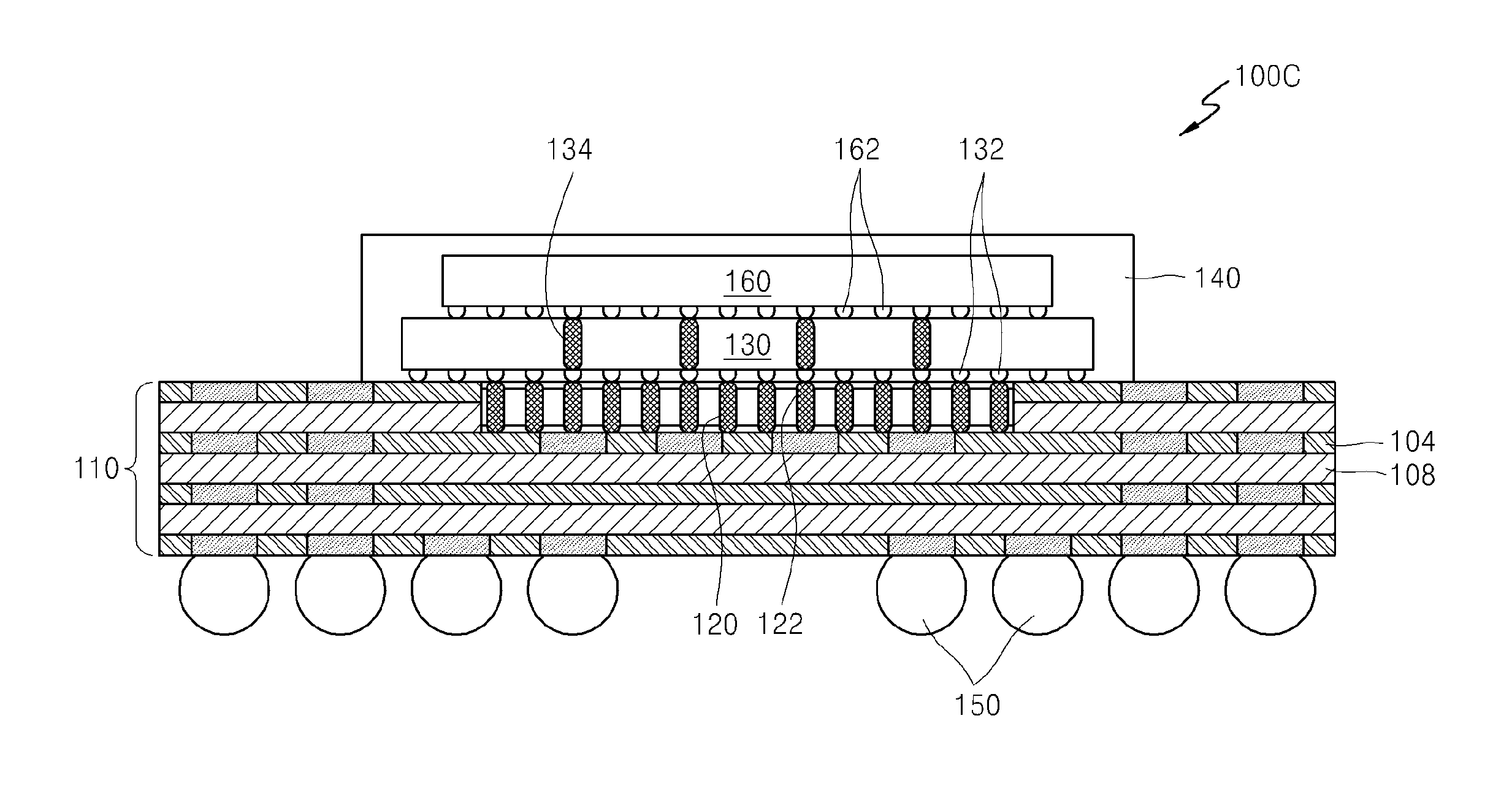

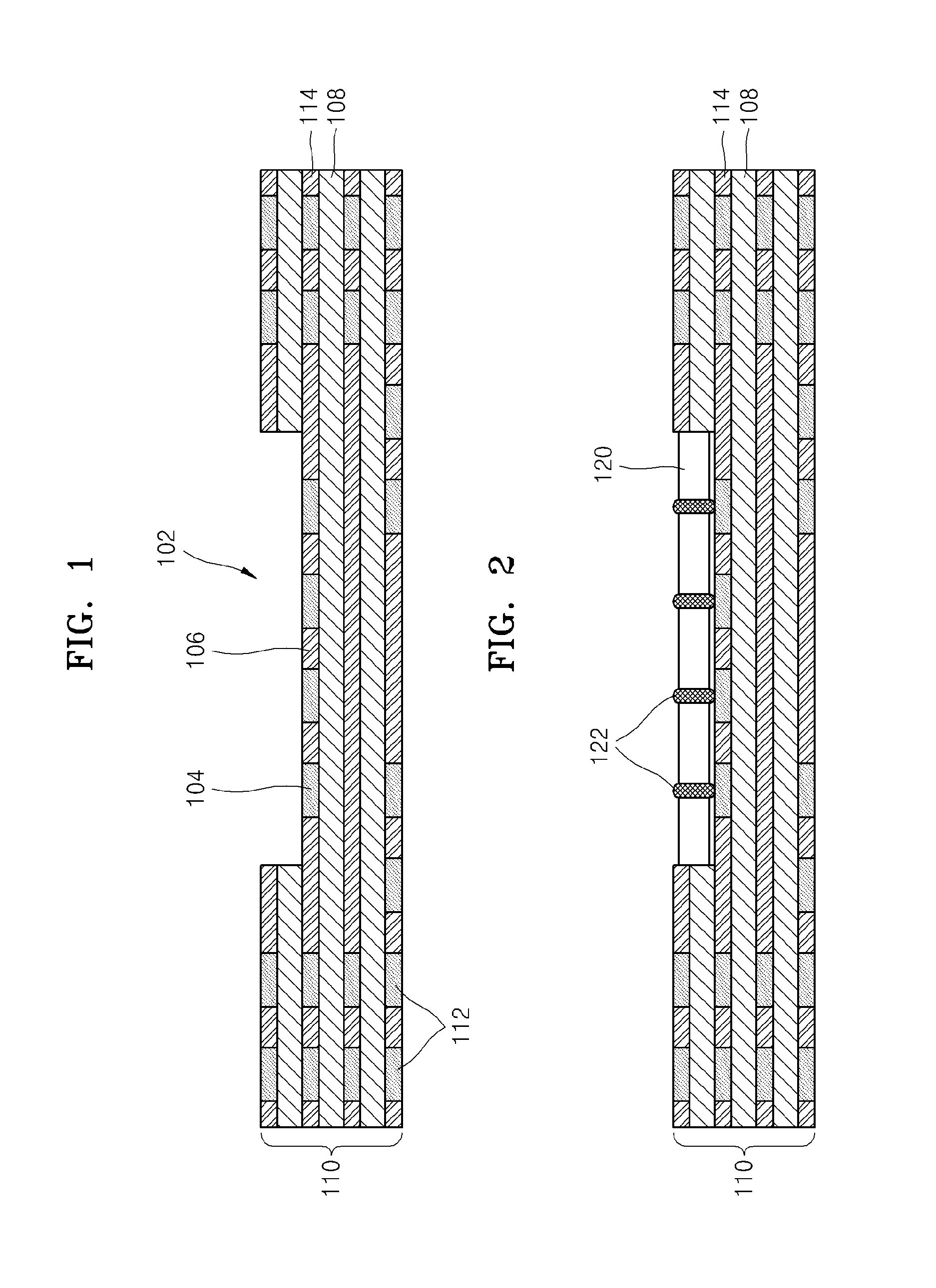

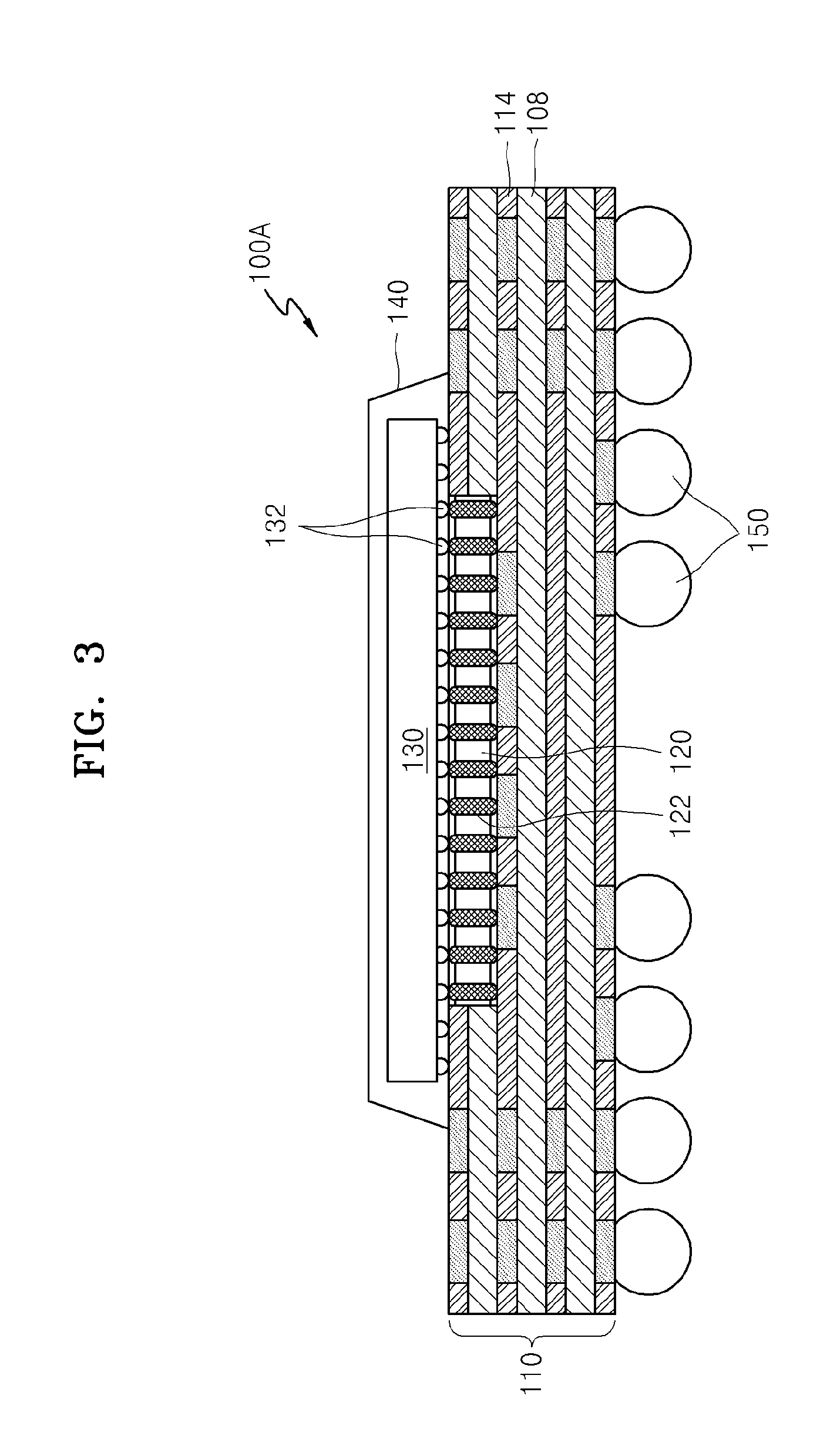

Flexible Packaging for Chip-on-Chip and Package-on-Package Technologies

ActiveUS20100230825A1Small sizeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical conductorChIP-on-chip

In one embodiment, a packaging solution for an application integrated circuit (IC) and one or more other ICs is provided. The packaging solution may support both chip-on-chip packaging of the application IC (in flip-chip connection to a package substrate) and other ICs (in non-flip chip orientation), and package-on-package packaging of the application IC and the other ICs. The package substrate may include a first set of pads proximate to the application IC to support chip-on-chip connection to the other ICs. The pads may be connected to conductors that extend underneath the application IC, to connect to the application IC. A second set of pads may be connected to package pins for package-on-package solutions. If the chip-on-chip solution proves reliable, support for the package-on-package solution may be eliminated and the package substrate may be reduced in size.

Owner:APPLE INC

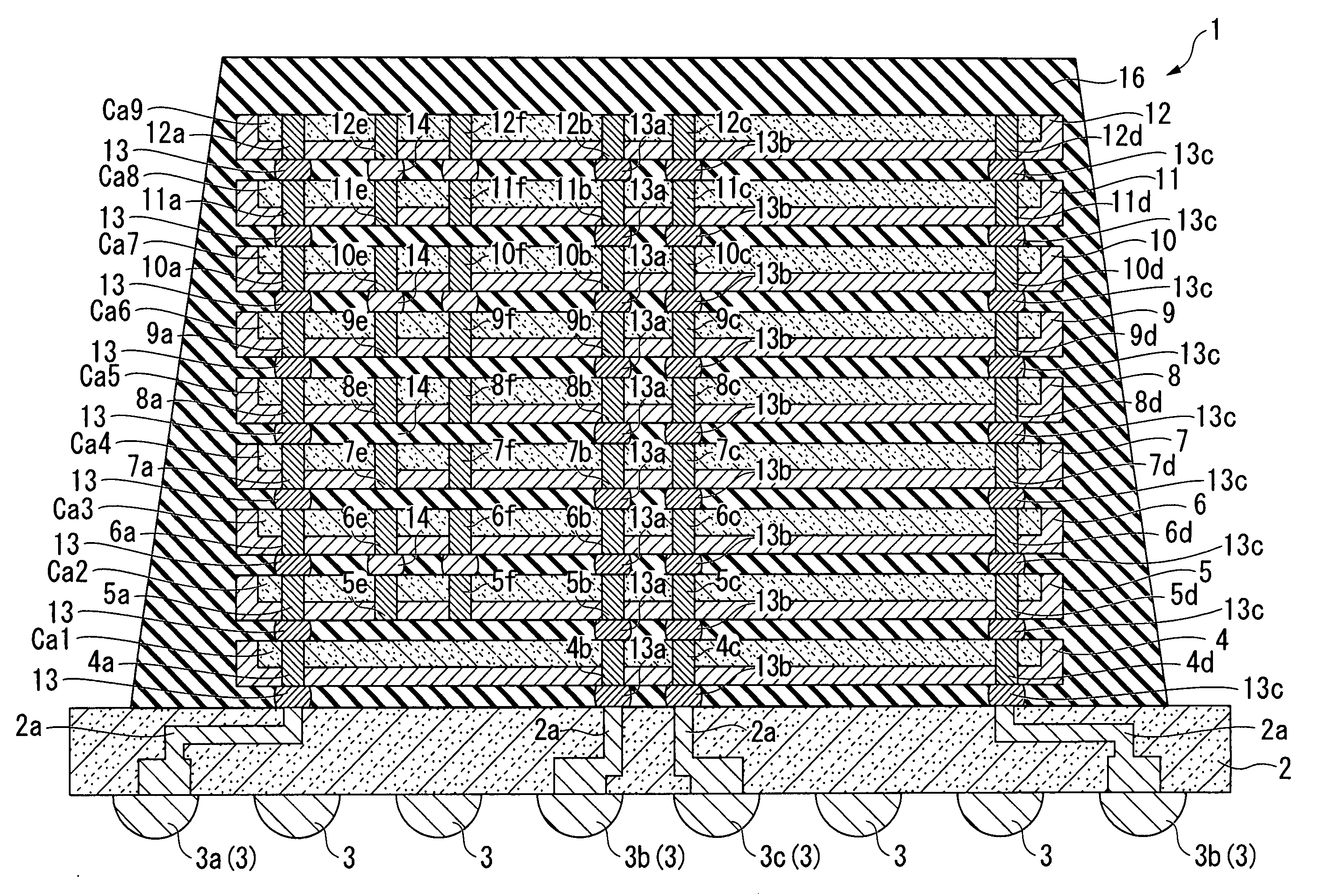

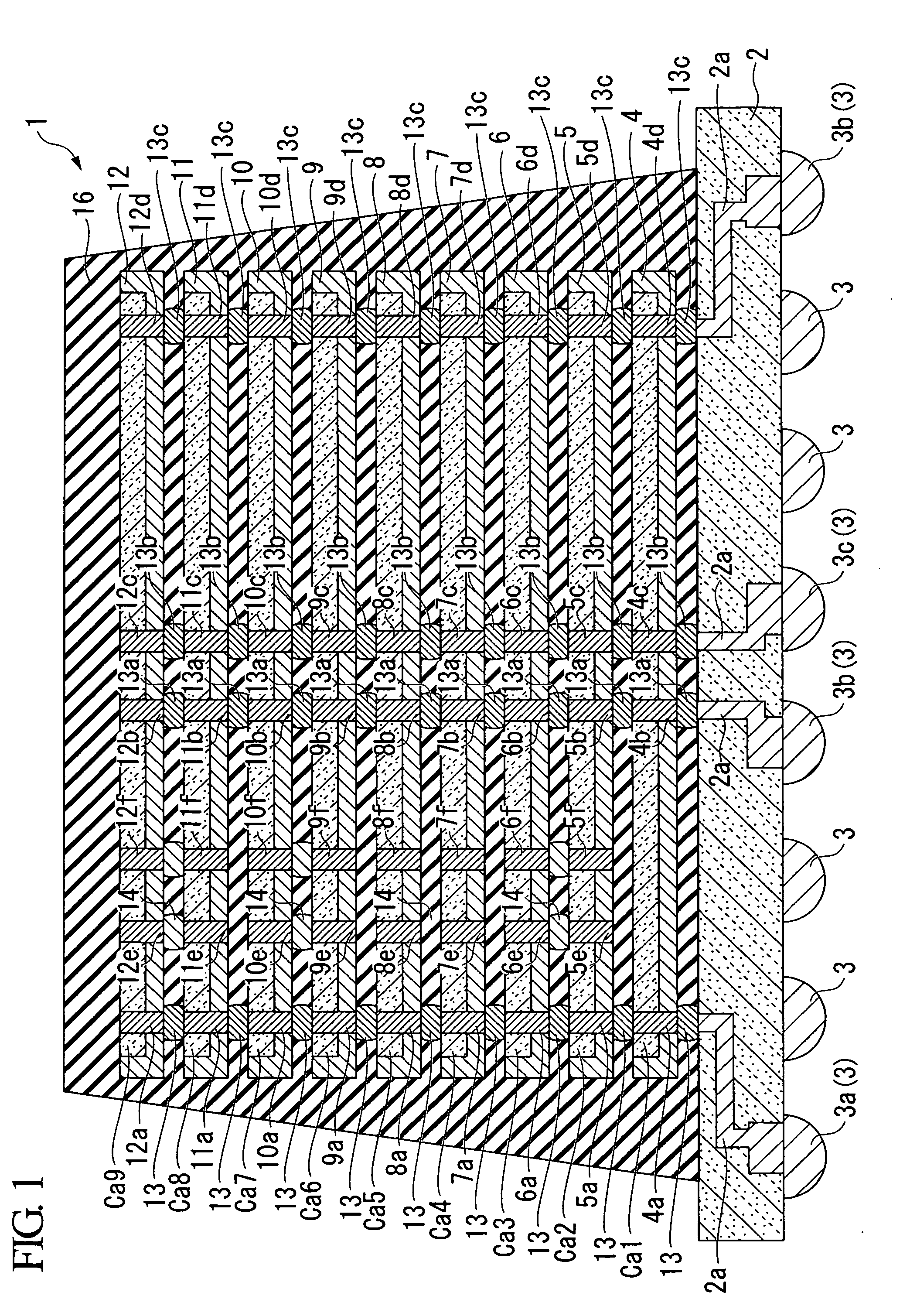

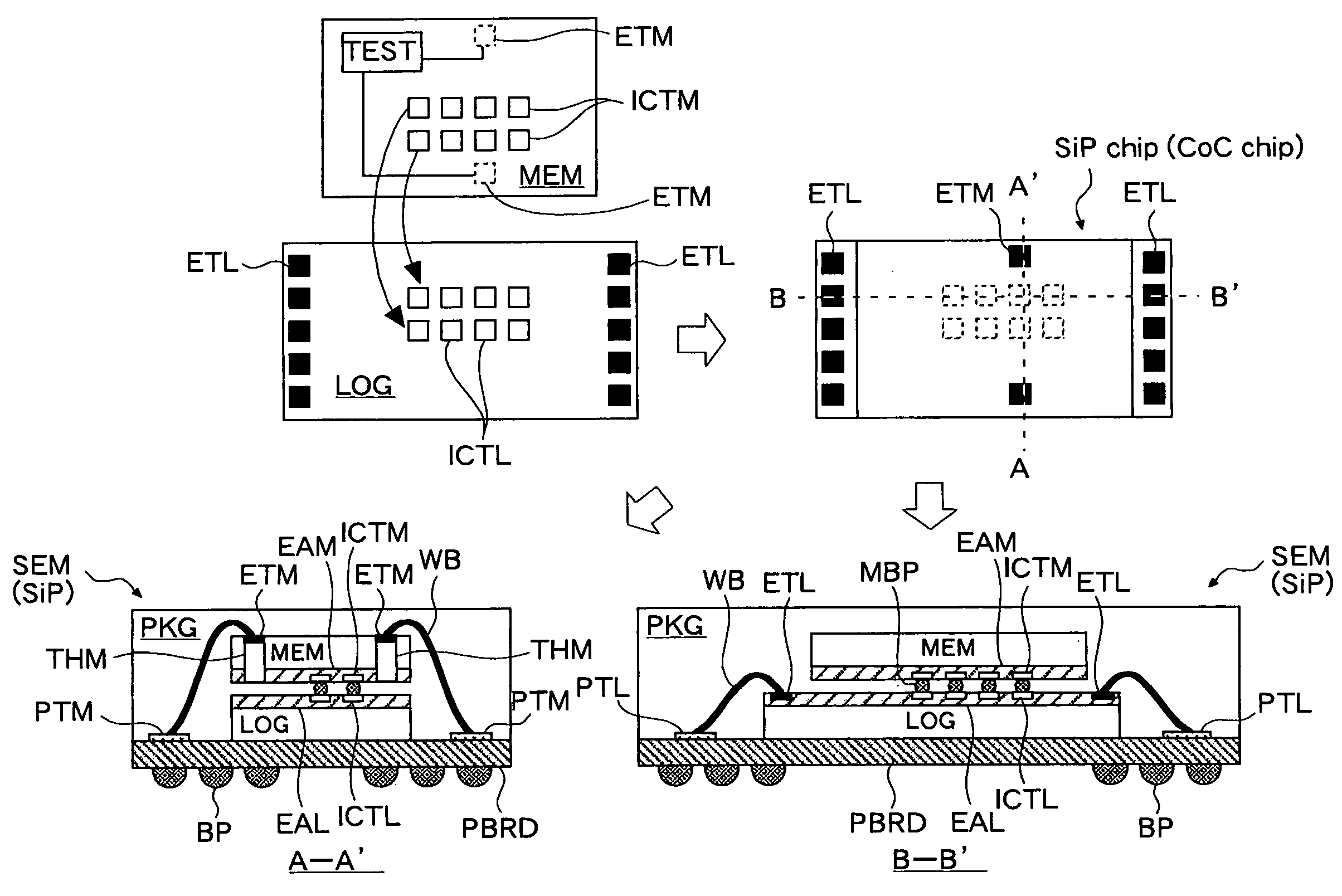

Semiconductor device comprising chip on chip structure

ActiveUS7741723B2Improve operating profitSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsChIP-on-chipSemiconductor chip

In a semiconductor device constituted of stacked semiconductor chips, in order to independently test each of the chips, a second chip is disposed to face a first chip, with a second interconnection terminal thereof connected to a first interconnection terminal of the first chip. First and second external terminals of the first and second chips are formed on surfaces of the first and second chips, the surface being on a same side of the first and second chips. Therefore, even after the first chip and the second chip are pasted together, it is possible to test the first chip and the second chip while operating them independently. Further, since test probes or the like can be brought into contact with the external terminals of the first chip and the second chip from the same side, it is possible to simultaneously test the first chip and the second chip.

Owner:SOCIONEXT INC

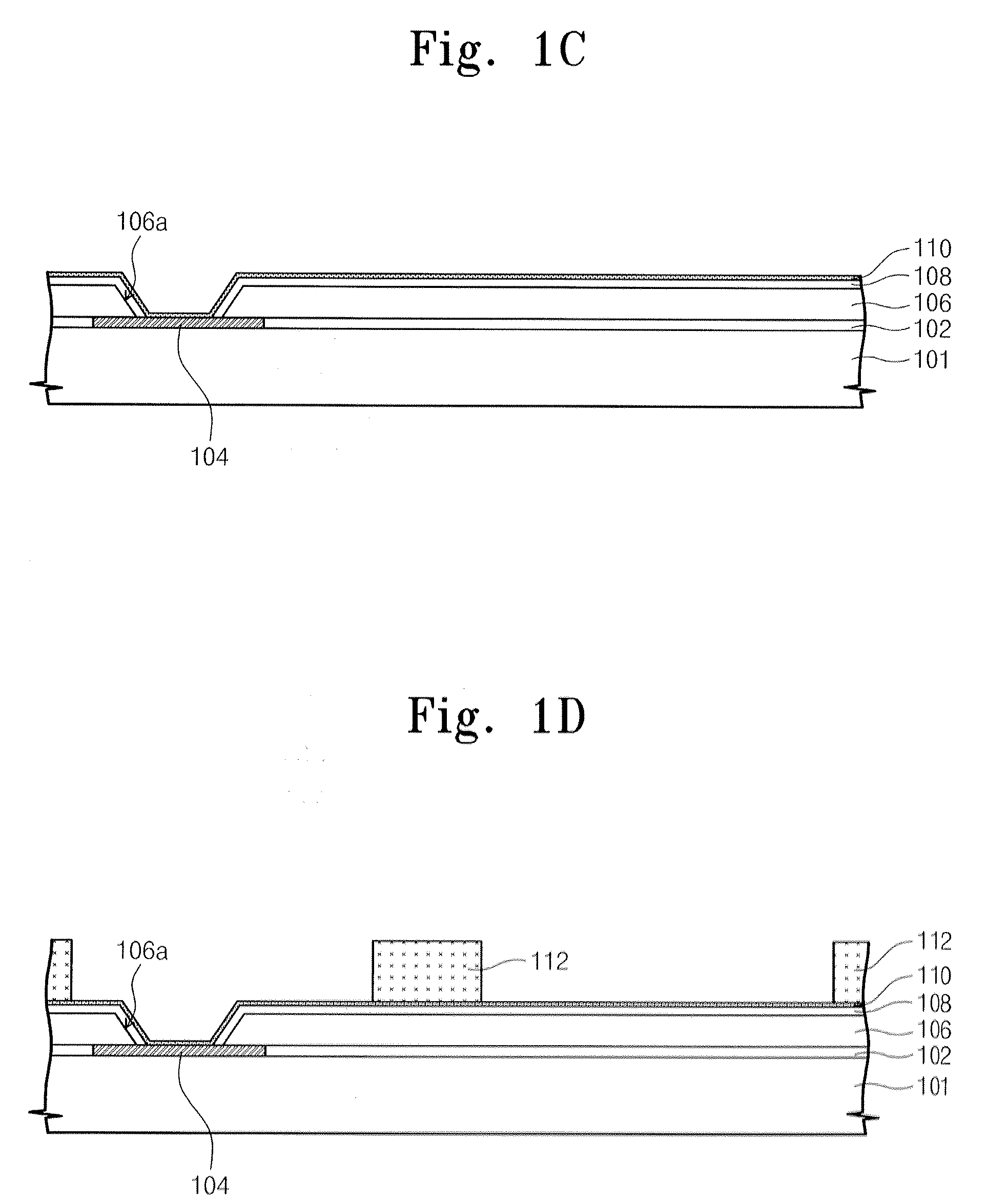

Organic light emitting display device and reworking method thereof

ActiveUS20130270528A1Eliminate the problemSemiconductor/solid-state device detailsPrinted circuit aspectsChip on filmChIP-on-chip

An organic light emitting display device is disclosed. The organic light emitting display device includes: an organic light emitting display panel defined into a display area for displaying an image and a non-display area surrounding the display area; a chip-on-film loaded with a driver IC chip, which is configured to drive the organic light emitting display panel, and attached to a pad portion which is formed on the non-display area of the organic light emitting display panel; and a printed circuit board configured to apply signals to the driver IC chip and attached to one edge of the chip-on-film, wherein the organic light emitting display panel includes a dummy pad portion which is formed on the non-display area in the same configuration as the pad portion and in opposition to the pad portion.

Owner:LG DISPLAY CO LTD

Flexible packaging for chip-on-chip and package-on-package technologies

ActiveUS8097956B2Small sizeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical conductorChIP-on-chip

In one embodiment, a packaging solution for an application integrated circuit (IC) and one or more other ICs is provided. The packaging solution may support both chip-on-chip packaging of the application IC (in flip-chip connection to a package substrate) and other ICs (in non-flip chip orientation), and package-on-package packaging of the application IC and the other ICs. The package substrate may include a first set of pads proximate to the application IC to support chip-on-chip connection to the other ICs. The pads may be connected to conductors that extend underneath the application IC, to connect to the application IC. A second set of pads may be connected to package pins for package-on-package solutions. If the chip-on-chip solution proves reliable, support for the package-on-package solution may be eliminated and the package substrate may be reduced in size.

Owner:APPLE INC

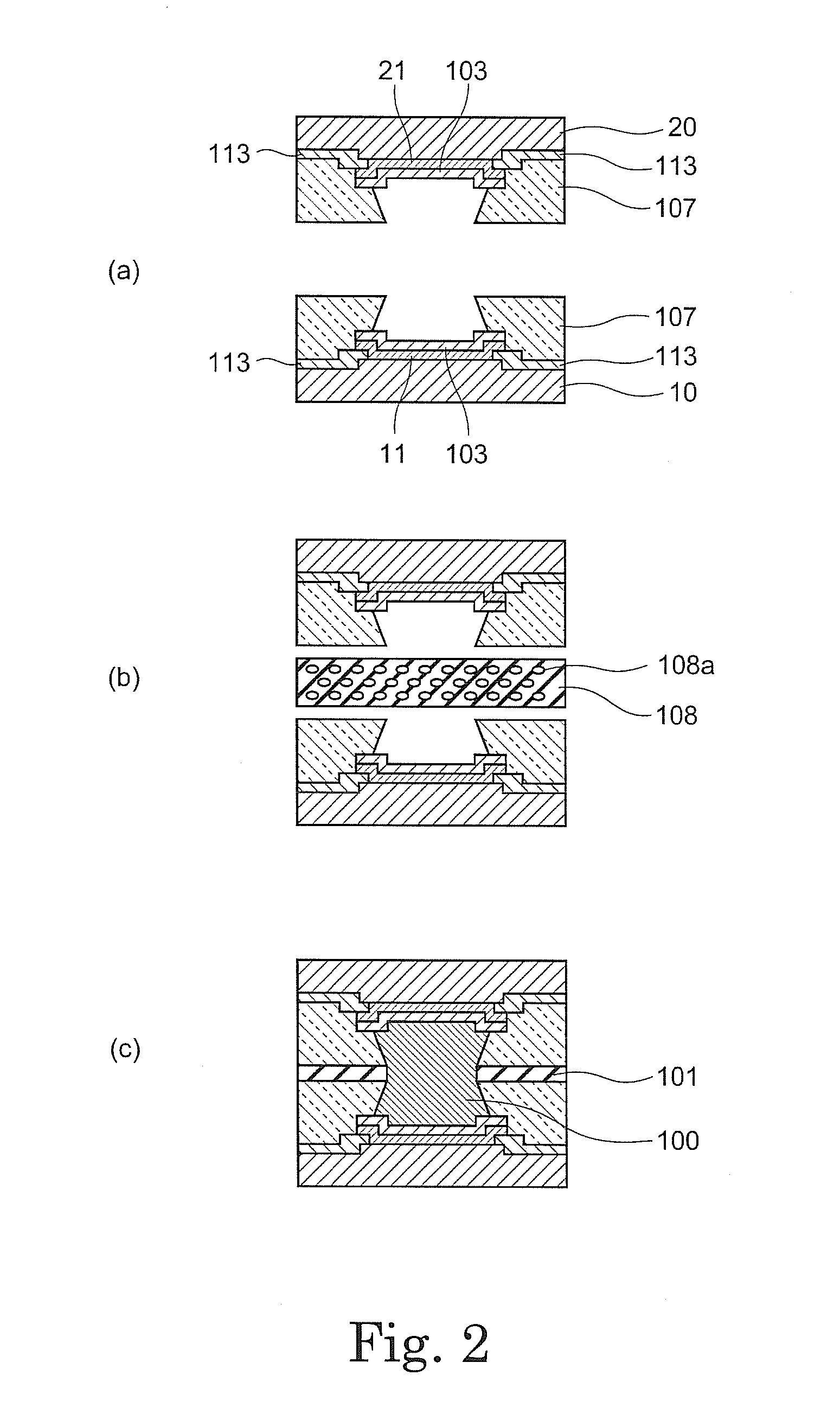

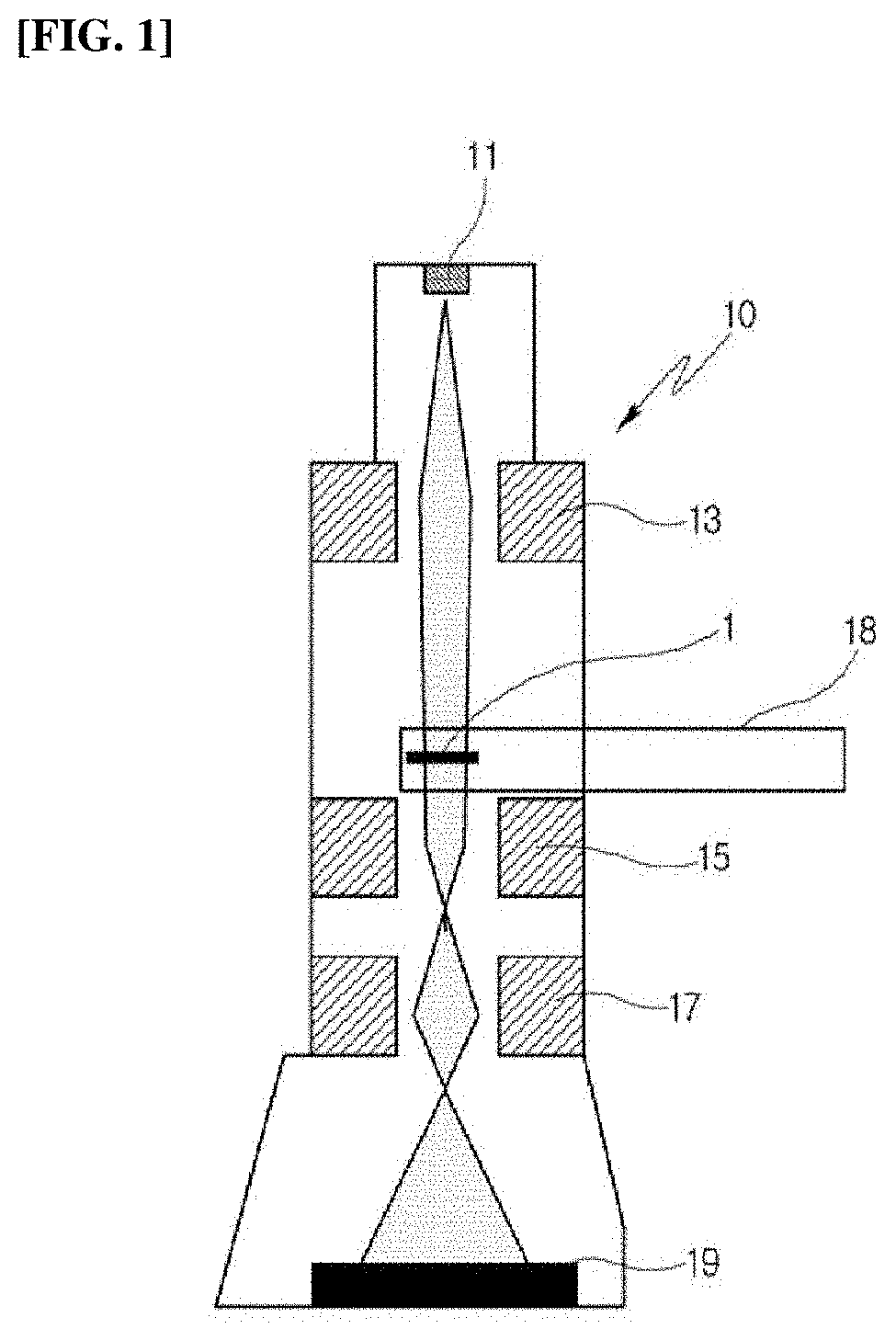

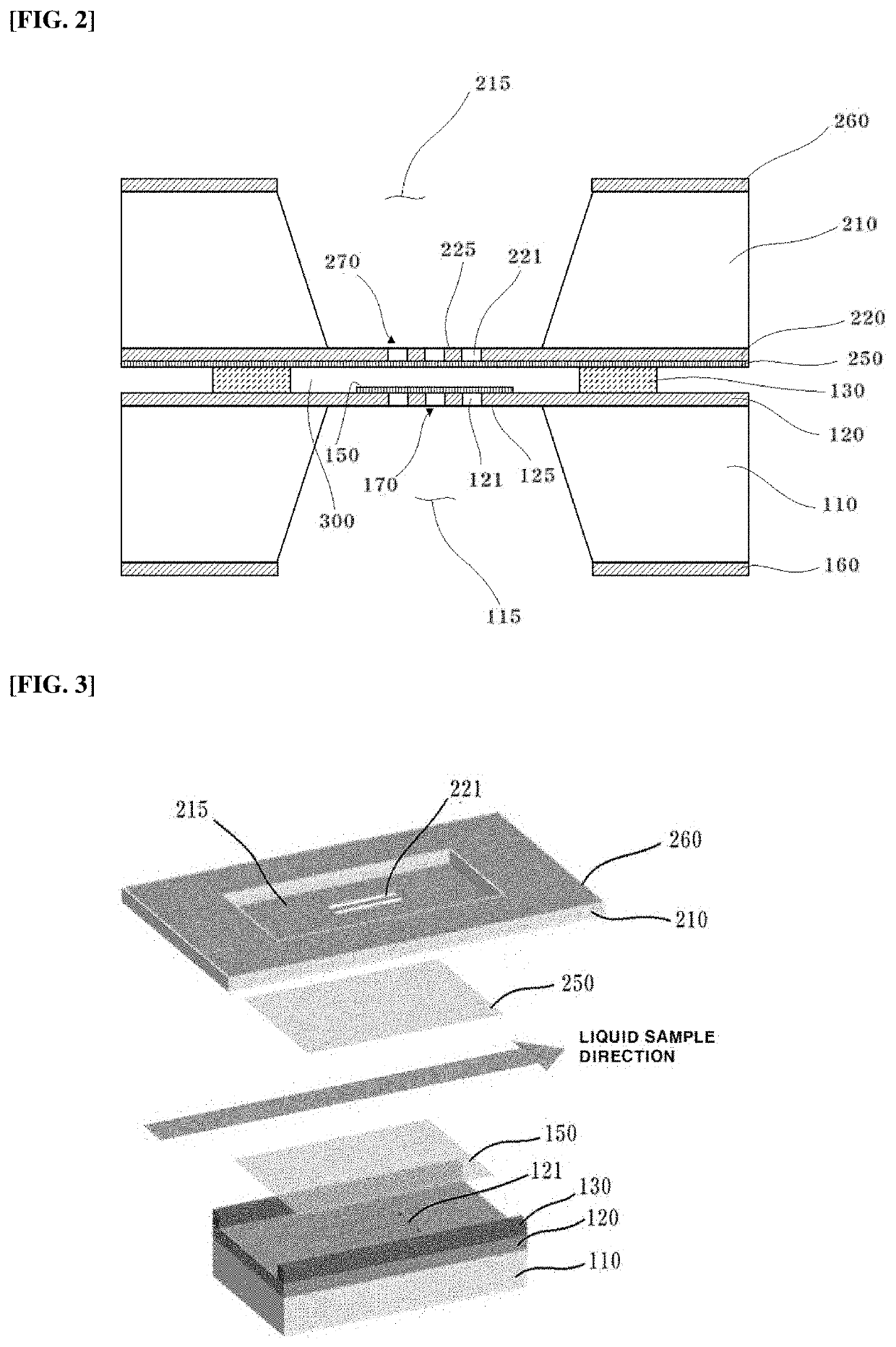

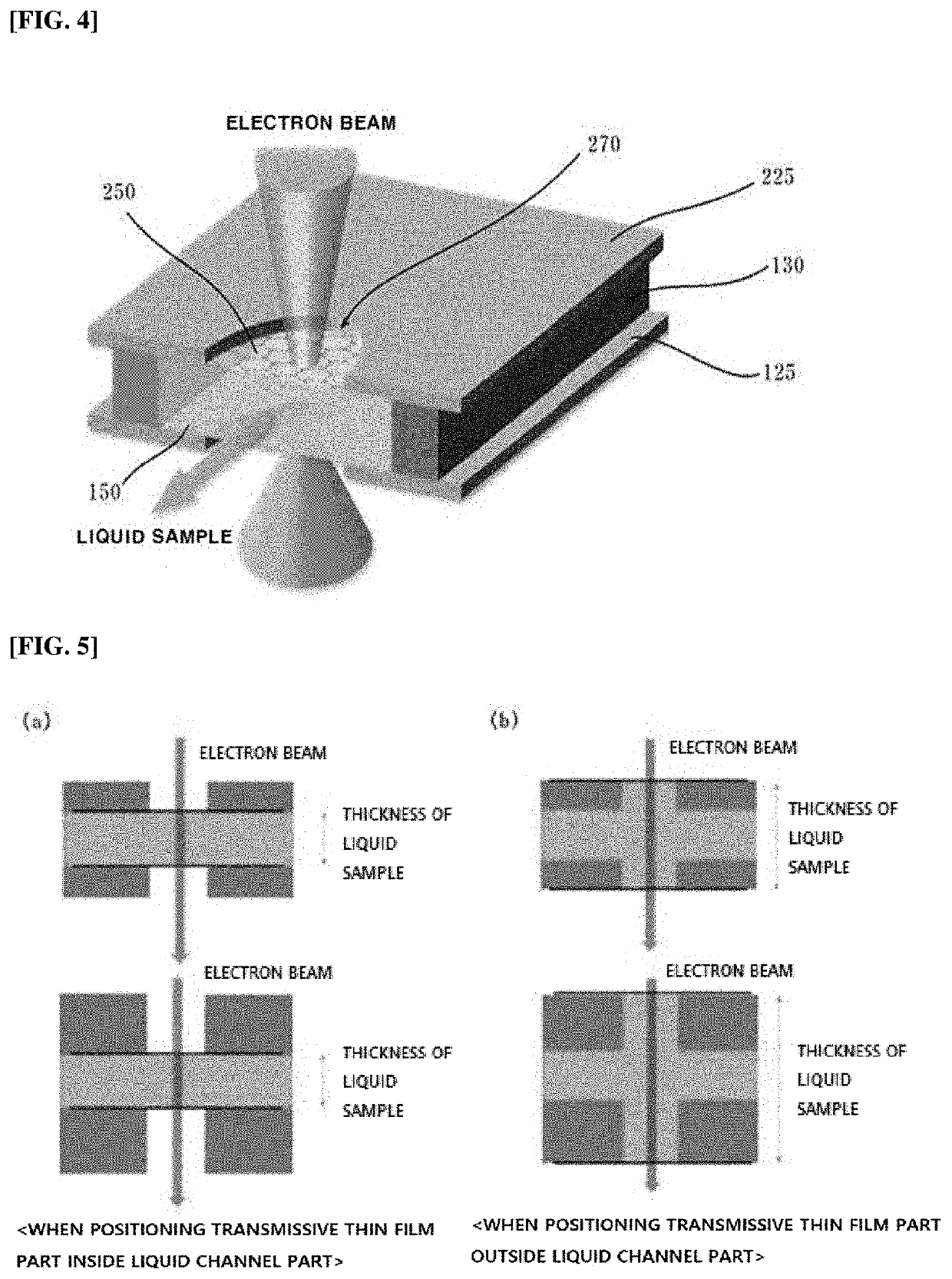

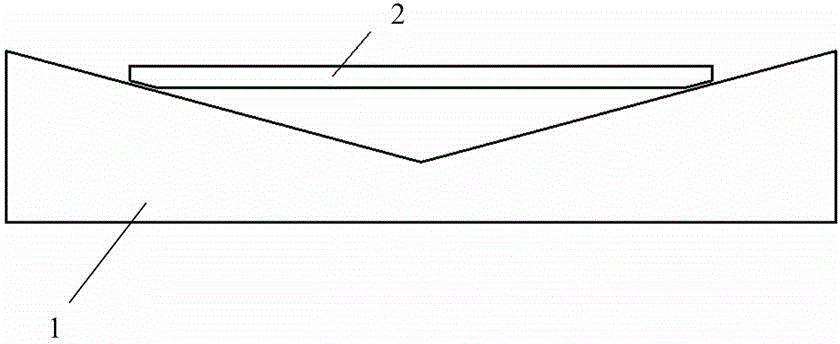

Liquid chip for electron microscope having excellent bulging resistance

ActiveUS20200240933A1Excellent productivity improvementSuppress the bulging phenomenon of a liquid chipElectric discharge tubesLaboratory glasswaresReal time analysisChIP-on-chip

The present disclosure relates to a liquid chip for an electron microscope including a lower chip, an upper chip, and a liquid channel part for supplying a liquid sample, and may attach a transmissive thin film part of a graphene material having excellent bulging resistance to a plurality of holes formed in a liquid channel part to increase the thickness of a support not serving as a transmissive window thicker than the conventional one, thereby minimizing the loss of a spatial resolution and also suppressing the bulging phenomenon of the transmissive window while supplying the liquid sample more stably.Further, the present disclosure may form an electrode which may be connected with an external electrical supply source in the liquid channel part, thereby analyzing electrochemical or thermochemical reaction of the liquid sample in the liquid channel part in real time.

Owner:KOREA ADVANCED INST OF SCI & TECH

Semiconductor electronic component and semiconductor device using the same

InactiveCN101529590AReduce thicknessIncrease containmentNon-macromolecular adhesive additivesFilm/foil adhesivesChIP-on-chipShortest distance

The present invention discloses a chip-on-chip type semiconductor electronic component and a semiconductor device which can meet the requirements for further density increase of semiconductor integrated circuits. The present invention provides: a chip-on-chip type semiconductor electronic component in which a circuit surface of a first semiconductor chip and a circuit surface of a second semiconductor chip are opposed to each other, wherein the distance X between the first semiconductor chip and the second semiconductor chip is 50 [mu]m or less, and the shortest distance Y between the side surface of the second semiconductor chip and the first external electrode is 1 mm or less; and a semiconductor device comprising the same.

Owner:SUMITOMO BAKELITE CO LTD

Embedded chip-on-chip package and package-on-package comprising same

ActiveUS8873245B2Small sizeFirmly connectedPrinted circuit assemblingPrinted electric component incorporationChIP-on-chipSemiconductor chip

An embedded chip-on-chip package includes a printed circuit board having a recessed semiconductor chip mounting unit constituted by a recess in the printed circuit board and a circuit pattern at the bottom of the recess, a first semiconductor chip embedded in the recessed semiconductor chip mounting unit and electrically connected to the circuit pattern at the bottom of the recess, and a second semiconductor chip mounted to the recessed semiconductor chip mounting unit and electrically connected to the first semiconductor chip and the printed circuit board independently of each other.

Owner:SAMSUNG ELECTRONICS CO LTD

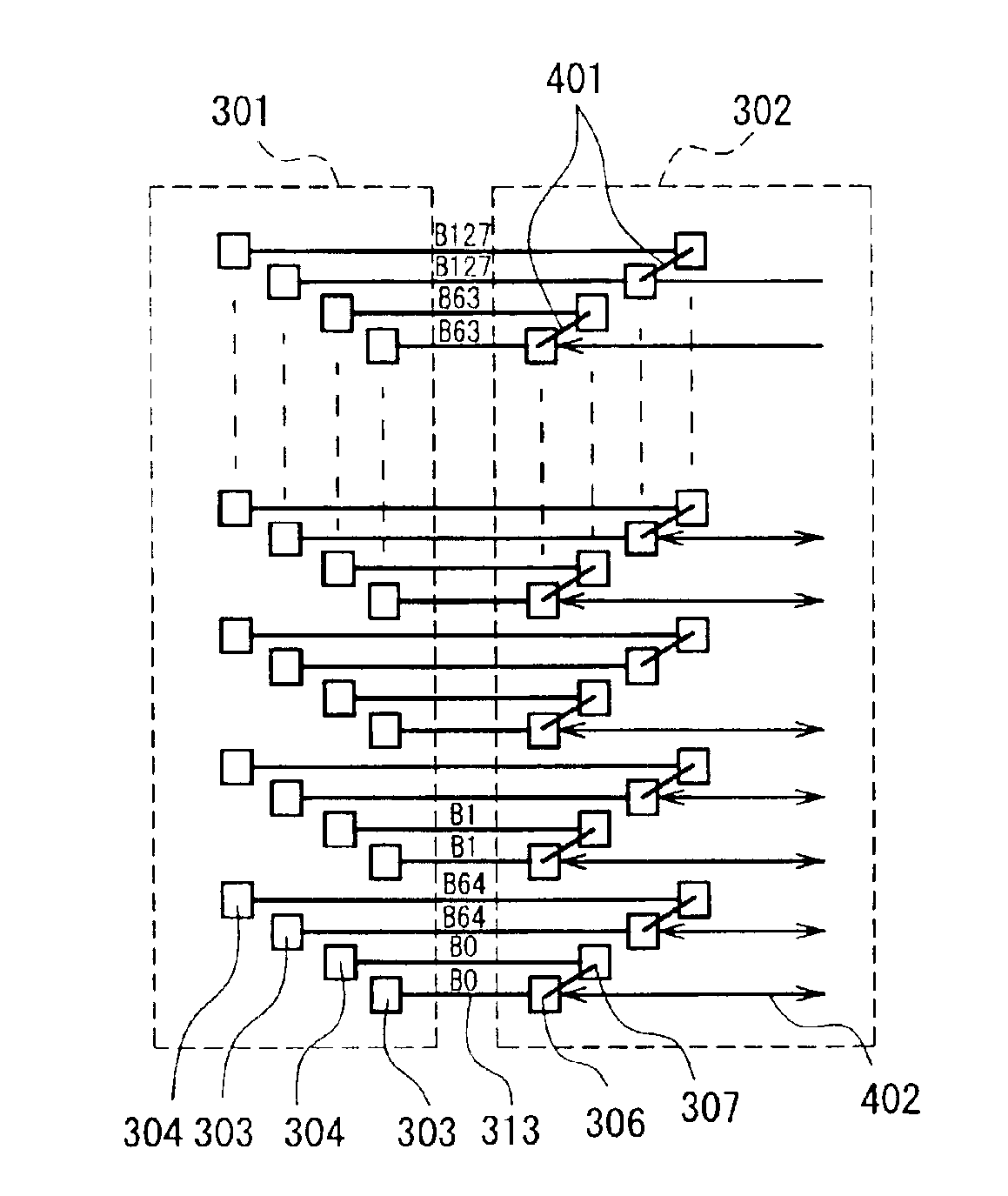

Semiconductor memory device and method of manufacturing semiconductor device with chip on chip structure

InactiveUS6879036B2Simple designIncrease productionSemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipDevice material

A semiconductor memory device for use in a semiconductor device with a chip on chip structure, which enables a memory specification to be selected and fixed, and improves design and production efficiencies. Bonding bumps corresponding to an input terminal and an output terminal of an interface circuit are connected to bonding bumps provided on another semiconductor device. Then, a polarity of a potential on a bus width varying terminal is fixed by the bonding bump provided on another semiconductor device, so that an isolated input / output specification is selected as a bus specification of the interface circuit and a bus width is selected.

Owner:CETUS TECH INC

Multi-chips stacked package

InactiveUS20070176278A1Improve reliabilityEasy to crackSemiconductor/solid-state device detailsPrinted electric component incorporationChIP-on-chipChip stacking

A multi-chips stacked package mainly comprises a substrate, a first lower chip, a second lower chip, an upper chip and a carrier. The substrate has an upper surface, and the first lower chip and the second lower chip are disposed on the upper surface of the substrate and electrically connected to the substrate. The carrier is disposed on and electrically connected to the first lower chip and the second lower chip simultaneously, and the upper chip is mounted on the carrier. Moreover, the upper chip is electrically connected to the substrate through the carrier, the first lower chip or the second lower chip.

Owner:ADVANCED SEMICON ENG INC

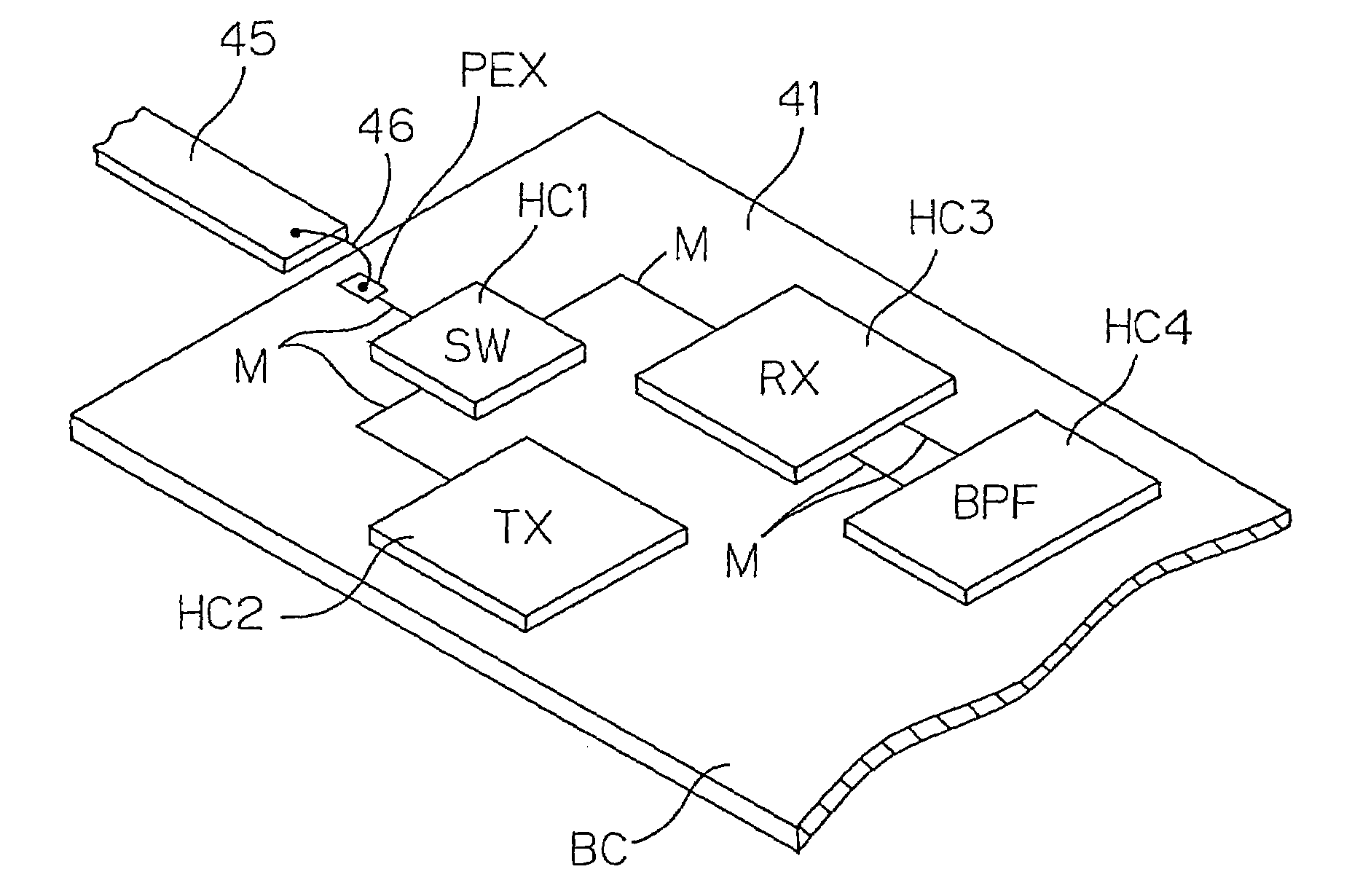

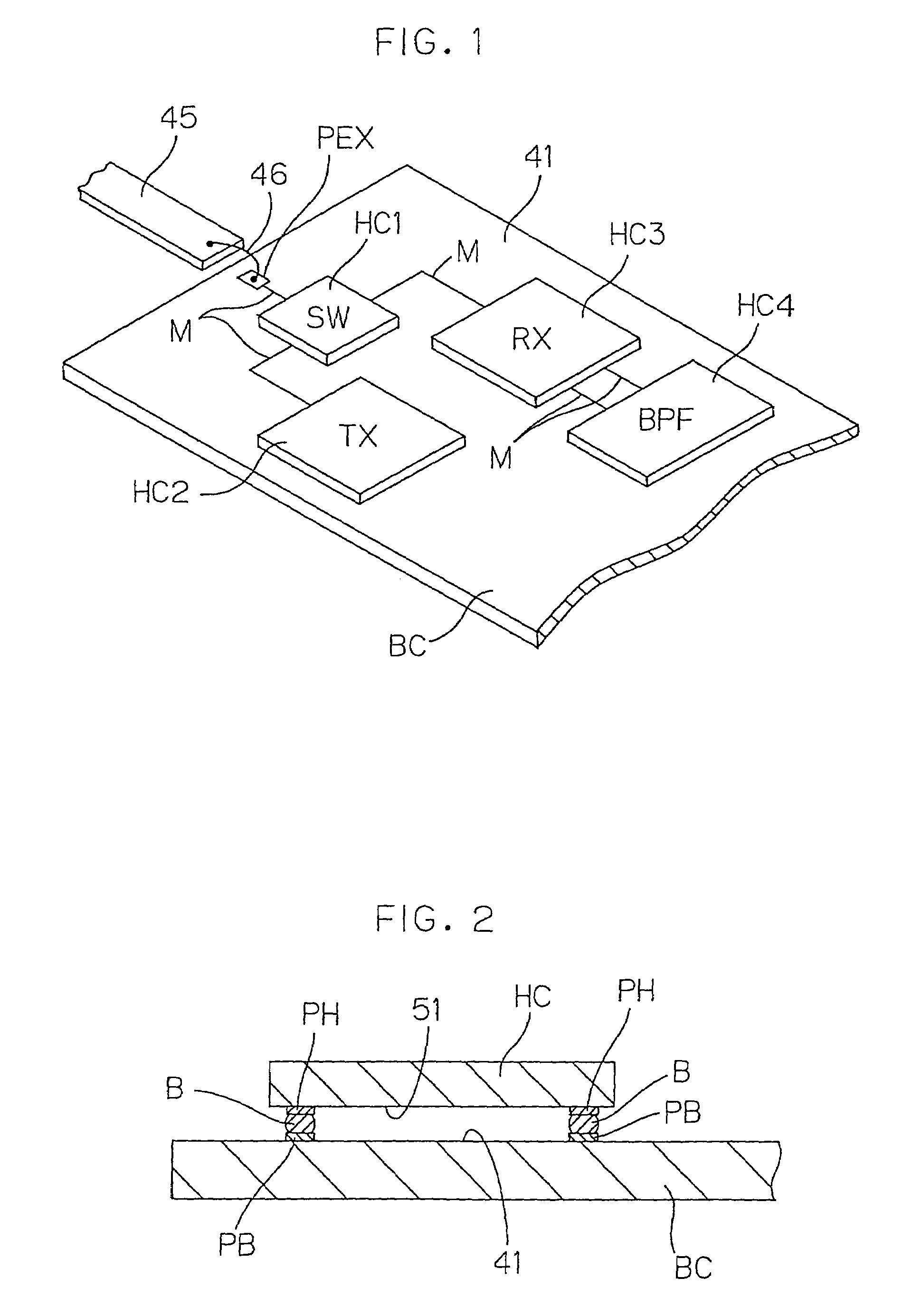

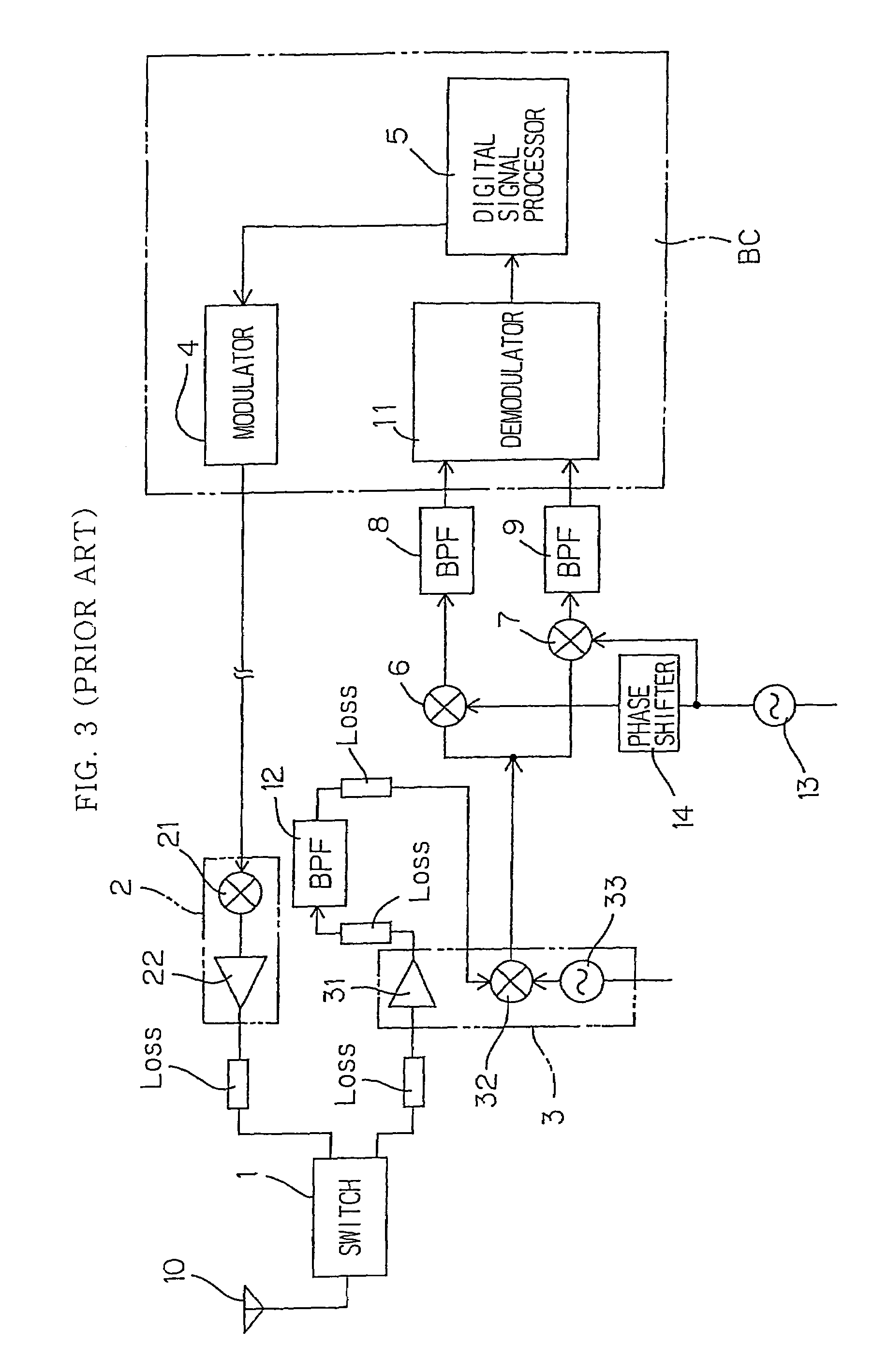

Semiconductor device for radio communication device, and radio communication device using said semiconductor device

InactiveUS7088983B2Convenient ArrangementReduce lossesSemiconductor/solid-state device detailsSolid-state devicesChIP-on-chipEngineering

A chip-on-chip-structure semiconductor device for a radio communication device, having a base band chip and a high-frequency chip piled up on and bonded to the surface thereof. The base band chip has a low-frequency signal processing unit for processing a signal in a first frequency band. The high-frequency chip has a high-frequency signal processing unit for processing a signal in a second frequency band of which frequency is higher than that of the first frequency band.

Owner:TAIWAN SEMICON MFG CO LTD

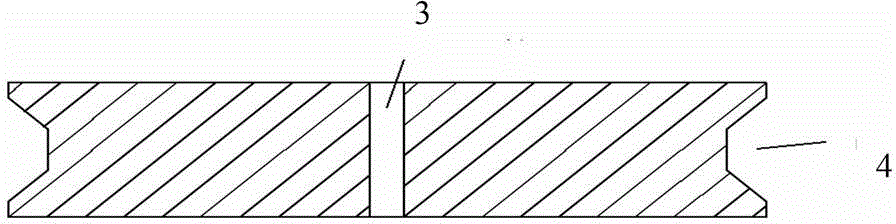

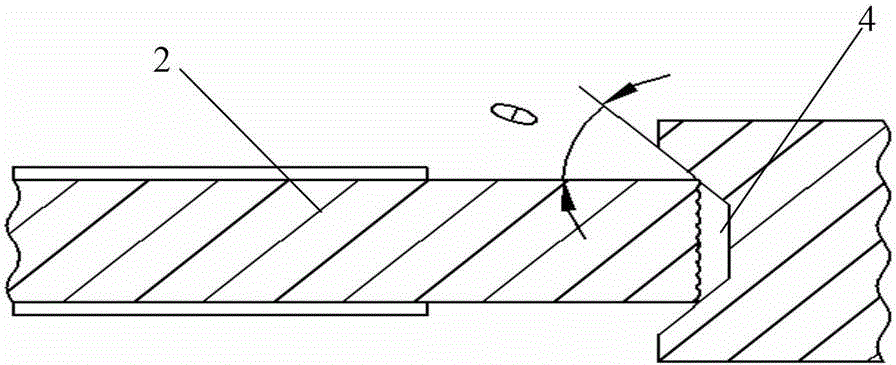

Method for shaping table surface of semiconductor chip

InactiveCN104952719AAngle fit fineImprove efficiencySemiconductor/solid-state device manufacturingChIP-on-chipSemiconductor chip

The invention discloses a method for shaping the table surface of a semiconductor chip. The method comprises the following steps: using a grinding wheel rotating at a high speed, forming a groove corresponding to the needed groove shape in the grinding wheel, plating a grinding layer in the groove, and after the cylindrical surface of a chip ending terminal on the chip to be machined stretches in the groove, shaping the table surface by means of contacting with the groove and grinding. The method disclosed by the invention has the advantages of being convenient and efficient, simple in process, high in yield, low in manufacturing cost, and the like.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

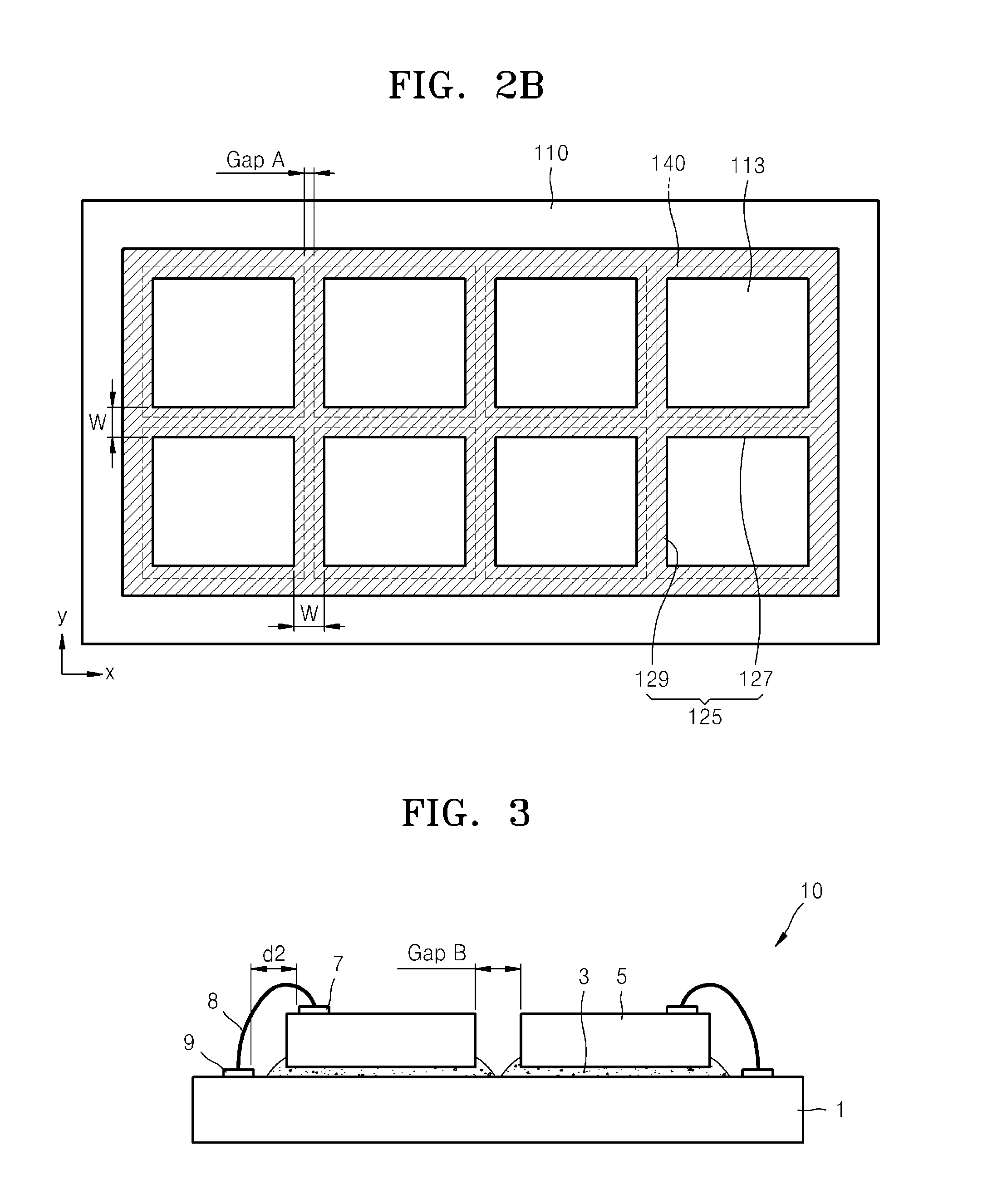

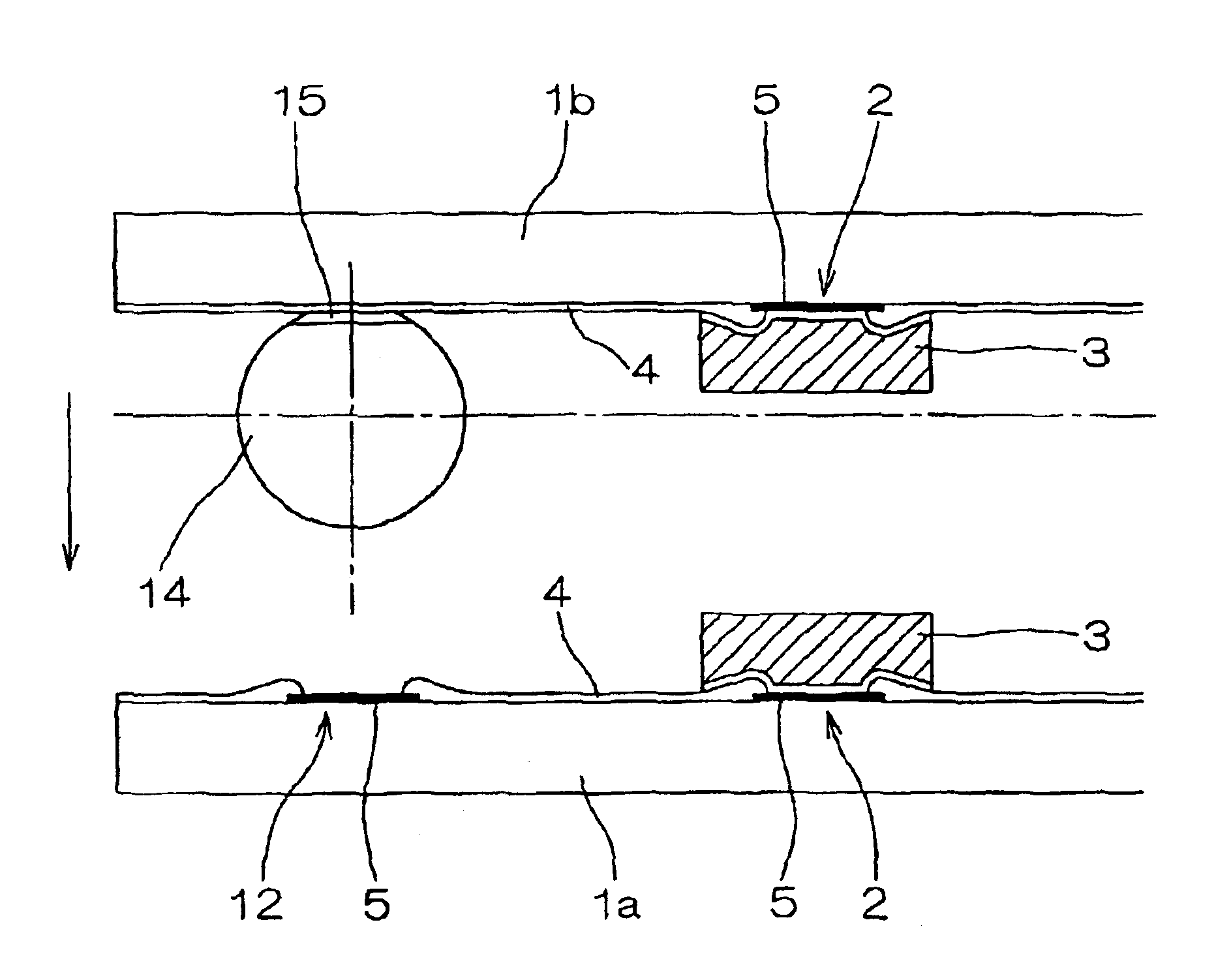

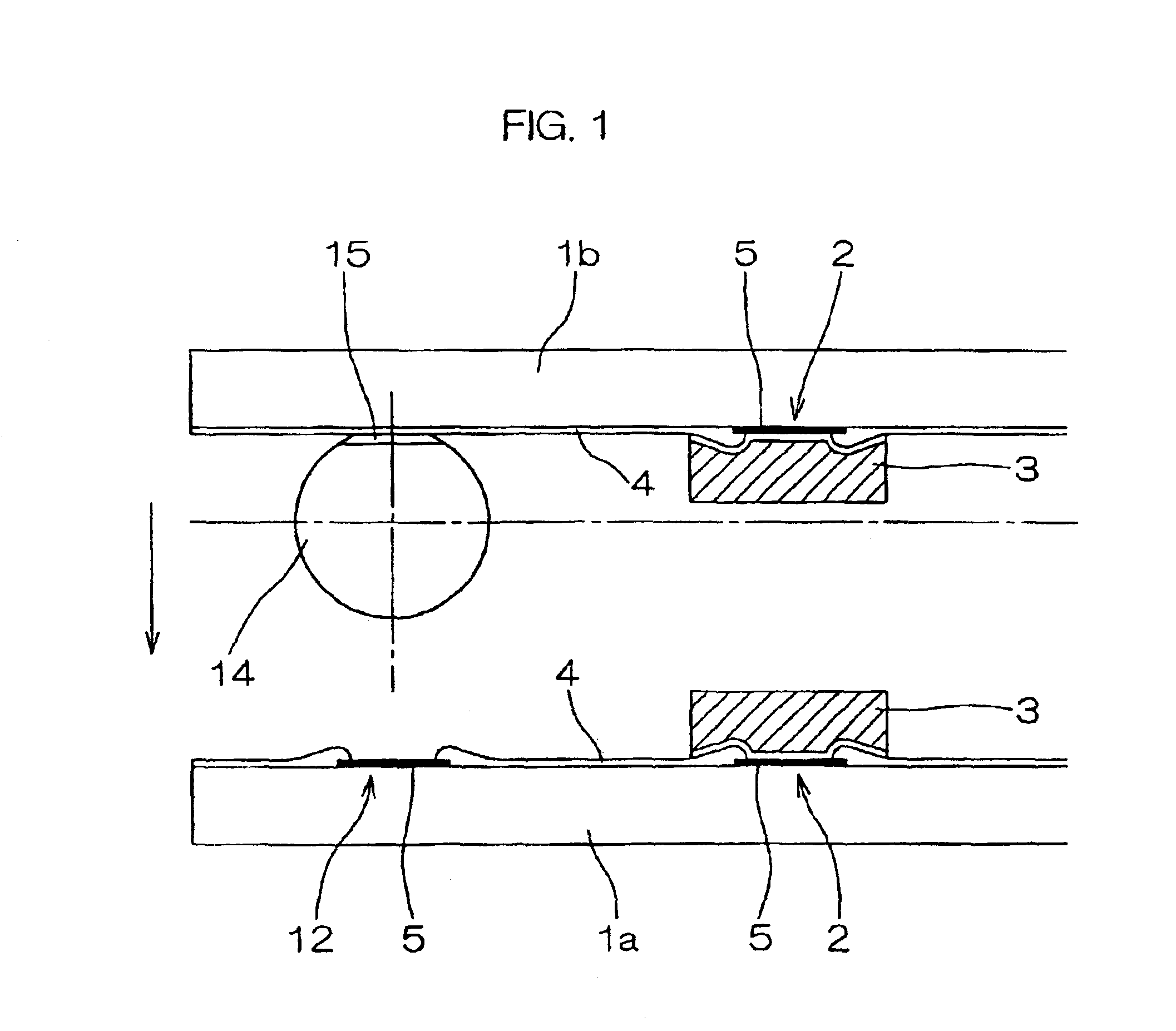

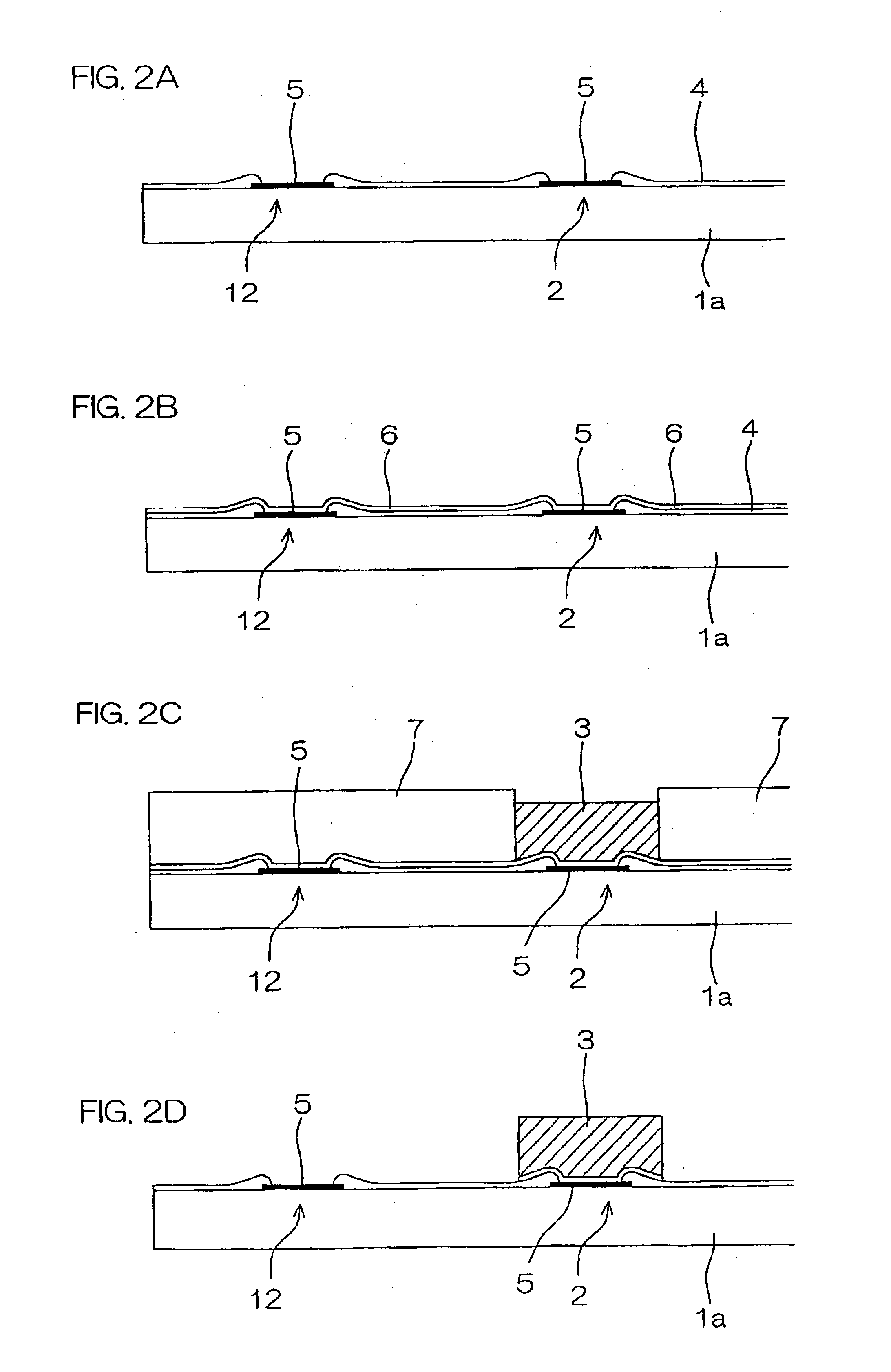

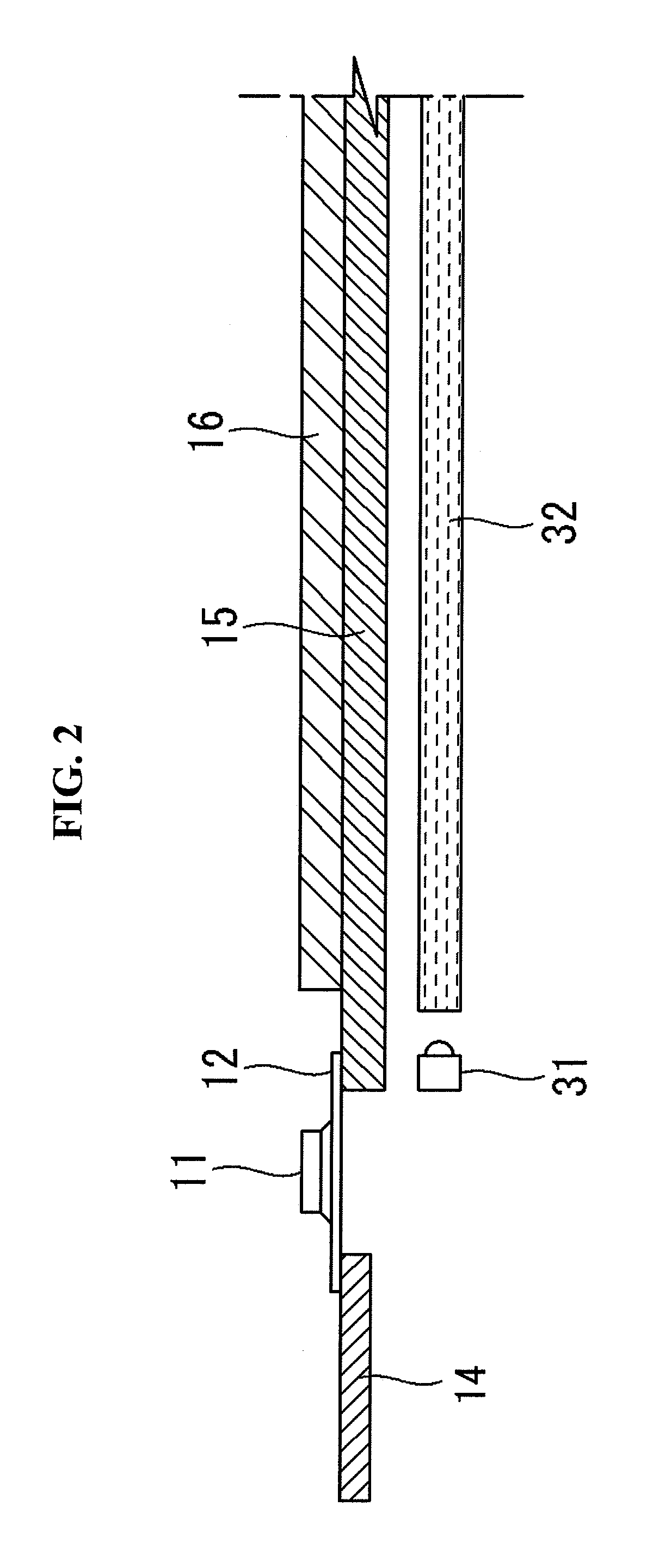

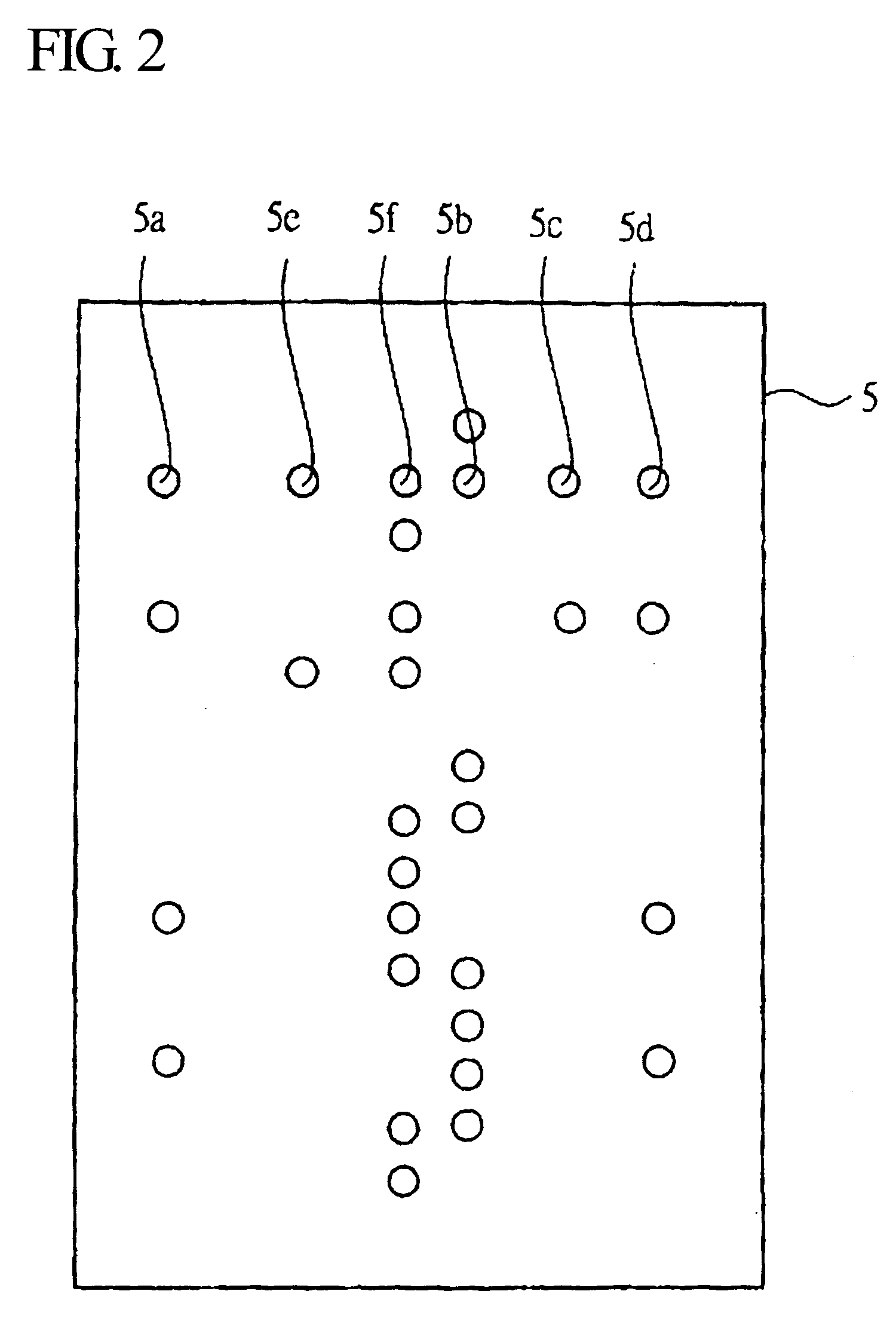

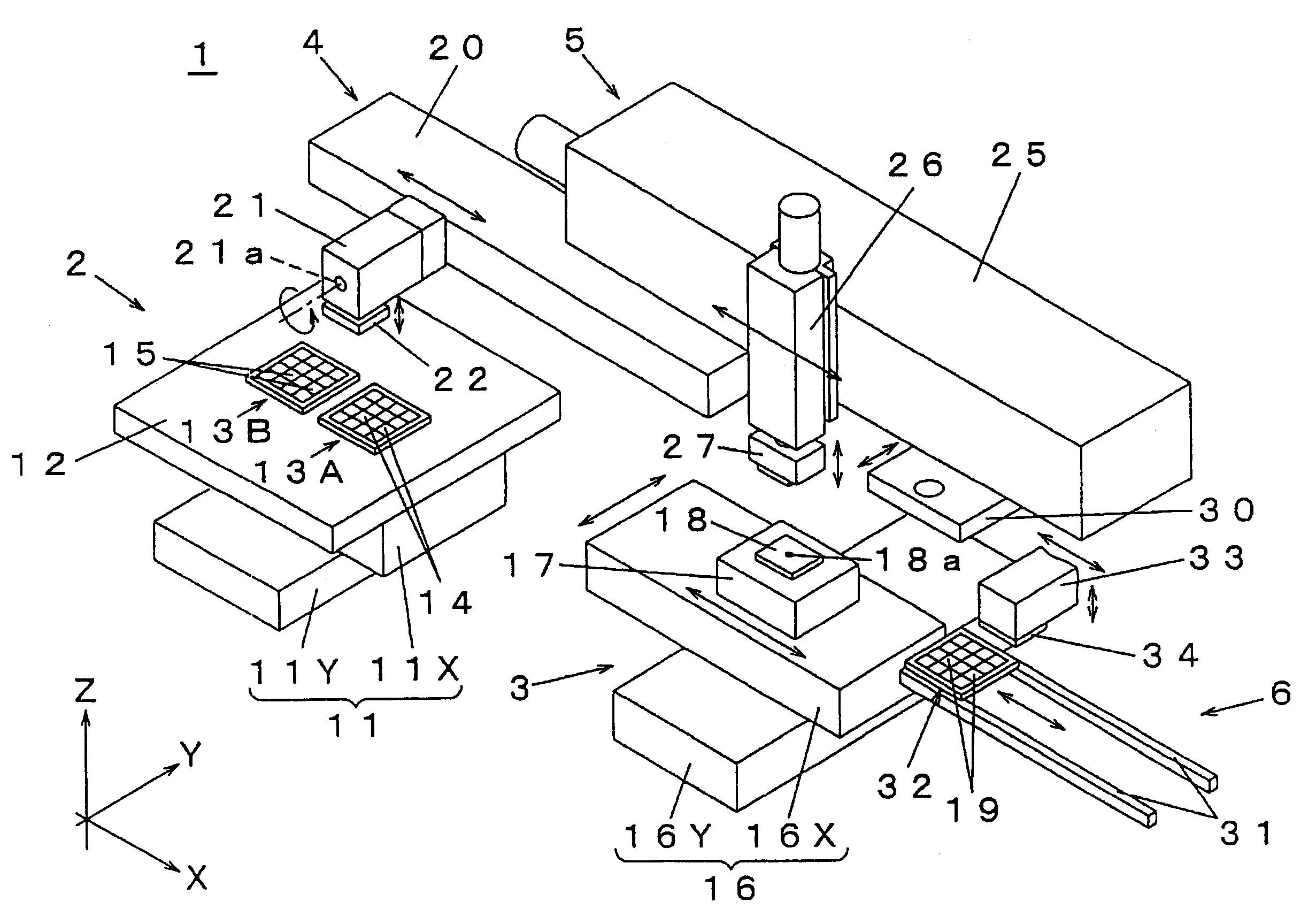

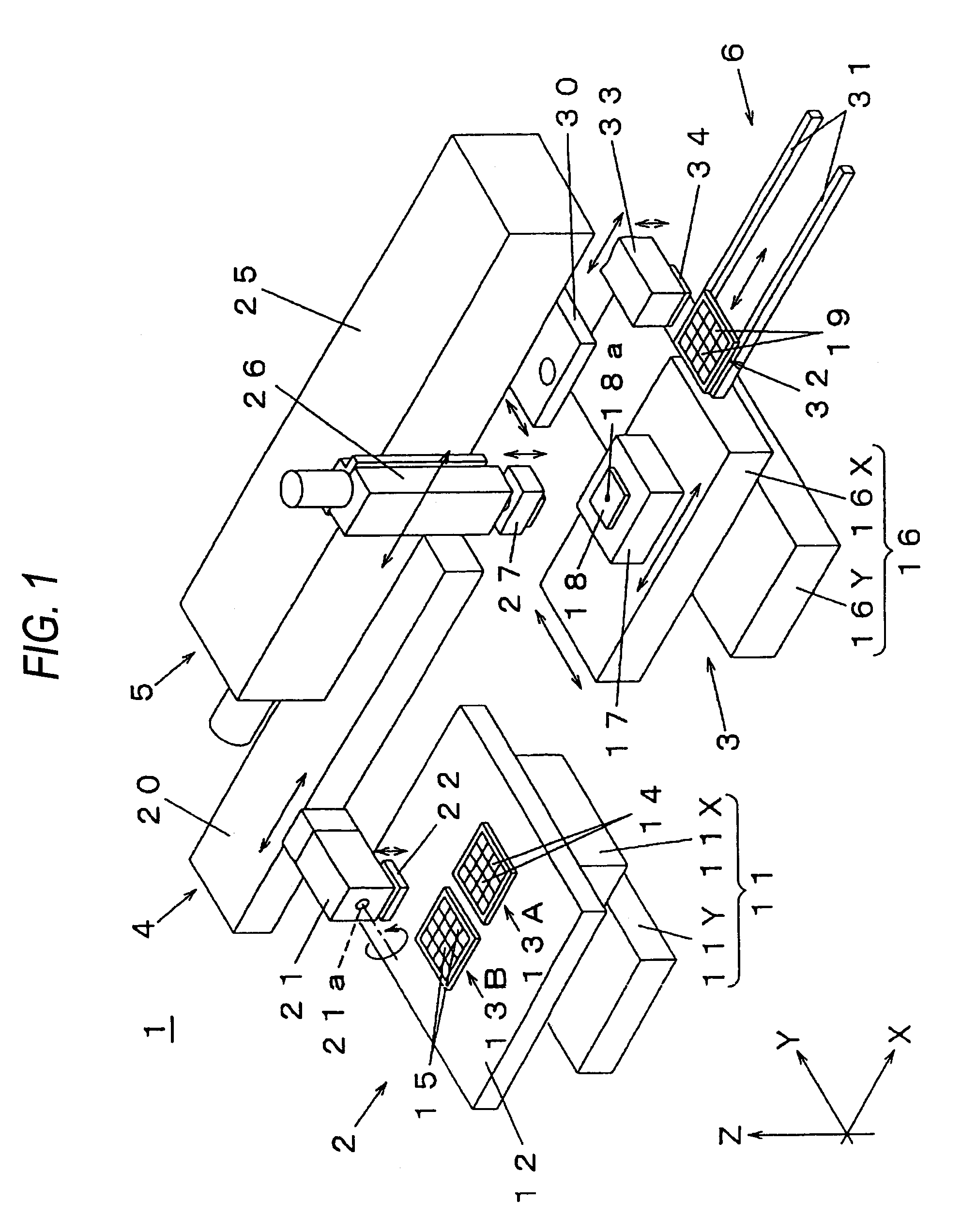

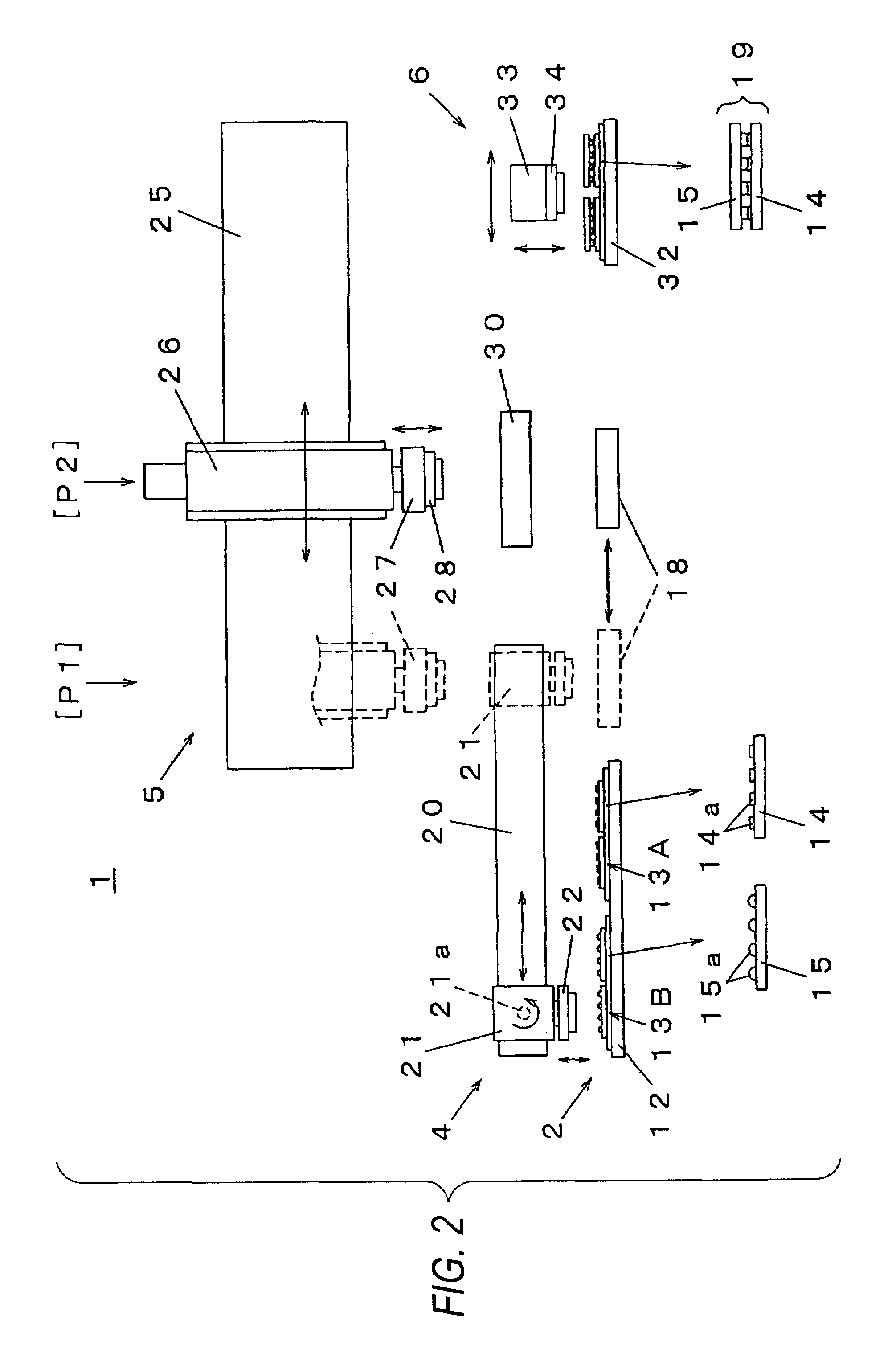

Component mounting method

ActiveUS7281322B2Efficient executionPrinted circuit assemblingSolid-state devicesChIP-on-chipMechanical engineering

Owner:PANASONIC CORP