Multi-chips stacked package

a technology of stacking and chips, applied in the field of stacking packages, can solve the problems of reducing affecting the development of packaged integrated circuits of higher performance, and affecting the development speed of integrated circuits, so as to prevent the damage of the upper chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

second embodiment

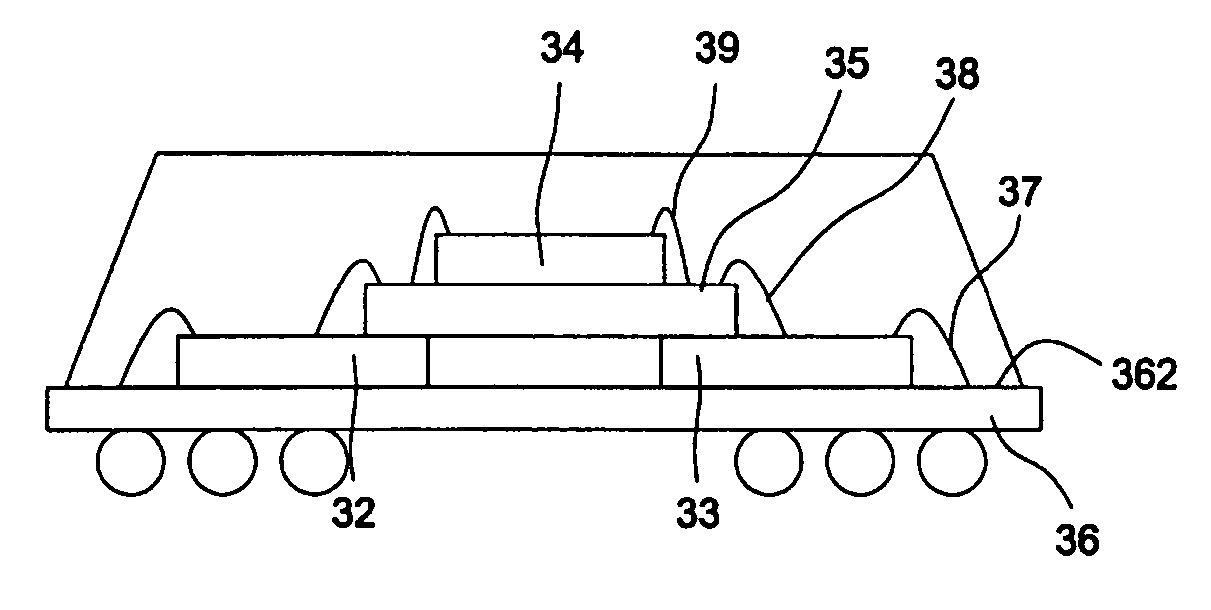

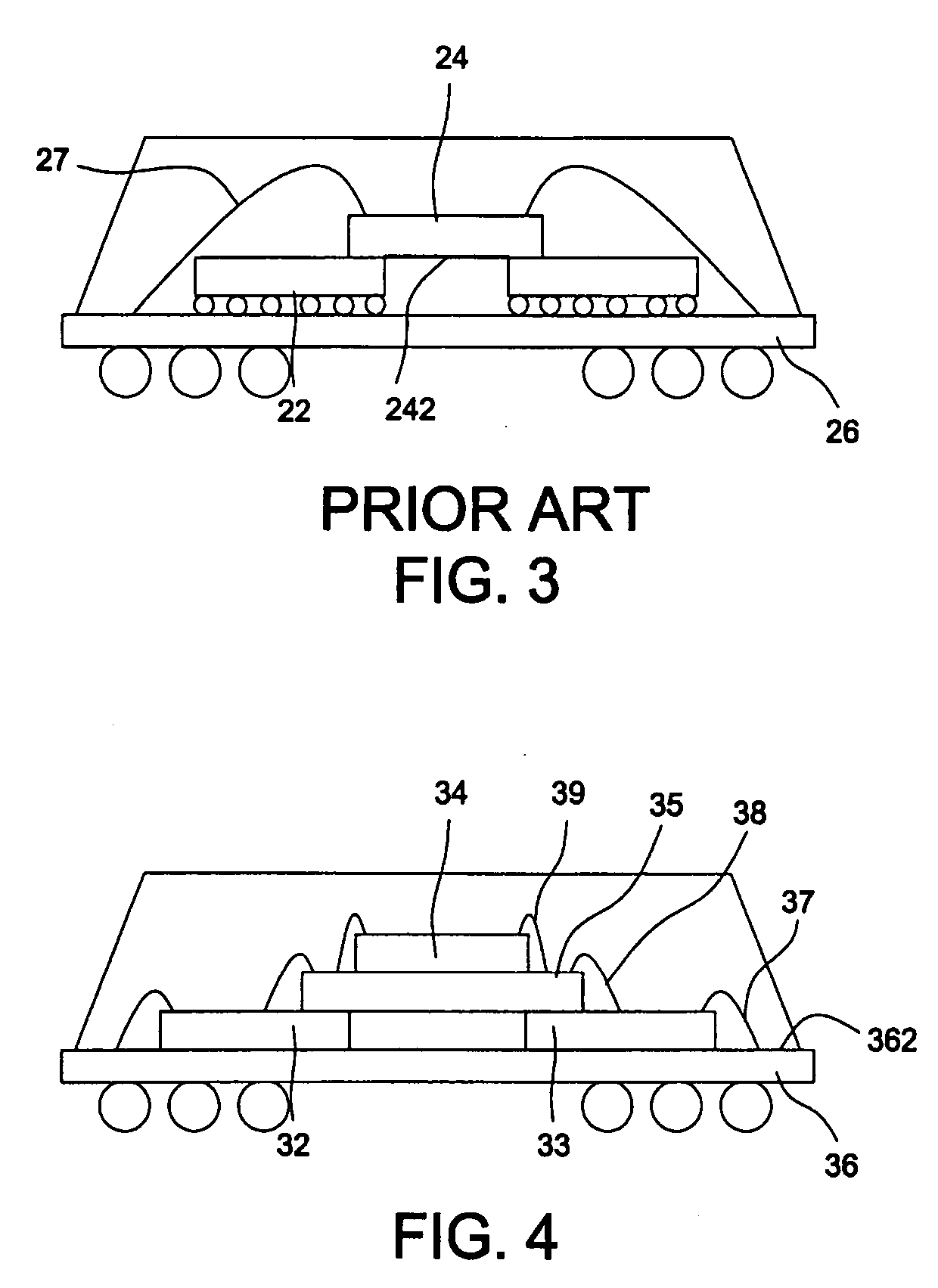

[0024] Besides, as shown in FIG. 5, it illustrates a second embodiment in according to this invention. The upper chip 34 is mounted on the carrier 35 via a plurality of electrically conductive bumps 342, for example solder bumps and gold bumps. In addition, the carrier 35 further has a circuit layer 352 for electrically connecting to the electrically conductive bumps 342. Thus, the upper chip 34 is electrically connected to the first lower chip 32 and the second lower chip 33 through the electrically conductive bumps 342, the circuit layer 352 and the electrically conductive wires 38.

[0025] Furthermore, as shown in FIG. 6, it illustrates a third preferred embodiment according to this invention. The upper chip 34 is electrically connected to the carrier 35 via a plurality of electrically conductive bumps 342 and the upper chip 34 is electrically connected to the substrate 36 through the electrically conductive bumps 342, the circuit layer 352 and electrically conductive wires 38′.

fourth embodiment

[0026] Next, as shown in FIG. 7, it illustrates a The upper chip 34 is electrically connected to the carrier 35 via a plurality of electrically conductive wires 39 by wire-bonding technology. Similarly, the carrier 35 further comprises a circuit layer 352 so as to have the upper chip 34 electrically connected to the substrate 36 through the electrically conductive wires 39, the circuit layer 352 and another electrically conductive wires 38″.

[0027] As mentioned above, said carrier 35 can be a printed circuit board. Generally speaking, it is composed of a core layer and a copper layer. Therein, the copper layer is patterned to form a circuit layer to be electrical paths and the core layer is formed of a material selected from Bismaleimide-Triazine (BT) and glass epoxy resins (FR4) so that the carrier 35 is able to bear the wire-bonding force by the stiffness of the core layer in the performance of the wire bonding process. Thus, the upper chip 34 can be prevented from being damaged. ...

sixth embodiment

[0029] Finally, referring to FIG. 9, there is provided a Said first lower chip 42 and said second lower chip 43 are disposed on the upper surface 462 of the substrate 46, and electrically connected to the substrate 46 via electrically conductive wires 48. In addition, the carrier 45 is disposed on the first lower chip 42 and the second lower chip 43 simultaneously, and electrically connected to the first lower chip 42 and the second lower chip 43 through electrically conductive bumps 47. Moreover, the upper chip 44 is disposed on the carrier 45 and electrically connected to the first lower chip 42 and the second lower chip 43 through electrically conductive wires 49, a circuit layer 452, a plurality of electrically conductive bumps 47. After the electrical signals are transmitted from the upper chip 44 to the first lower chip 42 and the second lower chip 43, the signals will be transmitted to the substrate 46 through electrically conductive wires 48. It should be noted that the ref...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More