Programmable visual chip-based visual image processing system

A visual image and processing system technology, applied in the field of visual image processing systems based on programmable visual chips, can solve the problems of large chip area, lack of advanced image processing functions, and inability to achieve fast and flexible wide-area processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0083] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

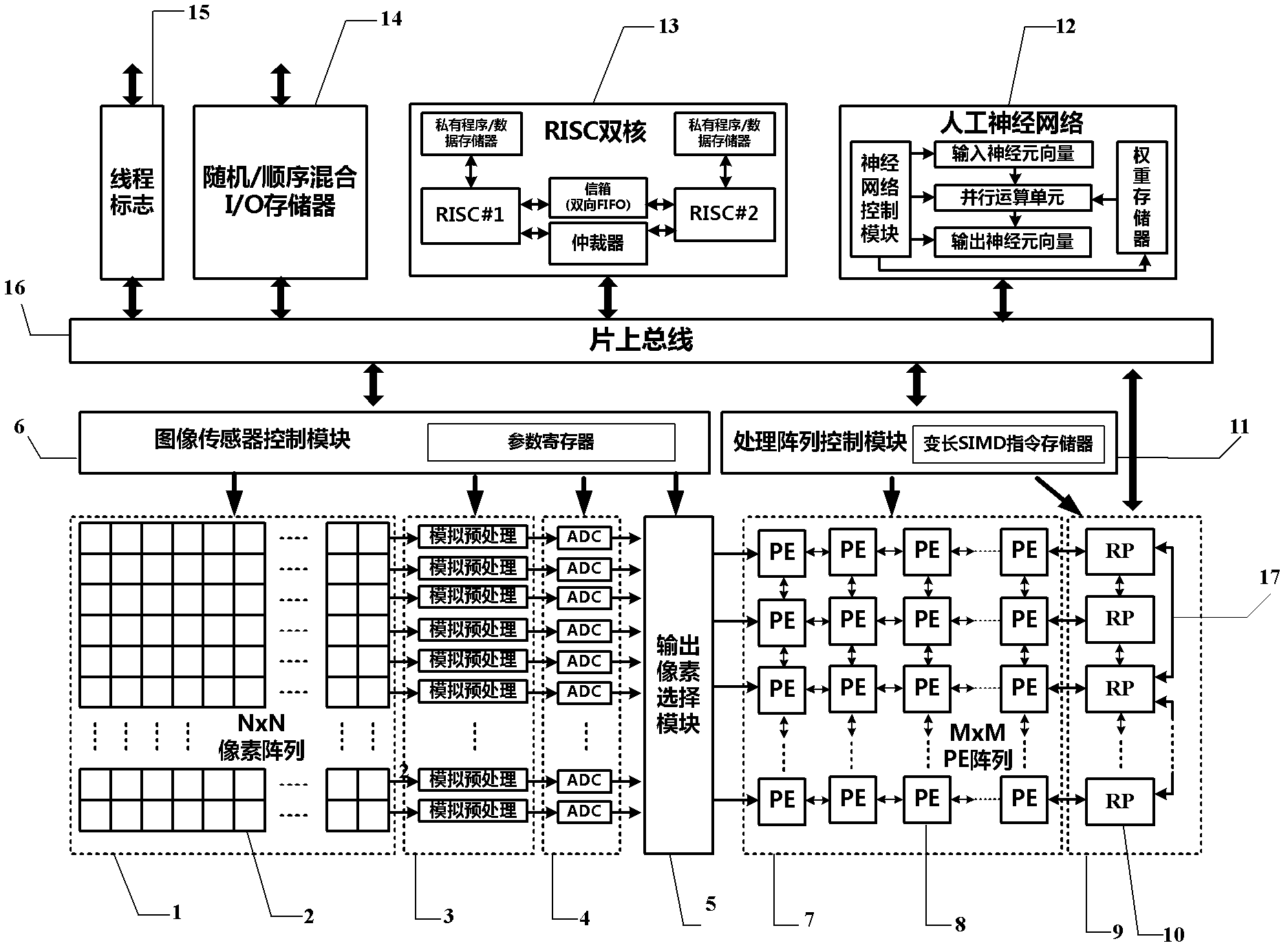

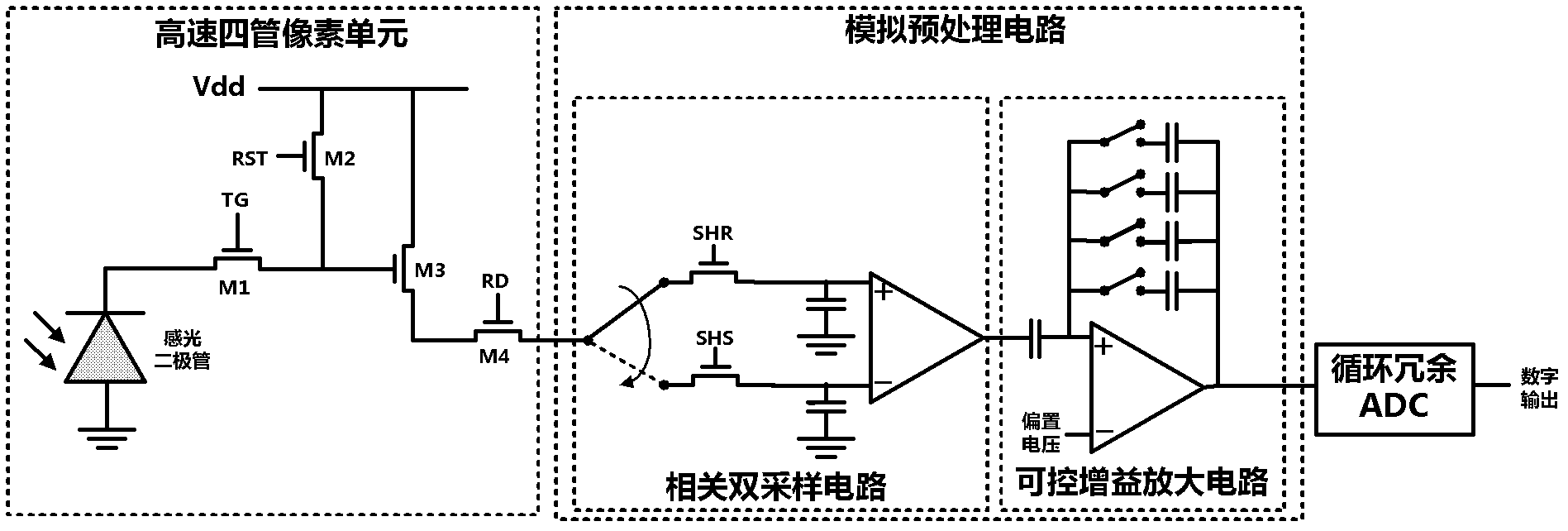

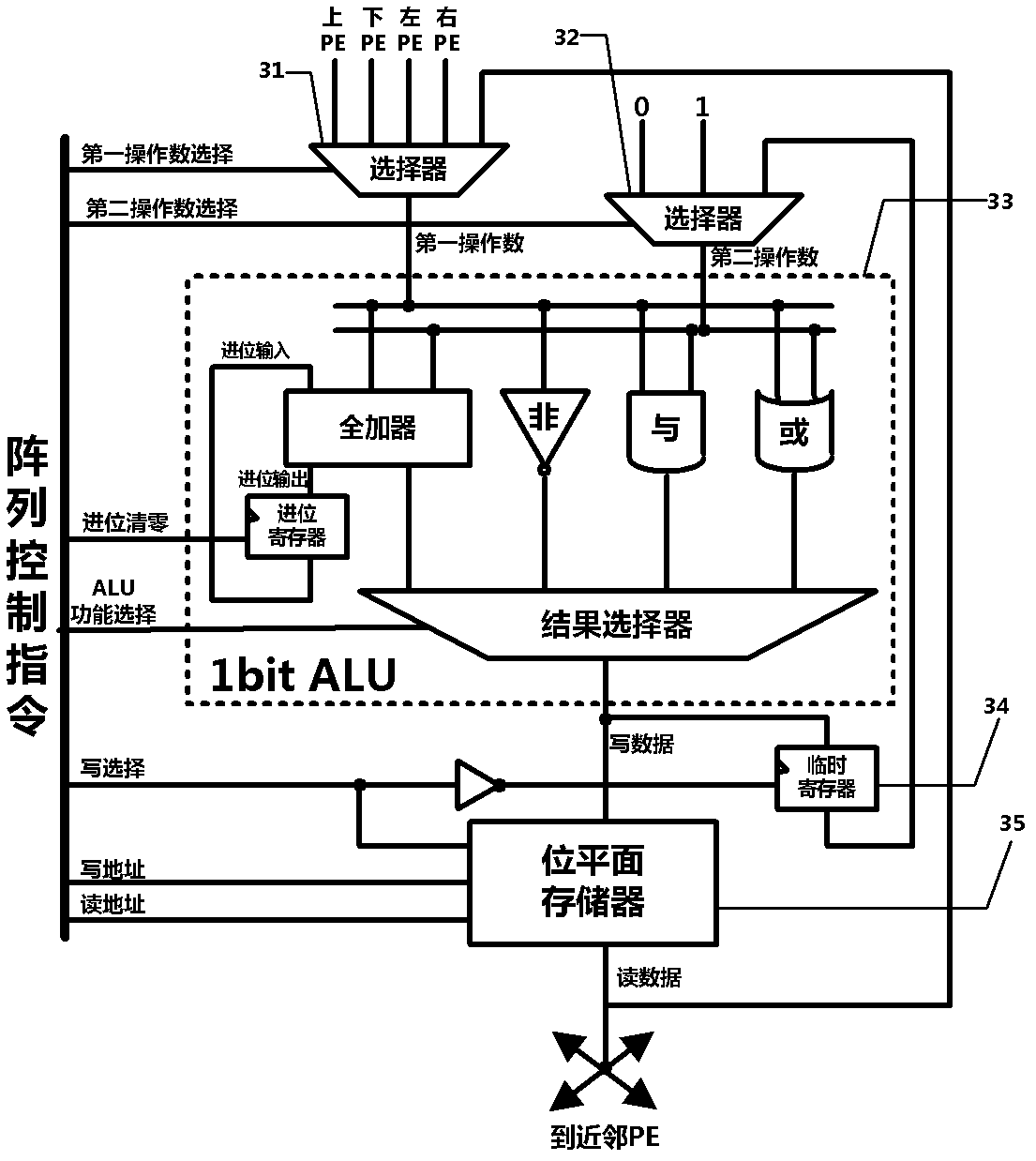

[0084] Such as figure 1 as shown, figure 1 It is a schematic structural diagram of a visual image processing system based on a programmable visual chip provided by the present invention, and the system includes two parts: an image sensing module and a multi-stage parallel digital image processing module. Wherein the image sensor module includes an N×N pixel array, an N×1 parallel analog preprocessing array, an N×1 parallel analog-to-digital conversion unit (ADC) array, an output pixel selection module and an image sensor control module, in this embodiment , N=256, which can reach the standard resolution in applications such as machine vision. Multi-level parallel digital image processing module includes M×M pixel-level ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More