Method for reducing analog-digital converter capacitance mismatch error based on capacitance match

An analog-to-digital converter and capacitance mismatch technology, applied in the direction of analog-to-digital converter, analog/digital conversion calibration/test, etc., can solve the problem of increasing the complexity of self-calibration circuit, affecting circuit continuity, and difficult to handle capacitance mismatch error and other problems, to achieve the effect of increasing power consumption, improving design simplicity, and reducing working speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

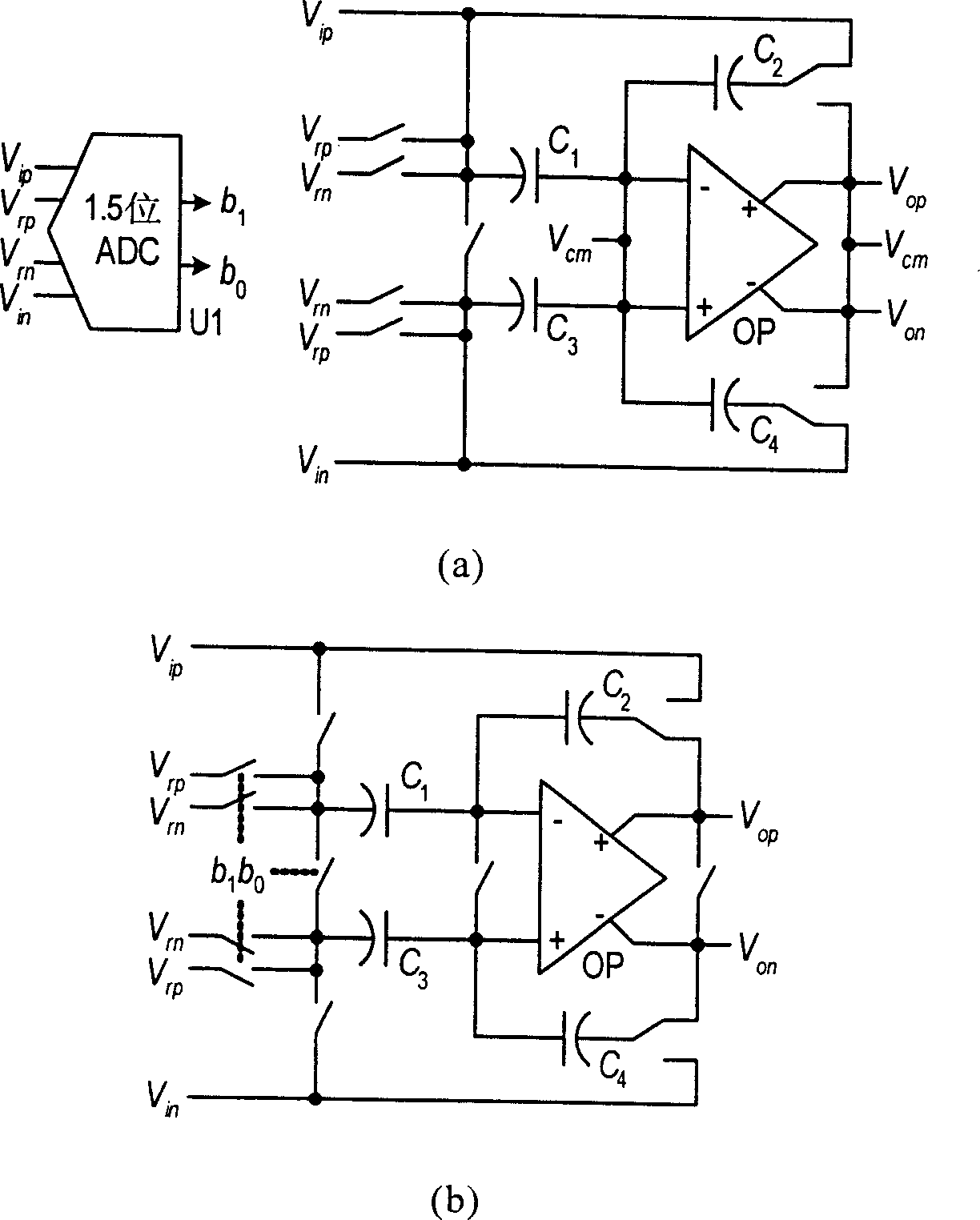

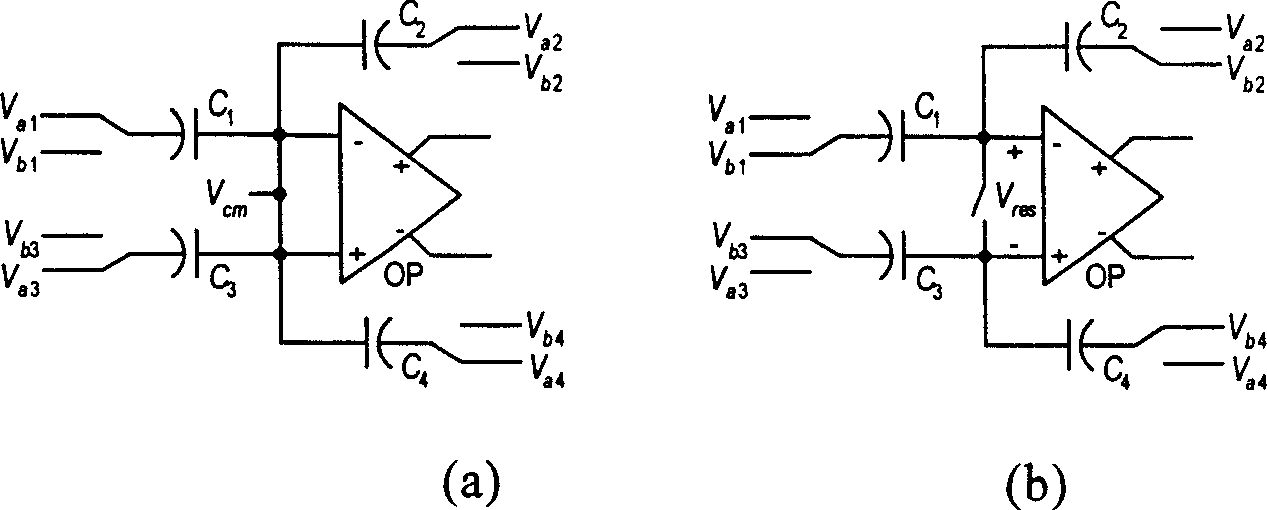

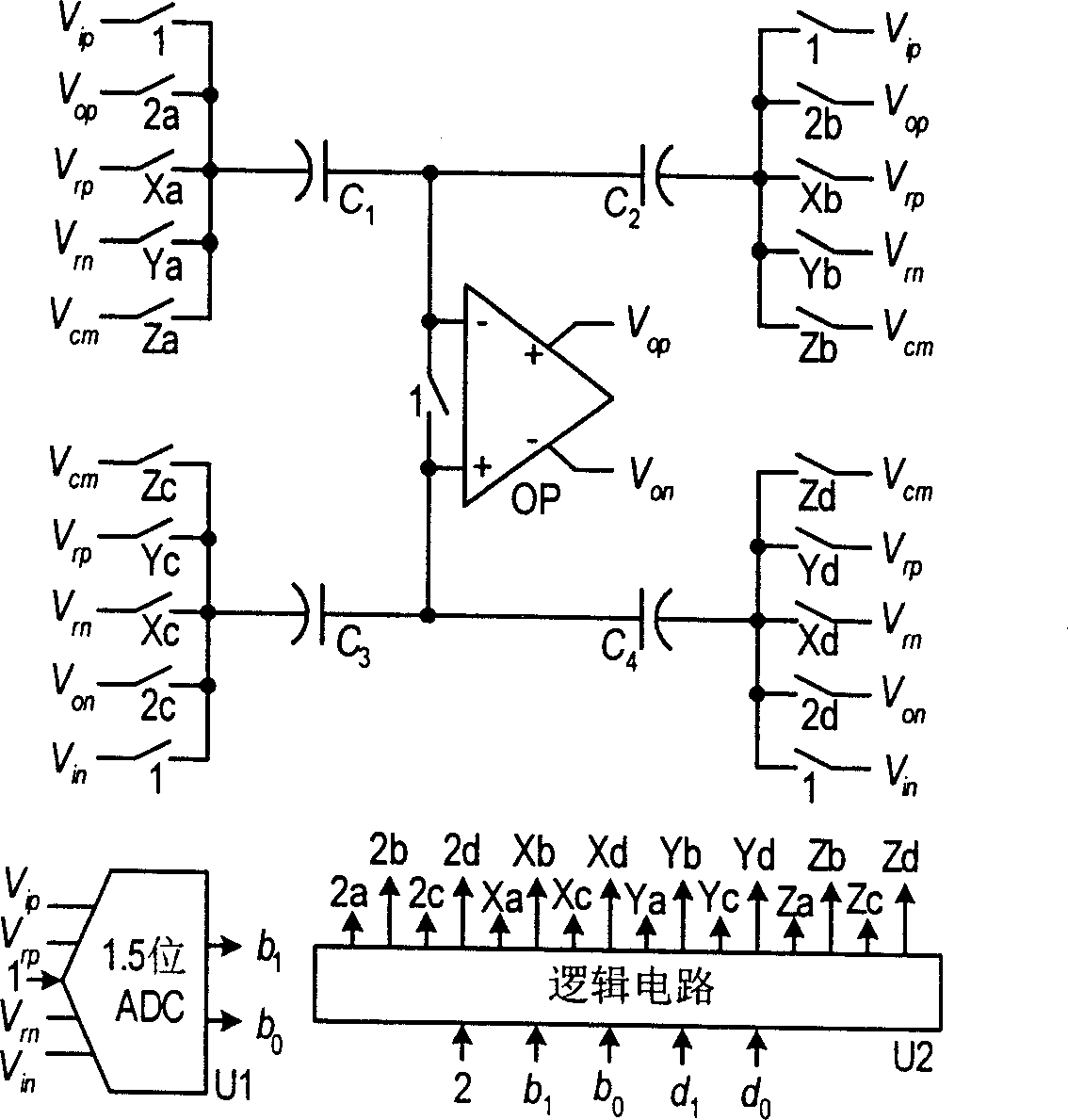

[0031] The method for reducing the capacitance mismatch error of the analog-to-digital converter based on capacitance pairing proposed by the present invention includes: defining among the 4 working capacitors of the intermediate circuit of the analog-to-digital converter, the capacitance of the two top plates connected to the positive input terminal of the operational amplifier is C 1 and C 2 , the two top plates are commonly connected to the negative input of the op amp with a capacitance of C 3 and C 4 , where C 1 and C 3 For the first pair of differential working capacitors, C 2 and C 4 It is the second pair of differential working capacitors, and these two pairs of differential working capacitors are respectively the differential sampling capacitors or differential feedback capacitors of the stage circuit; comparing the sizes of the above four working capacitors, if (C 1 +C 3 )-(C 2 +C 4 ) is greater than (C 1 +C 4 )-(C 2 +C 3 ), then let C 1 and C 4 paired ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More