Power device chip

A technology of power devices and chips, which is applied in the field of power device chips, and can solve problems such as weak current capabilities of power device chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

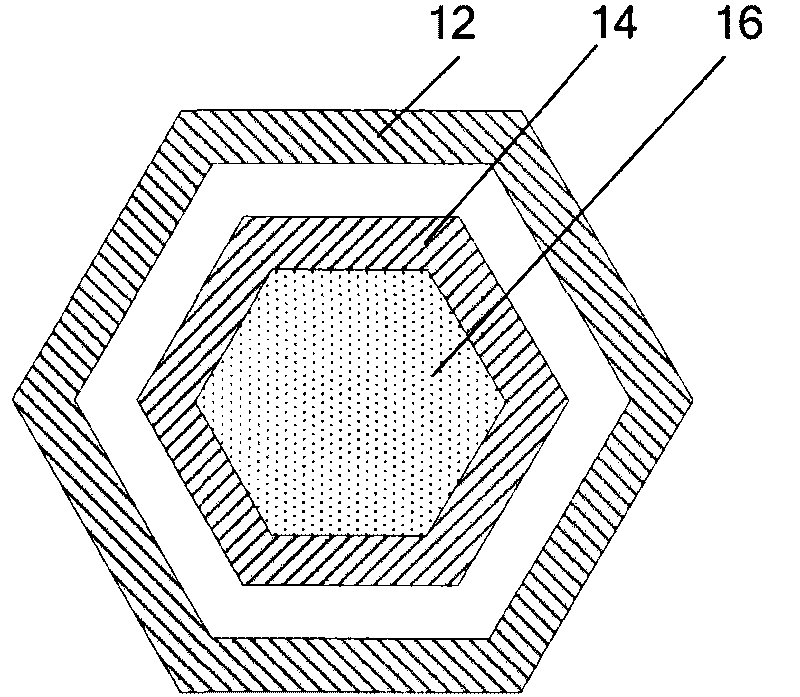

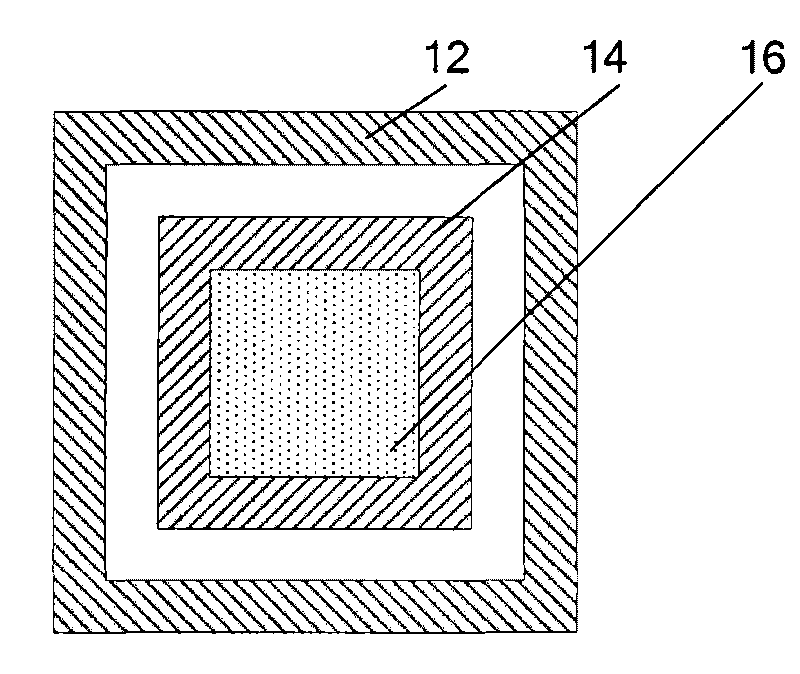

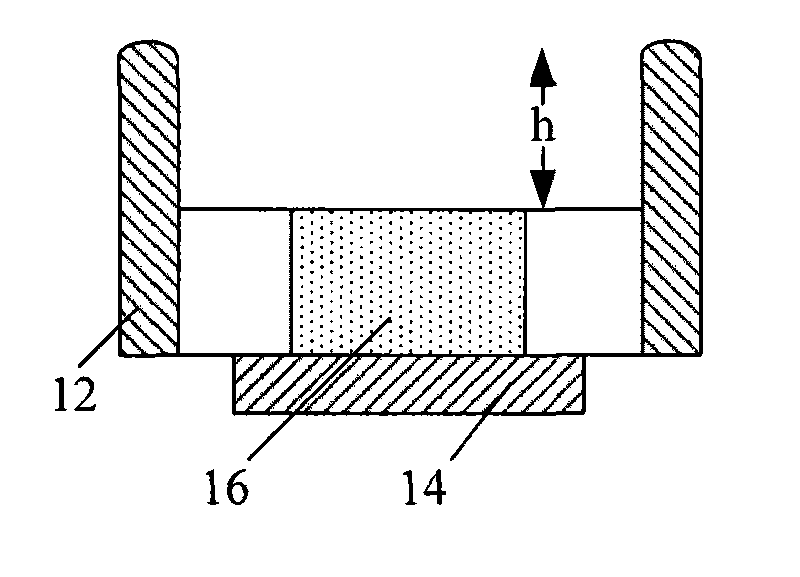

[0017] An embodiment of the present invention provides a chip. The chip includes a plurality of cells of the same shape that are seamlessly connected on a plane. On a plane, the shape of the gate dielectric layer of the cells is larger than the perimeter of the square when the area is the same. Shapes, such as: parallelograms, triangles, trapezoids and other shapes other than squares, these shapes have a perimeter greater than that of a square when they have the same area as a square. The shape of the cell grid dielectric layer 12 is as follows Figure 5 As shown, it is a parallelogram B with an angle between two adjacent sides of 45 degrees or 135 degrees, and the area of the square A parallelogram B is also a 2 , the side length of the square is 4a, and the parallelogram B has a pair of side lengths under the precondition of a, if the area is also a 2 , then the perimeter of the parallelogram B is about 4.828a. Under a certain process, the channel lengths of the square an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More