Transverse signal operation instruction (SOI) power device

A power device and lateral technology, applied in the field of SOI semiconductor power devices and SOI intelligent power integrated circuits, can solve the problems of increasing source contact resistance and decreasing effective channel width, and achieves higher breakdown voltage and higher off-state. Withstand voltage and suppress the effect of floating body effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

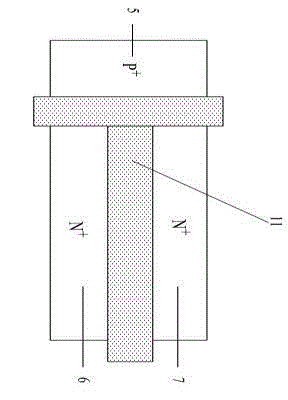

[0056] image 3 It is a horizontal SOI LDMOS structure diagram with a floating conventional n-type body region for comparison;

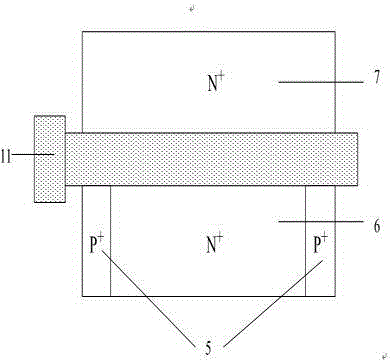

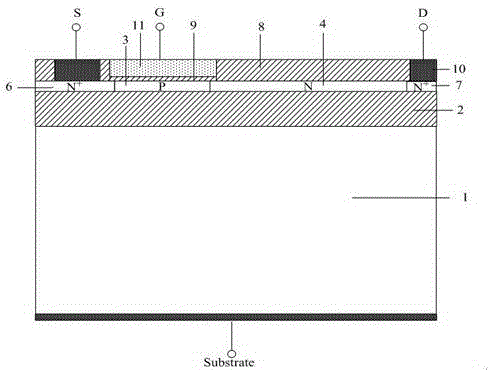

[0057] Figure 4 It is a schematic diagram of a lateral N-channel SOI LDMOS structure proposed by the present invention, in which the body region is drawn out through a silicon window.

[0058] Figure 4 The lateral N-channel SOI LDMOS structure in which the middle body region is drawn out through a silicon window includes: a semiconductor substrate 1 , an insulating dielectric layer 2 disposed on the semiconductor substrate 1 and a semiconductor active layer above the insulating dielectric layer 2 . The semiconductor substrate 1 , insulating dielectric layer 2 , and semiconductor active layer constitute SOI material, and a silicon window 13 is provided in the insulating dielectric layer 2 .

[0059] There are P-type body regions and N on the surface of the semiconductor active layer + drain region, the P-type body region and the N + There is a...

Embodiment 2

[0066] The structure of the semiconductor device of the present invention is described above by taking the lateral SOI LDMOS structure in which the N-channel body region is drawn out through the silicon window as an example, and the structure of the present invention is also applicable to the P-channel lateral SOI LDMOS. Such as Figure 5 shown in the lateral SOI LDMOS with Figure 4 The structure of the lateral SOI LDMOS corresponds to that, only the N-channel SOI LDMOS in Figure 4 is changed to the P-channel SOI LDMOS, so the conductivity type of each semiconductor region changes accordingly. In order to prevent the formation of a current path between the source and the substrate, only A P-type substrate can be used. However, the P-channel SOI LDMOS of the present invention is not suitable for integration with low-voltage SOI CMOS devices.

Embodiment 3

[0068]The structure of the semiconductor device of the present invention is described above by taking the lateral SOI LDMOS structure whose body region is drawn out through the silicon window as an example, and the structure of the present invention is also applicable to the lateral SOI LIGBT structure. Such as Figure 6 The lateral SOI IGBT structure shown with Figure 4 corresponding to the structure of the lateral SOI LDMOS, simply by Figure 4 The N-channel SOI LDMOS becomes an N-channel SOI LIGBT, so the conductivity type of the drain 7 changes accordingly. The N-channel SOI LIGBT of the invention can be well integrated with N-channel SOI LDMOS and low-voltage SOI CMOS devices on the same chip. P-channel SOI IGBT, like P-channel SOI LDMOS, is not suitable for integration with low-voltage SOI CMOS devices.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More