Silicon on insulator-lateral insulated gate bipolar transistor (SOI-LIGBT) device structure with low switch-off loss and dual groove gates

A technology of turn-off loss and device structure, used in semiconductor devices, electrical components, circuits, etc., can solve the problems of unsatisfactory turn-off loss effect and very high process requirements, and achieve uniform carrier distribution and carrier recombination. Reduced, turn-off loss reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

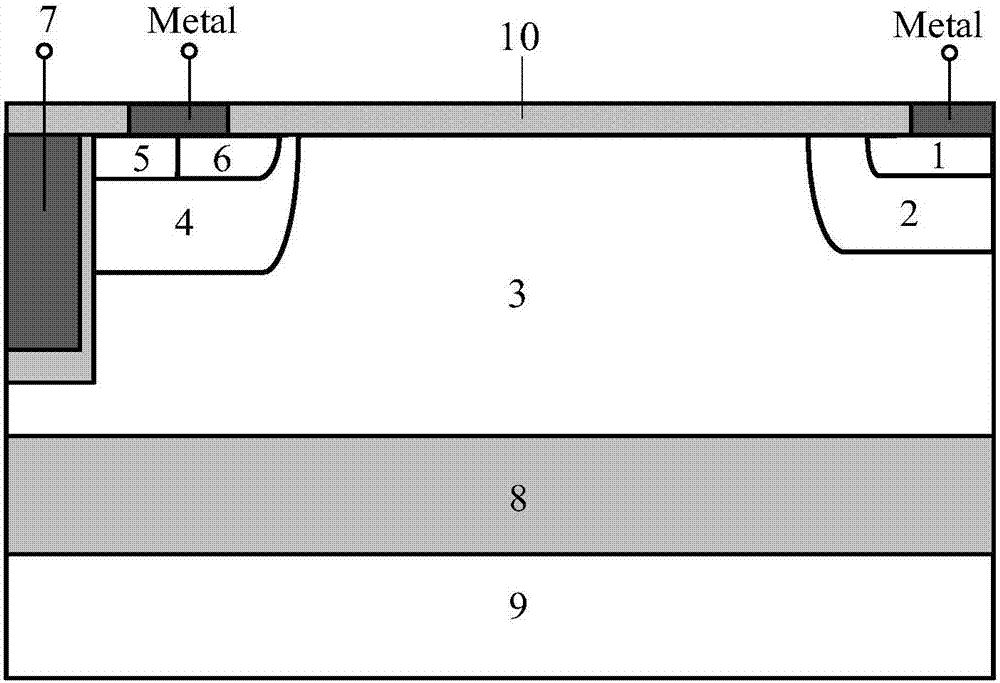

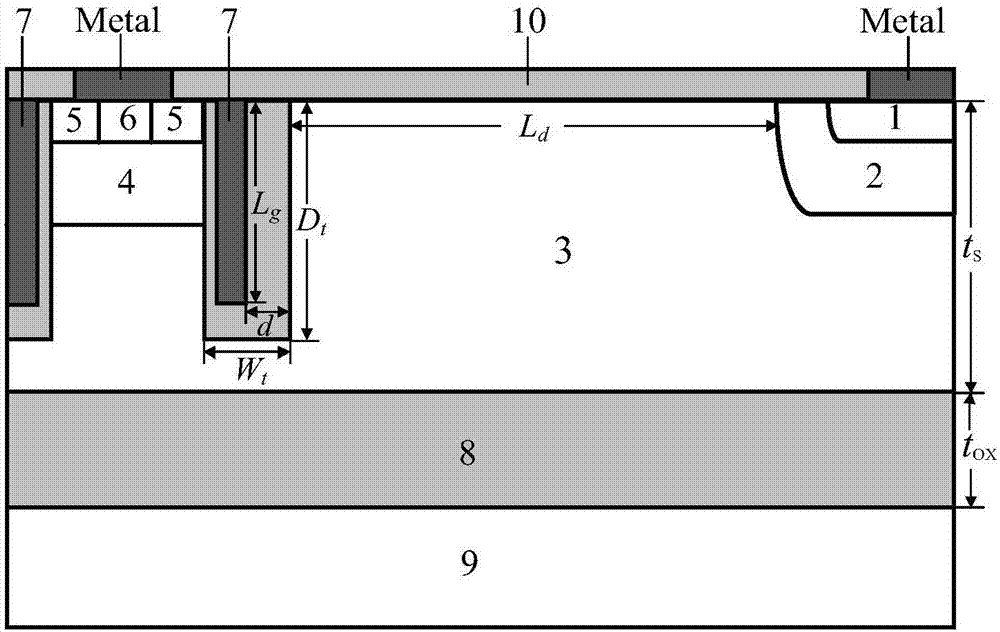

[0024] Such as figure 2 As shown, a low turn-off loss double-groove gate SOI-LIGBT device structure includes a P-type substrate 9, a buried oxide layer of silicon dioxide 8, an N-type drift region 3, and an N-type drift region 3 arranged in sequence from bottom to top. One end of the interior is provided with a P-type well region 4, the other end is provided with an N-buffer layer 2, and the surface of the device is provided with an oxide layer 10. The interior of the P-type well region 4 is provided with two N-type source terminals 5 and two N-buffer layers. The P-type contact region 6 between the source terminals 5; the N-type anode region 1 is provided above the inside of the N-buffer layer 2; the N-type source terminal 5, the P-type contact region 6 and the N-type anode region 1 are above A metal layer is provided; the left and right sides of the channel between the source end 5 and the P-type well region 4 are gate oxide layers, and polysilicon 7 is arranged next to the ...

Embodiment 2

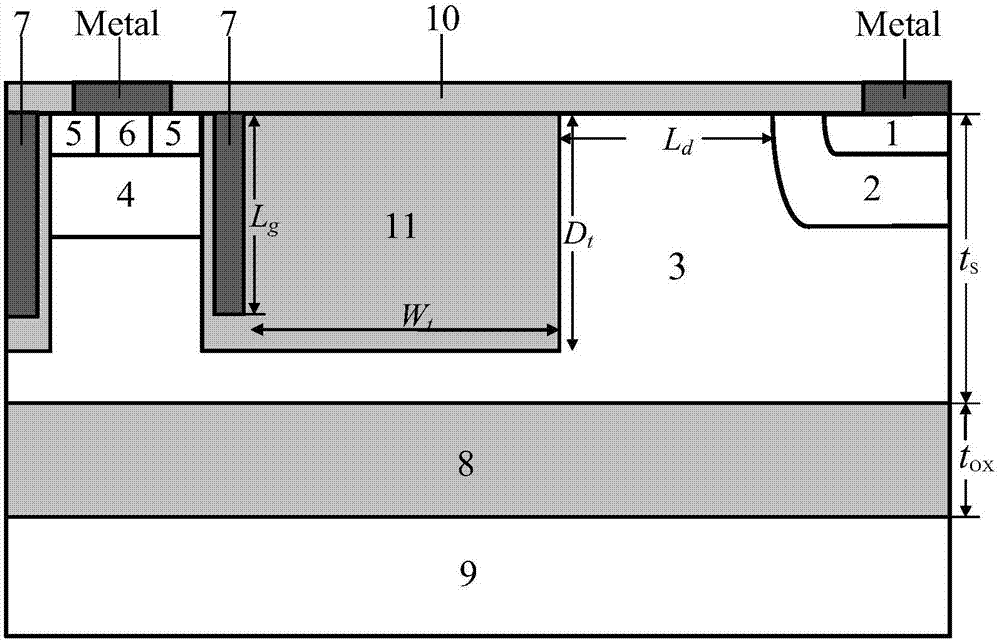

[0030] Such as image 3 As shown, the low turn-off loss double-groove gate SOI-LIGBT device structure of this embodiment is basically the same as that of Embodiment 1, the difference lies in: the inside of the N-type drift region 3 between the P-type well region 4 and the N-buffer layer 2 A silicon dioxide tank dielectric 11 is provided; the silicon dioxide tank dielectric 11 is located on the right side of the polysilicon 7 on the right side of the P-type well region 4 .

[0031] The minimum value of the width Wt of the silicon dioxide groove medium 11 is 1 μm.

[0032] Preferably, the right side of the silicon dioxide trough medium 11 may be in contact with the left side of the N-buffer layer 2 , that is, Ld is zero.

[0033] The depth of the silicon dioxide groove medium 11 is Dt, which is greater than the depth Lg of the polysilicon 7, and satisfies the thickness of the silicon layer, that is, the thickness t of the N-type drift region 3 s >D t ≥ L g +1um.

[0034] Sp...

Embodiment 3

[0039] Such as Figure 7 As shown, the low turn-off loss double-groove gate SOI-LIGBT device structure of this embodiment is basically the same as that of Embodiment 2, the difference is that an N-type carrier storage layer 12 is provided under the P-type well region 4 . Depth L of two polysilicon 7 g equal to and greater than the depth D of the N-type carrier storage layer 12 cs .

[0040] Specifically, the thickness t of the buried oxide silicon dioxide 8 ox is 3 μm, the thickness of the silicon layer is also the thickness t of the N-type drift region 3 s 4μm, the length L of the N-type drift region 3 d 13μm, doping concentration N d 2.5e15cm -3 , the gate oxide thickness is 20nm, the doping concentration N of the P-type well region 4 pwell 4e17cm -3 , the doping concentration of the N-type carrier storage layer 12 is 1e18cm -3 , the doping concentration of N-buffer layer 2 is 4e17cm -3 , polysilicon depth L g is 2.2 μm, the depth D of the silica groove dielectric...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More