Lateral trench insulated gate bipolar translator (IGBT) having self-biased positive channel metal oxide semiconductor (PMOS) and its preparation method

A lateral groove and self-bias technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing conduction voltage drop, slow turn-off speed, large turn-off loss, etc., and achieves reduction On-voltage drop, increased blocking voltage, and easy-to-drive effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

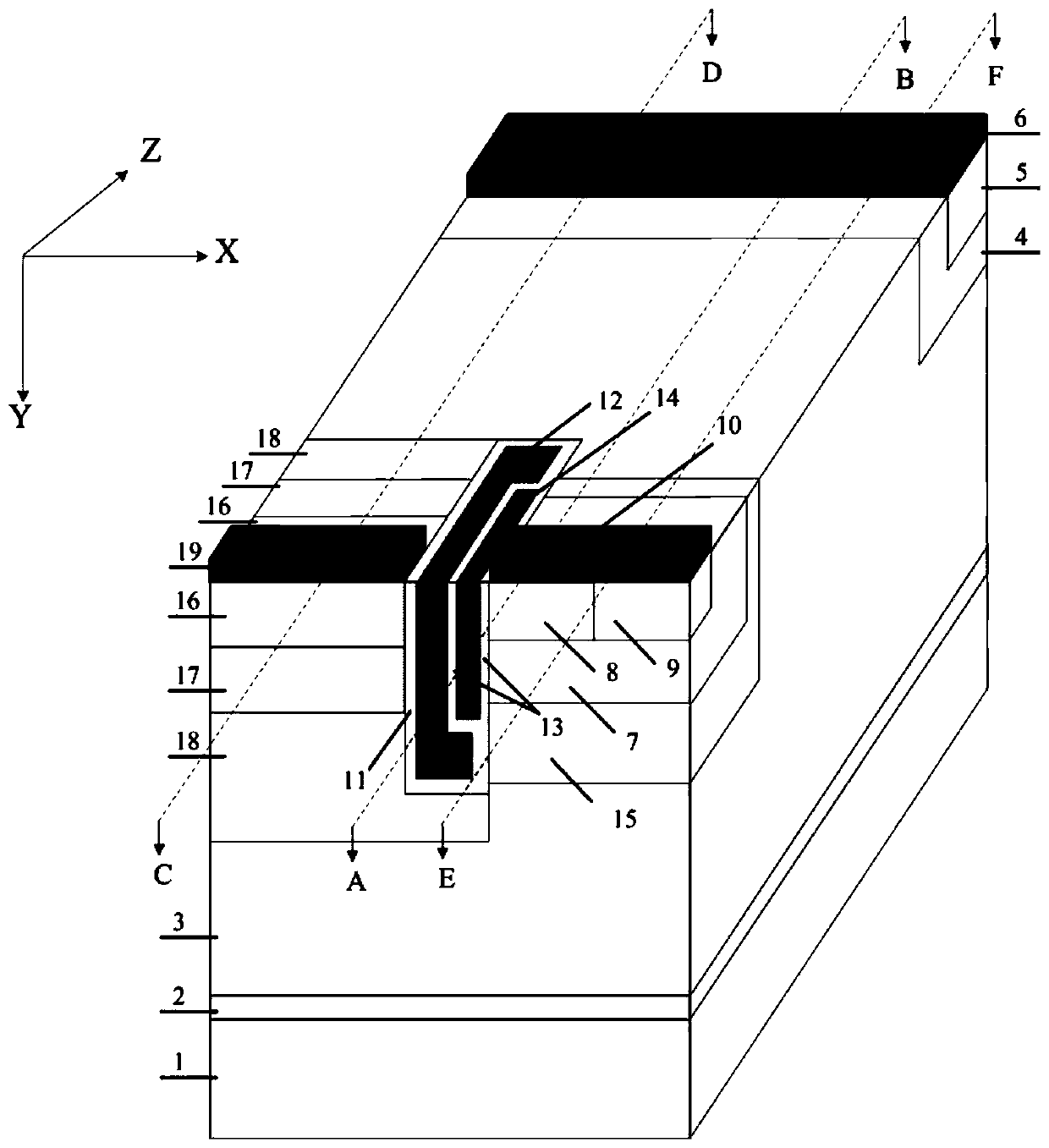

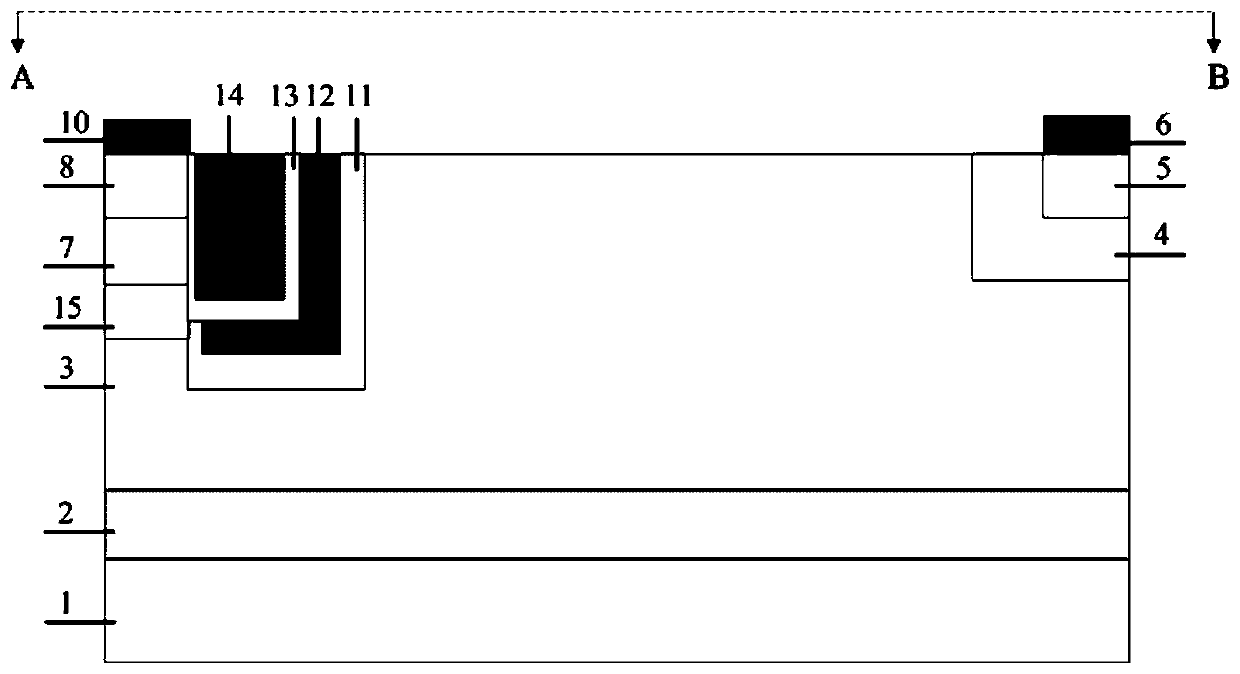

[0062] This embodiment provides a lateral insulated gate bipolar transistor whose half-cell structure is as follows figure 2 As shown, the two-dimensional cross-sectional structures obtained along the dotted line AB and dotted line CD in the semi-cellular structure are as follows image 3 and Figure 4shown. This embodiment includes a P-type substrate 1, a silicon dioxide isolation layer 2, and an N-type drift region 3 arranged in sequence from bottom to top; an N-type buffer zone 4 is arranged on one side of the top layer of the N-type drift region 3 in the longitudinal direction, so The longitudinal direction is the third dimension perpendicular to the horizontal and vertical directions of the device; the N-type buffer zone 4 is provided with an N-type collector region 5, and the upper surface of the N-type collector region 5 is provided with a first metallized collector 6; in the N-type drift region 3, the top of the side away from the N-type buffer zone 4 in the longitu...

Embodiment 2

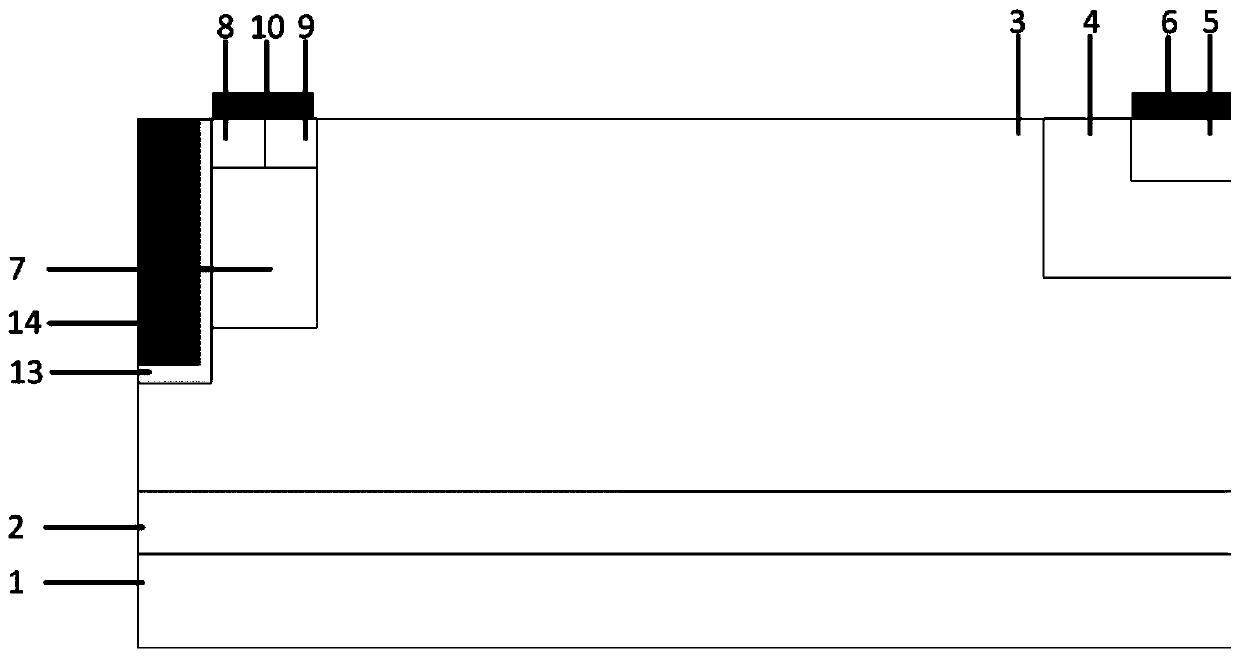

[0071] This embodiment provides a lateral insulated gate bipolar transistor, the half-cell structure of which is as follows Figure 5 shown. In this embodiment, on the basis of Embodiment 1, a third gate oxide layer 131 is provided on the upper surface of the P-type base region 8, and the third gate oxide layer 131 extends vertically above the N-type charge storage region 15; the third gate oxide layer A second polysilicon gate electrode 141 is disposed over layer 131 .

[0072] In particular, the horizontal direction of the third gate oxide layer 131 and the second polysilicon gate electrode 141 may be in contact with the border of the right half cell or the border of the N-type emitter region 8 .

[0073] In particular, a surface channel may be formed on the surface of the device under the second polysilicon gate electrode 141 when the device is turned on.

[0074] Compared with Embodiment 1, due to the existence of the third gate oxide layer 131 and the second polysilicon...

Embodiment 3

[0076] This embodiment provides a lateral insulated gate bipolar transistor, the half-cell structure of which is as follows Image 6 shown. In this embodiment, on the basis of Embodiment 1, the second trench structure includes a first polysilicon gate electrode 14 and a second silicon dioxide layer disposed on the side wall and bottom wall of the first polysilicon gate electrode 14 13 is transferred to the longitudinal direction of the N-type emitter region 8 and the P-type emitter region 9, and the second silicon dioxide layer 13 is in contact with the N-type emitter region 8 and the P-type emitter region 9; the position of the original second trench structure is determined by the second The second polysilicon emitter 12 is filled with the first silicon dioxide layer 11 disposed on the side wall and the bottom wall of the second polysilicon emitter 12 .

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More