Patents

Literature

84results about How to "Enhanced conductance modulation effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

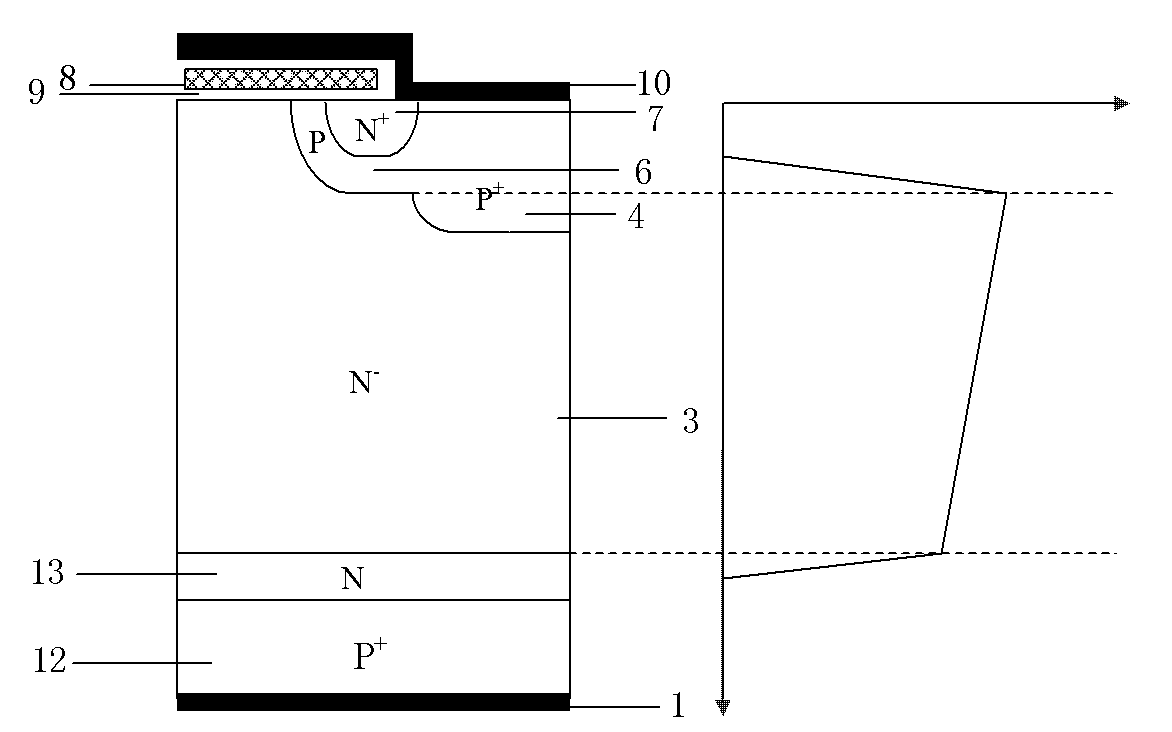

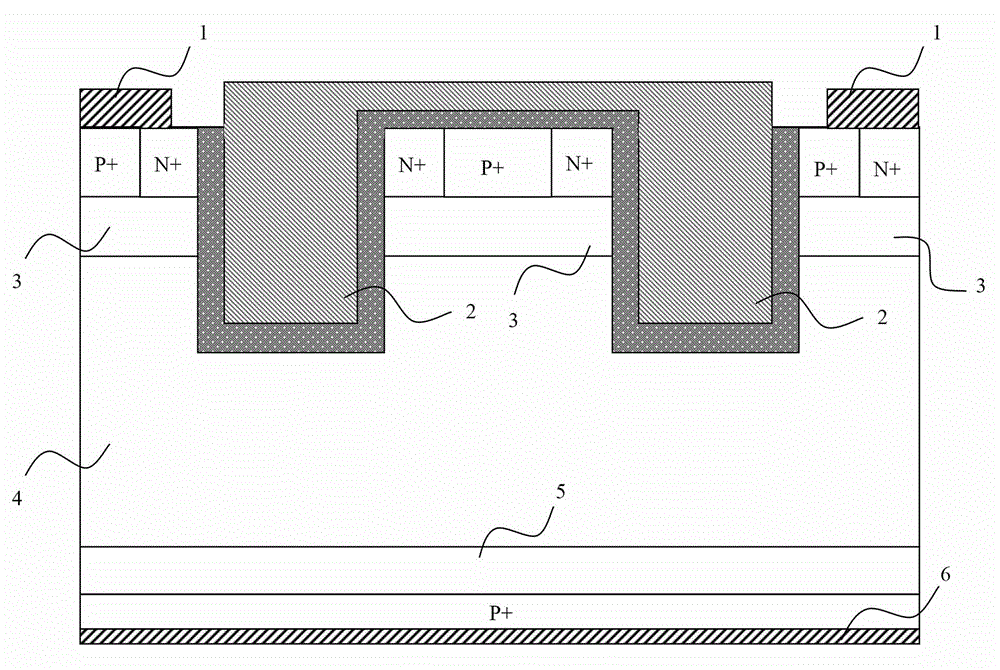

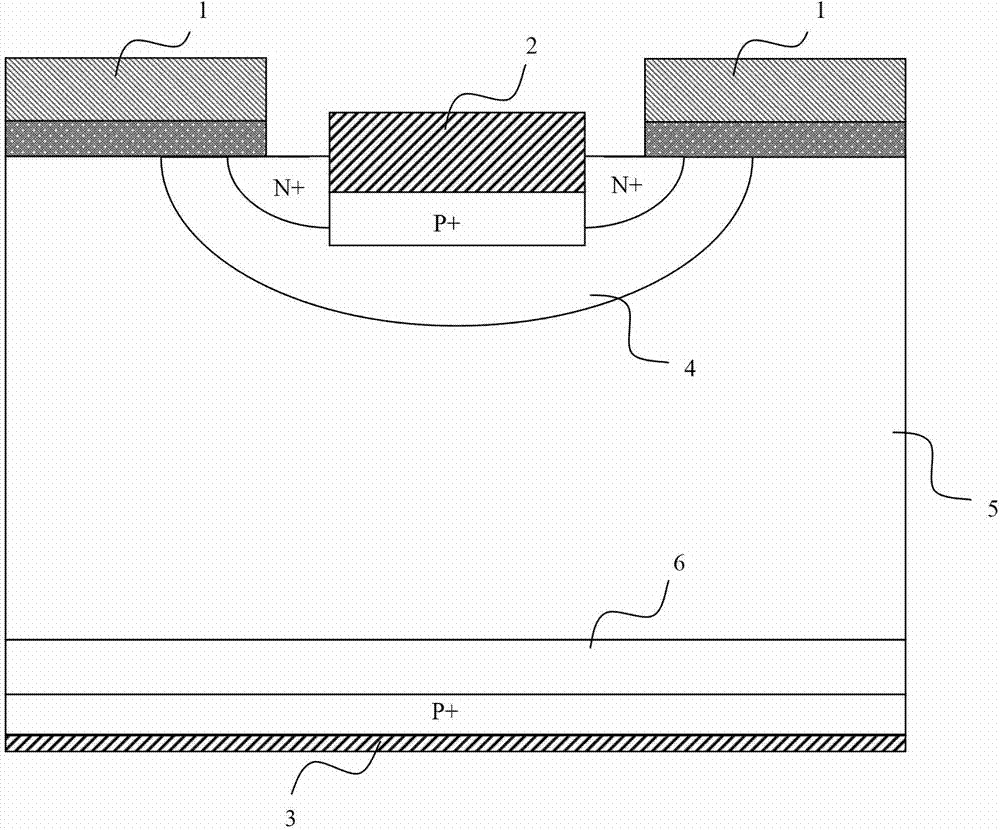

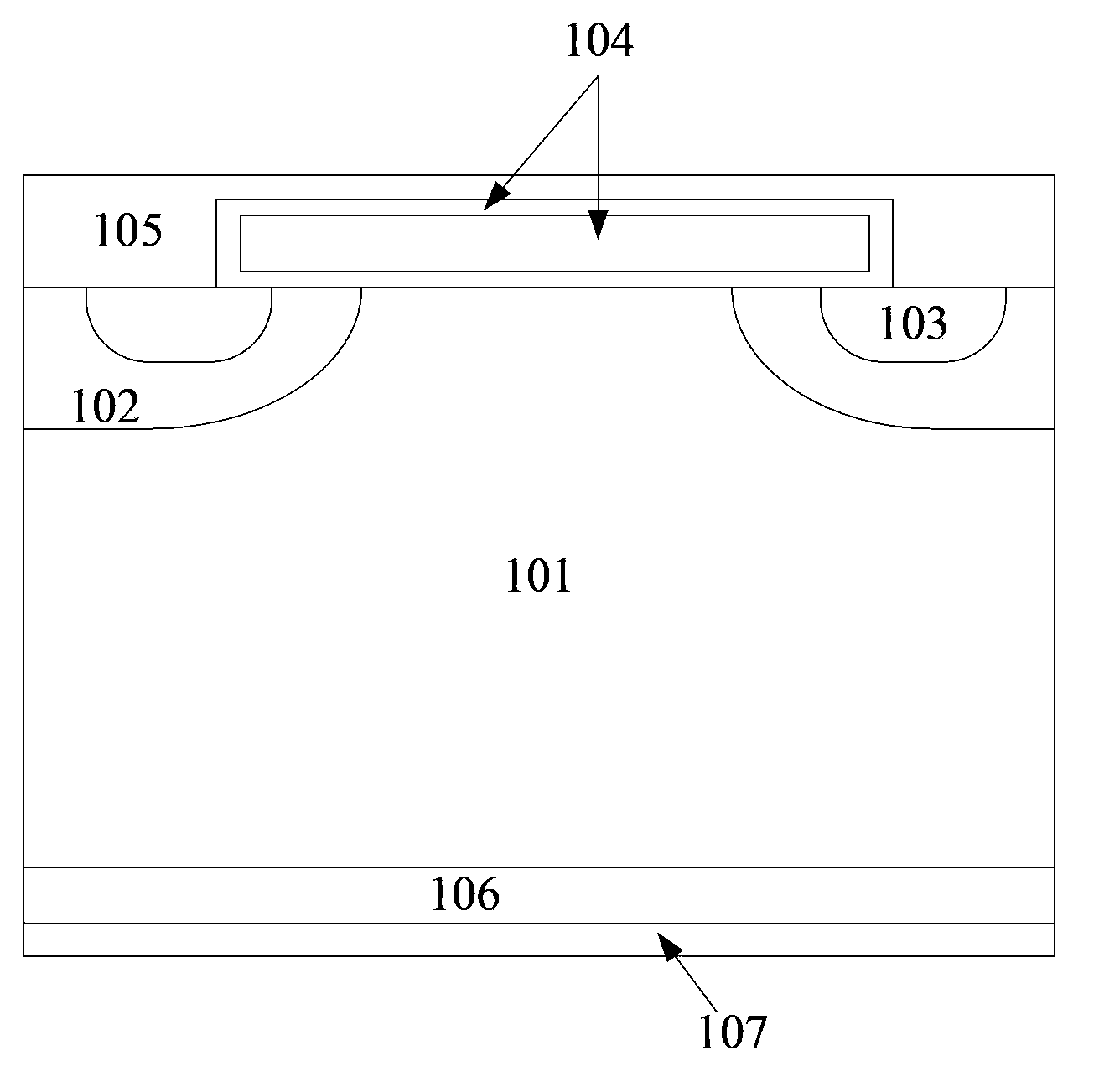

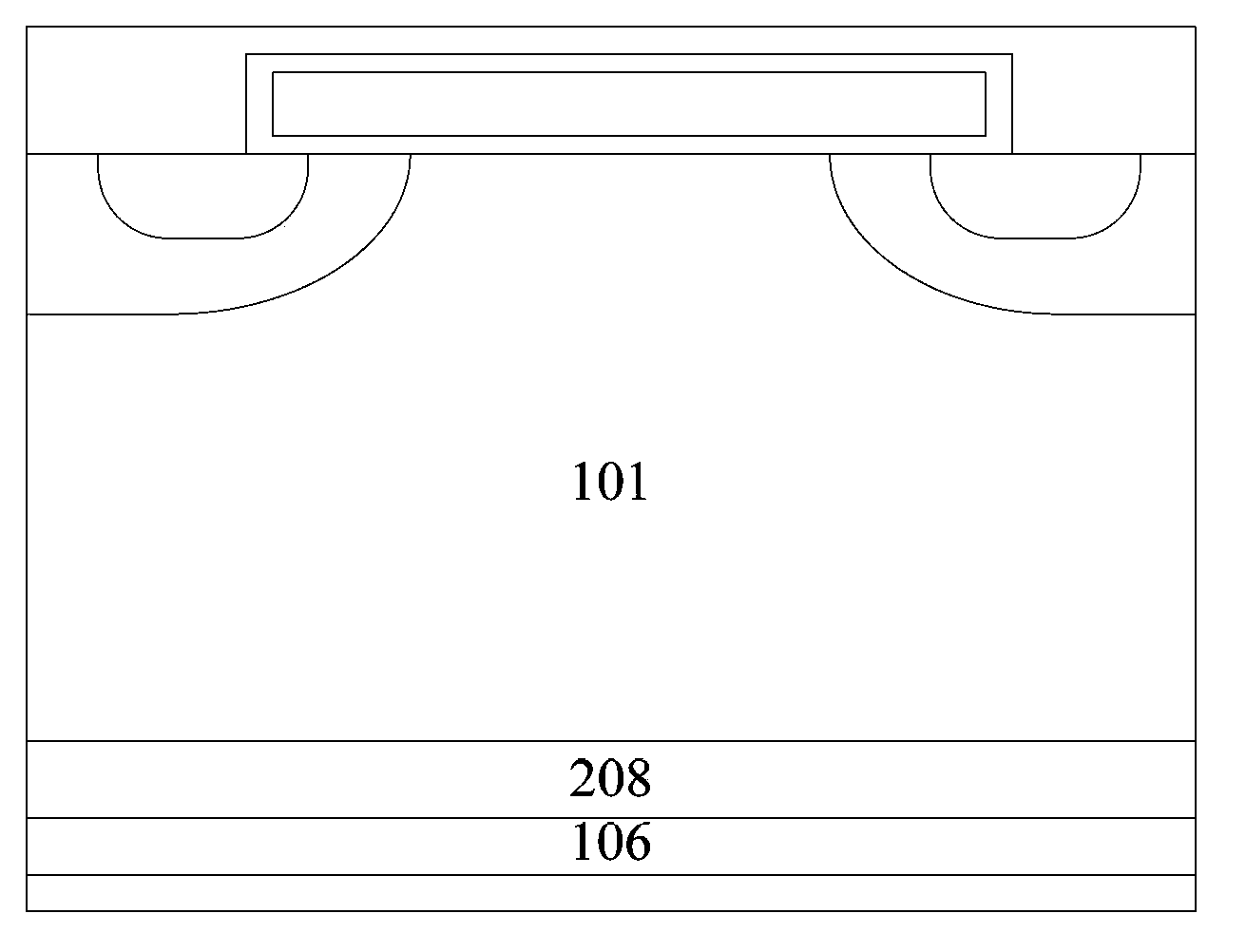

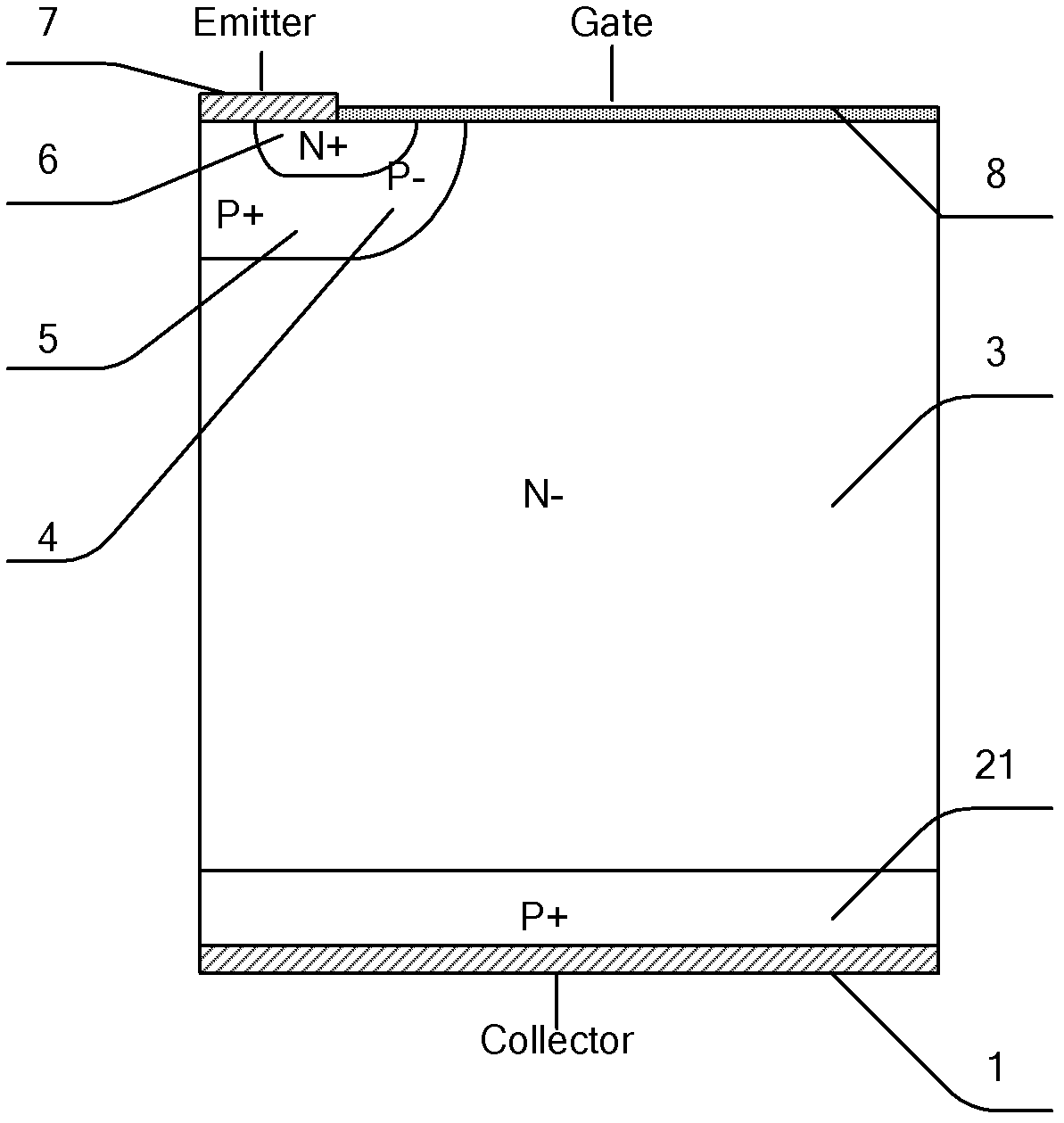

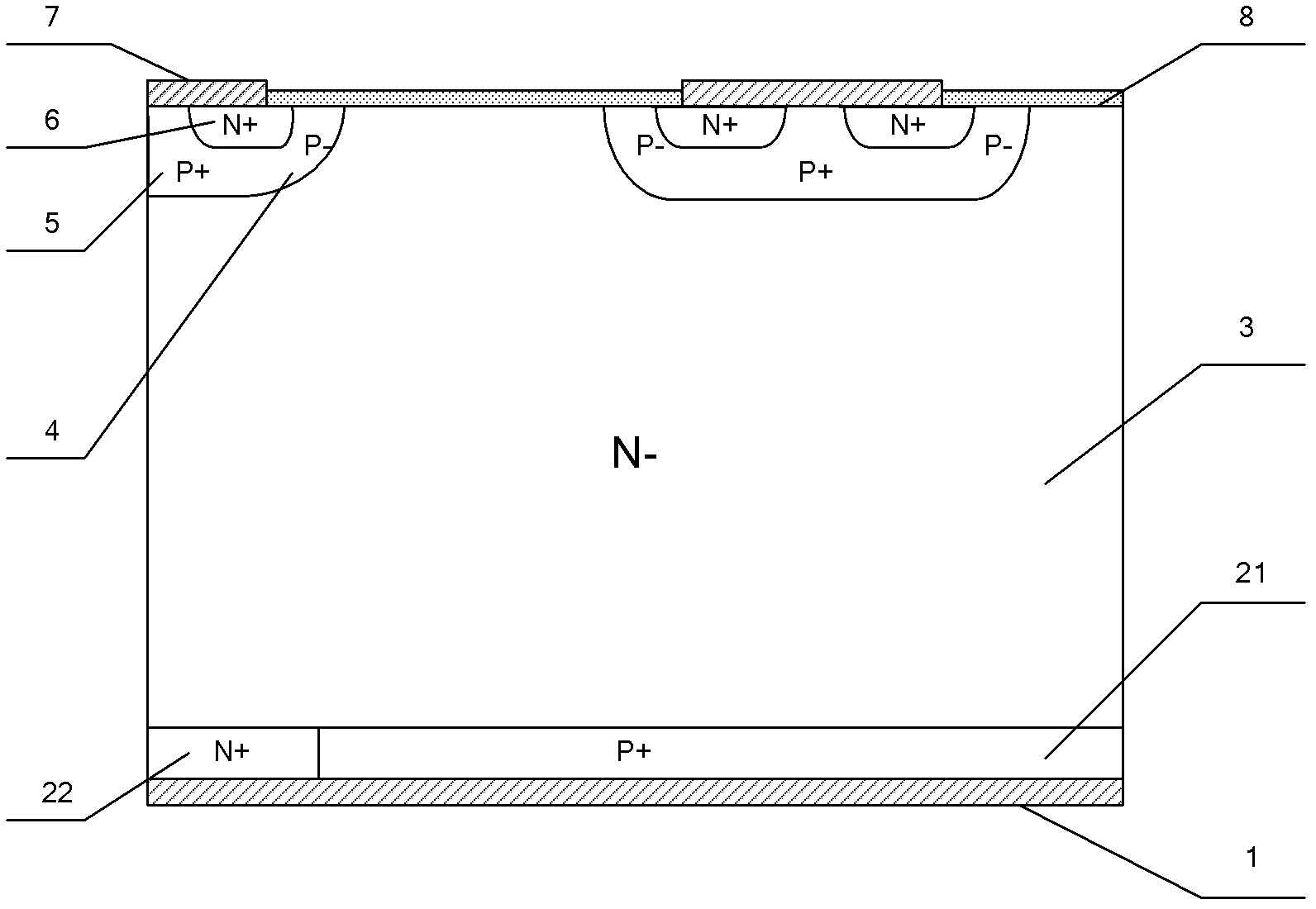

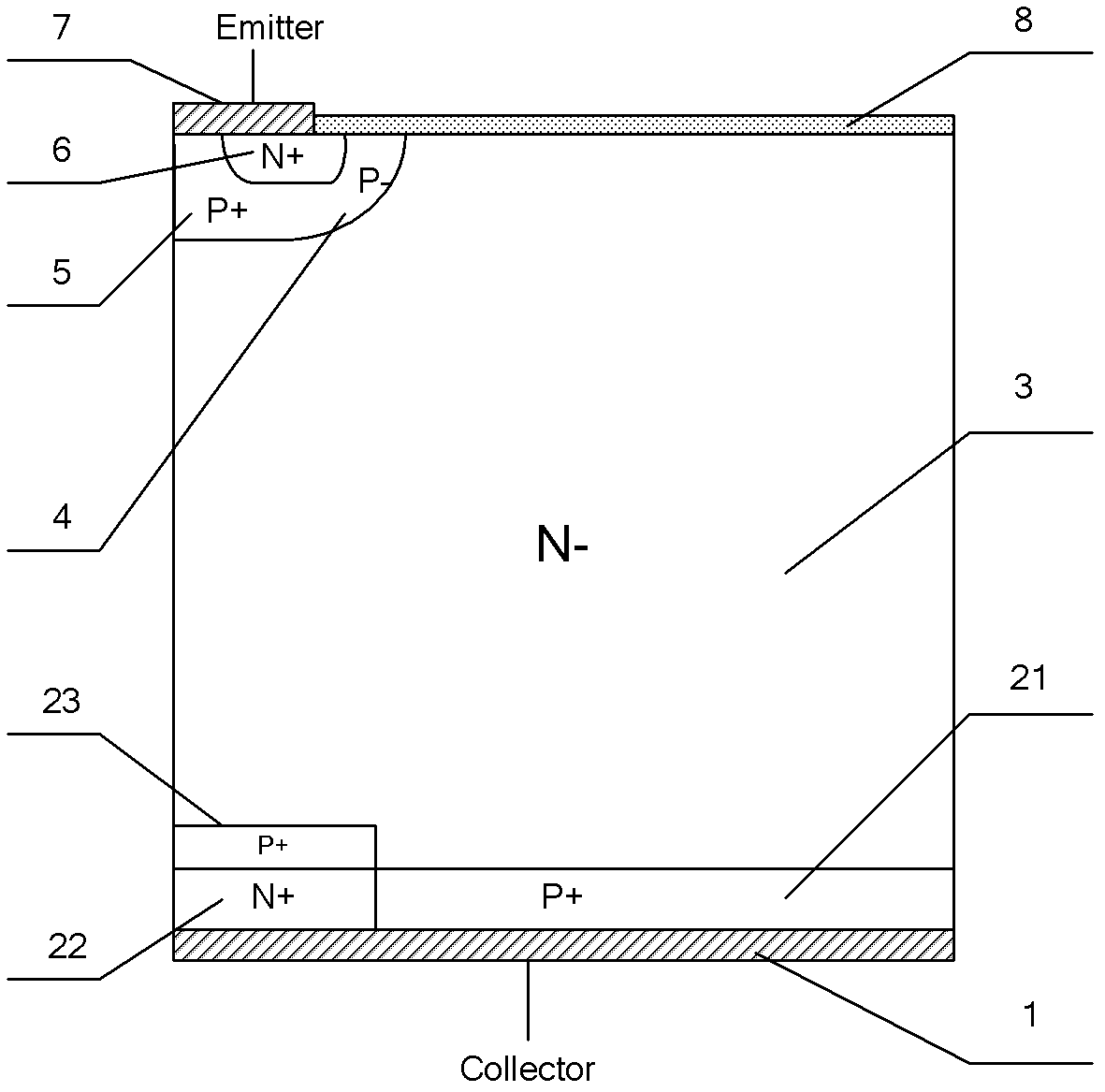

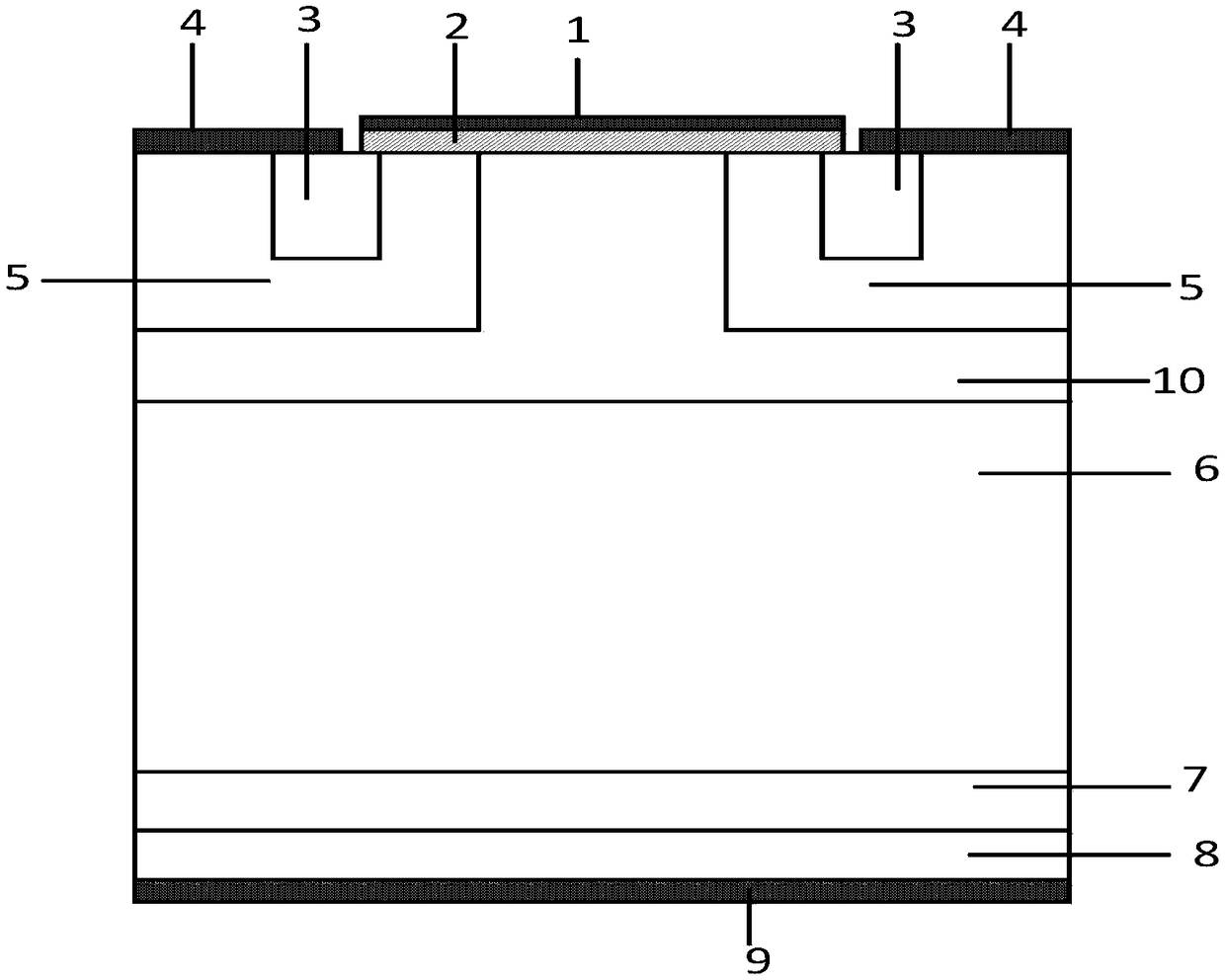

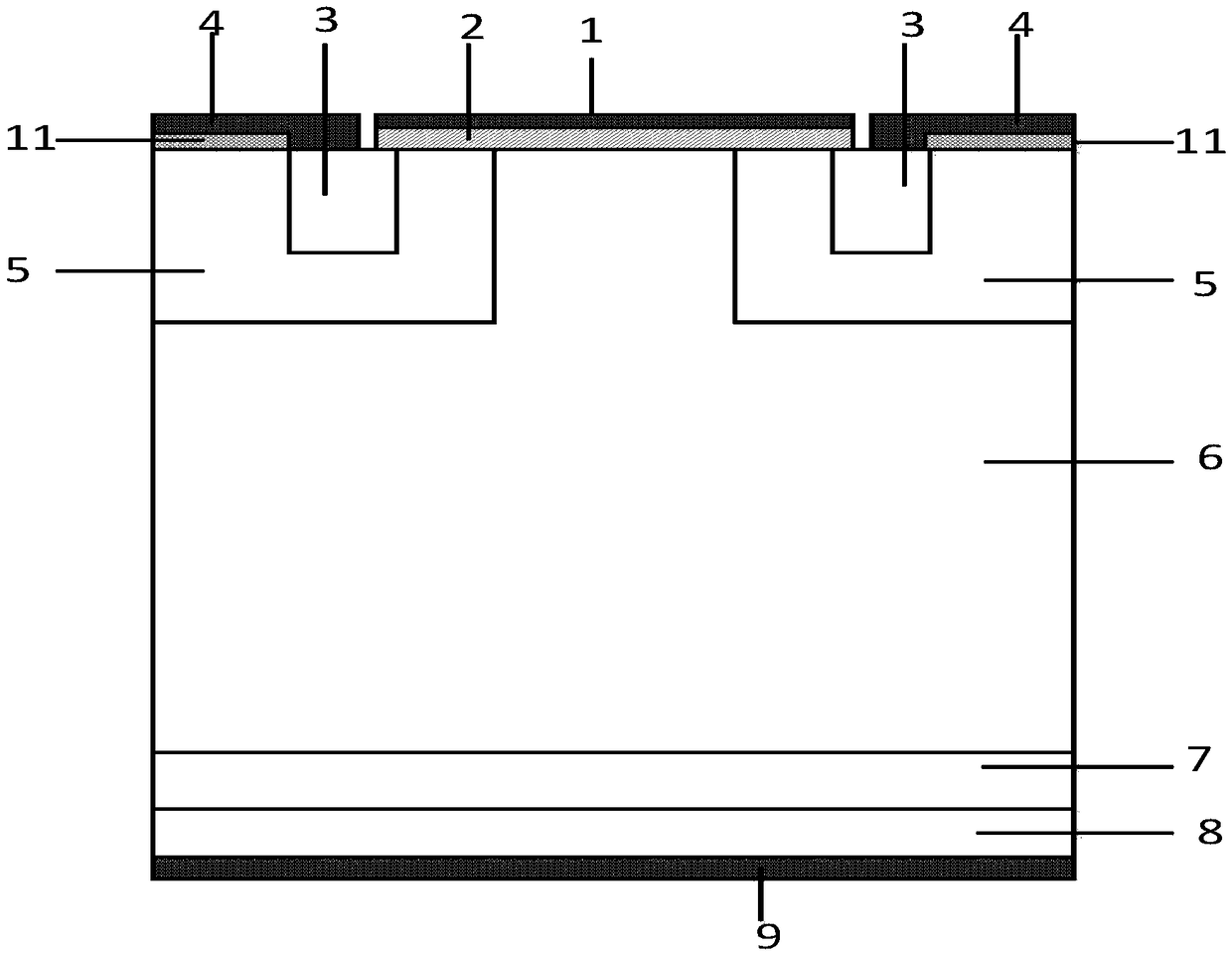

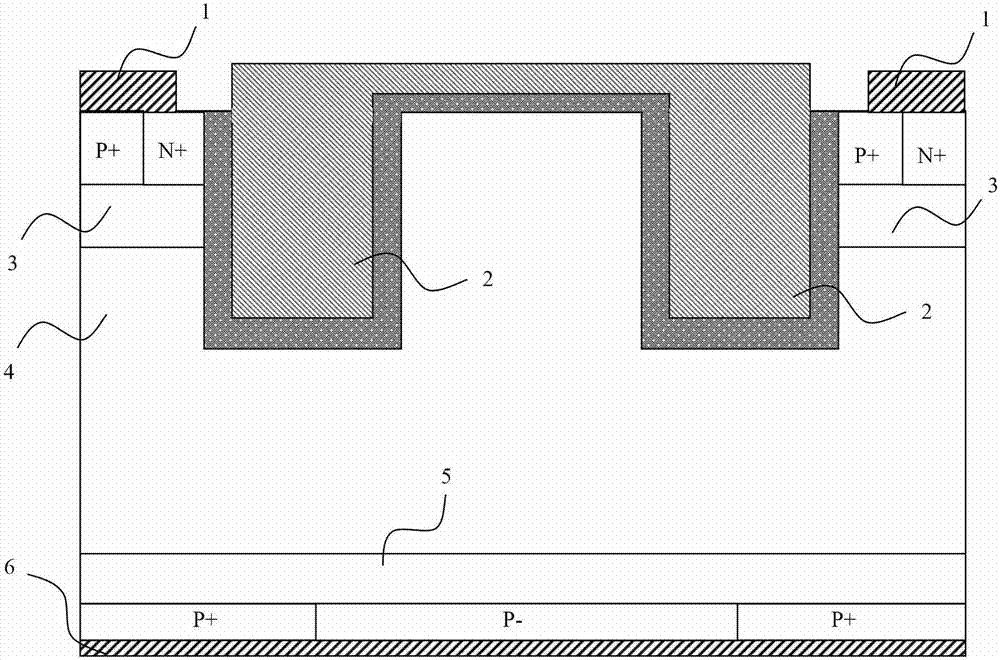

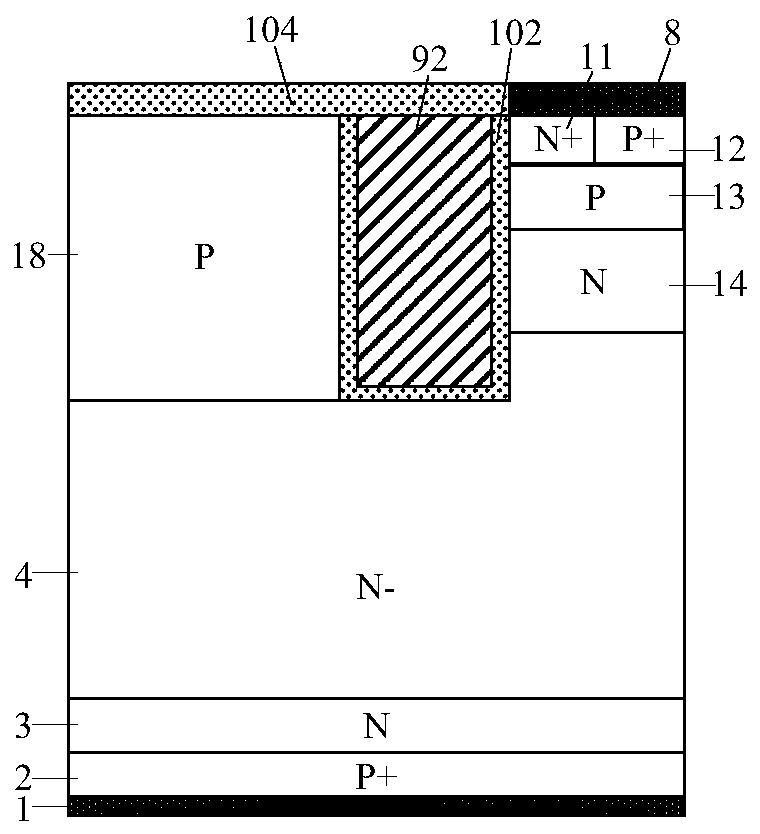

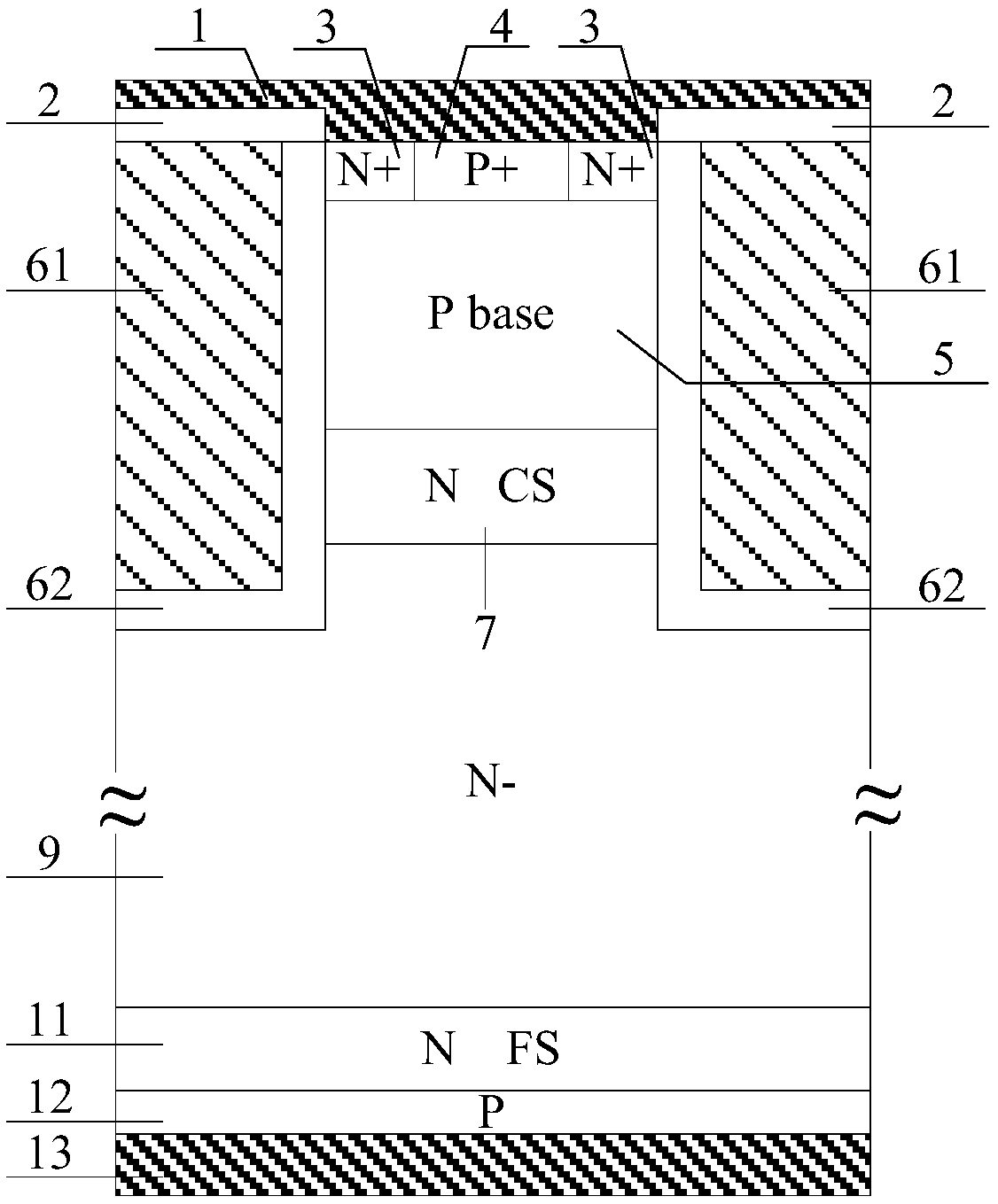

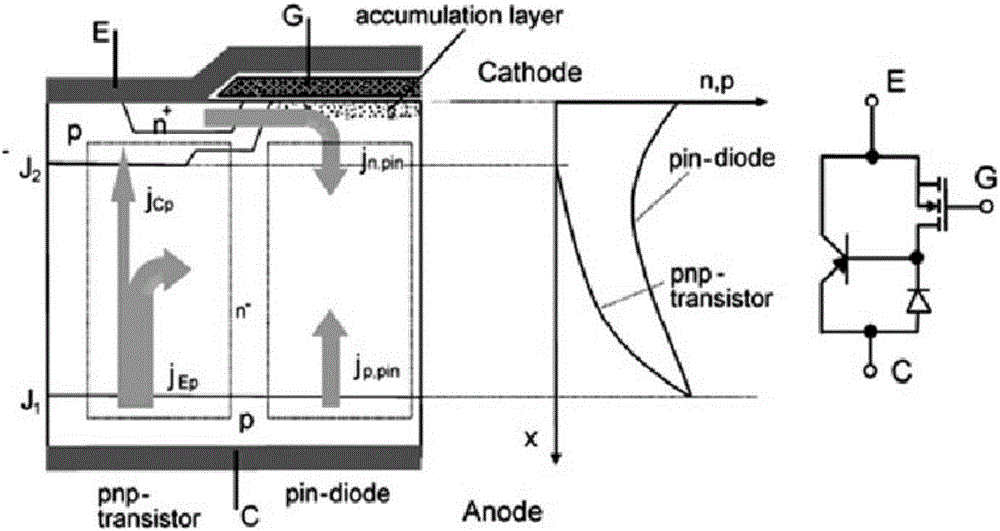

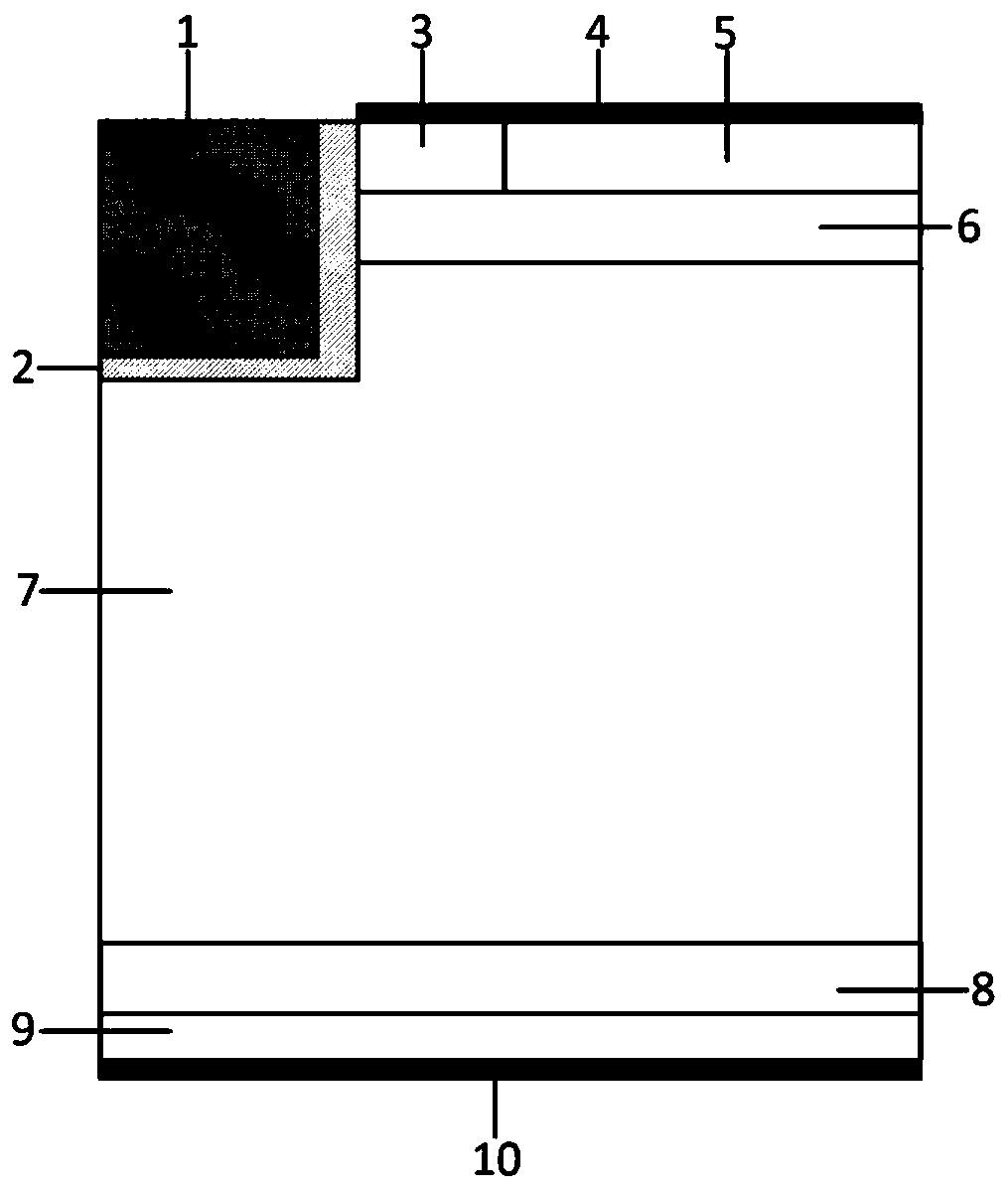

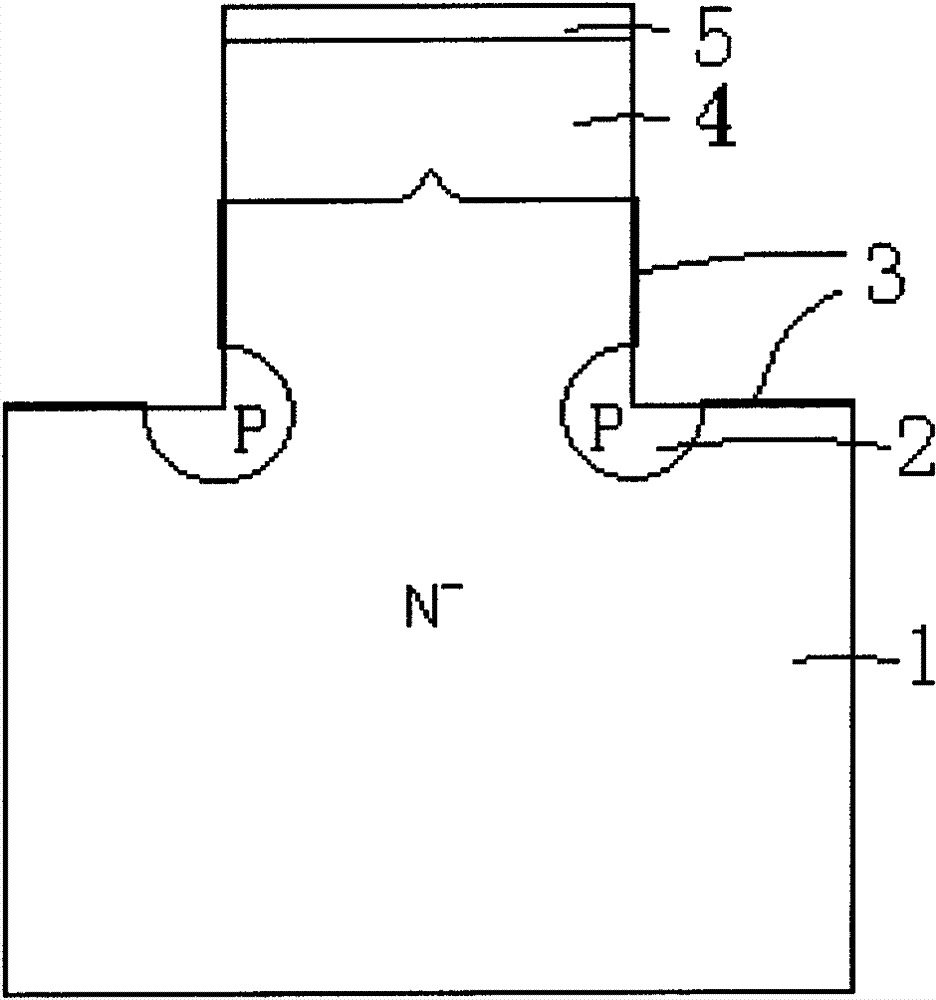

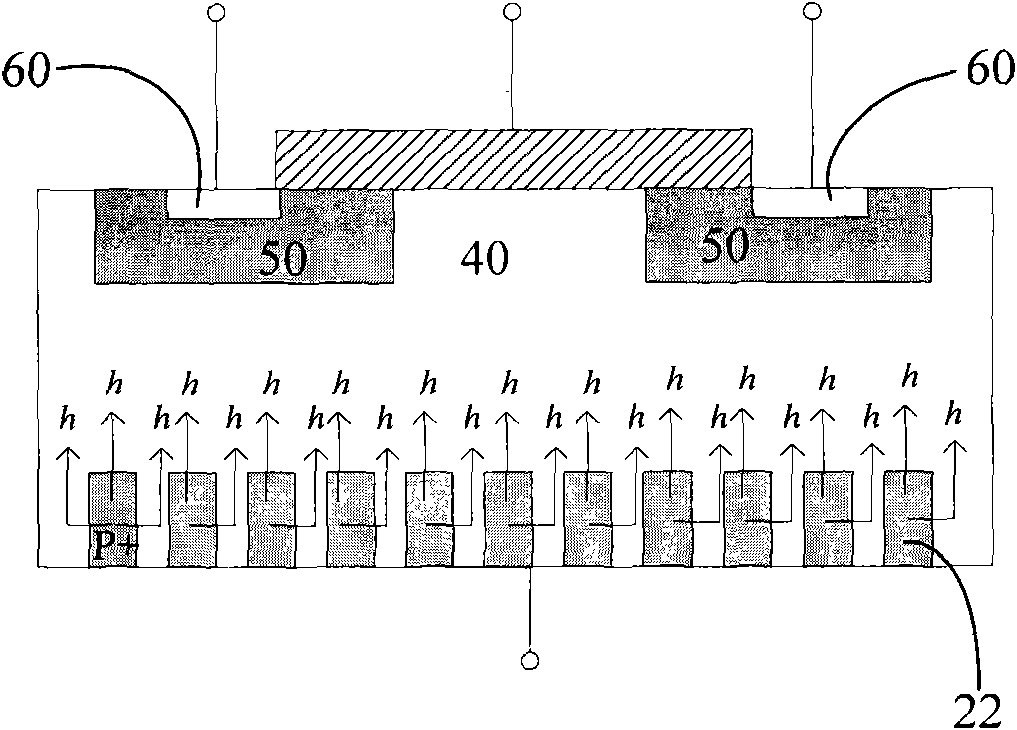

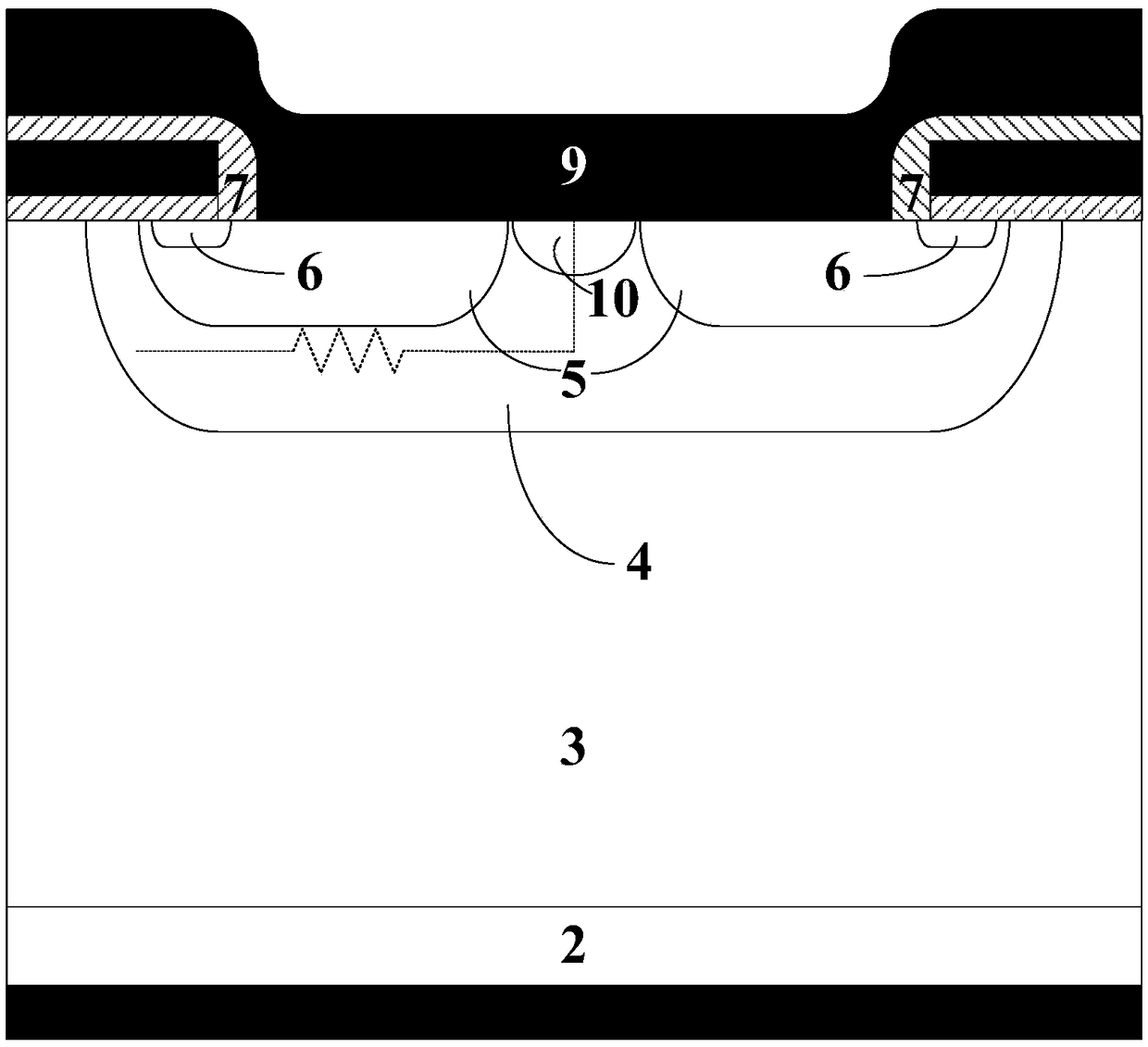

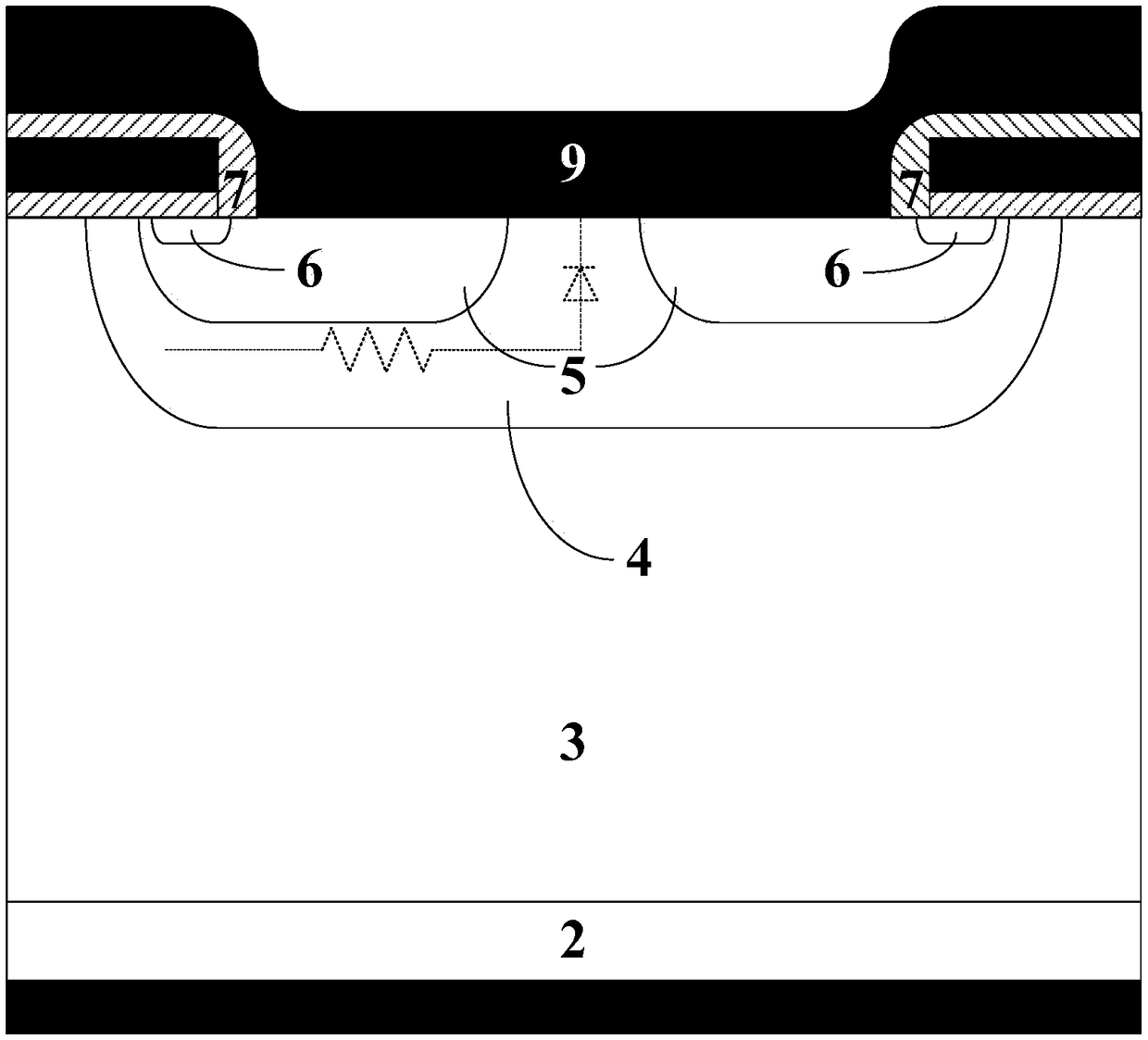

IGBT with current carrier storage layer and additional hole passage

InactiveCN102157551AIncrease the minority carrier concentrationPrevent openingSemiconductor devicesCharge carrierConductivity modulation

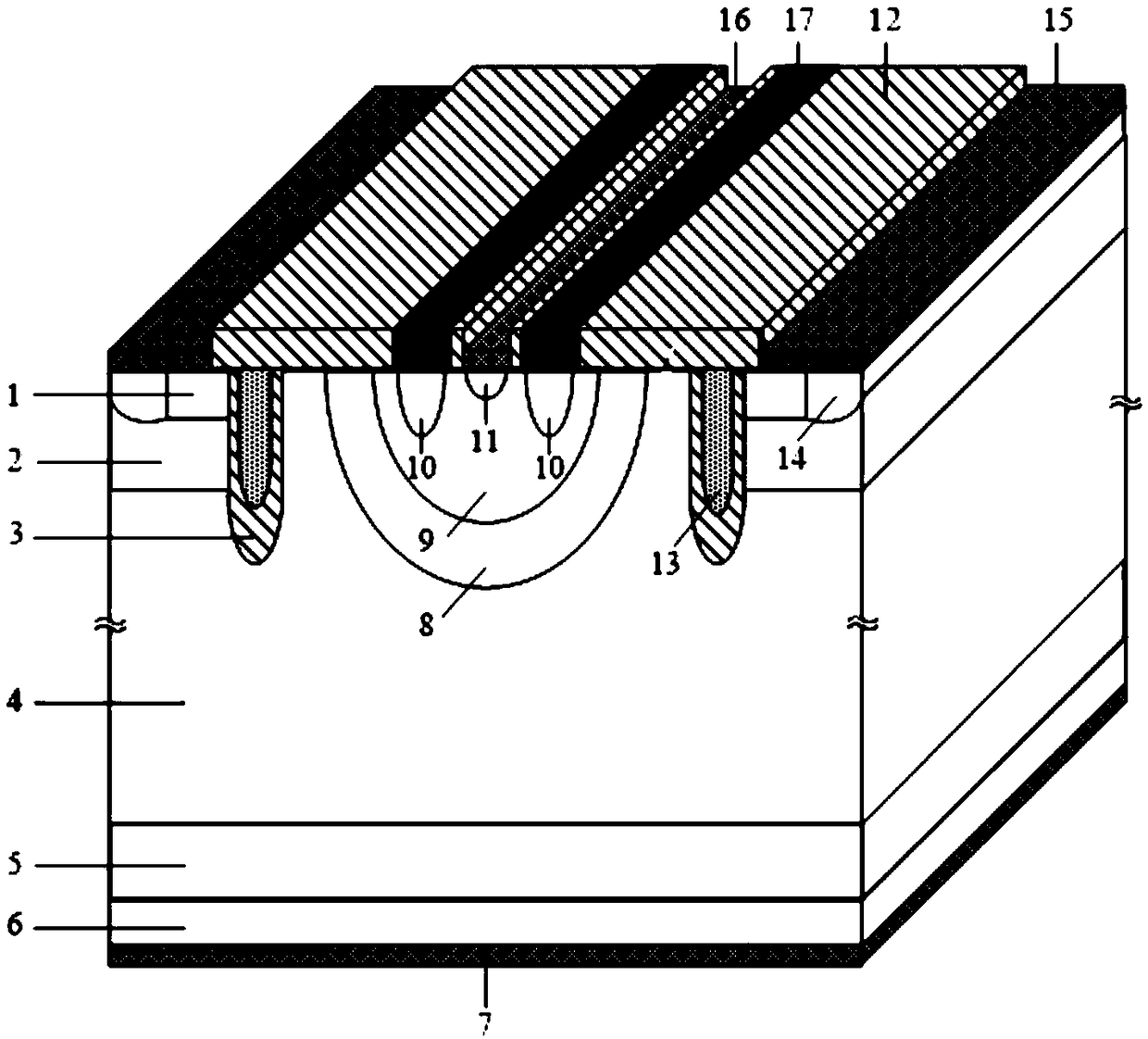

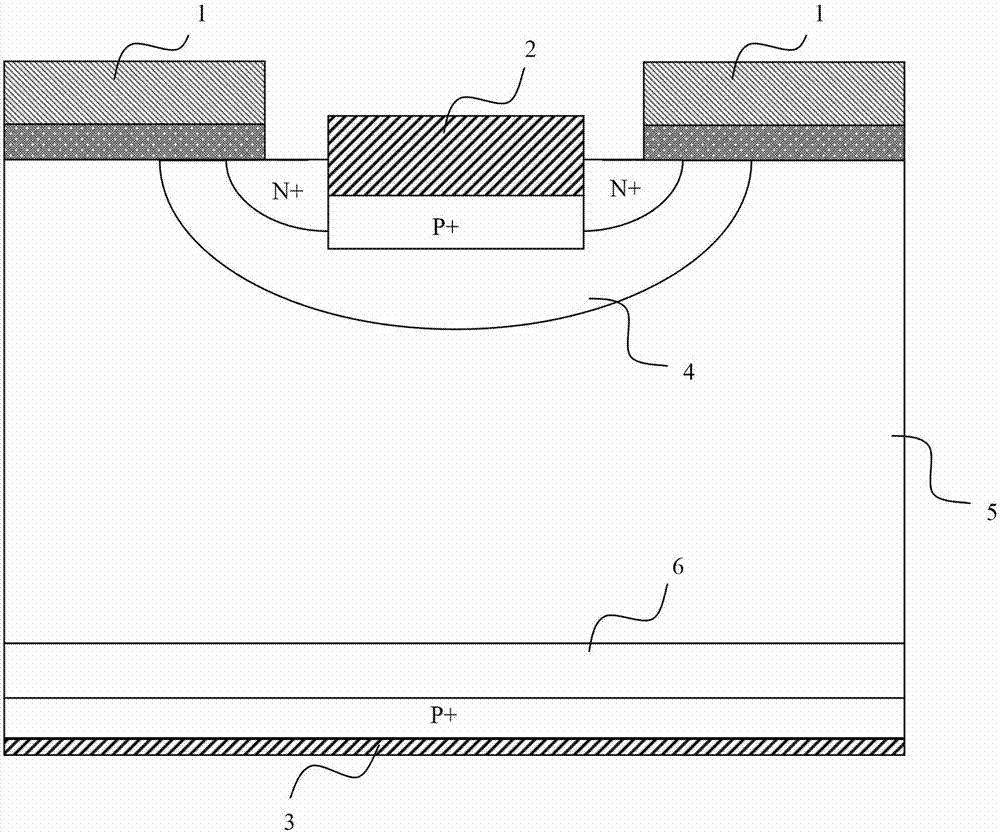

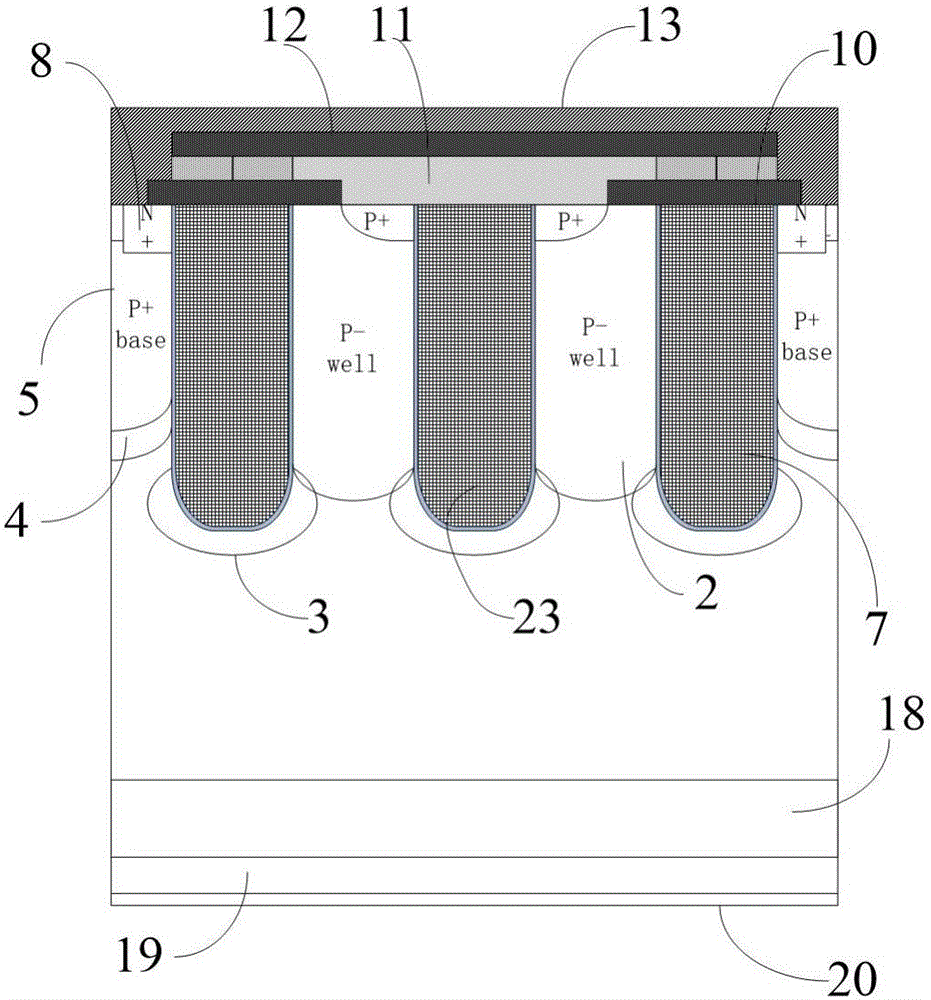

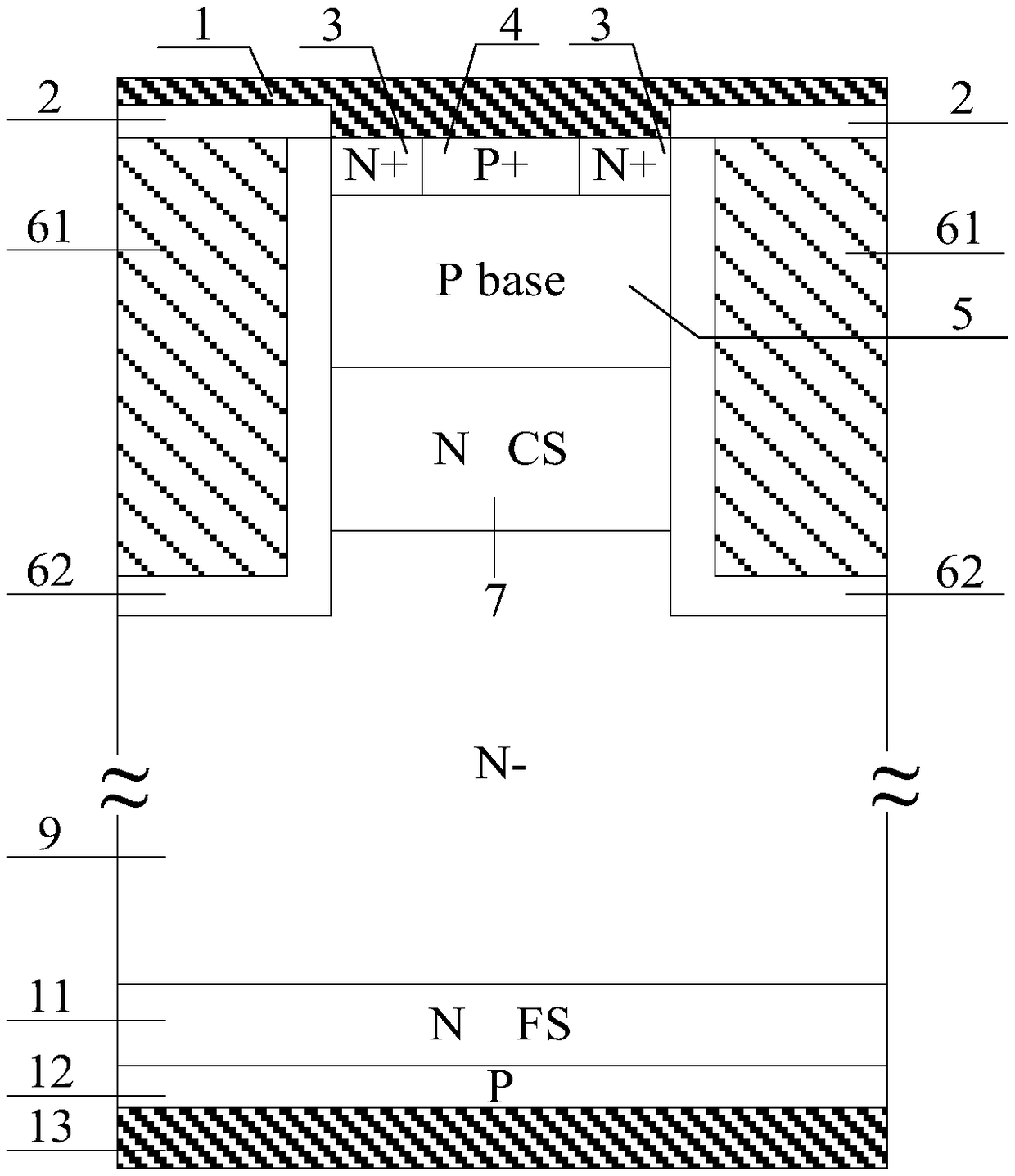

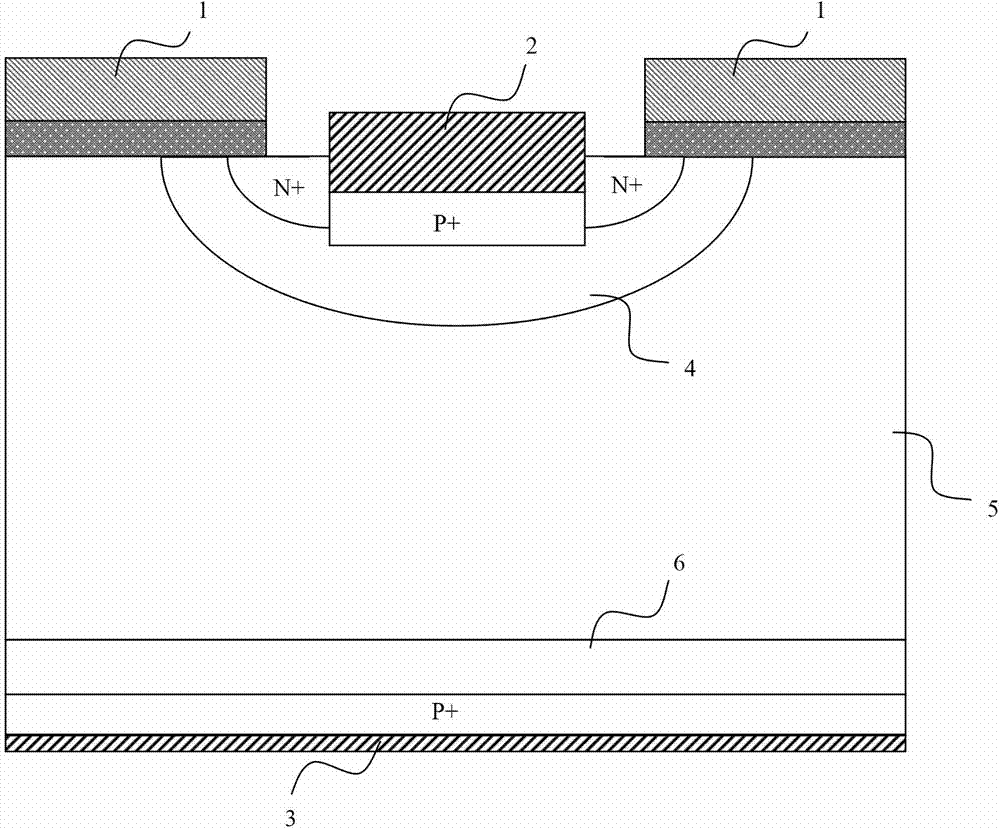

The invention discloses an insulate gate bipolar transistor (IGBT) with a current carrier storage layer and an additional hole passage, and belongs to the technical field of semiconductor power devices. In the IGBT, an N-type current carrier storage layer (5) and a large P<+> tagma (4) structure are introduced on the basis of a conventional planar non-pouch-through IGBT. The N-type current carrier storage layer (5) improves a conductivity modulation effect close to an emitter and the large P<+> tagma (4) structure plays a role in providing an additional passage for a hole so that the latch-up resistance is improved. Due to the design of the N-type current carrier storage layer (5) and the large P<+> tagma (4), the flow path of a hole current of the conventional IGBT is optimized, so that a safety operation area of a device is enlarged and the sensitivity of latch current density to a temperature is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

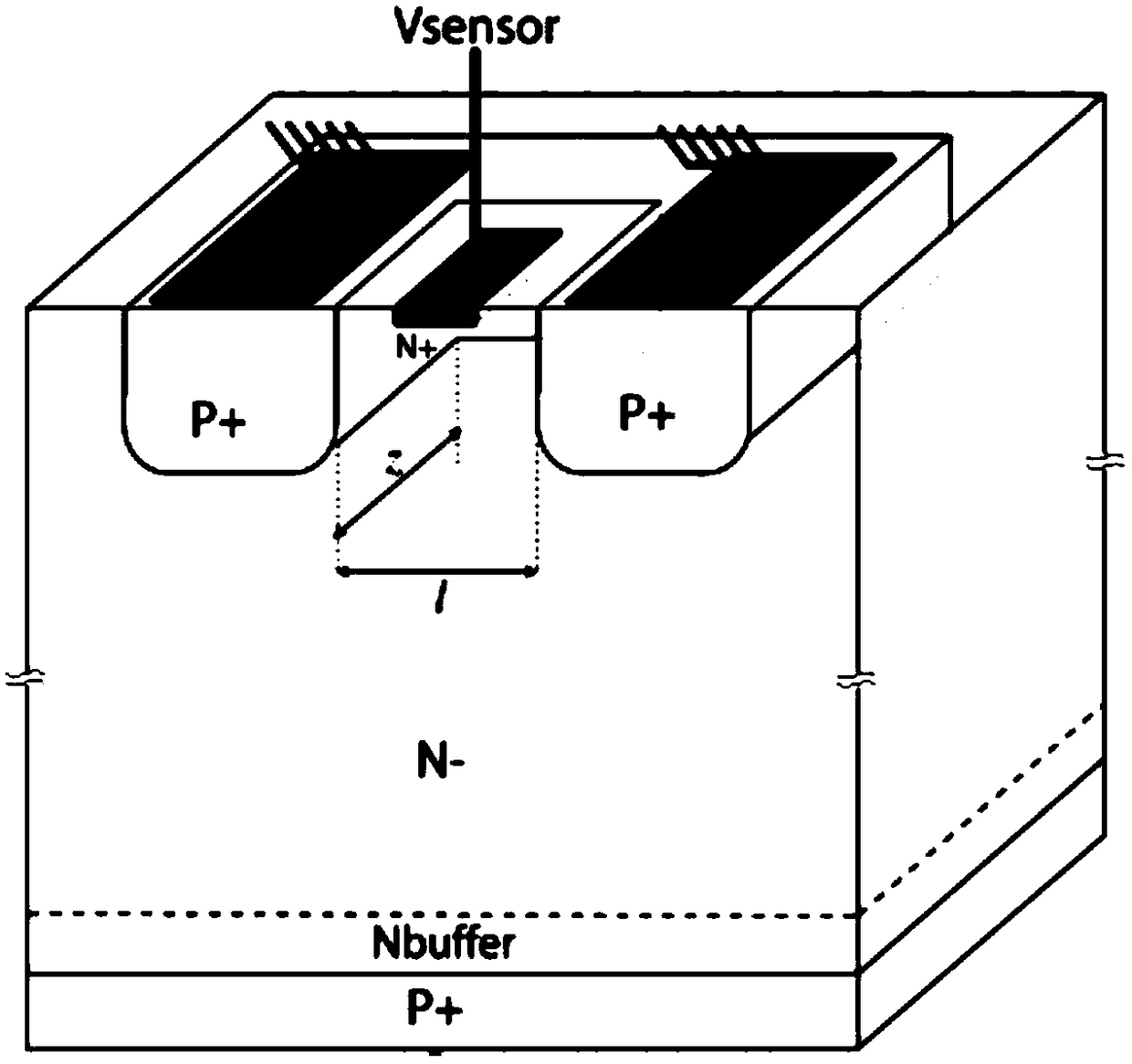

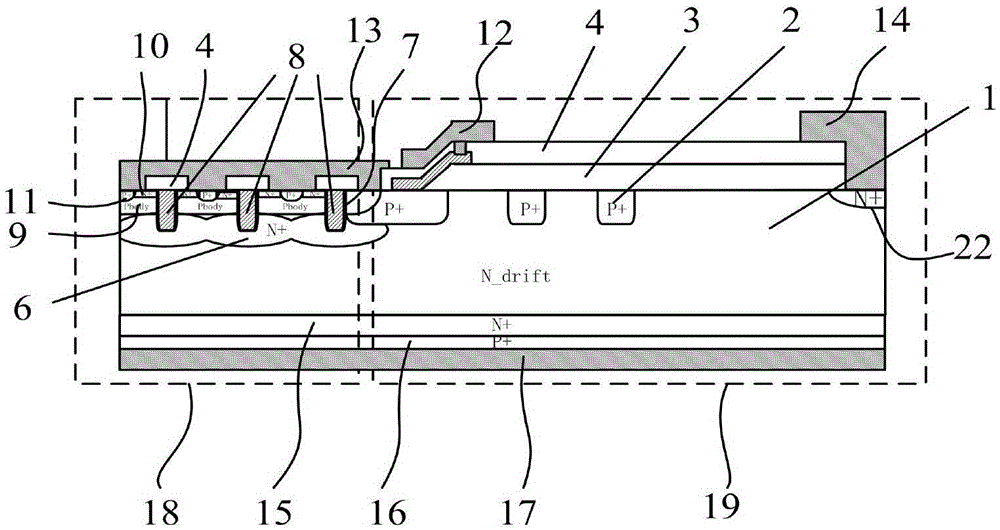

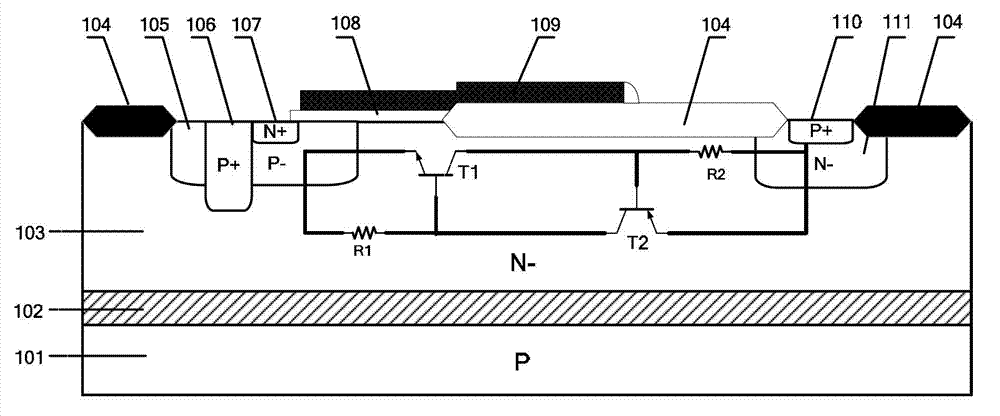

IGBT device with integrated voltage sampling function

ActiveCN108767006AMeet voltage sampling requirementsSimple sampling structureSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsIsolation effectEngineering

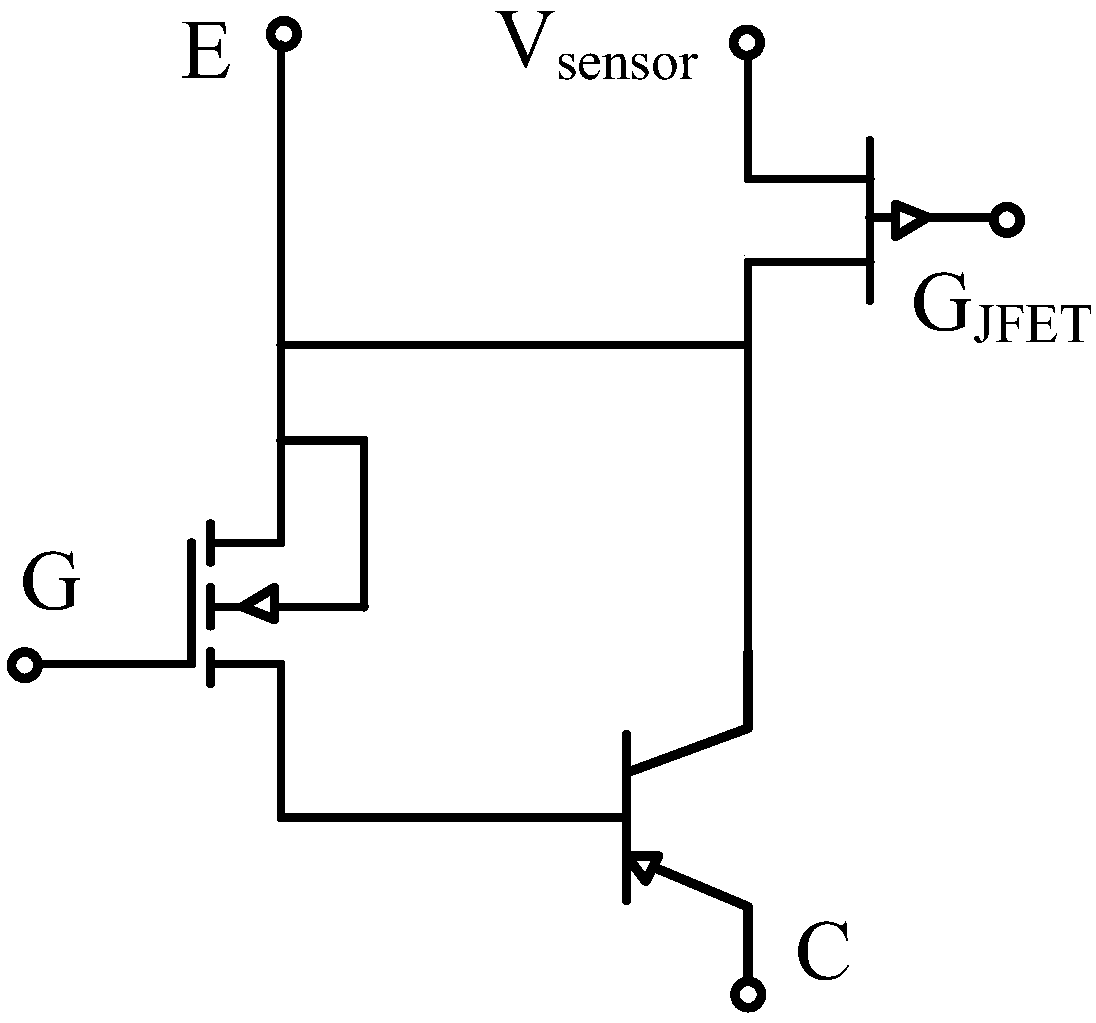

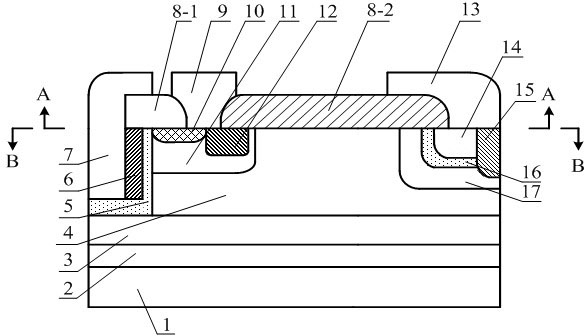

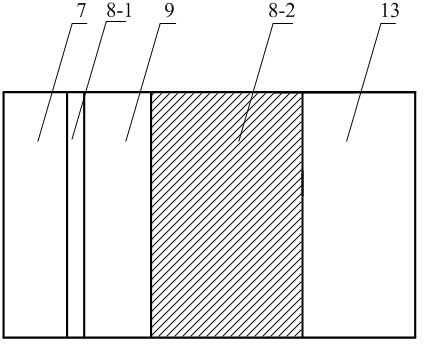

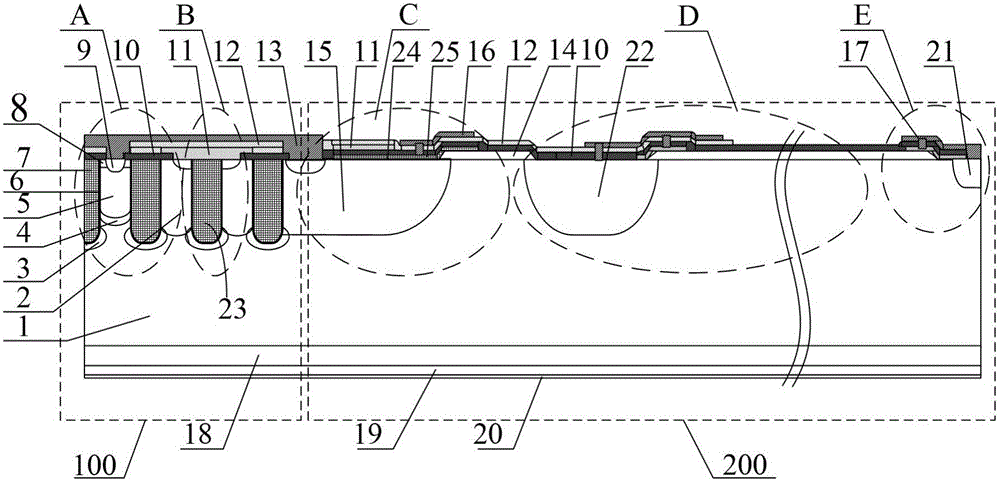

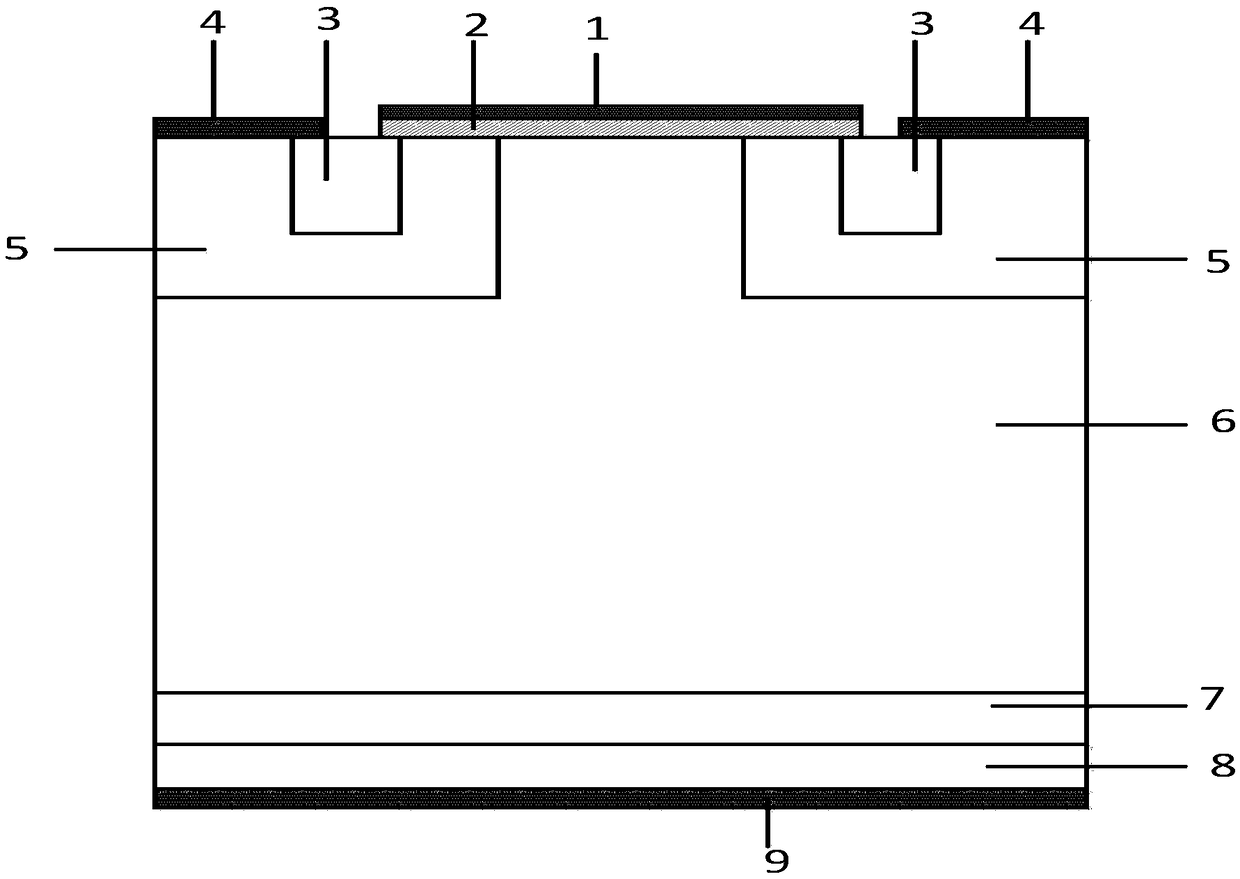

The invention provides an IGBT device with an integrated voltage sampling function, and belongs to the technical field of power semiconductor devices. A channel in which a JFET structure is introducedin a body region is in a normally-closed state, the device is in a forward turning-on state, and carriers are stored in the body region, so that an electric conductance modulating action is strengthened, and the saturated turning-on voltage drop of the device is reduced; in a turning-off state of the device, the body region plays a floating field limiting ring role, so that an electric field aggregation phenomena at the bottom of a groove gate is weakened, and the voltage withstand reliability of the device is improved; the grid electrode and the source electrode of the introduced JFET structure are connected with a peripheral control circuit and a sampling port respectively, a voltage sampling function can be realized by using a mapping reaction between the voltage change of the source electrode of the JFET structure and withstanding voltage of an IGBT, and the forward blocking characteristic of the device cannot be damaged while an electric isolation effect is reached; and the adjustment for voltage sampling rate is realized by changing the grid electrode bias voltage of the JFET structure, so that the requirement of different application conditions on voltage sampling is met. The IGBT device is simple in sampling structure, and is compatible with an existing technology.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

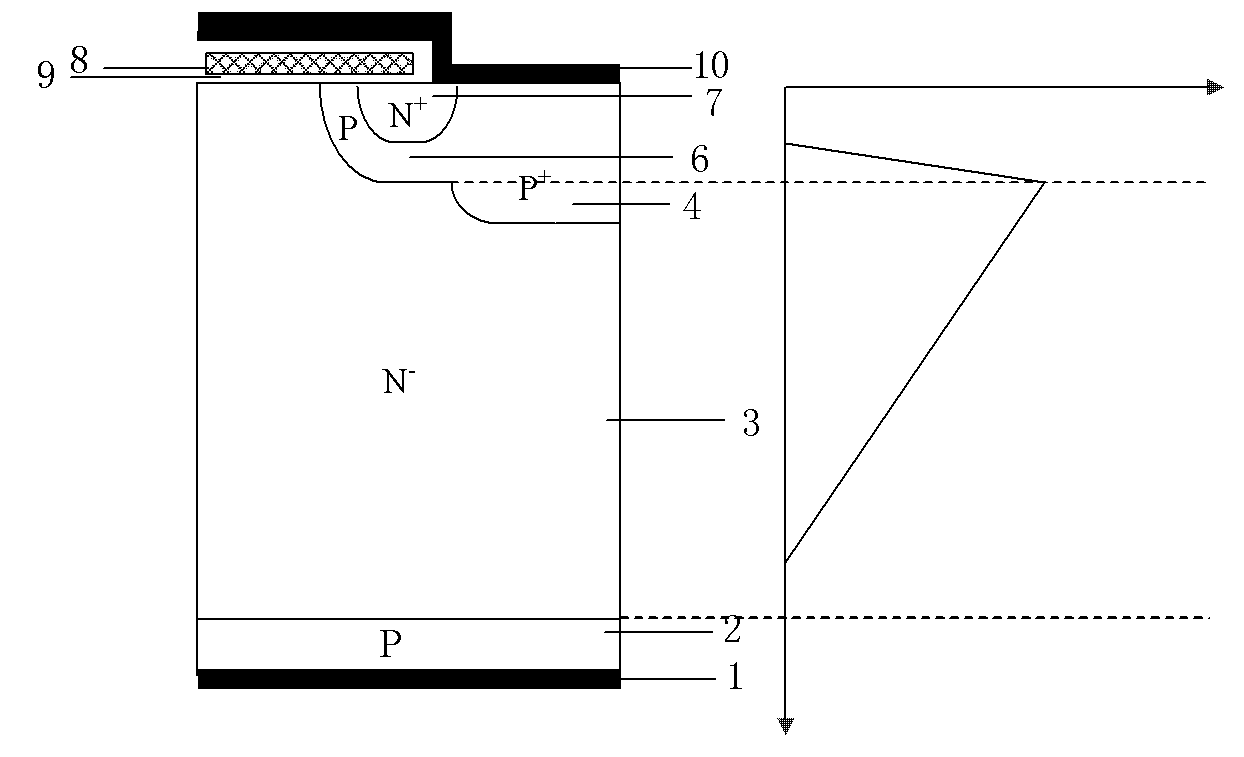

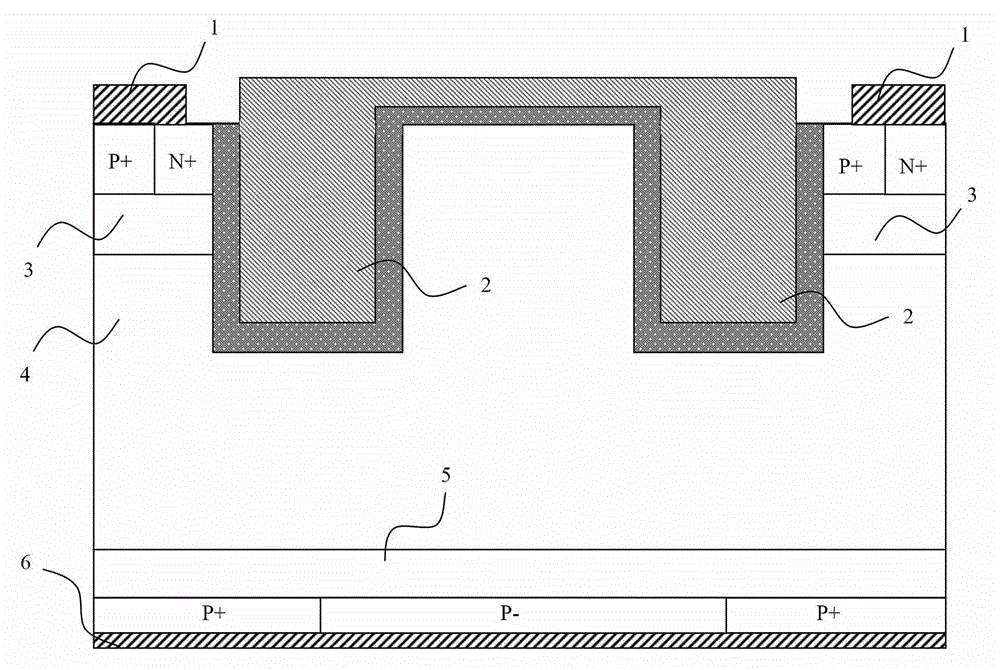

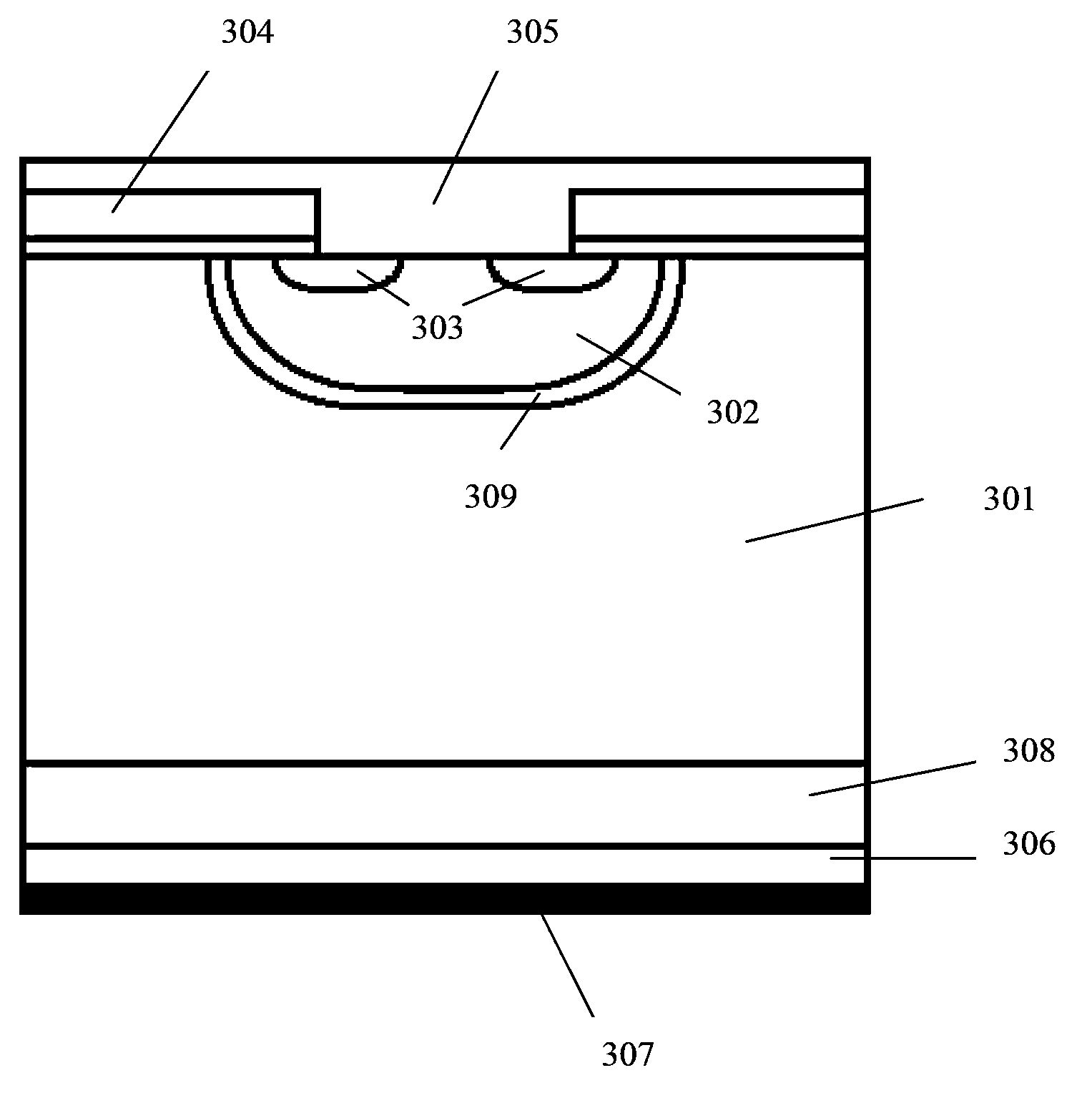

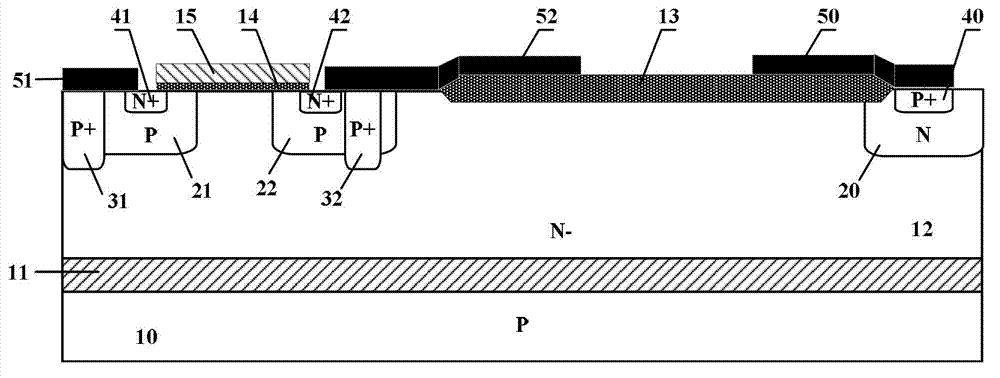

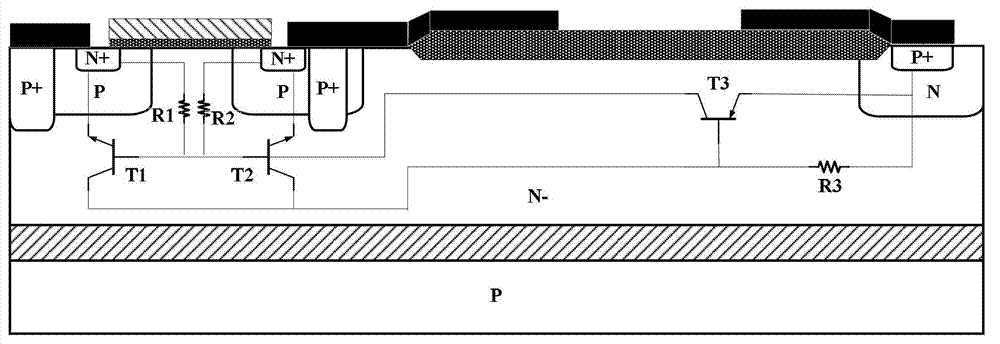

SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157550AReduce adverse effectsImprove vertical pressure resistanceSemiconductor devicesMetal electrodesConductivity modulation

The invention relates to an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The existing products restrict the improvement of the device structures and the electrical properties. The device unit comprises a p-type semiconductor substrate, a buried oxide layer and a p buried layer region in sequence, wherein a metal gate, an n-type heavily doped polysilicon gate, a gate oxide layer and an n-type lightly doped drift region are arranged at the top of the p buried layer region side by side in sequence; a first p-type well region and an n-type buffer region are respectively embedded at the two sides at the top of the n-type lightly doped drift region; an n-type cathode region and a first p well ohmic contact region are embedded at the top of the first p-type well region; a second p-type well region and an anode short-circuit point region are embedded at the top of the n-type buffer region; a second p well ohmic contact region is embedded at the top of the second p-type well region; and a first field oxide layer, a second field oxide layer, an anode metal electrode and a cathode metal electrode are arranged at the top of the device unit. The device unit has the beneficial effects of reducing the spreading resistance, improving the conductivity modulation effect of the drift region, reducing the on-state power consumption and obviously improving the thermal property of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

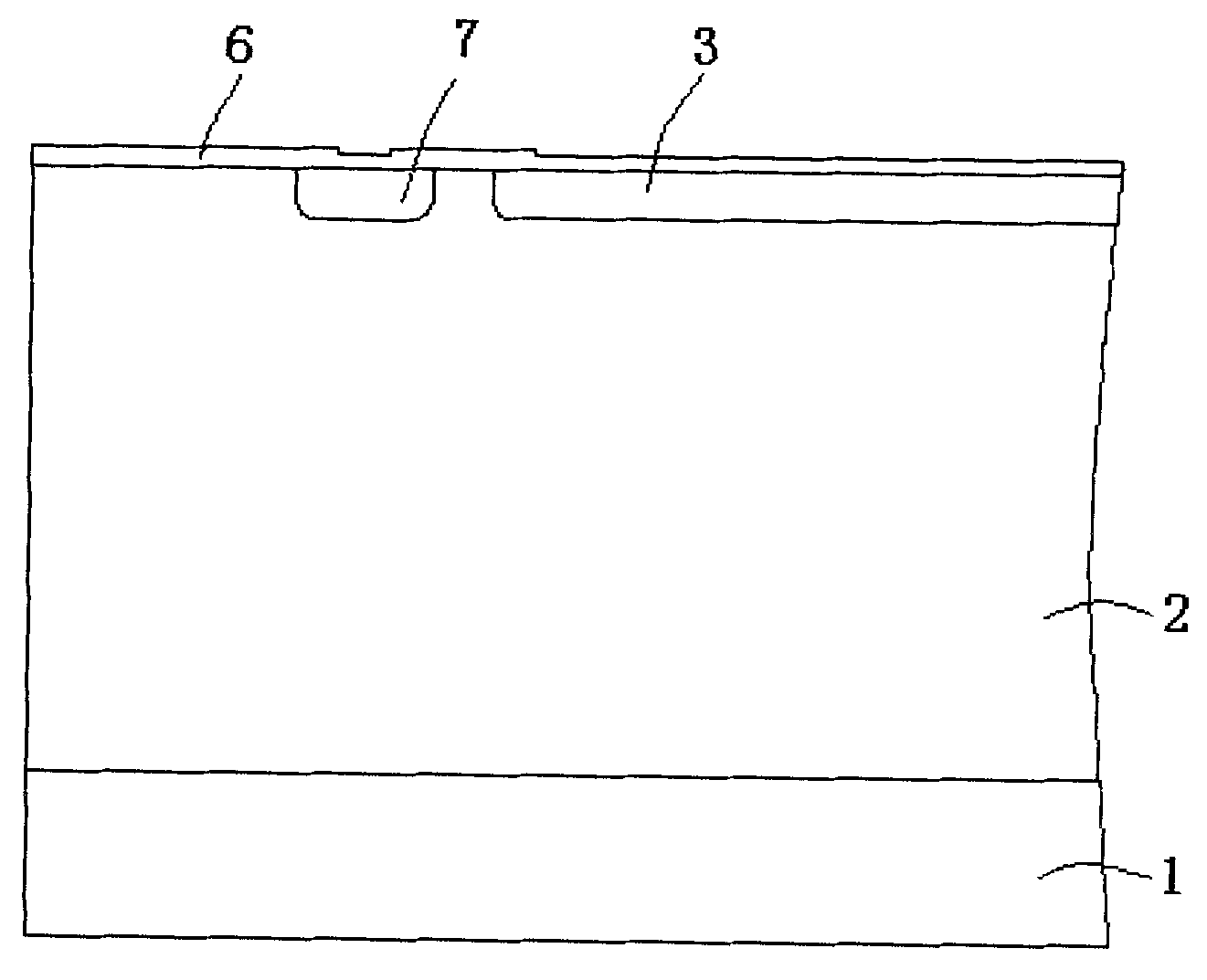

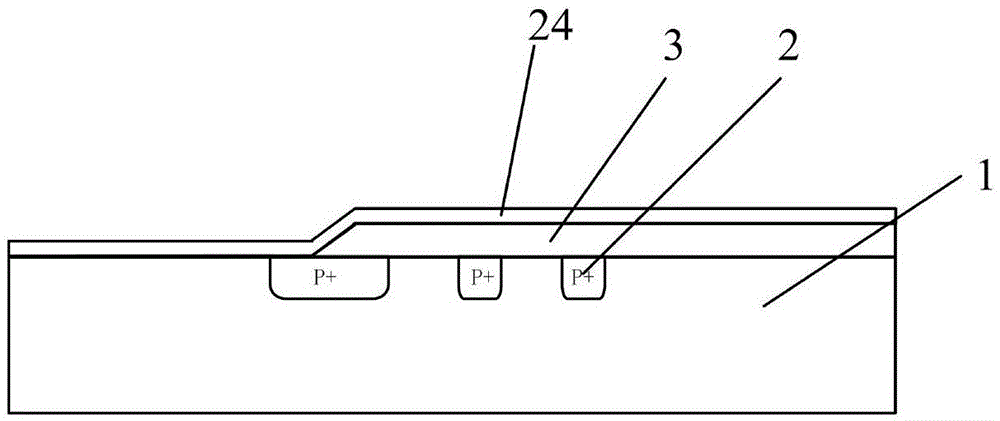

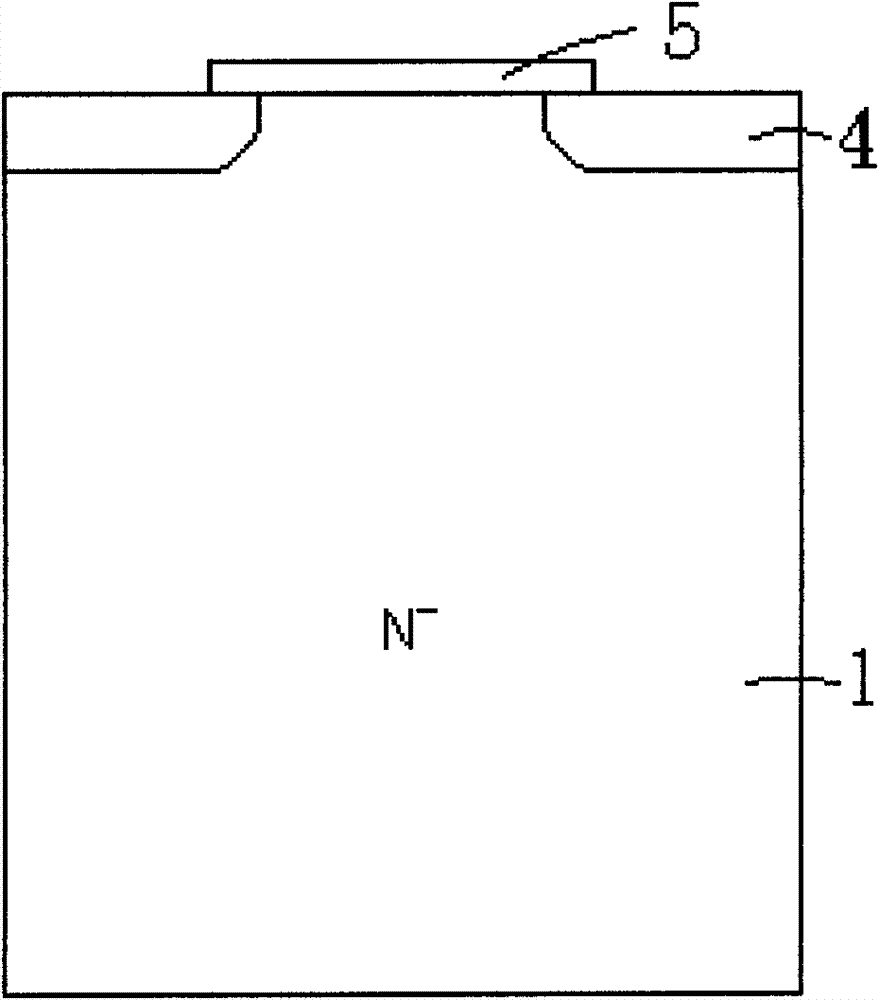

Plane gate type IGBT (Insulated Gate Bipolar Translator) chip production method

ActiveCN102969243AIncrease hole concentrationImprove injection efficiencySemiconductor/solid-state device manufacturingPhysicsInsulated-gate bipolar transistor

The invention discloses a plane gate type IGBT (Insulated Gate Bipolar Translator) chip production method. The method comprises the steps: firstly carrying out front side processing, and injecting and annealing a second N type current carrier buried layer to a semiconductor substrate; etching, injecting and annealing a first N type current carrier buried layer injection window; etching a first N type current carrier buried layer; removing an oxidization layer on the surface of the semiconductor substrate; depositing an insulating material on the outer surface of the first N type current carrier buried layer, and photoetching and etching the deposited insulating material to form a media buried layer; completing the remaining front side processing technology; conducting back side processing, thinning the back side part to the needed thickness; injecting, doping and propelling and annealing an N buffer layer; injecting, doping and propelling and annealing a P+ collector electrode region; and producing a metal collector electrode. According to the plane gate type IGBT chip production method, the drop voltage of an IGBT chip is reduced, the compromise relation of the turn-off loss can be optimized, and lower power consumption can be realized, so that the power density, operating junction temperature and reliability of the IGBT chip can be improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Insulated gate bipolar transistor device with low conduction voltage drop, and manufacturing method for insulated gate bipolar transistor device

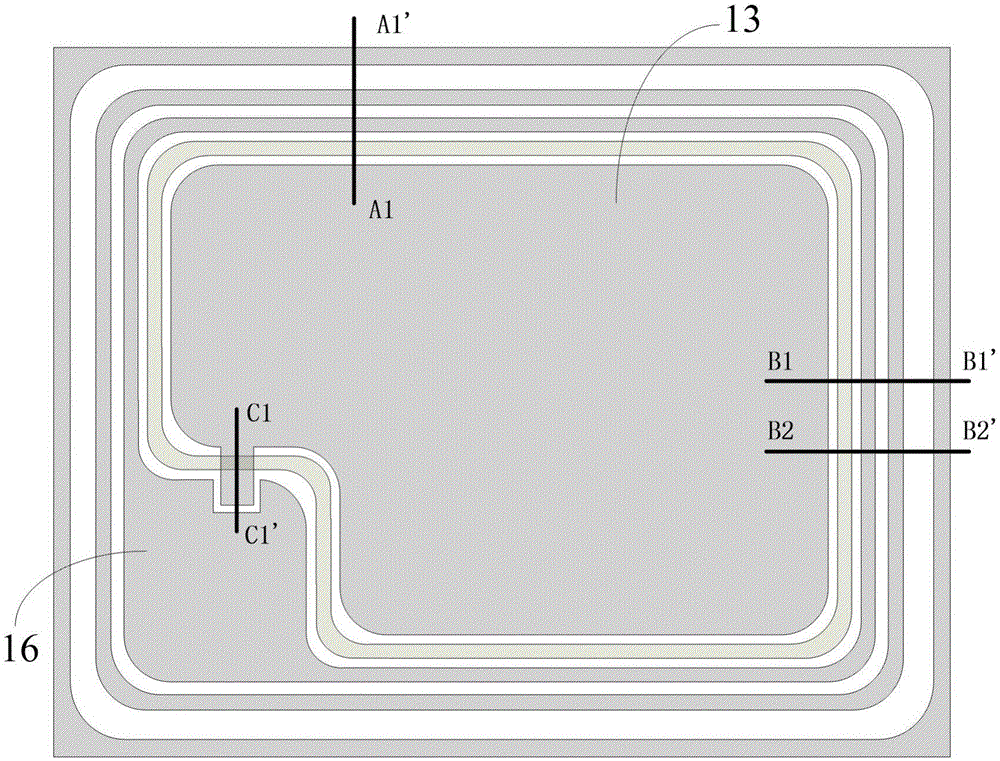

PendingCN106653836AEnhanced conductance modulation effectReduce saturation pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesInsulated-gate bipolar transistorPower flow

The invention relates to an insulated gate bipolar transistor device with low conduction voltage drop, and a manufacturing method for the insulated gate bipolar transistor device. The device comprises an active region located on a semiconductor substrate, and a terminal protection region. Active cells of the active region on the section of the device employ a trench structure, and comprise active cells and non-active cells. The bottom of an active cell trench and the bottom of a non-active cell trench are respectively provided with a floating region of a second conductive type, wherein the floating region of the second conductive type below the active cell trench wraps the bottom of the active cell trench, and the floating region of the second conductive type below the non-active cell trench wraps the bottom of the non-active cell trench. The device has extremely low conduction voltage drop and extremely quick cut-off speed under the condition that the withstand voltage is guaranteed, is lower in current and voltage oscillation, and greatly improves the work reliability.

Owner:WUXI NCE POWER

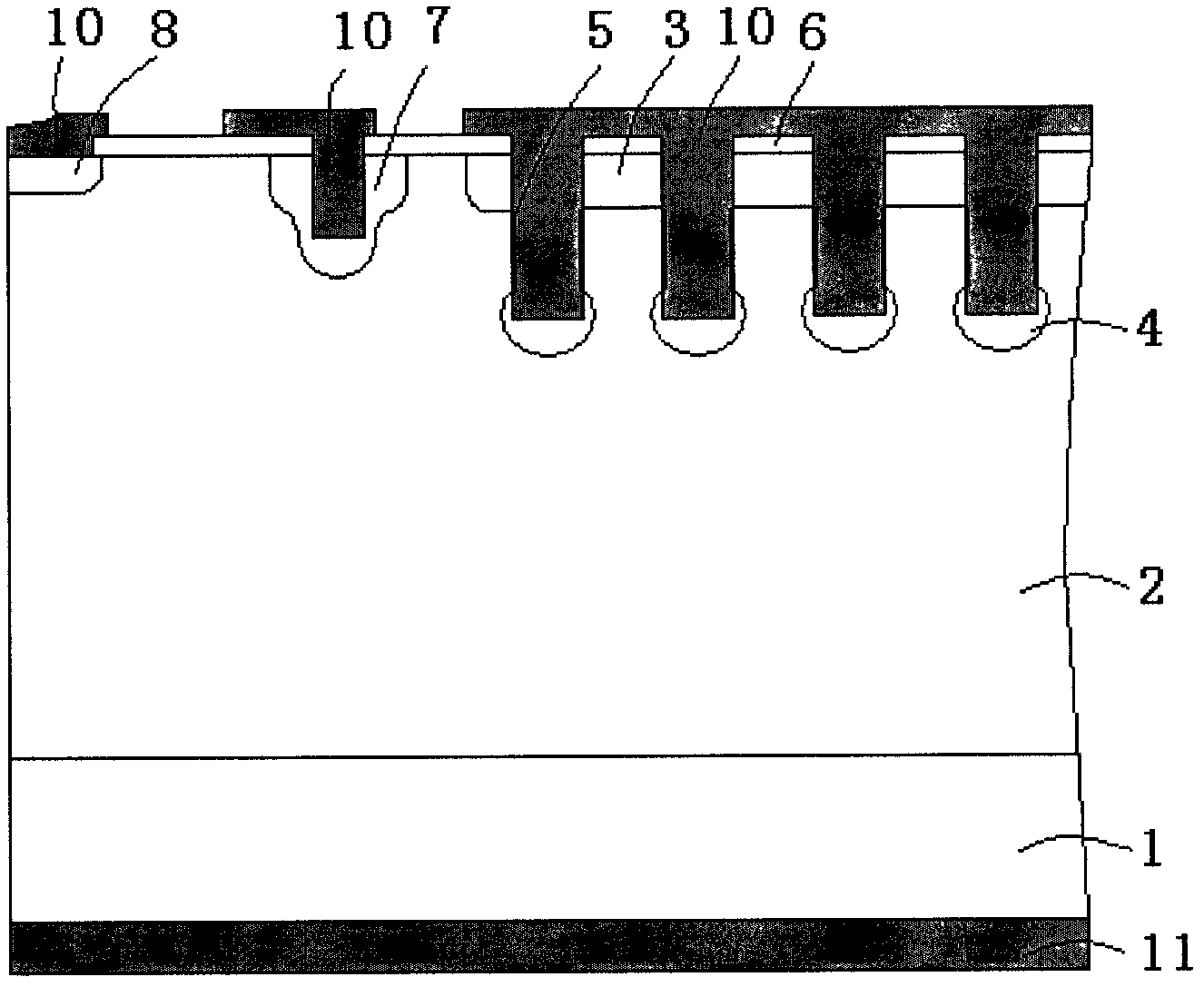

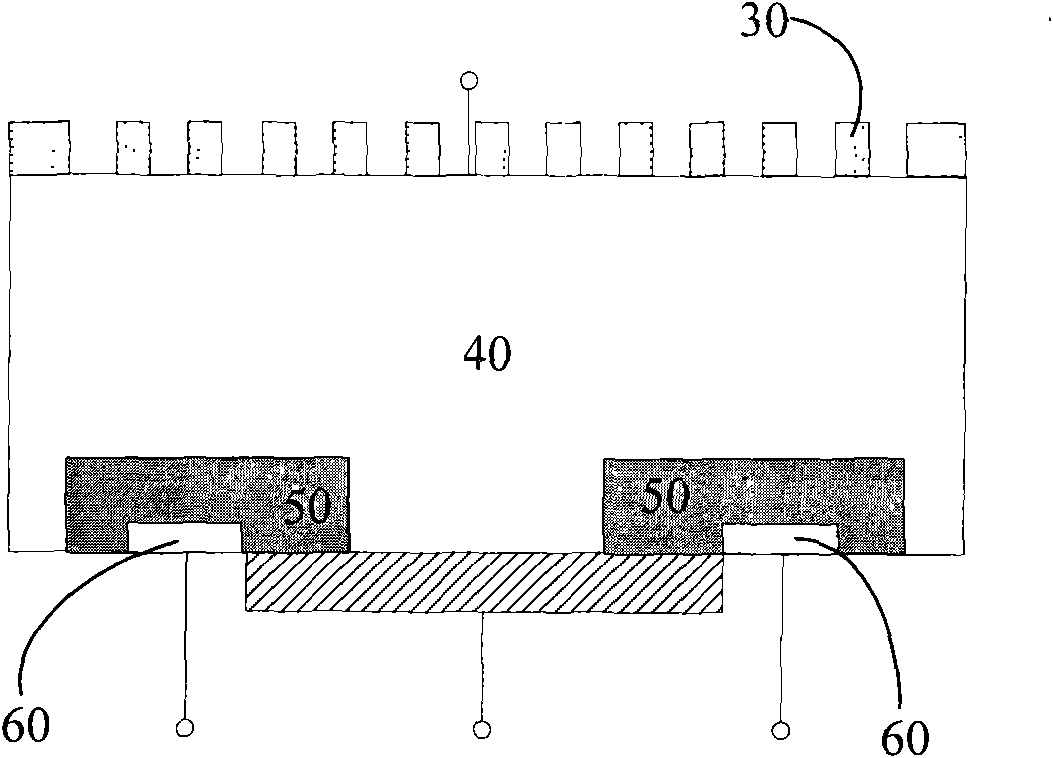

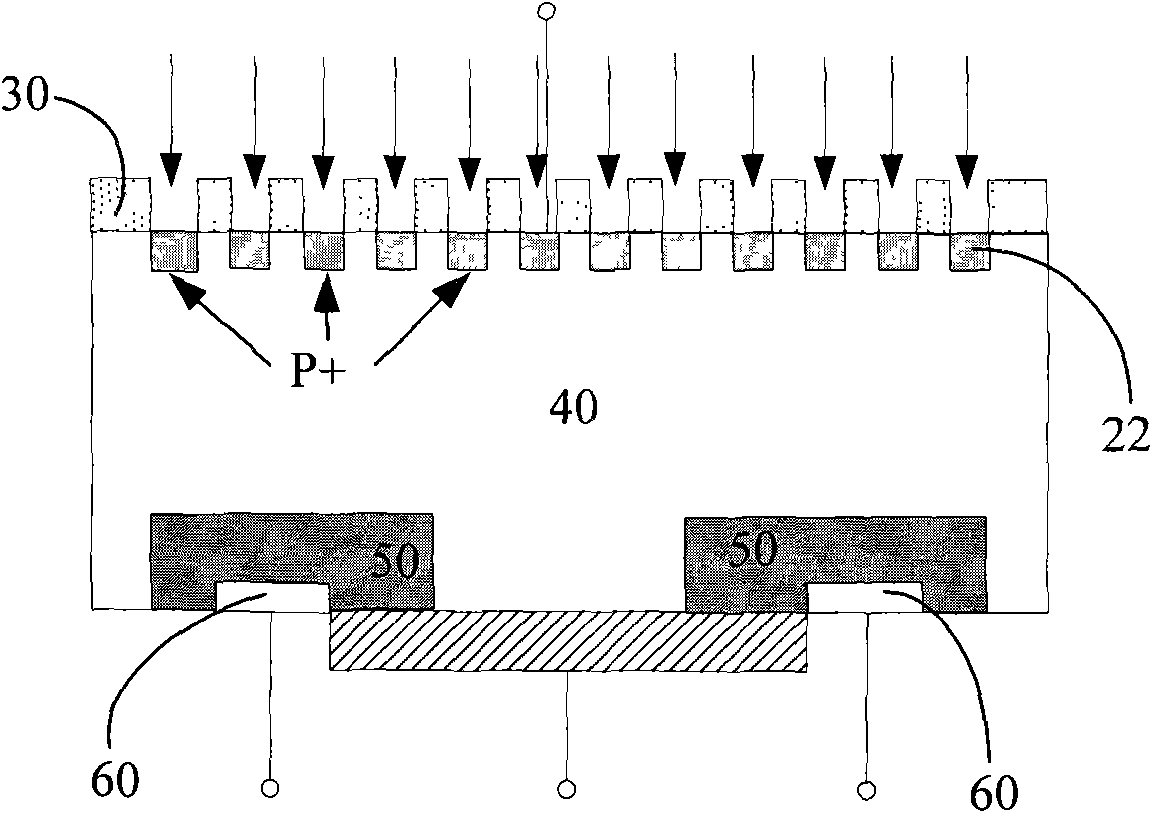

Method for manufacturing trench gate type IGBT (insulated gate bipolar transistor) chip

ActiveCN102945804AIncrease hole concentrationImprove injection efficiencySemiconductor/solid-state device manufacturingNitric oxideInsulated-gate bipolar transistor

The invention discloses a method for manufacturing a trench gate type IGBT (insulated gate bipolar transistor) chip, which comprises the following steps: selecting two N-shaped semiconductor substrates, and carrying out oxidation or deposition on one of the substrates, so that insulating materials including silicon oxides or nitric oxides are formed on the surface of the substrate; carrying out photoetching and etching on the insulating materials on the surface of the substrate so as to form a dielectric buried layer; carrying out photoetching and etching on the other substrates so as to form a figure coincided with the concave-convex surface of the dielectric buried layer; carrying out concave-convex surface butt-joint on the dielectric buried layer and the figure, and bonding the two substrates together at high temperature; according to voltage-withstanding requirements and machining allowances, respectively carrying out thinning processing on the two substrates, and controlling the dielectric buried layer at a design depth, so that a chip manufacturing intermediate is formed; and completing the manufacturing process of a trench gate type IGBT chip. According to the invention, the drop voltage of the chip is reduced, a compromising relation with shut-off loss is optimized, and the lower power consumption is realized, thereby improving the power density, operating junction temperature and reliability of the IGBT chip.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Fast recovery diode and manufacturing method thereof

InactiveCN102867849AIncreased Schottky areaReduce conduction voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesHigh current densitySchottky barrier

The invention relates to a fast recovery diode device, and also relates to a manufacturing method of the fast recovery diode device. According to the invention, a groove structure is added into a traditional Schottky barrier rectifier (MPS) structure intruding into a PN junction. Compared with the traditional MPS device, the fast recovery diode device disclosed by the invention has the advantages of lower forward voltage drop and higher current density.

Owner:盛况

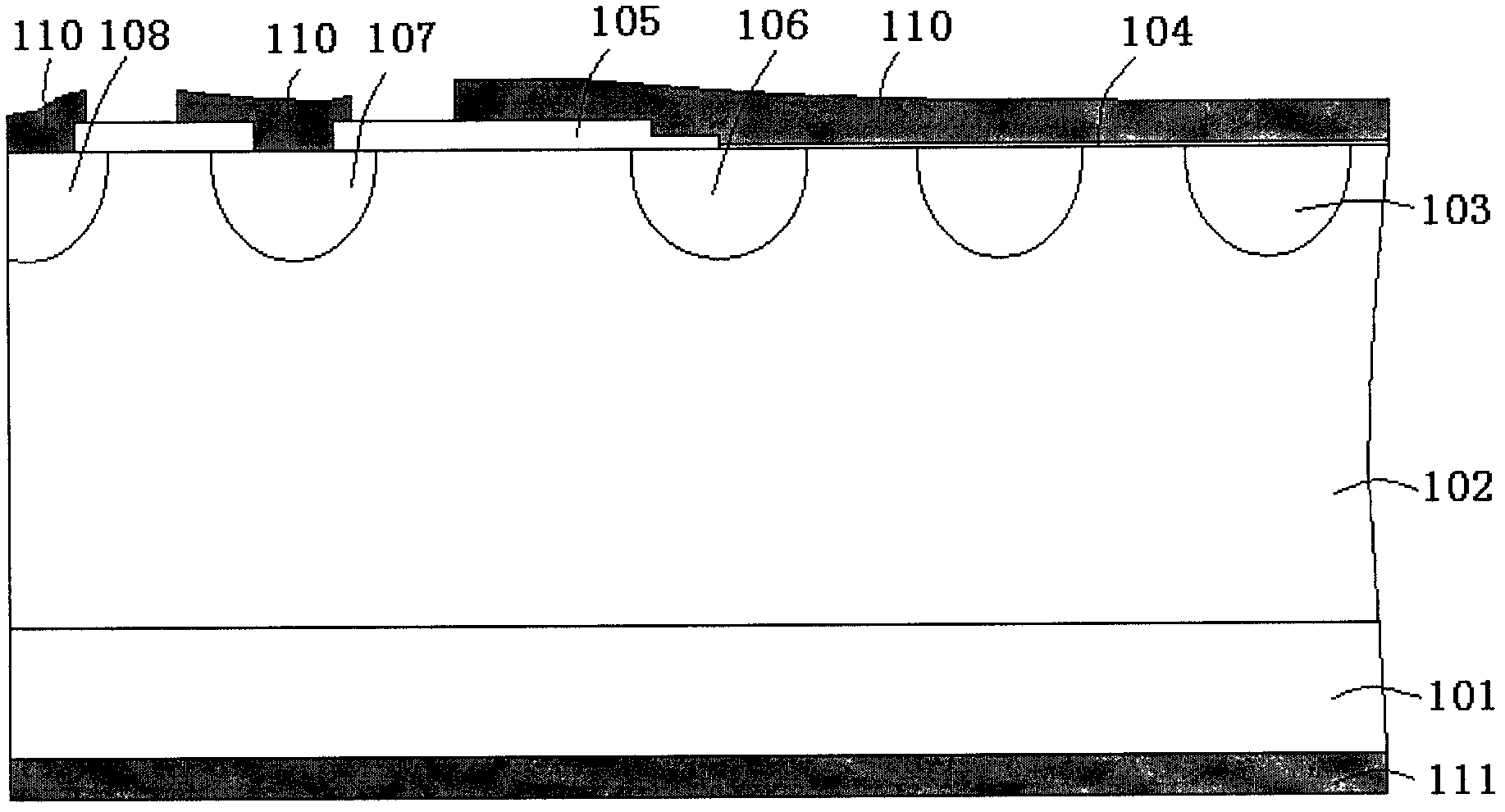

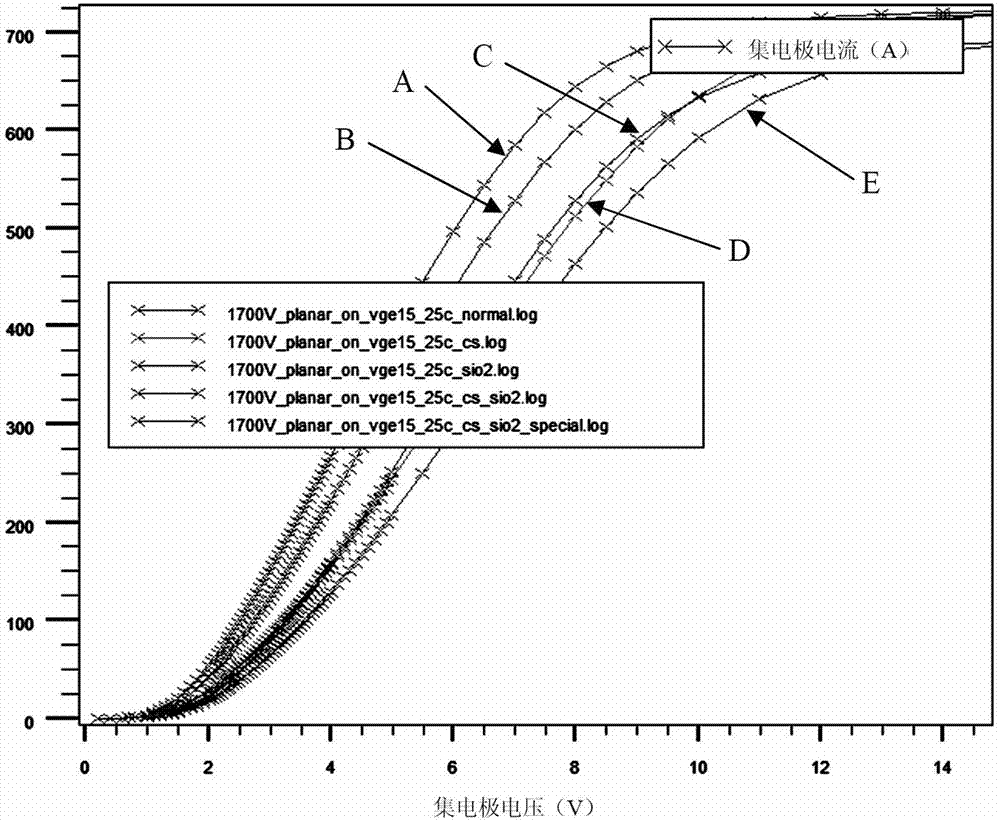

Planar gate IGBT (Insulated Gate Bipolar Transistor) chip

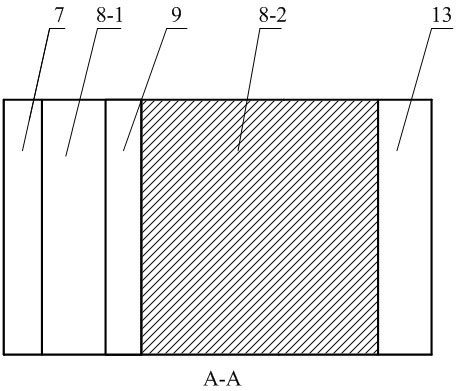

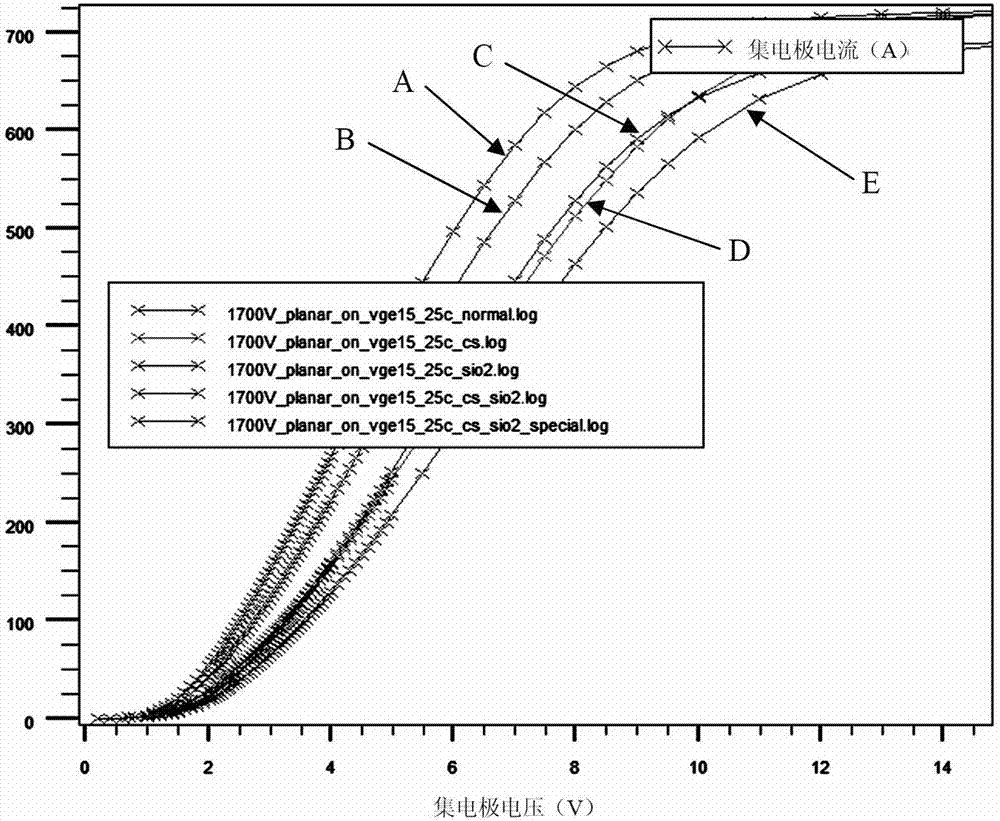

ActiveCN102969351AReduce conduction voltage dropImprove the conduction voltage dropSemiconductor devicesOhmic contactCharge carrier

The invention discloses a planar gate IGBT (Insulated Gate Bipolar Transistor) chip, which comprises a collector metal electrode, a P+ collector region, an N- drift region, a P- base region, a P+ ohmic contact region, an N+ source region, a gate oxide layer, a polysilicon gate and a gate metal electrode which are arranged successively, and an emitter metal electrode arranged above the P+ ohmic contact region, wherein the polysilicon gate of the planar gate IGBT chip adopts a planar gate structure. The planar gate IGBT chip also comprises a first N-type carrier buried layer and / or a second N-type carrier buried layer. The first N-type carrier buried layer is located below the P- base region. The second N-type carrier buried layer is located below the gate oxide layer and at both sides of the P- base region. The planar gate IGBT chip has the beneficial effects that the compromise relation between conduction pressure drop and turn-off loss of the IGBT is reduced, lower power consumption is realized, and thus the power density, the operating junction temperature and the long-term reliability of the IGBT chip are increased.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

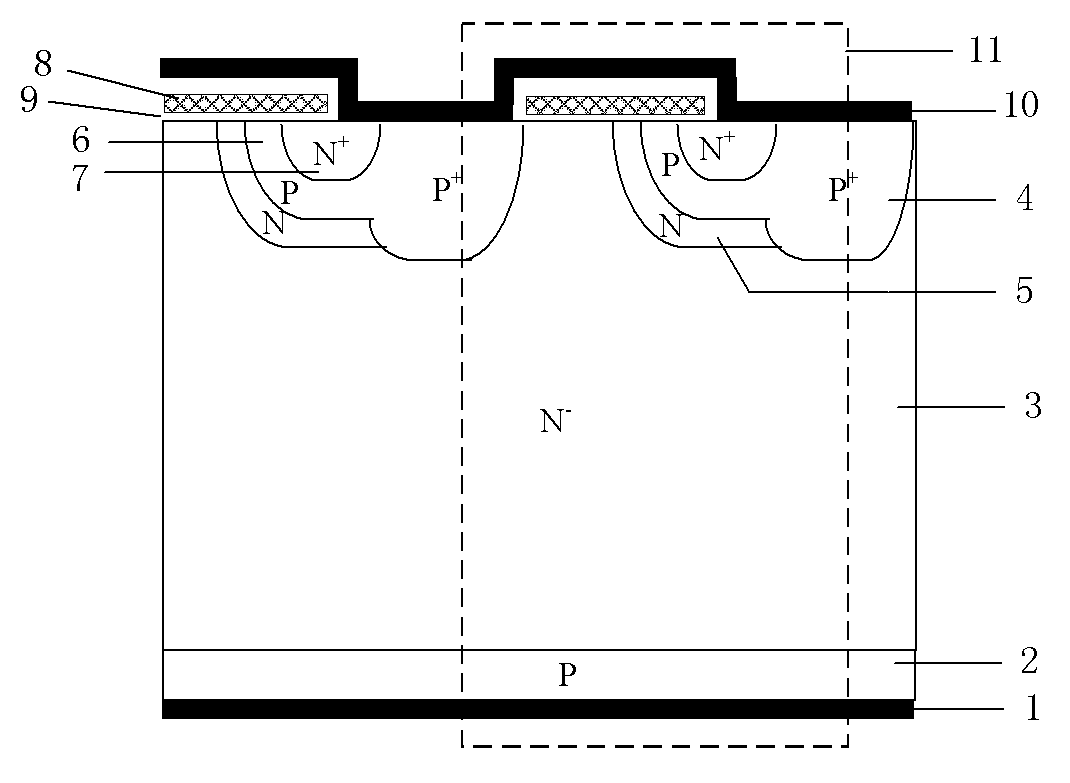

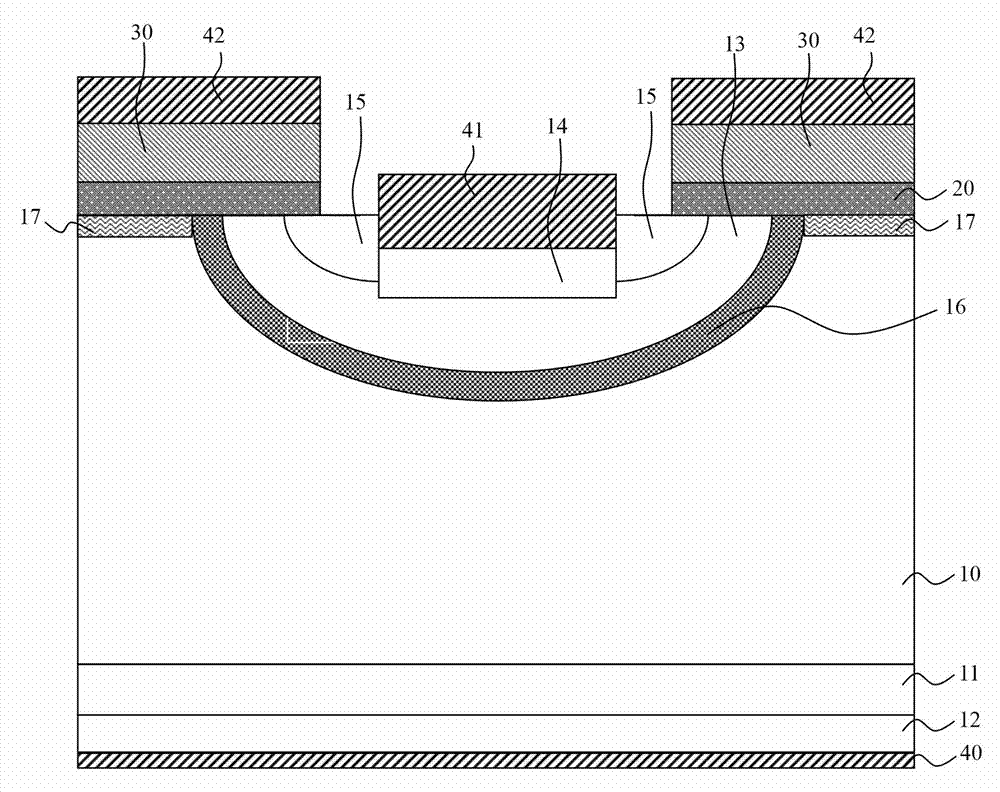

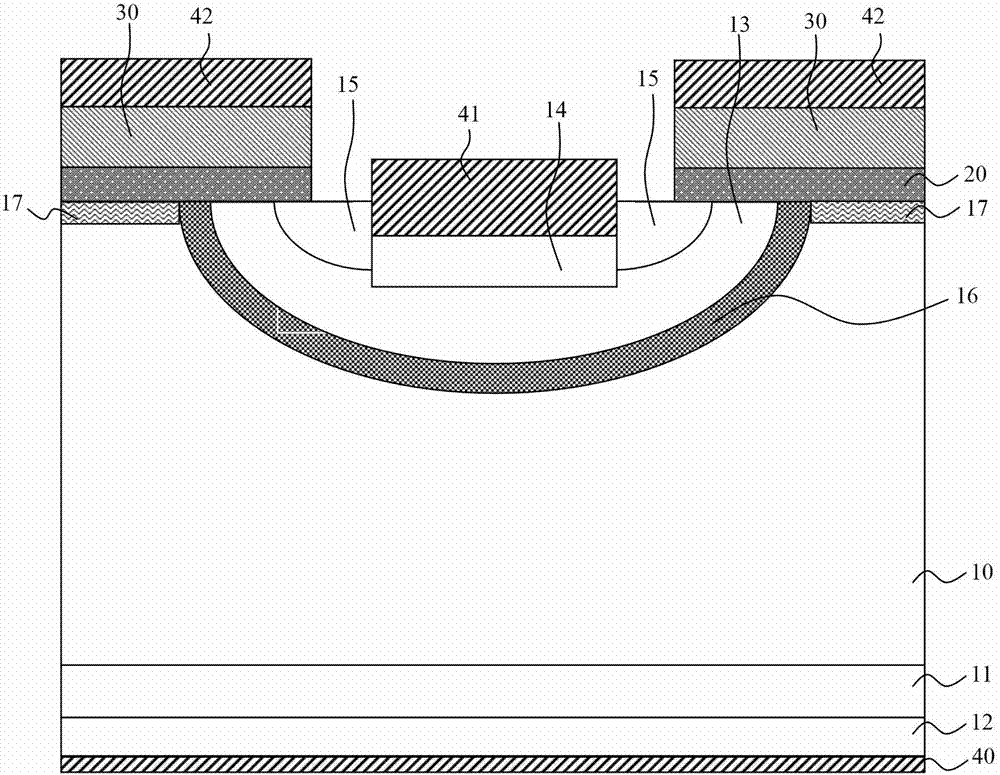

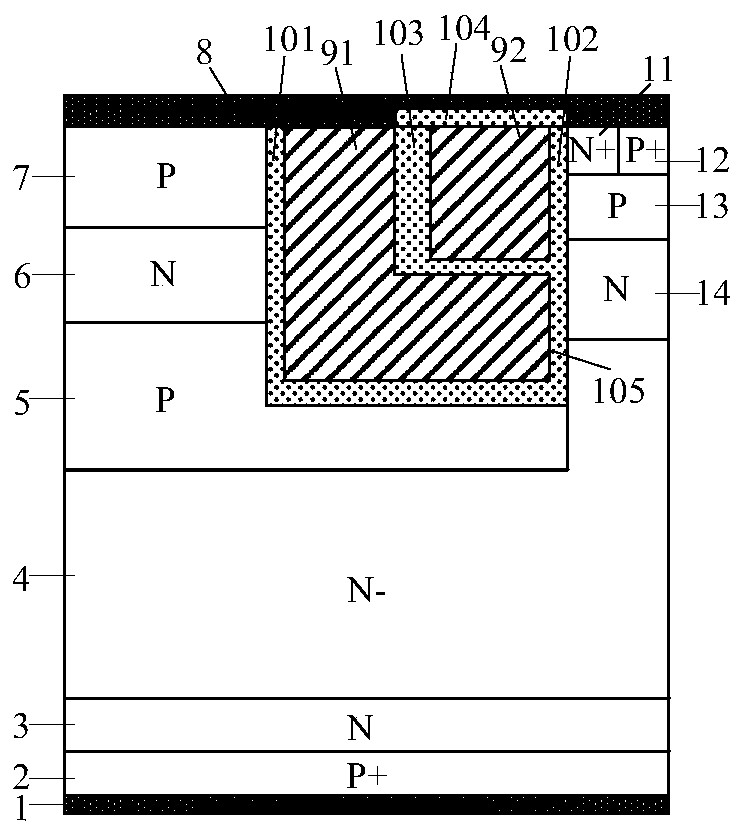

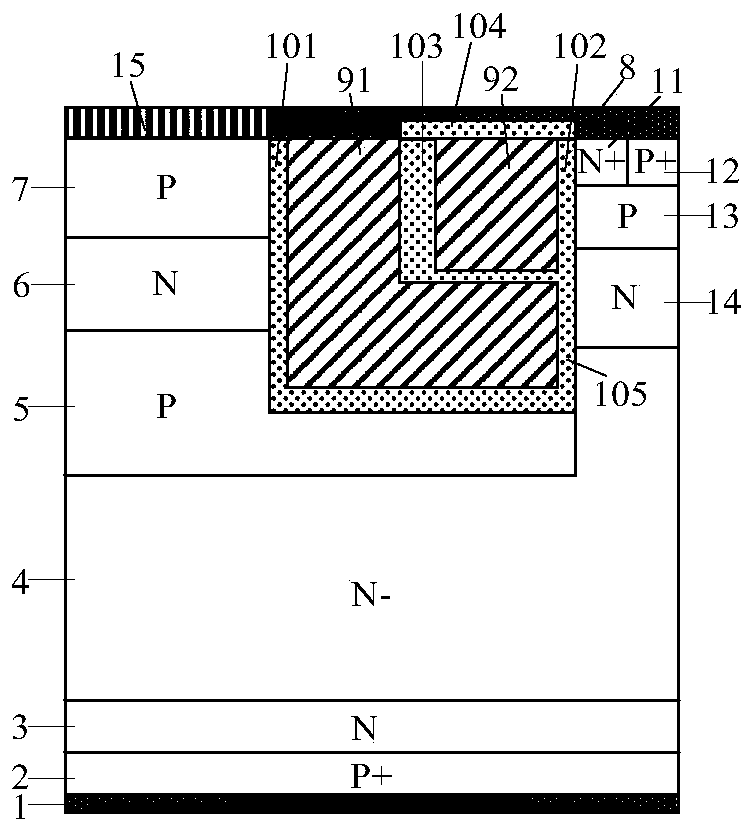

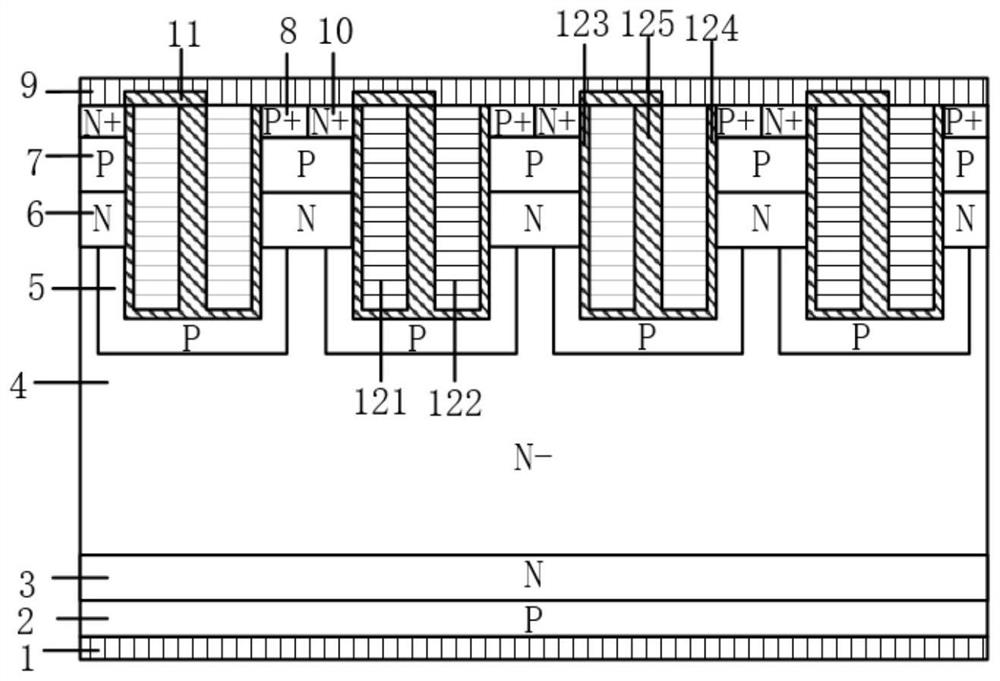

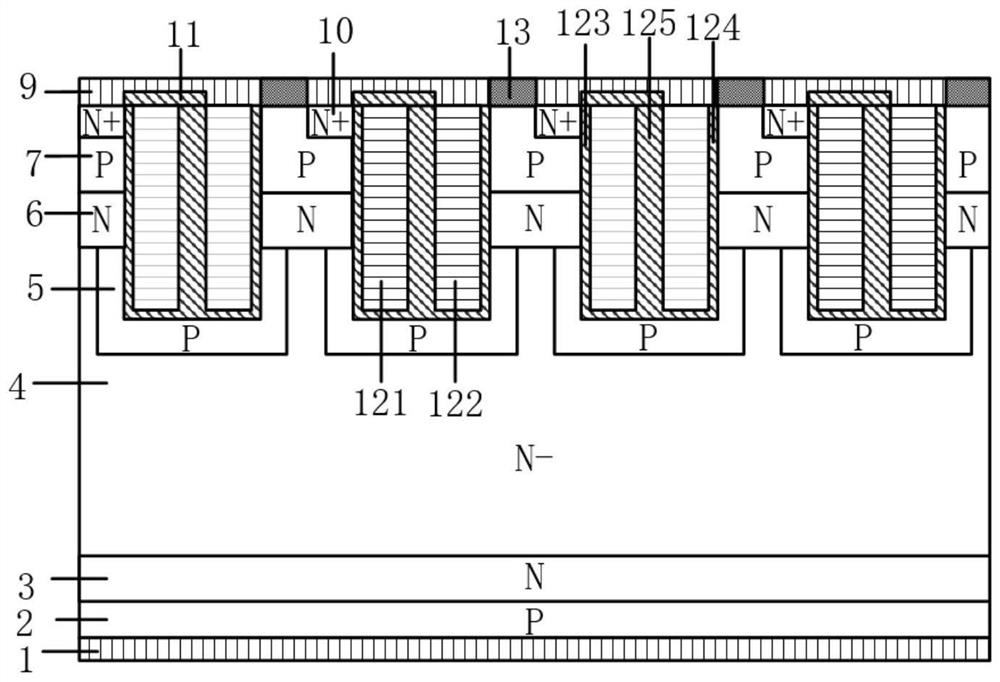

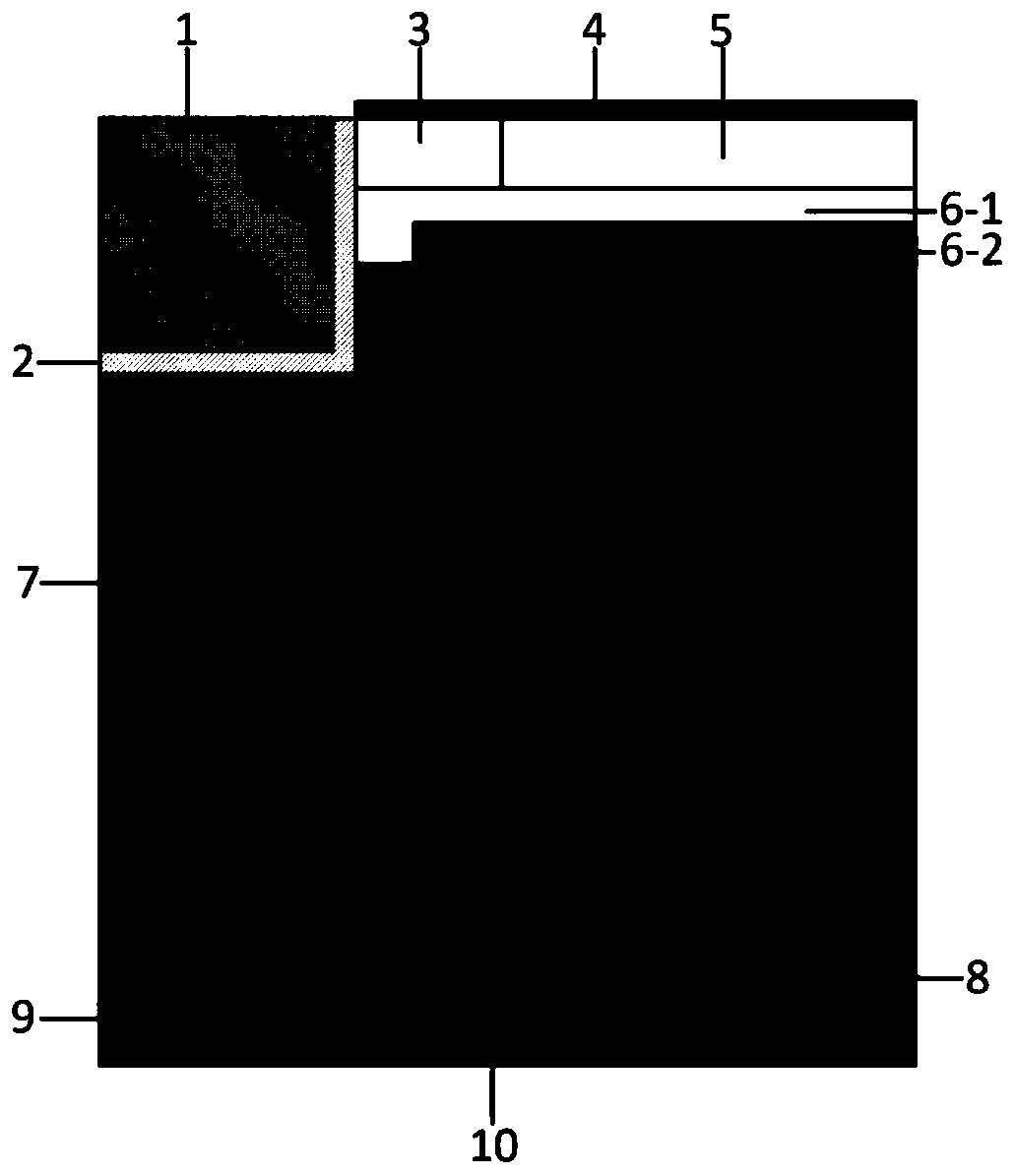

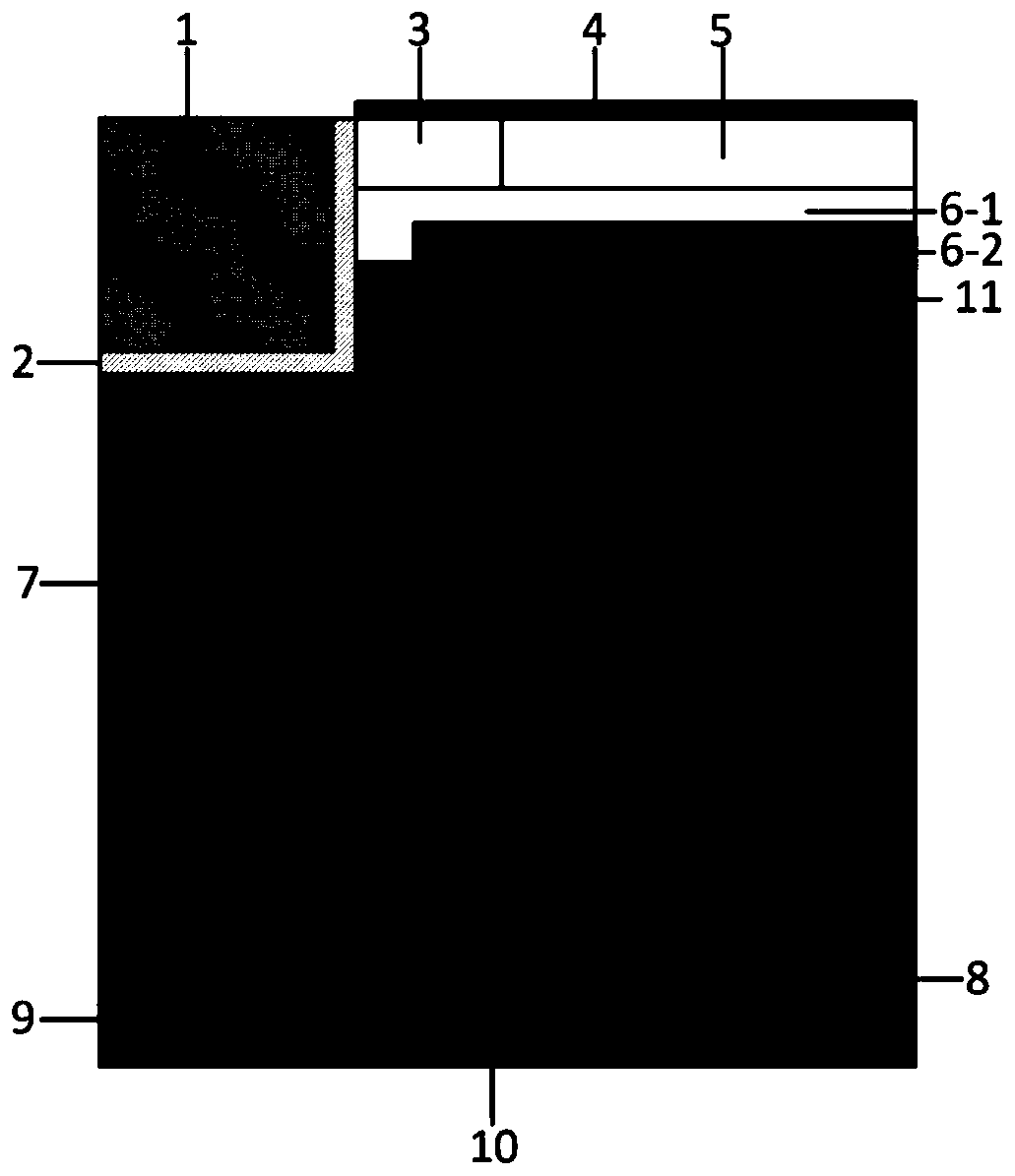

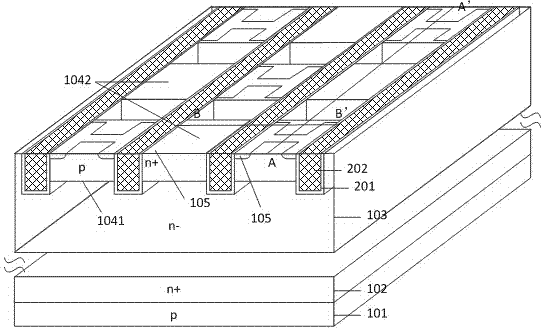

IGBT device with carrier storage structure and manufacturing method of IGBT device

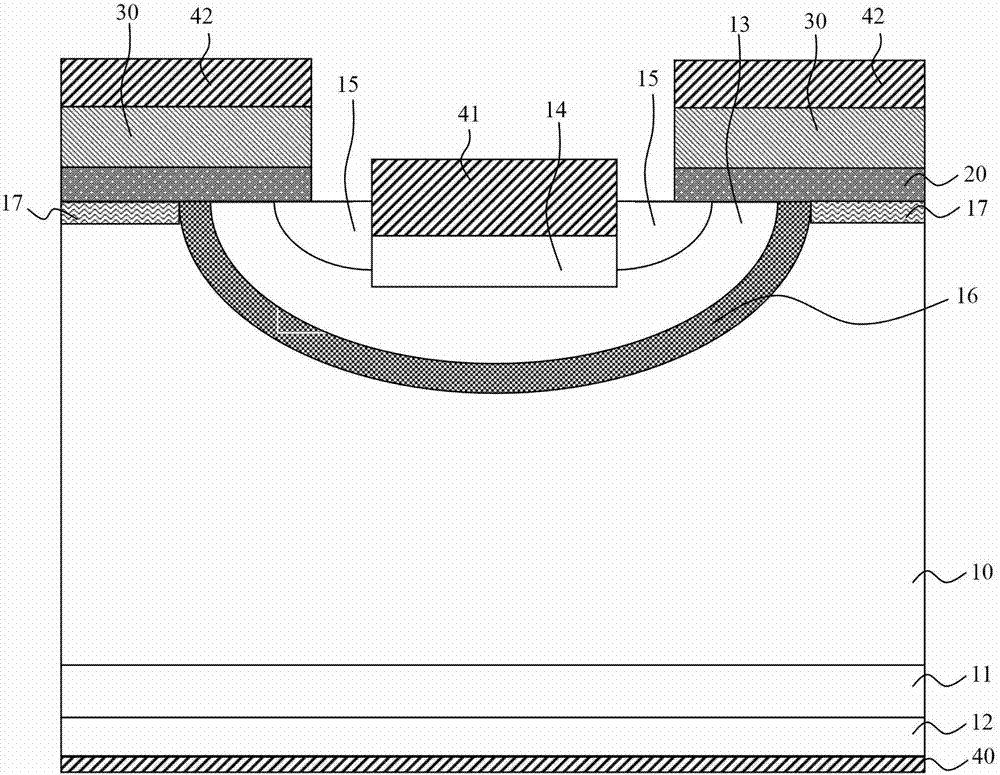

ActiveCN105633139AReduce saturation pressure dropEnhanced conductance modulation effectSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropHigh voltage

The invention relates to an IGBT device with a carrier storage structure and a manufacturing method thereof. An active area of the IGBT device adopts a groove structure; a second conduction type body area is arranged in a first conduction type drifting area of the active area; a cellular groove is located in the second conduction type body area and deeply extends into the first conduction type drifting area below the second conduction type body area; the carrier storage structure is arranged in the first conduction type drifting area of the active area; the carrier storage structure comprises a first conduction type carrier storage area which is used for completely surrounding the inner and outer walls, extending in the first conduction type drifting area, of the cellular groove; and the doping concentration of the first conduction type carrier storage area is greater than the doping concentration of the first conduction type drifting area. According to the IGBT device with the carrier storage structure and the manufacturing method thereof, the relatively low breakover voltage drop and extremely rapid turnoff characteristic can be satisfied at the same time, the pressurization breakdown position can be adjusted to a cellular area to ensure relatively high voltage surge resistance, the chip manufacturing cost is not increased, and the chip area is reduced.

Owner:WUXI NCE POWER

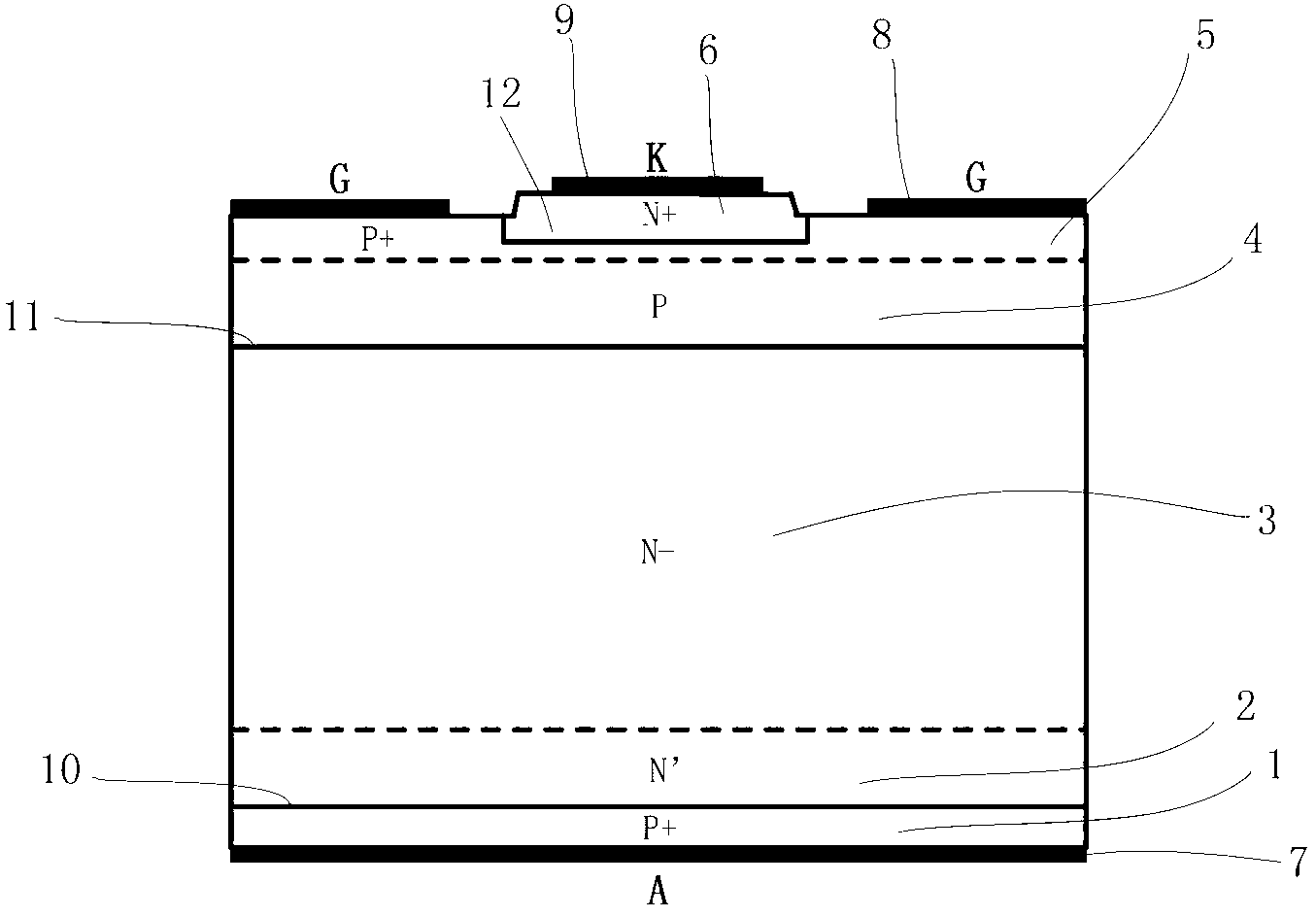

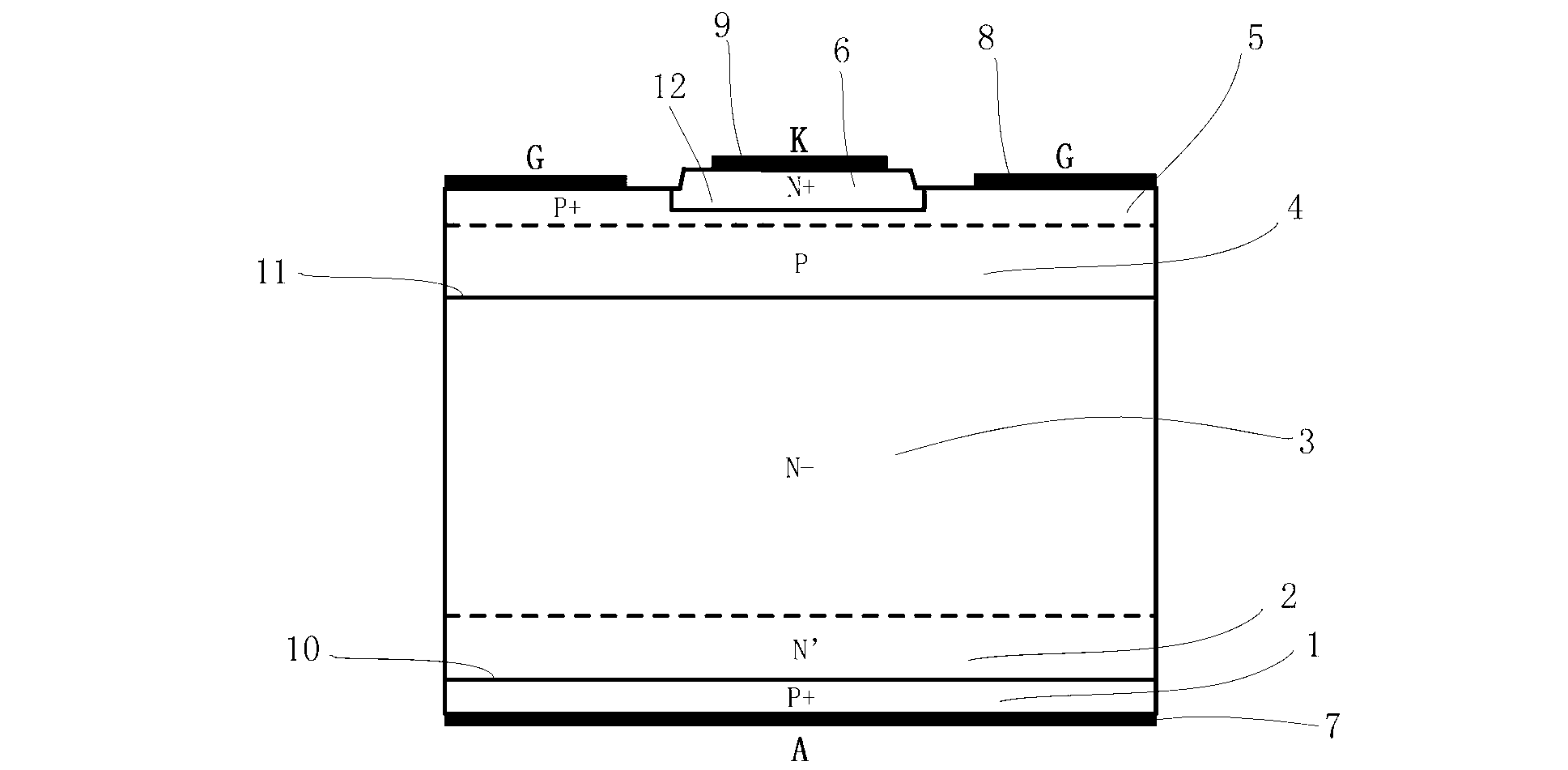

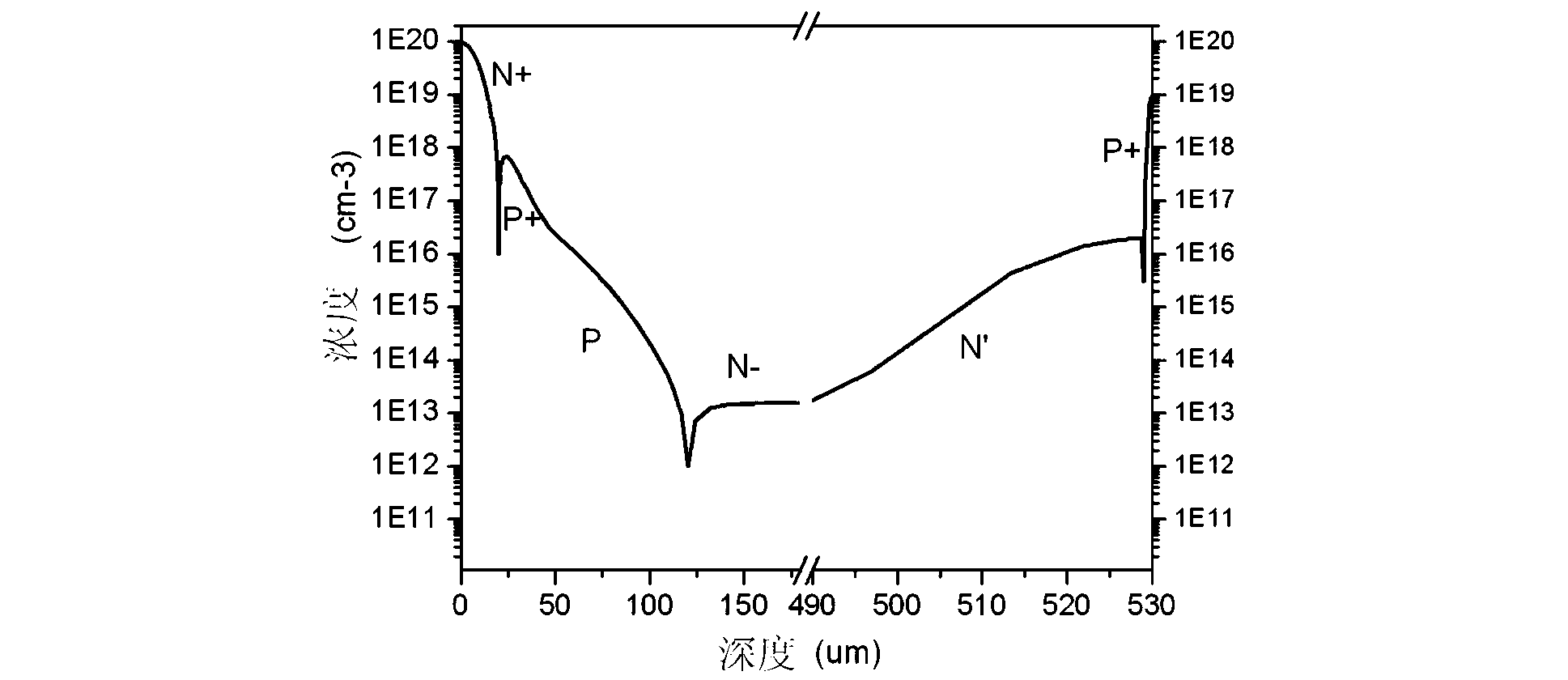

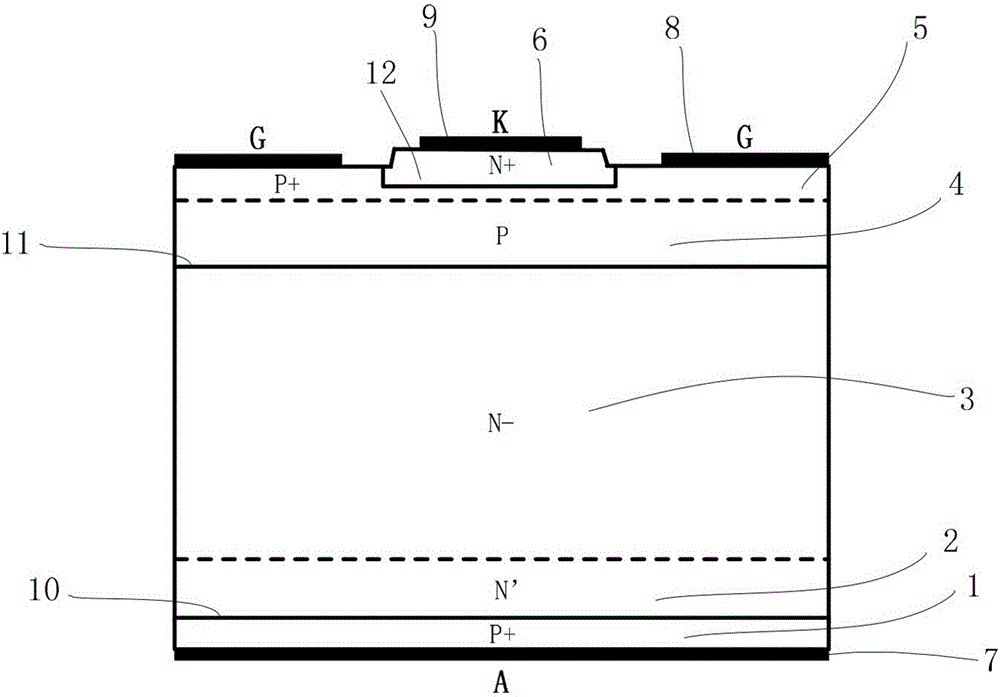

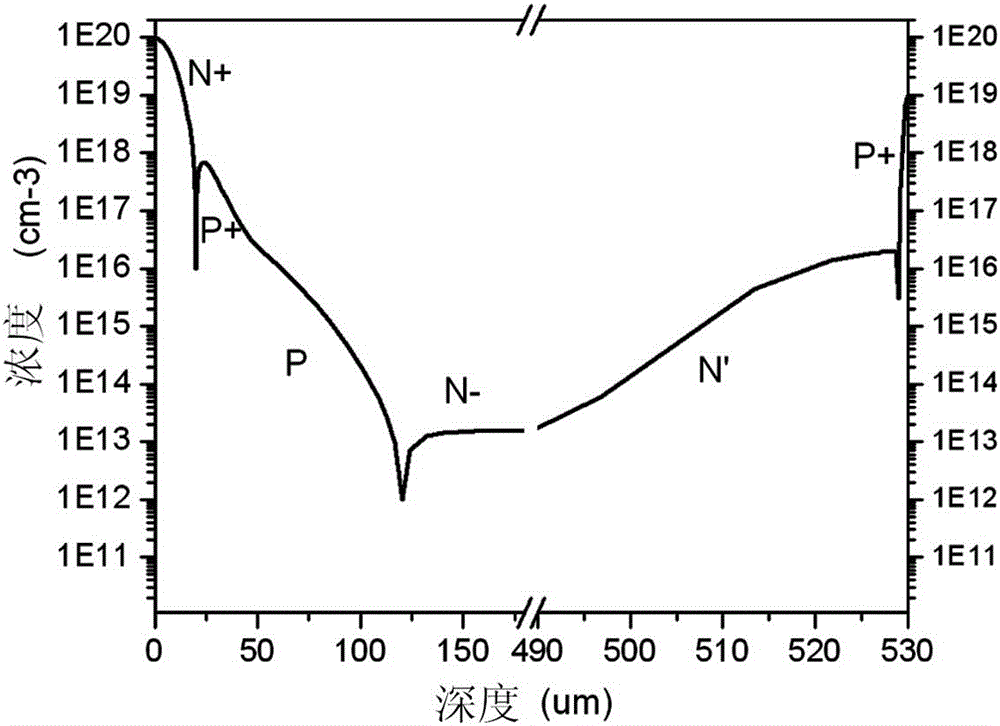

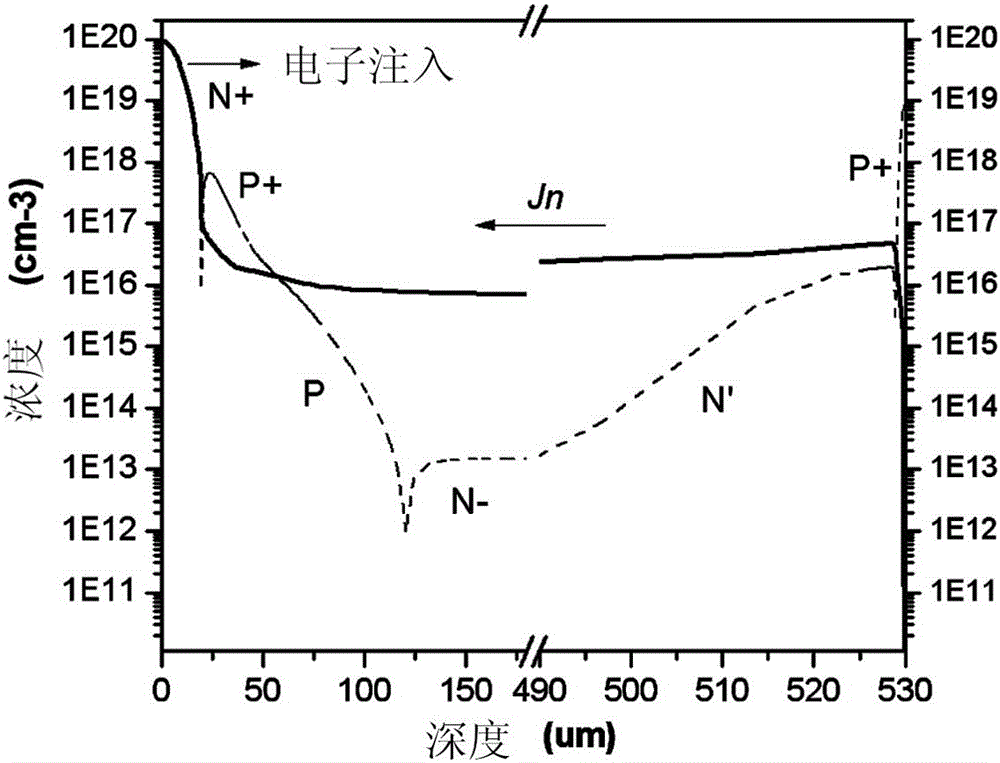

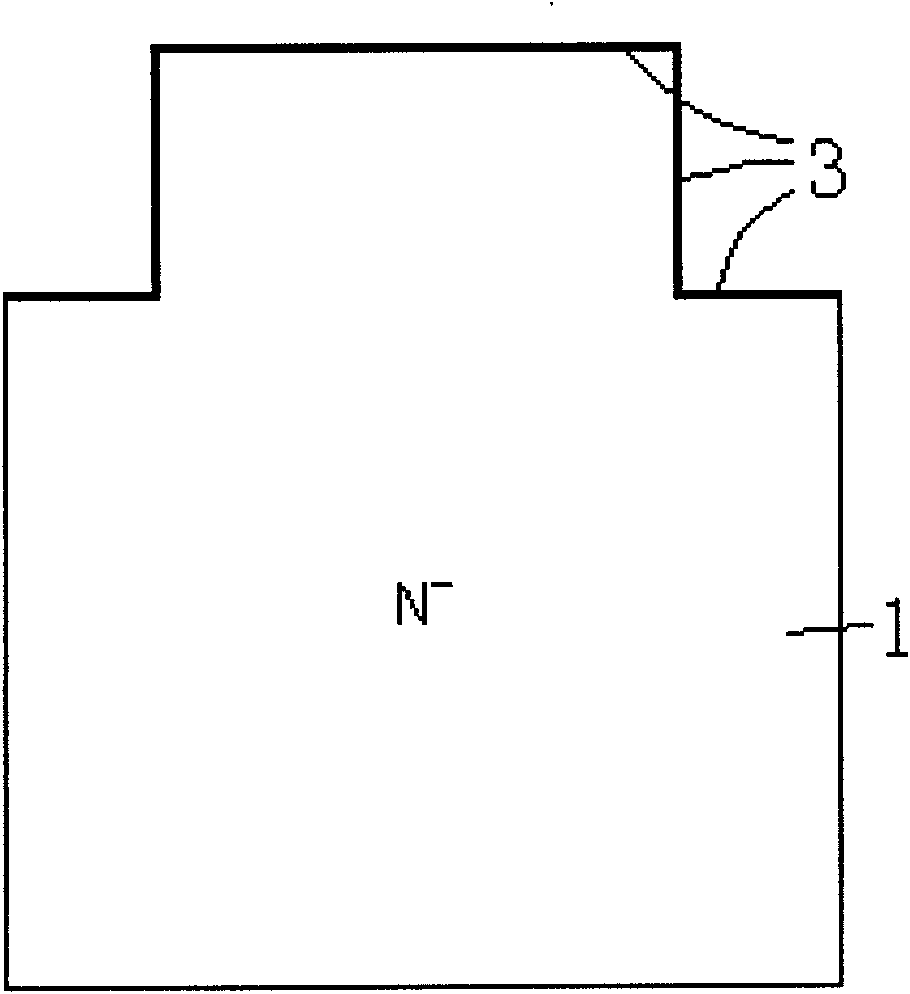

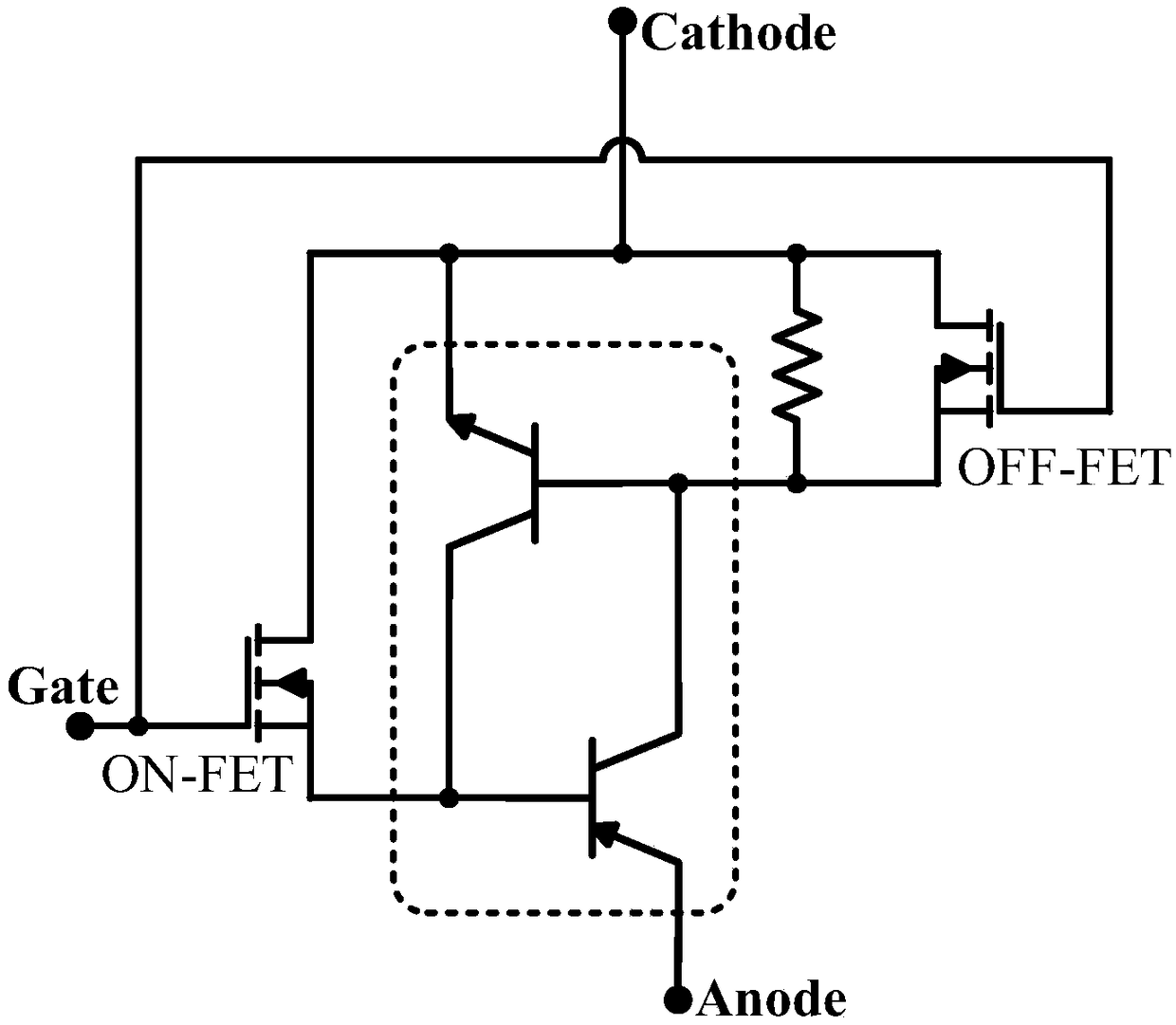

Thyristor gate cathode structure and gate pole commutation thyristor with thyristor gate cathode structure

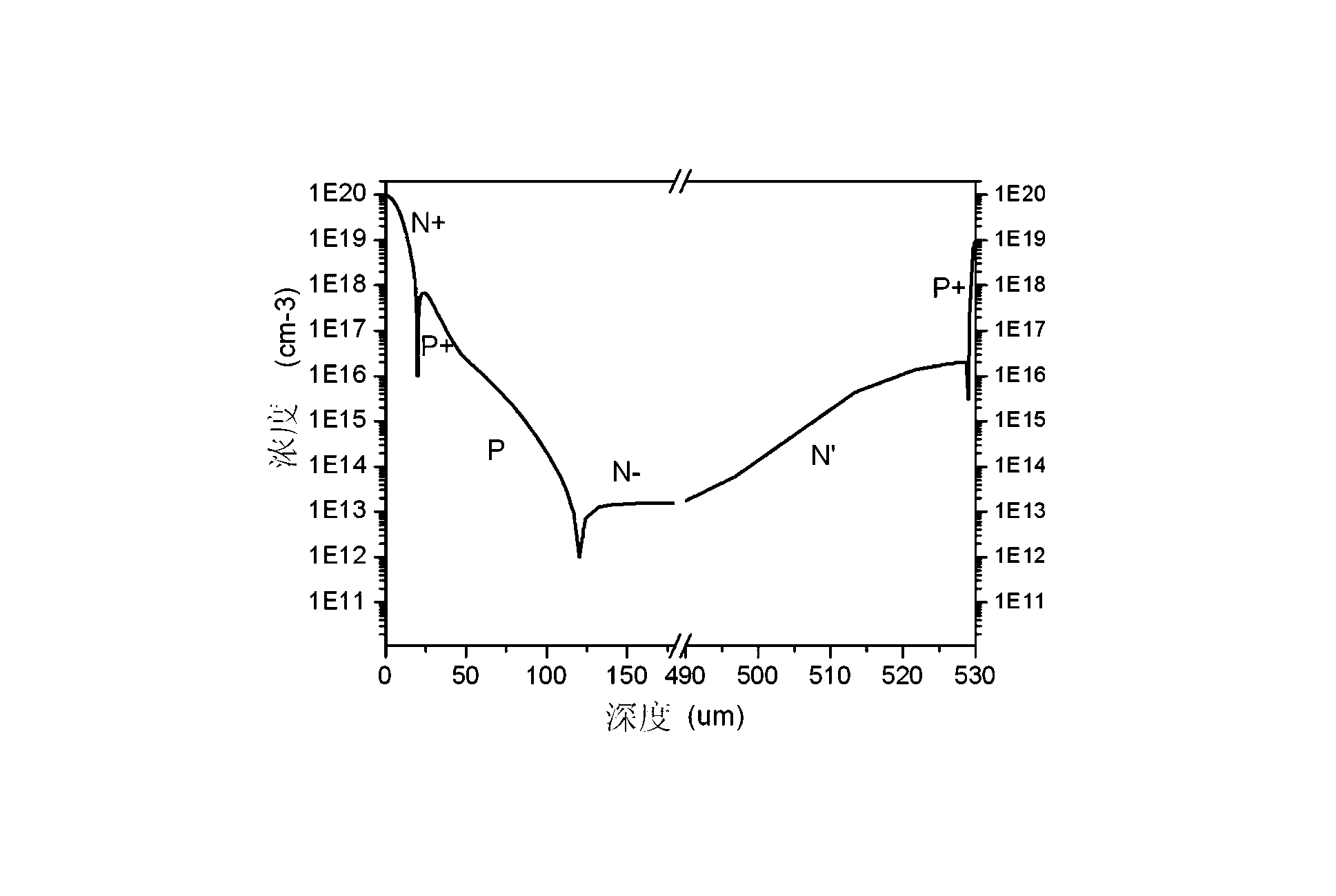

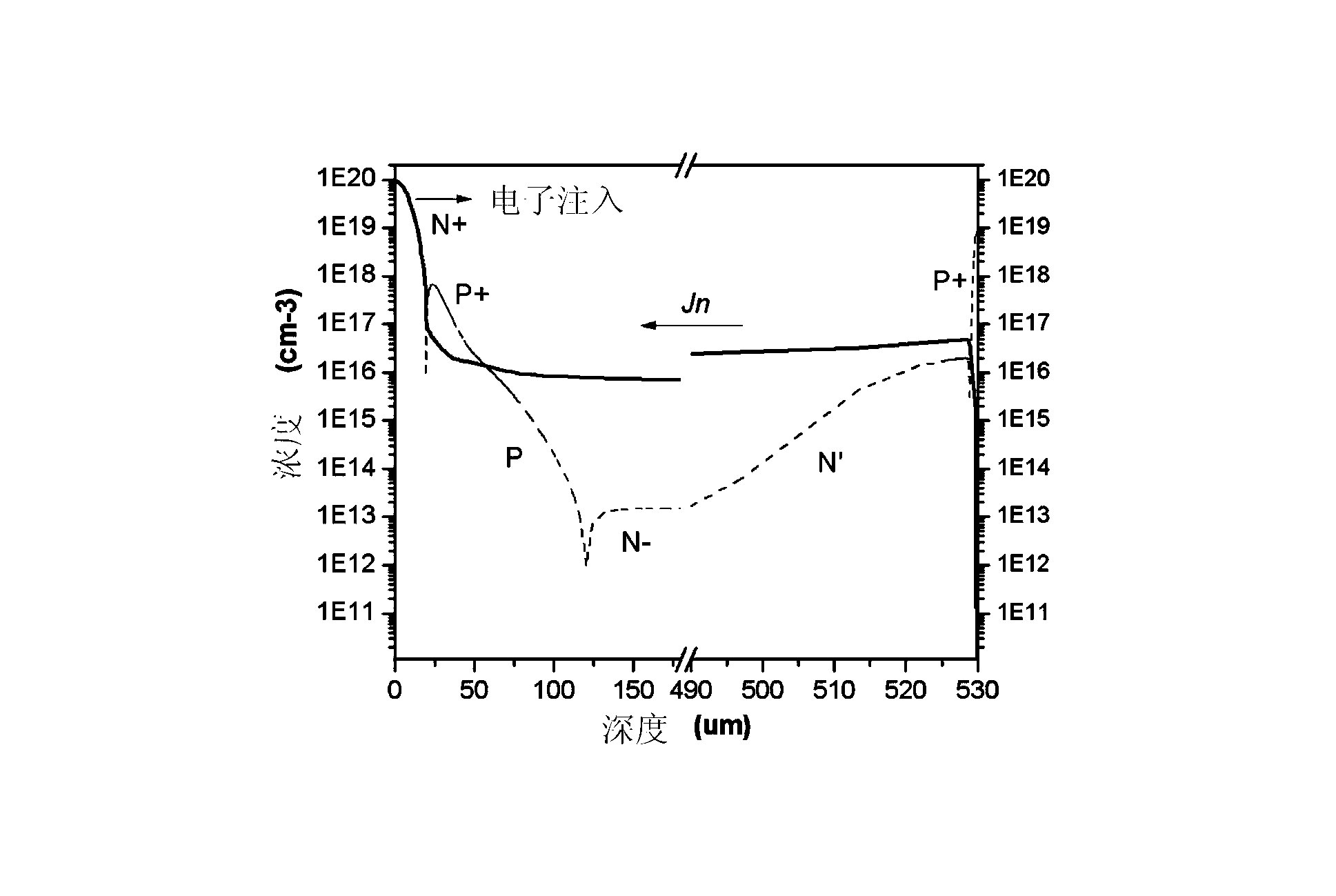

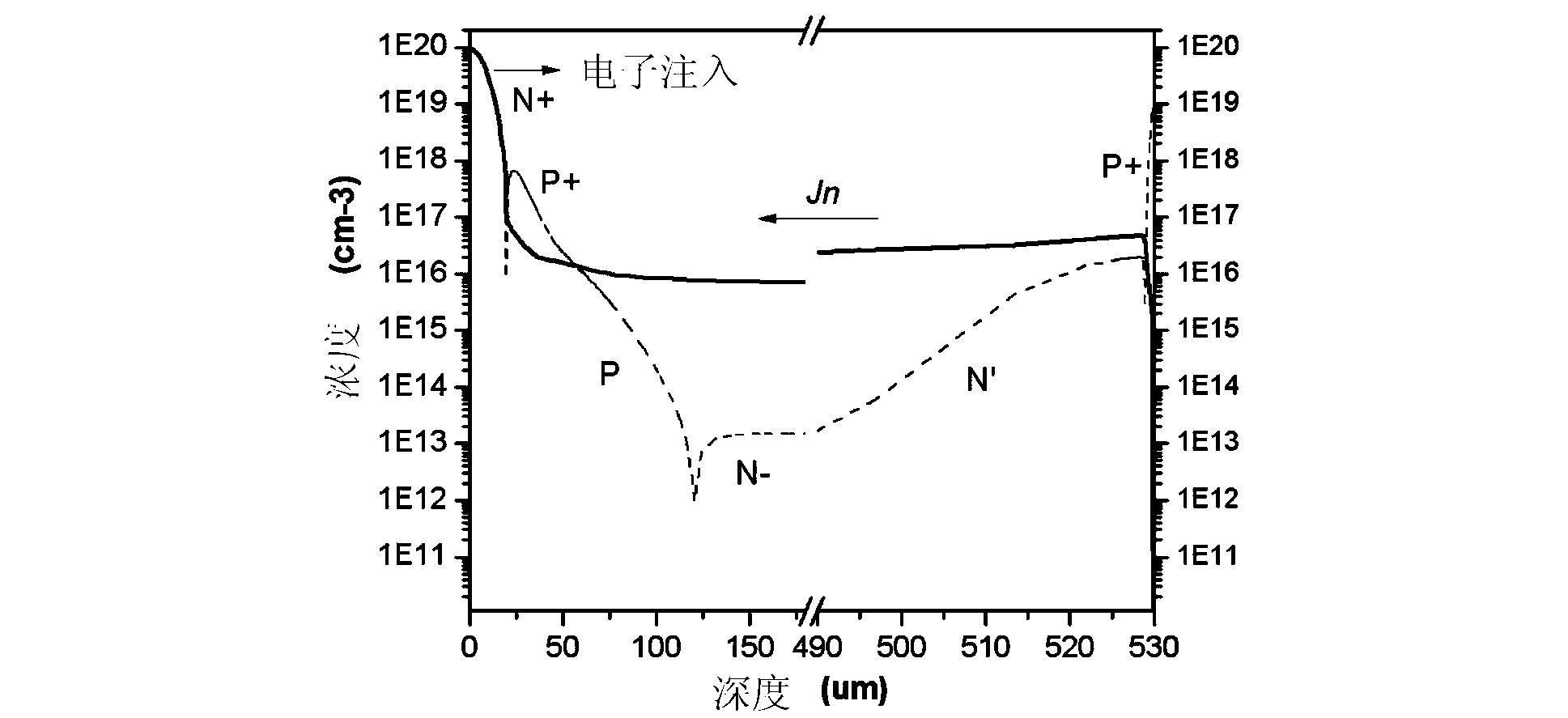

The invention discloses a thyristor gate cathode structure and a gate pole commutation thyristor with the thyristor gate cathode structure. The thyristor comprises an N-substrate, a P base region, a P+ short base region, an N+ emitter region, a door pole metal electrode and a cathode metal electrode. The N+ emitter region, the P+ short base region, the P base region and the N-substrate are sequentially distributed, the cathode metal electrode is arranged on the outer surface of the N+ emitter region, and the door pole metal electrode is arranged on the outer surface of the P+ short base region. The thyristor gate cathode structure is of a two-layer step structure, wherein the first layer of steps is a shallow step, and the bottom of the first layer of the steps is a P+N+ boundary. The second layer of the steps is a deep step, and the bottom of the second layer of the steps is a PN+ boundary. The gate pole commutation thyristor with the thyristor gate cathode structure further comprises an N' buffer layer and a P+ anode region. The combination of electrons injected in the N+ emitter region of the thyristor is reduced at the P+ short base region and the P base region, conductivity modulation effects of the thyristor are intensified, and connected currents and the starting speed can be further improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

IGBT device and manufacturing method thereof

InactiveCN103794638AIncrease the doping concentrationEnhanced conductance modulation effectTransistorSemiconductor/solid-state device manufacturingOptoelectronicsConduction loss

The invention discloses an IGBT device and a manufacturing method thereof. The IGBT device comprises a substrate which comprises a drift region; a grid electrode structure and a source electrode structure which are arranged on the front surface of the substrate, and the source electrode structure comprises a trap region which is arranged in the surface of the drift region and a source region which is arranged in the surface of the trap region; a carrier storage layer which is arranged in the surface of the drift region and below the trap region, a gap is arranged between the carrier storage layer and the bottom part of the trap region, a doping type of the carrier storage layer and the doping type of the drift region are identical and doping concentration of the carrier storage layer is greater than that of the drift region; and a current collection region which is arranged on the back surface of the substrate, and the doping types of the current collection region and the drift region are opposite. The IGBT device is lower in conduction pressure drop and thus is low in conduction loss.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Insulated gate bipolar translator (IGBT) device with two short-circuit positive electrodes

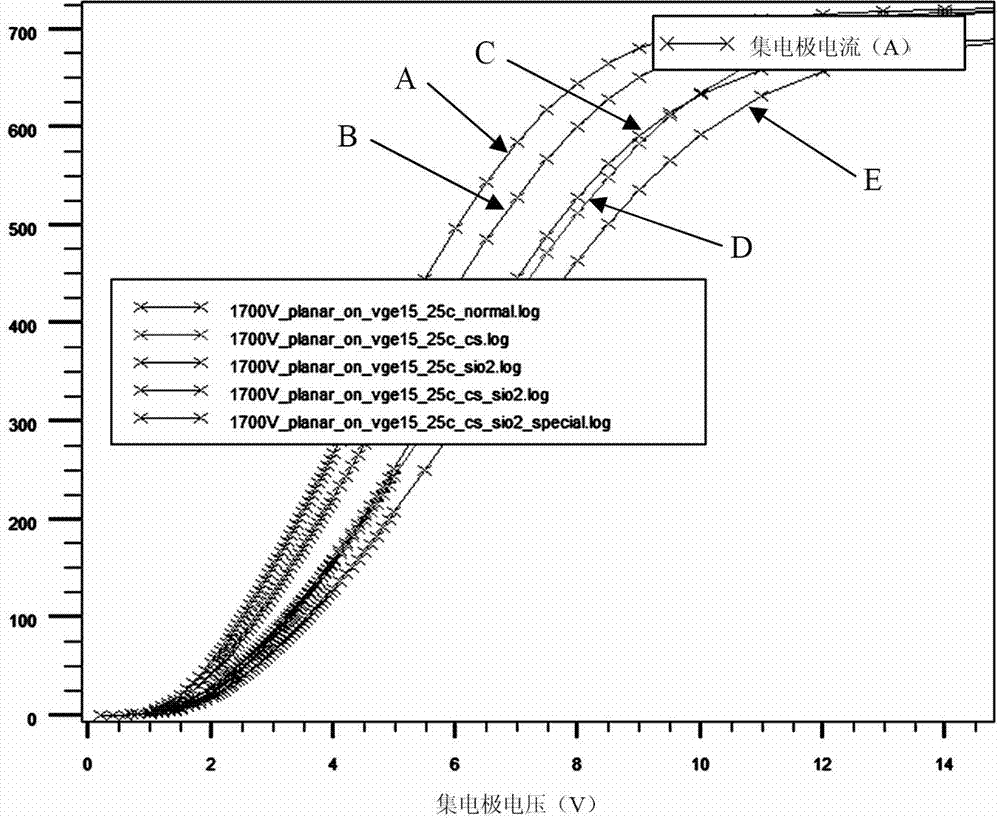

InactiveCN102544084AAnode Structure ImprovementReduce forward voltage dropSemiconductor devicesConductivity modulationSilicon dioxide

The invention discloses an insulated gate bipolar translator (IGBT) device with two short-circuit positive electrodes, and belongs to the technical field of semiconductor power devices. A positive electrode structure of the device is a two-positive-electrode short-circuit structure. The IGBT device comprises a first P+ hole emission layer, a second P+ hole emission layer, a metal collector and a silicon dioxide barrier layer, wherein the silicon dioxide barrier layer is positioned on the back face of the first P+ hole emission layer; the metal collector is positioned on the side face of the first P+ hole emission layer and below the second P+ hole emission layer, and the two P+ hole emission layers are contacted with each other; the second P+ hole emission layer is positioned at the bottom of an N- drift region and staggered in parallel with the first P+ hole emission layer; and an electronic trench is formed between the first P+ hole emission layer and the second P+ hole emission layer. The positive electrode structure of the IGBT device is improved, so that the hole injection efficiency is improved, the current carrier concentration distribution in the drift region is optimized, the conductivity modulation performance in the device body is improved, a negative differential resistance (NDR) region is eliminated effectively, the cut-off loss of the IGBT device is reduced effectively, and finally, compromise optimization for conductivity pressure drop and cut-off loss is realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

A charge storage type insulated gate bipolar transistor and a preparation method thereof

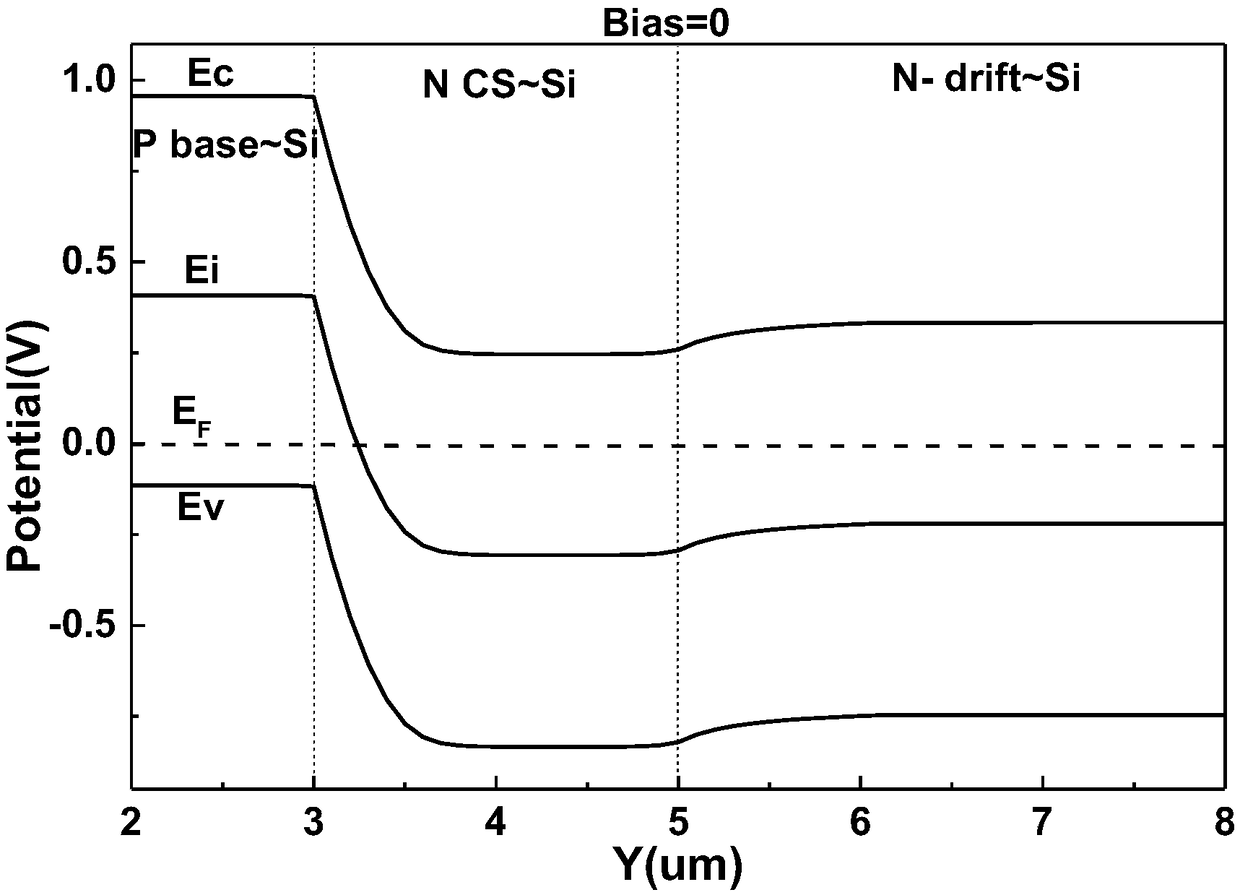

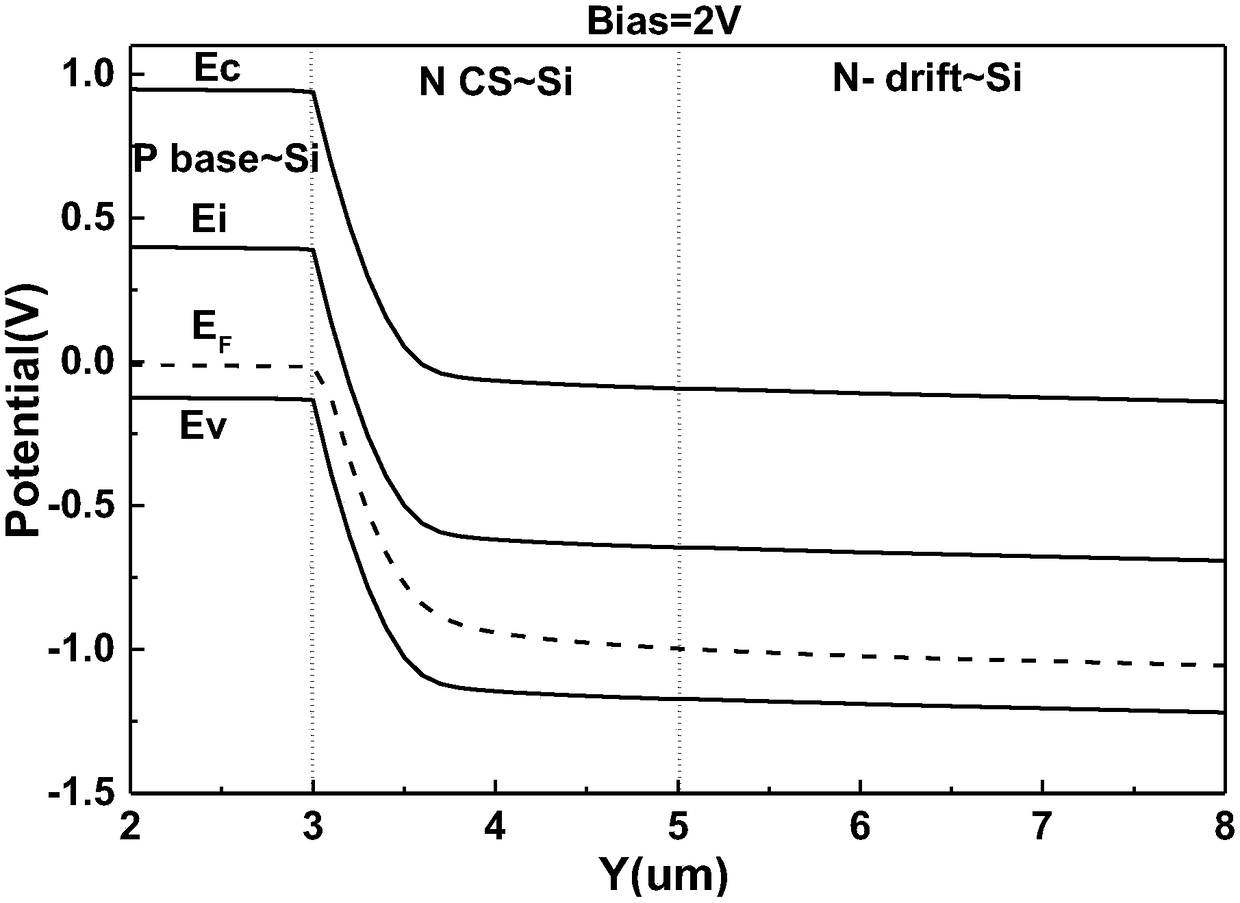

ActiveCN109192771AImprove concentration distributionImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

The invention relates to a charge storage type insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. By improving the charge storage layer of the traditional charge storage type IGBT device, a semiconductor material used for the charge storage layer remote from the drift region has a larger band gap than a semiconductor material used for the charge storage layer close to the drift region, so that the semiconductor materials with different forbidden band widths form the same-type heterojunction at their contact interfaces,thereby forming a potential barrier that prevents minority carriers in the drift region from entering the base region. As a result, the carrier distribution concentration in the drift region is improved, the conductivity modulation effect of the IGBT is enhanced, the forward conduction voltage drop Vceon of the device is reduced, the breakdown voltage of the IGBT is optimized, and the tradeoff between the forward conduction voltage drop Vceon and the shutdown loss Eoff is achieved. Moreover, by adjusting the doping concentration of materials with different bandgap widths in the charge storagelayer and the combination of materials with different bandgap widths, the invention can further optimize the working characteristics of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A planar insulated gate bipolar transistor and a preparation method thereof

ActiveCN109166917AImprove breakdown voltageImprove reliabilityTransistorSemiconductor/solid-state device manufacturingHeterojunctionParasitic bipolar transistor

The invention relates to a planar insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. A semiconductor layer or Schottky contact metal having a relatively small band gap is introduced into the upper surface of the base region of the device adjacent to the outer side of the emitter region, By using heterojunction or Schottky contact as minority carrier barrier to enhance the conductivity modulation effect, the conduction voltage drop is reduced and the tradeoff between forward voltage drop and turn-off loss is optimized. As the heterojunction or Schottky contact introduced by the invention can replace the CS layer functionally, the electric field strength of the PN junction formed in the base region and the drift region is reduced to improve the breakdown voltage of the device; And the electric field intensity of the gate oxide layer is below the safe value (3MV / cm), so the reliability of the gate oxide layer is ensured. In addition, the fabrication process of the device is simple and controllable, and the device has strong compatibility with the existing process.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method for manufacturing trench gate type IGBT (insulated gate bipolar transistor) chip

ActiveCN102945804BIncrease hole concentrationImprove injection efficiencySemiconductor/solid-state device manufacturingDielectricButt joint

The invention discloses a method for manufacturing a trench gate type IGBT (insulated gate bipolar transistor) chip, which comprises the following steps: selecting two N-shaped semiconductor substrates, and carrying out oxidation or deposition on one of the substrates, so that insulating materials including silicon oxides or nitric oxides are formed on the surface of the substrate; carrying out photoetching and etching on the insulating materials on the surface of the substrate so as to form a dielectric buried layer; carrying out photoetching and etching on the other substrates so as to form a figure coincided with the concave-convex surface of the dielectric buried layer; carrying out concave-convex surface butt-joint on the dielectric buried layer and the figure, and bonding the two substrates together at high temperature; according to voltage-withstanding requirements and machining allowances, respectively carrying out thinning processing on the two substrates, and controlling the dielectric buried layer at a design depth, so that a chip manufacturing intermediate is formed; and completing the manufacturing process of a trench gate type IGBT chip. According to the invention, the drop voltage of the chip is reduced, a compromising relation with shut-off loss is optimized, and the lower power consumption is realized, thereby improving the power density, operating junction temperature and reliability of the IGBT chip.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

SOI-LIGBT (Silicon on Insulator-Lateral Insulated-Gate Bipolar Transistor) device based on double channel structure

InactiveCN102956687ALower base resistanceLower resistanceSemiconductor devicesThyratronTotal current

The invention discloses an SOI-LIGBT (Silicon on Insulator-Lateral Insulated-Gate Bipolar Transistor) device based on a double channel structure. The SOI-LIGBT apparatus based on the double channel structure comprises a P type substrate, wherein a buried oxide layer is paved on the P type substrate, an N-epitaxial layer is paved on the buried oxide layer, a P+ collector region is embedded on the N-epitaxial layer, and two symmetrical body region structures are arranged in parallel on the N-epitaxial layer on one side of the P+ collector region. Each body region structure comprises a P well arranged on the N-epitaxial layer, an N+ emitter region embedded on the P well and a P+ contact region penetrating through the P well. According to the SOI-LIGBT device based on the double channel structure provided by the invention, two channel regions are arranged at the emitter region so that the cavity current flowing from the collector to the emitter is uniformly divided into two strands of current, therefore, the current flowing through a base electrode of a parasitic NPN triode is reduced to 50% of the total current. A parasitic thyristor is inhibited from being opened and the anti-latch capacity of the device is improved, so that the reliability of the device is improved.

Owner:ZHEJIANG UNIV

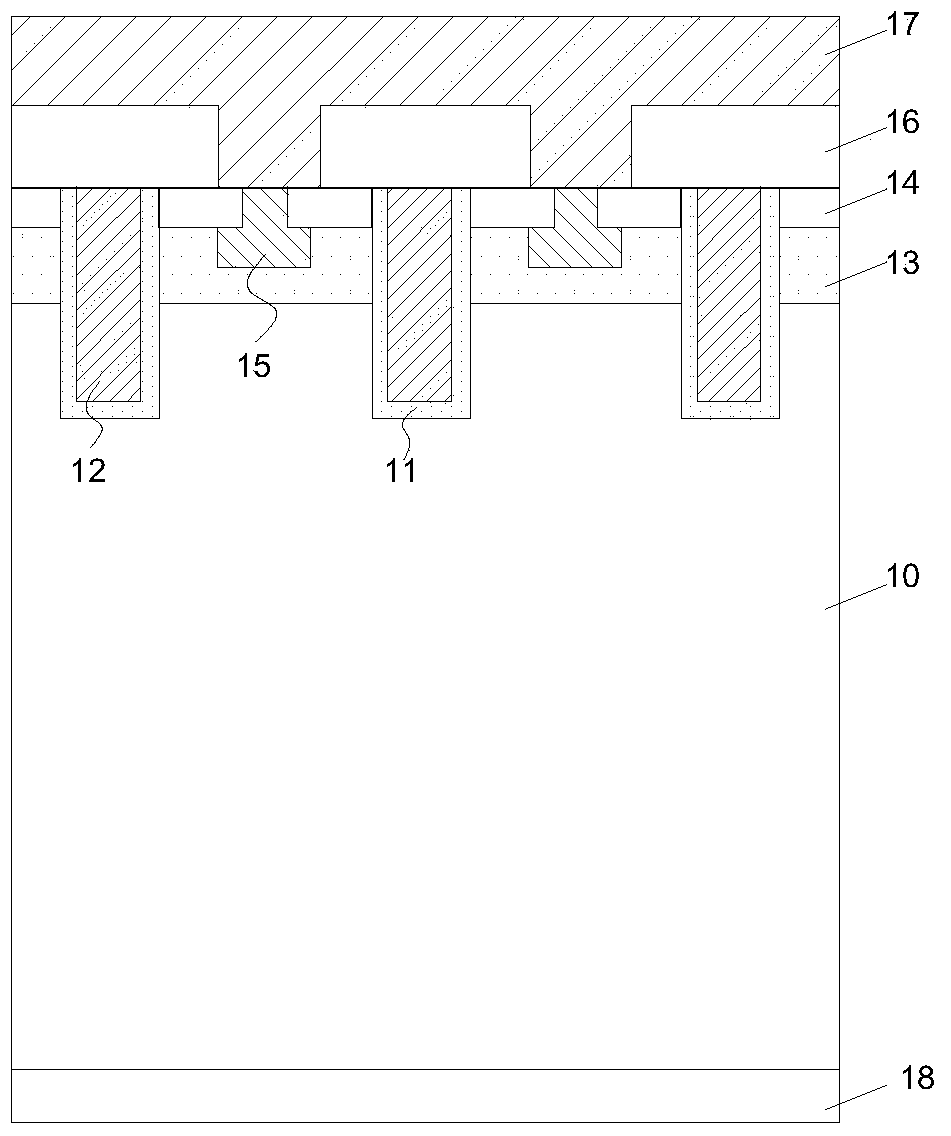

Split gate CSTBT with PMOS current clamping and manufacturing method of split gate CSTBT

ActiveCN110600537AImprove saturation currentImprove doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

The invention belongs to the technical field of a power semiconductor device and relates to a split gate CSTBT with PMOS current clamping and a manufacturing method of the split gate CSTBT. A PMOS structure is introduced on the basis of a traditional CSTBT, a saturation current during forward conduction of a device is effectively improved, the short-circuit safe working capability of the device isimproved, moreover, the influence of an N-type charge storage layer 14 on the breakdown characteristic of the device is eliminated, therefore, the doping concentration of the N-type charge storage layer 14 can be improved to improve carrier distribution during forward conduction of the device, so the conductivity modulation capability of a drift region is improved, forward conduction voltage dropof the device is reduced, the gate capacitance, especially the Miller capacitance, of the device is reduced by an L-shaped separated gate structure, the switching speed of the device is improved, switching loss of the device is reduced, since a separation gate and the gate structure are integrated in the same groove, the area of a chip is saved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

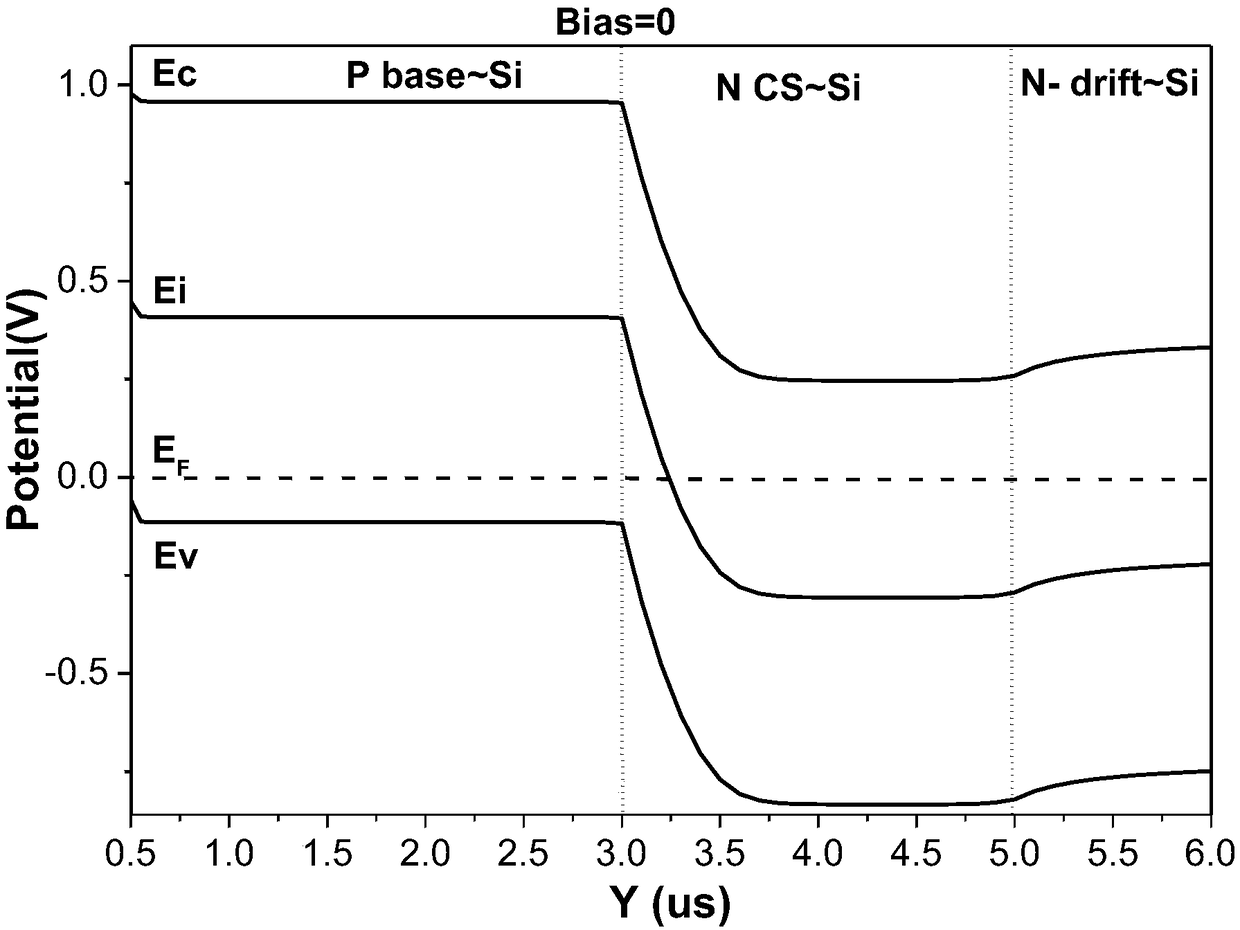

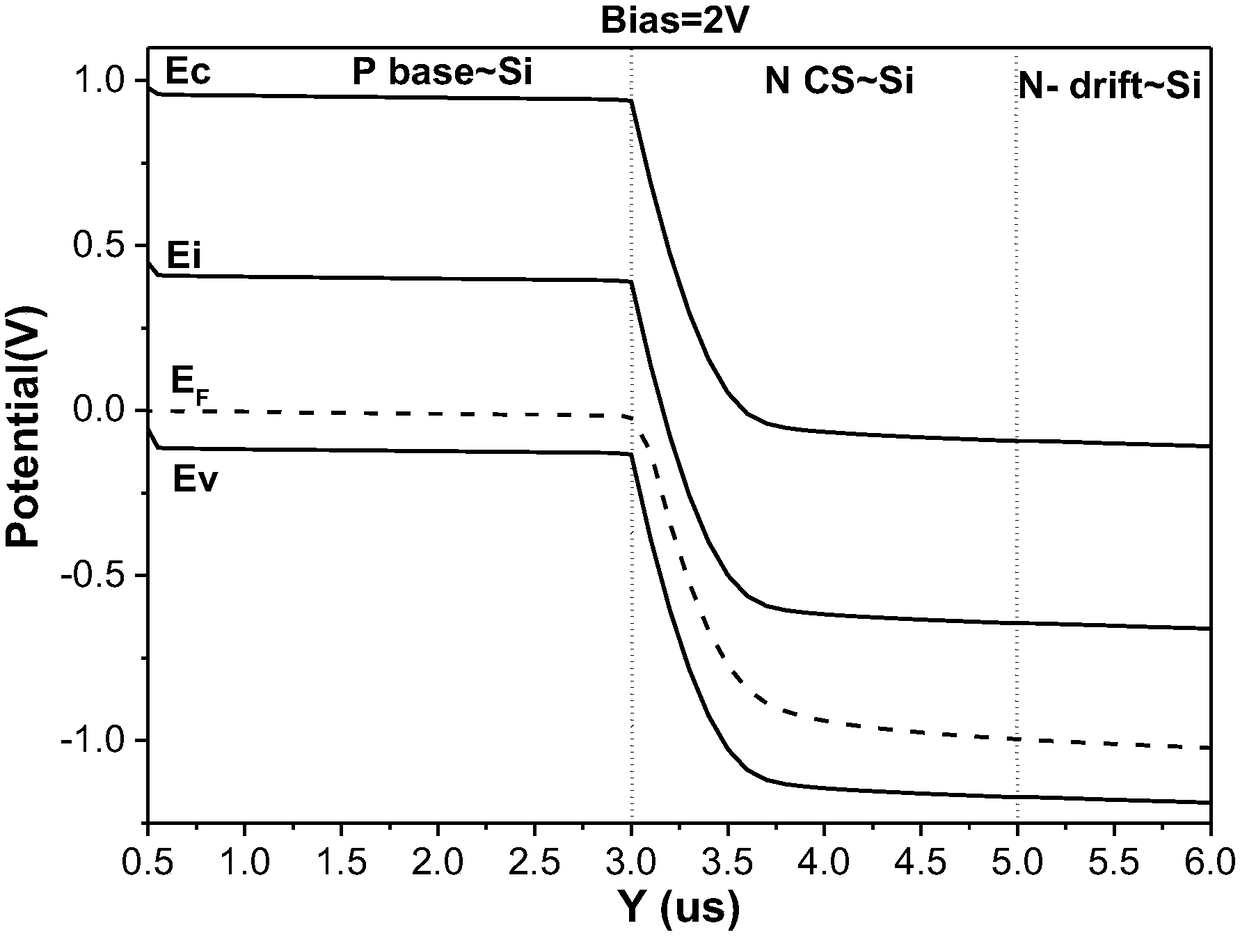

An insulated gate bipolar transistor and a preparation method thereof

ActiveCN109166916AImprove concentration distributionImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

The invention relates to an insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. On the basis of the traditional charge storagetype IGBT device structure, A heterojunction structure is formed in the base region, thereby forming a potential barrier that prevents minority carriers in the drift region from flowing into the baseregion, thereby greatly increasing the minority carrier concentration near the emitter side in the drift region, The carrier concentration distribution in drift region is improved and the conductivity modulation effect of IGBT is enhanced, which reduces the forward conduction voltage drop Vceon and optimizes the tradeoff between the forward conduction voltage drop Vceon and the shutdown loss Eoffof IGBT. It overcomes the shortcoming that the traditional charge storage layer reduces Vceon and breakdown voltage at the same time. Moreover, the device performance can be further optimized by adjusting the combination of semiconductor materials with different forbidden band widths to form heterojunction structures.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

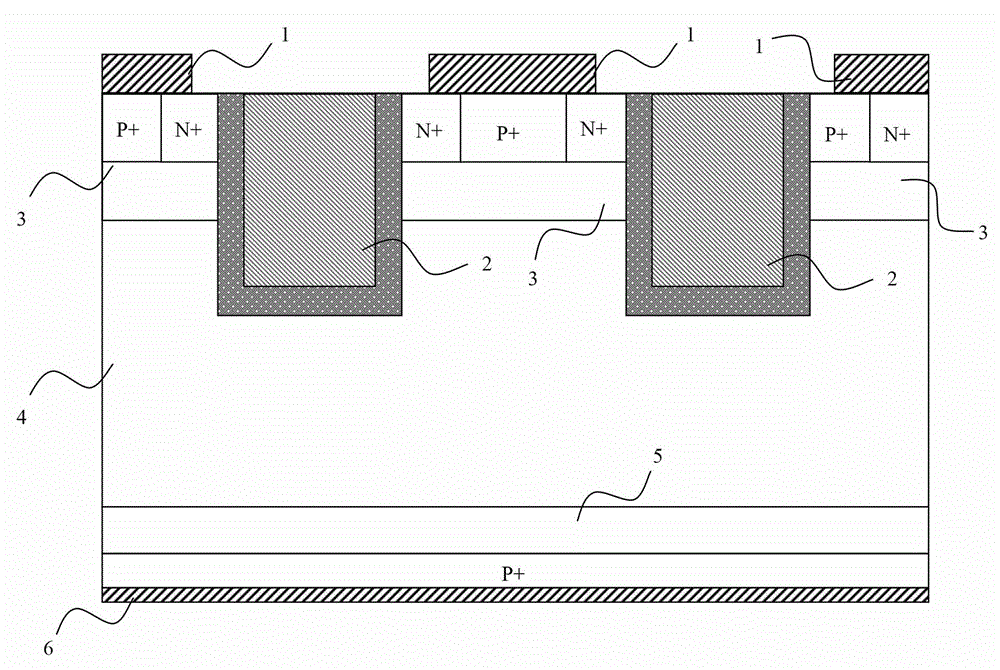

Groove type IGBT and manufacturing method

ActiveCN104241126AEnhanced conductance modulation effectReduce thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthModulation effect

The invention discloses a groove type IGBT and a manufacturing method. A P type region with heavy doping and an N type region with heavy doping are added in the middle region of a silicon substrate, so that electrons are induced to flow in an N junction region to be concentrated, penetrate through the P type region and finally reach a collector through the P type region. Based on the electric neutrality principle, the concentration of the electrons on the periphery of the N type region is increased due to the concentration of the electrons, the concentration of holes in the periphery of the N type region is increased, so that the conductance modulation effect of the N type region is increased due to the concentration of the electrons, and the holes are diffused to an emitter through the P type region. According to the groove type IGBI manufacturing method, the charge balance principle is utilized, the electric field intensity in the region is increased so that larger voltage can be obtained under the same drift region thickness, the thickness is reduced, the conductance modulation effect is improved, and the conduction voltage drop of a device is effectively reduced.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

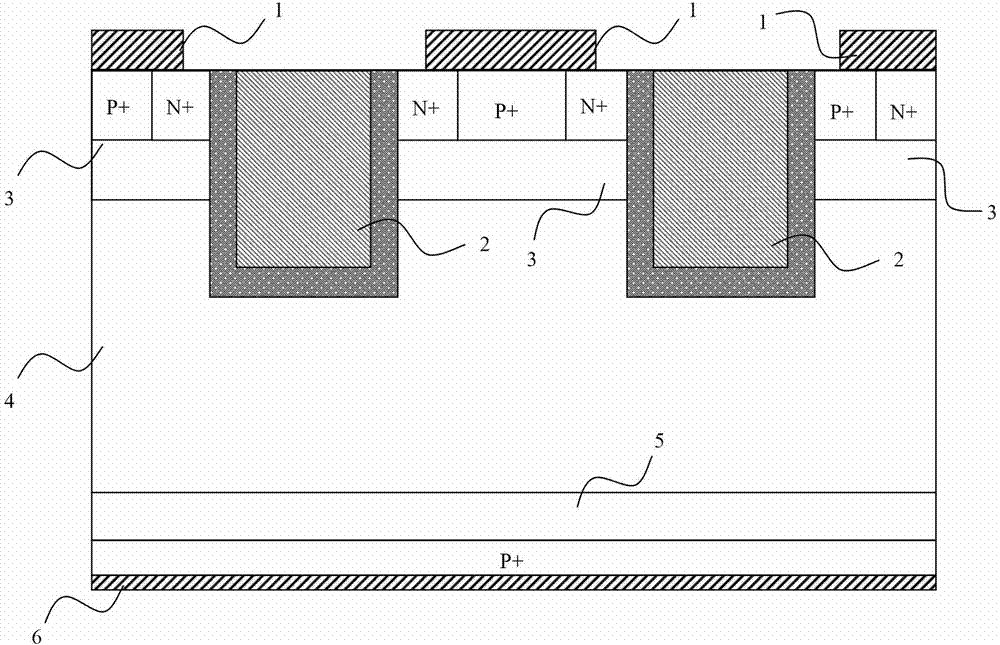

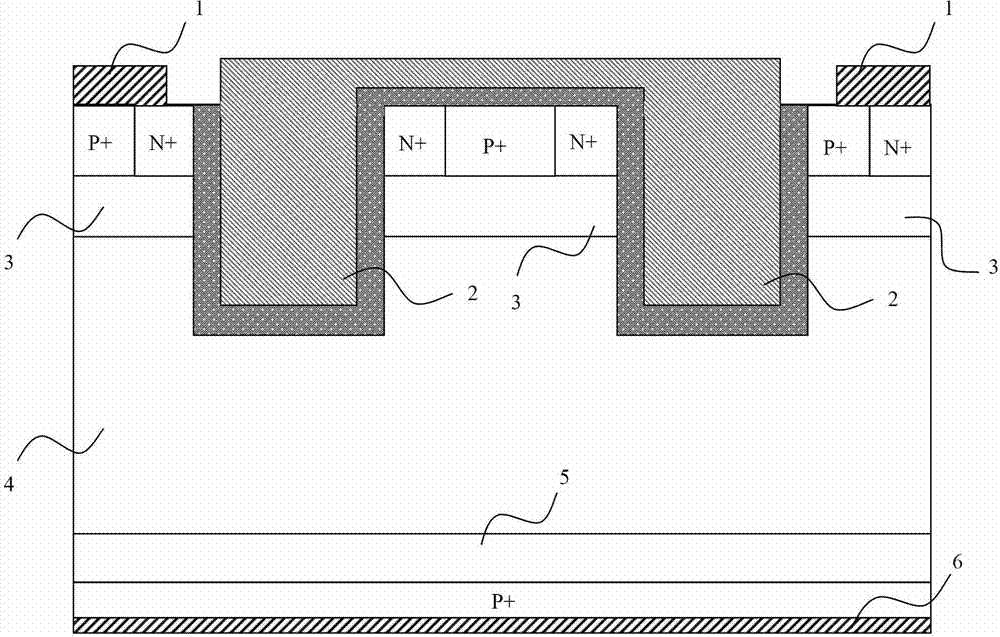

Low on-state loss insulated gate bipolar translator (IGBT) and manufacturing method thereof

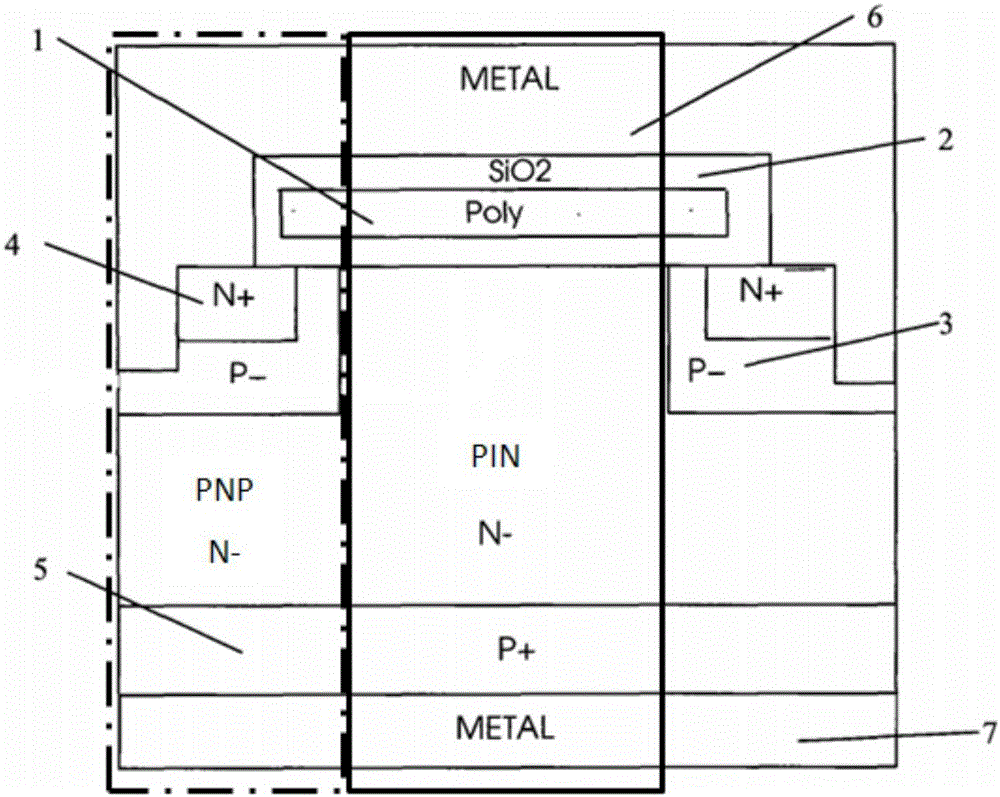

ActiveCN105047706AIncrease the area of the PIN areaEnhanced conductance modulation effectTransistorSemiconductor/solid-state device manufacturingCell regionEngineering

The invention provides a low on-state loss insulated gate bipolar translator (IGBT) and a manufacturing method thereof. The IGBT comprises an active region, a terminal region and a gate region, wherein the active region comprises an N-substrate region, a gate oxidation layer, a polycrystalline silicon gate, a P-base region, an N+ emitter region, a P+ collector region, emitter metal and collector metal; the active region is a cell region; a dummy cell structure is formed in the active region; the dummy cell structure is formed by sacrificing a cellular local channel; and the cellular local channel is sacrificed by changing one or combination of more of a pressure ring layer, a field oxide layer, a polycrystal layer and a contact hole layer. According to the manufacturing method provided by the invention, an invalid cell is introduced into the active region; the PIN / PNP region distribution of the active region is changed; the conductivity modulation effect of the cell of the IGBT is optimized; the saturation voltage of the IGBT is reduced; the current density of the IGBT is improved; and the on-state loss of the IGBT is reduced. The IGBT chip manufactured by the method has advantages in the field of high power density and low on-state loss application.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

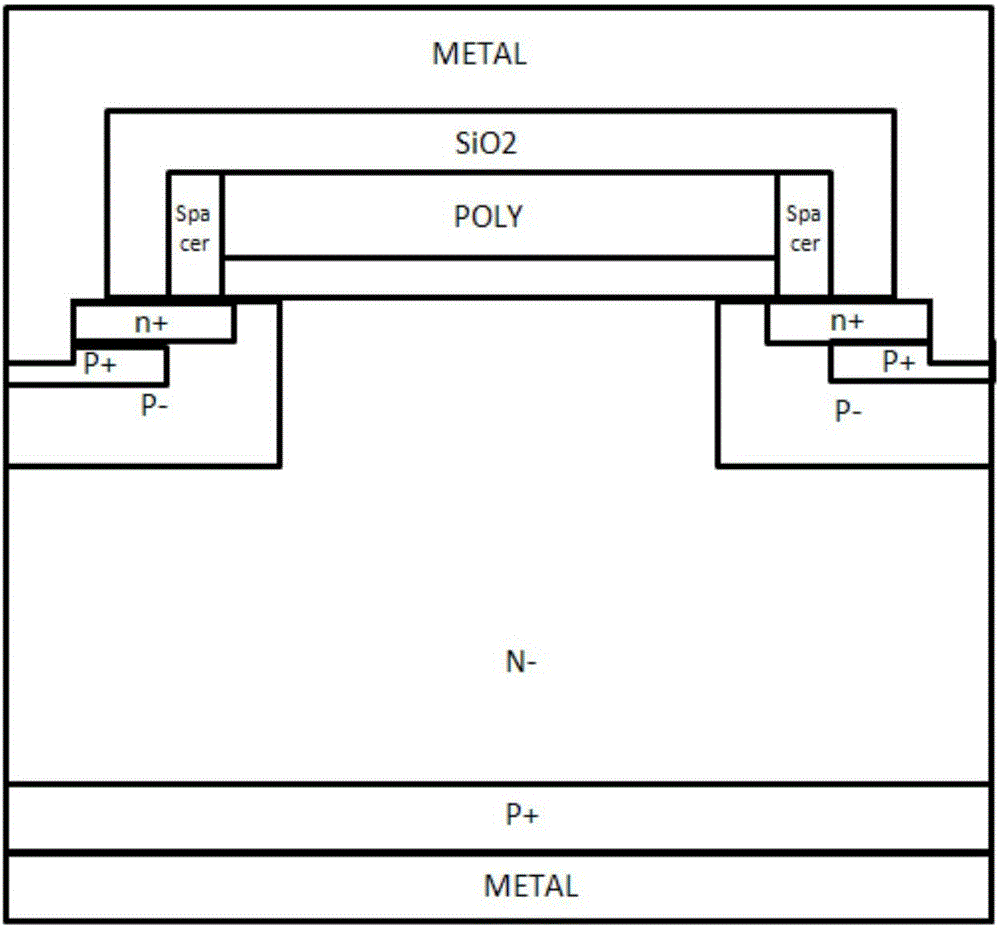

Planar gate IGBT (Insulated Gate Bipolar Transistor) chip

ActiveCN102969351BReduce conduction voltage dropImprove the conduction voltage dropSemiconductor devicesOhmic contactCharge carrier

The invention discloses a planar gate IGBT (Insulated Gate Bipolar Transistor) chip, which comprises a collector metal electrode, a P+ collector region, an N- drift region, a P- base region, a P+ ohmic contact region, an N+ source region, a gate oxide layer, a polysilicon gate and a gate metal electrode which are arranged successively, and an emitter metal electrode arranged above the P+ ohmic contact region, wherein the polysilicon gate of the planar gate IGBT chip adopts a planar gate structure. The planar gate IGBT chip also comprises a first N-type carrier buried layer and / or a second N-type carrier buried layer. The first N-type carrier buried layer is located below the P- base region. The second N-type carrier buried layer is located below the gate oxide layer and at both sides of the P- base region. The planar gate IGBT chip has the beneficial effects that the compromise relation between conduction pressure drop and turn-off loss of the IGBT is reduced, lower power consumption is realized, and thus the power density, the operating junction temperature and the long-term reliability of the IGBT chip are increased.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Separated gate CSTBT with self-biased PMOS and manufacturing method thereof

ActiveCN113838920AIncrease the doping concentrationImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceChannel density

The invention relates to a separated gate CSTBT with a self-biased PMOS and a manufacturing method of the separated gate CSTBT, and belongs to the technical field of power semiconductor devices. According to the present invention, on the basis of the traditional CSTBT, a separated gate electrode equipotential with the emitter and a P-type buried layer are introduced, the influence of an N-type charge storage layer on the breakdown characteristic of a device can be effectively shielded through charge compensation, and the compromise relation between the forward conduction voltage drop Vce (on) and the turn-off loss Eoff of the device can be improved. In addition, the separated gate electrode and a gate electrode are located in a same groove, so that the channel density can be reduced; the saturation current density is effectively reduced by turning on a parasitic PMOS to clamp the potential of the N-type charge storage layer, and the short-circuit safe working capability of the device is improved. Meanwhile, the gate capacitance can be reduced, the switching speed of the device is improved, and the switching loss of the device is reduced. In addition, the current uniformity in a chip can be improved, the current concentration is avoided, and the reliability and a reverse bias safety working area of the device are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Preparation methods of thyristor gate cathode junction and gate commutated thyristor with thyristor gate cathode junction

ActiveCN103227112AIncrease the on-currentEasy injectionSemiconductor/solid-state device manufacturingPower flowThyratron

The invention discloses a preparation method of a thyristor gate cathode junction and a preparation method of a gate commutated thyristor with the thyristor gate cathode junction. The preparation method of the thyristor gate cathode junction comprises the following steps of preparing an N-type substrate, conducting selective P+ diffusion treatment on the front surface of the N-type substrate to form a P+ short base region, conducting P diffusion treatment on the front surface of the N-type substrate to form a P base region, conducting N+ predeposition treatment to form an N+ layer, conducting gate etching treatment to etch off the N+ layer above a gate, conducting N+ boosting treatment on the N+ layer to form the gate cathode junction in a double-step structure, and conducting metal deposition and etching treatment to form a cathode metal electrode and a gate metal electrode respectively. According to the preparation methods of the thyristor gate cathode junction and the gate commutated thyristor with the thyristor gate cathode junction, the recombination of electrons injected into an N+ emitting region of the thyristor in the P+ short base region and the P base region can be reduced, a conductive modulation effect of the thyristor is improved, and the breakover current and breakover speed of the thyristor can be further increased.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Trench type insulated gate bipolar transistor and preparation method thereof

ActiveCN110416295AReduce capacitanceFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsTrade offs

The invention provides a trench type insulated gate bipolar transistor and a preparation method thereof, which belong to the technical field of power semiconductors. According to the invention, a narrow bandgap semiconductor material is used to form a conductive channel and form ohmic contact with emitter metal due to the characteristics of high channel mobility of a narrow bandgap material such as silicon and small ohmic contact resistance with the emitter metal; channel resistance and ohmic resistance are reduced; the forward conduction voltage drop of a device is reduced; in addition, due to the characteristic of high critical breakdown field strength of a wide bandgap material such as silicon carbide, the device is not limited by a gate oxide layer and prevented from avalanche breakdown; the position of a breakdown point is changed; the breakdown voltage of the device is improved to a certain extent, so that the thickness of a drift region can be appropriately reduced at a certainvoltage level; the forward conduction voltage drop and the turn-off loss are further reduced; and the trade-off relationship between the turn-on voltage drop and the turn-off loss is optimized. In addition, the invention further provides a preparation method of the trench type insulated gate bipolar transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Gate-cathode junction of thyristor and gate-commutated thyristor having the structure

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Semiconductor device and manufacture method thereof

InactiveCN102738210AEnhanced conductance modulation effectIncrease current densitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSemiconductor materials

The invention discloses a semiconductor device having a trench structure. A surface of an N-type conductive semiconductor material is provided with trenches, an entire area of an upper part of the semiconductor material between the trenches is a P-type conductive material area, and a passivation layer is disposed on an upper surface of the P-type conductive material area. The P-type conductive material area is also disposed in the semiconductor material on corners of trench bottom edges. And Schottky barrier junctions are disposed on side walls of the trenches and surfaces of a bottom N-type conductive semiconductor material. The invention also provides a manufacture method for the semiconductor device, and through the manufacture method, a rapid-recovery diode can be made by twice photolithography technique.

Owner:ZHEJIANG UNIV

Insulated gate bipolar transistor and manufacturing method thereof

InactiveCN101877359AEnhanced conductance modulation effectIncrease the effective areaSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic bipolar transistorVoltage drop

The invention provides an insulated gate bipolar transistor, which is manufactured by using a silicon chip. The insulated gate bipolar transistor comprises a P+ region, an N- region, a P region and an N+ region, wherein the P region and the N+ region are positioned on the front surface of the silicon chip; the P+ region is positioned on the back surface of the silicon chip; and the P+ region comprises a plurality of P-type impurity regions which are longitudinally distributed in a doping way. The invention also provides a method for manufacturing the insulated gate bipolar transistor. As the P+ region comprises the plurality of P-type impurity regions to increase the effective area of an emitter and increase injected P-type impurities, cavity minority carriers injected into the N- region are increased, conductivity modulation effect on the N- region is enhanced, the on-state voltage drop of the insulated gate bipolar transistor is reduced and the loss of own power of the insulated gate bipolar transistor is further reduced.

Owner:商海涵

Injection reinforced bipolar transistor of insulated gate

ActiveCN104332496AIncrease the carrier concentrationReduce conduction voltage dropSemiconductor devicesPower semiconductor deviceVoltage drop

Owner:中国东方电气集团有限公司

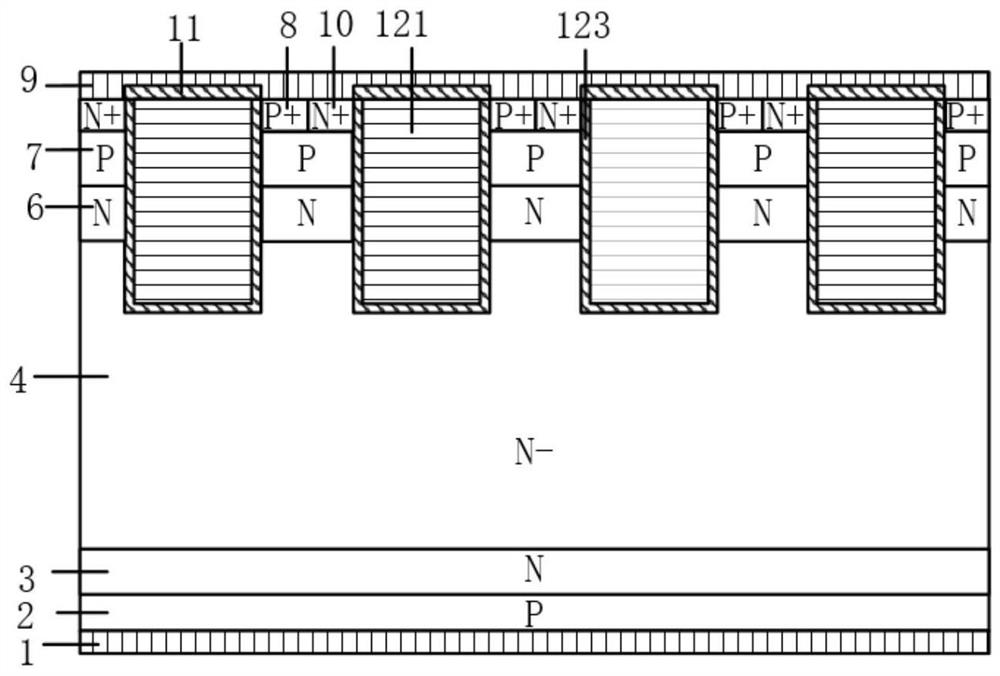

High-performance super-junction structure IGBT structure and method thereof

ActiveCN111627982AIncrease the doping concentrationEnhanced conductance modulation effectSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingVoltage drop

The invention provides a high-performance super-junction structure IGBT structure and a method thereof. The structure comprises a collector; a p-type buffer region arranged over the collector; an n-type buffer region arranged over the p-type buffer region; an n + type drift region arranged over the n type buffer region; a p-type block arranged in the n +-type drift region; a first etching groove formed in the top of the n + type drift region; a second etching groove formed in the bottom of the first etching groove; a p-type drain grid block arranged in the second etching groove; a p-type region arranged in the first etching groove; and a third etching groove formed in the top of the p-type region. The p-type block and the p-type drain grid block are arranged in a drift region, so that thedrift region is divided into three parts, the p-type block and the p-type drain grid block both play a role in blocking holes, the conductivity modulation effect is enhanced, the device has small conduction voltage drop under heavy current, the doping concentration of the drift region can be improved while the same withstand voltage is ensured, the conduction resistance and the forward voltage drop are reduced, and the power consumption is reduced.

Owner:苏州创芯致尚微电子有限公司

MOS (Metal Oxide Semiconductor) gated thyristor integrating Schottky diode and preparation method thereof

ActiveCN108899364AReduce the minimum currentShorten the timeThyristorSemiconductor/solid-state device manufacturingPeak currentPeak value

The invention belongs to the technical field of power semiconductor devices and relates to an MOS (Metal Oxide Semiconductor) gated thyristor integrating a Schottky diode. According to the MOS gated thyristor provided by the invention, a device cathode is designed to be in contact with Schottky, so that one Schottky diode is formed between a P trap region and the cathode, wherein the pumping of acharge carrier in a switching-off process can be accelerated by a P+ region, but the pulse performance of the device is not influenced; in a manufacturing process, whether the P+ region is remained ornot can be selected according to requirements. By adopting two structures, the current distribution is more uniform when the device works and the minimum current needed by a latch of the device is reduced; pulse peak value current is further improved under small current and the increasing rate of the current (di / dt) is improved; the time of the device which works under an IGBT (Insulated Gate Bipolar Transistor) mode is shortened; the crystal lattice temperature of the device which works under the IGBT mode at an pulse discharging initial stage of the device is effectively reduced, and furthermore, pulse properties of the device are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA