Patents

Literature

43results about How to "Reduce saturation pressure drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

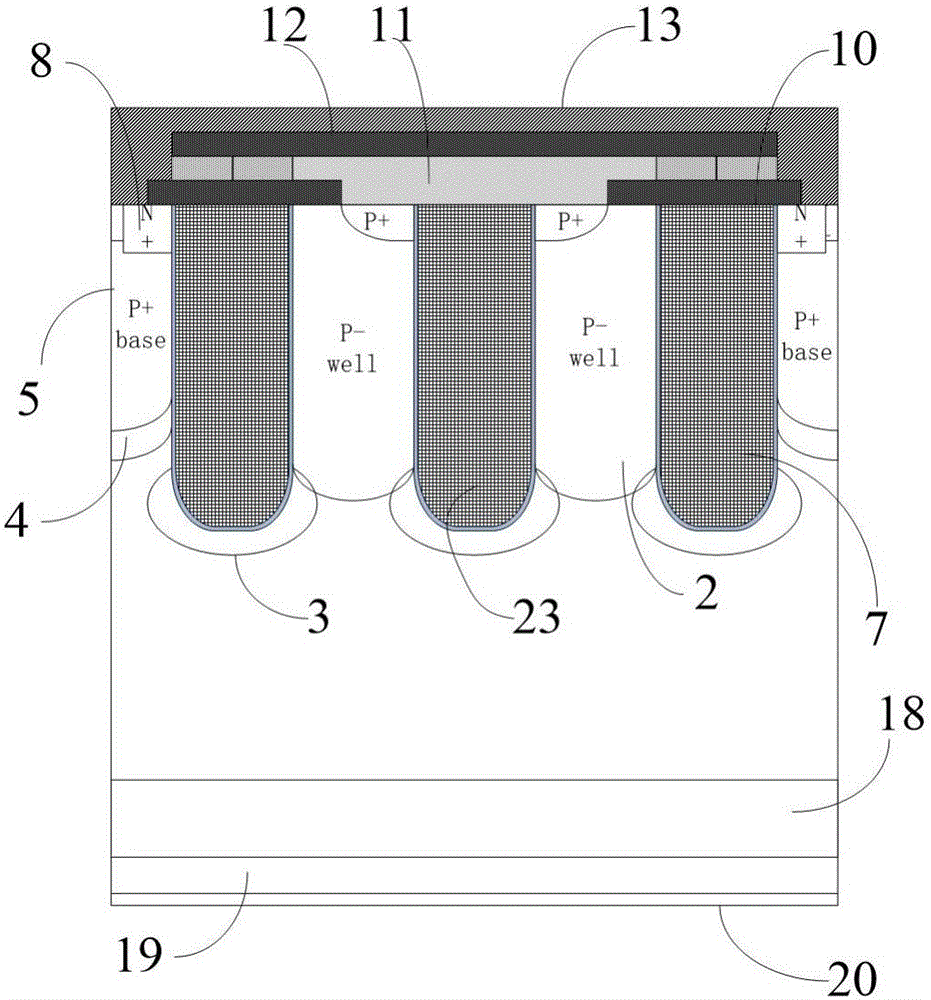

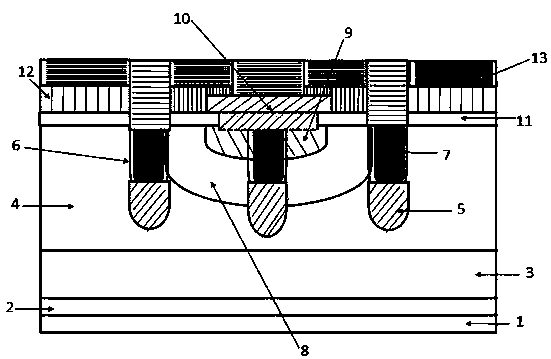

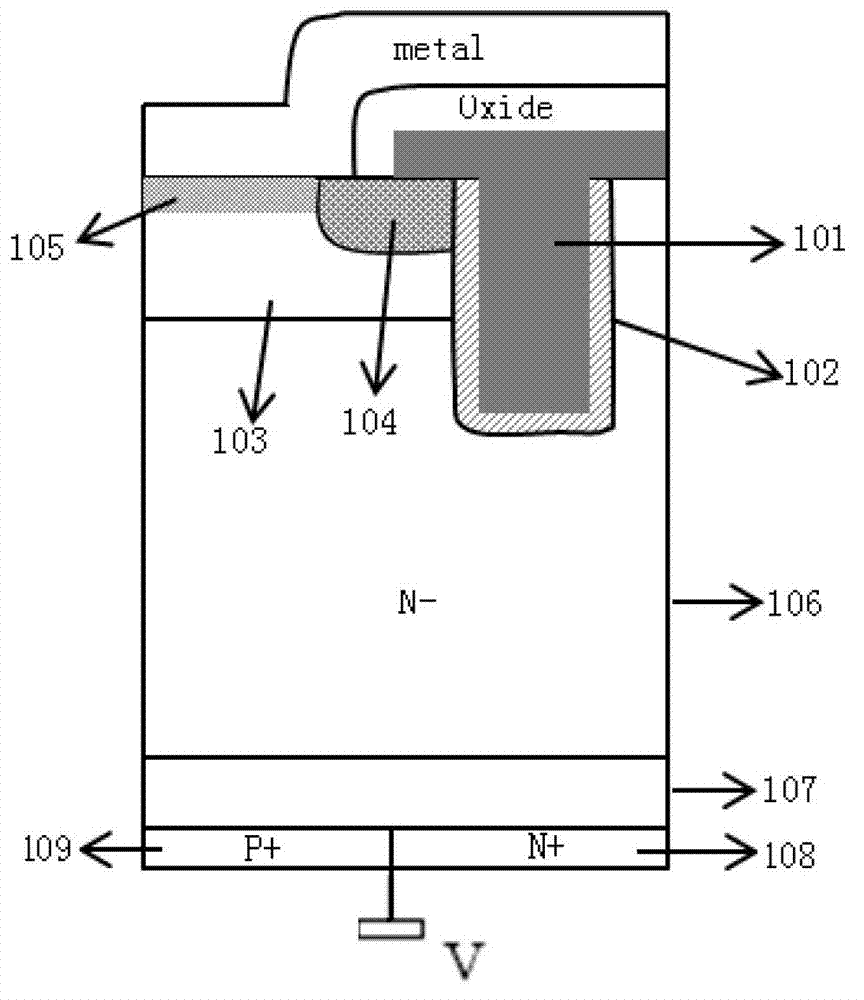

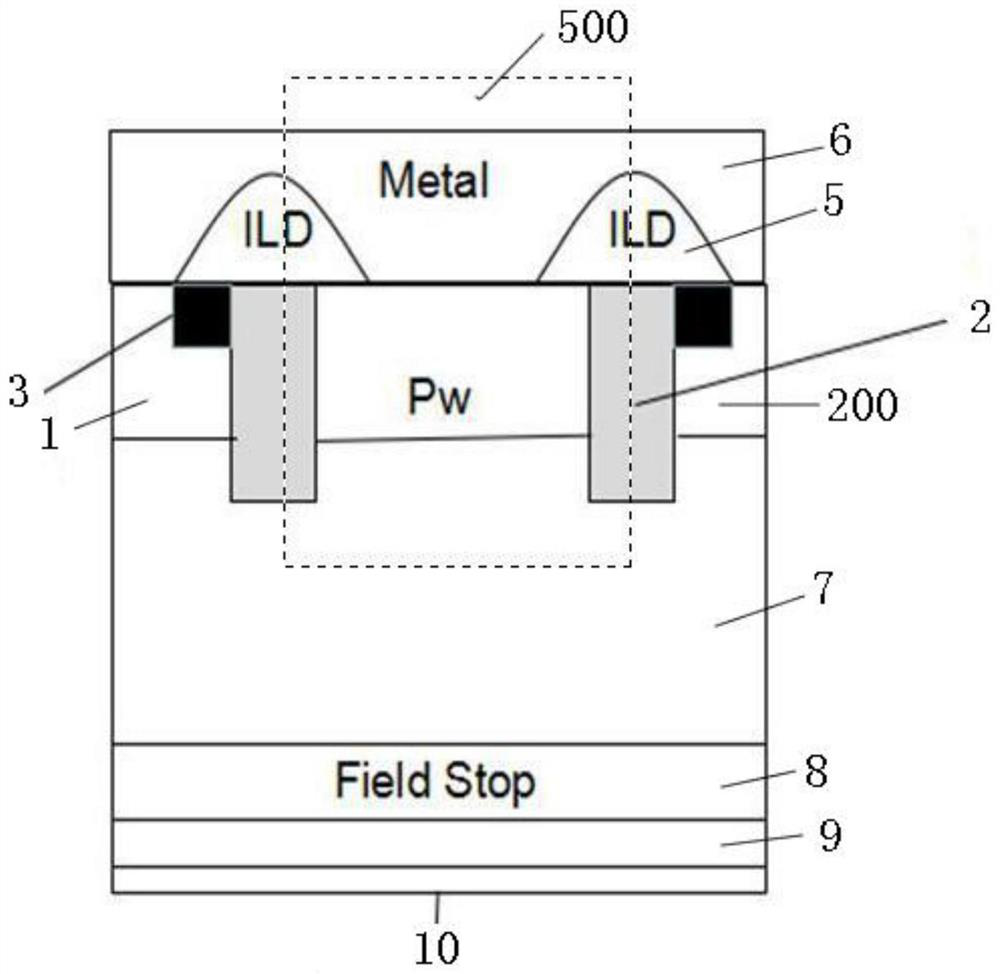

Insulated gate bipolar transistor device with low conduction voltage drop, and manufacturing method for insulated gate bipolar transistor device

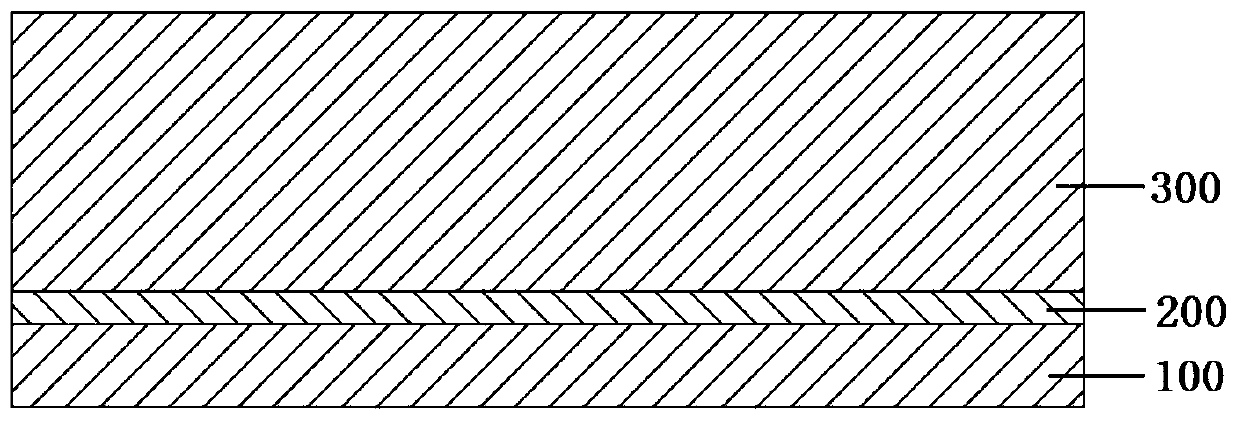

PendingCN106653836AEnhanced conductance modulation effectReduce saturation pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesInsulated-gate bipolar transistorPower flow

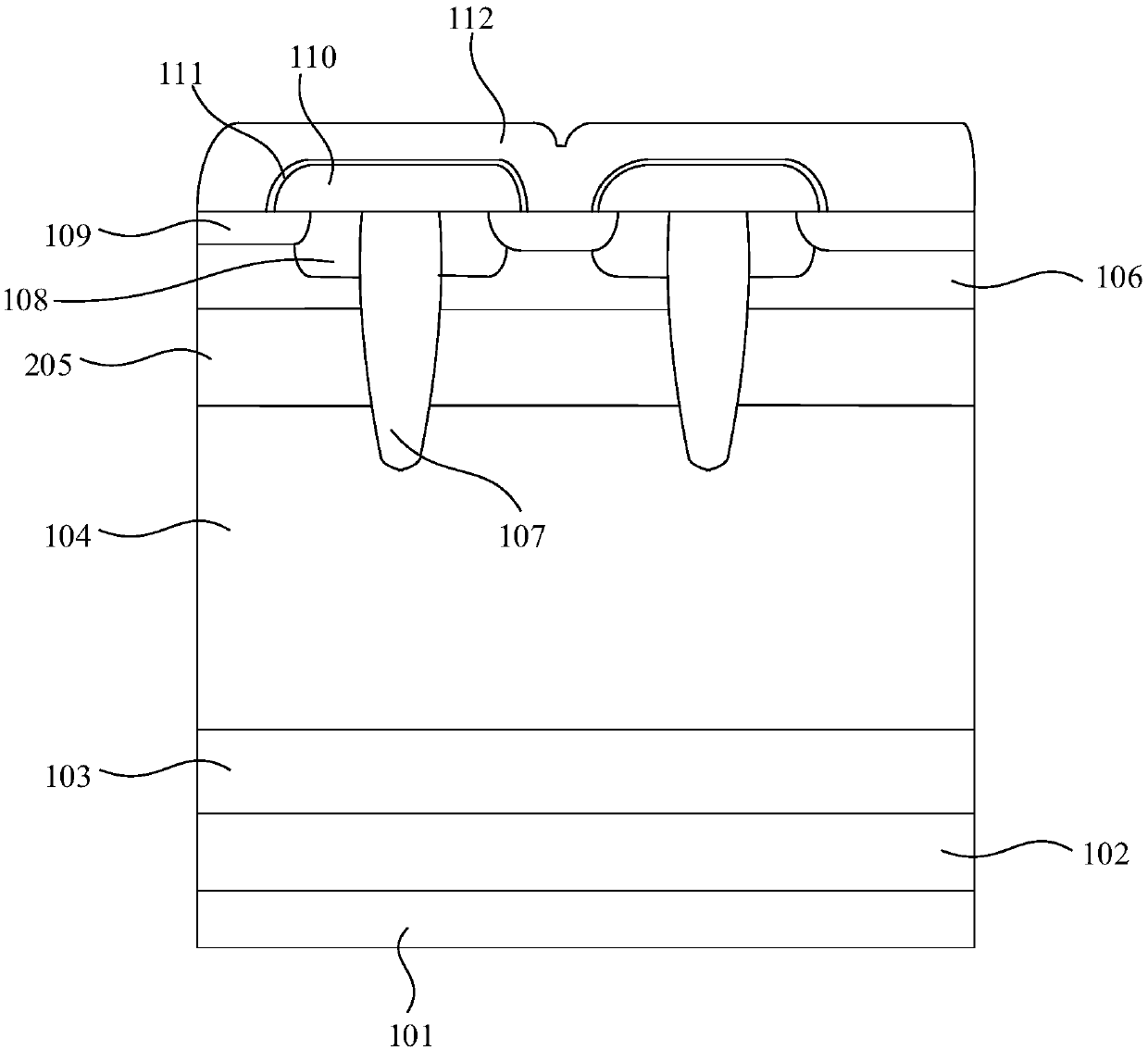

The invention relates to an insulated gate bipolar transistor device with low conduction voltage drop, and a manufacturing method for the insulated gate bipolar transistor device. The device comprises an active region located on a semiconductor substrate, and a terminal protection region. Active cells of the active region on the section of the device employ a trench structure, and comprise active cells and non-active cells. The bottom of an active cell trench and the bottom of a non-active cell trench are respectively provided with a floating region of a second conductive type, wherein the floating region of the second conductive type below the active cell trench wraps the bottom of the active cell trench, and the floating region of the second conductive type below the non-active cell trench wraps the bottom of the non-active cell trench. The device has extremely low conduction voltage drop and extremely quick cut-off speed under the condition that the withstand voltage is guaranteed, is lower in current and voltage oscillation, and greatly improves the work reliability.

Owner:WUXI NCE POWER

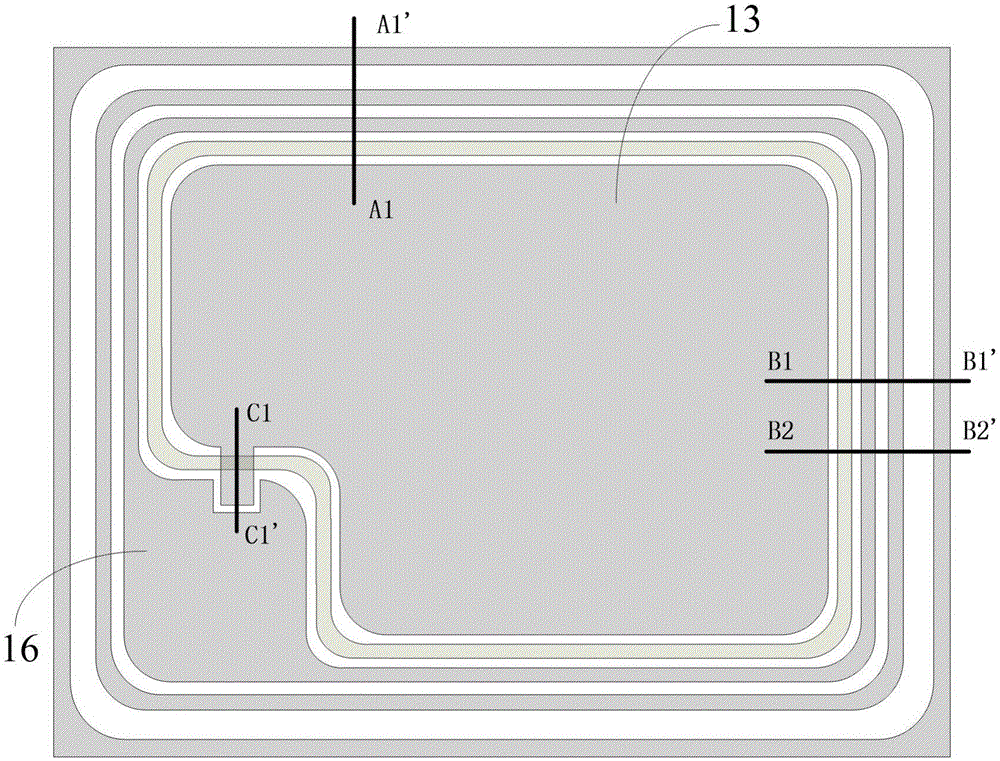

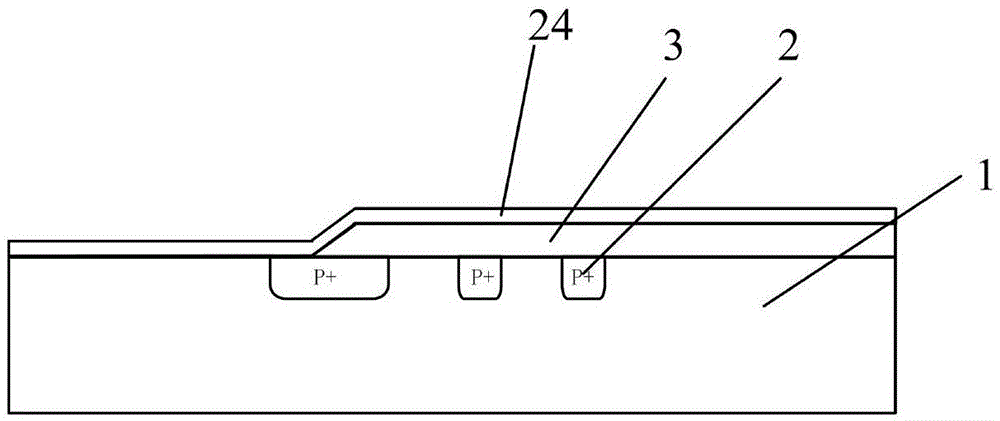

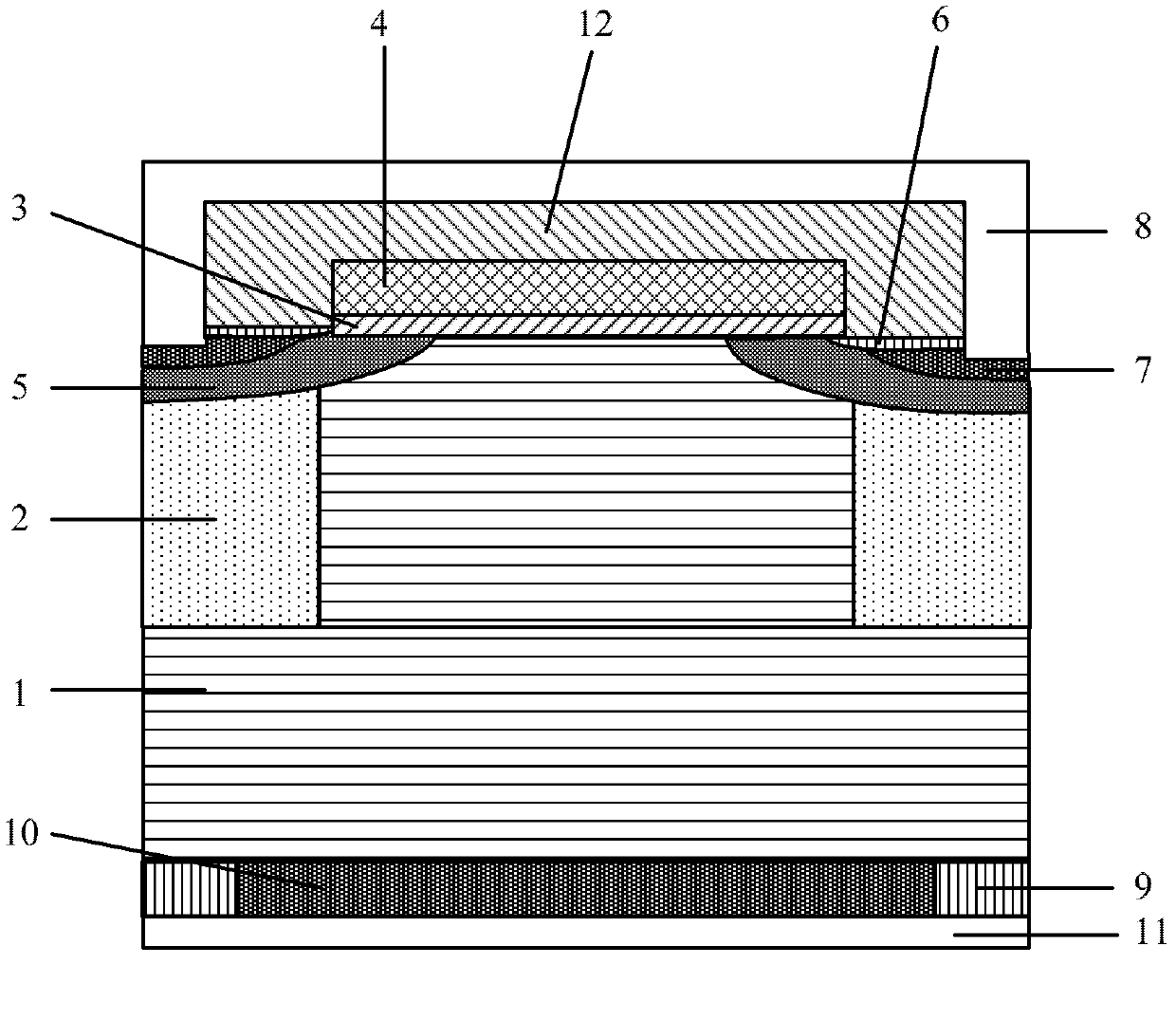

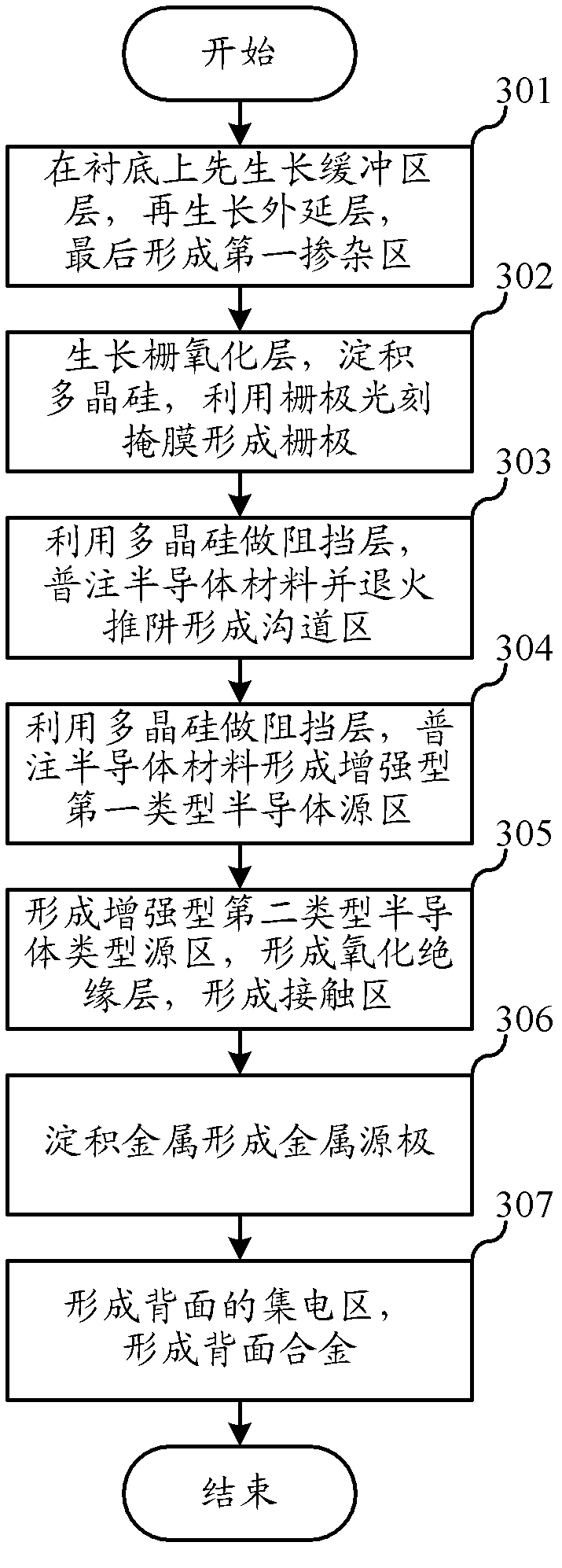

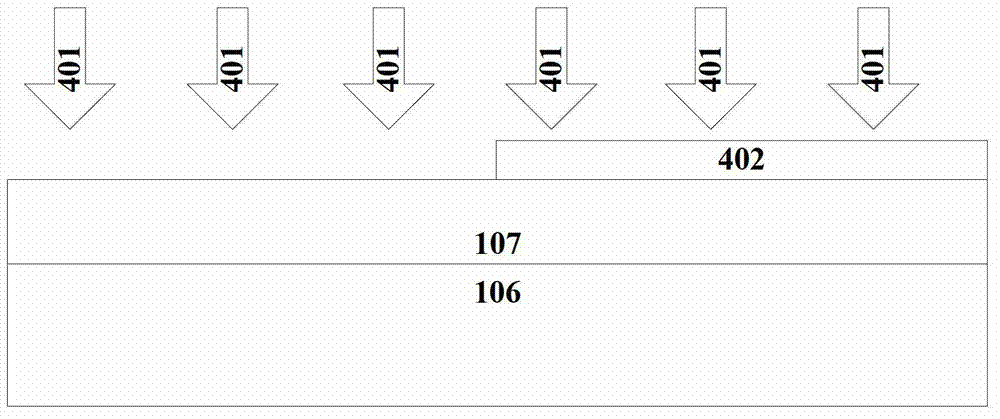

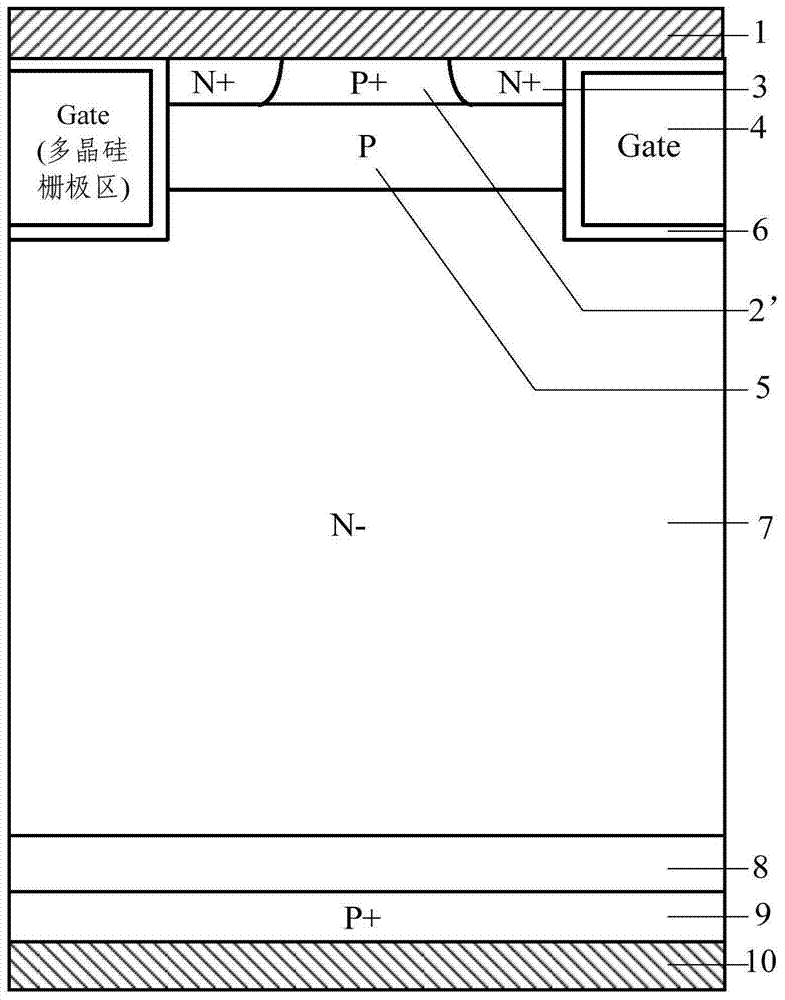

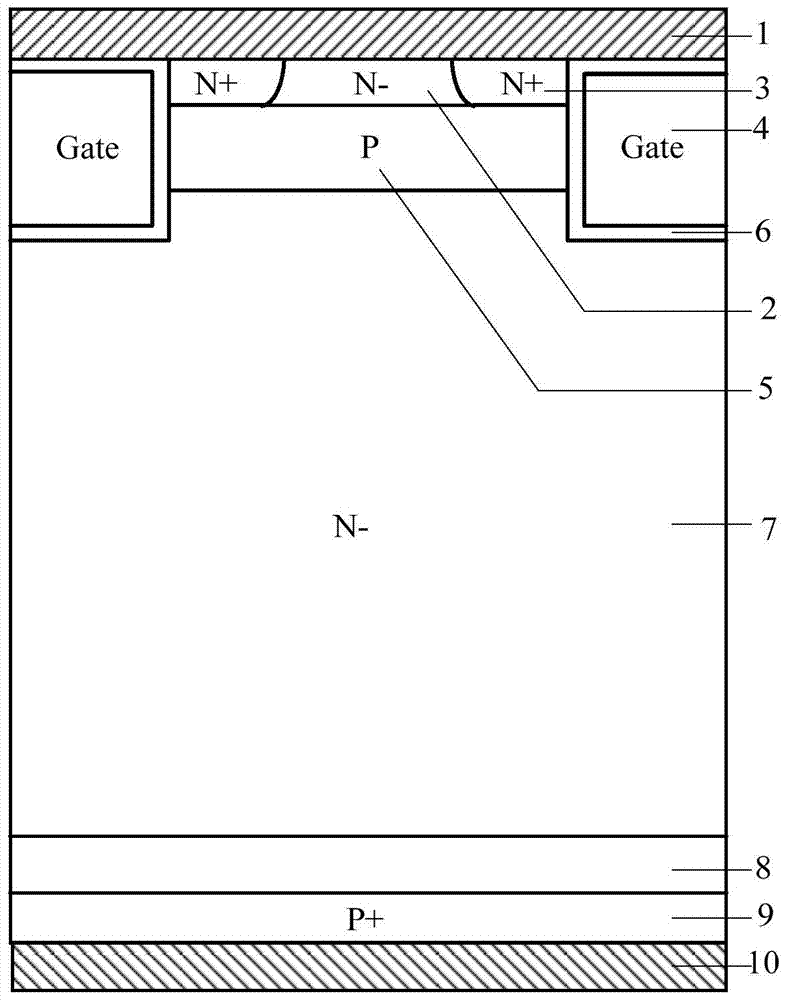

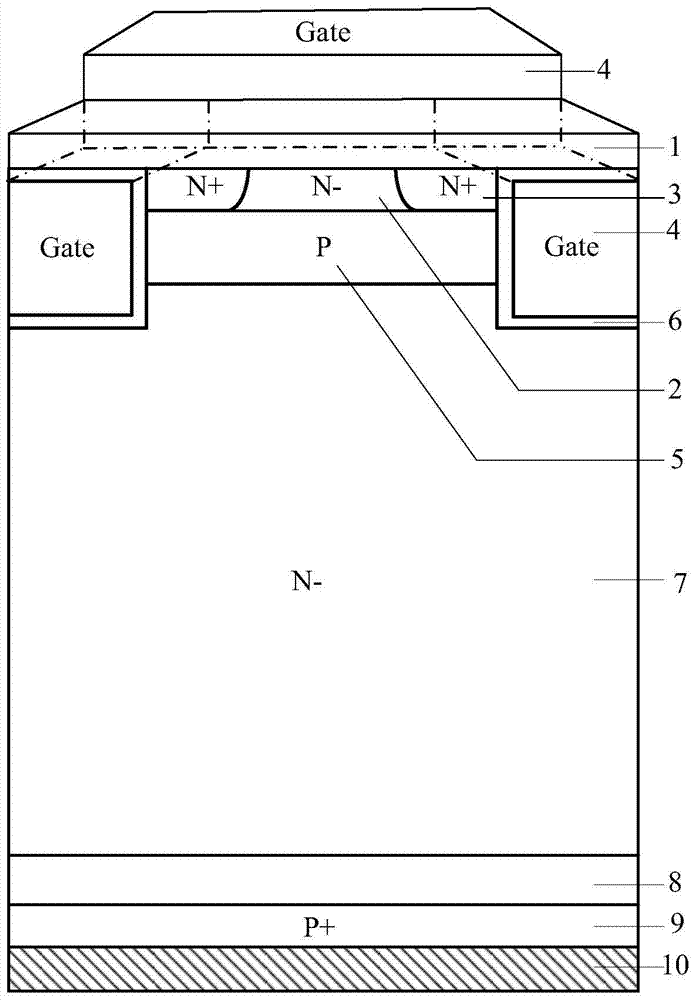

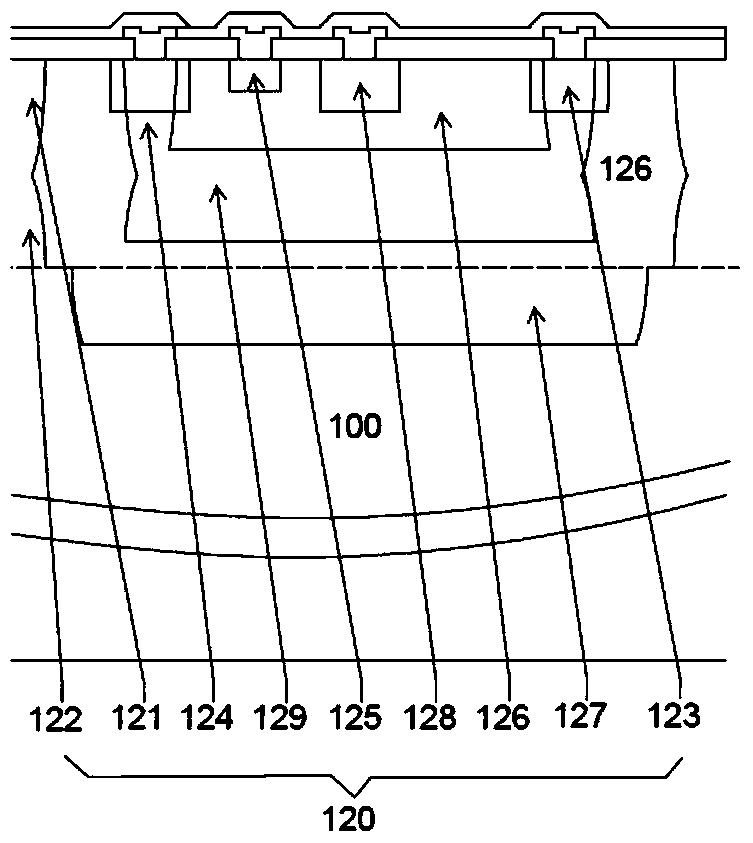

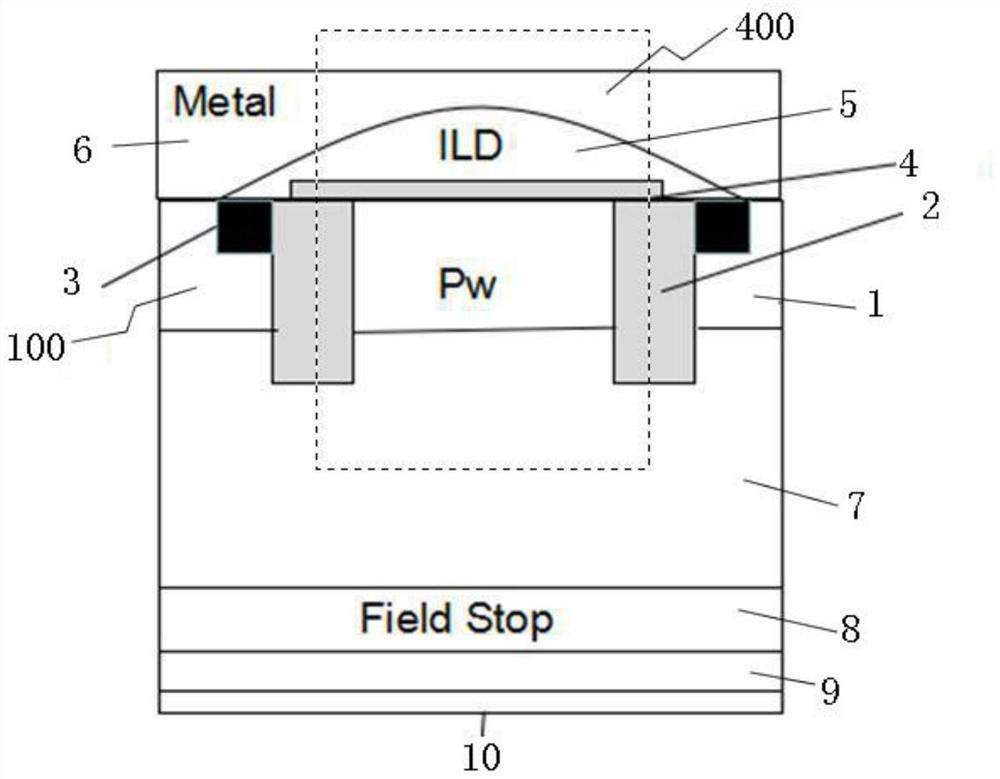

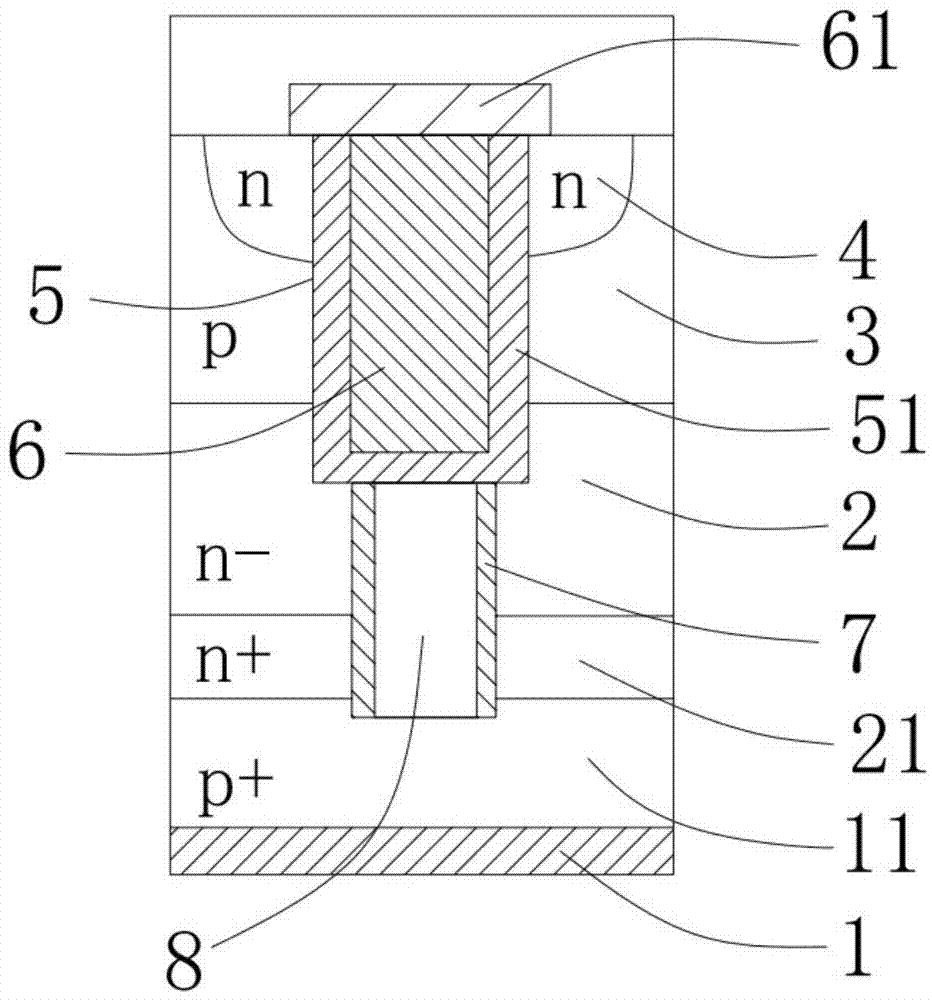

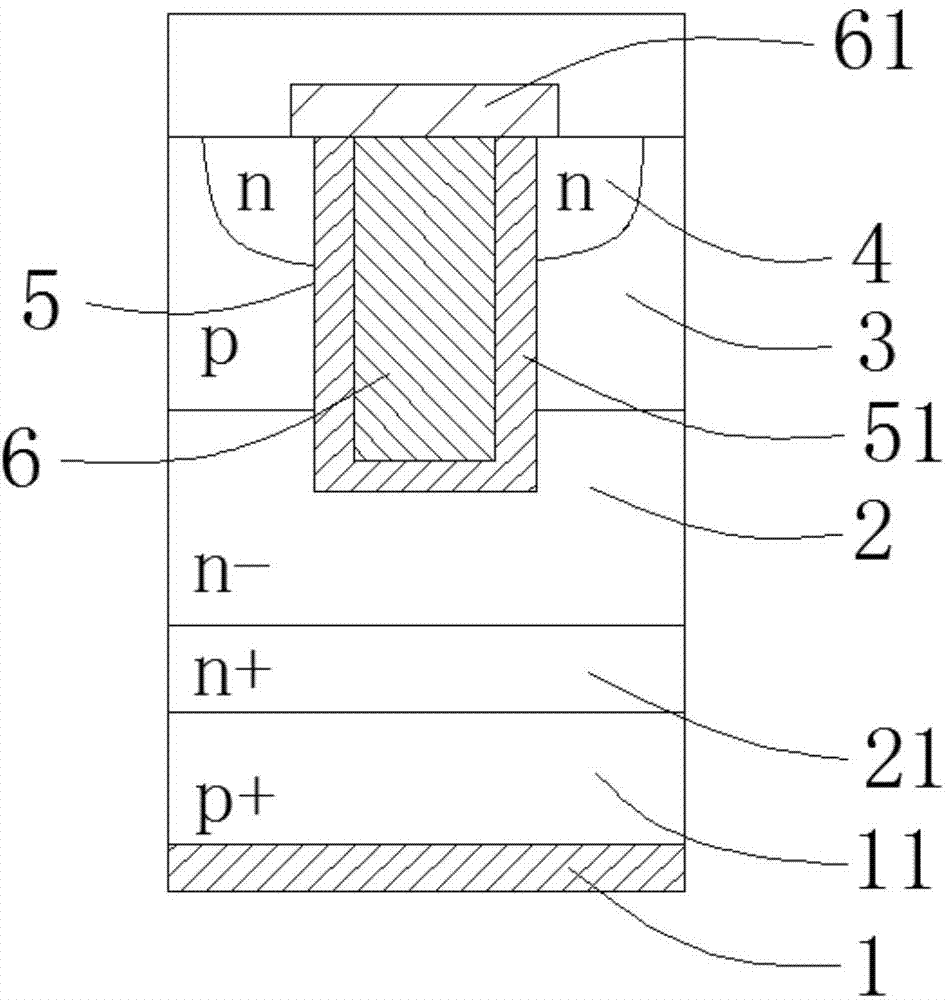

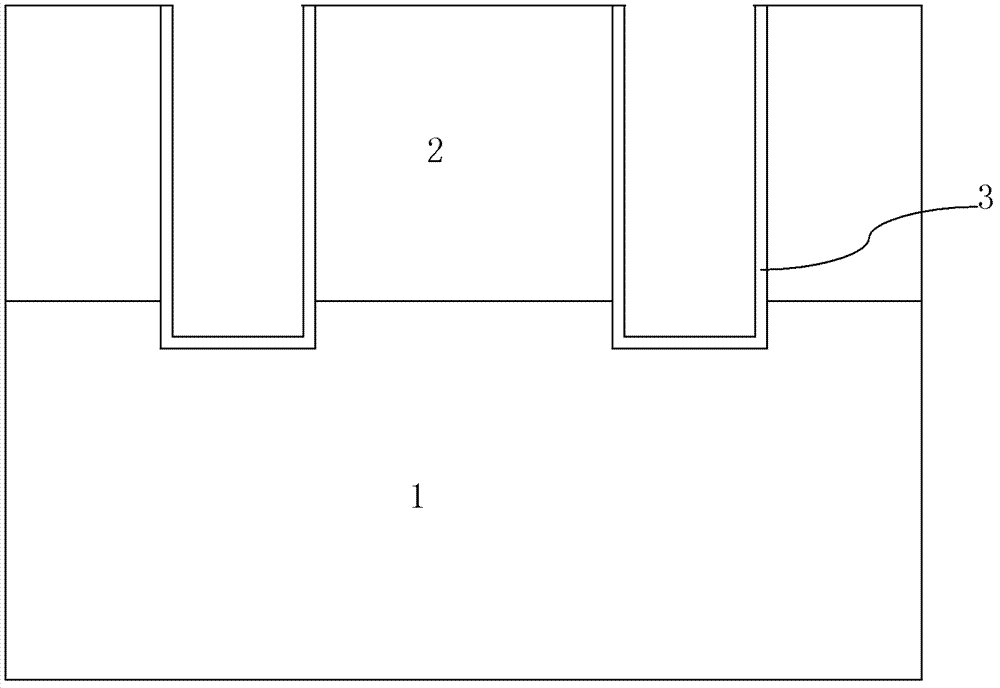

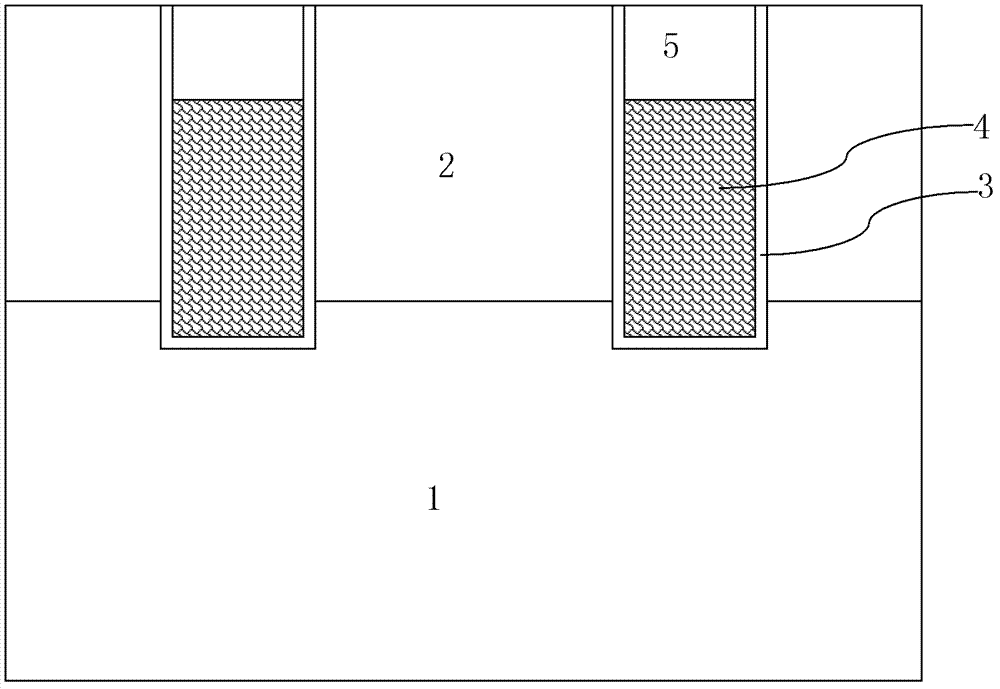

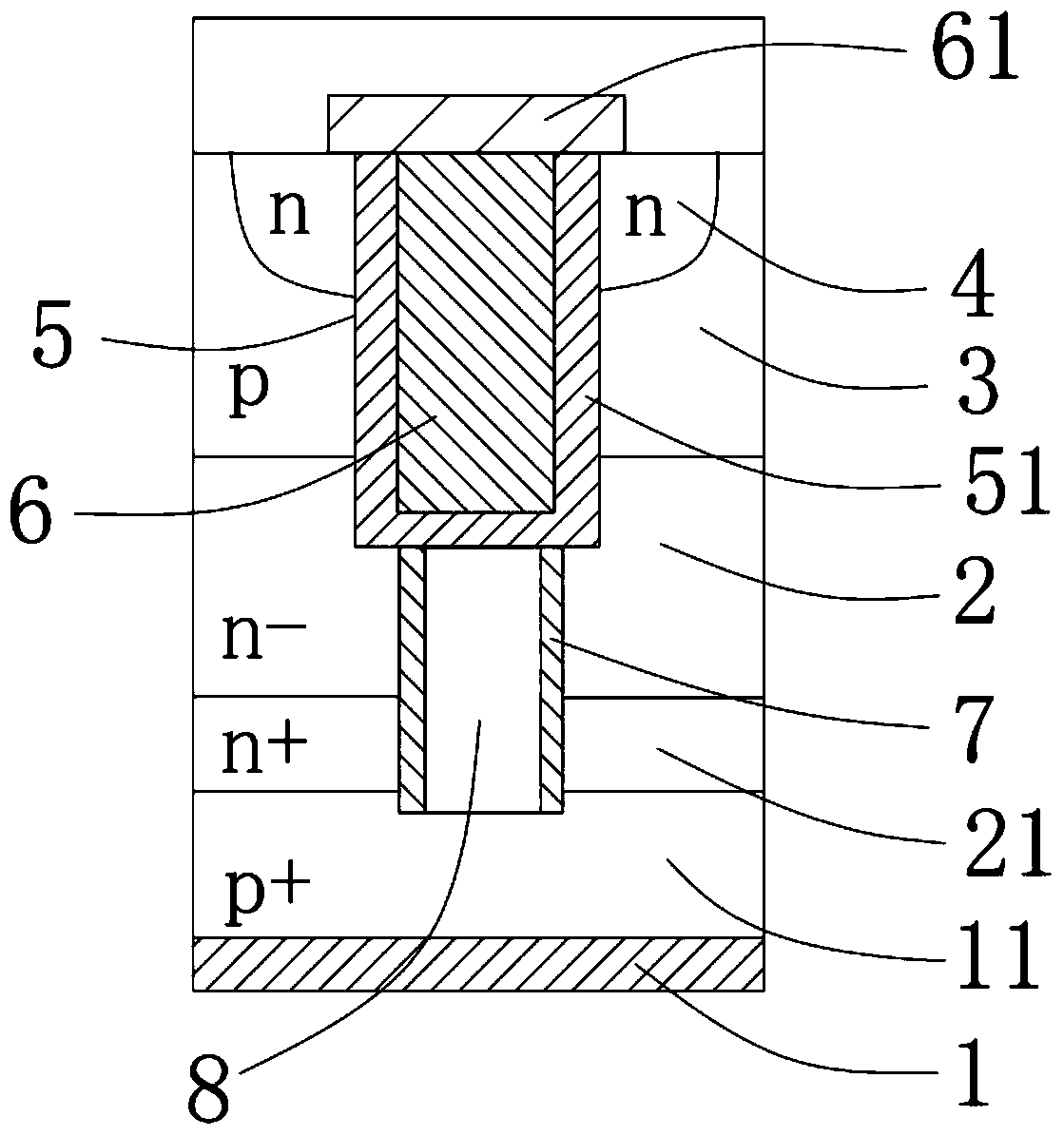

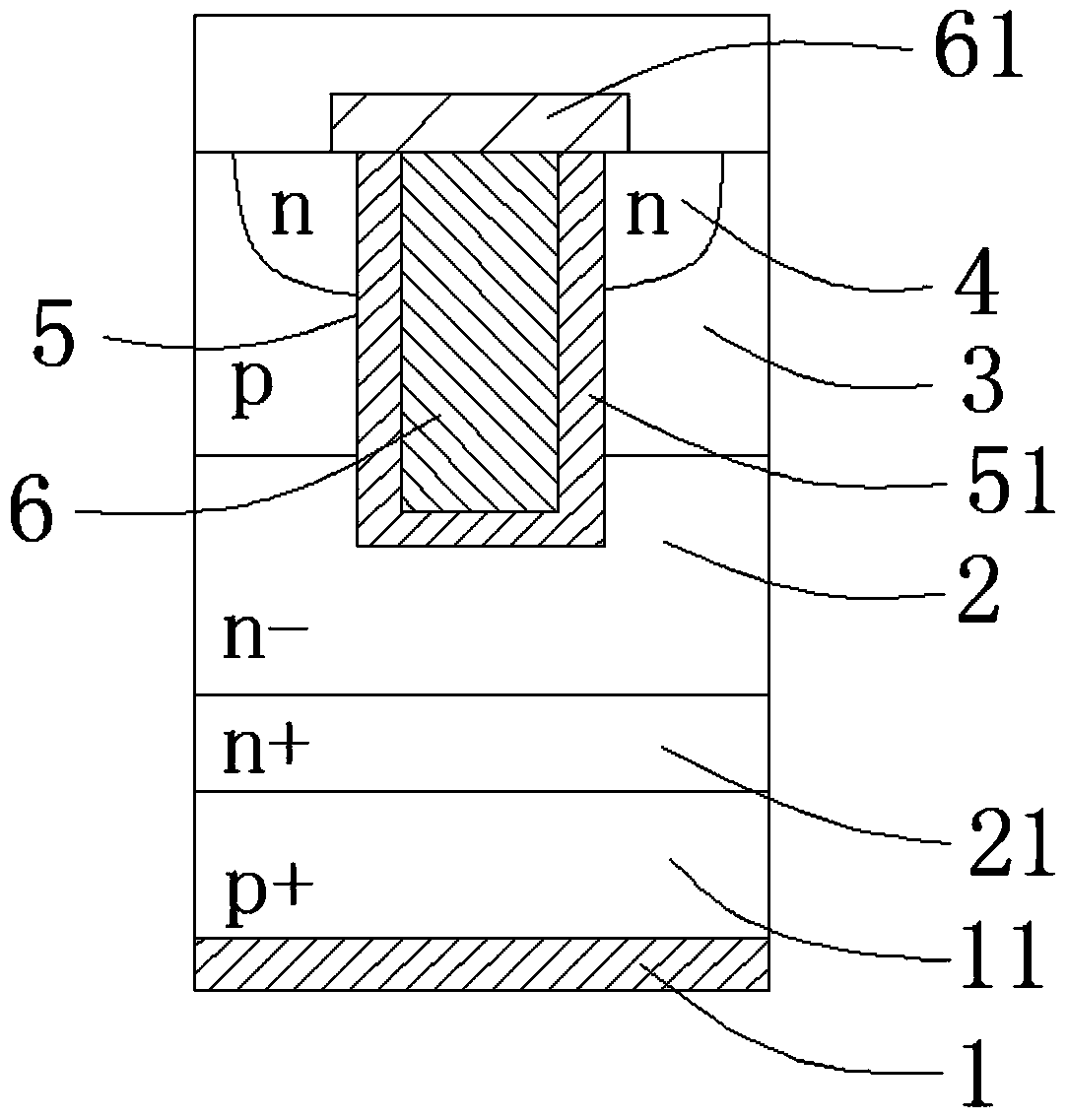

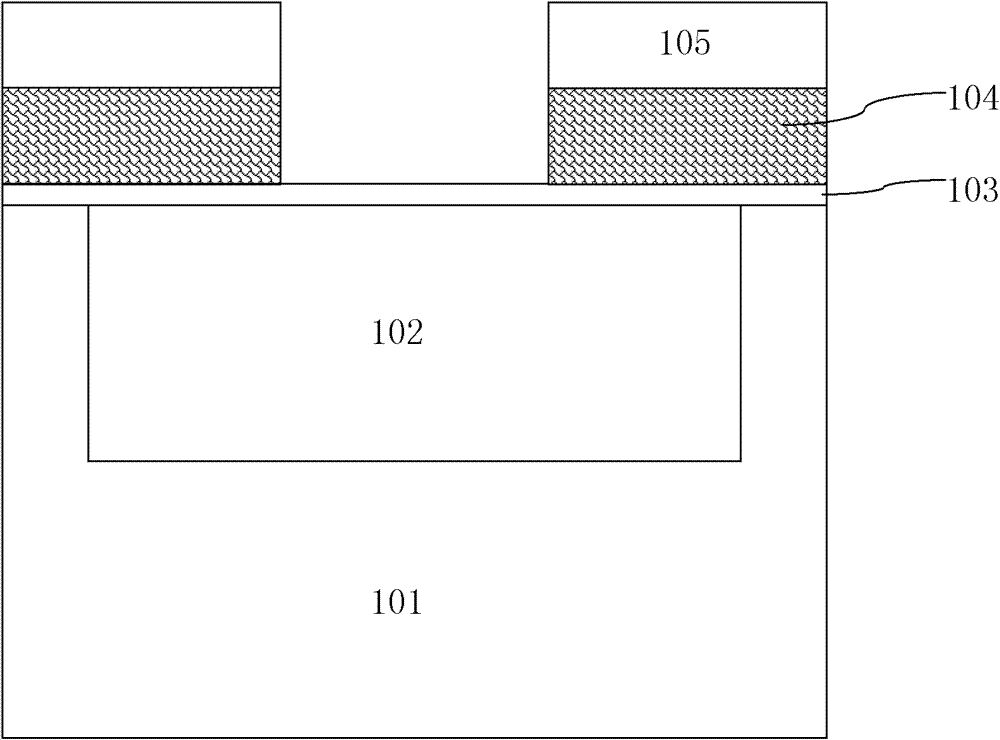

IGBT device with carrier storage structure and manufacturing method of IGBT device

ActiveCN105633139AReduce saturation pressure dropEnhanced conductance modulation effectSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropHigh voltage

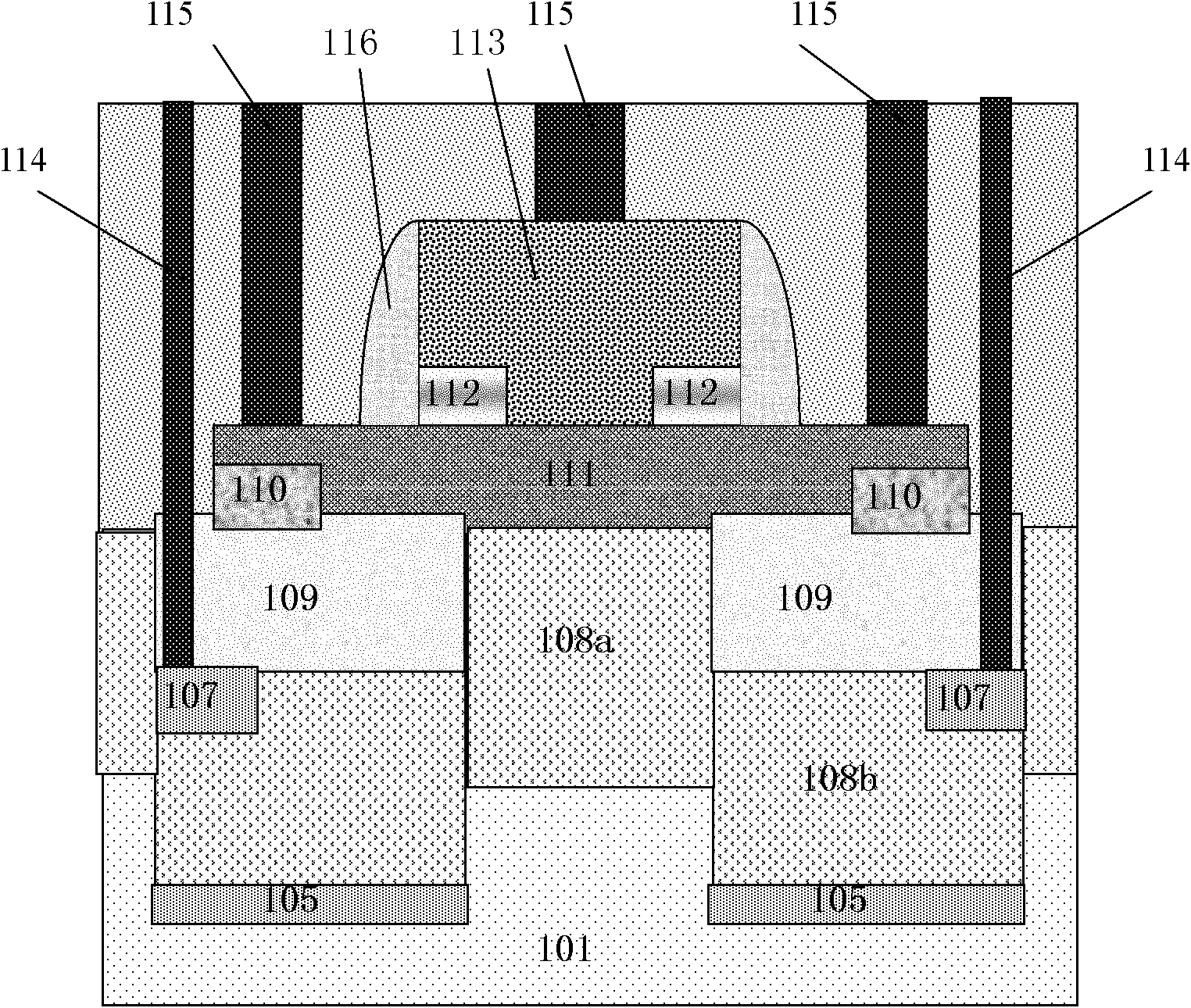

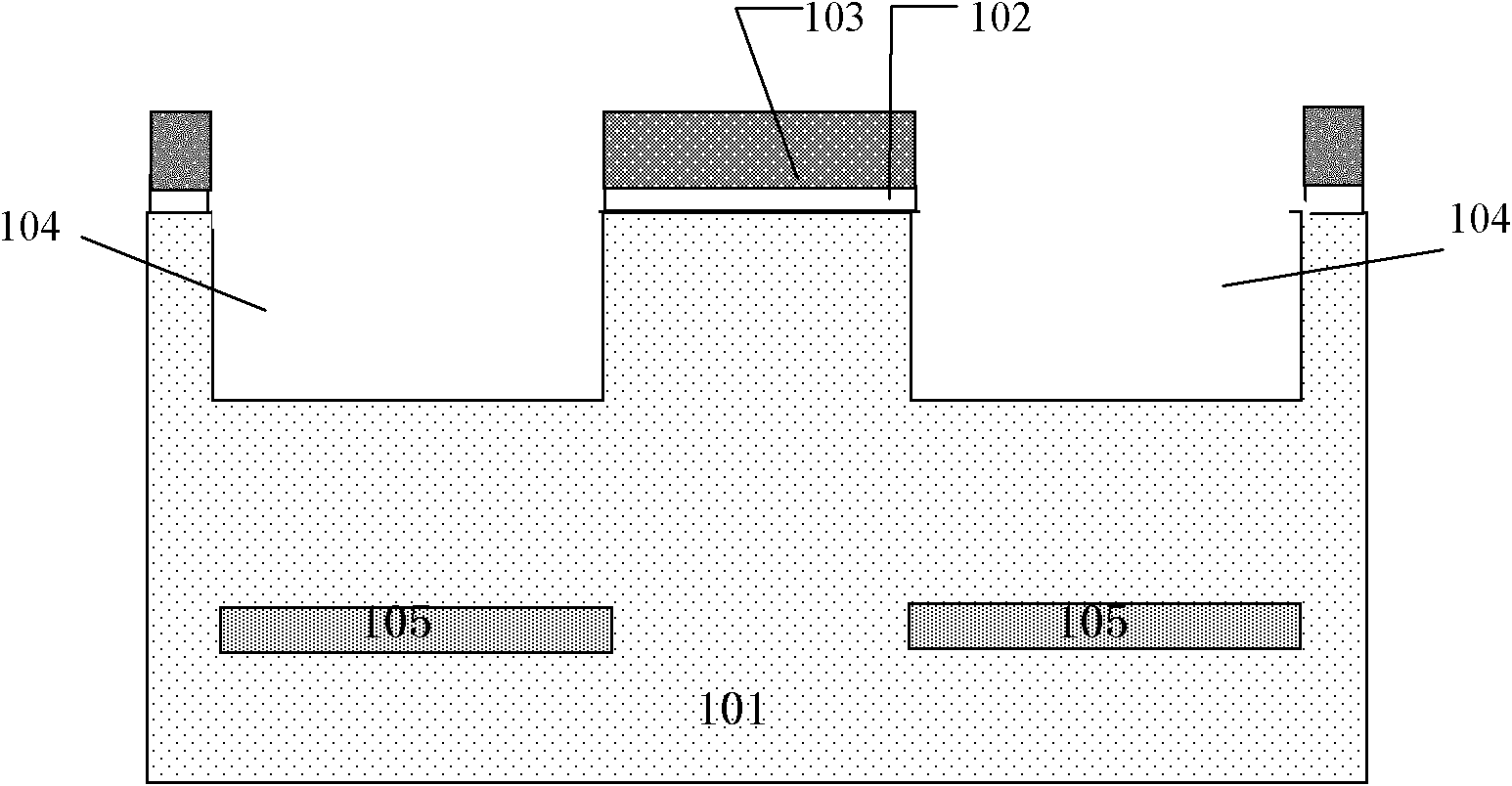

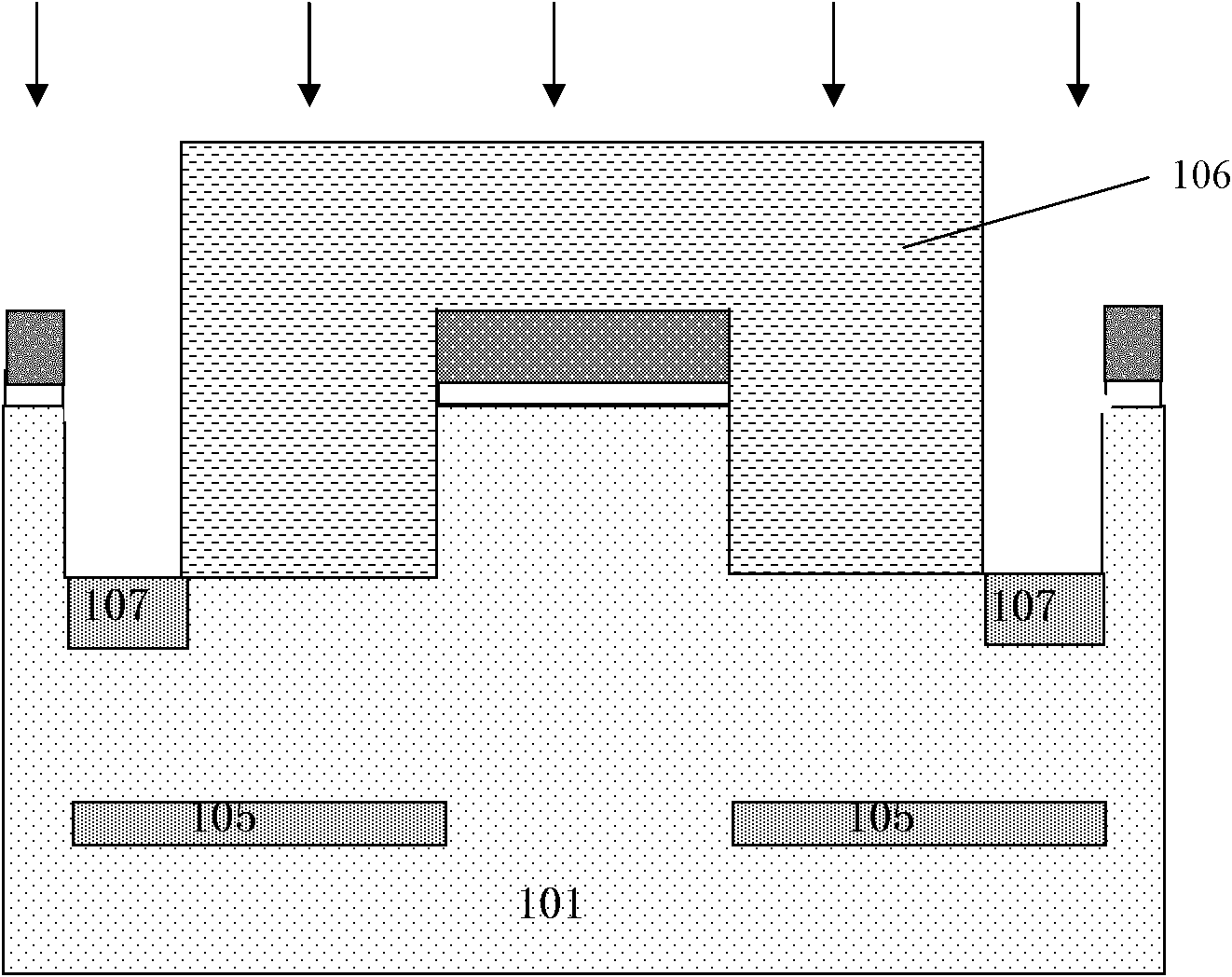

The invention relates to an IGBT device with a carrier storage structure and a manufacturing method thereof. An active area of the IGBT device adopts a groove structure; a second conduction type body area is arranged in a first conduction type drifting area of the active area; a cellular groove is located in the second conduction type body area and deeply extends into the first conduction type drifting area below the second conduction type body area; the carrier storage structure is arranged in the first conduction type drifting area of the active area; the carrier storage structure comprises a first conduction type carrier storage area which is used for completely surrounding the inner and outer walls, extending in the first conduction type drifting area, of the cellular groove; and the doping concentration of the first conduction type carrier storage area is greater than the doping concentration of the first conduction type drifting area. According to the IGBT device with the carrier storage structure and the manufacturing method thereof, the relatively low breakover voltage drop and extremely rapid turnoff characteristic can be satisfied at the same time, the pressurization breakdown position can be adjusted to a cellular area to ensure relatively high voltage surge resistance, the chip manufacturing cost is not increased, and the chip area is reduced.

Owner:WUXI NCE POWER

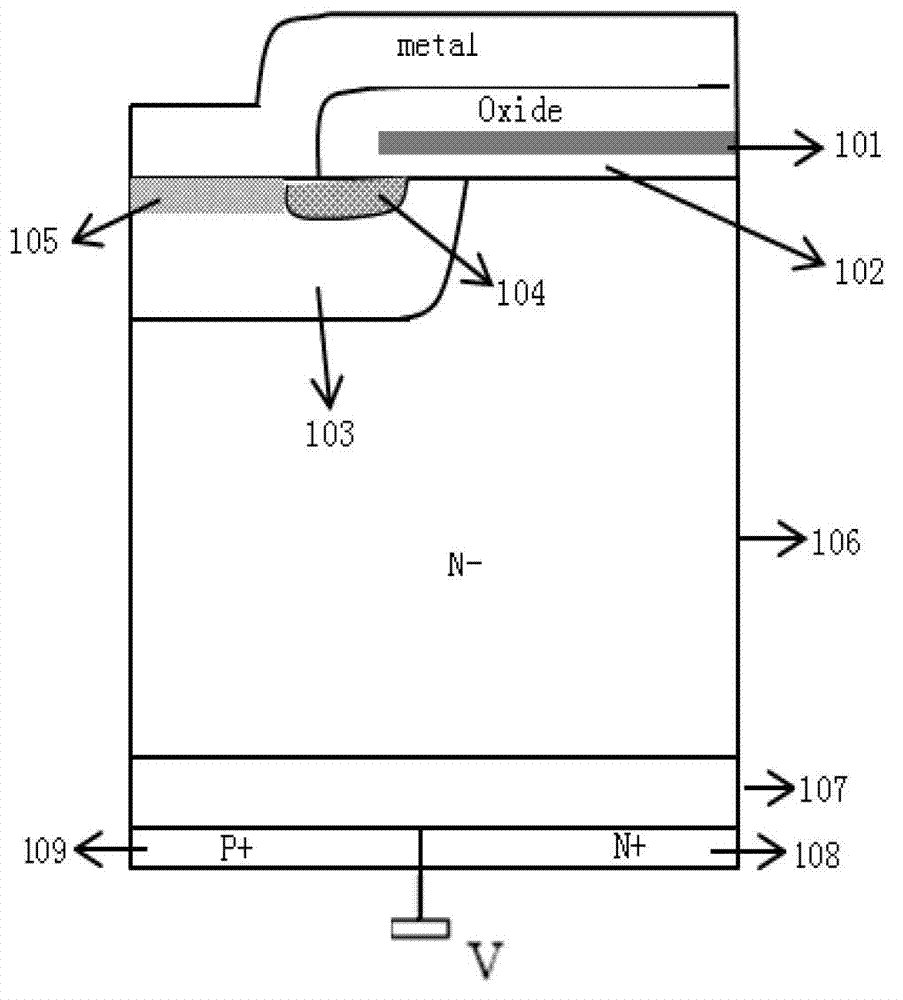

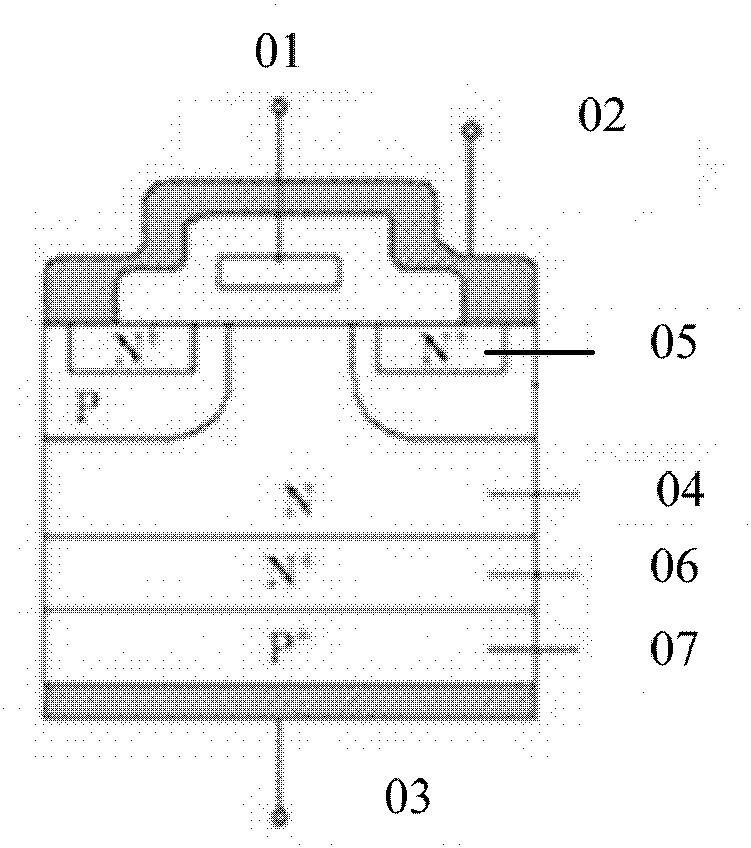

Electrostatic shielding effect transistor and design method thereof

ActiveCN104009087AImprove high frequency characteristicsReduce dynamic lossSemiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

The invention discloses an electrostatic shielding effect transistor. The electrostatic shielding effect transistor comprise a collector, groove-type grids, a base region, an oxidization layer, a polycrystalline silicon layer and emitters. The collector comprises a leading-out end, an N+ substrate, an N+ conductive material layer and an N- conductive material layer. The groove-type grids are arranged on the N- conductive material layer, B ions of certain concentration are injected into the bottom of a groove to serve as P+ regions, and the base region injected with the B ions is arranged between the grids. The oxidization layer is arranged on the grids and the base region, the emitters are formed on the base region and the oxidization layer, the polycrystalline silicon layer is deposited on the oxidization layer and the polycrystalline silicon layer forms an emitting region below the emitters after high-temperature diffusion. The electrostatic shielding effect transistor is provided with the emitters and the base region which are super shallow in junction and small in size, and therefore, the emitter current crowding effect and the base region flow extruding effect of the device can be greatly improved. Due to the super small junction depth of the structure and the base region of the device, the hole extraction speed is increased and the high frequency property of the device is improved.

Owner:SHENZHEN SHENGYUAN SEMICON

Insulated gate bipolar transistor and manufacturing method thereof

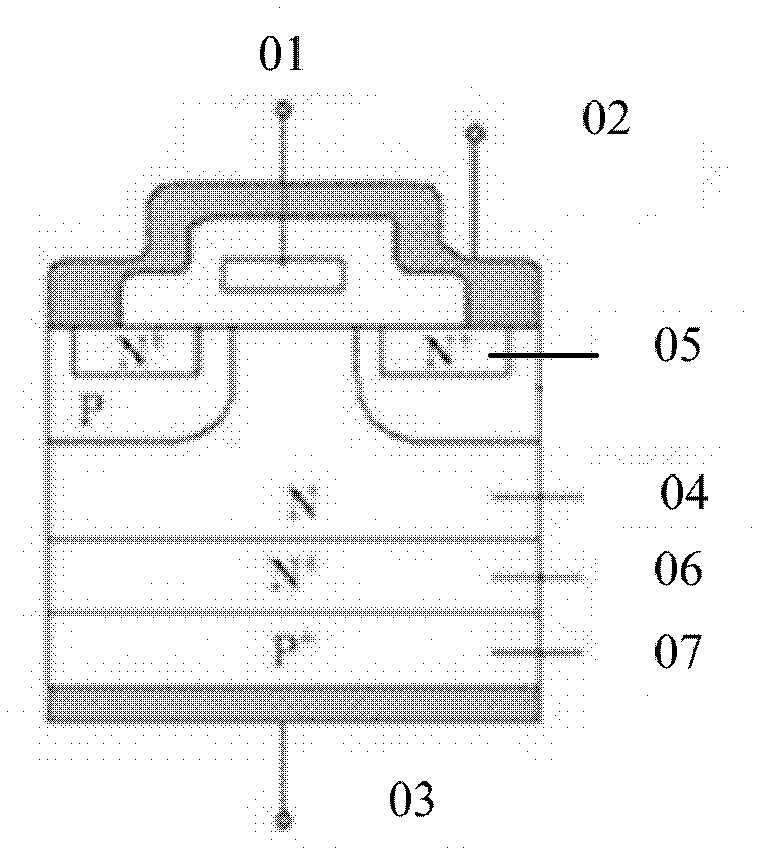

InactiveCN103378141AReduce thickness requirementsReduce smearing timeSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierParasitic bipolar transistor

The invention relates to the field of electronic devices, and discloses an insulated gate bipolar transistor and a manufacturing method thereof. According to the insulated gate bipolar transistor and the manufacturing method thereof, a first doping region is used as a super junction in the insulated gate bipolar transistor, internal fast recovery diodes are formed in a channel region and a second doping region, the advantages of a super junction MOS and the advantages of a reverse conducting insulated gate bipolar transistor are combined, the saturation voltage drop of the insulated gate bipolar transistor can be effectively lowered, higher power density is achieved, and meanwhile due to the fact that the fast recovery diodes are removed in module packaging process, production cost can be effectively lowered. Due to a buffer region layer, the requirement for the thickness of a substrate is lowered, the buffer region layer is used for accelerating the composite process of charge carriers, the trailing time of insulated gate bipolar transistor products can be effectively shortened, the turn-off loss of the products is reduced, and the cut-off frequency of the products is increased.

Owner:上海永电电子科技有限公司

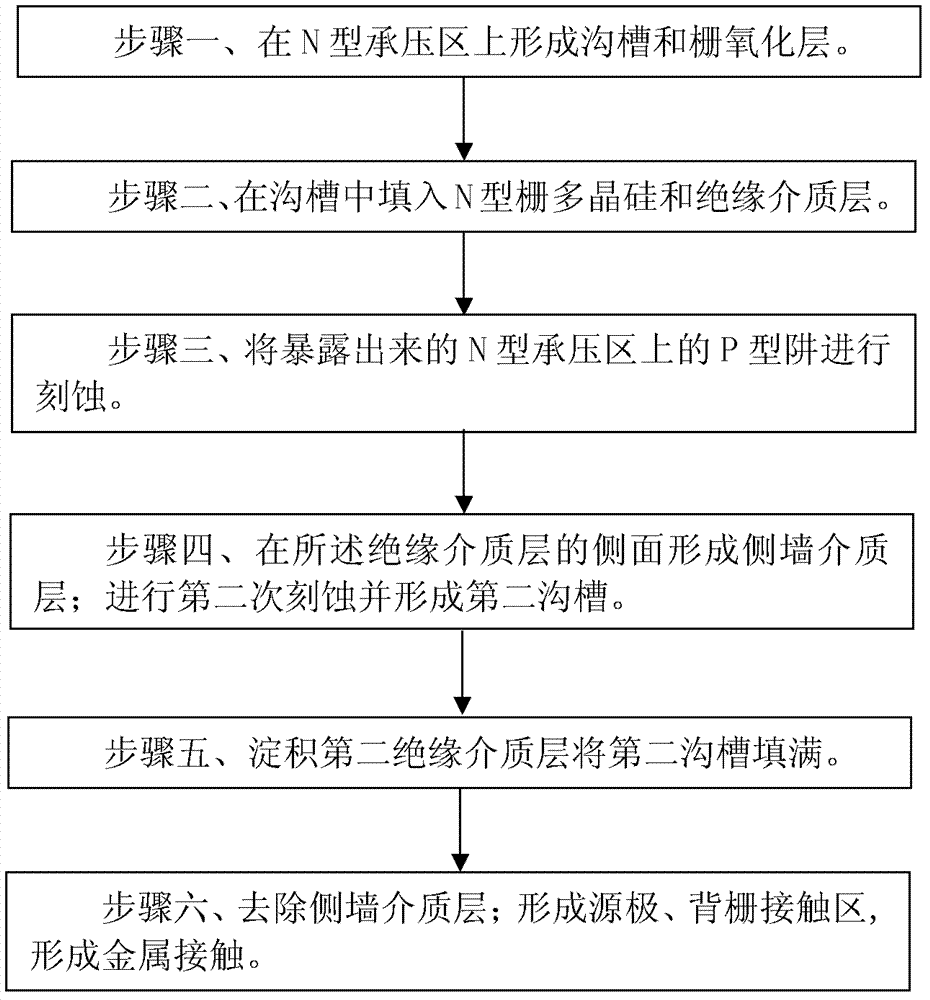

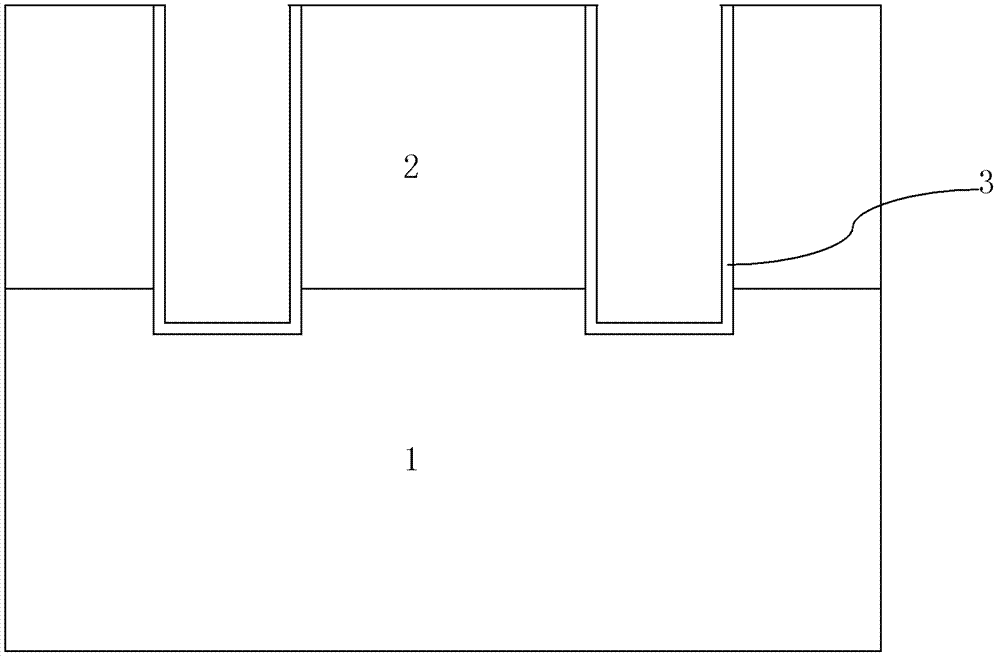

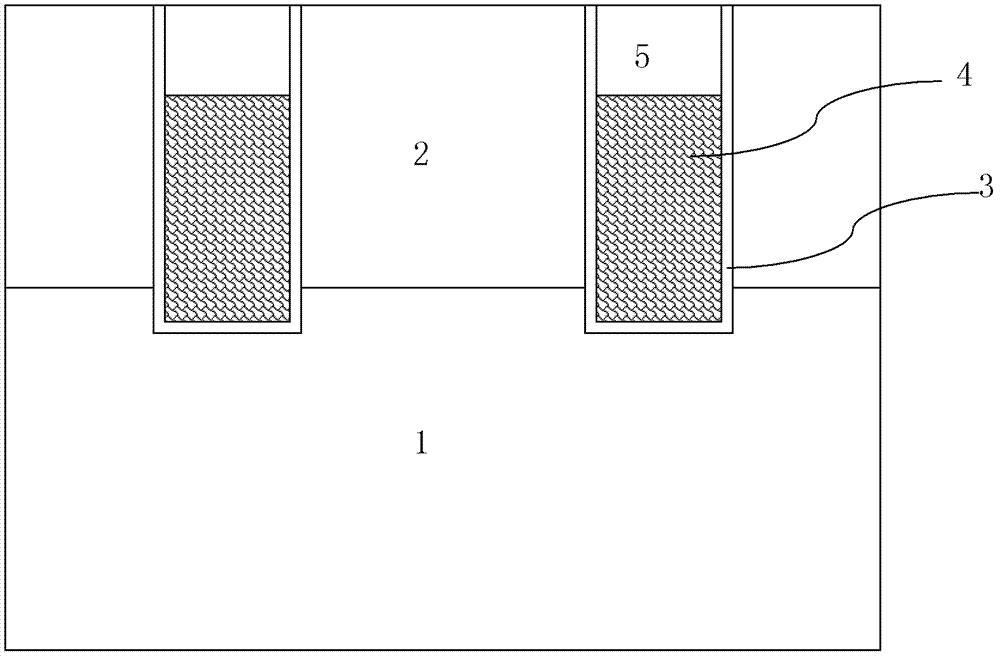

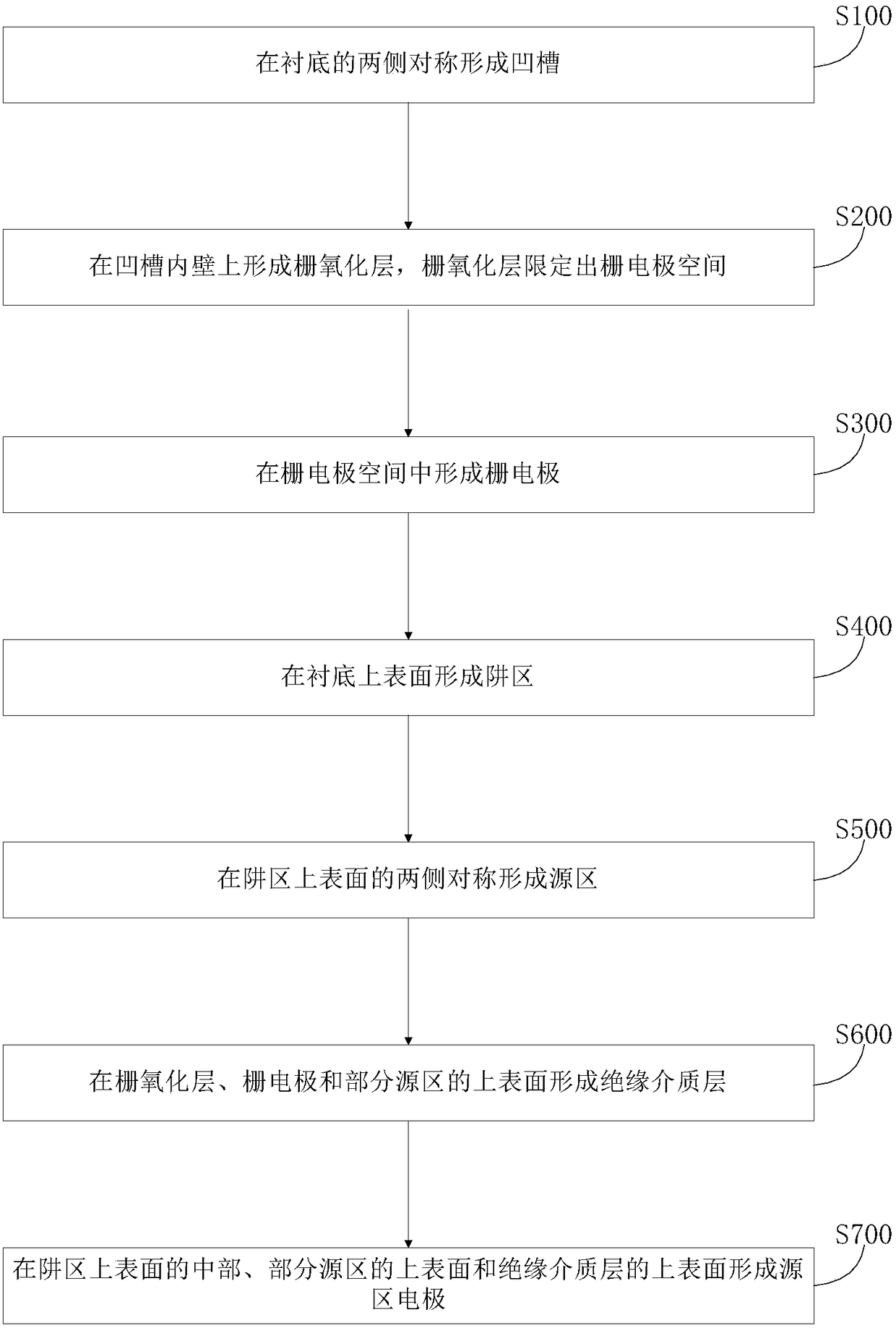

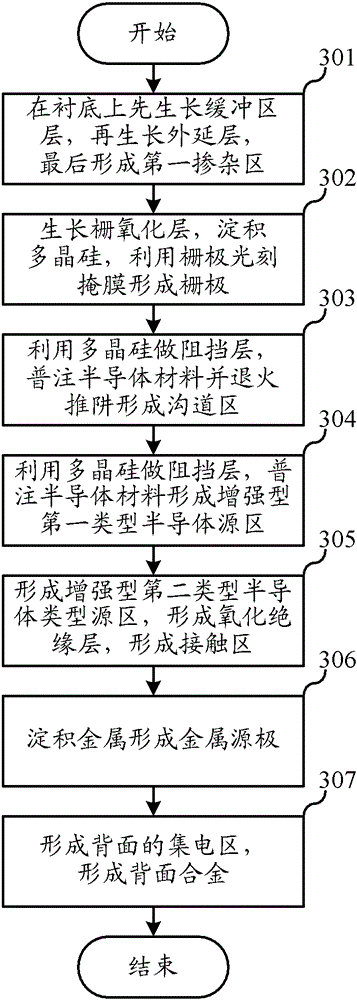

Manufacture method of isolation type power transistor

ActiveCN102956487AReduce crosstalk effectsLow densitySemiconductor/solid-state device manufacturingManufacturing cost reductionIsolation layer

The invention discloses a manufacture method of an isolation type power transistor. By the manufacture method, insulating medium layers formed on the top of gate polycrystalline silicon and spacer medium layers formed on the side faces of the insulating medium layers serve as hard masks for etching to form isolation layer trenches among devices, and an insulated isolation layer can be formed among transistors without adding extra masks, so that density of the transistors in a chip cannot be decreased, and mutual interference of the devices can be weakened. Increase of the size of the transistors and increase of density of transistors in the chip are benefited, and powder devices lower in breakover resistance and saturation voltage drop and higher in current driving capacity can be obtained. Manufacture cost can be further reduced as adding of extra masks is not needed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Structure and manufacturing method of power device MPT-TI-IGBT

InactiveCN103839987ALower on-resistanceReduce saturation pressure dropTransistorSemiconductor/solid-state device manufacturingVoltage dropGate oxide

The invention provides a structure of a power device MPT-TI-IGBT. The front face structure comprises a drift region, a grid, a gate-oxide piece, an emitter region, a base region and a heavily doped region, wherein the base region surrounds the lower portion of the emitter region and isolates the emitter region from the drift region. The emitter region and the heavily doped region are connected with an emitter, the emitter region and the drift region are connected with the grid, and the grid is insulated from a semi-conductor region through the gate-oxide region. The back face structure comprises a collector region, a short circuit region and a micro-punch-through region located below the drift region. The structure where the collector region and the short circuit region are distributed in a spaced mode is connected with collector metal so that a collector can be led out. The power device MPT-TI-IGBT is high in turn-off speed, and can reduce connection voltage drop and on-state losses of devices.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +2

MOS type power device and preparation method thereof

PendingCN109273529AGuaranteed Reliability CapabilitiesImprove high voltage and high current shutdown capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesChannel densityHigh pressure

The invention provides a MOS type power device and a preparation method thereof. A MOS-type power device comprises a substrate; a Well region; a Source region; a Gate oxide layer; a Gate electrode; anInsulating dielectric layer; A source region electrode, wherein a lower surface of the well region is provided with a protrusion extending downward. Thus, the MOS type power device has a well depth deep enough, sufficient withstand voltage margin can be ensured, At the same time, it has enough short channel and lower saturation voltage drop to increase channel density and reduce channel short-circuit current, effectively reduce on-resistance and improve short-circuit safety ability, fully ensure the reliability of device application, and has quasi-channel current self-pinch-off function to enhance the high-voltage and large-current shutdown ability of the device.

Owner:BYD SEMICON CO LTD

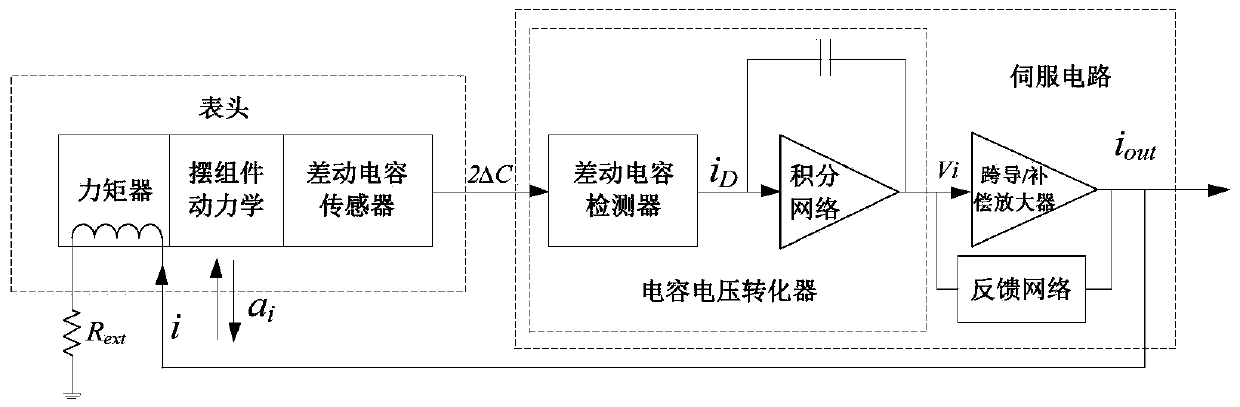

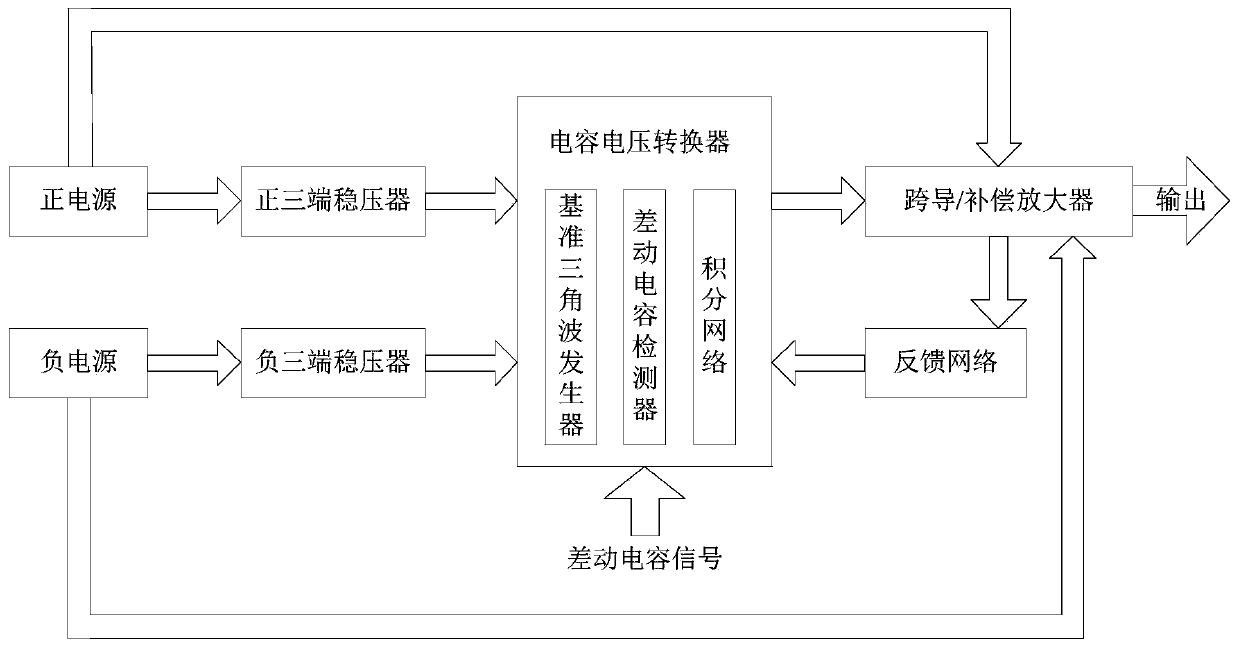

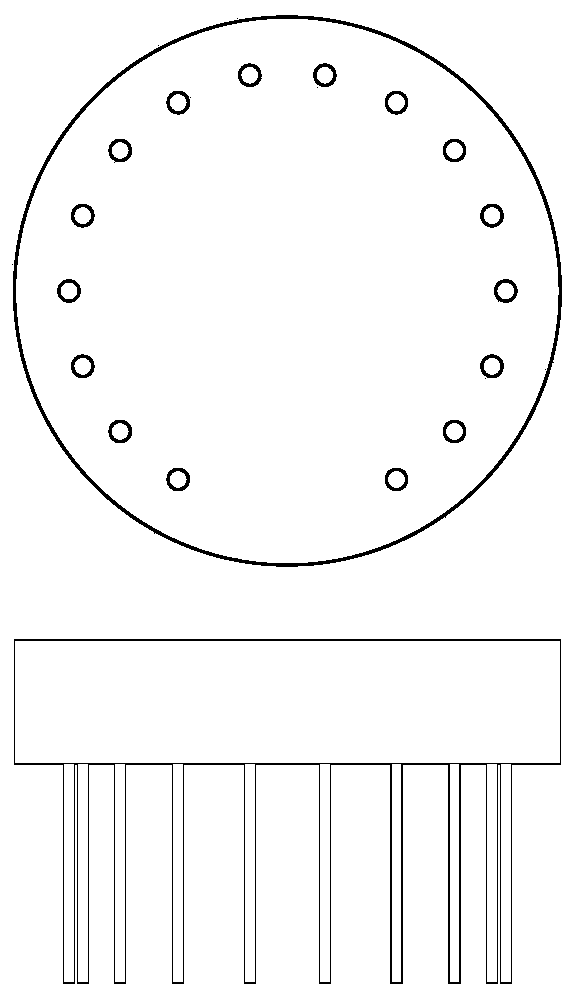

Miniature metal fully-sealed servo circuit of quartz flexible accelerometer and processing method of servo circuit

InactiveCN110579626AReduce weightReduce saturation pressure dropAcceleration measurementTransconductanceDifferential capacitance

The invention provides a miniature metal fully-sealed servo circuit of a quartz flexible accelerometer and a processing method of the servo circuit. The circuit comprises a capacitance-voltage converter, a transconductance / compensation amplifier and a feedback network, the capacitance-voltage converter comprises a differential capacitance detector and an integral network, the differential capacitance detector is connected with a differential capacitance sensor of an accelerometer gauge outfit, the differential capacitance detector, the integral network and the transconductance / compensation amplifier are connected in sequence, and the transconductance / compensation amplifier is connected with a torquer of the accelerometer gauge outfit; and all components of the servo circuit are integratedon a ceramic substrate through a thick film hybrid integration process, and the servo circuit is packaged in a metal full-sealed mode. According to the servo circuit, in a metal parallel seam packaging form, of the quartz flexible accelerometer, the servo circuit is full-sealed, and the problems in reliability and heat radiation of the servo motor in the extreme environment are solved.

Owner:XIAN MICROELECTRONICS TECH INST

Schottky barrier high current density igbt device

ActiveCN104966730BIncrease working voltageIncrease current densityTransistorSemiconductor/solid-state device manufacturingHigh current densitySchottky barrier

Owner:HUNAN UNIV

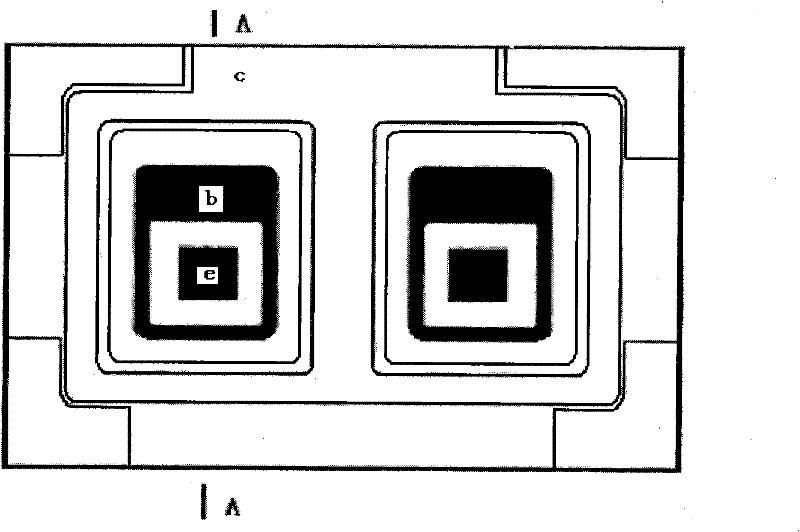

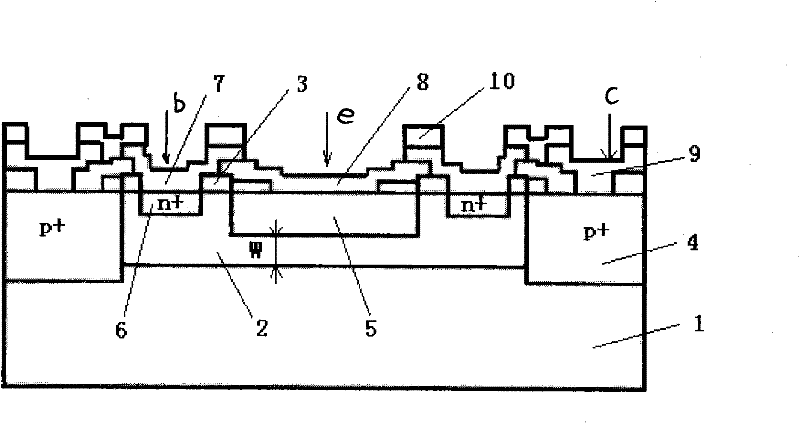

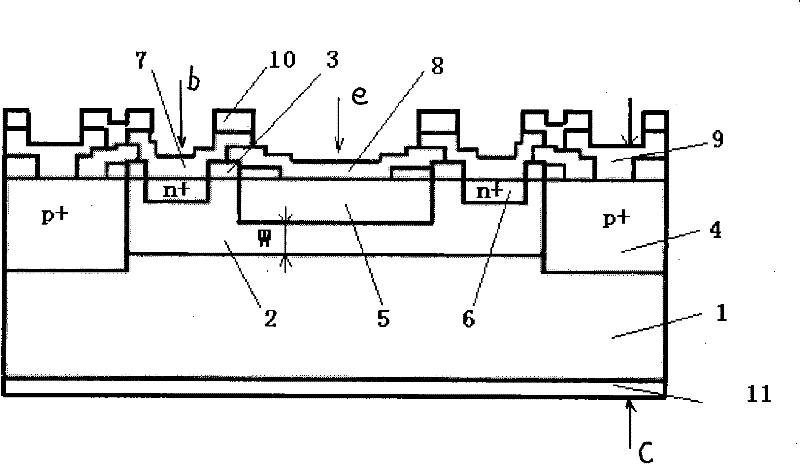

Suspended collector pnp integrated circuit transistor and method of making the same

ActiveCN105529361BP concentration is highReduced series resistanceTransistorSemiconductor/solid-state device manufacturingPower flowEngineering

The invention relates to a suspension collector PNP integrated circuit transistor and a manufacturing method thereof. An N-type first epitaxial layer and an N-type second epitaxial layer are sequentially formed on a P-type substrate; an N-type buried layer is arranged in the P-type substrate, a collector P-type buried layer is arranged in the first epitaxial layer which is positioned on the N-type buried layer, and a collector upper isolation unit is arranged in the second epitaxial layer which is positioned on the collector P-type buried layer; a P-type lower isolation unit is arranged in the first epitaxial layer which is positioned on the upper portion of the periphery of the N-type buried layer, and a P-type upper isolation unit is arranged in the second epitaxial layer which is positioned on the P-type lower isolation unit; a first P+ diffusion region is arranged in the P-type upper isolation unit, and serves as a collector; an N+ diffusion region is arranged in the second epitaxial layer enclosed by the collector upper isolation unit and the collector P-type buried layer, and serves as a base; and a second P+ diffusion region is arranged in the second epitaxial layer enclosed by the N+ diffusion region, and serves as an emitter. The suspension collector PNP integrated circuit transistor and the manufacturing method thereof can reduce collector series resistance and saturation voltage drop, and increase current output capacity.

Owner:CRM ICBG (WUXI) CO LTD

Insulated gate bipolar transistor and method of manufacturing the same

InactiveCN103378141BReduce saturation pressure dropPromote recoverySemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierEngineering

The invention relates to the field of electronic devices, and discloses an insulated gate bipolar transistor and a manufacturing method thereof. According to the insulated gate bipolar transistor and the manufacturing method thereof, a first doping region is used as a super junction in the insulated gate bipolar transistor, internal fast recovery diodes are formed in a channel region and a second doping region, the advantages of a super junction MOS and the advantages of a reverse conducting insulated gate bipolar transistor are combined, the saturation voltage drop of the insulated gate bipolar transistor can be effectively lowered, higher power density is achieved, and meanwhile due to the fact that the fast recovery diodes are removed in module packaging process, production cost can be effectively lowered. Due to a buffer region layer, the requirement for the thickness of a substrate is lowered, the buffer region layer is used for accelerating the composite process of charge carriers, the trailing time of insulated gate bipolar transistor products can be effectively shortened, the turn-off loss of the products is reduced, and the cut-off frequency of the products is increased.

Owner:上海永电电子科技有限公司

Manufacture method of isolation type power transistor

ActiveCN102956487BReduce crosstalk effectsLow densitySemiconductor/solid-state device manufacturingManufacturing cost reductionIsolation layer

The invention discloses a manufacture method of an isolation type power transistor. By the manufacture method, insulating medium layers formed on the top of gate polycrystalline silicon and spacer medium layers formed on the side faces of the insulating medium layers serve as hard masks for etching to form isolation layer trenches among devices, and an insulated isolation layer can be formed among transistors without adding extra masks, so that density of the transistors in a chip cannot be decreased, and mutual interference of the devices can be weakened. Increase of the size of the transistors and increase of density of transistors in the chip are benefited, and powder devices lower in breakover resistance and saturation voltage drop and higher in current driving capacity can be obtained. Manufacture cost can be further reduced as adding of extra masks is not needed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

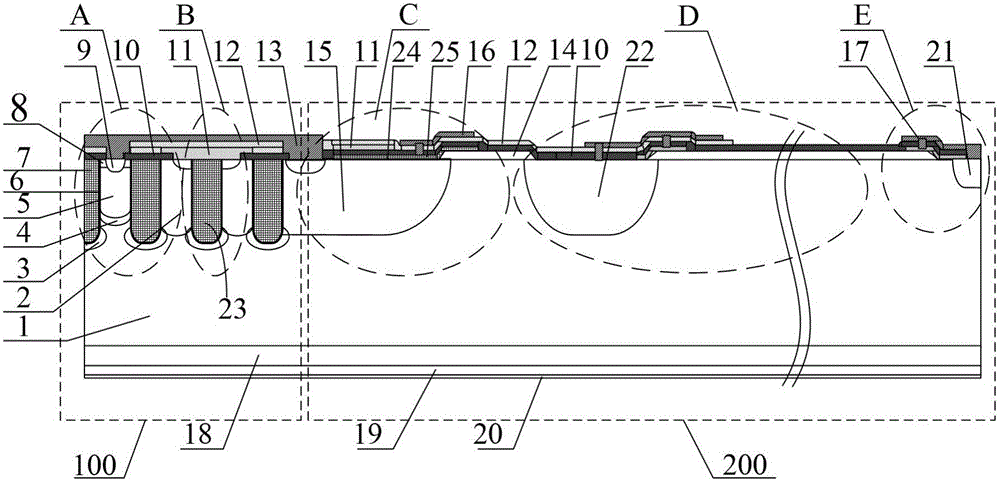

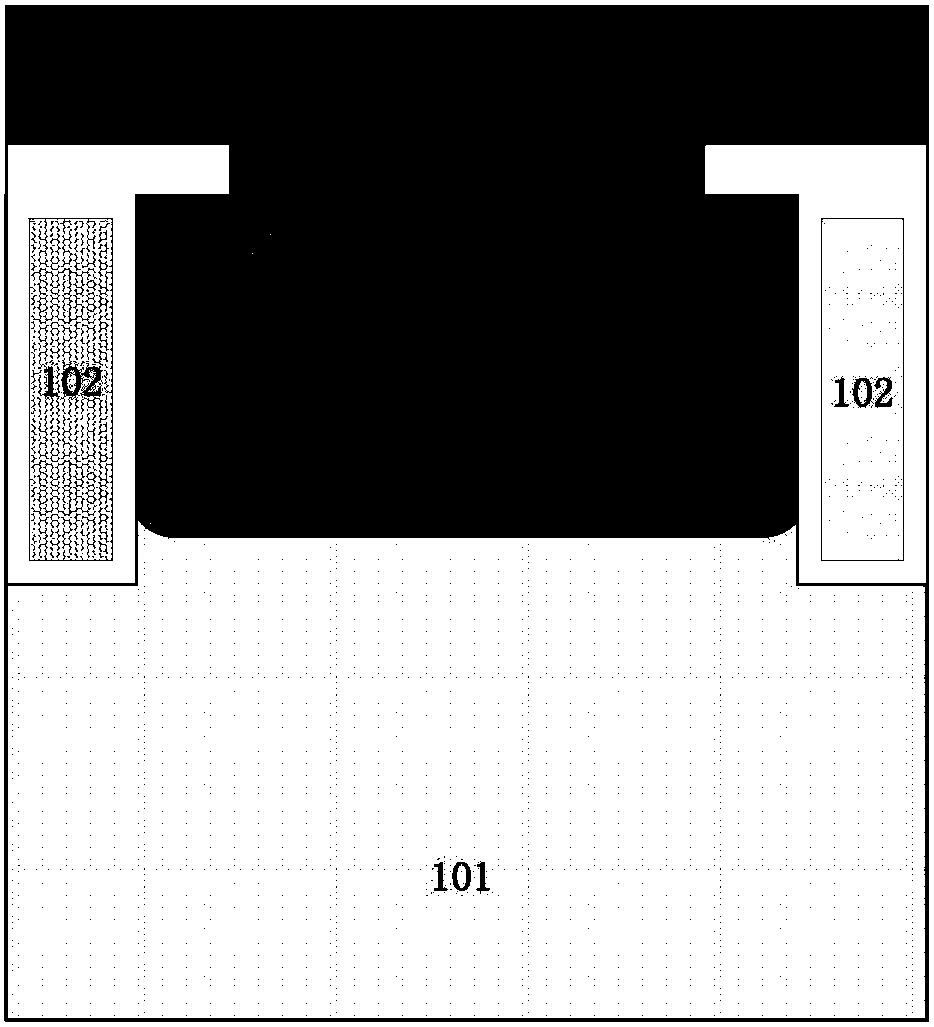

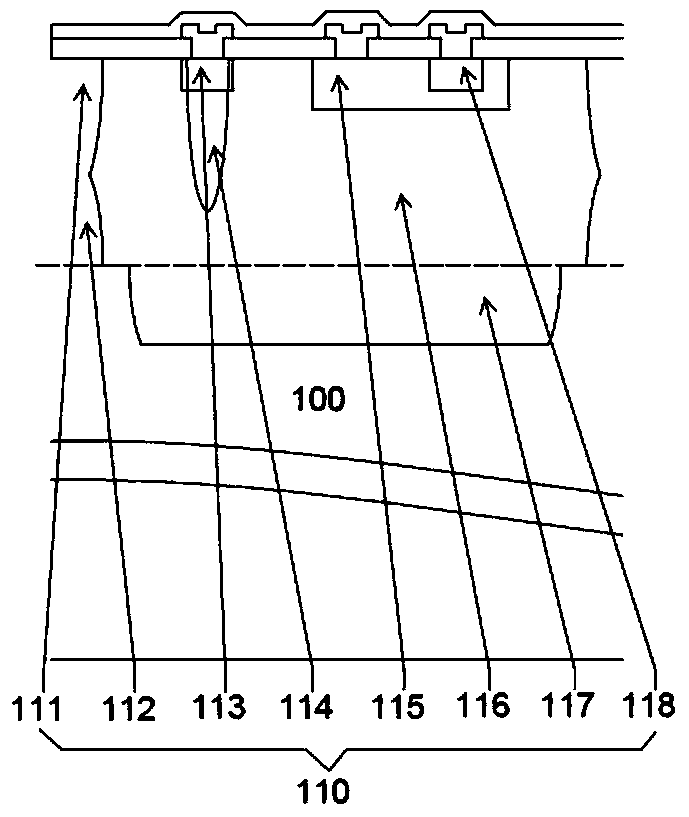

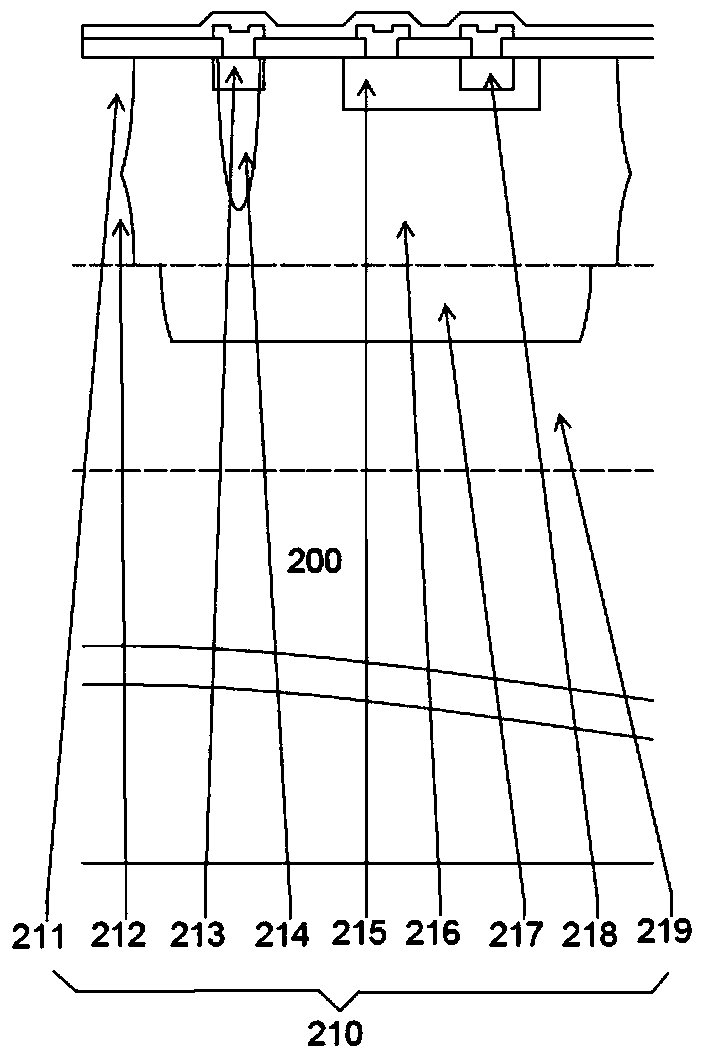

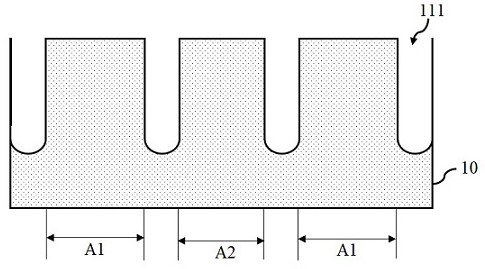

A kind of igbt device and its manufacturing process

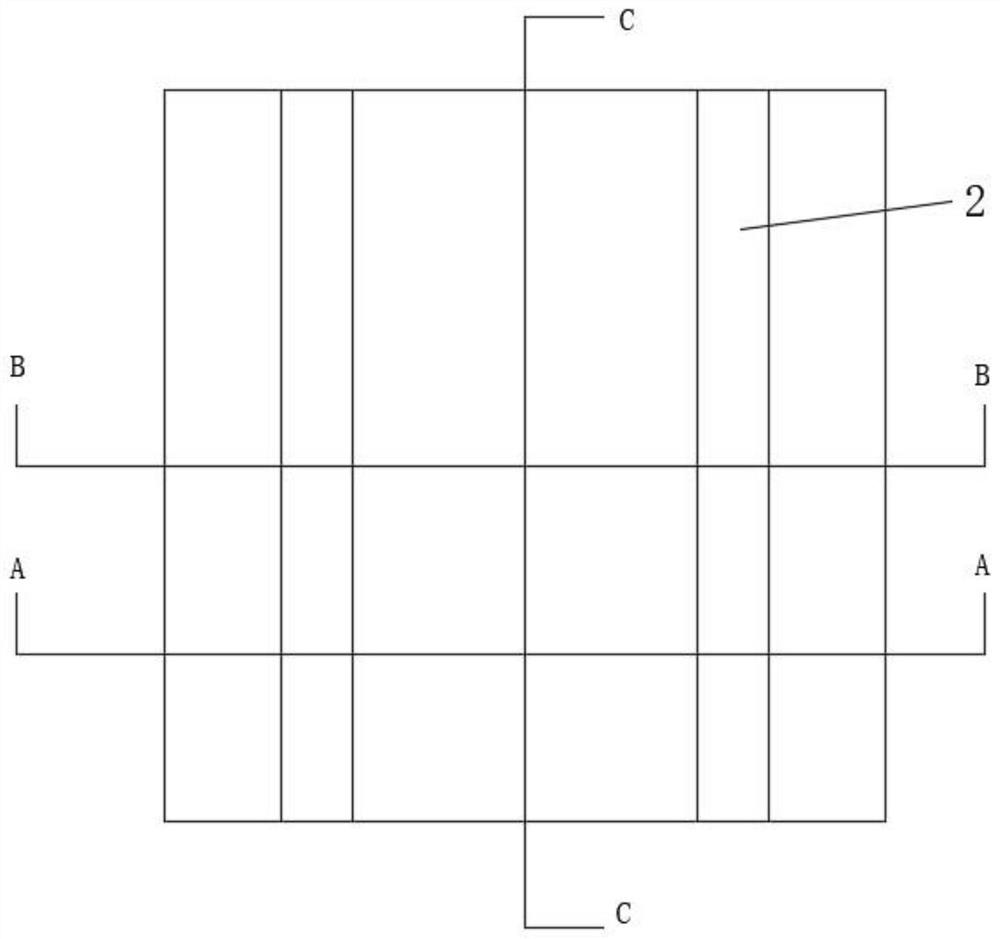

ActiveCN112117327BReduce generationReduce saturation pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesVirtual cellEngineering

The present invention provides an IGBT device, which has good short-circuit capability and can reduce the saturation voltage drop of the IGBT device and increase the current density, comprising a semiconductor substrate and cells arranged on the semiconductor substrate, and the cells include The effective cell and the virtual cell are characterized in that: on the cross section of the IGBT device, the effective cell includes: a first effective cell, a second effective cell, and a third effective cell, and the virtual cell includes : a first virtual cell, a second virtual cell, the first virtual cell is separated from the first effective cell by a trench gate, the second virtual cell is separated from the second effective cell Cells are separated by trench gates.

Owner:JIANGSU HAIDONG SEMICON TECH CO LTD

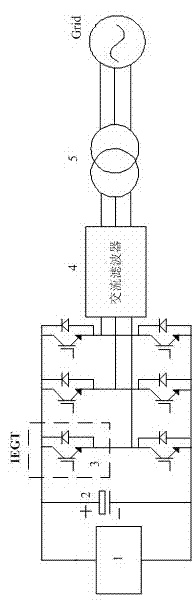

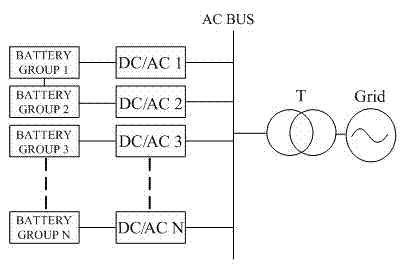

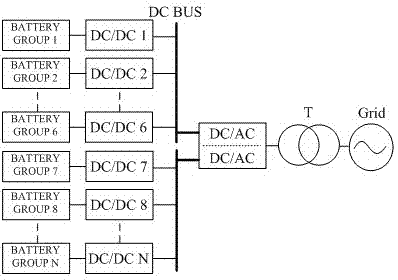

Power storage system based on IEGT (injection enhanced gate transistor)

InactiveCN103401261ALow saturation voltageReduce on-state voltage dropAc network load balancingConduction lossEngineering

The invention relates to the technical field of electronics, in particular to a power storage system based on an injection enhanced gate transistor (IEGT). By adopting the energy storage system, an IEGT device is used for replacing the current IGBT (insulated gate bipolar transistor) device in a power conversion system (PCS), the capacity of a single PCS is increased, the conduction loss is reduced, and the efficiency of the PCS is further improved.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD

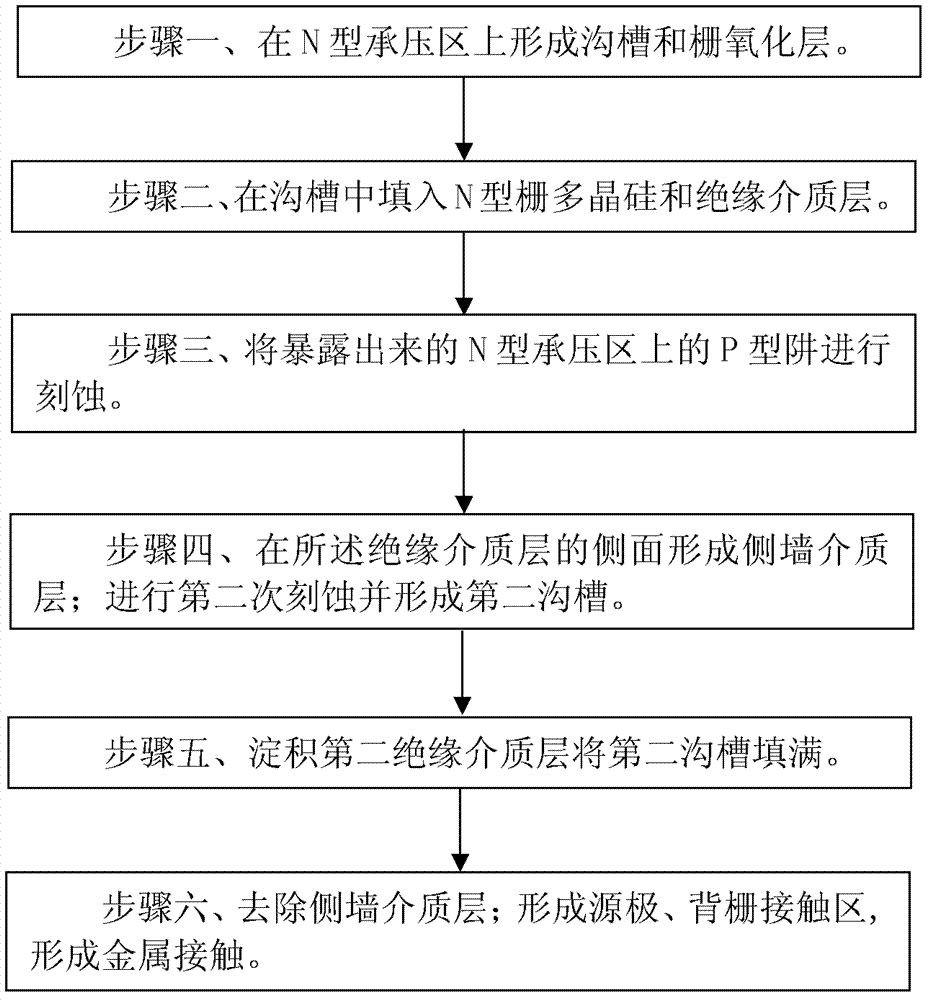

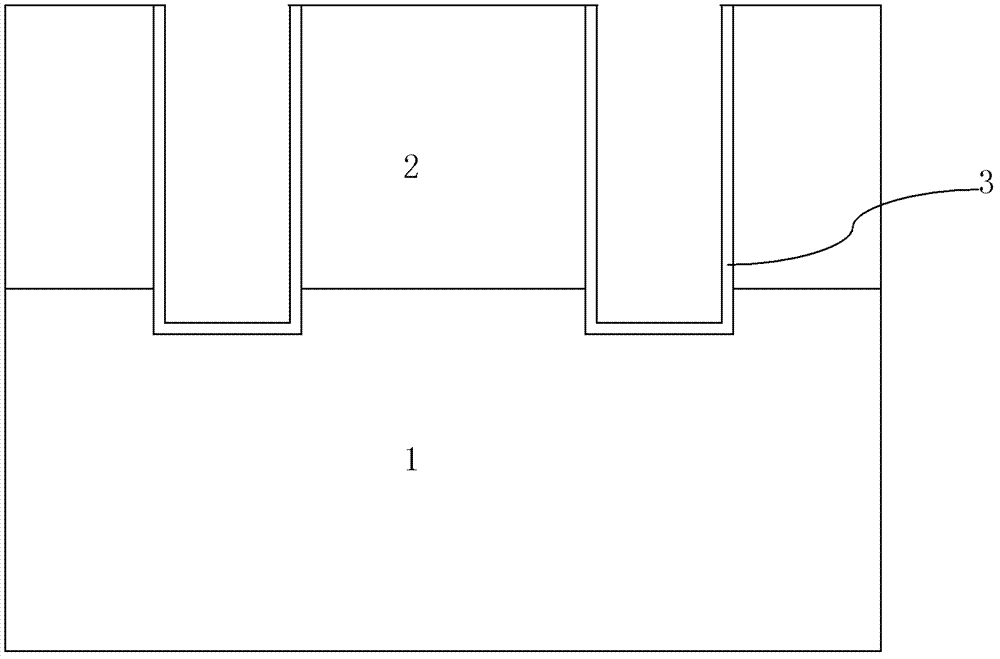

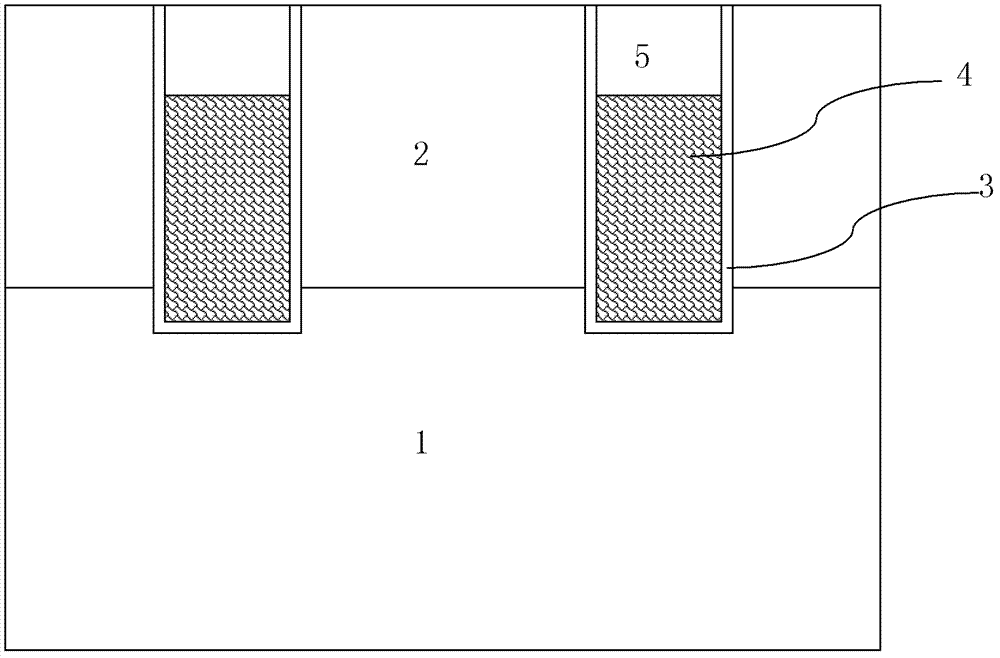

IGBT having super junction structure and preparation method thereof

ActiveCN104779276AReduce saturation pressure dropImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSaturation voltageElectric field

The present invention discloses an IGBT having with a super junction structure. The IGBT having the super junction structure comprises a collector, a drift region, a P-type base region and an N-type emitter region, wherein, gate grooves are formed in the P-type base region and the N-type emitter region, gate electrodes being arranged in the gate grooves; P-type regions are formed between the bottom of the gate grooves and the collector; the P-type regions are respectively connected with the bottom of the gate grooves and the collector; and spaces between the adjacent P-type regions are filled with an insulating medium. The present invention further discloses a preparation method of the IGBT having the super junction structure. The IGBT having the super junction structure provided by the present invention can generate a transverse electric field so as to improve the breakdown voltage and reduce the saturation voltage drop of a device. The preparation method provided by the present invention has the advantage of short processing time.

Owner:SHANGHAI TUNA ELECTRIC MECHANIC EQUIP CO LTD

Method for manufacturing integrated PNP differential pair tube

InactiveCN101740383BIncrease reverse voltageImprove reliabilitySemiconductor/solid-state device manufacturingPhysical chemistryEngineering

The invention relates to a method for manufacturing an integrated PNP differential pair tube. The method comprises the following steps: selecting a one-side polishing P+ silicon substrate with specific resistance ranging between 0.001 and 0.008ohm-centimeter; growing an epitaxial layer serving as an N base region on the silicon substrate, wherein the specific resistance of the epitaxial layer is between 0.2 and 2.0ohm-centimeter and the thickness is between 10 and 20 mu m, and growing an oxidation layer through thermal oxidation; diffusing boron on the surface of the N base region and connecting a diffused boron agglomeration with the P+ silicon substrate to form a common P+ collecting zone, and separating the epitaxial layer into two separate base regions; diffusing the boron on the surface of the N base region to form an emitter region and controlling the effective width of the N base region between 5 and 10 mu m; diffusing phosphorus on the surface of the N base region to form a contact zone of the N+ base region; leading metal electrodes out from the surface of the contact zone of the N+ base region, the P+ collecting zone surface and the emitter region surface; and leading the metal electrodes out from the surface of the P+ collecting zone or the back side of the P+ silicon substrate. The method has the advantages that the method can effectively reduce saturation voltage drop to ensure that base-emitter reverse voltage reaches 30-100V; and devices not only have a large forward DC amplification coefficient Beta, but also have a reverse DC amplification coefficient Betareaching 8 to 15.

Owner:JINZHOU 777 MICROELECTRONICS

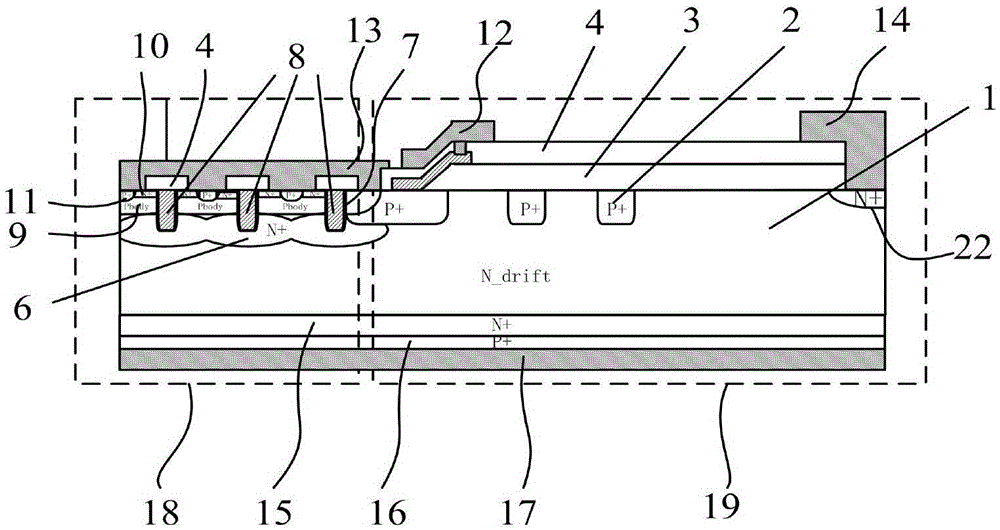

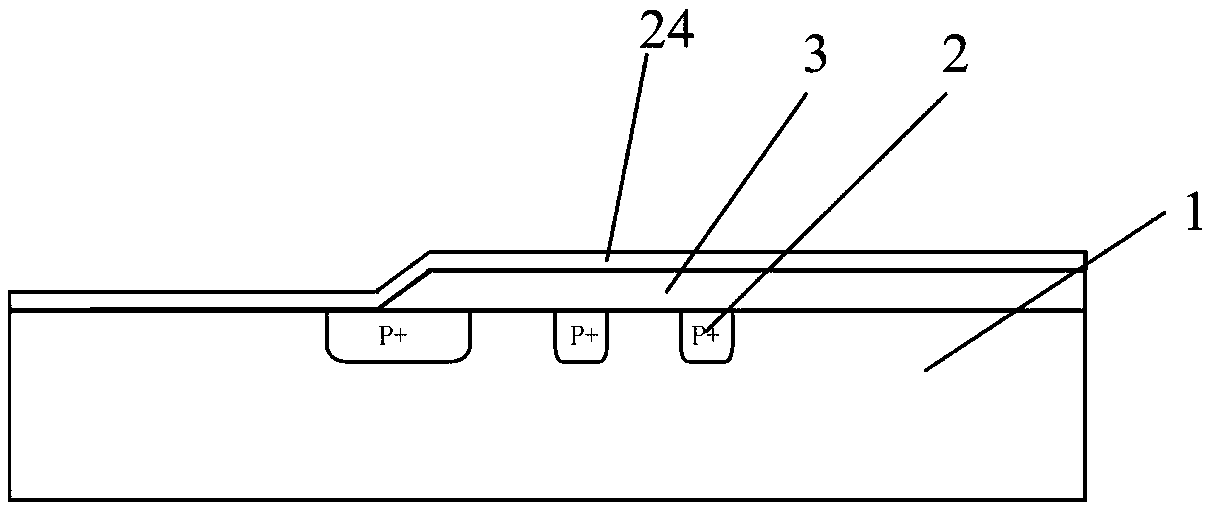

LIGBT with carrier storage region

The invention discloses a LIGBT with a carrier storage region. The LIGBT comprises an N-type drift region. The N-type drift region comprises an N-type silicon strip. The N-type silicon strip includesthe carrier storage region. The carrier storage region is doped with hydrogen ions. The N-type drift region of the LIGBT comprises the N-type silicon strip, and the N-type silicon strip includes the carrier storage region doped with hydrogen ions so that the carrier storage region can be represented as a hole barrier layer and can reduce the saturation voltage drop Vcesat when the LIGBT is forwardturned on and can also be represented as a composite center and and can shorten the lifetime of minority carriers when the LIGBT is turned off, thus shortening the turn-off time.

Owner:ADVANCED SEMICON MFG CO LTD

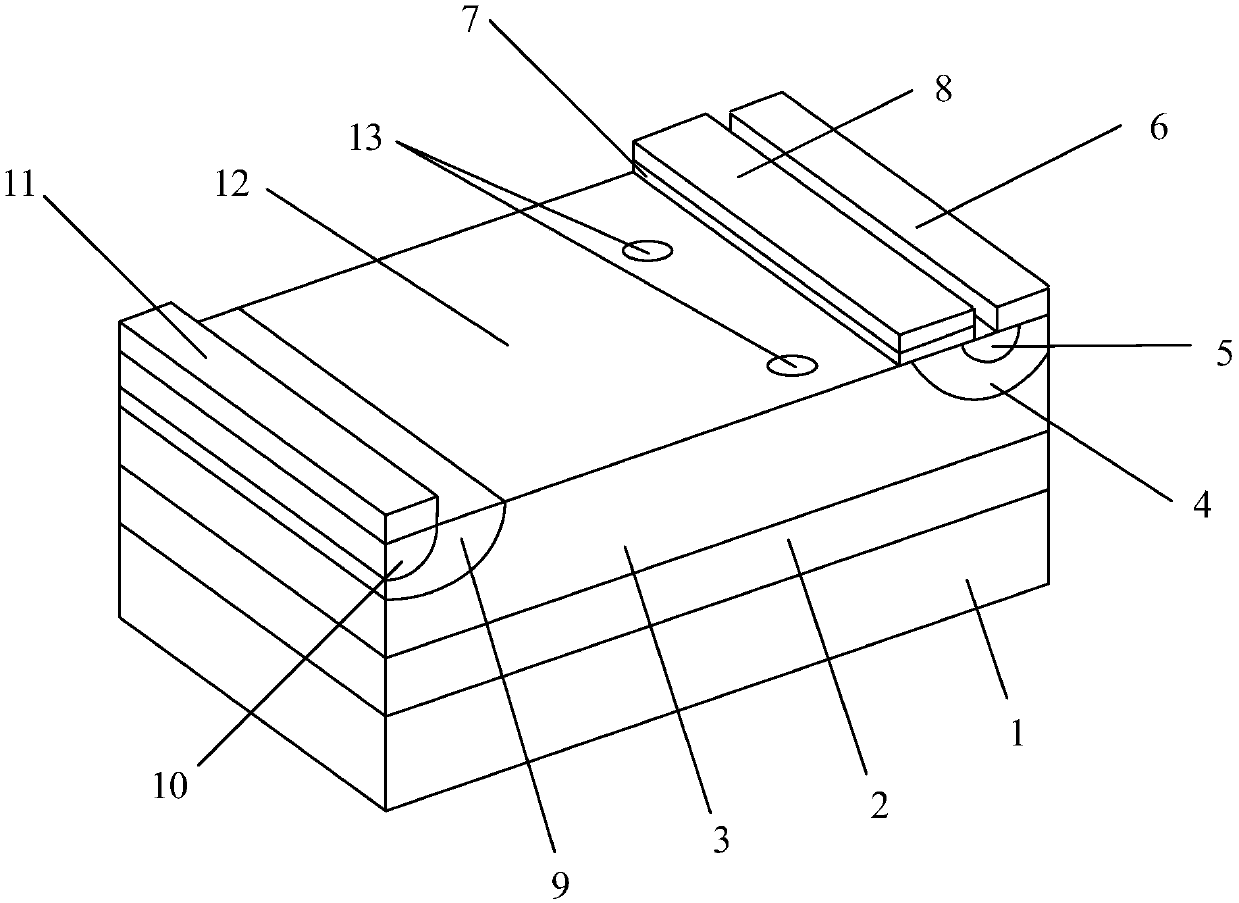

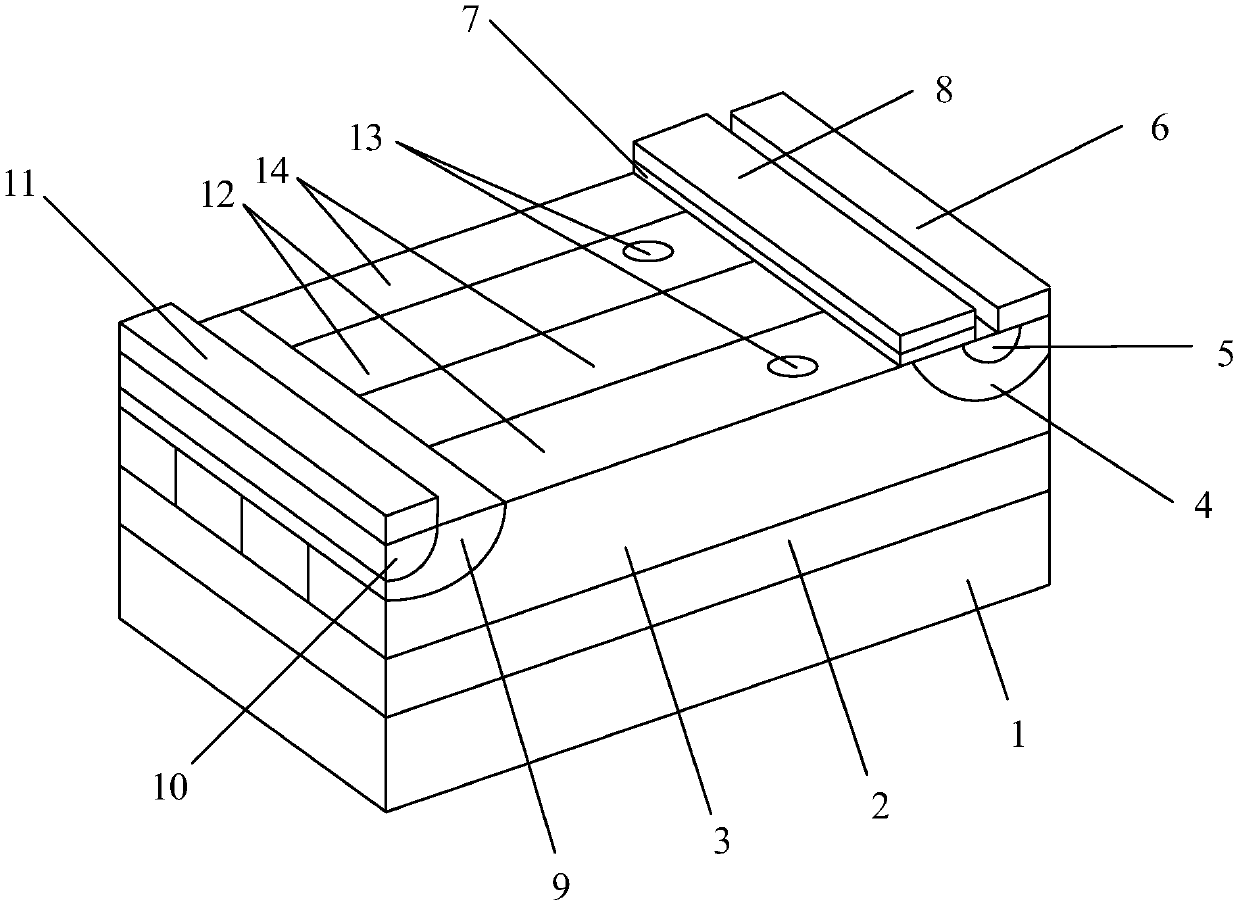

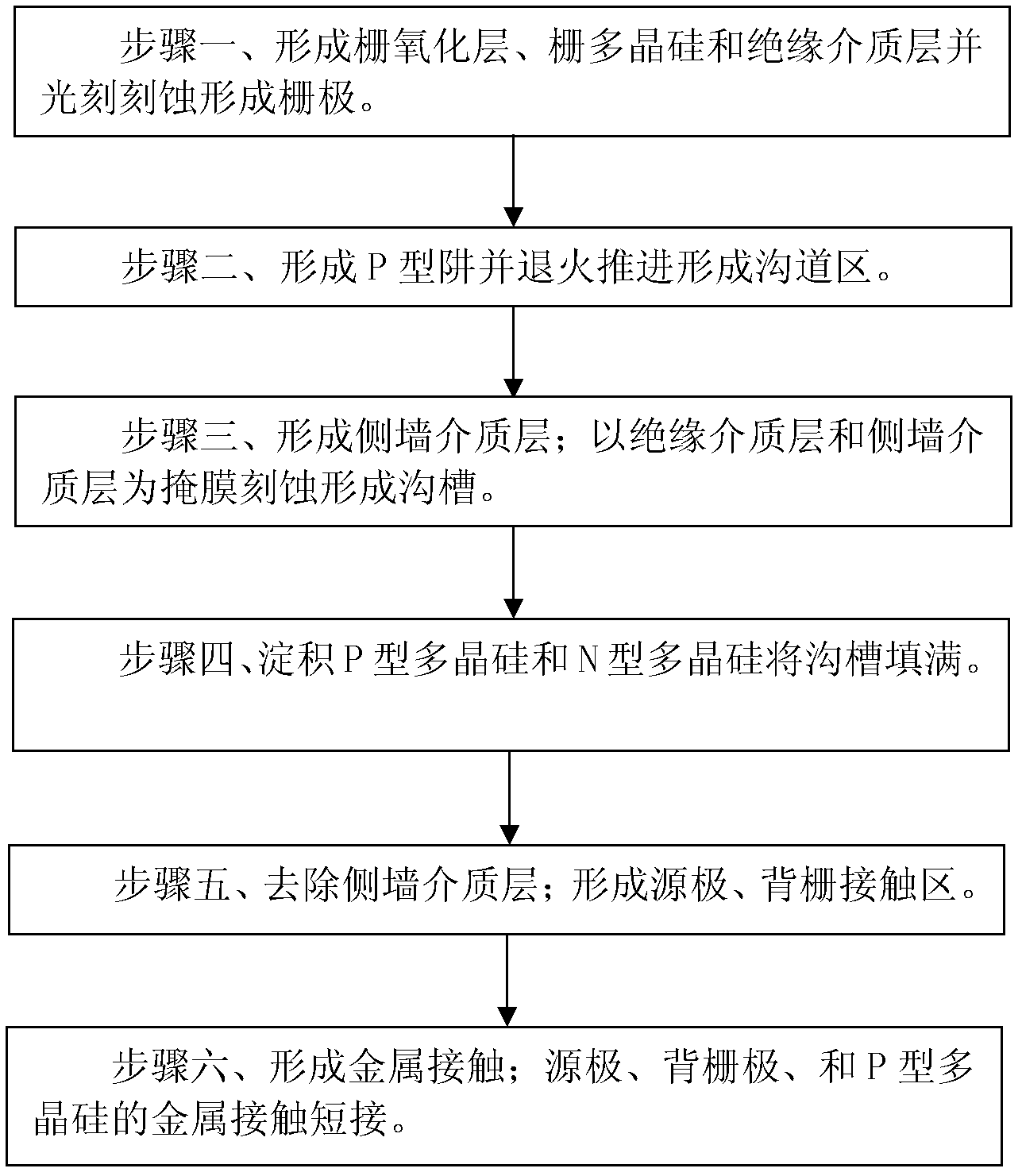

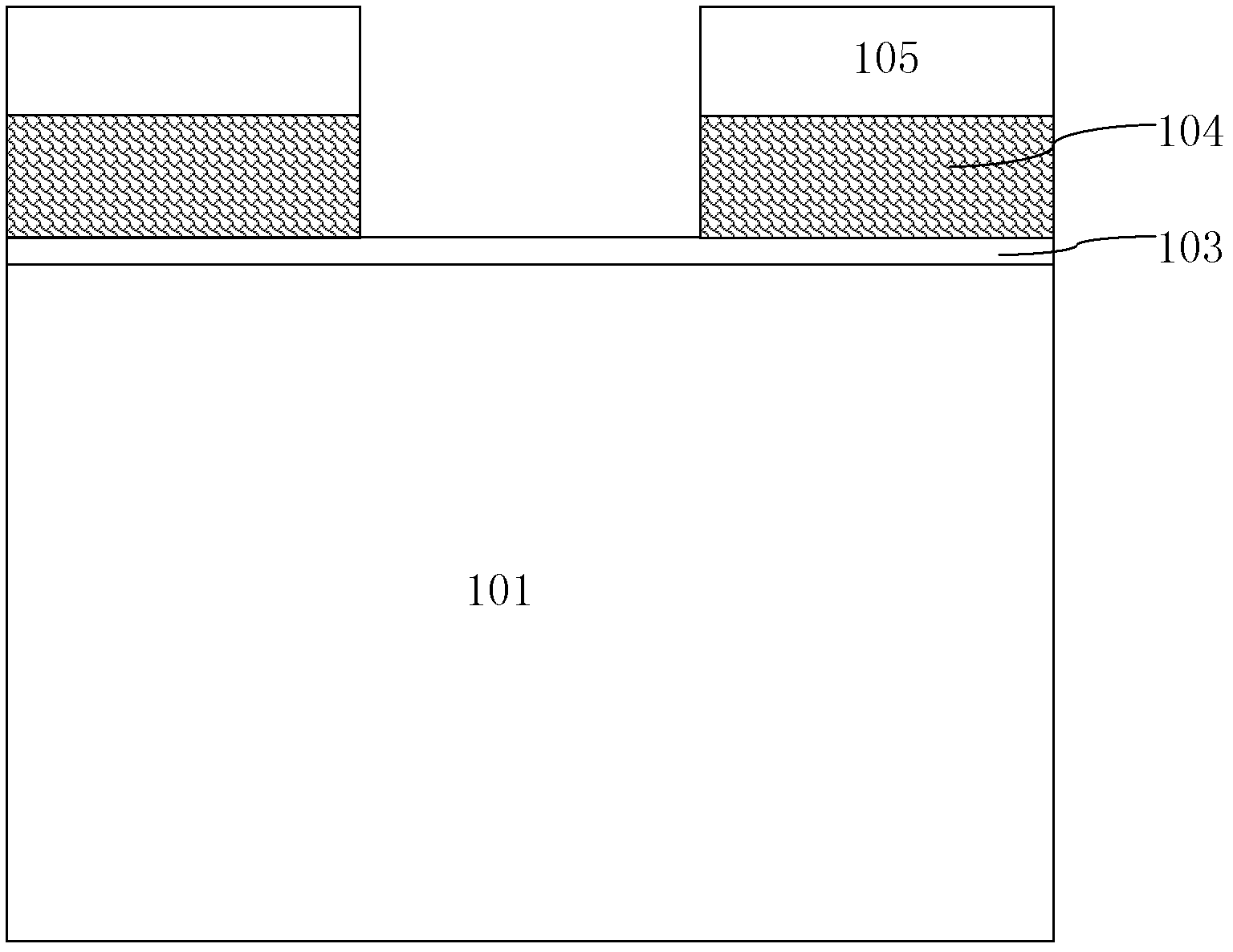

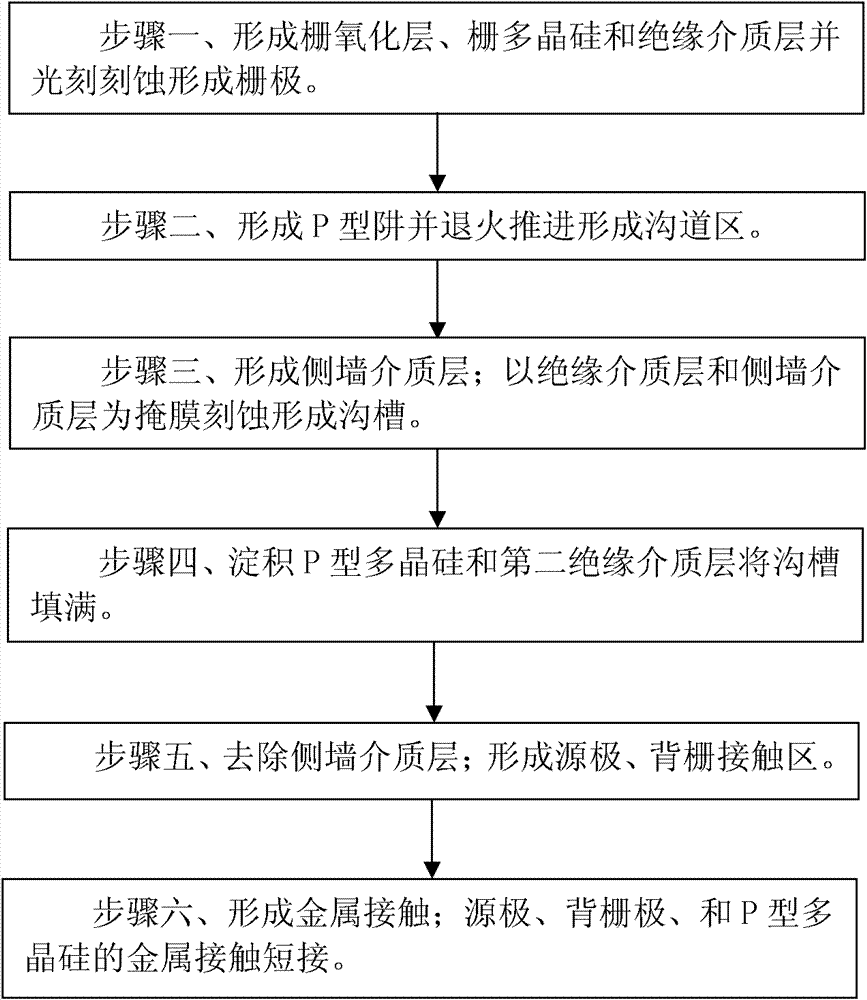

Power transistor manufacture method

ActiveCN102956488BReduce in quantityHigh densitySemiconductor/solid-state device manufacturingPower flowEngineering

The invention discloses a power transistor manufacture method. By the method, insulating medium layers formed on the top of gate polycrystalline silicon and spacer medium layers formed on the side faces of the insulating medium layers serve as hard masks for etching a pressure-bearing region, so that the number of masks required by the front-side process is decreased, and the density of transistors in a chip can be increased. By the aid of the method, a trench is formed in a P-type well region by etching, and a P-type polycrystalline silicon layer and an N-type polycrystalline silicon layer are filled inside the trench and subjected to annealing to promote formation of a source electrode and a back gate contact region which are longitudinally distributed, so that latching resistance of devices can be improved, and power devices lower in breakover resistance and saturation voltage drop and higher in current driving capacity can be obtained beneficially.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

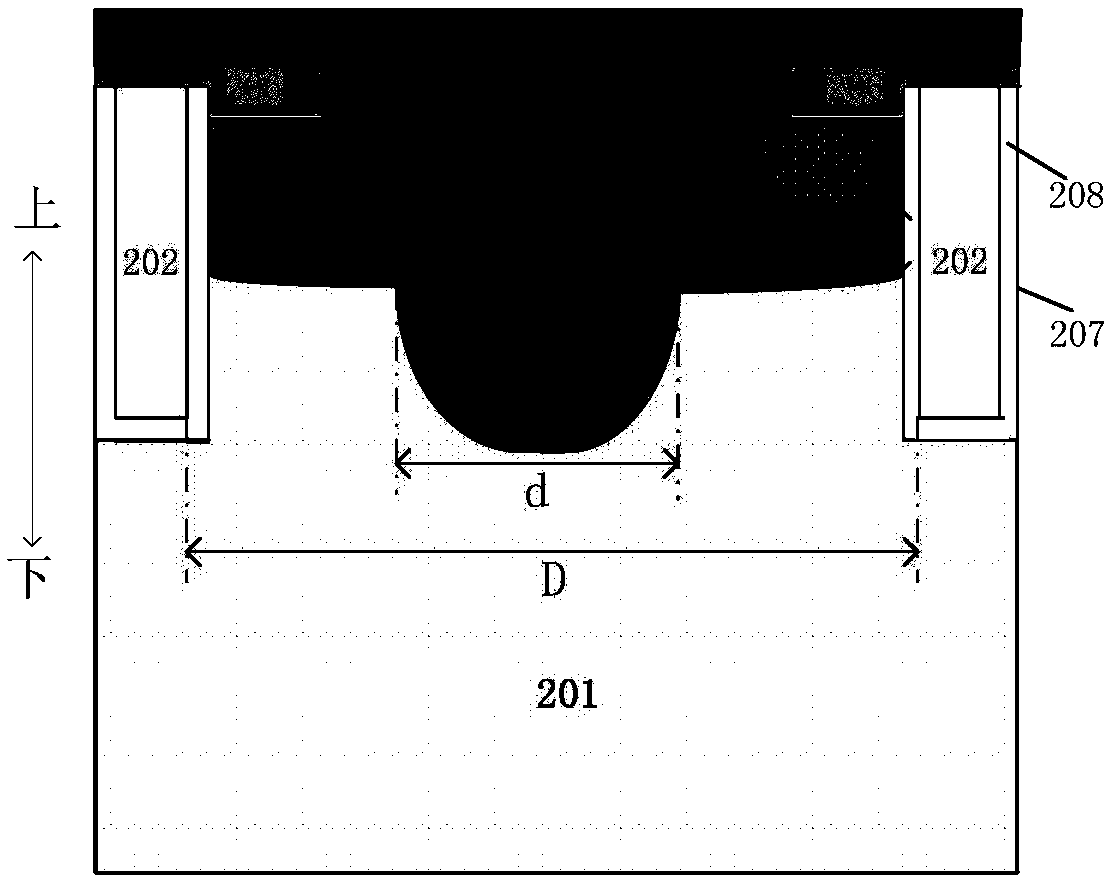

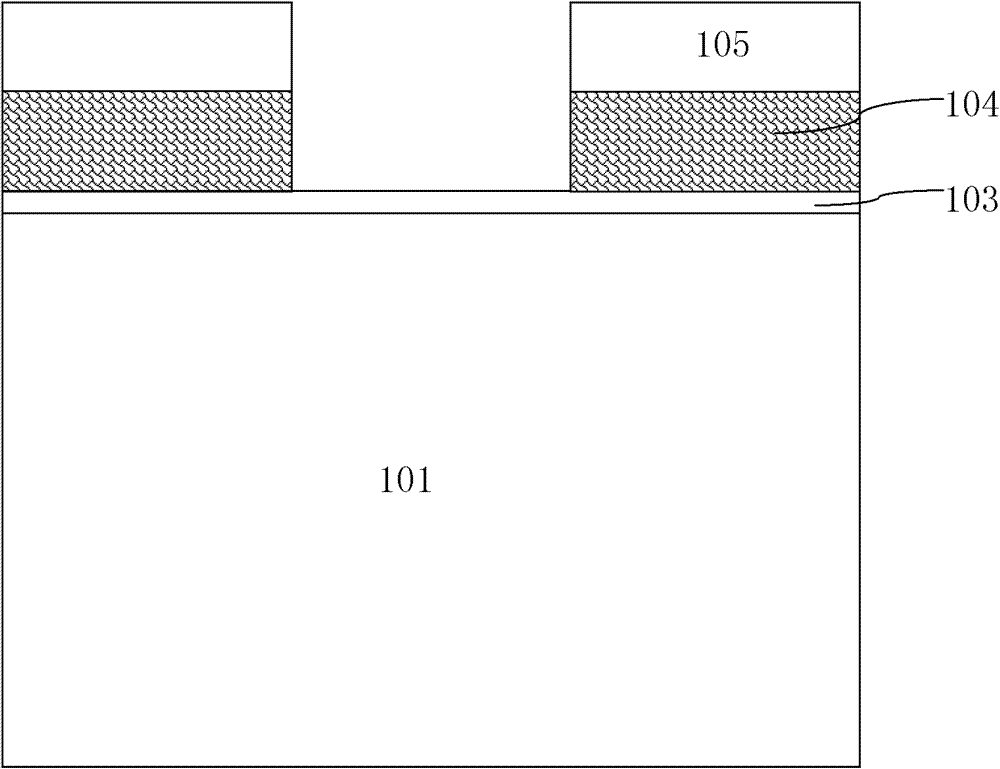

Insulated gate bipolar transistor and manufacturing method thereof

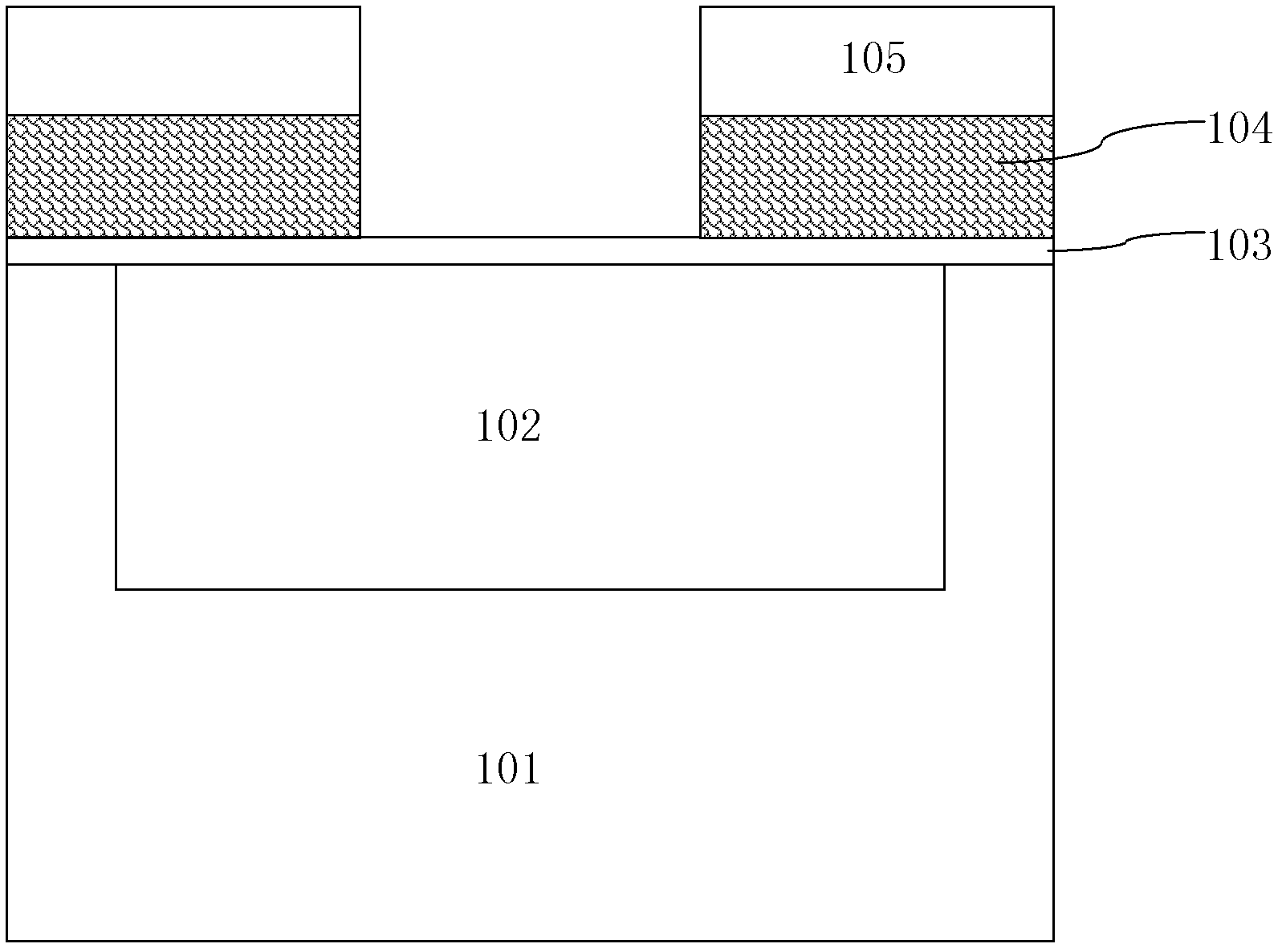

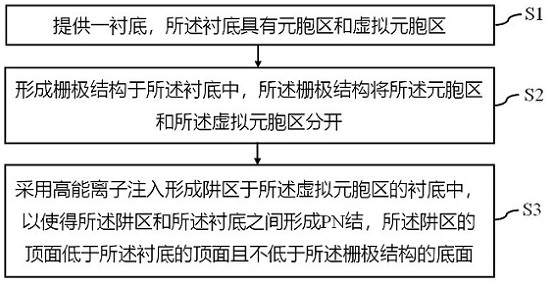

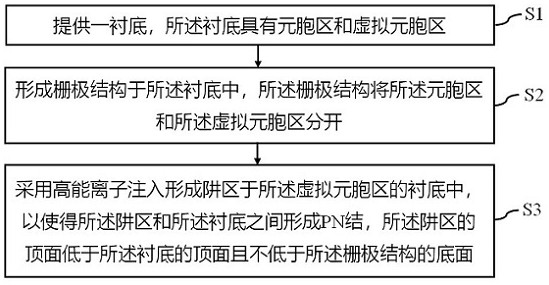

ActiveCN111933702BAccurate control of junction depthImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesVirtual cellCell region

The invention provides an insulated gate bipolar transistor and a manufacturing method thereof. The manufacturing method of the insulated gate bipolar transistor includes: providing a substrate, the substrate having a cell region and a dummy cell region; forming A gate structure is in the substrate, and the gate structure separates the cell region from the dummy cell region; and, high-energy ion implantation is used to form a well region in the substrate of the dummy cell region , so that a PN junction is formed between the well region and the substrate, and the top surface of the well region is lower than the top surface of the substrate and not lower than the bottom surface of the gate structure. The technical scheme of the invention can accurately control the junction depth of the PN junction in the virtual cell area, thereby improving the withstand voltage of the device, reducing the saturation voltage drop of the device, and improving the stability and uniformity of the threshold voltage.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP +1

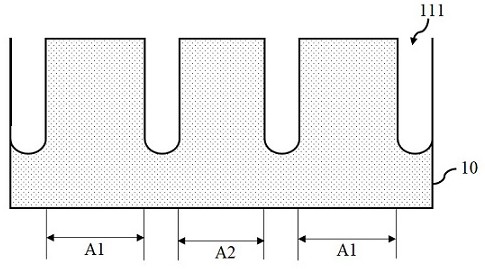

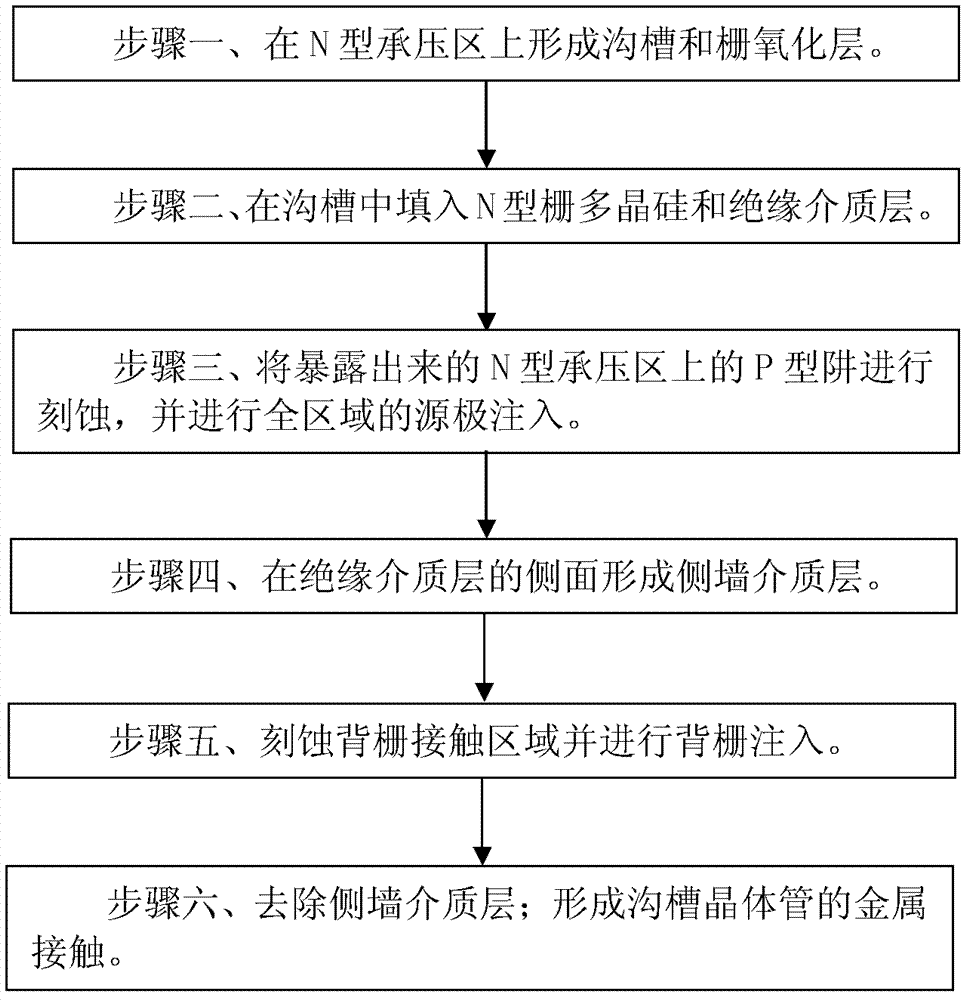

Manufacture method of trench transistor

ActiveCN102956489BReduce in quantitySmall sizeSemiconductor/solid-state device manufacturingMedia layerSaturation voltage

The invention discloses a manufacture method of a trench transistor. The manufacture method includes: subjecting a source electrode region to etching and source electrode implantation by forming insulating medium layers on the top of gate polycrystalline silicon and using the insulating medium layers as masks, and subjecting a back gate contact region to etching and back gate implantation by forming spacer medium layers on the side faces of the insulating medium layers and using the insulating medium layers and the spacer medium layers as masks. Therefore, the number of masks required by the front-side process can be decreased, production cost can be lowered, and limitations of different masks on alignment errors can be avoided, and further, the size of the trench transistors is further deceased, the density of trench transistors in a chip is increased, and the trench transistors lower in breakover resistance and saturation voltage drop and higher in current driving capacity are obtained beneficially.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A kind of igbt with superjunction structure and preparation method thereof

ActiveCN104779276BReduce saturation pressure dropIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSaturation voltage

The present invention discloses an IGBT having with a super junction structure. The IGBT having the super junction structure comprises a collector, a drift region, a P-type base region and an N-type emitter region, wherein, gate grooves are formed in the P-type base region and the N-type emitter region, gate electrodes being arranged in the gate grooves; P-type regions are formed between the bottom of the gate grooves and the collector; the P-type regions are respectively connected with the bottom of the gate grooves and the collector; and spaces between the adjacent P-type regions are filled with an insulating medium. The present invention further discloses a preparation method of the IGBT having the super junction structure. The IGBT having the super junction structure provided by the present invention can generate a transverse electric field so as to improve the breakdown voltage and reduce the saturation voltage drop of a device. The preparation method provided by the present invention has the advantage of short processing time.

Owner:SHANGHAI TUNA ELECTRIC MECHANIC EQUIP CO LTD

Direct-current overvoltage protection circuit

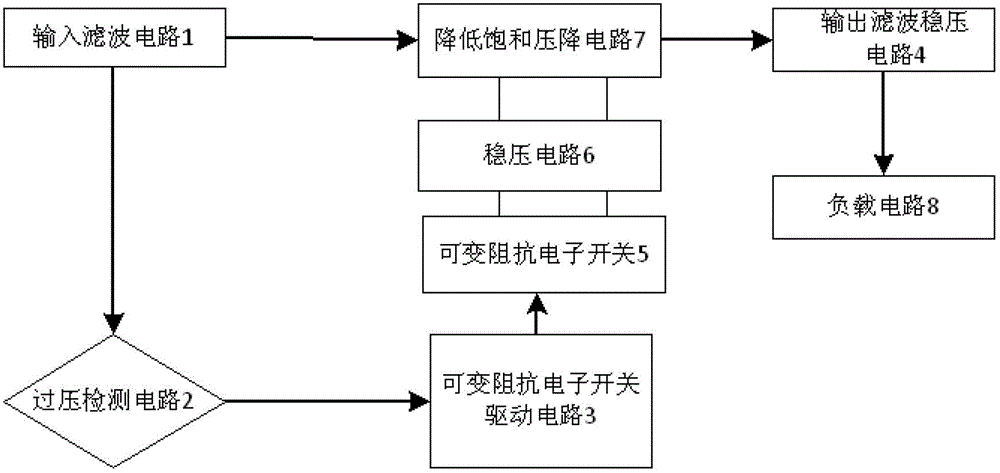

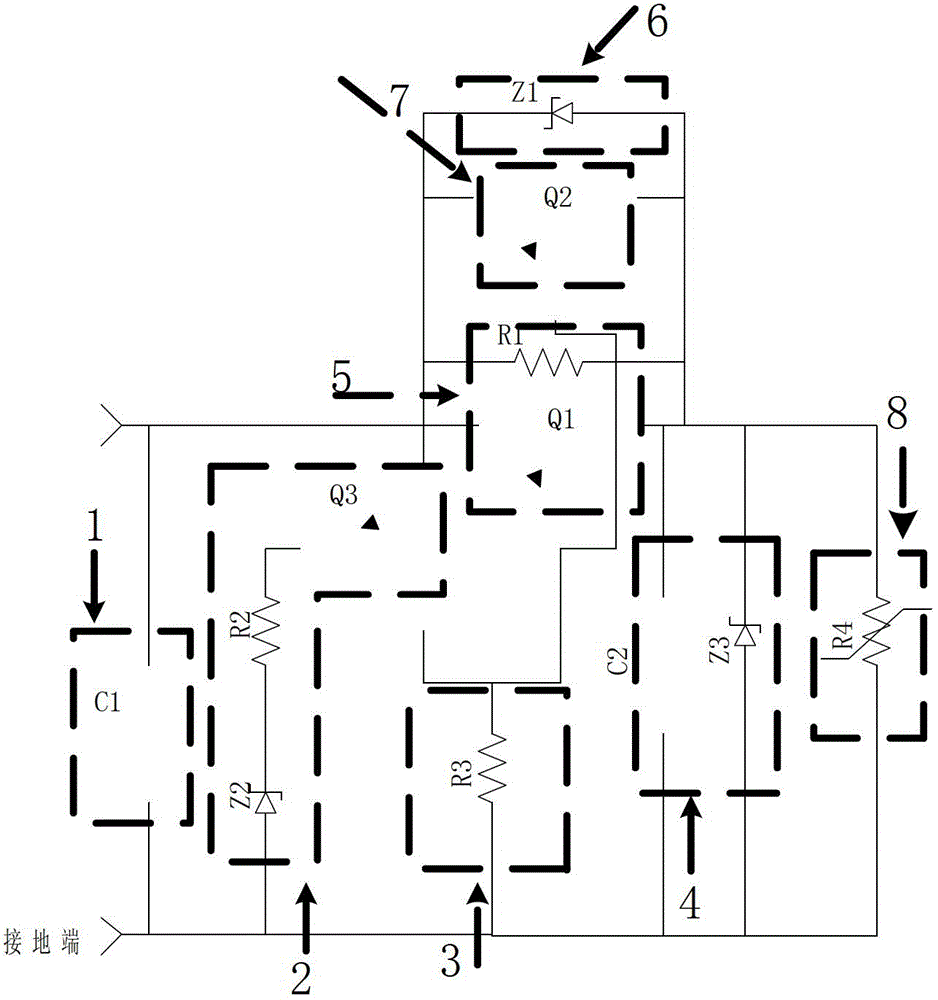

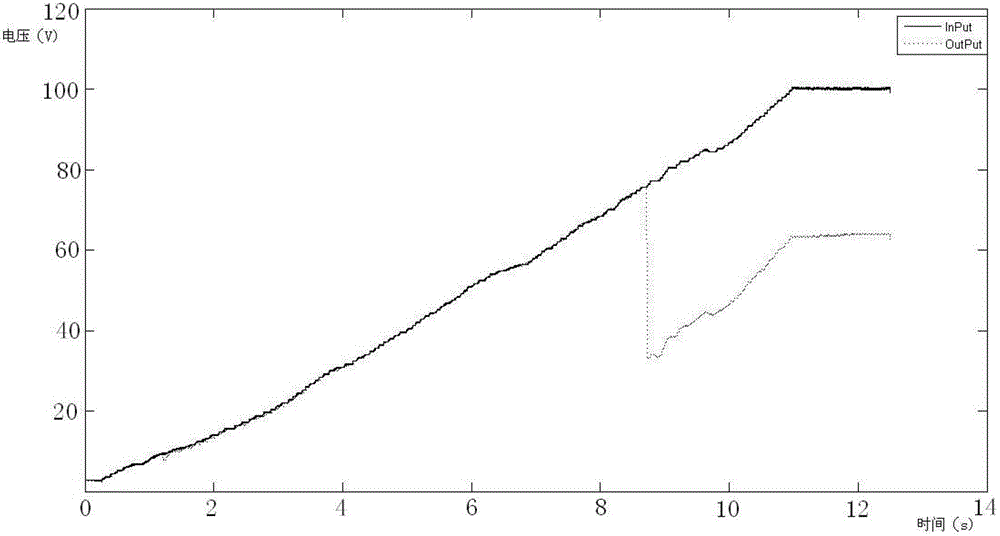

ActiveCN103326345BIncrease load capacityReduce the effect of load changesEmergency protective arrangements for limiting excess voltage/currentOvervoltageElectronic switch

The invention discloses a direct-current overvoltage protection circuit. The direct-current overvoltage protection circuit comprises an input filter circuit, an overvoltage detection circuit, a variable impedance electronic switch drive circuit, a variable impedance electronic switch circuit, a voltage stabilizing circuit, a reduced saturation voltage drop circuit, an output filter voltage stabilizing circuit and a load, wherein the input end of the input filter circuit is connected with an input signal; the output end of the input filter circuit is respectively connected with the overvoltage detection circuit and the reduced saturation voltage drop circuit; the output of the overvoltage detection circuit is connected with the variable impedance electronic switch drive circuit; the output of the variable impedance electronic switch drive circuit is connected with the variable impedance electronic switch circuit; the output of the variable impedance electronic switch circuit is connected with the voltage stabilizing circuit; the output of the voltage stabilizing circuit is connected with the reduced saturation voltage drop circuit; the output of the reduced saturation voltage drop circuit is connected with the output filter voltage stabilizing circuit; and the output of the output filter voltage stabilizing circuit is connected with the load.

Owner:SOUTHEAST UNIV

A method for manufacturing a silicon epitaxial wafer of a high-power pin device

ActiveCN104409345BReduce the effect of self-dopingReduce widthSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationGas phase

The invention provides a manufacturing method of a silicon epitaxial wafer of a large-power PIN device. The method is that a highly As-doped N type <100> polished wafer of which the resistivity does not exceeds 0.003 ohm / cm and local flatness does not exceeds 1.5mm and the rear surface is free of a back seal oxide layer is adopted. The manufacturing method of the silicon epitaxial wafer of the large-power PIN device has the advantages that 1, polycrystalline silicon is transferred from a graphite base to the rear surface of a substrate by the mass transfer principle, so as to reach the back enveloping purpose; 2, proper atmospheric corrosion flow and atmospheric corrosion time are selected and the gas phase concentration of atmospheric corrosion impurities in an epitaxial reaction chamber is reduced so as to reduce self doping under epitaxial growth; 3, after atmospheric corrosion, variable temperature and flow hydrogen is selected to purge the epitaxial reaction chamber; 4, during the growth of a first epitaxial layer, an intrinsic epitaxial layer grows under relatively low temperature to envelope the high-concentration substrate surface, and the growth temperature, rate and time are controlled to reach an ideal enveloping layer; and 5, during the growth of a second epitaxial layer, an epitaxial layer of which the surface concentration is below 10E13cm-3 grows under a low temperature.

Owner:NANJING GUOSHENG ELECTRONICS

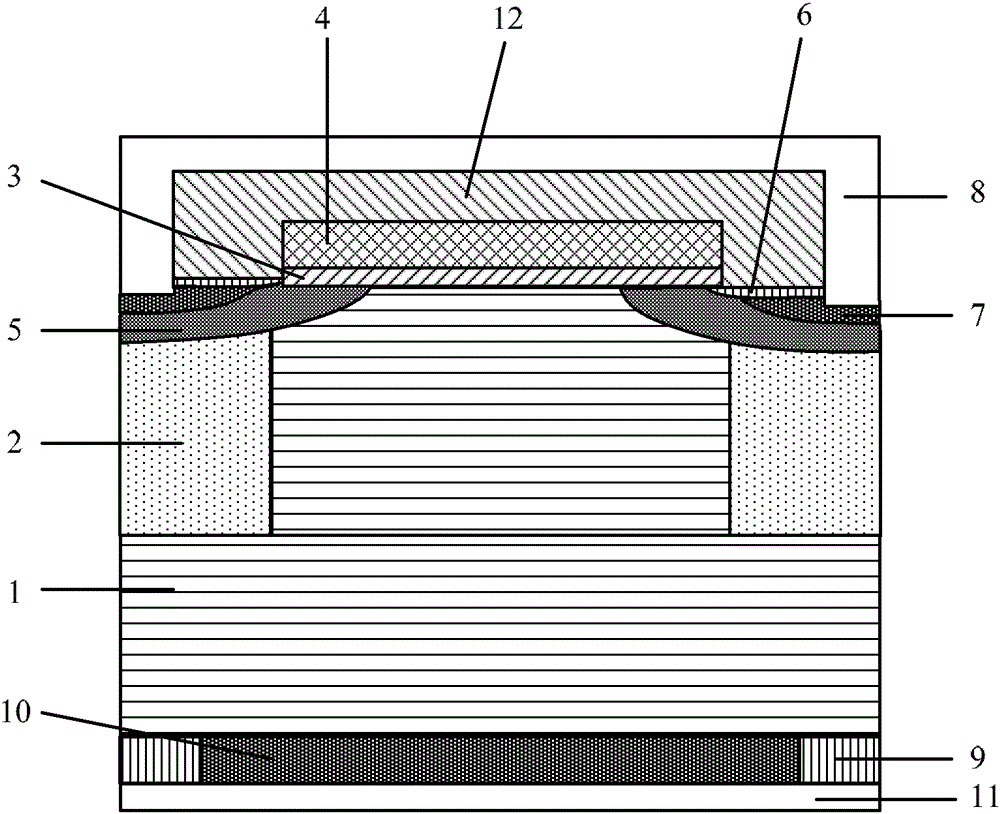

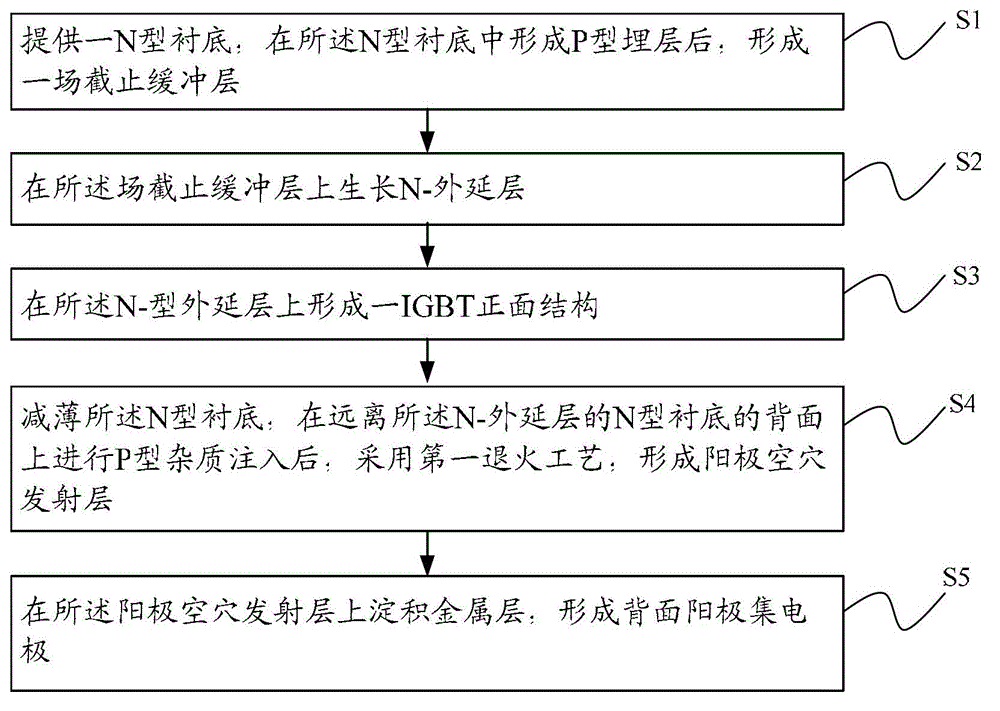

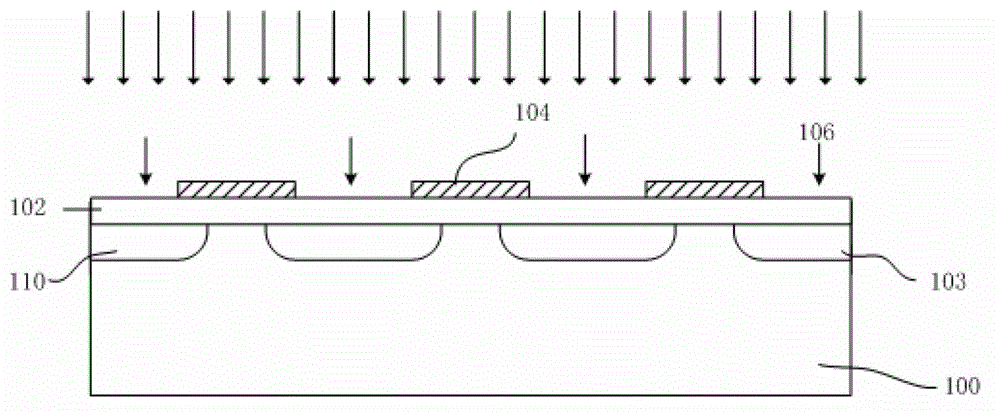

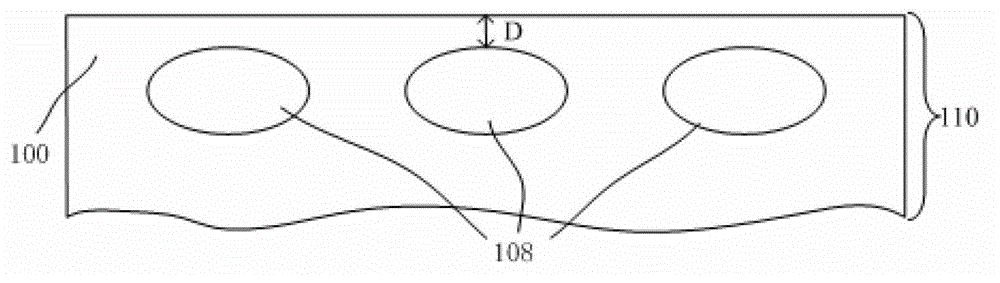

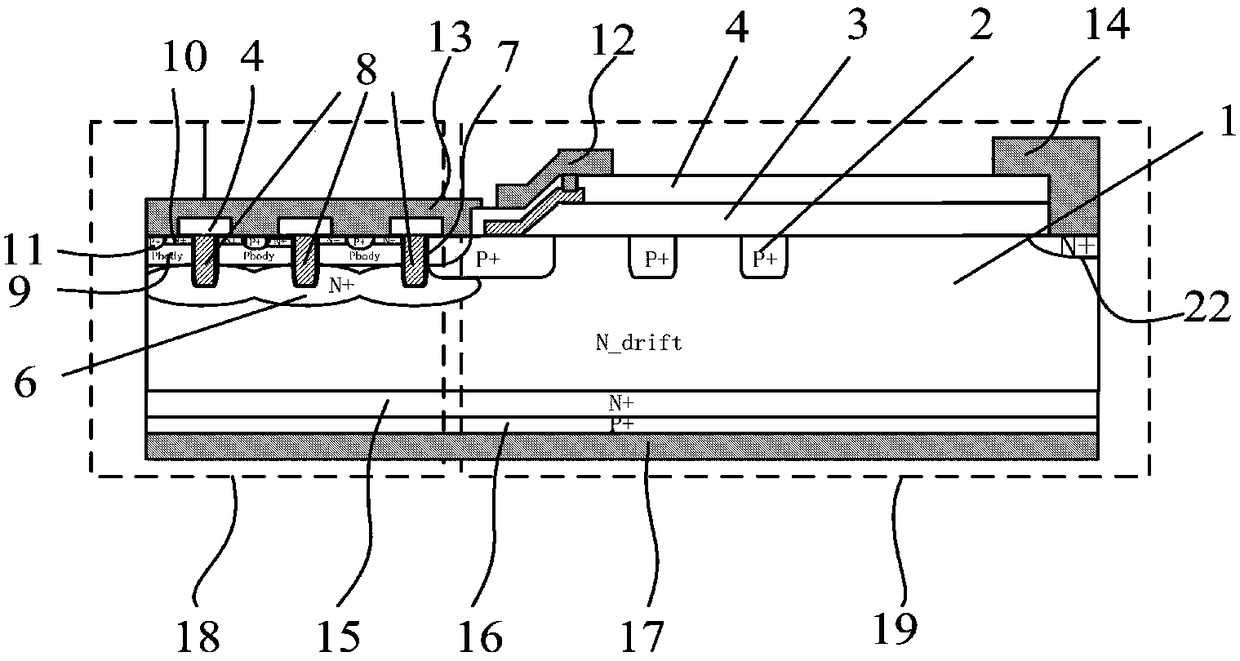

IGBT (Insulated Gate Bipolar Transistor) device with field stop buffer layer and manufacture method of IGBT device

ActiveCN102945858BIncreasing the thicknessLow processing technology requirementsTransistorSemiconductor/solid-state device manufacturingConduction lossTransistor

The invention provides a field stop buffer layer which is formed in an IGBT (Insulated Gate Bipolar Transistor) device. The field stop buffer layer comprises an N type substrate and a P type buried layer formed in the N type substrate. The invention also provides an IGBT device with the field stop buffer region. The IGBT device comprises the field stop buffer layer, an N-epitaxial layer, an IGBT front structure, an anode cavity emission region and a back anode collector electrode, wherein the field stop buffer layer comprises the N type substrate and the P type buried layer formed in the N type substrate; the N-epitaxial layer is formed on the surface of the N type substrate; the IGBT front structure is formed on the surface of the N-epitaxial layer; the anode cavity emission region is formed on the back surface, which is far away from the N-epitaxial layer, of the N type substrate; and the back anode collector electrode is formed on the anode cavity emission region. The invention also provides a manufacture method of the IGBT device with the field stop buffer layer. Through increasing the thickness of the field stop buffer layer and regulating the concentration and the thickness between the P type buried layer and the N type substrate, the current density of the IGBT device is increased, and the conduction loss is reduced.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

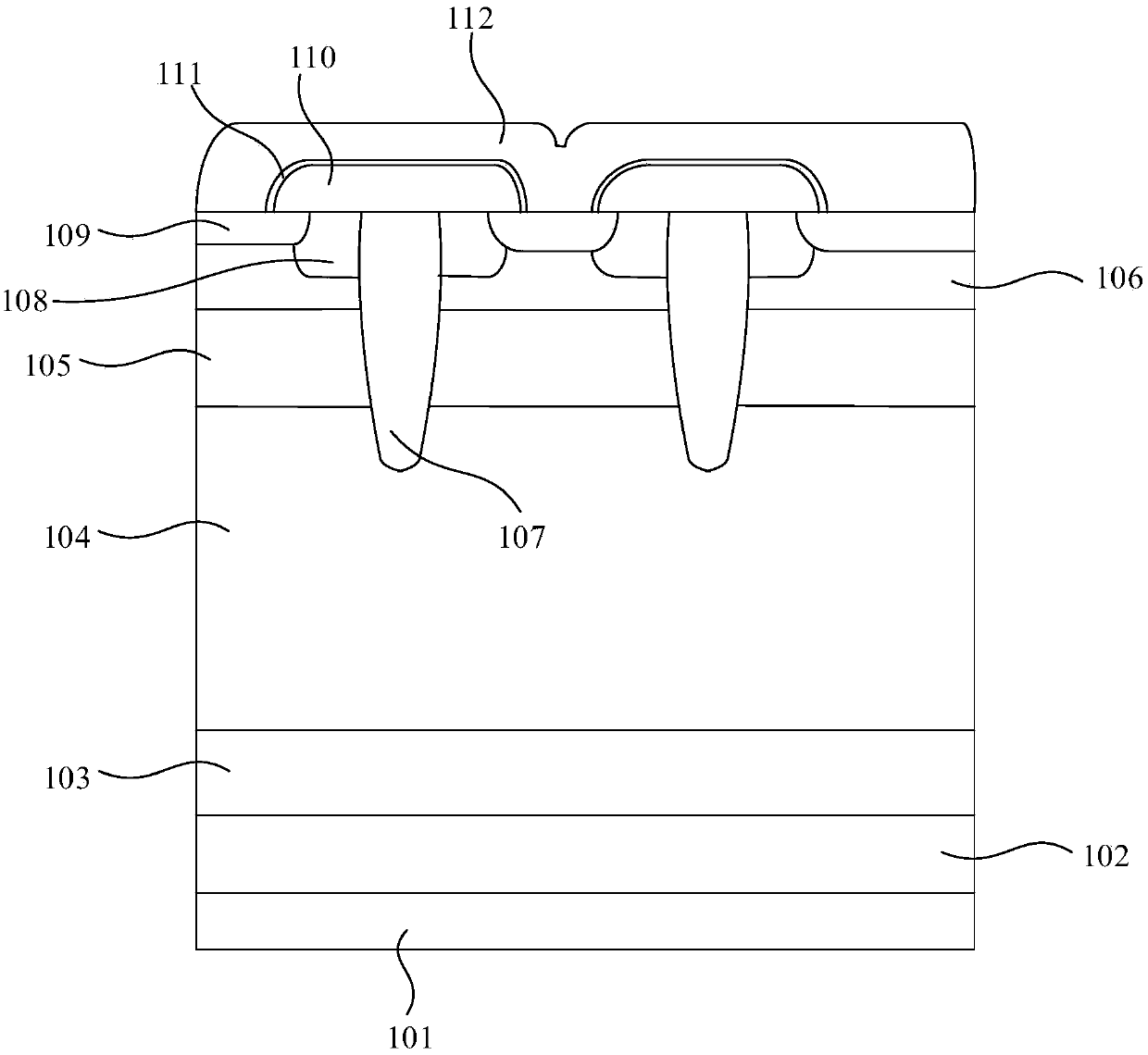

IGBT device with carrier storage structure and manufacturing method thereof

ActiveCN105633139BReduce saturation pressure dropEnhanced conductance modulation effectSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropBody area

The invention relates to an IGBT device with a carrier storage structure and a manufacturing method thereof. An active area of the IGBT device adopts a groove structure; a second conduction type body area is arranged in a first conduction type drifting area of the active area; a cellular groove is located in the second conduction type body area and deeply extends into the first conduction type drifting area below the second conduction type body area; the carrier storage structure is arranged in the first conduction type drifting area of the active area; the carrier storage structure comprises a first conduction type carrier storage area which is used for completely surrounding the inner and outer walls, extending in the first conduction type drifting area, of the cellular groove; and the doping concentration of the first conduction type carrier storage area is greater than the doping concentration of the first conduction type drifting area. According to the IGBT device with the carrier storage structure and the manufacturing method thereof, the relatively low breakover voltage drop and extremely rapid turnoff characteristic can be satisfied at the same time, the pressurization breakdown position can be adjusted to a cellular area to ensure relatively high voltage surge resistance, the chip manufacturing cost is not increased, and the chip area is reduced.

Owner:WUXI NCE POWER

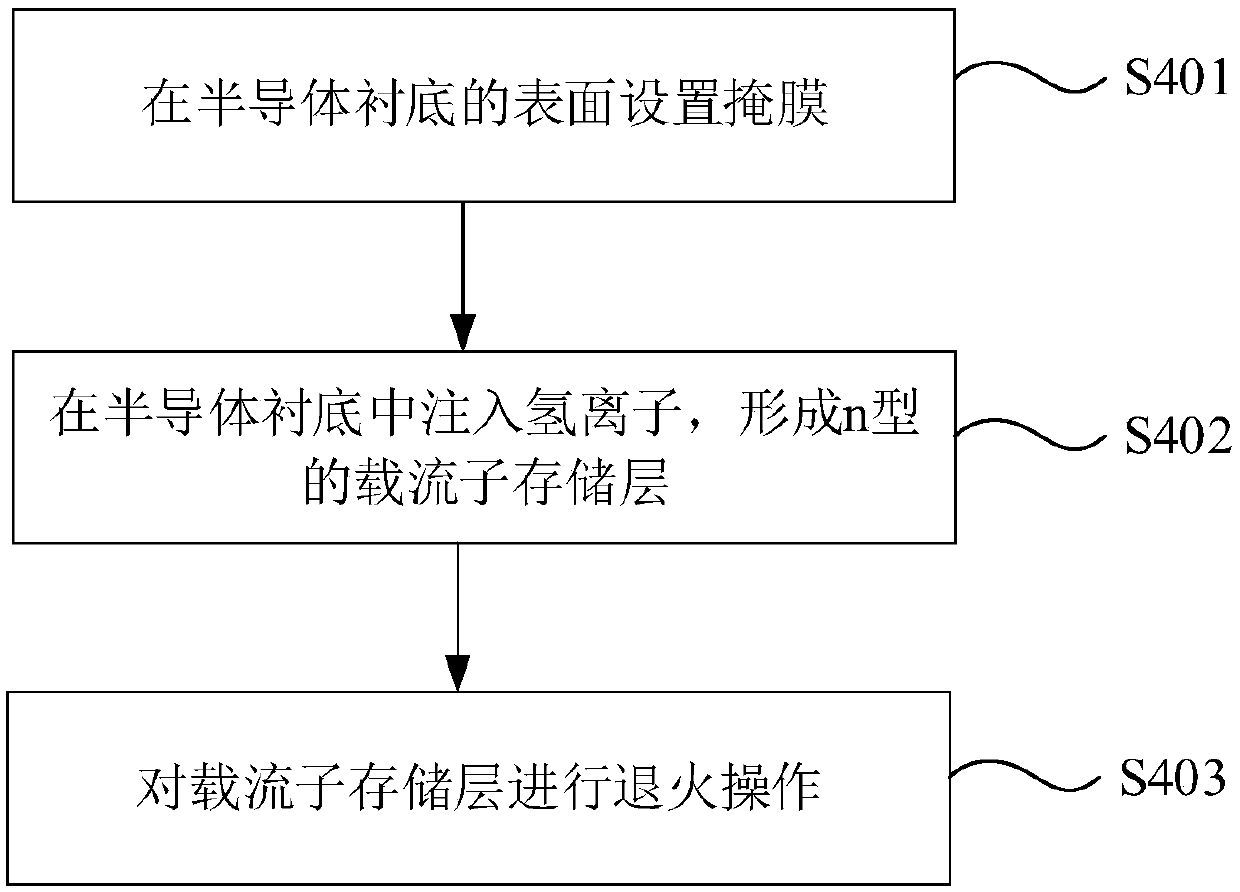

IGBT and manufacturing method thereof

PendingCN110416073AReduce saturation pressure dropShort lifeSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenCharge carrier

The invention discloses an IGBT and a manufacturing method thereof. The manufacturing method of the IGBT comprises the following steps of implanting hydrogen ions into a semiconductor substrate and forming an n-type carrier storage layer. According to the IGBT and the manufacturing method thereof disclosed by the invention, a hydrogen ion implantation technology is adopted in the step of fabricating the carrier storage layer, thereby playing a role of an n-type hole blocking layer after the carrier storage layer is formed and forming a recombination center. Therefore, a saturation voltage dropcan be reduced, and meanwhile, the minority carrier lifetime is effectively shortened.

Owner:ADVANCED SEMICON MFG CO LTD

Silicon germanium heterojunction bipolar transistor

ActiveCN102456726BImprove breakdown voltageRaise the eigenfrequencySemiconductor/solid-state device manufacturingSemiconductor devicesSaturation voltageIon implantation

The invention discloses a silicon germanium heterojunction bipolar transistor. The collector region of the silicon germanium heterojunction bipolar transistor consists of a first ion-implanted region which is formed in an active region, and second and third ion-implanted regions which are formed at the bottoms of field oxide regions on the two sides of the active region respectively. The third ion-implanted region is at a longitudinal distance away from the bottom surface of the field oxide region, and the width of the third ion-implanted region is the same as that of the field oxide region. The second ion-implanted region is positioned at the top of the ion-implanted region, and the bottom of the second ion-implanted region is overlapped and connected with the third ion-implanted region.The depth of the first ion-implanted region is greater than the depth of the bottom of the field oxide region, and the bottom of the first ion-implanted region is connected with the second ion-implanted region. The dosage concentration of the third ion-implanted region is greater than that of each of the first and second ion-implanted regions. Deep hole contact in the field oxide region at the top of a pseudo buried layer leads the collector region out. By the silicon germanium heterojunction bipolar transistor, the breakdown voltage of a device can be increased, relatively higher characteristic frequency can be maintained, the series resistance of the collector region can be decreased and the saturation voltage drop of the device can be decreased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Superjunction IGBT with cutoff reverse conduction field and manufacturing method thereof

InactiveCN110265299AReduce saturation pressure dropImprove power densityTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

The invention provides a superjunction IGBT with a cutoff reverse conduction field. A second semiconductor material is implanted in a first semiconductor substrate to form a reverse conducting structure with the first semiconductor substrate. A field stopping layer and a second semiconductor material epitaxial layer with a low doping concentration are successively stacked on the upper surface of the first semiconductor substrate. A first semiconductor material and a second semiconductor material having the same concentration are implanted in the second semiconductor material epitaxial layer with the low doping concentration. The first semiconductor material and the second semiconductor material alternately form a superjunction structure multiple times along a plane wherein the epitaxial layer is located. The invention also provides a method for manufacturing the IGBT. The superjunction IGBT with a cutoff reverse conduction field and its manufacturing method can effectively reduce the saturation voltage drop of the IGBT and obtain high power density, can make the IGBT thinner and smaller, integrate a reverse conducting diode, and reduce manufacturing cost.

Owner:厦门芯达茂微电子有限公司

Insulated gate bipolar transistor and manufacturing method thereof

ActiveCN111933702AAccurate control of junction depthImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesVirtual cellCell region

The invention provides an insulated gate bipolar transistor and a manufacturing method thereof, and the manufacturing method of the insulated gate bipolar transistor comprises the steps: providing a substrate which is provided with a cell region and a virtual cell region; forming a gate structure in the substrate, wherein the gate structure separates the cell region from the virtual cell region; and forming a well region in the substrate of the virtual cellular region by adopting high-energy ion implantation, so that a PN junction is formed between the well region and the substrate, and the top surface of the well region is lower than the top surface of the substrate and is not lower than the bottom surface of the gate structure. According to the technical scheme, the junction depth of thePN junction in the virtual cellular region can be accurately controlled, so that the withstand voltage of the device is improved, the saturation voltage drop of the device is reduced, and the stability and uniformity of the threshold voltage are improved.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP +1

Method for manufacturing power transistor

ActiveCN102956491AReduce in quantityReduce accumulationSemiconductor/solid-state device manufacturingDielectric layerSaturation voltage

The invention discloses a method for manufacturing a power transistor. By the method, insulating dielectric layers formed on the top of grid polycrystalline silicon and side-wall dielectric layers formed on side surfaces of the insulating dielectric layers are used as etching hard masks of a pressure bearing region, the quantity of masks required by a front-surface process is reduced, and the density of a transistor in a chip can be increased. A P-type polycrystalline silicon layer is planted into a P-type well region and is subjected to short circuit with a source electrode via metal contact, cavity flows of the P-type well region flow out advantageously, and accumulated cavities are reduced, so that latch-up resistance of a device is improved. The method is favorable for obtaining a power device with low conducting resistance, low saturation voltage drop and high current driving capacity.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP